# **Inductive Sensor Interface IC with Embedded MCU**

# **Features**

- · Built-In Oscillator for Driving Primary Coil

- Two Independent Analog Channels with Demodulation

- · 32-Bit Cortus APS1 RISC MCU

- Two 13-Bit ADCs

- · One 12-Bit DAC

- · One 16-Bit PWM

- · Fault Detection and Protection

- Digital Calibration with Nonvolatile Configuration Storage (EEPROM)

- · Protected Watchdog Timer

- · Low-Temperature Drift

- Wide Range Supply Voltage (4.0V to 11.0V)

- -40°C to +150°C Operation

- · Excellent Long-Term Stability

- · SENT Output

- · Asynchronous PSI5 Output

- · AEC-Q100 Certification

- ISO26262 ASIL B Support

# **Applications**

- · Automotive Control

- · ATE Equipment

- · Industrial Process Control

- · Smart Energy Saving Control

# **Description**

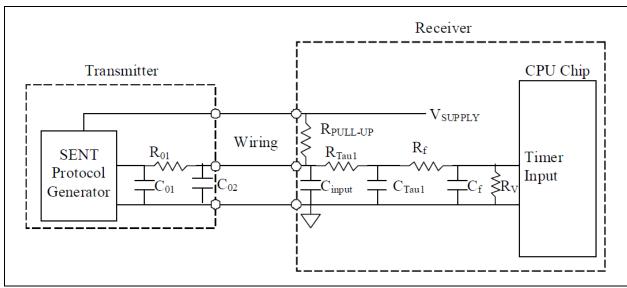

The LX3302A is a highly integrated programmable data conversion IC designed for interfacing to, and managing of, inductive sensors. The device includes an integrated oscillator circuit for driving the primary coil of an inductive sensor, along with two independent analog conversion paths for conditioning, converting and processing of two analog signals from the secondary coils of the sensor. Each path includes an EMI filter, demodulator, anti-alias filter, programmable amplifier and a 13-bit Sigma-Delta Analog-to-Digital Converter.

Each analog signal path includes digital calibration capability, which allows the complete analog path (including the external sensors) to be calibrated during the system manufacturing process. The calibration information is written to internal EEPROM resulting in improved production yields and in-line system upgrades.

The LX3302A integrates a 32-bit RISC processor, which provides programmable digital filtering and signal processing functions.

System interfaces include a SENT or PSI5 serial port, programmable PWM output and a 12-bit Digital-to-Analog Converter analog buffed output.

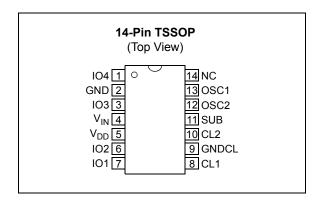

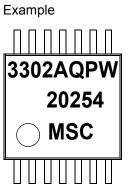

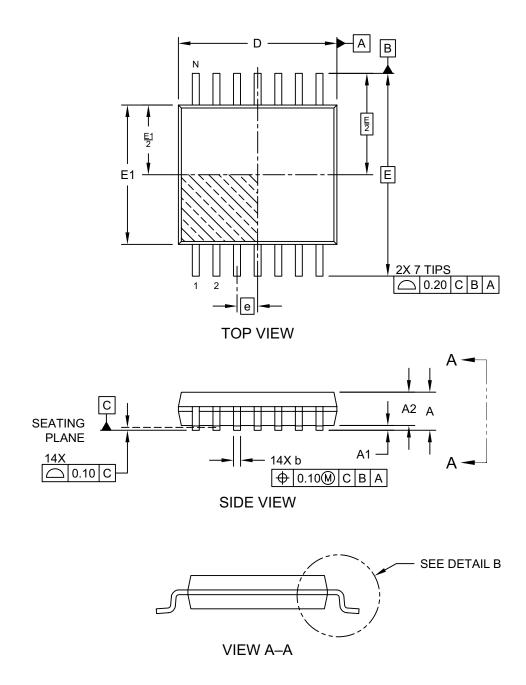

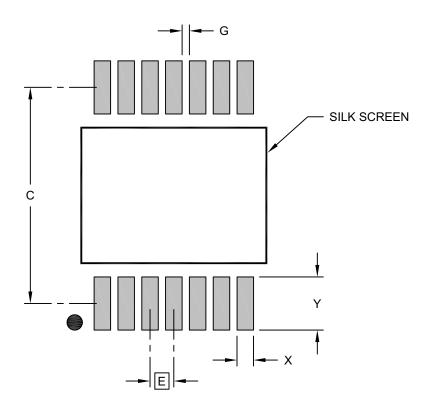

The LX3302A is offered in a 14-lead TSSOP package. The device is specified over a temperature range of -40°C to +150°C, making it suitable for a wide range of commercial, industrial, medical and/or automotive sensor applications.

# **Package Types**

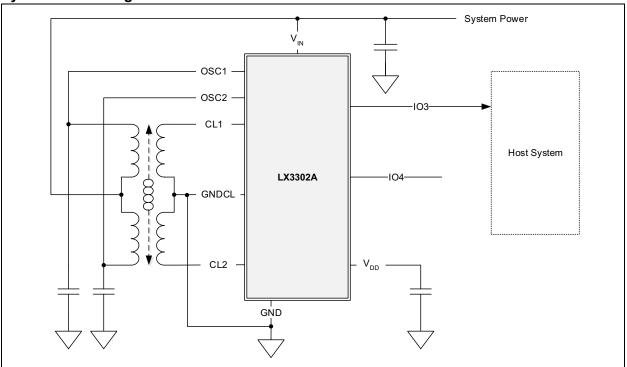

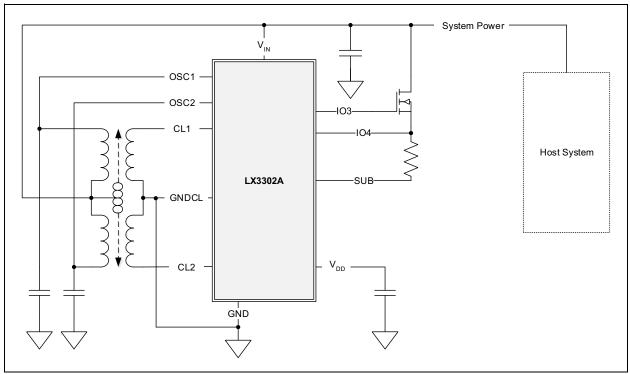

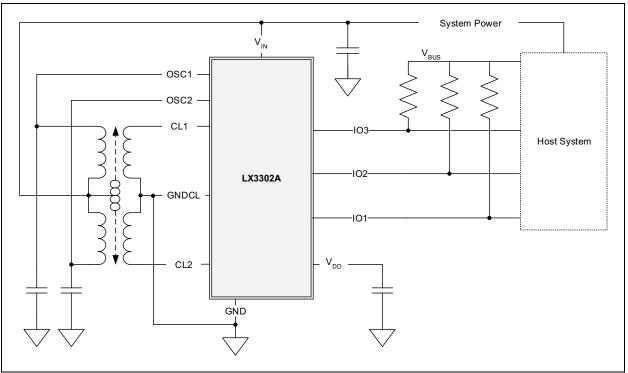

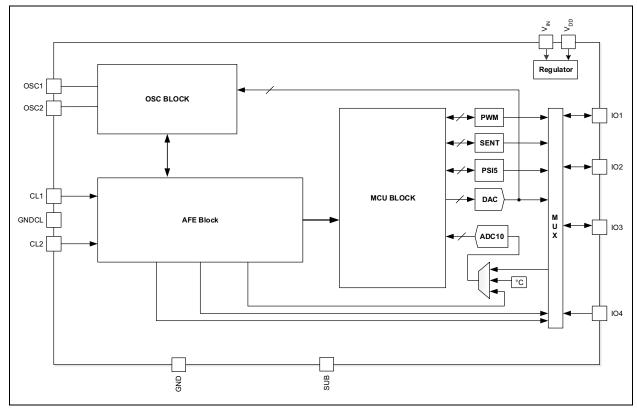

# **System Block Diagrams**

FIGURE 1: System Block Diagram: LX3302A.

FIGURE 2: System Block Diagram with PSI5 Output: LX3302A.

FIGURE 3: System Block Diagram with Open-Drain Outputs: LX3302A.

FIGURE 4: LX3302A Block Diagram.

# **Ordering Information**

| Ambient<br>Temperature | Туре                              | Package       | Part Number   | Packaging Type |

|------------------------|-----------------------------------|---------------|---------------|----------------|

| -40°C to +150°C        | RoHS2 Compliant,                  | 14-Lead TSSOP | LX3302AQPW    | Tube           |

|                        | Pb-Free MSL1,<br>AEC-Q100 Grade 0 |               | LX3302AQPW-TR | Tape and Reel  |

# 1.0 ELECTRICAL CHARACTERISTICS

# 1.1 Electrical Specifications

# Absolute Maximum Ratings†

| Supply Input Voltage Pin (V <sub>IN</sub> )                      |                |

|------------------------------------------------------------------|----------------|

| Load Current on V <sub>DD</sub> Pin                              | 1 mA to 15 mA  |

| Voltage on OSC1, OSC2 and IO3 Pins                               | 0.3V to 20V    |

| Voltage on IO3 Pin                                               |                |

| Voltage on IO1 and IO2 Pins                                      | 0.5V to 6.5V   |

| Current on IO1 and IO2 Pins                                      |                |

| Voltage on IO4, V <sub>DD</sub> , CL1 and CL2 Pins               | 0.5V to 3.6V   |

| Operating Humidity (non-condensing)                              | 0% to 95%      |

| Operating Temperature                                            |                |

| Storage Temperature                                              | 65°C to +150°C |

| Lead Temperature (soldering, 10 seconds)                         | +300°C         |

| Package Peak Temperature for Solder Reflow (40 seconds exposure) | +260°C         |

| ESD Rating – All Pins – HBM (AEC-Q100-002D)                      | ±2 kV          |

| ESD Rating – All Pins – CDM (AEC-Q100-011)                       | ±1.5 kV        |

Notice: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to above maximum rating conditions for extended periods may affect device reliability. All voltages are with respect to GND. All voltages on ESD are with respect to SUB.

# **Recommended Operating Range**

| Parameters                             | Symbol          | Min. | Тур. | Max. | Units | Conditions                                              |

|----------------------------------------|-----------------|------|------|------|-------|---------------------------------------------------------|

| Supply Voltage                         | V <sub>IN</sub> | 4.0  | 5.0  | 6.0  | V     | For normal operation                                    |

| V <sub>IN</sub> EEPROM Program<br>High | VIN_PH          | _    | _    | 18   | V     |                                                         |

| Supply Current                         | I <sub>IN</sub> | _    | _    | 15   | mA    | For normal operation, excluding oscillator tail current |

| Output Current                         | I_IO3_AN0       | -15  | _    | -8   | mA    | IO3 = Analog mode, 0V                                   |

|                                        | I_IO3_AN5       | 6    | _    | 15   |       | IO3 = Analog mode, 0V                                   |

|                                        | I_IO3_OD        | _    | _    | 28   |       | IO3 = OD mode, 0V                                       |

| Internal Clock Frequency               | Fosc            | 8.0  | 8.2  | 8.4  | MHz   |                                                         |

| Operating Temperature                  | T <sub>OP</sub> | -40  | _    | +150 | °C    |                                                         |

# **Electrical Characteristics**

Electrical Specifications: Unless otherwise indicated, the following specifications apply over the operating temperature range of  $-40^{\circ}\text{C} \le T_{\text{A}} \le +150^{\circ}\text{C}$  and the following test conditions:  $V_{\text{IN}} = 5\text{V}$ , f = 8.2 MHz,  $I_{\text{DD}} = 1$  mA, I/O = 0 mA. Typical values are at +25°C.

| Parameters                                                           | Symbol           | Min.       | Тур. | Max. | Units | Conditions                                                                                                     |

|----------------------------------------------------------------------|------------------|------------|------|------|-------|----------------------------------------------------------------------------------------------------------------|

| Power                                                                |                  |            |      |      |       | -                                                                                                              |

| V <sub>IN</sub> Input Voltage                                        | V <sub>IN1</sub> | 4.0        | 5.0  | 11   | V     | For normal operation, IO3 = PSI5                                                                               |

|                                                                      | V <sub>IN2</sub> | 4.0        | 5.0  | 6    | V     | For normal operation, IO1,2,3 = PWM, analog                                                                    |

| V <sub>IN</sub> Supply Current                                       | I <sub>IN</sub>  | _          | 12.3 | 15   | mA    | For normal operation, excluding oscillator tail current, I <sub>DD</sub> = 0 mA, IO1,2,3,4 = 0 mA, f = 8.2 MHz |

| V <sub>IN</sub> Threshold Disabling of IO1 and IO2 Push-Pull Buffers | VIN_DIS_IO       | 6          | 6.4  | 7    | V     |                                                                                                                |

| V <sub>IN</sub> Hysteresis of VIN_DIS_IO                             | VIN_DIS_IOhys    | _          | 0.25 | _    | V     |                                                                                                                |

| V <sub>IN</sub> UVLO High Threshold                                  | VIN_UVLO_HI      | 3.7        | 3.8  | 3.95 | V     | V <sub>IN</sub> POR error enabled                                                                              |

| V <sub>IN</sub> UVLO Hysteresis                                      | VIN_HYST         | _          | 0.05 | _    | V     |                                                                                                                |

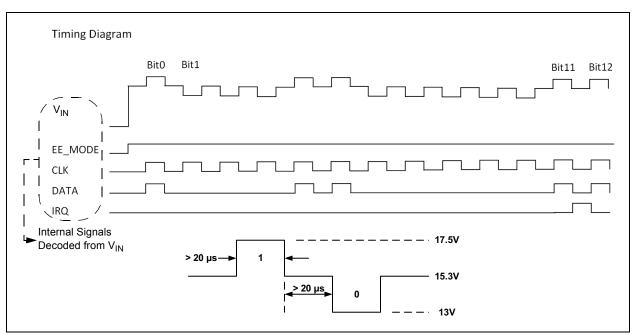

| V <sub>IN</sub> EEMode (EEPROM Progr                                 | ramming)         |            |      |      |       |                                                                                                                |

| Programming Mode<br>Threshold                                        | VIN_TH_EE        | 11.5       | 12   | 12.5 | V     | For EEPROM mode                                                                                                |

| Program Low                                                          | VIN_PL           | 12.6       | 13   | 13.6 | V     | For EEPROM Programming mode                                                                                    |

| Program Idle                                                         | VIN_PI           | 14.9       | 15.3 | 15.8 | V     | For EEPROM Programming mode                                                                                    |

| Program High                                                         | VIN_PH           | 17.1       | 17.5 | 18.0 | V     | For EEPROM Programming mode                                                                                    |

| Duration Time                                                        | td               | 20         | _    | 110  | μs    | Duration time for each voltage state                                                                           |

| Rise Time                                                            | tr               | _          | _    | 2.5  | ms    | To enter EEPROM mode,<br>V <sub>IN</sub> = 15.3V, 10-90%                                                       |

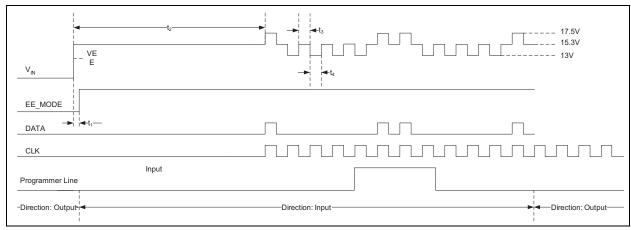

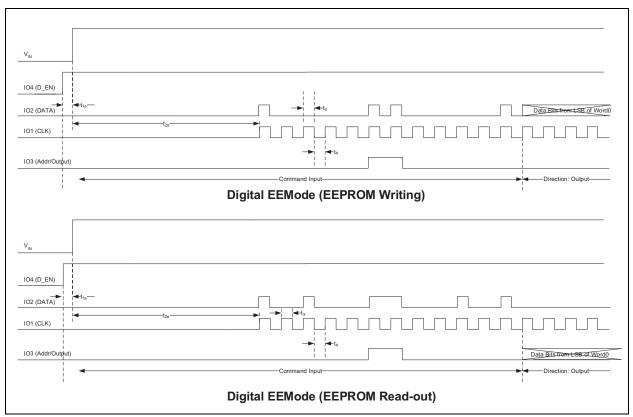

| Digital EEMode (EEPROM Pi                                            | rogramming (IO1, | IO2, IO4)) |      |      |       |                                                                                                                |

| Programming Mode<br>Threshold                                        | VEN_DEE          | 2.5        | _    | _    | V     | For Digital EEMode with IO4                                                                                    |

| CLK High Threshold                                                   | V_EECLK_HI       | 2.5        | _    | _    | V     | IO1 input for Digital EEMode                                                                                   |

| CLK Low Threshold                                                    | V_EECLK_LO       | _          | _    | 0.8  | V     | IO1 input for Digital EEMode                                                                                   |

| CLK Rise/Fall Time                                                   | tr_CLK           | _          | 1    | _    | μs    |                                                                                                                |

| CLK Duty                                                             | Duty_CLK         | _          | 50   | _    | %     |                                                                                                                |

| Data High Threshold                                                  | V_EEDATA_HI      | _          | 2.5  | _    | V     | IO2 input for Digital EEMode                                                                                   |

| Data Low Threshold                                                   | V_EEDATA_LO      | _          | _    | 8.0  | V     | IO2 input for Digital EEMode                                                                                   |

| Data Rise/Fall Time                                                  | Tr_DATA          | _          | 1    | _    | μs    |                                                                                                                |

| Duration Time for CLK                                                | Td_CLK           | 20         | _    | 110  | μs    | Duration time for each state                                                                                   |

| VEN_DEE Rise Time                                                    | Tr_CLK           | _          | 10   | _    | μs    | To enter Digital EEMode with IO4                                                                               |

| V <sub>DD</sub> Reference Voltage                                    |                  |            |      |      |       |                                                                                                                |

| Output Voltage                                                       | $V_{DD}$         | 3.24       | 3.3  | 3.36 | ٧     | I <sub>DD</sub> = 5 mA, after trimming                                                                         |

| Output Current                                                       | I <sub>DD</sub>  | _          | _    | 5    | mA    | Additional current sourced to external load(s)                                                                 |

| V <sub>DD</sub> POR Threshold                                        | VDD_POR          | _          | 2.9  | _    | V     | Monitor V <sub>DD</sub> , rising edge                                                                          |

| V <sub>DD</sub> UVLO Hysteresis                                      | VDD_Hyst         | _          | 0.20 | _    | V     | V <sub>DD</sub> UVLO hysteresis                                                                                |

| Short Current V <sub>DD</sub> to GND                                 | IDD_SC_5V        |            | 120  | _    | mA    | Shorted to GND, V <sub>IN</sub> = 5V, +25°C                                                                    |

| V <sub>DD</sub> Over Ripple Threshold                                | VDD_RIPPLE       | _          | 300  | _    | mVpp  | Noise frequency > 10 MHz                                                                                       |

Note 1: For 3 µs nominal clock tick including clock accuracy. For higher clock tick, times need to be increased proportionally.

# **Electrical Characteristics (Continued)**

Electrical Specifications: Unless otherwise indicated, the following specifications apply over the operating temperature range of  $-40^{\circ}\text{C} \le T_A \le +150^{\circ}\text{C}$  and the following test conditions:  $V_{\text{IN}} = 5V$ , f = 8.2 MHz,  $I_{\text{DD}} = 1$  mA,  $I_{\text{OD}} = 0$  mA. Typical values are at +25°C.

| -40°C ≤ T <sub>A</sub> ≤ +150°C and the f        | following test cond | tions: V <sub>IN</sub> : | = 5V, f = 8.2 | MHz, I <sub>DD</sub> : | = 1 mA, I/C | = 0 mA. Typical values are at +25°C.                             |

|--------------------------------------------------|---------------------|--------------------------|---------------|------------------------|-------------|------------------------------------------------------------------|

| Parameters                                       | Symbol              | Min.                     | Тур.          | Max.                   | Units       | Conditions                                                       |

| Oscillator OSC1 and OSC2                         |                     |                          |               |                        |             |                                                                  |

| Center Tap Voltage                               | $V_{TAP}$           | _                        | 5             | _                      | V           | V <sub>IN</sub> = 5V                                             |

| Center Tap Output Voltage<br>Detection Threshold | VTAP_OPEN           | _                        | 3.3           | _                      | V           | V <sub>IN</sub> = 5V                                             |

| IO1, IO2, IO3 Voltage from OSC1, OSC2 Pins       | VOSC_OV             | _                        | 0             | _                      | V           | V <sub>IN</sub> = 0V and OSC pins driven by external signal      |

| OSC AC Swing Peak<br>Overvoltage Detection       | VOSC_OV             | 10                       | _             | _                      | Vpp         | AC coupled                                                       |

| OSC AC Swing Peak<br>Undervoltage Detection      | VOSC_UV             | _                        | _             | 3                      | Vpp         | AC coupled                                                       |

| Total Tank DC Tail Current                       | ITK                 | 0                        | _             | 10                     | mA          | V <sub>TAP</sub> = 5V                                            |

| Amplitude of OSC1, OSC2                          | V <sub>OSC</sub>    | 3.1                      | _             | 9.9                    | Vpp         | V <sub>TAP</sub> = 5V                                            |

| Oscillation Frequency Range                      | FOSC_R              | 1                        | _             | 6                      | MHz         | V <sub>TAP</sub> = 5V                                            |

| Frequency Variation                              | FOSCTOL             | -5                       | _             | 5                      | %           | V <sub>TAP</sub> = 5V                                            |

| Oscillator Inductance                            | LOSC                | 3                        | 6             | 12                     | μH          | V <sub>TAP</sub> = 5V                                            |

| Tank Circuit Quality Factor                      | QOSC                | 10                       | 22            | 30                     | _           | $V_{TAP} = 5V ( X /R)$                                           |

| Harmonics                                        | HOSC                | _                        | _             | 2                      | %           | V <sub>TAP</sub> = 5V, GDNT                                      |

| Resistance Between OSC1 and OSC2                 | ROSC1&2_HI          | 500                      | 1000          | _                      | kΩ          | OSC1 = 1 Vpp, OSC2 = GND                                         |

| Resistance Between OSC1 and GND                  | ROSC1_GND           | 500                      | 2000          | _                      | kΩ          | V <sub>IN</sub> = 0V, OSC1 = 5V, measure current from OSC1 to 5V |

| Resistance Between OSC2 and GND                  | ROSC2_GND           | 500                      | 2000          | _                      | kΩ          | V <sub>IN</sub> = 0V, OSC1 = 5V, measure current from OSC1 to 5V |

| Resistance Between OSC1 and V <sub>DD</sub>      | ROSC1_VDD           | 500                      | 1000          | _                      | kΩ          |                                                                  |

| Resistance Between OSC2 and V <sub>DD</sub>      | ROSC2_VDD           | 500                      | 1000          | _                      | kΩ          |                                                                  |

| Oscillator Tail Current Digita                   | I Control OSCDA     | С                        |               |                        |             | •                                                                |

| OSCDAC Resolution                                | _                   | _                        | 11            | _                      | bits        |                                                                  |

| OSCDAC Range                                     | _                   | 0                        | _             | 2047                   | bits        |                                                                  |

| OSCDAC Allowable Max. Tail<br>Current            | Imax                | _                        | _             | 15                     | mA          | Over process and temperature range                               |

| Zero Code Error Current                          | Izero               | _                        | 25            | _                      | μΑ          |                                                                  |

| Step Current                                     | Istep               | 4.88                     | 6.9           | 8.88                   | μΑ          | IOSCDAC/VALOSCDAC                                                |

| ADC1 and ADC2                                    |                     |                          |               |                        |             | •                                                                |

| Resolution                                       | ADC_Res             | _                        | 13            | _                      | bits        |                                                                  |

| Integral Nonlinearity                            | ADC_INL             | -1                       | _             | 1                      | LSB         | GDNT                                                             |

| SINC or SINC+FIR Filter 1 ar                     | nd 2                |                          |               |                        |             | •                                                                |

| Crosstalk Rejection                              | FLTR_CTR            | _                        | _             | -44                    | dB          |                                                                  |

| PSRR                                             | FLTR_PSRR           | _                        | _             | -50                    | dB          | GDNT                                                             |

| Digital-to-Analog Converter                      | (DAC)               |                          |               |                        |             |                                                                  |

| DAC Resolution                                   | DACR                | _                        | 12            | _                      | bits        |                                                                  |

| Output Load (RL)                                 |                     |                          | ·             | ·                      |             |                                                                  |

| Output Load Range                                | RL                  | 0.9                      | 10            | 100                    | kΩ          |                                                                  |

| Maximum Allowable Output<br>Voltage              | $V_{OHmax}$         | _                        | 85            | _                      | %VIN        | $RL = 0.9 \sim 3 \text{ k}\Omega$                                |

Note 1: For 3 µs nominal clock tick including clock accuracy. For higher clock tick, times need to be increased proportionally.

# **Electrical Characteristics (Continued)**

Electrical Specifications: Unless otherwise indicated, the following specifications apply over the operating temperature range of  $-40^{\circ}\text{C} \le T_{A} \le +150^{\circ}\text{C}$  and the following test conditions:  $V_{IN} = 5V$ , f = 8.2 MHz,  $I_{DD} = 1$  mA, I/O = 0 mA. Typical values are at  $+25^{\circ}\text{C}$ .

| Parameters  101, IO2 Analog Outputs    | Symbol                       | Min.                  | Тур. | Max.     | Units | Conditions                                                                                                                    |

|----------------------------------------|------------------------------|-----------------------|------|----------|-------|-------------------------------------------------------------------------------------------------------------------------------|

|                                        |                              |                       |      |          |       | Conditions                                                                                                                    |

| and lavel Outer: 11/-11                |                              |                       |      |          |       |                                                                                                                               |

| Low-Level Output Voltage               | $V_{OLA}$                    | 0                     | _    | 0.3      | V     | Pull-up load ≥ 10 k $\Omega$ to V <sub>IN</sub>                                                                               |

| High-Level Output Voltage              | V <sub>OHA</sub>             | V <sub>IN</sub> – 0.3 | _    | VIN      | V     | Pull-down load ≥ 10 kΩ to GND,<br>Gain = $V_{IN}/V_{DD}$                                                                      |

| Output Short-Circuit Current           | ISHORT_12A                   | 9                     | _    | 20       | mA    | Short to 0 or short to 5V                                                                                                     |

| IO1, IO2 Digital Outputs               |                              |                       |      |          |       |                                                                                                                               |

| Low-Level Output Voltage               | $V_{OLD}$                    | _                     | _    | 3        | %VIN  | Pull-up load ≥ 10 kΩ to V <sub>IN</sub>                                                                                       |

| High-Level Output Voltage              | V <sub>OHD</sub>             | 97                    | _    | _        | %VIN  | Pull-down load ≥ 10 k $\Omega$ to GND                                                                                         |

| Output Short-Circuit Current           | ISHORT_12D                   | 9                     | _    | 20       | mA    | Short to 0 or short to 5V                                                                                                     |

| IO1, IO2 Digital Inputs (Addre         | ess for V <sub>IN</sub> EEMo | de)                   |      |          |       |                                                                                                                               |

| High-Level Input Voltage               | $V_{IHD}$                    | 2.5                   | _    | _        | V     |                                                                                                                               |

| Low-Level Input Voltage                | $V_{ILD}$                    |                       | _    | 0.8      | V     |                                                                                                                               |

| Input Impedance                        | RIN_12                       | 200                   | _    | _        | kΩ    |                                                                                                                               |

| Input Capacitance                      | CIN_12                       |                       | _    | 5        | pF    |                                                                                                                               |

| IO3 Analog Output                      |                              |                       |      |          |       |                                                                                                                               |

| Output Load                            | RL_3                         | 0.9                   | 10   | 100      | kΩ    |                                                                                                                               |

| Output Low                             | VLO_IO3                      | _                     | 40   | _        | mV    | Pull-up load ≥ 10 kΩ to V <sub>IN</sub>                                                                                       |

| Output Short-Circuit Current           | SHORT1_3A                    | _                     | 12   | 17       | mA    | Short to GND or short to V <sub>IN</sub>                                                                                      |

|                                        | SHORT2_3A                    |                       | _    | 45       | mA    | Short to 14V                                                                                                                  |

| V <sub>IN</sub> Ratiometric Error      | RaErr_3A                     | -0.5                  | 0    | 0.5      | %VIN  |                                                                                                                               |

| O3 Digital Output                      |                              |                       |      |          |       |                                                                                                                               |

| High-Level Output Voltage              | VOH_3                        | 98                    | _    | _        | %VIN  | Pull-up load ≥ 10 kΩ to V <sub>IN</sub>                                                                                       |

| Low-Level Output Voltage               | VOL_3                        | _                     | _    | 2        | %VIN  | Pull-down load ≥ 10 kΩ to GND                                                                                                 |

| Output Short-Circuit Current           | ISHORT_3A                    | 25                    | _    | 35       | mA    | Short to 0 or short to 5V                                                                                                     |

| IO3 Input                              |                              |                       |      |          |       |                                                                                                                               |

| High-Level Input Voltage               | VIH_3IN                      | 2.5                   | _    | _        | V     | Pull-up load ≥ 10 k $\Omega$ to V <sub>IN</sub>                                                                               |

| Low-Level Input Voltage                | VIL_3IN                      | _                     | _    | 0.8      | V     | Pull-down load ≥ 10 kΩ to GND                                                                                                 |

| Input Impedance                        | RIN_4                        | 450                   | _    | _        | kΩ    |                                                                                                                               |

| Input Capacitance                      | CIN_3                        | _                     | _    | 5        | pF    |                                                                                                                               |

| O4 Digital Input                       |                              |                       |      |          |       |                                                                                                                               |

| High-Level Input Voltage               | VIH_4                        | 2.5                   | _    | $V_{DD}$ | V     | Pull-up load ≥ 10 kΩ to V <sub>IN</sub>                                                                                       |

| Low-Level Input Voltage                | VIL_4                        | 0                     | _    | 0.8      | V     | Pull-down load ≥ 10 k $\Omega$ to GND                                                                                         |

| Input Impedance                        | RIN_4                        | 450                   | _    | _        | kΩ    |                                                                                                                               |

| Input Capacitance                      | CIN_4                        | _                     | _    | 5        | pF    |                                                                                                                               |

| O3 Fault Output                        |                              |                       |      |          |       |                                                                                                                               |

| Ground Off Output High Level           | VOH_IO3GF1                   | 99                    | 100  | _        | %VIN  | Broken GND, 100 k $\Omega \ge RL_IO3$ to $V_{IN}$                                                                             |

| V <sub>IN</sub> Open Output Low Level  | VOL_IO3_IN                   |                       | 0    | 1        | %VIN  | Broken $V_{IN}$ , RL_IO3 = 10 k $\Omega$ to GND                                                                               |

| V <sub>IN</sub> Open Output High Level | VOH_IO3_VIN1                 | 97                    | 99   | _        | %VIN  | Broken $V_{IN}$ , RL_IO3 $\geq$ 3 k $\Omega$ to $V_{IN}$                                                                      |

|                                        | VOH_IO3_VIN2                 | 97                    | 99   | _        | %VIN  | Broken $V_{IN}$ and pull-up load to $V_{IN}$ , 1 $k\Omega \le RL \le 3$ $k\Omega$ , with 3 $k\Omega$ between $V_{IN}$ and GND |

| Fault Output Low Level                 | VIO3_FL10K                   | _                     |      | 3        | %VIN  | RL_IO3 = 10 k $\Omega$ to V <sub>IN</sub>                                                                                     |

| Main Oscillator                        |                              |                       |      |          |       |                                                                                                                               |

| Main Oscillator Frequency              | F <sub>CLK</sub>             | _                     | 8.2  |          | MHz   |                                                                                                                               |

| Tolerance                              | FCLK_TOL                     | -1.5                  | _    | 1.5      | %     | T <sub>A</sub> = +25°C                                                                                                        |

Note 1: For 3 µs nominal clock tick including clock accuracy. For higher clock tick, times need to be increased proportionally.

# **Electrical Characteristics (Continued)**

Electrical Specifications: Unless otherwise indicated, the following specifications apply over the operating temperature range of  $-40^{\circ}\text{C} \le T_{A} \le +150^{\circ}\text{C}$  and the following test conditions:  $V_{IN} = 5V$ , f = 8.2 MHz,  $I_{DD} = 1$  mA,  $I_{DD} = 0$  mA. Typical values are at +25°C.

| Parameters                                                             | Symbol            | Min.      | Тур.   | Max. | Units  | Conditions                                                                           |

|------------------------------------------------------------------------|-------------------|-----------|--------|------|--------|--------------------------------------------------------------------------------------|

| Processor Resources                                                    |                   |           |        |      |        |                                                                                      |

| Data Bus                                                               | PR_DBUS           | _         | 32     | _    | bits   |                                                                                      |

| Instruction Size                                                       | PR_INSS           | _         | 32     | _    | bits   |                                                                                      |

| EEPROM Size                                                            | PR_EEPRMS         | _         | 32     | _    | words  | 16-bit words                                                                         |

| Number of EEPROM                                                       | PR_NEEWC1         | 100       | _      | _    | cycles | T <sub>A</sub> = +25°C, GDNT                                                         |

| Erase/Write Cycles                                                     | PR_NEEWC2         | 100       | _      | _    | cycles | T <sub>A</sub> = +125°C, GDNT                                                        |

| Max. Temperature for<br>Erase/Write EEPROM                             | PR_TmaxEW         | _         | +125   | _    | °C     |                                                                                      |

| EEPROM Data Retention                                                  | PR_DataR1         | 10        | _      | _    | Years  | T <sub>A</sub> = +85°C                                                               |

|                                                                        | PR_DataR2         | 1         | _      | _    | Years  | T <sub>A</sub> = +125°C                                                              |

|                                                                        | PR_DataR3         | 0.3       | _      | _    | Years  | T <sub>A</sub> = +150°C                                                              |

| PWM Controller                                                         |                   |           | •      |      |        |                                                                                      |

| Clock Prescale Bit                                                     | PWM_CPSB          | _         | 2      | _    | bits   | Divider = 1, 2, 4, 8                                                                 |

| PWM Clock                                                              | PWM_CLK           |           | 8.2    | _    | MHz    |                                                                                      |

| PWM Period                                                             | PWM_PER           |           | 16     | _    | bits   |                                                                                      |

| PWM Duty                                                               | PWM_Duty          |           | 16     | _    | bits   |                                                                                      |

| PWM Jitter                                                             | PWM_Jitter        |           | 0.2    | _    | %D     | No clamped output                                                                    |

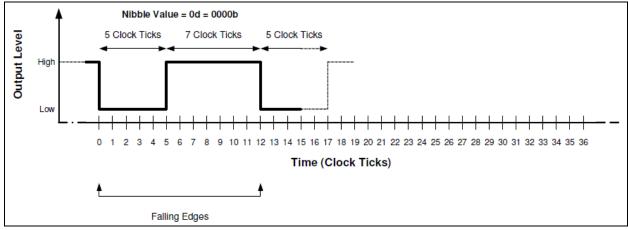

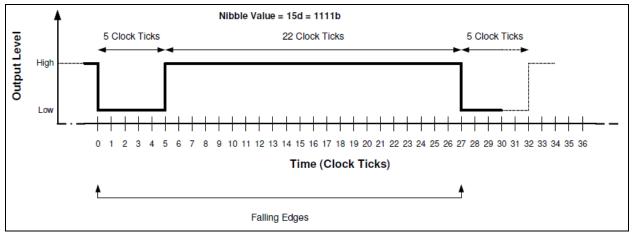

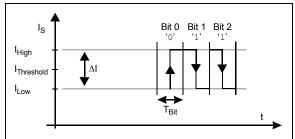

| Single-Edge Nibble Transmi                                             | ssion (SENT) Inte | rface and | Driver |      |        |                                                                                      |

| Low State Voltage                                                      | SENTVOL           | _         | _      | 0.5  | V      | IL = 5 mA                                                                            |

| High State Voltage                                                     | SENTVOH           | 4.1       | _      | _    | V      | IL = 5 mA, V <sub>IN</sub> = 5V                                                      |

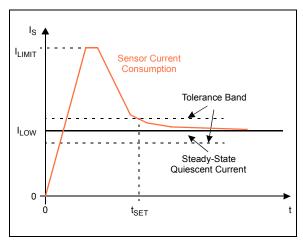

| Average Current Consumption                                            | SENTIS            | _         | _      | 15   | mA     | Average current consumption from receiver supply over one message                    |

| Supply Current Ripple                                                  | SENTISCR          | _         | _      | 9    | mApp   | Peak-to-peak variation                                                               |

| Square Wave Rising Time                                                | SENTTR            | _         | 0.3    | _    | μs     | From 1.1V to 3.8V. Load = 5 mA,<br>$C_{OUT}$ = 1 nF, SENTCLK = 3 $\mu$ s<br>(Note 1) |

| Square Wave Falling Time                                               | SENTTF            | _         | 0.3    | _    | μs     | From 3.8V to 1.1V. Load = 5 mA,<br>$C_{OUT}$ = 1 nF, SENTCLK = 3 $\mu$ s<br>(Note 1) |

| Edge-to-Edge Jitter with<br>Static Environment for Any<br>Pulse Period | SENTJIT           | _         | _      | 0.1  | μs     | Note 1                                                                               |

| Nominal Clock Period (Tick)                                            | SENTCLK           | 3.0       | _      | 24.0 | μs     | By two program bits                                                                  |

| Clock Accuracy                                                         | SENTCLKAC         | -10       | _      | +10  | %      |                                                                                      |

| Clock Jitter and Drift Error                                           | SENTCLKJIT        |           | _      | 0.05 | μs     | Note 1                                                                               |

| PSI5 (Asynchronous Mode (                                              | Only)             |           | •      |      |        |                                                                                      |

| Absolute Bit Time Range                                                | ATBitR1           | 7.6       | 8.0    | 8.4  | μs     | 125 kbps                                                                             |

|                                                                        | ATBitR2           | 5.0       | 5.3    | 5.6  | μs     | 189 kbps                                                                             |

| Absolute Gap Time                                                      | ATGAP1            | 8.4       | _      | _    | μs     | 125 kbps, T <sub>GAP</sub> > T <sub>BIT</sub>                                        |

|                                                                        | ATGAP2            | 5.6       | _      | _    | μs     | 189 kbps, T <sub>GAP</sub> > T <sub>BIT</sub>                                        |

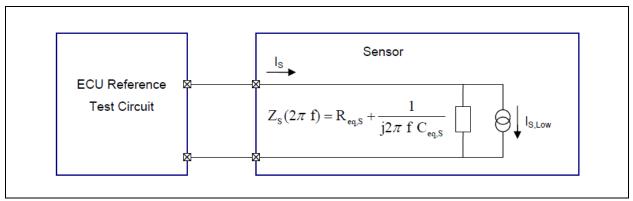

| Current Regulation Ref.                                                | $V_{REF}$         | 390       | 412.5  | 435  | mV     | For PSI5 operation                                                                   |

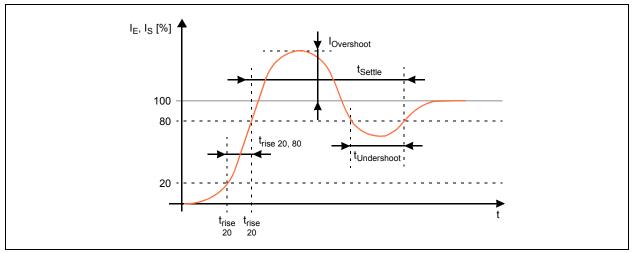

| Fall/Rise Time Driver<br>Voltage Slope                                 | PSI5_Tr_Tf        | 0.33      | _      | 1    | μs     | 20% to 80%, RL = 12.5Ω,<br>CL = 100 nF, L = 0 μH                                     |

| Total Overshoot Time per Cycle                                         | PSI5_TOTPC        | _         | _      | 0.52 | μs     | Voltage over 10%, RL = 2.5Ω,<br>CL = 47 nF, L = 8.7 μH                               |

| Total Undershoot Time per<br>Cycle                                     | PSI5_TUTPC        | _         | _      | 0.52 | μs     | Voltage under 10%, RL = 2.5Ω,<br>CL = 47 nF, L = 8.7 μH                              |

Note 1: For 3 µs nominal clock tick including clock accuracy. For higher clock tick, times need to be increased proportionally.

# **Electrical Characteristics (Continued)**

Electrical Specifications: Unless otherwise indicated, the following specifications apply over the operating temperature range of  $-40^{\circ}\text{C} \le T_{\text{A}} \le +150^{\circ}\text{C}$  and the following test conditions:  $V_{\text{IN}} = 5V$ , f = 8.2 MHz,  $I_{\text{DD}} = 1$  mA,  $I_{\text{CD}} = 0$  mA. Typical values are at +25°C.

| 10 0 = 1A = 1100 0 dnd tho   | ttorio. VIIV                              | O V, 1 O.L | טטי ,בי ייייי | ,    | o mir i. Typicar varace are at 120 o. |                                                |  |  |  |  |  |  |  |

|------------------------------|-------------------------------------------|------------|---------------|------|---------------------------------------|------------------------------------------------|--|--|--|--|--|--|--|

| Parameters                   | Symbol                                    | Min.       | Тур.          | Max. | Units                                 | Conditions                                     |  |  |  |  |  |  |  |

| PSI5 (Asynchronous Mode C    | PSI5 (Asynchronous Mode Only) (Continued) |            |               |      |                                       |                                                |  |  |  |  |  |  |  |

| Overshoot Voltage            | PSI5_OV                                   | _          | _             | 10   | %                                     | RL = $2.5\Omega$ , CL = 47 nF, L = $8.7 \mu H$ |  |  |  |  |  |  |  |

| Undershoot Voltage           | PSI5_UV                                   | -10        | _             | _    | %                                     | RL = $2.5\Omega$ , CL = 47 nF, L = $8.7 \mu H$ |  |  |  |  |  |  |  |

| Embedded Temperature Sen     | sor                                       |            |               |      |                                       |                                                |  |  |  |  |  |  |  |

| Temperature Sensing Range    | Tsnsrng                                   | -40        | _             | +175 | °C                                    |                                                |  |  |  |  |  |  |  |

| Temperature Sensing Accuracy | Tsnsacc                                   | 1          | ±12           |      | °C                                    | T <sub>A</sub> = +25°C                         |  |  |  |  |  |  |  |

| Sensor Output at +25°C       | Tsnsout25                                 |            | 500           | _    | LSB                                   | T <sub>A</sub> = +25°C, GBNT                   |  |  |  |  |  |  |  |

| Temperature Coefficient      | TCsns                                     | _          | 1.681         | _    | LSB/°C                                | -40°C ≤ T <sub>A</sub> ≤ +175°C                |  |  |  |  |  |  |  |

Note 1: For 3 µs nominal clock tick including clock accuracy. For higher clock tick, times need to be increased proportionally.

# Temperature Specifications<sup>(1)</sup>

| Parameters                                 | Symbol            | Min. | Тур. | Max. | Units | Conditions |

|--------------------------------------------|-------------------|------|------|------|-------|------------|

| Thermal Resistance,<br>Junction to Ambient | $\theta_{\sf JA}$ | _    | 117  | _    | °C/W  |            |

| Thermal Resistance,<br>Junction to Case    | θЈС               | _    | 22   | _    | °C/W  |            |

Note 1: The  $\theta_{JA}$  numbers assume no forced airflow. Junction temperature is calculated using the formula:  $T_J = T_A + (P_D \times \theta_{JA})$ . In particular,  $\theta_{JA}$  is a function of the PCB construction. The stated number above is for a four-layer board in accordance with JESD-51-7 (JEDEC) with thermal vias on  $V_{IN}$ , IO3 and GND pins.

# 2.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 2-1.

TABLE 2-1: PIN DESCRIPTIONS

| 14-Lead<br>TSSOP | Symbol          | Description                                                                                                                                                                                                                                                                                                 |

|------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | IO4             | I/O Pin 4. External FET current limits sensing. Pulled high to overwrite EEWR when one of the EELOCK bits is set to '1'. Pulled high to enable EEPROM programming via the IO1, IO2 or IO3 pins (hereafter Digital EEMode).                                                                                  |

| 2                | GND             | Ground pin.                                                                                                                                                                                                                                                                                                 |

| 3                | IO3             | I/O Pin 3. Can be programmed to provide DAC output, PWM output, reverse PWM output, SENT output, PSI5 external FET drive and $\mu P$ digital output. Alternatively, IO3 can be configured as an address pin for $V_{IN}$ EEMode and Digital EEMode.                                                         |

| 4                | V <sub>IN</sub> | Power Supply and Internal EEPROM Programming Pin. DC input power is applied to this pin for normal operation. Also used for EEPROM programming (refer to application information). Bypass this pin to GND pin with a low-ESR capacitor, not lower than 100 nF.                                              |

| 5                | $V_{DD}$        | Regulator Output Pin. This is the output of the internal voltage regulator providing power to the analog and digital blocks. Bypass this pin to the SUB pin with a low-ESR capacitor, not lower than 100 nF. A maximum load of 5 mA is allowed.                                                             |

| 6                | IO2             | I/O Pin 2. When configured as an output: PGA1 or PGA2 analog output, digital push-pull output (PWM/PWMB/SENT/ $\mu$ P GPO) or open-drain output (PWM/PWMB/ $\mu$ P GPO). Configured as an input: for V <sub>IN</sub> EEMode as address pin or for Digital EEMode as data input.                             |

| 7                | IO1             | I/O Pin 1. When configured as an output: PGA1 or PGA2 analog output, digital push-pull output (PWM/PWMB/SENT/ $\mu$ P GPO) or open-drain output (PWM/PWMB/ $\mu$ P GPO). Configured as an input: for V <sub>IN</sub> EEMode as an address pin or for Digital EEMode as a CLK input.                         |

| 8                | CL1             | Sensor Signal from Secondary Coil 1 of Inductive Sensor Pin.                                                                                                                                                                                                                                                |

| 9                | GNDCL           | Reference Ground for CL1 and CL2 Pin. Connect directly to GND on board via a star connection.                                                                                                                                                                                                               |

| 10               | CL2             | Sensor Signal from Secondary Coil 2 of Inductive Sensor Pin.                                                                                                                                                                                                                                                |

| 11               | SUB             | Substrate Pin. It should not be connected to GND. For normal applications, $V_{\text{DD}}$ bypass capacitor is connected.                                                                                                                                                                                   |

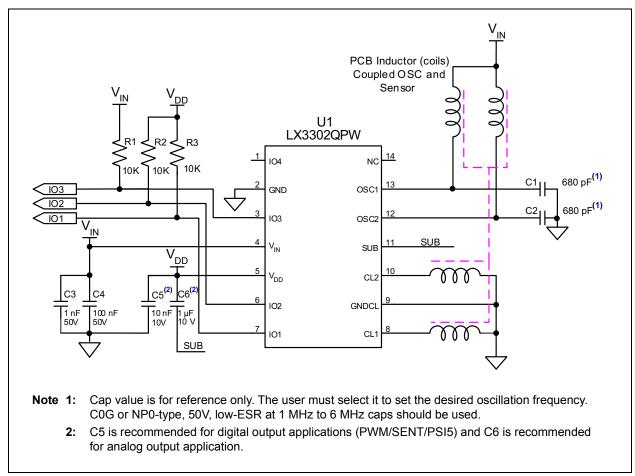

| 12               | OSC2            | LC Oscillator Pin. Connects to the second side of the primary inductor coil. An external capacitor is connected between this pin and GND as part of the LC oscillator tank circuit. External capacitor should be C0G or NP0, or equivalent type and low-ESR at 1 MHz to 6 MHz, rated voltage 50V or higher. |

| 13               | OSC1            | LC Oscillator Pin. Connects to the first side of the primary inductor coil. An external capacitor is connected between this pin and GND as part of the LC oscillator tank circuit. External capacitor should be C0G or NP0, or equivalent type and low-ESR at 1 MHz to 6 MHz, rated voltage 50V or higher.  |

| 14               | NC              | Not Connected.                                                                                                                                                                                                                                                                                              |

NOTES:

# 3.0 CONFIGURATION EEPROM

The LX3302A integrates a 32 words by 16 bits (512-bit) user-programmable EEPROM for storing calibration and configuration parameters. The calibration parameters enable the production sensor assembly to be customer-factory calibrated, assuring consistent unit to unit performance. Table 3-2 shows the LX3302A EEPROM Configuration map and Table 3-1 itemizes the LX3302A Configuration EEPROM contents.

TABLE 3-1: LX3302A CONFIGURATION EEPROM<sup>(1)</sup>

| Name     | Description                               | Size<br>(bits) | Words and Bits<br>(MSB:LSB) | Sign | Min.<br>Value | Max.<br>Value | Factory<br>Default |

|----------|-------------------------------------------|----------------|-----------------------------|------|---------------|---------------|--------------------|

| ID       | Part ID                                   | 18             | W0[15:0]W1[15:14]           | _    | _             | _             | Serial #           |

| Reserved | Reserved                                  | 3              | W1[13:11]                   | _    | _             | _             | 0                  |

| GADJ     | PGA Gain                                  | 4              | W1[10:7]                    | No   | 0000 b        | 1111 b        | 0                  |

| IOSC     | Oscillator Tail Current                   | 2              | W1[6:5]                     | No   | 0             | 3             | 0                  |

| Reserved | Reserved                                  | 1              | W1[4]                       | _    | _             | _             | 0                  |

| Reserved | Reserved                                  | 1              | W1[3]                       | _    | _             | _             | 0                  |

| REFRESH  | ADC Clock and PWM Clock                   | 3              | W1[2:0]                     | No   | 011 b         | 110 b         | 011 b              |

| FILTER   | Select Digital Filter                     | 1              | W2[15]                      | No   | 0             | 1             | 0                  |

| CLSEL    | Select CL1 and CL2                        | 1              | W2[14]                      | No   | 0             | 1             | 0                  |

| GMTCH    | Channel Gain Mismatch<br>Correction       | 7              | W2[13:7]                    | Yes  | -12.1%        | 12.1%         | 0                  |

| DCOS     | Cosine Channel Dynamic Offset Correction  | 10             | W2[6:0]W3[15:13]            | Yes  | -511          | 511           | 0                  |

| SCOS     | Cosine Channel Offset<br>Correction       | 10             | W3[12:3]                    | Yes  | -511          | 511           | 0                  |

| DSIN     | Sine Channel Dynamic<br>Offset Correction | 10             | W3[2:0]W4[15:9]             | Yes  | -511          | 511           | 0                  |

| SSIN     | Sine Channel Offset<br>Correction         | 10             | W4[8:0]W5[15]               | Yes  | -511          | 511           | 0                  |

| OSCOMP   | Max. Oscillator Swing                     | 10             | W5[14:5]                    | No   | 0             | 1023          | 1023               |

| Reserved | _                                         | 5              | W5[4:0]                     | _    | _             | _             | 00000 b            |

| ORIGIN   | Origin                                    | 12             | W6[15:4]                    | No   | 0             | 4095          | 0                  |

| HCLMP    | High Plateau Value                        | 12             | W6[3:0]W7[15:8]             | No   | 0             | 4095          | 4095               |

| LCLMP    | Low Plateau Value                         | 12             | W7[7:0]W8[15:2]             | No   | 0             | 4095          | 0                  |

| S0       | Initial Slope                             | 12             | W8[11:0]                    | No   | 0             | 4095          | 511                |

| X1       | Linearization Point 1<br>X-Coordinate     | 12             | W9[15:4]                    | No   | 0             | 4095          | 511                |

| X2       | Linearization Point 2<br>X-Coordinate     | 12             | W9[3:0]W10[15:8]            | No   | 0             | 4095          | 1023               |

| X3       | Linearization Point 3<br>X-Coordinate     | 12             | W10[7:0]W11[15:12]          | No   | 0             | 4095          | 1535               |

| X4       | Linearization Point 4<br>X-Coordinate     | 12             | W11[11:0]                   | No   | 0             | 4095          | 2047               |

| X5       | Linearization Point 5<br>X-Coordinate     | 12             | W12[15:4]                   | No   | 0             | 4095          | 2559               |

Note 1: 'xxx b' stands for 'xxx' binary numbers.

TABLE 3-1: LX3302A CONFIGURATION EEPROM<sup>(1)</sup> (CONTINUED)

| Name      | Description                                            | Size<br>(bits) | Words and Bits<br>(MSB:LSB) | Sign | Min.<br>Value | Max.<br>Value | Factory<br>Default |

|-----------|--------------------------------------------------------|----------------|-----------------------------|------|---------------|---------------|--------------------|

| X6        | Linearization Point 6<br>X-Coordinate                  | 12             | W12[3:0]W13[15:8]           | No   | 0             | 4095          | 3071               |

| X7        | Linearization Point 7<br>X-Coordinate                  | 12             | W13[7:0]W14[15:12]          | No   | 0             | 4095          | 3583               |

| Y1        | Linearization Point 1<br>Y-Coordinate                  | 12             | W14[11:0]                   | No   | 0             | 4095          | 511                |

| Y2        | Linearization Point 2<br>Y-Coordinate                  | 12             | W15[15:4]                   | No   | 0             | 4095          | 1023               |

| Y3        | Linearization Point 3<br>Y-Coordinate                  | 12             | W15[3:0]W16[15:8]           | No   | 0             | 4095          | 1535               |

| Y4        | Linearization Point 4<br>Y-Coordinate                  | 12             | W16[7:0]W17[15:12]          | No   | 0             | 4095          | 2047               |

| Y5        | Linearization Point 5<br>Y-Coordinate                  | 12             | W17[11:0]                   | No   | 0             | 4095          | 2559               |

| Y6        | Linearization Point 6<br>Y-Coordinate                  | 12             | W18[15:4]                   | No   | 0             | 4095          | 3071               |

| Y7        | Linearization Point 7<br>Y-Coordinate                  | 12             | W18[3:0]W19[15:8]           | No   | 0             | 4095          | 3583               |

| S7        | Final Slope                                            | 12             | W19[7:0]W20[15:12]          | No   | 0             | 4095          | 511                |

| TD        | Threshold Detect                                       | 13             | W20[11:0]W21[15]            | No   | 0             | 8191          | 8191               |

| TDPOL     | TD Output Logic Level                                  | 1              | W21[14]                     | No   | 0             | 1             | 0                  |

| DIAGMK    | Diagnostic Error Mask                                  | 12             | W21[13:2]                   | No   | 0             | 0xFFF         | 0xFFF              |

| SENTCLK   | SENT Clock Tick                                        | 2              | W21[1:0]                    | No   | 00 b          | 11 b          | 00 b               |

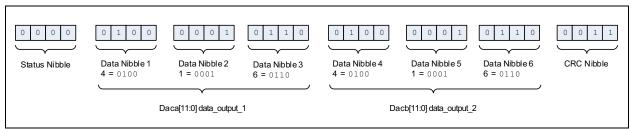

| SENTFCM   | SENT Protocol Select                                   | 4              | W22[15:12]                  | No   | 0000 b        | 1100 b        | 0000 b             |

| SENTREFR  | SENT Constant Clock<br>Ticks Sync. with Pause<br>Pulse | 11             | W22[11:1]                   | No   | 0             | 0x7FF         | 0                  |

| SENTPPE   | SENT Pause Pulse                                       | 1              | W22[0]                      | No   | 0             | 1             | 0                  |

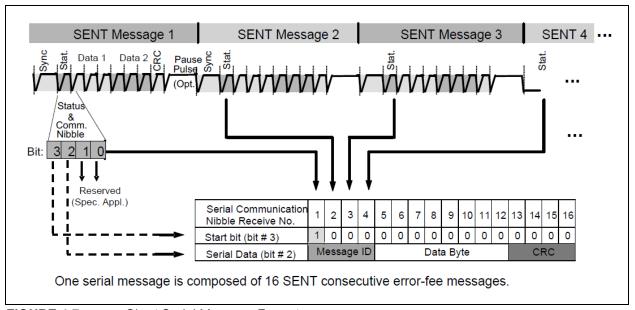

| SENTSCM   | SENT Serial Message                                    | 2              | W23[15:14]                  | No   | 00 b          | 11 b          | 00 b               |

| MSGMUX    | Message MUX                                            | 1              | W23[13]                     | No   | 0             | 1             | 0                  |

| DIAGPOL   | Diagnostic Level                                       | 1              | W23[12]                     | No   | 0             | 1             | 0                  |

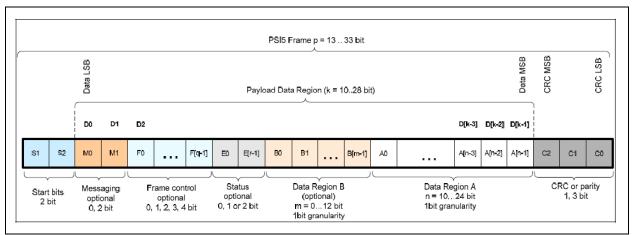

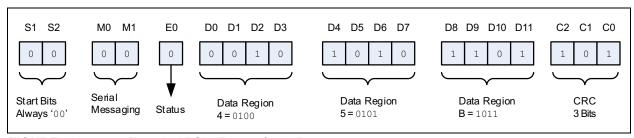

| PSI5FR    | PSI5 Frame                                             | 3              | W23[11:9]                   | No   | 000 b         | 100 b         | 000 b              |

| PSI5STS   | PSI5 Status                                            | 2              | W23[8:7]                    | No   | 00 b          | 10 b          | 00 b               |

| PSI5MSG   | PSI5 Serial Message                                    | 2              | W23[6:5]                    | No   | 00 b          | 11 b          | 00 b               |

| PSI5ERRCS | PSI5 Error Check<br>Selection                          | 1              | W23[4]                      | No   | 0             | 1             | 0                  |

| PSI5DRB   | PSI5 Data Region B                                     | 4              | W23[3:0]                    | No   | 0000 b        | 1100 b        | 0000 b             |

| PSI5DRA   | PSI5 Data Region A                                     | 4              | W24[15:12]                  | No   | 0000 b        | 1110 b        | 0000 b             |

| PSI5REFR  | PSI5 Refresh Rate                                      | 11             | W24[11:1]                   | No   | 0             | 0x7FF         | 0                  |

| PSI5BR    | PSI5 Bit Time                                          | 1              | W24[0]                      | No   | 0             | 1             | 0                  |

| IOSEL     | Output Selection                                       | 15             | W25[15:1]                   | No   | 0             | FBBD          | E000               |

| OSCDFB    | Oscillator DAC Control                                 | 1              | W25[0]                      | No   | 0             | 1             | 0                  |

| OSCDAC    | Oscillator DAC Data                                    | 12             | W26[15:4]                   | No   | 0             | 0xFFF         | 0                  |

| TD MASK   | TD Input Source Select                                 | 2              | W26[3:2]                    | No   | 0             | 3             | 0                  |

| EELOCK    | EEPROM Lock                                            | 2              | W26[1:0]                    | No   | 0             | 3             | 0                  |

Note 1: 'xxx b' stands for 'xxx' binary numbers.

TABLE 3-1: LX3302A CONFIGURATION EEPROM<sup>(1)</sup> (CONTINUED)

| Name     | Description                    | Size<br>(bits) | Words and Bits<br>(MSB:LSB)     | Sign | Min.<br>Value | Max.<br>Value | Factory<br>Default |

|----------|--------------------------------|----------------|---------------------------------|------|---------------|---------------|--------------------|

| MESSAGE  | Message                        | 16             | W27[15:0]                       | No   | 0             | 0xFFF         | 0                  |

| MSGID    | Message ID                     | 8              | W28[15:8]                       | No   | 0             | 0xFF          | 0                  |

| TDHYST   | Threshold Detect<br>Hysteresis | 8              | W28[7:0]                        | No   | 0             | 255           | 255                |

| ADC10IN  | ADC10_IN                       | 1              | W29[15]                         | No   | 0             | 1             | 1                  |

| CLCHK    | Range Check Ignore             | 1              | W29[14]                         | No   | 0             | 1             | 0                  |

| WDSCALE  | Watchdog Timer Scale           | 3              | W29[13:11]                      | No   | 0             | 7             | 001 b              |

| Reserved | _                              | 43             | W29[10:0]W30[15:0]<br>W31[15:0] | _    |               | _             | _                  |

Note 1: 'xxx b' stands for 'xxx' binary numbers.

# TABLE 3-2: LX3302A CONFIGURATION EEPROM MAP

|        | MSB             |          |       |          |       |                         | _      |         |        | _       |        |         | _      |       |         | LSB         |

|--------|-----------------|----------|-------|----------|-------|-------------------------|--------|---------|--------|---------|--------|---------|--------|-------|---------|-------------|

|        | 15              | 14       | 13    | 12       | 11    | 10                      | 9      | 8       | 7      | 6       | 5      | 4       | 3      | 2     | 1       | 0           |

| WORD0  | ID[172]         |          |       |          |       |                         |        |         |        |         |        |         |        |       |         |             |

| WORD1  | ID[1            | 10]      | ſ     | Reserved | t     | GADJ IOSC Reserved REFR |        |         |        | REFRES  | SH     |         |        |       |         |             |

| WORD2  | Filter          | CLSEL    |       |          | G     | MTCH[6                  | 0]     |         |        |         |        | D       | COS[9  | 3]    |         |             |

| WORD3  | D               | COS[20   | )]    |          |       |                         |        | SCOS    | [90]   |         |        |         |        |       | DSIN[9  | .7]         |

| WORD4  |                 |          | D     | SIN[60]  |       |                         |        |         |        |         | S      | SIN[91] |        |       |         |             |

| WORD5  | SSIN[0]         |          |       |          |       | OSCON                   |        |         |        |         |        |         |        | Reser |         |             |

| WORD6  |                 |          |       |          |       | ORIGI                   | N[110] |         |        |         |        |         |        | HCI   | _MP[118 | ]           |

| WORD7  |                 |          |       | HCLMF    | P[70] |                         |        |         |        |         |        | LCLMP[  | [114]  |       |         |             |

| WORD8  |                 | LCLMF    | P[30] |          |       |                         |        |         |        | S0[1    | 10]    |         | 1      |       |         |             |

| WORD9  |                 |          |       |          |       | X1[1                    | 10]    |         |        |         |        |         |        | Х     | [2[118] |             |

| WORD10 |                 |          |       | X2[7     | 0]    |                         |        |         |        |         |        | X3[11   | 4]     |       |         |             |

| WORD11 |                 | X3[3     | 0]    |          |       |                         |        |         |        | X4[1    | 10]    |         |        |       |         |             |

| WORD12 |                 |          |       |          |       | X5[1                    | 10]    |         |        |         |        |         |        | Х     | (6[118] |             |

| WORD13 |                 |          |       | X6[7     | 0]    |                         |        |         |        |         |        | X7[11   | 4]     |       |         |             |

| WORD14 | X7[30] Y1[110]  |          |       |          |       |                         |        |         |        |         |        |         |        |       |         |             |

| WORD15 | Y2[110] Y3[118] |          |       |          |       |                         |        |         |        |         |        |         |        |       |         |             |

| WORD16 |                 |          |       | Y3[7     | ':0]  |                         |        |         |        |         |        | Y4[11   | 1:4]   |       |         |             |

| WORD17 |                 |          |       |          |       |                         |        |         |        |         |        |         |        |       |         |             |

| WORD18 | Y6[·            |          |       | Y6[1     | 10]   |                         |        |         |        |         |        | Y       | 7[118] |       |         |             |

| WORD19 |                 |          |       | Y7[7     | 0]    |                         |        |         |        |         |        | S7[11   | 4]     |       |         |             |

| WORD20 |                 | S7[3     | 0]    |          |       |                         |        |         |        | TD[1    | 21]    |         |        |       |         |             |

| WORD21 | TD[0]           | TDPOL    |       |          |       |                         |        | DIAGMK  |        |         |        |         |        |       | SEN     | ITCLK       |

| WORD22 |                 | SENTFO   | M[30] |          |       |                         |        |         | SENT   | REFR[1  | 00]    |         |        |       |         | SENT<br>PPE |

| WORD23 | SENTS           | CM[10]   | MSG   | DIAG     | PS    | SI5FR[2                 | .0]    | PSI5S   | TS[10] | PSI5M   | SG[10] |         |        | PSI   | 5DRB[30 |             |

|        |                 |          | MUX   | POL      |       |                         |        |         |        |         |        | ERRCS   |        |       |         |             |

| WORD24 |                 | PSI5DR   | A[30] |          |       |                         |        |         |        | REFR[10 | 00]    |         |        |       |         | PSI5BR      |

| WORD25 | iOSEL[140]      |          |       |          |       | OSC<br>DFB              |        |         |        |         |        |         |        |       |         |             |

| WORD26 | OSCDAC[110]     |          |       |          |       |                         |        |         |        | TDN     | ЛАSK   | EEL     | OCK    |       |         |             |

| WORD27 |                 |          |       |          |       |                         | Ŋ      | //ESSAG | E[150] |         |        |         |        |       | •       |             |

| WORD28 |                 |          |       | MSGIE    | [70]  |                         |        |         |        |         |        | TDHYS   | T[70]  |       |         |             |

| WORD29 | ADC10           | CLCHK    | WD    |          |       |                         |        |         | R      | eserve  | i      |         |        |       |         |             |

| WORD30 | IN              | <u> </u> | SCALE |          |       |                         |        | Dagas   | a rod  |         |        |         |        |       |         |             |

| WORD30 |                 |          |       |          |       |                         |        | Reser   |        |         |        |         |        |       |         |             |

| WUKD31 | Reserved        |          |       |          |       |                         |        |         |        |         |        |         |        |       |         |             |

# 3.1 GADJ (Four Bits, W1[10:7])

This parameter is used to adjust the gain of the Programmable Gain Amplifier (PGA). The bit, WORD1[10], is the polarity bit. The remaining three bits ([9:7]) adjust gains. The default gain ('00000 b') is 3.125. The gain can be adjusted in increments of approximately 3%. The smallest number is '1000' and the largest number is '0111'.

# 3.2 IOSC (Two Bits, W1[6:5])

The IOSC bits set the oscillator tail current value, as shown in Table 3-3.

TABLE 3-3: IOSC CONFIGURATION

| IOSC Bits | Tail Current | Feedback |

|-----------|--------------|----------|

| 0.0       | Normal mode  | Enabled  |

| 01        | 1/2          | Enabled  |

| 10        | 1/4          | Enabled  |

| 11        | 1/8          | Enabled  |

# 3.3 REFRESH (Three Bits, W1[2:0])

This parameter sets the value of the refresh rate of the ADC update. If the PWM output is selected then the PWM frequency is always equal to the ADC update rate. Also WDSCALE should be selected, as shown in Table 3-4.

TABLE 3-4: REFRESH CONFIGURATION

| Bit<br>Value | ADC1 and ADC2<br>Sampling Clock | PWM<br>Frequency | WDSCALE |

|--------------|---------------------------------|------------------|---------|

| 011          | F <sub>CLK</sub> /8             | 2 kHz            | 001     |

| 100          | F <sub>CLK</sub> /16            | 1 kHz            | 001     |

| 101          | F <sub>CLK</sub> /32            | 500 Hz           | 010     |

| 110          | F <sub>CLK</sub> /64            | 250 Hz           | 011     |

# 3.4 FILTER (One Bit, W2[15])

This bit selects the digital filter type. Setting the bit to '0' will set the filter type to SINC, while assigning a value of '1' will set the filter to SINC+FIR, as shown in Table 3-5.

TABLE 3-5: FILTER CONFIGURATION

| FILTER Bit | Filter Type |

|------------|-------------|

| 0          | SINC        |

| 1          | SINC+FIR    |

# 3.5 CLSEL (One Bit, W2[14])

When the CLSEL bit is set to '1', it swaps the Sine and Cosine inputs (CL1 and CL2).

# 3.6 GMTCH (Seven Bits, W2[13:7])

The GMTCH bits set the value of the input channel gain mismatch correction used in input correction calculations.

# 3.7 DCOS (Ten Bits, W2[6:0]W3[15:13])

These bits set the dynamic offset correction of the CL1 input channel used in input correction calculations.

# 3.8 SCOS (Ten Bits, W3[12:3])

These bits set the offset correction of the CL1 input channel used in input correction calculations.

# 3.9 DSIN (Ten Bits, W3[2:0]W4[15:9])

These bits set the offset correction of the CL2 input channel used in input correction calculations.

# 3.10 SSIN (Ten Bits, W4[8:0]W5[15])

These bits set the dynamic offset correction of the CL2 input channel used in input correction calculations.

# 3.11 OSCOMP (Ten Bits, W5[14:5])

These bits set the maximum amplitude of the oscillator swing used in the input correction calculations. The maximum value of the OSCOMP setting is 1023 at Step 1.

## 3.12 ORIGIN (Twelve Bits, W6[15:4])

Offset value of the system origin relative to fore-and-after position. This is not a DC output offset adjustment.

# 3.13 HCLMP (Twelve Bits, W6[3:0]W7[15:8])