# 71M6511/71M6511H 71M6513/71M6513H Power Meter IC Family

**SOFTWARE USER'S GUIDE**

8/11/2006 Revision 2.4

# **TERIDIAN Semiconductor Corporation**

6440 Oak Canyon Rd.

Irvine, CA 92618-5201

Ph: (714) 508-8800 • Fax: (714) 508-8878

meter.support@teridian.com

http://www.teridian.com/

TERIDIAN Semiconductor Corporation makes no warranty for the use of its products, other than expressly contained in the Company's warranty detailed in the TERIDIAN Semiconductor Corporation standard Terms and Conditions. The company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice and does not make any commitment to update the information contained herein.

# 71M651xH 71M651x

Power Meter IC FAMILY

# **SOFTWARE USER'S GUIDE**

Demo Code Revisions 3.04 and 3.05

# **Table of Contents**

| 1. INTRODUCTION                                              | 12 |

|--------------------------------------------------------------|----|

| 1.1. Use of this Document                                    | 12 |

| 1.2. Related Documentation                                   | 13 |

| 1.3. Compatibility Statement                                 | 13 |

| 2. DESIGN GUIDE                                              |    |

| 2.1. Hardware Requirements                                   | 14 |

| 2.2. Software Requirements                                   |    |

| 2.3. Utilities                                               | 16 |

| 2.3.1. IO_MERGE                                              | 16 |

| 2.3.2. CE_MERGE                                              |    |

| 3. DESIGN REFERENCE                                          |    |

| 3.1. Program Memory                                          |    |

| 3.2. Data Memory                                             |    |

| 3.3. Programming of the 71M651X Chips                        |    |

| 3.4. Test Tools                                              | 19 |

| 3.4.1. Running the 651X_Demo.hex Program                     | 19 |

| 3.4.2. Complete List of CLI Commands                         | 21 |

| 3.4.3. Command (Macro) Files                                 |    |

| 4. TOOL INSTALLATION GUIDE                                   |    |

| 4.1. Installing the Programs for the ADM51 Emulator          |    |

| 4.2. Installing the Wemu Program (Chameleon Debugger)        |    |

| 4.3. Installing the ADM51 USB Driver                         |    |

| 4.4. Installing Updates to the Emulator Program and Hardware |    |

| 4.5. Creating a Project                                      |    |

| 4.6. Installing the Keil Compiler                            |    |

| 4.7. Creating a Project for the Keil Compiler                |    |

| 4.7.1. Directory Structure                                   |    |

| 4.7.2. Adjusting the Keil Compiler Settings                  |    |

| 4.7.3. Manually Controlling the Keil Compiler Settings       |    |

| 4.8. Project Management Tools                                |    |

| 4.9. Alternative Compilers                                   |    |

| 4.10. Alternative Editors                                    |    |

| 5. Demo Code Description                                     |    |

| 5.1. 80515 Data Types and Compiler-Specific Information      |    |

| 5.1.1. Data Types                                            |    |

| 5.1.2. Compiler-Specific Information                         |    |

| 5.2. Program Flow                                            | 46 |

|    | 5.2.1. Startup and Initialization                 |      |

|----|---------------------------------------------------|------|

|    | 5.3. Basic Code Architecture                      | 48   |

|    | 5.3.1. Initialization                             | . 48 |

|    | 5.3.2. Foreground                                 | 48   |

|    | 5.3.3. Background Tasks                           | . 55 |

|    | 5.3.4. Watchdog Timer                             | 68   |

|    | 5.3.5. Real-Time Clock (RTC)                      | 68   |

|    | 5.4. Data Flow                                    | 68   |

|    | 5.5. CE/MPU Interface                             |      |

|    | 5.6. Source Files                                 |      |

|    | 5.7. Auxiliary Files                              |      |

|    | 5.8. Include/Header Files                         |      |

|    | 5.9. CE Image Files                               |      |

|    | 5.10. Common MPU Addresses                        |      |

|    | 5.11. Firmware Application Information            |      |

|    | 5.11.1. Sag Detection                             |      |

|    | 5.11.2. Temperature Measurement                   |      |

|    | 5.11.3. Temperature Compensation for Measurements |      |

|    | 5.11.4. Temperature Compensation for the RTC      |      |

|    | 5.12. Validating the Battery                      |      |

|    | 5.13. Alphabetical Function Reference             |      |

|    | 5.14. Errata for Demo Code Revision 3.04          |      |

|    |                                                   |      |

|    | 5.15.1. 6513 CE Example                           |      |

|    | 5.15.2. Serial Port Tests                         |      |

|    | 5.15.3. Timer Tests                               |      |

|    | 5.15.4. EEPROM Tests                              |      |

|    | 5.15.5. Generating DIO Pulses on Reset            |      |

|    | 5.15.6. Testing the Security Bit                  |      |

|    | 5.15.7. Software Timer Test                       |      |

|    | 5.15.8. Interrupt Test                            |      |

|    | 5.15.9. RTC Test.                                 |      |

| 6  | 5.15.10. LCD Test                                 |      |

| ٥. | 6.1. 80515 Overview                               |      |

|    |                                                   |      |

|    | 6.1.1. 80515 Performance                          |      |

|    | 6.1.2. 80515 Features                             |      |

|    |                                                   |      |

|    | 6.2.1. Memory organization                        |      |

|    | 6.2.2. The 80515 Instruction Set                  | 105  |

| 6.3. 80515 Hardware Description                                          | 115             |

|--------------------------------------------------------------------------|-----------------|

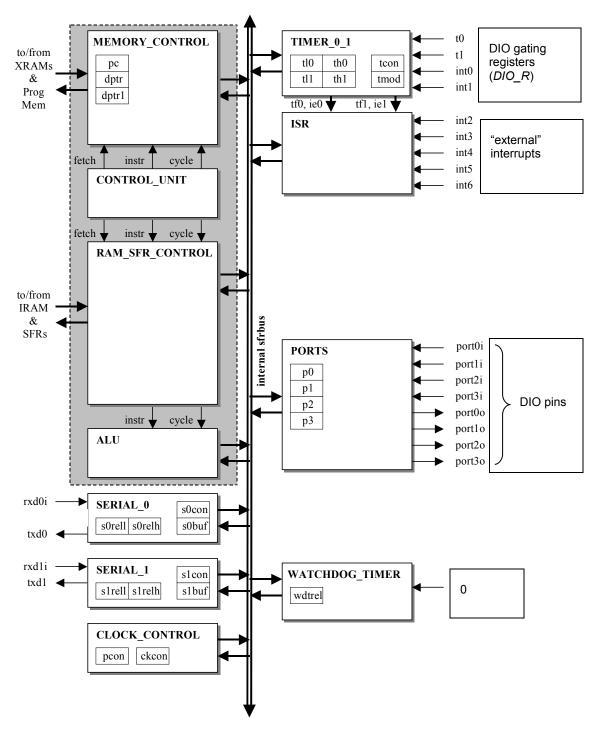

| 6.3.1. Block Diagram                                                     | 116             |

| 6.3.2. 80515 MPU                                                         | 117             |

| 6.3.3. Serial Interface 0 and 1                                          | 12 <sup>2</sup> |

| 6.3.4. Software Watchdog Timer                                           | 125             |

| 6.3.5. The Interrupt Service Routine Unit                                |                 |

| 7. ACRONYMS                                                              |                 |

|                                                                          |                 |

|                                                                          |                 |

| List of Figures                                                          |                 |

| Figure 2-1: Software Structure                                           | 14              |

| Figure 3-1: Port Speed and Handshake Setup (left) and Port Configuration |                 |

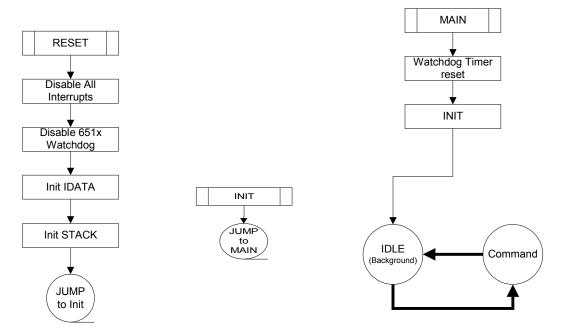

| Figure 5-1: STARTUP.A51                                                  |                 |

| Figure 5-2: INIT.A51                                                     |                 |

| Figure 5-3: DEMO.C                                                       | 45              |

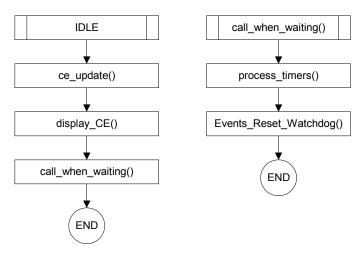

| Figure 5-4: MAIN LOOP                                                    | 46              |

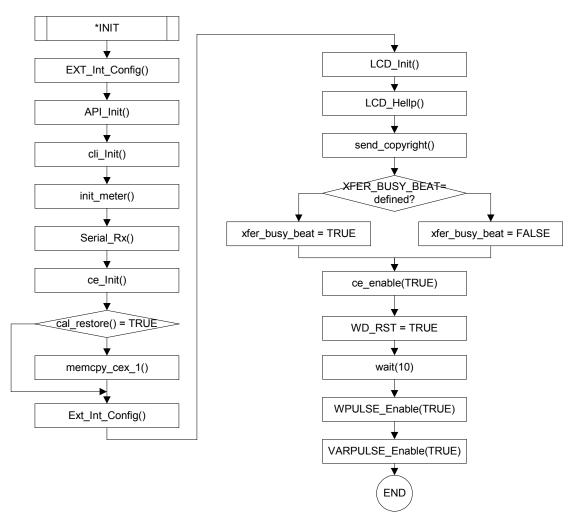

| Figure 5-5: INIT Function                                                | 46              |

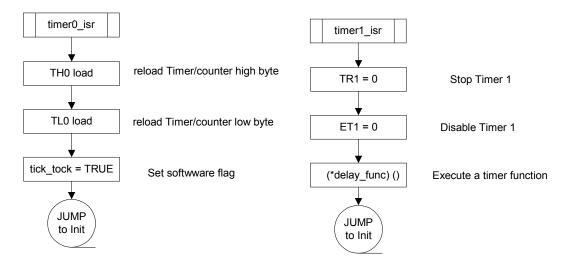

| Figure 5-6: Timer ISRs                                                   | 48              |

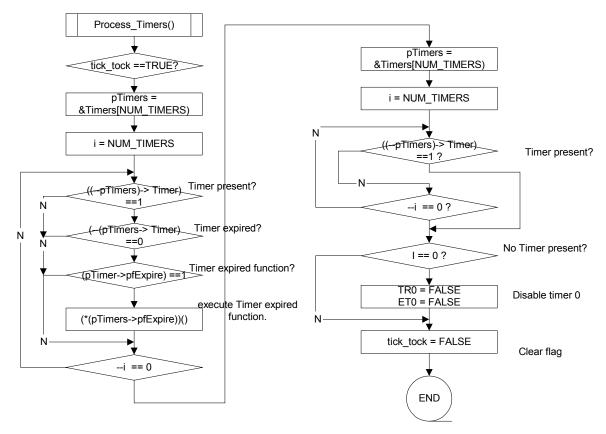

| Figure 5-7: Process Timer (non-ISR)                                      | 49              |

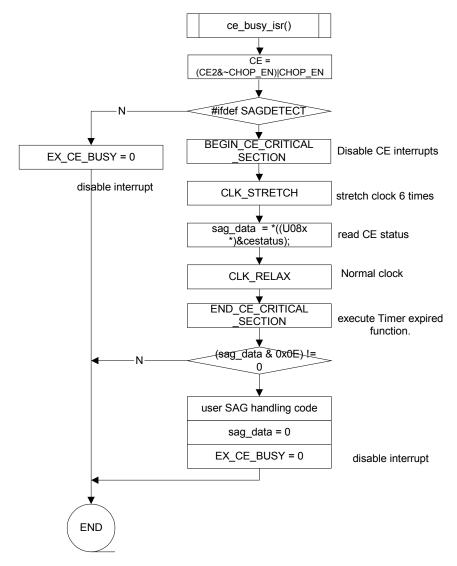

| Figure 5-8: CE_BUSY ISR                                                  | 50              |

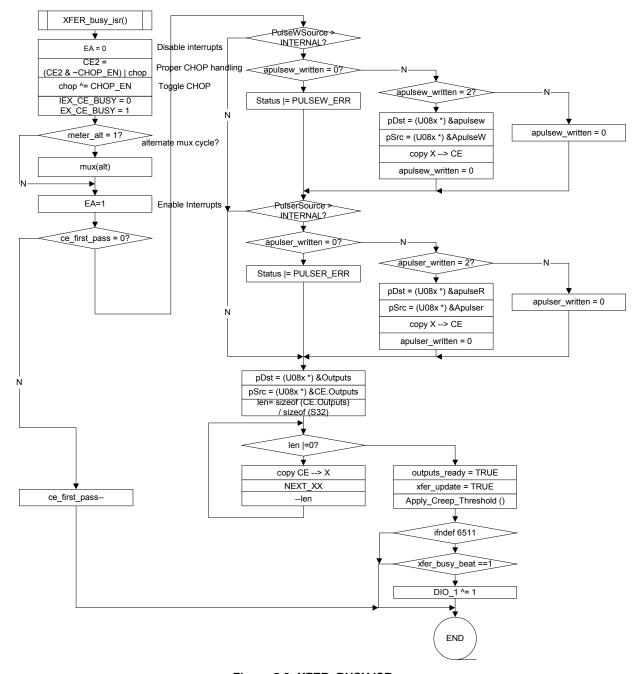

| Figure 5-9: XFER_BUSY ISR                                                | 51              |

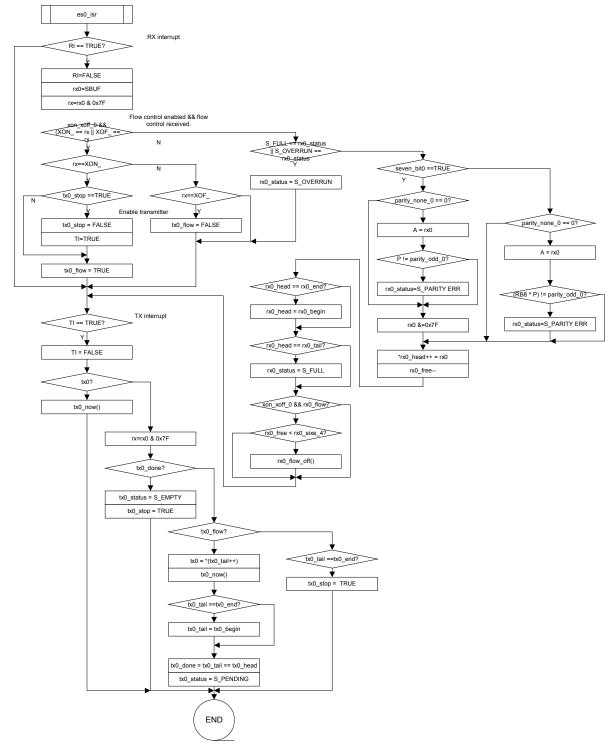

| Figure 5-10: Serial 0 isr                                                | 52              |

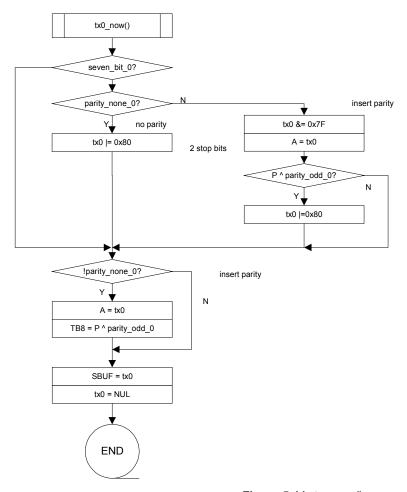

| Figure 5-11: tx_now()                                                    | 53              |

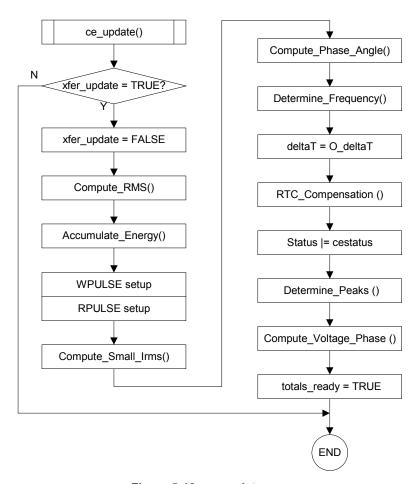

| Figure 5-12: ce_update                                                   | 54              |

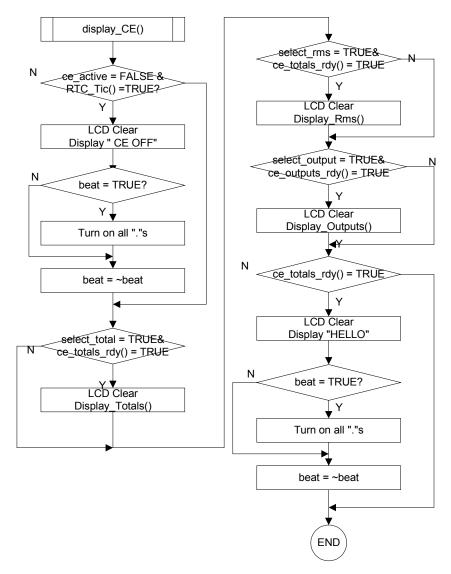

| Figure 5-13: Display CE                                                  | 55              |

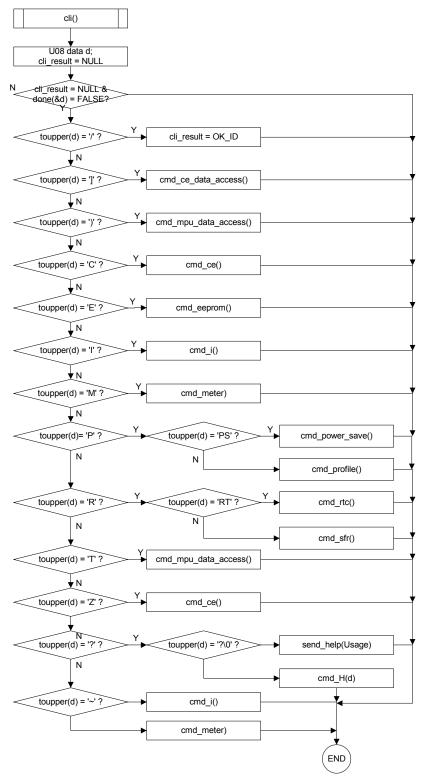

| Figure 5-14: Command Line Interpreter                                    | 56              |

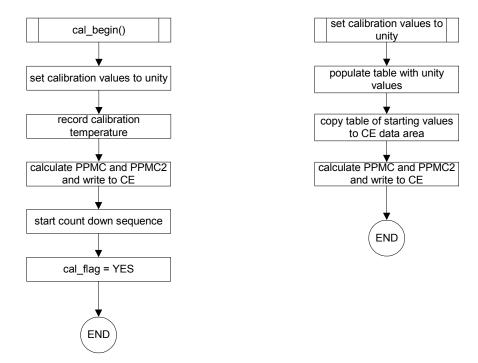

| Figure 5-15: Auto-Calibration                                            | 57              |

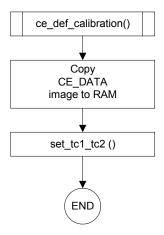

| Figure 5-16: ce_default Calibration                                      | 58              |

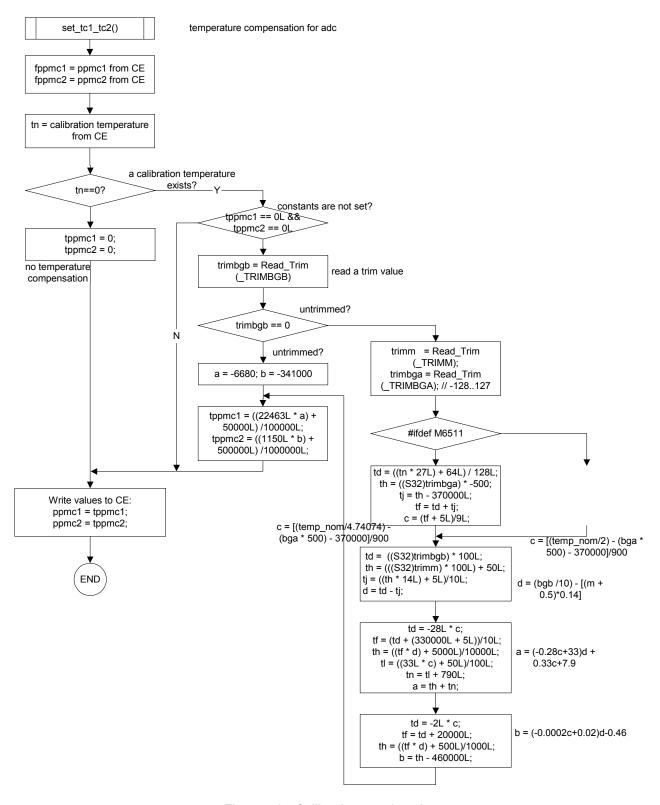

| Figure 5-17: Calibration, continued                                      | 59              |

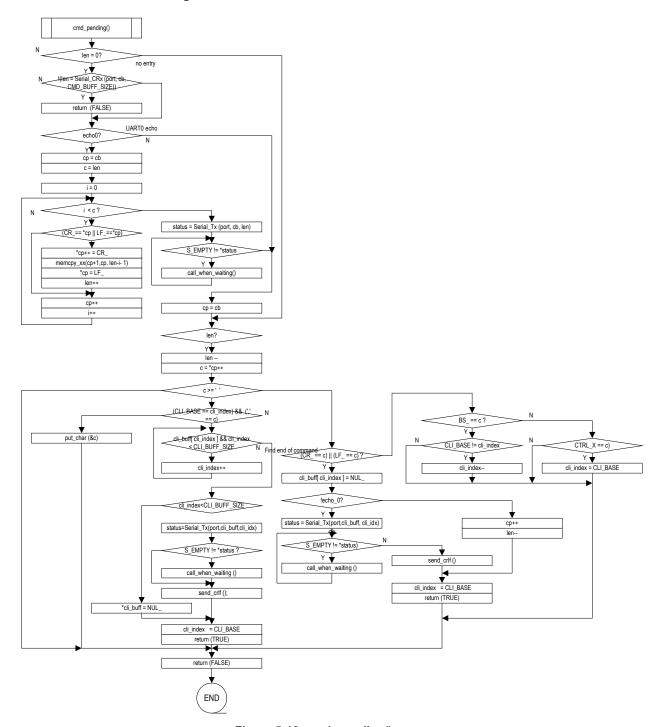

| Figure 5-18: cmd_pending()                                               | 60              |

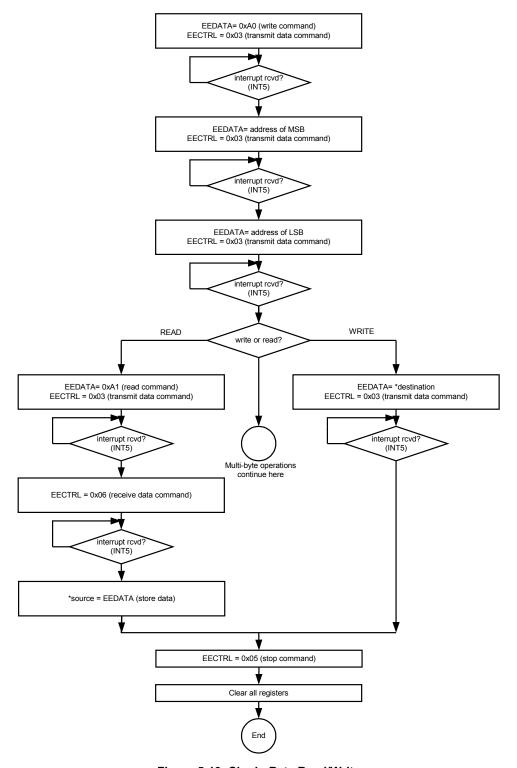

| Figure 5-19: Single-Byte Read/Write                                      | 61              |

| Figure 5-20: Multi-Byte Read                                             | 62              |

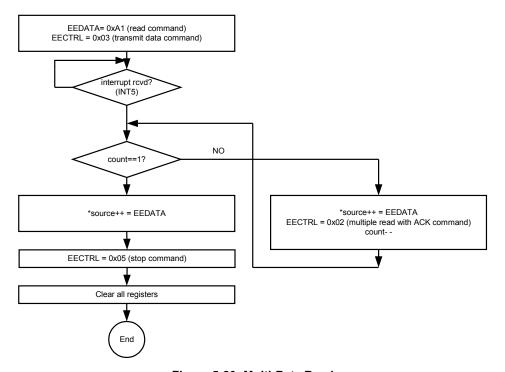

| Figure 5-21: Multi-Byte Write                                            | 63              |

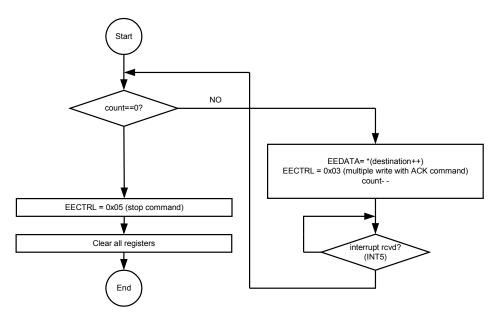

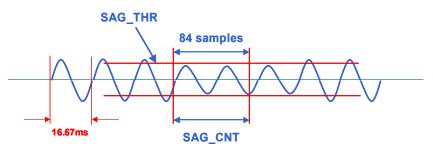

| Figure 5-22: Sag and Dip Conditions                                      | 80              |

| Figure 5-23: Sag Event                                                   | 80              |

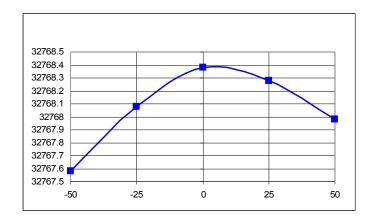

| Figure 5-24: Crystal Frequency over Temperature                          | 82              |

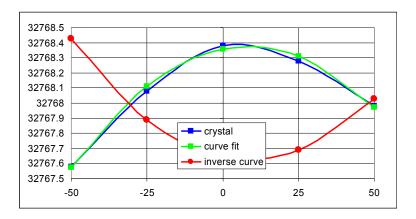

| Figure 5-25: Crystal Compensation                                        | 82              |

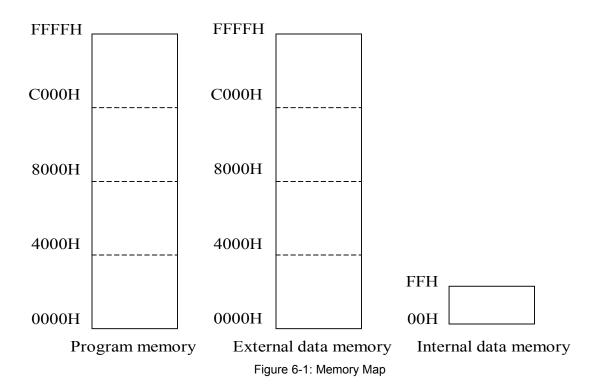

| Figure 6-1: Memory Map                                                   | 97              |

| Figure 6-2: 80515 MPU Block Diagram                                      | 114             |

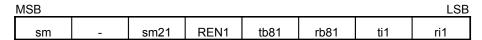

| Figure 6-3: Watchdog Block Diagram                                       | 123             |

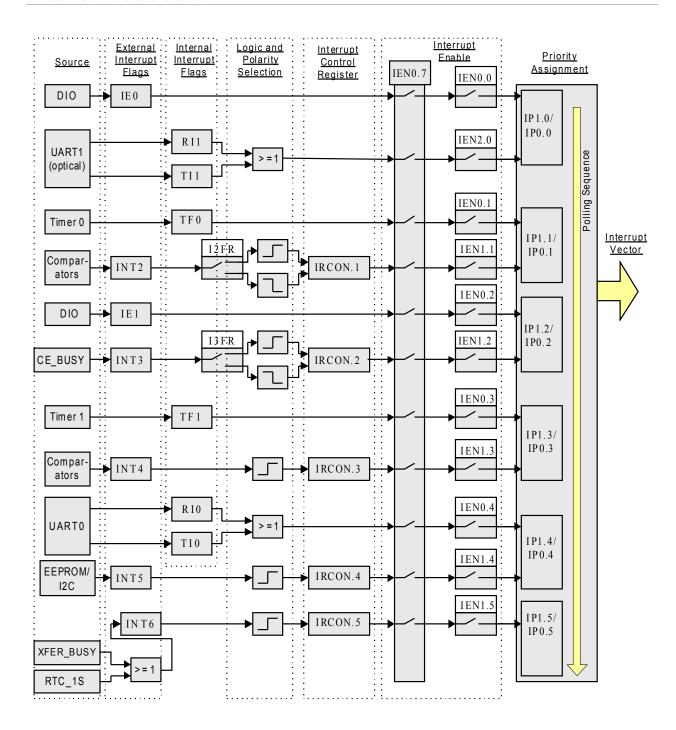

| Figure 6-4: Interrupt Sources Diagram                                    | 133             |

# **List of Tables**

| Table 3-1: Memory Map                                                   | 17  |

|-------------------------------------------------------------------------|-----|

| Table 5-1: Data Types                                                   | 44  |

| Table 5-2: Interrupt Service Routines                                   | 47  |

| Table 5-3: MPU Input Parameters                                         | 71  |

| Table 5-4: Pulse Source Parameters (6511)                               | 72  |

| Table 5-5: Pulse Source Parameters (6513)                               | 73  |

| Table 5-6: MPU Instantaneous Output Variables (6511)                    | 74  |

| Table 5-7: MPU Instantaneous Output Variables (6513)                    | 75  |

| Table 5-8: MPU Status Word Bit Assignment                               | 76  |

| Table 5-9: MPU Accumulation Output Variables (6511)                     | 77  |

| Table 5-10: MPU Accumulation Output Variables (6513)                    | 78  |

| Table 5-11: MPU Variables Related to Phase B (6511, Revision 3.05 only) |     |

| Table 5-12: Frequency over Temperature                                  | 81  |

| Table 6-1: Speed Advantage Summary                                      | 95  |

| Table 6-2: Stretch Memory Cycle Width                                   | 98  |

| Table 6-3: Internal Data Memory Map                                     | 99  |

| Table 6-4: Special Function Registers Locations                         | 99  |

| Table 6-5: Special Function Registers Reset Values                      | 101 |

| Table 6-6: Notes on Data Addressing Modes                               | 103 |

| Table 6-7: Notes on Program Addressing Modes                            |     |

| Table 6-8. Arithmetic Operations                                        |     |

| Table 6-9. Logic Operations                                             | 105 |

| Table 6-10: Data Transfer Operations                                    | 106 |

| Table 6-11: Program Branches                                            | 107 |

| Table 6-12: Boolean Manipulations                                       | 108 |

| Table 6-13: Instruction Set in Hexadecimal Order (1/3)                  | 109 |

| Table 6-14: Instruction Set in Hexadecimal Order (2/3)                  |     |

| Table 6-15: Instruction Set in Hexadecimal Order (3/3)                  | 111 |

| Table 6-16: Instructions Affecting Flags                                | 112 |

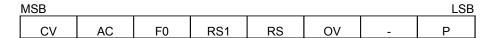

| Table 6-17: PSW Register Flags                                          | 115 |

| Table 6-18: PSW Bit Functions                                           |     |

| Table 6-19: Register Bank Location                                      | 116 |

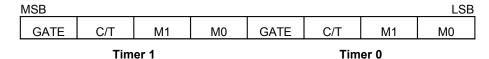

| Table 6-20: The TMOD Register                                           | 117 |

| Table 6-21: The TMOD Register Bits Description                          | 117 |

| Table 6-22: Timers/Counters Mode Description                            | 117 |

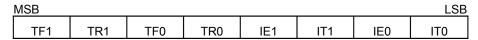

| Table 6-23: The TCON Register                                           | 117 |

| Table 6-24: The TCON Register Bit Functions                             |     |

| Table 6-25: Timer Modes                                                 |     |

| Table 6-26: The PCON Register                                           | 118 |

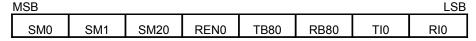

| Table 6-27: The S0CON Register                                          | 119 |

| Table 6-28: The S0CON Bit Functions                                     | 120 |

| Table 6-29: Serial Port 0 Modes                                         | 120 |

| Table 6-30: Serial 1 Modes                       | 120 |

|--------------------------------------------------|-----|

| Table 6-31: The S1CON Register                   |     |

| Table 6-32: The S1CON Bit Functions              | 121 |

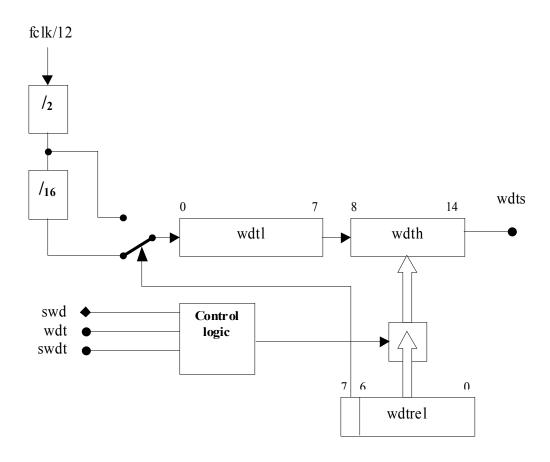

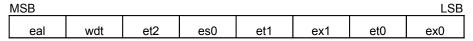

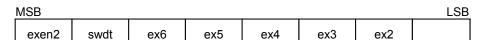

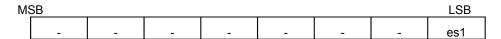

| Table 6-33: The IEN0 Register                    | 124 |

| Table 6-34: The IEN0 Bit Functions               | 124 |

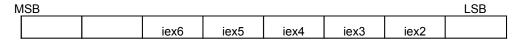

| Table 6-35: The IEN1 Register                    |     |

| Table 6-36: The IEN1 Bit Functions               | 124 |

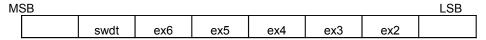

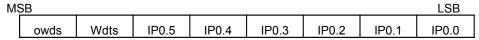

| Table 6-37: The IP0 Register                     | 125 |

| Table 6-38: The IP0 Bit Functions                |     |

| Table 6-39: The WDTREL Register                  | 125 |

| Table 6-40: The WDTREL Bit Functions             | 125 |

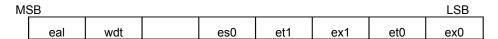

| Table 6-41: The IEN0 Register                    | 126 |

| Table 6-42: The IEN0 Bit Functions               | 126 |

| Table 6-43: The IEN1 Register                    |     |

| Table 6-44: The IEN1 Bit Functions               |     |

| Table 6-45: The IEN2 Register                    | 127 |

| Table 6-46: The IEN2 Bit Functions               |     |

| Table 6-47: The TCON Register                    |     |

| Table 6-48: The TCON Bit Functions               |     |

| Table 6-49: The IRCON Register                   | 128 |

| Table 6-50: The IRCON Bit Functions              |     |

| Table 6-51: Priority Level Groups                | 129 |

| Table 6-52: External MPU Interrupts              |     |

| Table 6-53: Control Bits for External Interrupts |     |

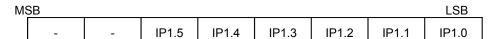

| Table 6-54: The IP0 Register:                    |     |

| Table 6-55: The IP1 Register:                    |     |

| Table 6-56: Priority Levels                      |     |

| Table 6-57: Groups of Priority                   |     |

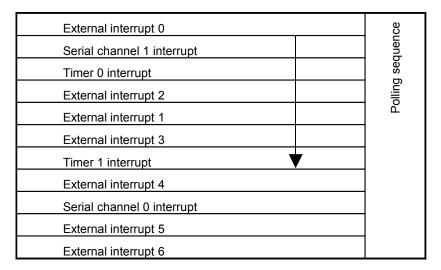

| Table 6-58: Polling Sequence:                    | 131 |

| Table 6-59: Interrupt Vectors                    | 132 |

# LIMITED USE LICENSE AGREEMENT

**Acceptance:** By using the Application Programming Interface and / or other software described in this document ("Licensed Software") and provided by TERIDIAN Semiconductor Corporation ("TSC"), the recipient of the software ("Licensee") accepts, and agrees to be bound by the terms and conditions hereof.

Acknowledgment: The Licensed Software has been developed for use specifically and exclusively in conjunction with TSC's meter products: 71M6511, 71M6511H, 71M6513, and 71M6513H. Licensee acknowledges that the Licensed Software was not designed for use with, nor has it been checked for performance with, any other devices.

<u>Title</u>: Title to the Licensed Software and related documentation remains with TSC and its licensors. Nothing contained in this Agreement shall be construed as transferring any right, title, or interest in the Licensed Software to Licensee except as expressly set forth herein. TSC expressly disclaims liability for any patent infringement claims based upon use of the Licensed Software either solely or in conjunction with third party software or hardware.

Licensee shall not make nor to permit the making of copies of the Licensed Software (including its documentation) except as authorized by this License Agreement or otherwise authorized in writing by TSC. Licensee further agrees not to engage in, nor to permit the recompilation, disassembly, or other reverse engineering of the Licensed Software.

<u>License Grant</u>: TSC grants Licensee a limited, non-exclusive, non-sub licensable, non-assignable and non-transferable license to use the software solely in conjunction with the meter devices manufactured and sold by TSC.

Non-disclosure and confidentiality: For the purpose of this Agreement, "Confidential Information" shall mean the Licensed Software and related documentation and information received by Licensee from TSC. All Confidential Information shall be maintained in confidence by Licensee and shall not be disclosed to any third party and shall be protected with the same degree of care as the Licensee normally uses in the protection of its own confidential information, but in no case with any less degree than reasonable care. Licensee further agrees not to use any Confidential Information received from TSC except as contemplated by the license granted herein.

<u>Disclaimer of Warranty</u>: TSC makes no representations or warranties, express or implied, regarding the Licensed Software, including any implied warranty of title, no infringement, merchantability, or fitness for a particular purpose, regardless of whether TSC knows or has reason to know Licensee's particular needs. TSC does not warrant that the functions of the Licensed Software will be free from error or will meet Licensee's requirements. TSC shall have no responsibility or liability for errors or product malfunction resulting from Licensee's use and/or modification of the Licensed Software.

<u>Limitation of Damages/Liability</u>: IN NO EVENT WILL TSC NOR ITS VENDORS OR AGENTS BE LIABLE TO LICENSEE FOR INDIRECT, INCIDENTAL, SPECIAL OR CONSEQUENTIAL DAMAGES IN CONNECTION WITH, OR ARISING OUT OF, THIS LICENSE AGREEMENT OR USE OF THE LICENSED SOFTWARE.

**Export:** Licensee shall adhere to the U.S. Export Administration Laws and Regulations ("EAR") and shall not export or re-export any technical data or products received from TSC or the direct product of such technical data to any proscribed country listed in the EAR unless properly authorized by the U.S. Government.

**Termination:** TSC shall have the right to terminate the license granted herein in the event Licensee fails to cure any material breach within thirty (30) days from receipt of notice from TSC. Upon termination, Licensee shall return or, at TSC's option certify destruction of, all copies of the Licensed Software in its possession.

<u>Law</u>: This Agreement shall be construed in accordance with the laws of the State of California. The Courts located in Orange County, CA shall have exclusive jurisdiction over any legal action between TSC and Licensee arising out of this License Agreement.

**Integration:** This License Agreement constitutes the entire agreement of the parties as to the subject matter hereof. No modification of the terms hereof shall be binding unless approved in writing by TSC.

1

### 1. INTRODUCTION

TERIDIAN Semiconductor Corporation's (TSC) 71M651x and 71M651XH single chip Power Meter Controllers are a family of Systems-on-Chip that supports all functionalities required to build a low-cost power meter. Demo Boards are available for each chip (71M6511/6511H and 71M6513/6513H) to allow development of embedded application, in conjunction with an In-Circuit Emulator. Development of a 71M651x application can be started in either 80515 assembly language, or more favorably in C using the Demo Boards. TSC provides, along with the 71M651x Demo Boards, a development toolkit that includes a demonstration program ("Demo Code") written in ANSI C that controls all features present on the Demo Boards. This Demo Code includes functions to manage the low level 80515 core such as memory, clock, power modes, interrupts; and high level functions such as the LCD, Real Time Clock, Serial interfaces and I/Os. The use of Demo Code portions will help reduce development time dramatically, since they allow the developer to focus on developing the application without dealing with the low-level layer such as hardware control, timing, etc. This document describes the different software layers and how to use them.

The Demo Code should allow customers to evaluate various resources of the 651X ICs but should not be regarded as production code. The Demo Code and all its components, with the exception of the CE code, are only example code and the use of it is as is and without guarantees implied. Customers may use the Demo Code as starting point at any given released revision level but should keep themselves informed about subsequent revisions of the Demo Code. Demo Code revisions may not be directly compatible with previously released revisions and/or embedded software used by customers. Customers need to adapt the Demo Code or other example code supplied by TERIDIAN Application Engineering to their own code base, and in this context TERIDIAN Semiconductor can only provide indirect assistance and support.

This Software User's Guide provides information on the following separate subjects:

- General software architecture and minimum requirements (Design Guide)

- Memory model, programming, test tools (Design Reference)

- Demo code structure, flow-charts, data flow, functions (Demo Code Description)

- Installing and using the EEP, compiler, ICE (Tool Installation Guide)

- Understanding and using the 80515 micro controller (80515 Reference)

#### 1.1. USE OF THIS DOCUMENT

The reader should have a basic familiarity with microprocessors, particularly the 80515 architecture, firmware, software development and power meter applications. Prior experience with, or knowledge of, the applicable ANSI and/or IEC standards will also be helpful.

This document presents the features included in the 71M651x Demo Boards in terms of software and some hardware. To get the most out of this document, the reader should also have available other 71M651x publications such as the 71M651x Demo Board User's Manual, respective data-sheets, errata list and application notes for additional details and recent developments.

#### 1.2. RELATED DOCUMENTATION

Please refer to the following documents for further information:

- 71M6511 Demo Board User's Manual

- 71M6513 Demo Board User's Manual

- 71M6511 Data Sheet

- 71M6513 Data Sheet

- Signum Systems ADM-51 In-Circuit Emulator Manual

- Keil Compiler Manual (Version 7.5 or later)

- µVision2 (Version 2.20a or later) Manual

TERIDIAN's web site (<a href="http://www.teridian.com">http://www.teridian.com</a>) should be frequently checked for updates, application notes and other helpful information.

Questions to TERIDIAN Applications Engineering can be directed via e-mail to the address:

meter.support@teridian.com

#### 1.3.COMPATIBILITY STATEMENT

Information presented in this manual applies to the following hardware and software revisions:

- 71M6511 Demo Code Revision 3.04 and 3.05

- 71M6513 Demo Code Revision 3.04 and 3.05

- 71M6511 Demo Board Revision 2.0 and 2.1

- 71M6513 Demo Board Revision 2.0 and 2.1

- Signum Systems Wemu51 Software 3.07.00 (2/14/2005) or later

- Signum Systems ADM51 firmware version 3 (2005/02/08) or later

The revision 3.04 of the Demo Board Code is the basis for all discussed sources, commands, register addresses and so forth. Known issues with revision 3.04 are disclosed within the code description, and workarounds or improvements are shown.

Features unique to Demo Board Code revision 3.05 are highlighted and discussed where necessary.

2

#### 2. DESIGN GUIDE

This section provides designers with some basic guidance in developing power meter applications utilizing the TSC 71M651x devices. There are two types of applications that can be developed:

- •Embedded application using the sources provided by TERIDIAN, or

- •Embedded application using only customer generated functions.

#### 2.1.HARDWARE REQUIREMENTS

The following are the minimum hardware requirements for developing custom programs:

- TERIDIAN 71M651x Demo Board. This board interfaces with a PC via the RS232 serial interface (COM port).

- AC Adaptor (AC/DC output) or variable power supply.

- PC Pentium with 512MB RAM and 10GB hard drive, 1 COM port and 1 USB port, running either Windows 2000, or Windows ME or Windows XP.

- Signum Systems ADM-51 In-Circuit Emulator (for loading and debugging the embedded application) and its associated cables. Signum references this device as ADM-51.

#### 2.2.SOFTWARE REQUIREMENTS

The following are the minimum software requirements for embedded application programming:

- Keil Compiler version 7.5 or later.

- μVision2 version 3.05c (Note: this version comes with Keil Compiler version 7.5).

- Signum Systems software Wemu51 (comes with Signum Systems ADM-51 ICE hardware).

The following software tools/programs are included in the 71M651x development kit and should be installed on the development PC:

- Demo Code with Command Line Interface (CLI) Used to interface directly to metering functions and to the chip hardware.

- Source files

- Demo Code object file (hex file).

In order to generate and test software, the Keil compiler and the Signum in-circuit emulator (ICE) must be installed per the instructions in section 4. The include files and header files must also be present on the development PC. Typically, a design session consists of the following steps:

- Editing C source code using μVision2

- Compiling the source code using the Keil compiler

- · Modifying the source code and recompiling until all compiler error messages are resolved

- Using the assembler and linker to generate executable code

- Downloading the executable code to the ICE

- Executing the code and watching its effects on the target

#### Software Architecture:

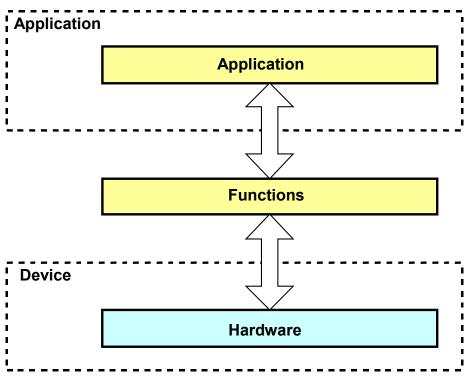

The 71M651x software architecture is partitioned into three separate layers:

- The lowest level is the device or hardware layer, i.e. the discrete functional blocks of the chip and the peripheral components, such as RTC, EEPROM, MPU clock management, LCD etc.

- 2. The second layer consists of the functions, which enable the application to communicate with the device layer.

- 3. The third layer is the application layer. This layer is partially implemented by the Demo Code for evaluation purposes, but extensions and enhancements can be added by the application software developer to design suitable electronic power meter applications.

Figure 1 shows the partitions of each software component. As illustrated, there are many different designs an application can develop depending on its usage. Section 5 describes in more detail the functions within each component.

Figure 2-1: Software Structure

#### 2.3.UTILITIES

Two utilities are offered that make it possible to perform certain operations on the object (HEX) files without having to use a compiler:

- IO\_MERGE.EXE allows combining the object file with a text script in order to change certain default settings

of the program. For example, modified calibration coefficients resulting from an actual calibration can be

inserted into the object file.

- CE MERGE.EXE allows combining the object file with an updated image of the CE code.

Both utilities are executed from a DOS window (DOS command prompt). To invoke the DOS window, the "command prompt" option is selected after selecting Start – All Programs – Accessories.

# 2.3.1. **IO\_MERGE**

Any changes to I/O RAM (Configuration RAM) can be made permanent by merging them into the object file. The first step for this is to create a maco file (macro.txt) containing the commands adjusting the I/O RAM, such as the following commands affecting calibration:

]8=+16381 ]9=+16397 ]E=+237

The io\_merge program updates the 6511\_demo.hex file with the values contained in the macro file. The io\_merge program must be in the same directory as the source files, or a path to the executable must be declared. Executing the io\_merge program with no arguments will display the syntax description. To merge the file macro.txt and the object file old 6511 demo.hex into the new object file new 6511 demo.hex, use the command:

io\_merge old\_6511\_demo.hex macro.txt new\_6511\_demo.hex

## 2.3.2. **CE\_MERGE**

The ce\_merge program updates the 6511\_demo.hex file with the CE program image contained in the CE.CE file and the data image CE.DAT. Both CE.CE and CE.DAT must be in Intel HEX format, i.e. both files are not in the source format but in the compiled format (Verilog HEX). These files will be made available from Teridian in the cases when updates to the CE images are necessary.

To merge the object file old\_6511\_demo.hex with CE.CE and CE.DAT into the new object file new\_6511\_demo.hex, use the command:

ce\_merge old\_6513\_demo.hex ce.ce ce.dat 6513\_demo.hex

3

## 3. DESIGN REFERENCE

As depicted in Figure 1 of section 2, the 71M651x provides a great deal of design flexibility for the application developer. Programming details are described below.

#### 3.1.PROGRAM MEMORY

The embedded 80515 MPU within the 71M651x has separate program (64K bytes) and data memory (2K bytes). In addition, it has 4K bytes of Compute Engine program RAM.

The Flash program memory is addressed as a 64KB block, segmented in 512-byte pages. Selection of these individual blocks is accomplished using the function calls related to flash memory, which are described in more detail below.

When generating code for ROM applications, special precautions have to be taken. Contact TERIDIAN Semiconductor for details.

#### 3.2.DATA MEMORY

The 71M651x has 2K bytes of Data Memory for exclusive use of the embedded 80C515 MPU. In addition, there are 5K byte shared with the Compute Engine. See Table 3-1 for a summary.

| Address<br>(hex) | Memory<br>Technology | Memory Type      | Typical Usage                             | Wait States<br>(at 5MHz) | Memory Size<br>(bytes) |

|------------------|----------------------|------------------|-------------------------------------------|--------------------------|------------------------|

| 0000-FFFF        | Flash Memory         | Non-volatile     | Program and non-volatile data             | 0                        | 64KB                   |

| 0000-07FF        | Static RAM           | Battery-buffered | MPU data XRAM,                            | 0                        | 2KB                    |

| 1000-13FF        | Static RAM           | Volatile         | CE data                                   | 5                        | 1KB                    |

| 2000-20FF        | Static RAM           | Volatile         | Miscellaneous I/O RAM (configuration RAM) | 0                        | 256                    |

| 3000-3FFF        | Static RAM           | Volatile         | CE Program code                           | 5                        | 4KB                    |

Table 3-1: Memory Map

#### 3.3.PROGRAMMING OF THE 71M651X CHIPS

There are two ways to download a hex file to the 71M651x Flash Memory:

- Using a Signum Systems ADM-51 ICE.

- Using the TERIDIAN Semiconductor Flash Download Board Module (FDBM).

The 71M651x also is available in a ROM version. Testing of the ROM version is supported with the onek\_c.asm assembler code.

For both programming and debugging code it is important that the hardware watchdog timer is disabled. See the Demo Board User's Manual for details.

#### 3.4.TEST TOOLS

A command line interface operated via the serial interface of the 71M651X MPU provides a test tool that can be used to exercise the functions provided by the low-level libraries. The command-line interface requires the following environment:

- 1) Demo Code (651X demo.hex) must be resident in flash memory

- The Demo Board is connected via a Debug Board to a PC running Hyperterminal or another type of terminal program.

- 3) The communication parameters are set at 9600 bps, 8N1, XON/XOFF flow control

#### 3.4.1. Running the 651X Demo.hex Program

This object file is the 71M651x embedded application developed by TERIDIAN to exercise all low-level function calls using a serial interface. Demo Boards ship pre-installed with this program. To run this program:

- Connect a serial cable between the serial port of the Debug Board RS232 and a COM port of a Windows PC.

- Open a Windows' Hyperterminal session at 9600 bps, 8N1 with XON/XOFF flow control enabled.

- Power on the Demo Board and hit <CR> a few times on the PC keyboard until '>' is displayed on the Hyperterminal screen.

- Type '??' for general usage help. Type '? [Cmd]' for specific command help. For example, ?M will display

how to run the Meter Display command.

- All references to 'c' (lower case c) indicate any ASCII character, all other lowercase letters are one-byte numbers

- Numbers can be entered in decimal by preceding them with a plus-sign (e.g. hex 20 = +32)

The 71M6511 and 71M6513 Demo Board User's Manuals contain instructions on how to connect the serial cable.

Figure 3-1: Port Speed and Handshake Setup (left) and Port Configuration Setup (right)

HyperTerminal can be found by selecting Programs →Accessories → Communications from the Windows start menu. The connection parameters are configured by selecting File → Properties and then by pressing the Configure button. Port speed and flow control are configured under the General tab (figure 1-3, left), bit settings are configured by pressing the Configure button (figure 3-1, right), as shown below.

# 3.4.2. Complete List of CLI Commands

# **Command Overview**

It is best to use the help utility of the demo code to determine how to use the commands of the command line interface. The tables in this section serve only as an overview of the capabilities of the serial command interface.

| Letter(s) | Function                               | Comment                          |

|-----------|----------------------------------------|----------------------------------|

| ?         | Help                                   |                                  |

| ]         | CE data access                         |                                  |

| )         | MPU data access                        |                                  |

| ,         | Repeat command                         |                                  |

| 1         | Ignore rest of line                    | Comment – for use in macro files |

| С         | Compute engine (CE), RTM, TMUX control |                                  |

| CL        | Calibration (auto-calibration)         |                                  |

| СР        | Pulse count control                    | Demo Code revision 3.05 only     |

| EE        | EEPROM control                         |                                  |

| I         | Information message                    |                                  |

| М         | Meter display                          |                                  |

| Р         | Meter profile                          |                                  |

| PS        | Power Save Mode                        |                                  |

| R         | User I/O and SFR access                |                                  |

| RT        | Real-Time clock                        |                                  |

| Т         | Display Trim Information               |                                  |

| w         | Wait/reset command                     | Demo Code revision 3.05 only     |

| Z         | Reset                                  |                                  |

# **Detailed Command Descriptions**

| ?            | HELP                                                  |                                                   |

|--------------|-------------------------------------------------------|---------------------------------------------------|

| Description: | Command help available for each of the options below. |                                                   |

| Usage:       | ? [option]                                            |                                                   |

| Options:     | ?                                                     | Command line interpreter help menu.               |

|              | 1                                                     | Display help on access CE data RAM                |

|              | )                                                     | Display help on access MPU RAM                    |

|              | ,                                                     | Display help on repeat last command               |

|              | 1                                                     | Display help on ignore rest of line               |

|              | С                                                     | Display help on compute engine control            |

|              | EE                                                    | Display help on EEPROM control                    |

|              | I                                                     | Display help on information message               |

|              | M                                                     | Display help on meter display control             |

|              | Р                                                     | Display help on profile of meter                  |

|              | R                                                     | Display help on SFR control                       |

|              | RT                                                    | Display help on RTC control                       |

|              | Т                                                     | Display help on trim control                      |

|              | Z                                                     | Display help on reset                             |

|              | w                                                     | Wait/reset command - Demo Code revision 3.05 only |

| Examples:    | ??                                                    | Display the command line interpreter help menu.   |

|              | ?C                                                    | Displays compute engine control help.             |

| 1            | CE DATA ACCESS                                  |                                                   |

|--------------|-------------------------------------------------|---------------------------------------------------|

| Description: | Allows user to read and write to CE data space. |                                                   |

| Usage:       | ] [Starting CE Data Address] [option][option]   |                                                   |

| Options:     | ???                                             | Read consecutive 16-bit words in Decimal          |

|              | \$\$\$                                          | Read consecutive 16-bit words in Hex              |

|              | =n=n                                            | Write consecutive memory values                   |

|              | ΙΠ                                              | Update default version of CE Data in flash memory |

| Example:     | ]40\$\$\$                                       | Reads CE data words 0x40, 0x41 and 0x42.          |

|              | ]7E=12345678=9876ABCD                           | Writes two words starting @ 0x7E                  |

CE data space is the address range for the CE DRAM (0x1000 to 0x13FF). All CE data words are in 4-byte (32-bit) format. The offset of 0x1000 does not have to be entered when using the ] command, thus typing ]A? will access the 32-bit word located at the byte address 0x1000 + 4 \* A = 0x1028.

| )            | MPU DATA ACCESS                                       |                                          |

|--------------|-------------------------------------------------------|------------------------------------------|

| Description: | Allows user to read from and write to MPU data space. |                                          |

| Usage:       | ) [Starting MPU Data Address] [option][option]        |                                          |

| Options:     | ???                                                   | Read consecutive 32-bit words in Decimal |

|              | \$\$\$                                                | Read consecutive 32-bit words in Hex     |

|              | =n=n                                                  | Write consecutive memory values          |

| Example:     | 08\$\$\$                                              | Reads data words 0x08, 0x0C, 0x10, 0x14  |

|              | 04=12345678=9876ABCD                                  | Writes two words starting @ 0x04         |

MPU or XDATA space is the address range for the MPU XRAM (0x0000 to 0x7FFF). All MPU data words are in 4-byte (32-bit) format. Typing ]A? will access the 32-bit word located at the byte address 4 \* A = 0x28. The energy accumulation registers of the Demo Code can be accessed by typing two Dollar signs ("\$\$"), typing question marks will display negative decimal values if the most significant bit is set.

RAM access is limited to the lower 1KB address range. Read and write operations will "wrap around" at higher addresses, i.e. ) 200? will yield the same result as ) 0?

| , (comma)    | REPEAT LAST COMMAND                                    |  |

|--------------|--------------------------------------------------------|--|

| Description: | Repeats the last command issued from the command line. |  |

| Usage:       | , (comma)                                              |  |

| Options:     | NONE                                                   |  |

| 1            | IGNORE REST OF LINE                                    |                                                                                                   |

|--------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Description: | Interpreter ignores anything following this character. |                                                                                                   |

| Usage:       | I                                                      | Useful to separate comments from commands when sending macro text files via the serial interface. |

| Options:     | NONE                                                   |                                                                                                   |

| С            | COMPUTE ENGINE, TMUX, and RTM CONTROL |                                                                                                        |  |

|--------------|---------------------------------------|--------------------------------------------------------------------------------------------------------|--|

| Description: | Allows the user to enable and cor     | Allows the user to enable and configure the compute engine plus other controls                         |  |

| Usage:       | C [option] [argument]                 |                                                                                                        |  |

| Options:     | En                                    | Compute Engine Enable (1 → Enable, 0 → Disable)                                                        |  |

|              | Tn                                    | Select input n for TMUX output pin                                                                     |  |

|              | REn                                   | RTM output control (1 → Enable, 0 → Disable)                                                           |  |

|              | RSa.b.c.d                             | Selects RTM output                                                                                     |  |

| Example:     | CE0                                   | Disables CE, followed by "CE OFF" display on LCD. The Demo Code will reset if the WD timer is enabled. |  |

|              | СТЗ                                   | Selects VBIAS for TMUX output pin                                                                      |  |

| CL           | CALIBRATION CONTROL                                                           |                                                                                                                                                                                                                          |

|--------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description: | Allows the user to initiate auto-calibration and to store calibration values. |                                                                                                                                                                                                                          |

| Usage:       | CL [option]                                                                   |                                                                                                                                                                                                                          |

| Options:     | В                                                                             | Begin auto-calibration. Prior to auto-calibration, the calibration coefficients are automatically restored from flash memory. If the coefficients are not unity gain (0x4000), auto-calibration will yield poor results. |

|              | S                                                                             | Save calibration coefficients to EEPROM starting at address 0x0004                                                                                                                                                       |

|              | R                                                                             | Restore calibration coefficients from EEPROM                                                                                                                                                                             |

|              | D                                                                             | Restore coefficients from flash memory                                                                                                                                                                                   |

| Example:     | CLB                                                                           | Starts auto-calibration                                                                                                                                                                                                  |

Before starting the auto-calibration process, target values for voltage and current must be entered in I/O RAM prior to calibration (V at 0x2029, I at 0x202A, duration in accumulation intervals at 0x2028), and the target voltage and current must be applied constantly during calibration. No phase adjustment will be performed. Coefficients can be saved to EEPROM using the CLS command.

| СР                    | PULSE-COUNT CONTROL                                   | Demo Code Revision 3.05 only                                                                                            |

|-----------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Description:          | Allows the user to control the pulse count functions. |                                                                                                                         |

| Usage:                | CP [option]                                           |                                                                                                                         |

| Command combinations: | СРА                                                   | Start pulse counting for time period defined with the CPD command. Pulse counts will display with commands M15.2, M16.2 |

|                       | CPC                                                   | Clear the absolute pulse count displays (shown with commands M15.1, M16.1)                                              |

|                       | CPDn                                                  | Set time window for pulse counters to n seconds, n is interpreted as a decimal number.                                  |

| Example:              | CPD60                                                 | Set time window to 60 seconds.                                                                                          |

Pulse counts accumulated over a time window defined by the CPD command will be displayed by M15.2 or M16.2 after the defined time has expired.

Commands M15.1 and M16.1 will display the **absolute** pulse count for the W and VAR outputs. These

displays are reset to zero with the CPC command (or the XRAM write )1=2). Commands M15.2 and M16.2 will display the number of pulses counted during the interval defined by the CPD command. These displays are reset only after a new reading, as initiated by the CPA command.

| EE           | EEPROM CONTROL                                  |                                                  |

|--------------|-------------------------------------------------|--------------------------------------------------|

| Description: | Allows user to enable read and write to EEPROM. |                                                  |

| Usage:       | EE [option] [arguments]                         |                                                  |

| Options:     | Cn                                              | EEPROM Access (1 → Enable, 0 → Disable)          |

|              | Ra.b                                            | Read EEPROM at address 'a' for 'b' bytes.        |

|              | Sabcxyz                                         | Write characters to buffer (sets Write length)   |

|              | Та                                              | Transmit buffer to EEPROM at address 'a'.        |

|              | Wa.bz                                           | Write values to buffer                           |

| Example:     | EEShello; EET\$0210                             | Writes 'hello' starting at EEPROM address 0x210. |

| 1            | INFORMATION MESSAGES                                |                                       |  |

|--------------|-----------------------------------------------------|---------------------------------------|--|

| Description: | Allows user to read and write information messages. |                                       |  |

| Usage:       | I [option] [argument]                               | I [option] [argument]                 |  |

| Options:     | 0                                                   | Displays complete version information |  |

|              | 1                                                   | Displays Demo Code version string     |  |

|              | 1=abcdef                                            | Change Demo Code version string       |  |

|              | 2                                                   | Displays Copyright string             |  |

|              | 3                                                   | CE Version string                     |  |

|              | 3=abcdef                                            | Change CE Code version string         |  |

| Example:     | I1                                                  | Returns Demo Code version             |  |

| М            | METER DISPLAY<br>CONTROL (LCD) |                                                                                                    |  |

|--------------|--------------------------------|----------------------------------------------------------------------------------------------------|--|

| Description: | Allows user to select in       | Allows user to select internal variables to be displayed.                                          |  |

| Usage:       | M [option]. [option]           |                                                                                                    |  |

| Options:     | None                           | Displays "HELLO" message                                                                           |  |

|              | 0                              | Disables display updates                                                                           |  |

|              | 1                              | Temperature (C° delta from nominal)                                                                |  |

|              | 2                              | Frequency (Hz)                                                                                     |  |

|              | 3. [phase]                     | kWh Total Consumption (display wraps around at 999.999)                                            |  |

|              | 4. [phase]                     | kWh Total Inverse Consumption (display wraps around at 999.999)                                    |  |

|              | 5. [phase]                     | kVARh Total Consumption (display wraps around at 999.999)                                          |  |

|              | 6. [phase]                     | kVAh Total Inverse Consumption (display wraps around at 999.999)                                   |  |

|              | 7. [phase]                     | VAh Total (display wraps around at 999.999)                                                        |  |

|              | 8                              | Operating Time (in hours)                                                                          |  |

|              | 9                              | Real Time Clock                                                                                    |  |

|              | 10                             | Calendar Date                                                                                      |  |

|              | 11 [phase]                     | V/I Phase at phase (degrees)                                                                       |  |

|              | 12. [phase] (6513)             | V/V Angle between phases (1= A/B, 2 = A/C))                                                        |  |

|              | 12.1 (6511)<br>13.1 (6513)     | Main edge count (accumulated)                                                                      |  |

|              | 12.2 (6511)<br>13.2 (6513)     | CE main edge count for the last accumulation interval                                              |  |

|              | 13.1 (6511)<br>14.1 (6513)     | Absolute count for W pulses. Reset with CPC command. <b>Demo Code revision 3.05 only.</b>          |  |

|              | 13.2 (6511)<br>14.2 (6513)     | Count for W pulses in time window defined by the CPD command. <b>Demo Code revision 3.05 only.</b> |  |

|              | 14.1 (6511)<br>15.1 (6513)     | Absolute count for VAR pulses. Reset with CPC command.  Demo Code revision 3.05 only.              |  |

|              | 14.2 (6511)<br>15.2 (6513)     | Count for W pulses in time window defined by the CPD command. <b>Demo Code revision 3.05 only.</b> |  |

| Example:     | M3.1                           | Displays Wh total consumption of phase A.                                                          |  |

Displays for total consumption wrap around at 999.999kWh (or kVARh, kVAh) due to the number of available display digits. Internal registers (counters) of the Demo Code are 64 bits wide and do not wrap around.

Values for [phase]: 0 = sum, 1 = A, 2 = B, 3 = C (6513), 0 = sum, 1 = A, 2 = B (6511)

| MR           | RMS DISPLAY CONTROL (LCD)                                       |                                         |

|--------------|-----------------------------------------------------------------|-----------------------------------------|

| Description: | Allows user to select meter RMS display for voltage or current. |                                         |

| Usage:       | MR [option]. [option]                                           |                                         |

| Options:     | 1. [phase]                                                      | Displays instantaneous RMS current      |

|              | 2. [phase]                                                      | Displays instantaneous RMS voltage      |

|              |                                                                 | Values for [phase]: 1 = A, 2 = B, 3 = C |

| Example:     | MR1.1                                                           | Displays phase A RMS current.           |

| Р            | PROFILE OF METER                            |  |

|--------------|---------------------------------------------|--|

| Description: | Returns current meter configuration profile |  |

| Usage:       | Р                                           |  |

| Options:     | None                                        |  |

The profile of the meter is a summary of the important settings of the I/O RAM registers.

| PS           | POWER SAVE MODE        |                                                                                                |

|--------------|------------------------|------------------------------------------------------------------------------------------------|

| Description: | Enters power save mode | Disables CE, ADC, CKOUT, ECK, RTM, SSI, TMUX VREF, and serial port, sets MPU clock to 38.4KHz. |

| Usage:       | PS                     |                                                                                                |

| Options:     | None                   |                                                                                                |

| R            | USER I/O AND SFR<br>CONTROL        |                                                                  |  |

|--------------|------------------------------------|------------------------------------------------------------------|--|

| Description: | Allows user to read and write to I | ORAM and special function registers.                             |  |

| Usage:       | R [option] [register] [option]     | R [option] [register] [option]                                   |  |

| Options:     | lx                                 | Select I/O RAM location x (\$2000 offset is automatically added) |  |

|              | x                                  | Select internal SFR at address x                                 |  |

|              | ???                                | Read consecutive registers in Decimal                            |  |

|              | \$\$\$                             | Read consecutive registers in Hex                                |  |

|              | =n=n                               | Set consecutive registers' values                                |  |

|              | ,                                  | Exit SFR controls                                                |  |

| Example:     | RI0\$\$\$                          | Read CE0, CE1 and CE2 registers                                  |  |

| RT           | REAL TIME CLOCK<br>CONTROL                       |                                          |

|--------------|--------------------------------------------------|------------------------------------------|

| Description: | Allows user to read and set the real time clock. |                                          |

| Usage:       | RT [option] [value] [value]                      |                                          |

| Options:     | Dy.m.d.w: Day of week                            | (year, month, day, weekday [1 = Sunday]) |

|              | R                                                | Read Real Time Clock.                    |

|              | Th.m.s                                           | Time of day: (hr, min, sec).             |

|              | As.t                                             | Real Time Adjust: (speed, trim)          |

| Example:     | RTD05.03.17.5                                    | Programs the RTC to Thursday, 3/17/2005  |

The "Military Time Format" is used for the RTC, i.e. 15:00 is 3:00 PM.

| Т            | TRIM CONTROL                      |                                           |  |

|--------------|-----------------------------------|-------------------------------------------|--|

| Description: | Allows user to read trim and fuse | Allows user to read trim and fuse values. |  |

| Usage:       | T [option]                        |                                           |  |

| Options:     | 4                                 | Read fuse 4.                              |  |

|              | 5                                 | Read fuse 5.                              |  |

|              | 6                                 | Read fuse 6.                              |  |

| Example:     | NONE                              |                                           |  |

These commands are only accessible for the 6511H (0.1%) parts. When used on a 71M6511 (0.5%) part, the results will be displayed as zero.

| W            | WATCHDOG RESET                                                                                                                                                                         |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description: | Halts the Demo Code program, thus suppressing the triggering of the hardware watchdog timer. This will cause a reset, if the watchdog timer is enabled.  Demo Code revision 3.05 only. |

| Usage:       | W                                                                                                                                                                                      |

| Options:     | NONE                                                                                                                                                                                   |

| Z            | RESET       |

|--------------|-------------|

| Description: | Soft Reset. |

| Usage:       | Z           |

| Options:     | NONE        |

# 3.4.3. Command (Macro) Files

Commands or series of commands may be stored in text (ASCII) files and sent to the 71M651X using the "Transfer – Send Text File" command of Hyperterminal or any other terminal program.

# 4. TOOL INSTALLATION GUIDE

This section provides detailed installation instructions for the Signum ADM-51 in-circuit emulator and for the Keil compiler.

### 4.1.INSTALLING THE PROGRAMS FOR THE ADM51 EMULATOR

The AMD51 ICE interfaces with the PC is via the USB serial interface.

The installation process consists of the following steps:

- 1. Installing the Chameleon Debugger used with the Signum ICE

- 2. Installing the ADM51 USB driver

- 3. Installing updates

- 4. Creating a project

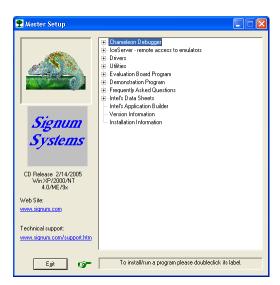

# 4.2.INSTALLING THE WEMU PROGRAM (CHAMELEON DEBUGGER)

Insert the CD from Signum Systems and connect the ICE ADM51 to the PC with the provided USB cable.

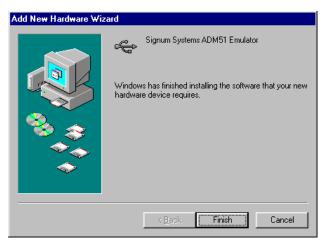

The following dialog box will appear (this dialog box also shows the release date of the program):

Click on "Chameleon Debugger" and then select "ADM51 Emulator".

Follow the instructions given by the installation program.

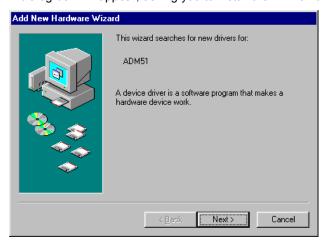

### 4.3.INSTALLING THE ADM51 USB DRIVER

The Wemu51 program communicates with the emulator ADM51 via the USB interface of the PC. The USB driver for the ADM51 has to be installed prior to using the emulator. After plugging in the USB cable into the PC and the ADM51 ICE the status light of the ADM51 emulator should come on.

A dialog box will appear, asking you to install the ADM51 driver.

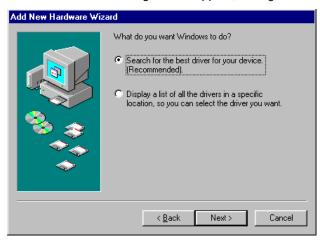

Click Next. Another dialog box will appear, asking how to search for the driver. Use the recommended method.

Click Next.

Another screen (not shown) will appear asking to locate the driver. Select *Specific Path* and browse to: C:\Program Files\Signum Systems\Wemu51\Drivers\USB. Click Next.

Click Finish.

Click Finish again.

USB 1.1 is sufficient for operation of the ADM51. If higher performance is desired and no USB 2.0 port is available on the host PC, a USB 2.0 card can be installed as an option.

# 4.4.INSTALLING UPDATES TO THE EMULATOR PROGRAM AND HARDWARE

If the Wemu51 program is revision 3.07 or later, no special precautions have to be taken. Otherwise, the program should be updated using the Signum Systems web site (<a href="https://www.signum.com">www.signum.com</a>).

When running the Wemu51 program revision 3.07 or later, the firmware in the ADM51 will be checked automatically. ADM51 emulators with outdated firmware will not function properly. The Wemu51 will offer an automatic update for the ADM51, if necessary. For a successful upgrade it is vital to follow the instructions on screen precisely.

#### **4.5.CREATING A PROJECT**

Double click on the WEMU51 icon to start the Chameleon debugger.

```

🧬 Signum Systems Wemu51 - ADM51 Emulator: <u>"6513"</u>

<u>File Edit View Debug Project Options Window Help</u>

CFU SRC PEM XBM BM & SVM SCO

RES 🚇

Source_1 - APIE.C - Follow code focus

*This code and information is provided "as is" without warranty of any *kind, either expressed or implied, including but not limited to the *implied warranties of merchantability and/or fitness for a particular

25

3>

5> * purpose.

6>

7>

* Copyright (C) 2003 TDK SemiConductor, Corporation. All Rights Reserved. *

11> //

12> // DESCRIPTION: 71M651x POWER METER - API Exerciser Routines

13> //

14> // AUTHOR: MTF

15> //

16> // HISTORY: 2003 OCTOBER 30; First Version.

19> //

20> // File: APIE.C

```

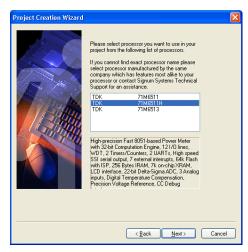

Click Project/Create New Project. The following screen will appear:

Follow the instructions of the Create Project Wizard by selecting Next.

When prompted for the project name to be used, type a convenient project name. Click Next.

When prompted for the project directory to be used, select an existing folder on the PC. any folder in the Wemu51 installation directory! Click *Next*.

When prompted for the emulator to be used, select ADM51 Emulator. Click Next.

When prompted for the communication device to be used, select USB ADM51. Click Next.

When prompted for the processor to be used, select either *71M6511* or *71M6513*. For all firmware purposes, there is no difference between 6511 and 6511H or between 6513 and 6513H. Click *Next*.

Click Finish.

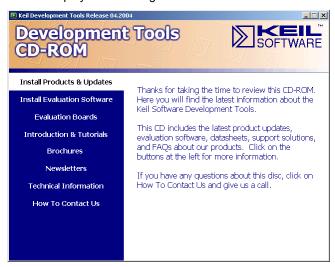

#### 4.6.INSTALLING THE KEIL COMPILER

After inserting the Keil CD-ROM into the CD drive of the PC, the on-screen instructions should be followed to install the Keil compiler.

For PCs that can only use one type of drive at a time (CD-ROM drive, floppy drive, such as certain laptops), it is helpful to copy the contents of the floppy labeled "Add-On Disk" to the hard drive of the PC. That way, drives do not have to be swapped out during the installation.

The installer will display the following screen:

Select Install Products & Updates

Select C51 Compiler and Tools

Follow the on-screen instructions of the installation program. When prompted for the add-on disk, insert the disk in the floppy drive and click *Next* or browse to the location of the files (if they were previously copied to the hard drive of the PC) by clicking Browse.

#### 4.7.CREATING A PROJECT FOR THE KEIL COMPILER

## 4.7.1. Directory Structure

The following directory structure is established when the files from the archive 651X\_Demo.zip are unpacked while maintaining the structure of subdirectories:

- <drive letter>:\...\meter project\

- <drive letter>:\...\meter project\CE

- <drive letter>:\...\meter project\CLI

- <drive letter>:\...\meter project\CLI\_651X

- <drive letter>:\...\meter project\docs

- <drive letter>:\...\meter project\IO

- <drive letter>:\...\meter project\Main 651X

- <drive letter>:\...\meter project\Util

The project control file 651X\_demo.uv2 will be in the directory <drive letter>:\...\meter project. The Keil compiler can be configured easily by loading the file 651X\_demo.uv2, using the *Project* Menu and selecting the *Open Project* command.

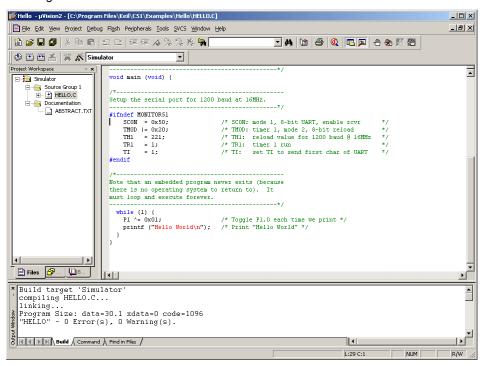

The window shown below should appear when the project control file is opened.

The Project Workspace screen on the left side of the window shows the main components of the source (Startup and main, Metering, CE, IO, Utilities, Command Line Interface) in folders. Folders can be opened by clicking on the plus sign next to them. Opening the folders will display the source files associated with them. Opening the source files will display the header files used by them.

It should be noted that not all header files are physically present in the project directory. The files absacc.h, string.h, ctype.h, and setjmp.h are provided by the compiler manufacturer, and they are located in the Keil\C51\INC directory.

# 4.7.2. Adjusting the Keil Compiler Settings

Once, the Keil compiler is installed, the most convenient method to start the project is to double-click on the file 651X\_demo.UV2. This will start the Keil compiler with the proper settings stored in the 651X\_demo.UV2 file.

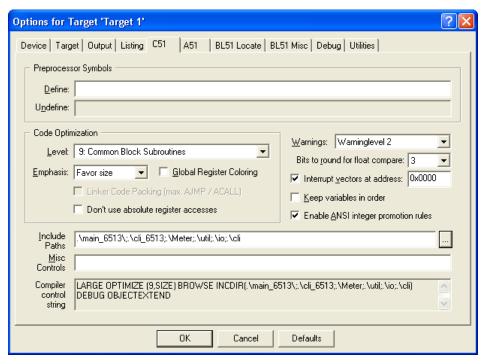

Directory structures and drive names vary from PC to PC. The settings for the compiler can be adjusted using the following method:

- 1. Select "target1" in the leftmost window.

- 2. Select "project" from the top menu and then select "options for target 1".

- 3. Select the "C51" tab.

- 4. Click the button right next to the "Include Paths" window. Three paths will be listed, pointing to meter projects, meter projects\demo, and meter projects\demo\header files.

- 5. If necessary, delete these path entries (X button) and replace them with the corresponding path entries for your PC ( button).

The dialog box should look like shown below. After making the necessary changes, the project file (651X\_demo.UV2) should be stored.

# 4.7.3. Manually Controlling the Keil Compiler Settings

If the method described in section "Adjusting the Keil Compiler Settings" is not followed, the Keil compiler settings can also be controlled manually.

The target options should be selected in order to adapt the compiler controls properly to the target. The uVision compiler environment is started by selecting Programs  $\rightarrow$  Keil  $\rightarrow$  uVision2. uVision should start up and present the following window:

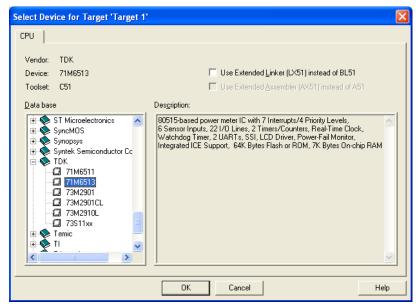

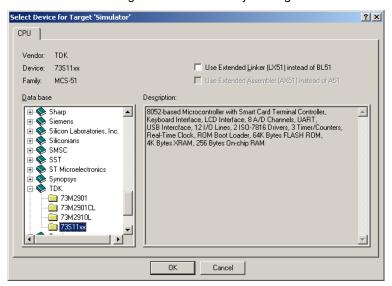

Under *Project* → *Options for Target1*, select the *Device* tab and check the selected device. Newer versions of the Keil Compiler offer selection of TERIDIAN (labeled "TDK") 71M6511 and 71M6513 devices:

For older versions of the Keil compiler, select the TERIDIAN folder (labeled "TDK"), open it by clicking on the + sign and select 73M2910L as the target device. Confirm by clicking OK.

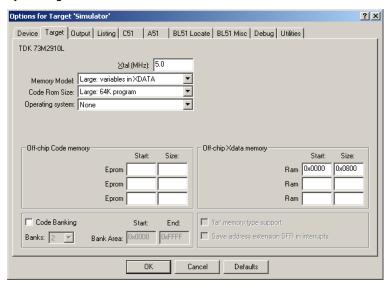

Under *Project* → *Options for Target1*, select the *Target* tab and enter the values in the fields as shown above. Confirm by clicking *OK*.

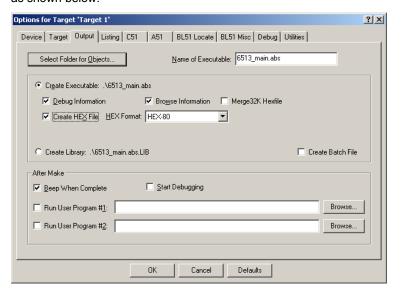

Under the Output tab, select a name for the executable (object) file with .abs extension' in the field labeled "Name of the executable" and check the fields by "Debug Information", "Browse Information" and "Create HEX File". This will guarantee that high-level source information will be embedded in the output file. Select *HEX-80* as the output format, as shown below:

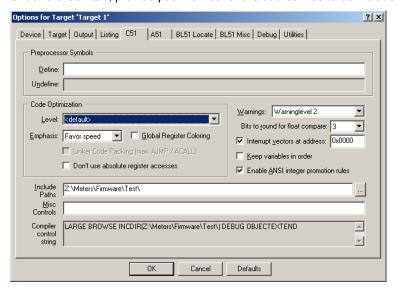

Under the C51 tab, provide path names for the source files to be included, as shown below.

Click OK to set all the options selected for project and return to the main menu.

With the source and header files now existing in the newly created project, the files can be compiled using the Build Target option under the Project menu.

#### 4.8.PROJECT MANAGEMENT TOOLS

With large software projects involving a multitude of source, object, list and other files in various revisions, it is very helpful to use a version control tool.

To manage file versions under Windows, Tortoise CVS, a free version control utility, might be useful. This utility can be found at <a href="http://www.tortoisecvs.org/">http://www.tortoisecvs.org/</a>.

### **4.9.ALTERNATIVE COMPILERS**

The Demo Code was written for the Keil compiler. However, alternative compilers may be used if the code is modified to ensure compatibility with the alternative compiler. One example of an alternative compiler is SDCC, a free compiler available from www. Sourceforge.net.

The Keil extensions for the 8051 are not compatible with the 8051 extensions used by the SDCC.

The batch files BUILD6511.BAT and BUILD6513.BAT are provided with the Demo Kit to support building object files using alternative compilers. These batch files use the Keil compiler calls with the applicable compiler options and can therefore serve as examples on how to invoke alternative compilers. The linker control files LINK6511.TXT and LINK6513.TXT called by the batch files can show how to properly invoke linkers.

To compile with DOS-style tools, arrange for a DOS batch file to invoke the tools and set the properties of the batch file to leave the window open, so that errors can be seen. Then, to compile, double click on this batch file in Windows explorer.

#### 4.10.ALTERNATIVE EDITORS

Many modern text editors have a feature called "tag jumping" that helps a programmer to read and understand unfamiliar code. TERIDIAN Semiconductor recommends using such an editor to read, understand and modify demonstration code. Tag jumping is a feature that is not supported by the Keil uVision editor.

This is how tag jumping works:

- 1. A "tag file generator" program is run on some directories containing .c or .h files. TERIDIAN Semiconductor recommends placing the tag file generator in a DOS batch file in the same directory as the make file of the project. Wattmeter demonstration code includes such a batch file: "T.BAT". To run a batch file, double-click it in windows explorer. A DOS batch file is just an ASCII file (like a .C file) containing DOS commands. DOS commands are described at <a href="http://www.computerhope.com/msdos.htm">http://www.computerhope.com/msdos.htm</a>.

- 2. The tag file should then be copied to convenient places for a text editor. TERIDIAN Semiconductor recommends copying the tag file into each source code directory. In that way, the default tag file location for most editors becomes just ".\tags" for all projects, and multiple projects do not conflict. Copying the tag file can be an automatic part of the DOS batch file that generates the tag file.

- 3. It is easiest if Windows explorer opens .C files automatically with the editor when they are clicked. To do this, change file associations. (See Windows help.)