User's Guide SBOU215–January 2019

# SMALL-AMP-DIP Evaluation Module (EVM)

This user's guide contains support documentation for the SMALL-AMP-DIP evaluation module (EVM). Included is a step-by-step guide on setting up and configuring the EVM, bill of materials (BOM), and printed circuit board (PCB) layout.

|   | Contents                         |    |

|---|----------------------------------|----|

| 1 | Contents                         |    |

| 2 | Hardware Setup                   |    |

| 3 | EVM Description and PCB Layout   |    |

| 4 | Bill of Materials and References | 10 |

|   | List of Figures                  |    |

| 1 | Location of packages on EVM      |    |

| 2 | Detach desired PCB               |    |

| 3 | Detached PCB with soldered IC    |    |

| 4  | Terminal strip (TS-132-G-AA) broken into 4 position length                | 5 |

|----|---------------------------------------------------------------------------|---|

| 5  | Terminal strip (TS-132-G-AA) inserted into spare DIP socket               | 6 |

| 6  | Fully assembled PCB                                                       | 6 |

| 7  | DPW package top layer (left) and bottom layer (right) PCB layout          | 7 |

| 8  | DSG package top layer (left) and bottom layer (right) PCB layout          | 7 |

| 9  | DCN and DDF packages top layer (left) and bottom layer (right) PCB layout | 7 |

| 10 | RUG package top layer (left) and bottom layer (right) PCB layout          | 8 |

| 11 | RUC package top layer (left) and bottom layer (right) PCB layout          | 8 |

| 12 | RGY package top layer (left) and bottom layer (right) PCB layout          | 9 |

| 13 | RTE package top layer (left) and bottom layer (right) PCB layout          | 9 |

|    |                                                                           |   |

## List of Tables

| 1 P | Package type mapped to EVM | ŧ |

|-----|----------------------------|---|

|-----|----------------------------|---|

# Trademarks

All trademarks are the property of their respective owners.

# 1 Introduction

The SMALL-AMP-DIP-EVM is designed to facilitate evaluation of op amps offered in small packages. This EVM gives users an easy tool to test the following op amp packages: DPW, DCN, DDF, DSG, RUG, RUC, RGY, and RTE. This EVM routes each pin of the device to a header pin and can be used as a basic building block for circuit design and device testing purposes.

#### 1.1 List of Packages

The SMALL-AMP-DIP-EVM contains the following packages:

- DPW-5

- DCN-8

- DDF-8

- DSG-8

- RUG-10

- RUC-14

- RGY-14

- RTE-16

# 2 Hardware Setup

The SMALL-AMP-DIP-EVM setup requires identifying and breaking out the desired PCB from the EVM and then soldering the IC and terminal strips onto the EVM. This section presents the details of these procedures.

#### 2.1 EVM Package Locations

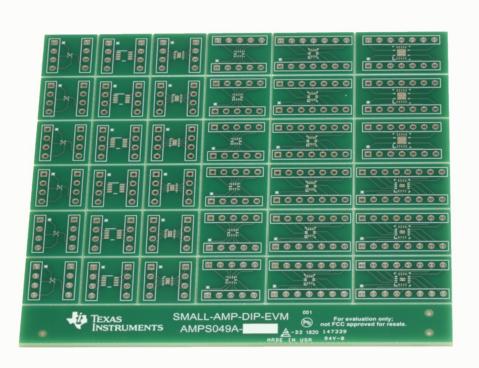

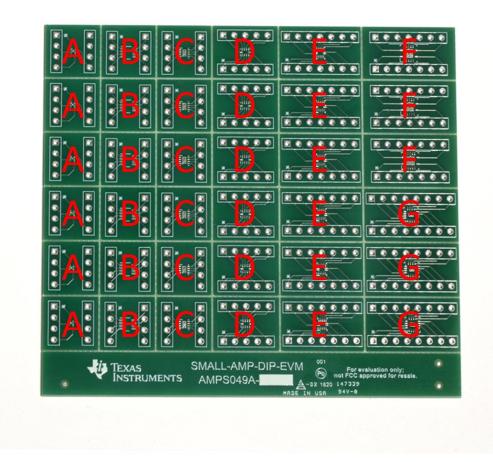

Figure 1 and Table 1 map the location of each package on the EVM. Figure 1 labels each package drawing with a letter ranging from A to G. Table 1 matches the package drawing to a letter in Figure 1.

Figure 1. Location of packages on EVM

| Package Name | Letter in Figure 1 |

|--------------|--------------------|

| DPW-5        | A                  |

| DCN-8        | В                  |

| DDF-8        | В                  |

| DSG-8        | C                  |

| RUG-10       | D                  |

| RUC-14       | E                  |

| RGY-14       | F                  |

| RTE-16       | G                  |

# 2.2 EVM Assembly Instructions

This section provides step-by-step instructions on how to assemble the EVM.

- 1. Choose the desired package. See Section 2.1 for the location of each package type.

- 2. Gently flex the PCB panel at the score lines to separate the desired package from the EVM.

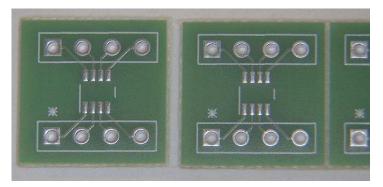

Figure 2. Detach desired PCB

3. Solder the device onto the separated PCB.

Figure 3. Detached PCB with soldered IC

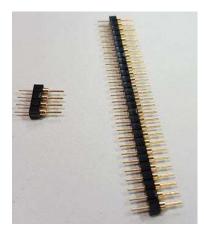

- 4. Use long-nose pliers to snap terminal header strips into the desired position lengths.

- For the DPW, DCN, DDF and DSG packages, the terminal strips need to be snapped into 4 position lengths, as shown in Figure 4.

- For the RUG package, use 5 position lengths.

- For the RUC and RGY packages, use 7 position lengths.

- And for the RTE package, use 8 position lengths.

Figure 4. Terminal strip (TS-132-G-AA) broken into 4 position length

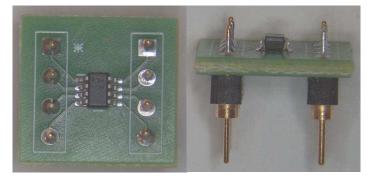

5. Insert the header strips into a spare DIP socket or breadboard as shown in Figure 5.

Figure 5. Terminal strip (TS-132-G-AA) inserted into spare DIP socket

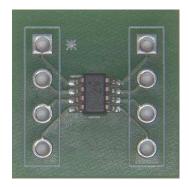

6. Position the separated PCB with the soldered IC over the terminal strips and solder each pin in place. Carefully remove the PCB from the DIP socket. Figure 6 displays a fully assembled PCB.

Figure 6. Fully assembled PCB

# 3 EVM Description and PCB Layout

This section shows the PCB layout of each circuit configuration provided on the EVM.

#### 3.1 DPW Package

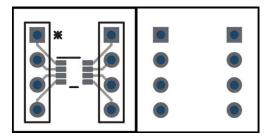

Figure 7 displays the PCB layout of the top (left) and bottom layers (right) for the DPW package.

Figure 7. DPW package top layer (left) and bottom layer (right) PCB layout

The X2SON (DPW) package has the following dimensions: 0.48-mm pitch, 0.37-mm maximum height, 0.8-mm length, and 0.8-mm width.

# 3.2 DSG Package

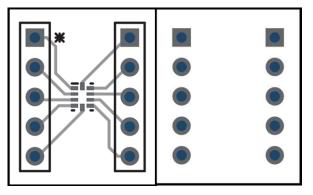

Figure 8 displays the PCB layout of the top (left) and bottom layers (right) for the DSG package.

Figure 8. DSG package top layer (left) and bottom layer (right) PCB layout

The WSON (DSG) package has the following dimensions: 0.5-mm pin pitch, 0.75-mm maximum height, 2.0-mm length, and 2.0-mm width.

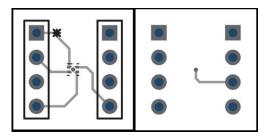

# 3.3 DCN and DDF Packages

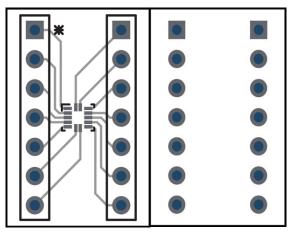

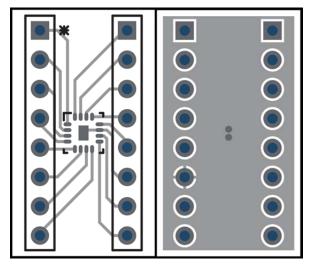

Figure 9 displays the PCB layout of the top (left) and bottom layers (right) for the DCN and DDF packages.

Figure 9. DCN and DDF packages top layer (left) and bottom layer (right) PCB layout

The SOT-23 (DCN and DDF) package has the following dimensions: 0.65-mm pin pitch, 1.1-mm maximum height, 2.9-mm length, and 1.63-mm width.

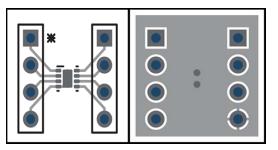

#### 3.4 RUG Package

Figure 10 displays the PCB layout of the top (left) and bottom layers (right) for the RUG package.

Figure 10. RUG package top layer (left) and bottom layer (right) PCB layout

The X2QFN (RUG) package has the following dimensions: 0.5-mm pin pitch, 0.37-mm maximum height, 1.5-mm length, and 2.0-mm width.

## 3.5 RUC Package

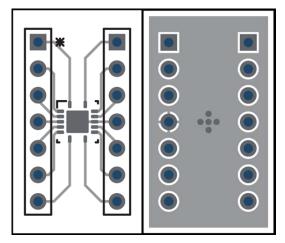

Figure 11 displays the PCB layout of the top (left) and bottom layers (right) for the RUC package.

Figure 11. RUC package top layer (left) and bottom layer (right) PCB layout

The X2QFN (RUC) package has the following dimensions: 0.4-mm pin pitch, 0.35-mm maximum height, 2.0-mm length, and 2.0-mm width

#### 3.6 RGY Package

Figure 12 displays the PCB layout of the top (left) and bottom layers (right) for the RGY package.

Figure 12. RGY package top layer (left) and bottom layer (right) PCB layout

The VQFN (RGY) package has the following dimensions: 0.5-mm pin pitch, 0.9-mm maximum height, 3.5-mm length, and 3.5-mm width.

# 3.7 RTE Package

Figure 13 displays the PCB layout of the top (left) and bottom layers (right) for the RTE package.

Figure 13. RTE package top layer (left) and bottom layer (right) PCB layout

The WQFN (RTE) package has the following dimensions: 0.5-mm pin pitch, 0.75-mm maximum height, 3.0-mm length, and 3.0-mm width.

#### 4 Bill of Materials and References

## 4.1 Bill of Materials

| Designator    | QTY | Description                          | Part Number       |

|---------------|-----|--------------------------------------|-------------------|

| PCB           | 1   | Printed-Circuit-Board                | SMALL-AMP-DIP-EVM |

| Header Strips | 2   | Header, 2.54 mm, 32 × 1,<br>Gold, TH | TS-132-G-AA       |

#### 4.2 References

- (1) DIYAMP-EVM Tool Folder

- (2) DUAL-DIYAMP-EVM Tool Folder

- (3) DIP Adapter EVM Tool Folder

- (4) TI Precision Labs Training

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated