TPS2596

# SLVSET8A -MAY 2019-REVISED AUGUST 2019

# TPS2596 2.7 to 19 V, 0.125 to 2-A, 89-m $\Omega$ eFuse With Accurate Current Monitor and Fast Overvoltage Protection

#### 1 Features

- Wide input voltage range: 2.7-V to 19-V

- 21-V Absolute maximum

- Low On-Resistance: Ron = 89-mΩ (typical)

- Active high enable input with adjustable undervoltage lockout (UVLO)

- · Overvoltage protection options available:

- Fast overvoltage clamp (3.8-V, 5.7-V and 13.8-V pin-selectable thresholds) with a response time of 5-μs (typical)

- Adjustable overvoltage lockout (OVLO) with a response time of 1.3-μs (typical)

- Adjustable current limit with load current monitor output (ILM)

- Current range: 0.125-A to 2-A

- Current limit accuracy:

- ±10.4 % (maximum) across current range

- ±5.5 % (maximum) at 1-A current limit

- Immune to Electrical Fast Transients (IEC 61000-4-4)

- Adjustable output slew rate control (dVdt)

- Overtemperature protection (OTP)

- Fault indication pin (FLT)

- UL 2367 recognition (pending)

- IEC 62368 CB certification (pending)

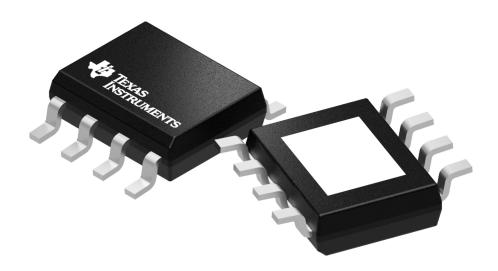

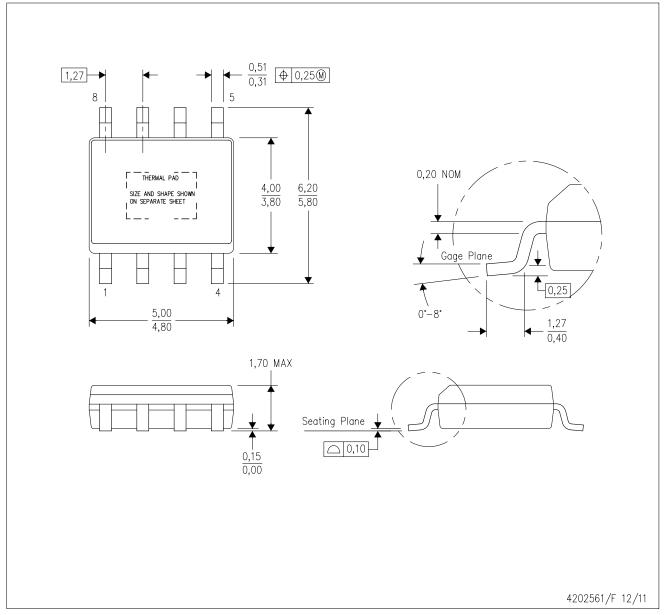

- Small footprint: 4.91 mm x 3.9 mm SOIC package

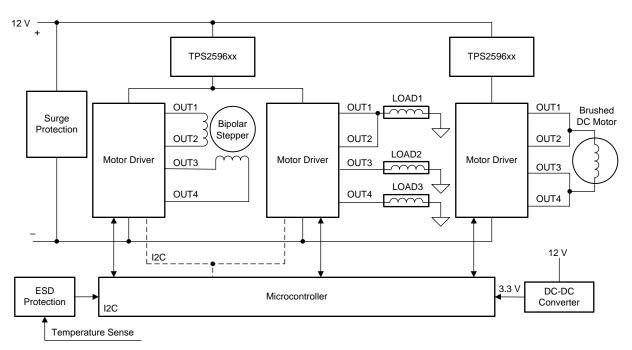

## 2 Applications

- Energy meters

- UL 60335-1 15-W LPC in Appliances

- Refrigerators

- Dishwashers

- Washing machine and dryers

- Set-top boxes

- IP Network cameras

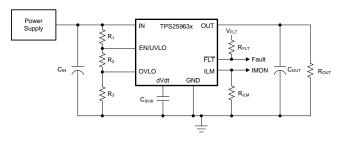

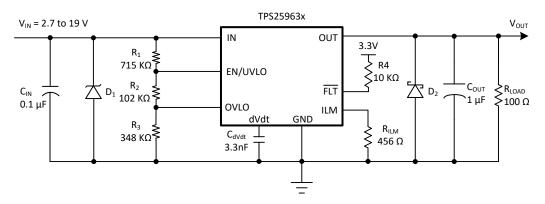

#### Simplified Schematic

#### 3 Description

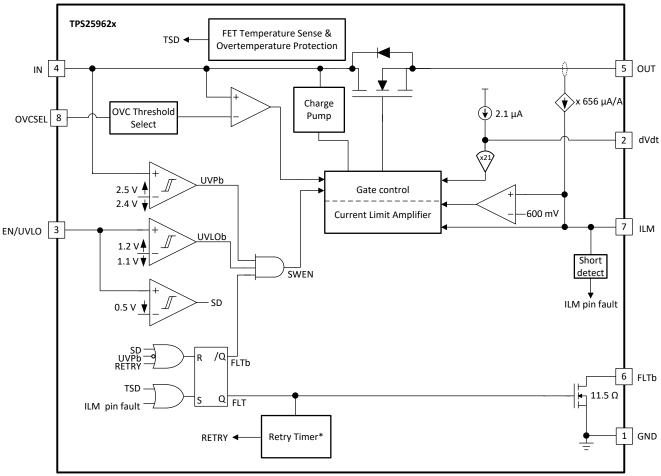

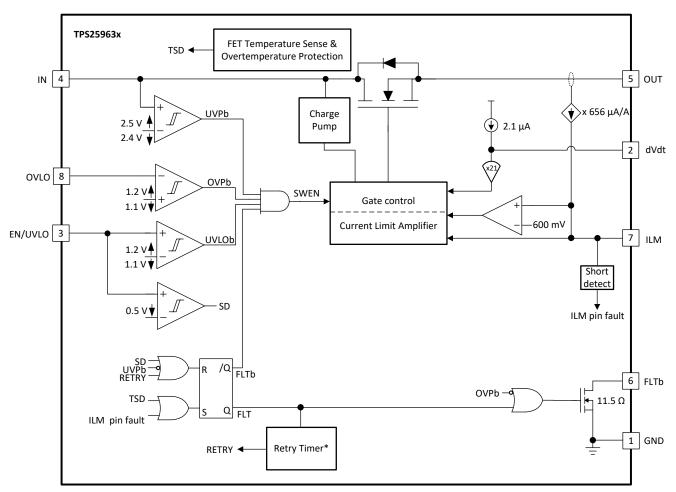

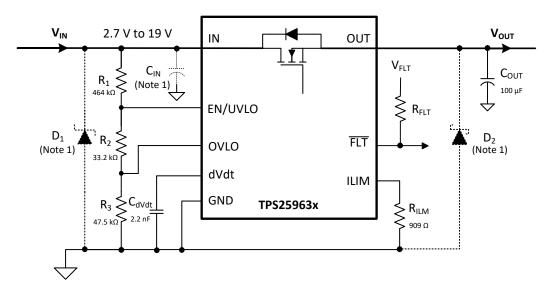

The TPS2596xx family of eFuses (integrated FET hot-swap devices) is a highly integrated circuit protection and power management solution in a small package. The devices provide multiple protection modes using very few external components and are a robust defense against overloads, short circuits, voltage surges, and excessive inrush current. Output current limit level can be set with a single external resistor. It is also possible to get an accurate sense of the output load current by measuring the voltage drop across the current limit resistor. Applications with particular inrush current requirements can set the output slew rate with a single external capacitor. For the TPS25962x variants, in case of an input overvoltage condition, internal clamping circuits limit the output to a safe fixed maximum voltage (pin selectable), with no external components. TPS25963x variants provide an option to set a userdefined overvoltage cutoff threshold.

The devices are characterized for operation over a junction temperature range of -40 °C to +125 °C.

#### Device Information<sup>(1)</sup>

| PART NUMBER  | PACKAGE  | BODY SIZE (NOM)  |

|--------------|----------|------------------|

| TPS259620DDA | SOIC (8) | 4.91 mm x 3.9 mm |

| TPS259621DDA | SOIC (8) | 4.91 mm x 3.9 mm |

| TPS259630DDA | SOIC (8) | 4.91 mm x 3.9 mm |

| TPS259631DDA | SOIC (8) | 4.91 mm x 3.9 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

#### TPS25963x 1KV EFT Response

# **Table of Contents**

| Features 1              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8.4 Device Functional Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Applications 1          | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Application and Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Description 1           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9.1 Application Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9.2 Typical Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9.3 System Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                         | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Power Supply Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| _                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10.1 Transient Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| •                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10.2 Output Short-Circuit Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

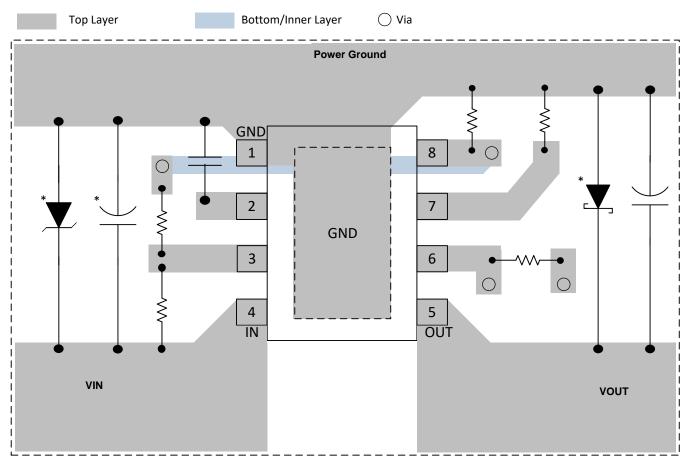

|                         | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 11.1 Layout Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 11.2 Layout Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                         | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Device and Documentation Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12.1 Documentation Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| •                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12.2 Receiving Notification of Documentation Update                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | s 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| •                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12.3 Community Resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ••                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12.4 Trademarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12.5 Electrostatic Discharge Caution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12.6 Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 8.3 Feature Description | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Mechanical, Packaging, and Orderable Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                         | Applications         1           Description         1           Revision History         2           Device Comparison Table         3           Pin Configuration and Functions         4           Specifications         5           7.1 Absolute Maximum Ratings         5           7.2 ESD Ratings         5           7.3 Recommended Operating Conditions         5           7.4 Thermal Information         6           7.5 Electrical Characteristics         6           7.6 Timing Requirements         8           7.7 Switching Characteristics         8           7.8 Typical Characteristics         10           Detailed Description         17           8.1 Overview         17           8.2 Functional Block Diagram         17 | Applications       1       9         Description       1       1         Revision History       2       2         Device Comparison Table       3       3         Pin Configuration and Functions       4       10         Specifications       5       5         7.1 Absolute Maximum Ratings       5       11         7.2 ESD Ratings       5       11         7.3 Recommended Operating Conditions       5       1         7.4 Thermal Information       6       6         7.5 Electrical Characteristics       6       12         7.6 Timing Requirements       8       8         7.7 Switching Characteristics       8       8         7.8 Typical Characteristics       10       10         Detailed Description       17       17         8.1 Overview       17       17         8.2 Functional Block Diagram       17 | Applications19Application and ImplementationDescription19.1 Application InformationRevision History29.2 Typical ApplicationDevice Comparison Table39.3 System ExamplesPin Configuration and Functions49.3 System ExamplesSpecifications510 Power Supply Recommendations7.1 Absolute Maximum Ratings510.1 Transient Protection7.2 ESD Ratings510.2 Output Short-Circuit Measurements7.3 Recommended Operating Conditions511.1 Layout7.4 Thermal Information611.2 Layout Example7.5 Electrical Characteristics612 Device and Documentation Support7.6 Timing Requirements812.1 Documentation Support7.7 Switching Characteristics812.2 Receiving Notification of Documentation Update7.8 Typical Characteristics1012.3 Community ResourcesDetailed Description1712.4 Trademarks8.1 Overview1712.5 Electrostatic Discharge Caution8.2 Functional Block Diagram1712.6 Glossary8.3 Feature Description1818 |

# 4 Revision History

| Cl | hanges from Original (May 2019) to Revision A      | Page | •     |

|----|----------------------------------------------------|------|-------|

| •  | Change from Advance Information to Production Data | 1    | -<br> |

# 5 Device Comparison Table

| Part Number | Overvoltage Response                        | Response to Thermal Shutdown (TSD) |

|-------------|---------------------------------------------|------------------------------------|

| TPS259620   | OVC - 3.8 V, 5.7 V, 13.8 V (Pin Selectable) | Latch-off                          |

| TPS259621   | OVC - 3.8 V, 5.7 V, 13.8 V (Pin Selectable) | Auto-retry                         |

| TPS259630   | Adjustable OVLO                             | Latch-off                          |

| TPS259631   | Adjustable OVLO                             | Auto-retry                         |

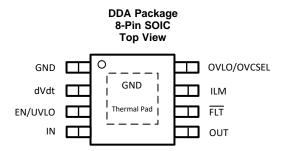

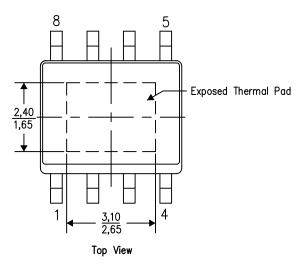

# 6 Pin Configuration and Functions

#### **Pin Functions**

| PI          | IN  | 1/0              | DESCRIPTION                                                                                                                                                                                                             |  |  |

|-------------|-----|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME        | NO. | I/O              | DESCRIPTION                                                                                                                                                                                                             |  |  |

| GND         | 1   | Ground           | Ground                                                                                                                                                                                                                  |  |  |

| dVdt        | 2   | Analog<br>Output | A capacitor from this pin to GND sets the output turn on slew rate. Leave this pin floating for the fastest turn on slew rate.                                                                                          |  |  |

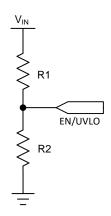

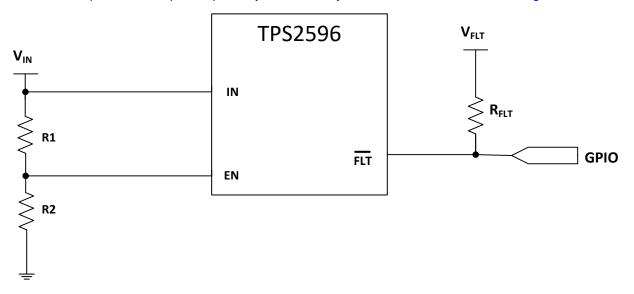

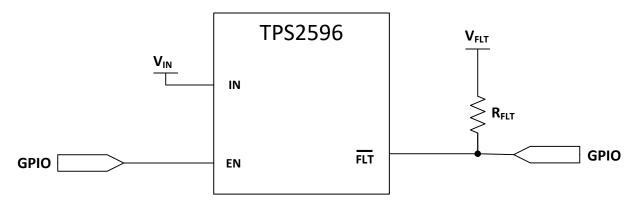

| EN/UVLO     | 3   | Analog Input     | Active High Enable for the Device. A resistor divider can be used to adjust the Undervoltage Lockout threshold. <b>Do not leave floating.</b>                                                                           |  |  |

| IN          | 4   | Power            | Power Input                                                                                                                                                                                                             |  |  |

| OUT         | 5   | Power            | Power Output                                                                                                                                                                                                            |  |  |

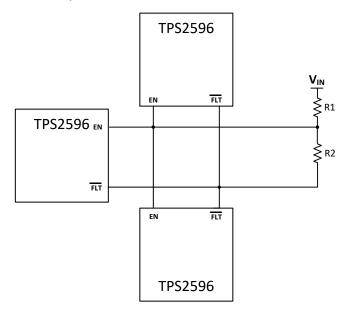

| FLT         | 6   | Digital Output   | Active Low indicator which will be pulled low when a fault is detected. It is an open-drain output that requires an external pull-up resistance.                                                                        |  |  |

| ILM         | 7   | Analog<br>Output | This is a dual function pin used to limit and monitor the output current. An external resistor from this pin to GND sets the output current limit. The pin voltage can also be used to monitor the output load current. |  |  |

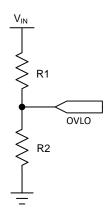

| OVLO        |     | Analan lanut     | TPS25963x: A resistor divider can be used to adjust the Overvoltage Lockout threshold. Do not leave floating.                                                                                                           |  |  |

| OVCSEL      | 8   | Analog Input     | <b>TPS25962x:</b> Overvoltage Clamp level select pin. Refer to <i>Overvoltage Clamp</i> for more details.                                                                                                               |  |  |

| Thermal pad |     | Ground           | The Exposed Pad is used primarily for heat dissipation and must be connected to system ground plane for best thermal performance.                                                                                       |  |  |

#### 7 Specifications

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                      | PARAMETER                                            | PIN         | MIN MAX                              | UNITS |

|----------------------|------------------------------------------------------|-------------|--------------------------------------|-------|

| .,                   | Maximum Input Voltage Range                          | IN          | -0.3 21                              | V     |

| V <sub>IN</sub>      | Maximum Input Voltage Range (T <sub>A</sub> = 25 °C) | IIN         | 22                                   | V     |

| V <sub>OUT</sub>     | Maximum Output Voltage Range                         | OUT         | −0.3 min (21, V <sub>IN</sub> + 0.3) | V     |

| V <sub>EN/UVLO</sub> | Maximum Enable Pin Voltage Range                     | EN/UVLO     | -0.3 7                               | V     |

| V <sub>OV</sub>      | Maximum OVCSEL/OVLO Pin Voltage Range                | OVCSEL/OVLO | -0.3 7                               | V     |

| $V_{dVdT}$           | Maximum dVdT Pin Voltage Range                       | DVDT        | 2.5                                  | V     |

| $V_{FLTB}$           | Maximum FLTb Pin Voltage Range                       | FLT         | -0.3 7                               | V     |

| I <sub>FLTB</sub>    | Maximum FLTb Pin Sink Current                        | FLT         | 10                                   | mA    |

| I <sub>MAX</sub>     | Maximum Continuous Switch Current                    | IN to OUT   | Internally Limited                   | Α     |

| $T_J$                | Junction temperature                                 |             | Internally Limited                   | °C    |

| T <sub>LEAD</sub>    | Maximum Lead Temperature                             |             | 300                                  | °C    |

| T <sub>stg</sub>     | Storage temperature                                  |             | <b>-65</b> 150                       | °C    |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 7.2 ESD Ratings

|                                            |                                                                                         |                                                                             | VALUE | UNIT |

|--------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------|------|

| M                                          | Floatroatatia diaaharaa                                                                 | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup> | ±2000 | V    |

| V <sub>(ESD)</sub> Electrostatic discharge | Charged device model (CDM), per JEDEC specificationJESD22-C101, all pins <sup>(2)</sup> | ±500                                                                        | V     |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                      | PARAMETER                               | PIN       | MIN | MAX               | UNITS |

|----------------------|-----------------------------------------|-----------|-----|-------------------|-------|

| $V_{IN}$             | Input Voltage Range                     | IN        | 2.7 | 19 <sup>(1)</sup> | V     |

| V <sub>OUT</sub>     | Output Voltage Range                    | OUT       |     | $V_{IN} + 0.3$    | V     |

| V <sub>EN/UVLO</sub> | Enable Pin Voltage Range                | EN/UVLO   |     | 6 <sup>(2)</sup>  | V     |

| V <sub>OV</sub>      | OVLO Pin Voltage Range (TPS25963x Only) | OVLO      | 0.5 | 2                 | V     |

| $V_{dVdT}$           | dVdT Pin Capacitor Voltage Rating       | DVDT      | 4   |                   | V     |

| $V_{FLTB}$           | FLTB Pin Voltage Range                  | FLT       |     | 6                 | V     |

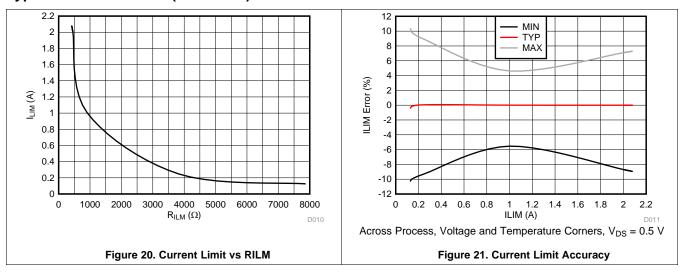

| R <sub>ILM</sub>     | ILM Pin Resistance                      | ILM       | 453 | 7869              | Ω     |

| I <sub>MAX</sub>     | Continuous Switch Current               | IN to OUT |     | 2                 | Α     |

| TJ                   | Junction temperature                    |           | -40 | 125               | °C    |

For TPS25962x, the input voltage should be limited to the selected Output Voltage Clamp Option as listed in the Electrical Characteristics section

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> For supply voltages below 6V, it is okay to pull up the EN pin to IN through a resistor of 100 KΩ or higher. For supply voltages greater than 6V, it is recommended to use an appropriate resistor divider between IN, EN and GND to ensure the voltage at the EN pin is within the specified limits.

#### 7.4 Thermal Information

|                 |                                              | TPS2596X             |      |

|-----------------|----------------------------------------------|----------------------|------|

|                 | THERMAL METRIC <sup>(1)</sup>                | DDA (SOIC-EP)        | UNIT |

|                 |                                              | 8 PINS               |      |

| $R_{\theta JA}$ | Junction-to-ambient thermal resistance       | 52.7 <sup>(2)</sup>  | °C/W |

| $R_{\theta JA}$ | Junction-to-ambient thermal resistance       | 119.8 <sup>(3)</sup> | °C/W |

| $\Psi_{JT}$     | Junction-to-top characterization parameter   | 8.9 <sup>(2)</sup>   | °C/W |

| $\Psi_{JT}$     | Junction-to-top characterization parameter   | 17.5 <sup>(3)</sup>  | °C/W |

| $\Psi_{JB}$     | Junction-to-board characterization parameter | 27.1 <sup>(2)</sup>  | °C/W |

| $\Psi_{JB}$     | Junction-to-board characterization parameter | 68.1 <sup>(3)</sup>  | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 7.5 Electrical Characteristics

(Test conditions unless otherwise noted)  $-40^{\circ}\text{C} \le \text{T}_\text{J} \le 125^{\circ}\text{C}$ ,  $\text{V}_\text{IN} = 12 \text{ V}$ ,  $\text{R}_\text{ILM} = 453 \ \Omega$ ,  $\text{C}_\text{dVdT} = \text{Open}$ , OUT = Open. All voltages referenced to GND.

|                     | PARAMETER                                                                                | TEST CONDITIONS                                                               | MIN    | TYP    | MAX    | UNITS |

|---------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------|--------|--------|-------|

| INPUT SUF           | PPLY (IN)                                                                                |                                                                               |        |        | •      |       |

| •                   | IN and a second second                                                                   | TPS25963x                                                                     |        | 193    | 259    | μA    |

| Q                   | IN quiescent current                                                                     | TPS25962x                                                                     |        | 206    | 266    | μA    |

|                     | IN Shutdown Current                                                                      | V <sub>IN</sub> < 4 V, V <sub>EN/UVLO</sub> < V <sub>SD</sub>                 |        |        | 0.1    | μΑ    |

| SD                  | IN Shutdown Current                                                                      | V <sub>IN</sub> ≥ 4 V, V <sub>EN/UVLO</sub> < V <sub>SD</sub>                 |        | 0.4    | 1.132  | μΑ    |

| / <sub>UVP(R)</sub> | IN Undervoltage Protection                                                               | V <sub>IN</sub> Rising                                                        | 2.46   | 2.53   | 2.58   | V     |

| / <sub>UVP(F)</sub> | threshold                                                                                | V <sub>IN</sub> Falling                                                       | 2.36   | 2.42   | 2.46   | V     |

|                     | IN Undervoltage Protection<br>Hysteresis                                                 |                                                                               |        | 110    |        | mV    |

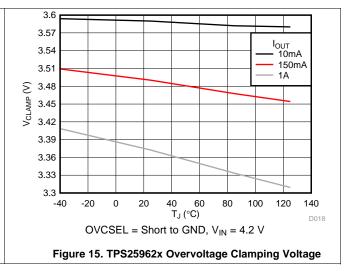

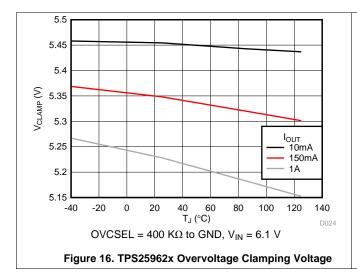

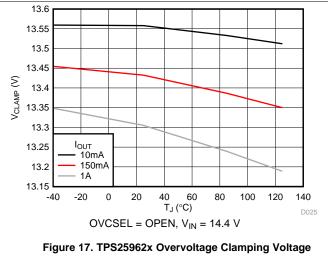

| OUTPUT V            | OLTAGE CLAMP (OUT) - TPS259                                                              | 962X                                                                          |        |        |        |       |

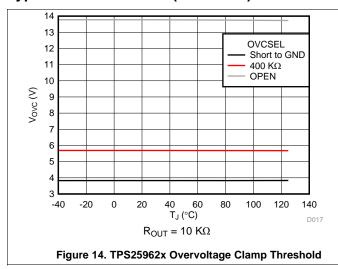

|                     |                                                                                          | $R_{OVCSEL}$ = Short to GND,<br>$R_{OUT}$ = 10 K $\Omega$                     | 3.75   | 3.83   | 3.92   | V     |

| / <sub>ovc</sub>    | Overvoltage Clamp<br>Threshold                                                           | $R_{OVCSEL}$ = 400 K $\Omega$ to GND,<br>$R_{OUT}$ = 10 K $\Omega$            | 5.54   | 5.69   | 5.83   | V     |

|                     |                                                                                          | $R_{OVCSEL} = OPEN, R_{OUT} = 10$<br>$K\Omega$                                | 12.97  | 13.77  | 14.52  | V     |

|                     |                                                                                          | R <sub>OVCSEL</sub> = Short to GND,<br>I <sub>OUT</sub> = 10 mA               | 3.47   | 3.59   | 3.7    | V     |

| V <sub>CLAMP</sub>  | Output Voltage During Clamping                                                           | $R_{OVCSEL}$ = 400 K $\Omega$ to GND, $I_{OUT}$ = 10 mA                       | 5.28   | 5.45   | 5.61   | V     |

|                     |                                                                                          | R <sub>OVCSEL</sub> = OPEN, I <sub>OUT</sub> = 10 mA                          | 13.13  | 13.58  | 13.97  | V     |

| OUTPUT C            | URRENT LIMIT AND MONITOR (                                                               | ILM)                                                                          |        |        | ,      |       |

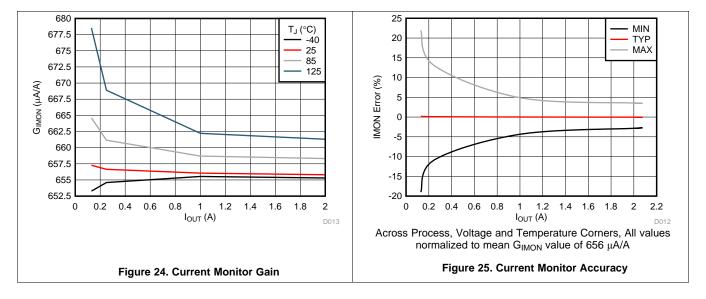

| _                   | Current monitor gain                                                                     | I <sub>OUT</sub> = 0.13 A                                                     | 531.22 | 653.21 | 800.00 | μA/A  |

| 3 <sub>IMON</sub>   | as measured on ILM pin ( $I_{\rm ILM}$ / $I_{\rm OUT}$ )                                 | I <sub>OUT</sub> = 2 A                                                        | 635.77 | 657.15 | 684.05 | μA/A  |

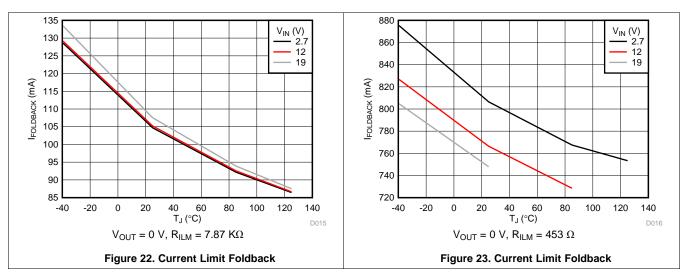

|                     |                                                                                          | $R_{ILM} = 7.87 \text{ K}\Omega, V_{DS} = 0.5$<br>V, -40°C \le T_A \le 80°C   | 0.113  | 0.125  | 0.139  | Α     |

|                     |                                                                                          | $R_{ILM} = 3.83 \text{ K}\Omega, V_{DS} = 0.5 \text{ V}$                      | 0.224  | 0.247  | 0.269  | Α     |

| LIM                 | I <sub>OUT</sub> Current Limit                                                           | $R_{ILM} = 909 \Omega, V_{DS} = 0.5 V$                                        | 0.949  | 1.005  | 1.051  | Α     |

|                     |                                                                                          | R <sub>ILM</sub> = 453 Ω, V <sub>DS</sub> = 0.5 V                             | 1.83   | 2.004  | 2.147  | Α     |

|                     |                                                                                          | R <sub>ILM</sub> = OPEN                                                       |        | 0      |        | Α     |

| СВ                  | I <sub>OUT</sub> Circuit Breaker<br>Threshold<br>during R <sub>ILM</sub> Short condition | R <sub>ILM</sub> = Short to GND (Single<br>Point Failure Test IEC<br>62368-1) |        |        | 1.5    | А     |

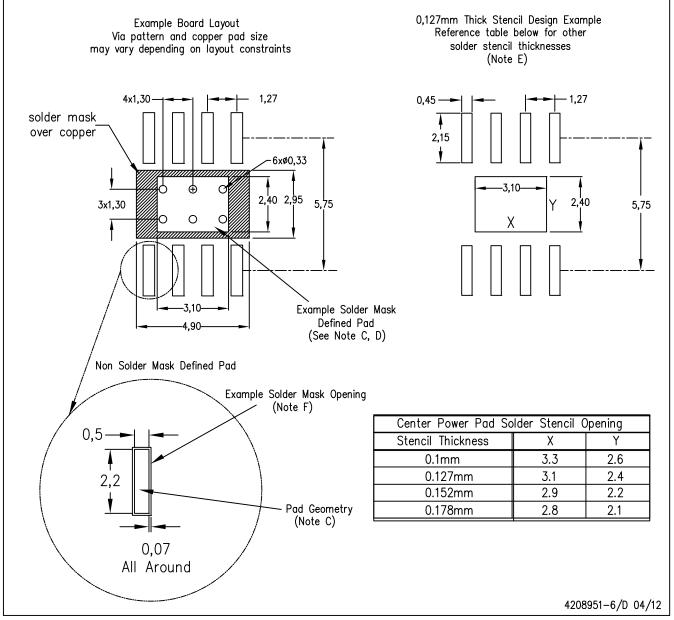

<sup>(2)</sup> With exposed pad soldered to PCB

<sup>(3)</sup> Without exposed pad soldered to PCB

# **Electrical Characteristics (continued)**

(Test conditions unless otherwise noted)  $-40^{\circ}\text{C} \le \text{T}_\text{J} \le 125^{\circ}\text{C}, \text{ V}_\text{IN} = 12 \text{ V}, \text{ R}_\text{ILM} = 453 \Omega, \text{ C}_\text{dVdT} = \text{Open, OUT} = \text{Open. All voltages referenced to GND.}$

|                      | PARAMETER                                             | TEST CONDITIONS                                                                 | MIN   | TYP   | MAX   | UNITS     |

|----------------------|-------------------------------------------------------|---------------------------------------------------------------------------------|-------|-------|-------|-----------|

| ON-RESIST            | ANCE (IN TO OUT)                                      |                                                                                 |       |       |       |           |

|                      |                                                       | V <sub>IN</sub> < 4 V, I <sub>OUT</sub> = 0.2 A, T <sub>J</sub> = 25 °C         |       | 97    | 99.8  | mΩ        |

|                      |                                                       | V <sub>IN</sub> < 4 V, I <sub>OUT</sub> = 0.2 A, T <sub>J</sub> = -40 to 85 °C  |       |       | 125.4 | mΩ        |

| D                    | ON State Resistance                                   | V <sub>IN</sub> < 4 V, I <sub>OUT</sub> = 0.2 A, T <sub>J</sub> = -40 to 125 °C |       |       | 143.4 | mΩ        |

| R <sub>ON</sub>      | ON State Resistance                                   | V <sub>IN</sub> > 4 V, I <sub>OUT</sub> = 0.2 A, T <sub>J</sub> = 25 °C         |       | 89    | 92.6  | mΩ        |

|                      |                                                       | V <sub>IN</sub> > 4 V, I <sub>OUT</sub> = 0.2 A, T <sub>J</sub> = -40 to 85 °C  |       |       | 115.3 | mΩ        |

|                      |                                                       | V <sub>IN</sub> > 4 V, I <sub>OUT</sub> = 0.2 A, T <sub>J</sub> = -40 to 125 °C |       |       | 131   | $m\Omega$ |

| ENABLE/UN            | NDERVOLTAGE LOCK OUT (EI                              | N/UVLO)                                                                         |       |       |       |           |

| V <sub>UVLO(R)</sub> | LIVII O Threat and                                    | V <sub>EN</sub> Rising                                                          | 1.18  | 1.2   | 1.22  | V         |

| V <sub>UVLO(F)</sub> | UVLO Threshold                                        | V <sub>EN</sub> Falling                                                         | 1.08  | 1.1   | 1.13  | V         |

|                      | UVLO Hysteresis                                       |                                                                                 |       | 95    |       | mV        |

| V <sub>SD</sub>      | V <sub>EN</sub> threshold for lowest shutdown current | V <sub>EN</sub> Falling                                                         | 0.53  |       | 1.05  | V         |

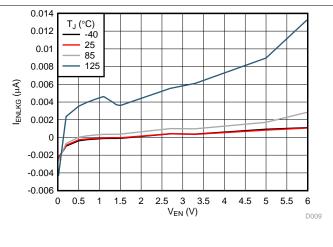

| I <sub>ENLKG</sub>   | EN leakage current                                    |                                                                                 | -0.1  |       | 0.1   | μA        |

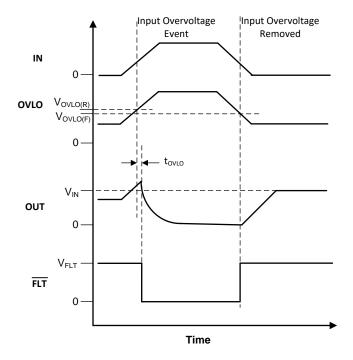

| OVERVOLT             | AGE LOCKOUT (OVLO) - TPS                              | 25963X                                                                          |       |       |       |           |

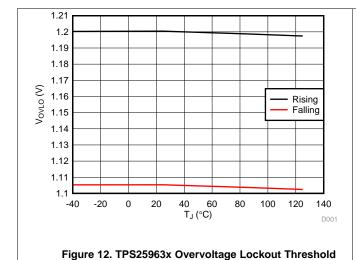

| V <sub>OVLO(R)</sub> | OVII O Three-sheets                                   | V <sub>OVLO</sub> Rising                                                        | 1.17  | 1.2   | 1.22  | V         |

| V <sub>OVLO(F)</sub> | OVLO Threshold                                        | V <sub>OVLO</sub> Falling                                                       | 1.08  | 1.1   | 1.13  | V         |

| , ,                  | OVLO Hysteresis                                       |                                                                                 |       | 95    |       | mV        |

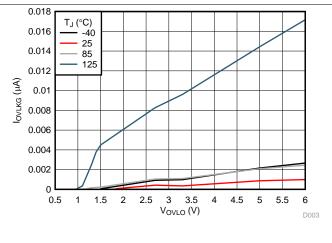

| I <sub>OVLKG</sub>   | OVLO pin leakage current                              | 0.5 ≤ V <sub>OVLO</sub> ≤1.5V                                                   | -0.1  |       | 0.1   | uA        |

| FAULT IND            | ICATION (FLT)                                         | ,                                                                               |       |       |       |           |

| R <sub>FLTB</sub>    | FLT Internal Pull-down resistance                     | FLT asserted                                                                    |       | 11.52 |       | Ω         |

| I <sub>FLTLKG</sub>  | FLT pin leakage current                               | FLT de-asserted, pull-up voltage 6 V                                            | -1    |       | 1     | μΑ        |

| OVERTEME             | PERATURE PROTECTION (OTP                              | 2)                                                                              |       |       | •     |           |

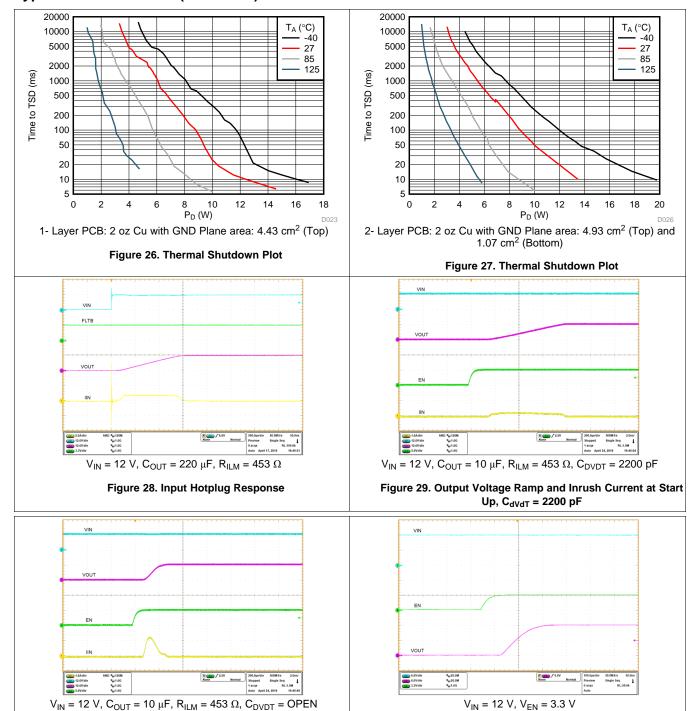

| TSD                  | Thermal Shutdown Rising Threshold                     | T <sub>J</sub> Rising                                                           |       | 157   |       | °C        |

| TSD <sub>HYS</sub>   | Thermal Shutdown<br>Hysteresis                        | T <sub>J</sub> Falling                                                          |       | 11.5  |       | °C        |

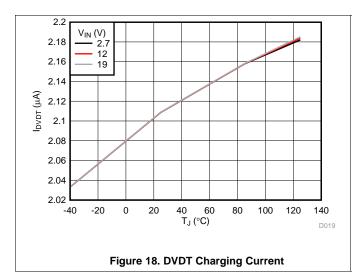

| DVDT                 |                                                       |                                                                                 |       |       |       |           |

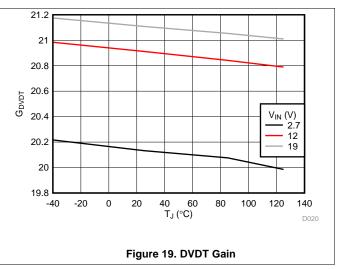

| I <sub>DVDT</sub>    | dVdt Pin Charging Current                             |                                                                                 | 1.89  | 2.11  | 2.33  | μΑ        |

| G <sub>DVDT</sub>    | DVDT gain                                             |                                                                                 | 20.31 | 20.93 | 21.5  | V         |

#### 7.6 Timing Requirements

Typical Values are taken at  $T_J = 25$ °C unless specifically noted otherwise.

|                      | PARAMETER                                   | TEST CONDITIONS                                                                     | MIN | TYP | MAX | UNITS |

|----------------------|---------------------------------------------|-------------------------------------------------------------------------------------|-----|-----|-----|-------|

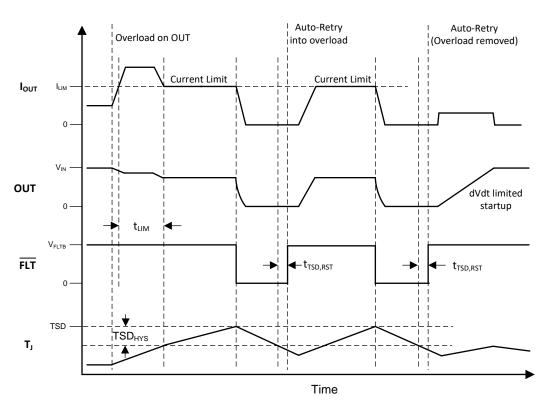

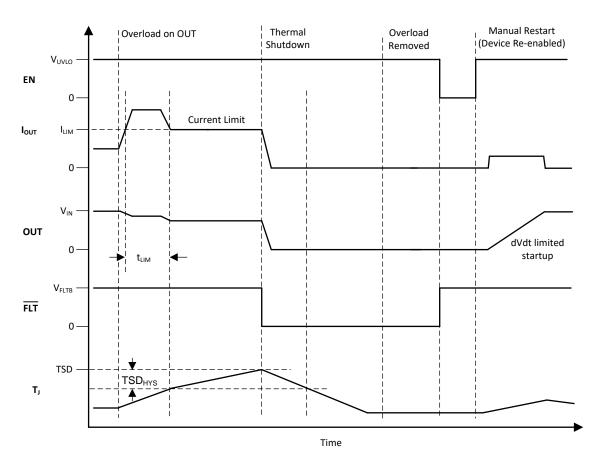

| t <sub>LIM</sub>     | Current limit response time                 | I <sub>OUT</sub> > 20% over I <sub>LIM</sub> to I <sub>OUT</sub> ≤ I <sub>LIM</sub> |     | 87  |     | μs    |

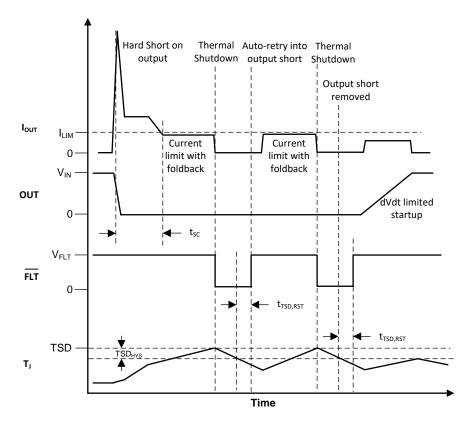

| t <sub>SC</sub>      | Short circuit response time                 | V <sub>OUT</sub> ↓ to I <sub>OUT</sub> ≤ I <sub>LIM</sub>                           |     | 5   |     | μs    |

| t <sub>OVLO</sub>    | Overvoltage lockout response time           | TPS25963x Only                                                                      |     | 1.3 |     | μs    |

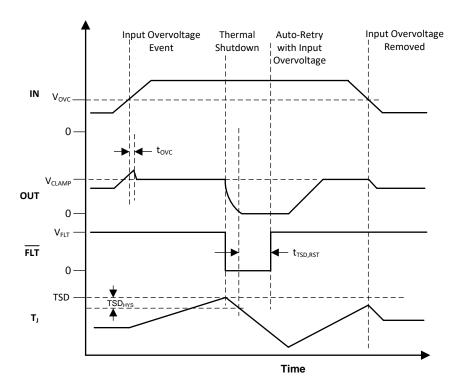

| tovc                 | Output clamp response time                  | TPS25962x Only , I <sub>OUT</sub> = 2 A                                             |     | 5   |     | μs    |

| t <sub>TSD,RST</sub> | Thermal Shutdown Auto-<br>Retry<br>Interval | TPS2596x1 Only                                                                      |     | 95  |     | ms    |

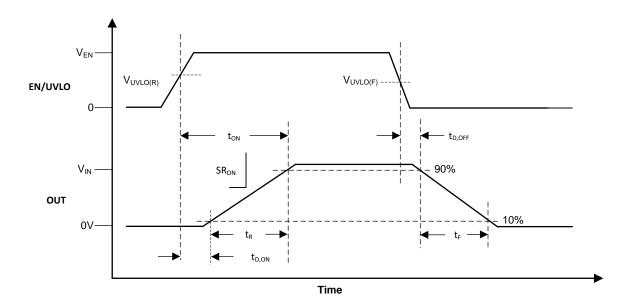

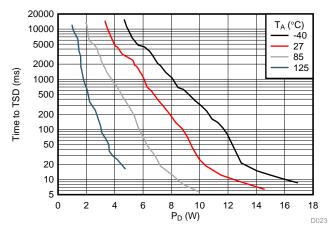

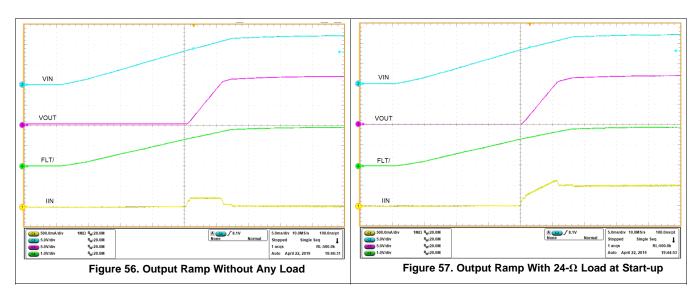

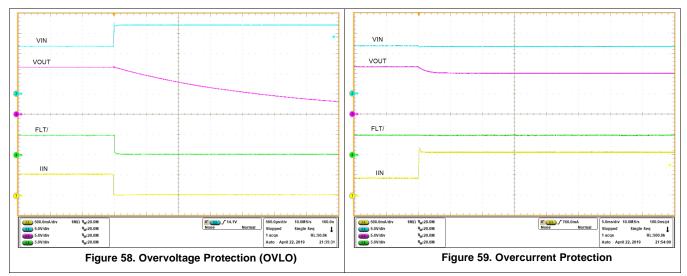

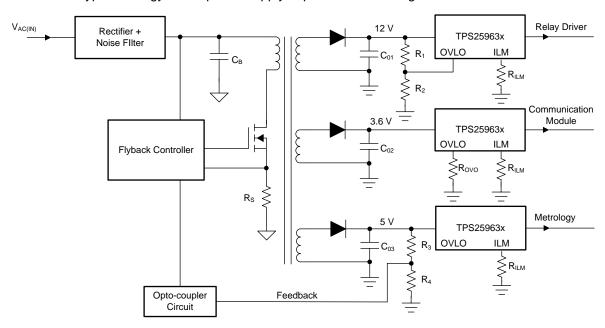

#### 7.7 Switching Characteristics