Silicon Errata SPRZ295Q-April 2009-Revised January 2019

# TMS320F2803x Piccolo™ MCUs Silicon Revisions A, 0

#### 1 Introduction

This document describes the silicon updates to the functional specifications for the TMS320F2803x microcontrollers (MCUs).

The updates are applicable to:

- 56-pin Plastic Quad Flatpack, RSH Suffix

- 64-pin Thin Quad Flatpack, PAG Suffix

- 80-pin Low-Profile Quad Flatpack, PN Suffix

#### 2 Device and Development Support Tool Nomenclature

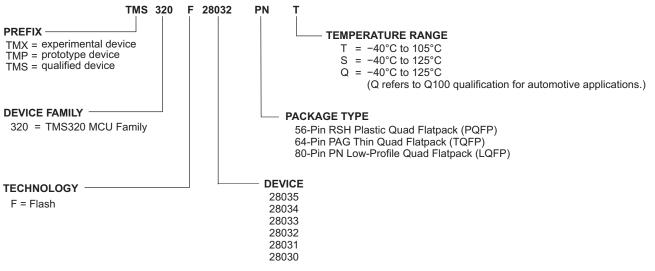

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of all [TMS320] DSP devices and support tools. Each TMS320<sup>™</sup> DSP commercial family member has one of three prefixes: TMX, TMP, or TMS (for example, **TMS**320F28035). Texas Instruments recommends two of three possible prefix designators for its support tools: TMDX and TMDS. These prefixes represent evolutionary stages of product development from engineering prototypes (TMX/TMDX) through fully qualified production devices/tools (TMS/TMDS).

- **TMX** Experimental device that is not necessarily representative of the final device's electrical specifications

- **TMP** Final silicon die that conforms to the device's electrical specifications but has not completed quality and reliability verification

- **TMS** Fully qualified production device

Support tool development evolutionary flow:

- **TMDX** Development-support product that has not yet completed Texas Instruments internal qualification testing

- TMDS Fully qualified development-support product

TMX and TMP devices and TMDX development-support tools are shipped against the following disclaimer:

"Developmental product is intended for internal evaluation purposes."

TMS devices and TMDS development-support tools have been characterized fully, and the quality and reliability of the device have been demonstrated fully. TI's standard warranty applies.

Predictions show that prototype devices (TMX or TMP) have a greater failure rate than the standard production devices. Texas Instruments recommends that these devices not be used in any production system because their expected end-use failure rate still is undefined. Only qualified production devices are to be used.

TI device nomenclature also includes a suffix with the device family name. This suffix indicates the package type (for example, PN) and temperature range (for example, T).

#### 3 Device Markings

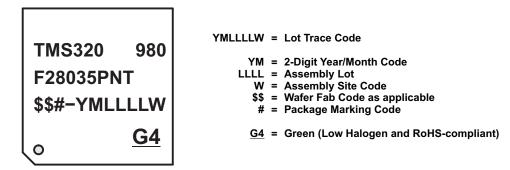

Figure 1 provides an example of the 2803x device markings and defines each of the markings. The device revision can be determined by the symbols marked on the top of the package as shown in Figure 1. Some prototype devices may have markings different from those illustrated. Figure 2 shows the device nomenclature.

Figure 1. Example of Device Markings

| Table 1. Determining | Silicon Revisior | n From Lot Trace Code |

|----------------------|------------------|-----------------------|

|----------------------|------------------|-----------------------|

| PACKAGE MARKING CODE | SILICON REVISION     | REVISION ID<br>Address: 0x0883 | COMMENTS                                           |

|----------------------|----------------------|--------------------------------|----------------------------------------------------|

| Blank                | Indicates Revision 0 | 0x0000                         | This silicon revision is available as TMX and TMS. |

| A                    | Indicates Revision A | 0x0001                         | This silicon revision is available as TMS.         |

#### 4 Usage Notes and Known Design Exceptions to Functional Specifications

#### 4.1 Usage Notes

Usage notes highlight and describe particular situations where the device's behavior may not match presumed or documented behavior. This may include behaviors that affect device performance or functional correctness. These usage notes will be incorporated into future documentation updates for the device (such as the device-specific data sheet), and the behaviors they describe will not be altered in future silicon revisions.

Table 2 shows which silicon revision(s) are affected by each usage note.

#### Table 2. List of Usage Notes

| TITLE                                                                                                                                                                                             |     | SILICON REVISION(S)<br>AFFECTED |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------|--|

|                                                                                                                                                                                                   |     | Α                               |  |

| PIE: Spurious Nested Interrupt After Back-to-Back PIEACK Write and Manual CPU Interrupt Mask Clear                                                                                                | Yes | Yes                             |  |

| CAN Bootloader: Internal Oscillator Tolerance is Not Sufficient for CAN Operation at High Temperatures                                                                                            | Yes | Yes                             |  |

| Flash: MAX "Program Time" and "Erase Time" in Revision L of the <i>TMS320F2803x Piccolo™</i><br><i>Microcontrollers Data Manual</i> are only Applicable for Devices Manufactured After April 2017 | Yes | Yes                             |  |

#### 4.1.1 PIE: Spurious Nested Interrupt After Back-to-Back PIEACK Write and Manual CPU Interrupt Mask Clear Usage Note

#### Revision(s) Affected: 0, A

Certain code sequences used for nested interrupts allow the CPU and PIE to enter an inconsistent state that can trigger an unwanted interrupt. The conditions required to enter this state are:

- 1. A PIEACK clear is followed immediately by a global interrupt enable (EINT or asm(" CLRC INTM")).

- 2. A nested interrupt clears one or more PIEIER bits for its group.

Whether the unwanted interrupt is triggered depends on the configuration and timing of the other interrupts in the system. This is expected to be a rare or nonexistent event in most applications. If it happens, the unwanted interrupt will be the first one in the nested interrupt's PIE group, and will be triggered after the nested interrupt re-enables CPU interrupts (EINT or asm(" CLRC INTM")).

**Workaround:** Add a NOP between the PIEACK write and the CPU interrupt enable. Example code is shown below.

| <pre>//Bad interrupt nesting code PieCtrlRegs.PIEACK.all = 0xFFFF; EINT;</pre>               | //Enable nesting in the PIE<br>//Enable nesting in the CPU                                           |

|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| <pre>//Good interrupt nesting code PieCtrlRegs.PIEACK.all = 0xFFFF; asm(" NOP"); EINT;</pre> | //Enable nesting in the PIE<br>//Wait for PIEACK to exit the pipeline<br>//Enable nesting in the CPU |

#### 4.1.2 CAN Bootloader: Internal Oscillator Tolerance is Not Sufficient for CAN Operation at High Temperatures

#### Revision(s) Affected: 0, A

The CAN bootloader in the device's boot ROM uses the internal oscillator as the source for the CAN bit clock. At high temperatures, the frequency of the internal oscillator can deviate enough to prevent messages from being received.

**Workaround:** Recalibrate the internal oscillator before invoking the CAN bootloader. This can be done in application code. For more flexibility, a wrapper function may be programmed into the device's OTP memory. See the Using the Piccolo<sup>TM</sup> CAN Bootloader at High Temperature Application Report for details on how to implement this workaround.

#### 4.1.3 Flash: MAX "Program Time" and "Erase Time" in Revision L of the *TMS320F2803x Piccolo*™ *Microcontrollers Data Manual* are only Applicable for Devices Manufactured After April 2017

#### Revision(s) Affected: 0, A

The MAX parameters added for the flash "Program Time" and "Erase time" in revision L of the *TMS320F2803x Piccolo<sup>TM</sup> Microcontrollers Data Manual* are only applicable for devices manufactured after April 2017.

#### Known Design Exceptions to Functional Specifications 4.2

#### Table 3. Table of Contents for Advisories

| ītle                                                                                                                                                          | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Advisory — ADC: Temperature Sensor Minimum Sample Window Requirement                                                                                          | . 7  |

| Advisory — ADC: DC Specifications: Linearity Limitation                                                                                                       | . 7  |

| Advisory — ADC: Offset Self-Recalibration Requirement                                                                                                         | . 7  |

| Advisory — ADC: ADC Result Conversion When Sampling Ends on 14th Cycle of Previous Conversion, ACQPS = 6                                                      |      |

| or 7                                                                                                                                                          |      |

| Advisory — ADC: Initial Conversion                                                                                                                            | . 8  |

| Advisory — ADC: ADC can Become Non-Responsive When ADCNONOVERLAP or RESET is Written During a Conversion                                                      | 0    |

| Advisory — ADC: New ADC Control Bits Added to Revision A Silicon                                                                                              |      |

| Advisory — ADC: Out-of-Specification Current Consumption on Power Up                                                                                          |      |

|                                                                                                                                                               |      |

| Advisory — Memory: Prefetching Beyond Valid Memory                                                                                                            |      |

| Advisory — GPIO: GPIO Qualification                                                                                                                           |      |

| Advisory —Code Security Module: Memory Access Conflicts With Code Security Module (CSM) PWL Registers                                                         |      |

| Advisory —eCAN: Abort Acknowledge Bit Not Set                                                                                                                 |      |

| Advisory —eCAN: Unexpected Cessation of Transmit Operation                                                                                                    |      |

| Advisory — LIN: SCI Operation in Multi-Buffer Mode                                                                                                            |      |

| Advisory — LIN: Possible Data Corruption in Extended Frame Mode                                                                                               | 14   |

| Advisory —LIN: LIN Transmission is Affected if Previous Transmission was not Complete due to Bit Error (BE)<br>During Checksum Field in Single Buffer Mode    | 14   |

| Advisory —LIN: TOA3WUP Gets Flagged When New Header is Received During Wait Time of 1.5 s                                                                     | 15   |

| Advisory —LIN: Frame Error (FE) During Checksum Byte Restarts Reception. A Frame Error is Flagged if a New Header is Received.                                | 15   |

| Advisory —LIN: When LIN Slave Adapts Itself to a Faster Incoming Header, No Response Error (NRE)/Time-out<br>Might not get Flagged Within Expected Time Frame | 15   |

| Advisory — LIN: LIN Rejects a Valid Byte Followed Upon After a False Start Bit                                                                                | 16   |

| Advisory —LIN: Incomplete Synch Field Reception Results in Loss of Next Header                                                                                | 16   |

| Advisory —LIN: When a Slave Receives a Wake-up Request With Length > 500 μs, it Does Not Transmit a Response to the First Header Following the Wake-up.       | 16   |

| Advisory —LIN: Incomplete Frame Header Consisting of Only Sync Break Will Cause the Following Complete<br>Header to be not Received by Slave                  | 17   |

| Advisory — Zero-Pin Oscillator: Modification to Oscillator Frequency Parameter                                                                                |      |

| Advisory —Watchdog: Incorrect Operation of CPU Watchdog When WDCLK Source is OSCCLKSRC2                                                                       |      |

| Advisory —Oscillator: CPU Clock Switching to INTOSC2 May Result in Missing Clock Condition After Reset                                                        |      |

| Advisory —eQEP: Missed First Index Event                                                                                                                      |      |

| Advisory —eQEP: Position Counter Incorrectly Reset on Direction Change During Index                                                                           |      |

| Advisory — eQEP: eQEP Inputs in GPIO Asynchronous Mode                                                                                                        |      |

| Advisory — ePWM: An ePWM Glitch can Occur if a Trip Remains Active at the End of the Blanking Window                                                          |      |

| Advisory — Boot ROM: Flash API [Flash_Erase() Function]                                                                                                       |      |

| Advisory — Boot-ROM: eCAN Boot Mode Not Available on TMX Samples                                                                                              |      |

|                                                                                                                                                               |      |

Table 4 shows which silicon revision(s) are affected by each advisory.

#### Table 4. List of Advisories

| TITLE                                                                                                                                               |     | SILICON REVISION(S)<br>AFFECTED |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------|--|

|                                                                                                                                                     | 0   | Α                               |  |

| ADC: Temperature Sensor Minimum Sample Window Requirement                                                                                           | Yes | Yes                             |  |

| ADC: DC Specifications: Linearity Limitation                                                                                                        | Yes | Yes                             |  |

| ADC: Offset Self-Recalibration Requirement                                                                                                          | Yes | Yes                             |  |

| ADC: ADC Result Conversion When Sampling Ends on 14th Cycle of Previous Conversion, ACQPS = 6 or 7                                                  | Yes | Yes                             |  |

| ADC: Initial Conversion                                                                                                                             | Yes | Yes                             |  |

| ADC: ADC can Become Non-Responsive When ADCNONOVERLAP or RESET is Written During a<br>Conversion                                                    | Yes | Yes                             |  |

| ADC: New ADC Control Bits Added to Revision A Silicon                                                                                               |     | Yes                             |  |

| ADC: Out-of-Specification Current Consumption on Power Up                                                                                           | Yes |                                 |  |

| Memory: Prefetching Beyond Valid Memory                                                                                                             | Yes | Yes                             |  |

| GPIO: GPIO Qualification                                                                                                                            | Yes | Yes                             |  |

| Code Security Module: Memory Access Conflicts With Code Security Module (CSM) PWL Registers                                                         | Yes | Yes                             |  |

| eCAN: Abort Acknowledge Bit Not Set                                                                                                                 | Yes | Yes                             |  |

| eCAN: Unexpected Cessation of Transmit Operation                                                                                                    | Yes | Yes                             |  |

| LIN: SCI Operation in Multi-Buffer Mode                                                                                                             | Yes | Yes                             |  |

| LIN: Possible Data Corruption in Extended Frame Mode                                                                                                | Yes | Yes                             |  |

| LIN: LIN Transmission is Affected if Previous Transmission was not Complete due to Bit Error (BE)<br>During Checksum Field in Single Buffer Mode    | Yes | Yes                             |  |

| LIN: TOA3WUP Gets Flagged When New Header is Received During Wait Time of 1.5 s                                                                     | Yes | Yes                             |  |

| LIN: Frame Error (FE) During Checksum Byte Restarts Reception. A Frame Error is Flagged if a New Header is Received.                                | Yes | Yes                             |  |

| LIN: When LIN Slave Adapts Itself to a Faster Incoming Header, No Response Error (NRE)/Time-out<br>Might not get Flagged Within Expected Time Frame | Yes | Yes                             |  |

| LIN: LIN Rejects a Valid Byte Followed Upon After a False Start Bit                                                                                 | Yes | Yes                             |  |

| LIN: Incomplete Synch Field Reception Results in Loss of Next Header                                                                                | Yes | Yes                             |  |

| LIN: When a Slave Receives a Wake-up Request With Length > 500 $\mu$ s, it Does Not Transmit a Response to the First Header Following the Wake-up   | Yes | Yes                             |  |

| LIN: Incomplete Frame Header Consisting of Only Sync Break Will Cause the Following Complete Header to be not Received by Slave                     | Yes | Yes                             |  |

| Zero-Pin Oscillator: Modification to Oscillator Frequency Parameter                                                                                 | Yes | Yes                             |  |

| Watchdog: Incorrect Operation of CPU Watchdog When WDCLK Source is OSCCLKSRC2                                                                       | Yes | Yes                             |  |

| Oscillator: CPU Clock Switching to INTOSC2 May Result in Missing Clock Condition After Reset                                                        | Yes | Yes                             |  |

| eQEP: Missed First Index Event                                                                                                                      | Yes | Yes                             |  |

| eQEP: Position Counter Incorrectly Reset on Direction Change During Index                                                                           | Yes | Yes                             |  |

| eQEP: eQEP Inputs in GPIO Asynchronous Mode                                                                                                         | Yes | Yes                             |  |

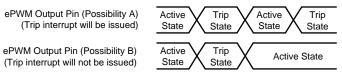

| ePWM: An ePWM Glitch can Occur if a Trip Remains Active at the End of the Blanking Window                                                           | Yes | Yes                             |  |

| Boot ROM: Flash API [Flash_Erase() Function]                                                                                                        | Yes | Yes                             |  |

| Boot-ROM: eCAN Boot Mode Not Available on TMX Samples                                                                                               | Yes |                                 |  |

| Advisory             | ADC: Temperature Sensor Minimum Sample Window Requirement                                                                                                                                                                                 |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Revision(s) Affected | 0, A                                                                                                                                                                                                                                      |  |

| Details              | If the minimum sample window is used (6 ADC clocks at 60 MHz, 116.67 ns), the resul of a temperature sensor conversion can have a large error, making it unreliable for the system.                                                       |  |

| Vorkaround(s)        |                                                                                                                                                                                                                                           |  |

|                      | <ol> <li>If double-sampling of the temperature sensor is used to avoid the corrupted first<br/>sample issue, the temperature sensor result is valid. This is equivalent to giving the<br/>S/H circuit adequate time to charge.</li> </ol> |  |

|                      | <ol> <li>In all other conditions, the sample-and-hold window used to sample the temperature<br/>sensor should not be less than 550 ns.</li> </ol>                                                                                         |  |

| Advisory             | ADC: DC Specifications: Linearity Limitation                                                                                                                                                                                              |  |

| Revision(s) Affected | 0, A                                                                                                                                                                                                                                      |  |

| Details              | The linearity degrades with increasing temperature in the upper half of the transfer function.                                                                                                                                            |  |

| Workaround(s)        | The impact from this limitation has been addressed in the revision A silicon. The following features have been added:                                                                                                                     |  |

|                      | 1. ADC clock divider-by-2 enable bit. At 60 MHz, the effective sample rate will be                                                                                                                                                        |  |

|                      | 2.3 MSPS. This offers a 30-MHz ADC and a 60-MHz system clock, and improves linearity.                                                                                                                                                     |  |

|                      | <ol> <li>Existing pipeline mode with 4.6 MSPS at 60-MHz system clock will have improved<br/>linearity compared to revision 0 silicon.</li> </ol>                                                                                          |  |

|                      | <b>NOTE:</b> For 60-MHz operation, there are periodic missing codes, and INL will be bounded by ±28 LSBs MAX/MIN.                                                                                                                         |  |

|                      | For 30-MHz operation, see the <i>TMS320F2803x Piccolo</i> <sup>™</sup> <i>Microcontrollers Data Manual.</i>                                                                                                                               |  |

| Advisory             | ADC: Offset Self-Recalibration Requirement                                                                                                                                                                                                |  |

| Revision(s) Affected | 0, A                                                                                                                                                                                                                                      |  |

| Details              | The factory offset calibration from Device_cal() may not ensure that the ADC offset remains within specifications under all operating conditions in the customer's system.                                                                |  |

| Vorkaround(s)        |                                                                                                                                                                                                                                           |  |

|                      | <ul> <li>To ensure that the offset remains within the data sheet's "single recalibration"<br/>specifications, perform the AdcOffsetSelfCal() function after Device_cal() has<br/>completed and the ADC has been configured.</li> </ul>    |  |

|                      | • To ensure that the offset remains within the data sheet's "periodic recalibration" specifications, perform the AdcOffsetSelfCal() function periodically with respect to temperature drift.                                              |  |

|                      | For more details on AdcOffsetSelfCal(), refer to the "ADC Zero Offset Calibration"                                                                                                                                                        |  |

| Advisory             | ADC: ADC Result Conversion When Sampling Ends on 14th Cycle of Previous Conversion, ACQPS = 6 or 7                                                                                                                                                                                                                                                                                                                                                    |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected | 0, A                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Details              | The on-chip ADC takes 13 ADC clock cycles to complete a conversion after the sampling phase has ended. The result is then presented to the CPU on the 14th cycle post-sampling and latched on the 15th cycle into the ADC result registers. If the next conversion's sampling phase terminates on this 14th cycle, the results latched by the CPU into the result register are not assured to be valid across all operating conditions.               |

| Workaround(s)        | Some workarounds are as follows:                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                      | <ul> <li>Due to the nature of the sampling and conversion phases of the ADC, there are only<br/>two values of ACQPS (which controls the sampling window) that would result in the<br/>above condition occurring—ACQPS = 6 or 7. One solution is to avoid using these<br/>values in ACQPS.</li> </ul>                                                                                                                                                  |

|                      | • When the ADCNONOVERLAP feature (bit 1 in ADCTRL2 register) is used, the above condition will never be met; so the user is free to use any value of ACQPS desired.                                                                                                                                                                                                                                                                                   |

|                      | • Depending on the frequency of ADC sampling used in the system, the user can determine if their system will hit the above condition if the system requires the use of ACQPS = 6 or 7. For instance, if the converter is continuously converting with ACQPS = 6, the above condition will never be met because the end of the sampling phase will always fall on the 13th cycle of the current conversion in progress.                                |

| Advisory             | ADC: Initial Conversion                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Revision(s) Affected | 0, A                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Details              | When the ADC conversions are initiated by any source of trigger in either sequential or simultaneous sampling mode, the first sample may not be the correct conversion result.                                                                                                                                                                                                                                                                        |

| Workaround(s)        | For sequential mode, discard the first sample at the beginning of every series of conversions. For instance, if the application calls for a given series of conversions, $SOC0 \rightarrow SOC1 \rightarrow SOC2$ , to initiate periodically, then set up the series instead as $SOC0 \rightarrow SOC1 \rightarrow SOC2 \rightarrow SOC3$ and only use the last three conversions, ADCRESULT1, ADCRESULT2, ADCRESULT3, thereby discarding ADCRESULT0. |

|                      | For simultaneous sample mode, discard the first sample of both the A and B channels at the beginning of every series of conversions.                                                                                                                                                                                                                                                                                                                  |

|                      | User application should validate if this workaround is acceptable in their application.                                                                                                                                                                                                                                                                                                                                                               |

|                      | The following is applicable to the revision A silicon:                                                                                                                                                                                                                                                                                                                                                                                                |

|                      | <ul> <li>For 30-MHz operation and below, this is fixed completely by writing a 1 to the<br/>ADCNONOVERLAP and CLKDIV2EN bits in the ADCTRL2 register. This will give a<br/>30-MHz ADC clock when the CPU clock = 60 MHz, and will only allow the sampling<br/>of ADC channels when the ADC is finished with any pending conversion.</li> </ul>                                                                                                        |

| www.ti.com           | Usage Notes and Known Design Exceptions to Functional Specifications                                                                                                                                                           |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Advisory             | ADC: ADC can Become Non-Responsive When ADCNONOVERLAP or RESET is<br>Written During a Conversion                                                                                                                               |  |

| Revision(s) Affected | 0, A                                                                                                                                                                                                                           |  |

| Details              | The ADC can get into a non-responsive state when the ADCCTL2[ADCNONOVERLAP] is modified while a conversion is in progress. When in this condition, no further conversion from the ADC will be possible without a device reset. |  |

|                      | <ul> <li>There are two different ways to cause this condition:</li> <li>Writing to ADCCTL2[ADCNONOVERLAP] while a conversion is in progress.</li> <li>Writing to ADCCTL1[RESET] while a conversion is in progress.</li> </ul>  |  |

| Workaround(s)        | Follow this sequence to modify ADCCTL2[ADCNONOVERLAP] or write<br>ADCCTL1[RESET]:                                                                                                                                              |  |

|                      | 1. Set all SOC trigger sources ADCSOCxCTL[TRIGSEL] to 0.                                                                                                                                                                       |  |

|                      | 2. Set all ADCINTSOCSEL1/2 to 0.                                                                                                                                                                                               |  |

|                      | 3. Ensure there is not another SOC pending (This can be accomplished by polling SOC Flags).                                                                                                                                    |  |

|                      | 4. Wait for all conversions to complete.                                                                                                                                                                                       |  |

|                      | a. ADCCTL2[CLKDIV2EN] = 0, ADCCTL2[CLKDIV4EN] = $x \rightarrow$ (ACQPS + 13 ) * 1 SYSCLKs                                                                                                                                      |  |

|                      | b. ADCCTL2[CLKDIV2EN] = 1, ADCCTL2[CLKDIV4EN] = 0 $\rightarrow$ (ACQPS + 13 ) * 2 SYSCLKs                                                                                                                                      |  |

|                      | c. ADCCTL2[CLKDIV2EN] = 1, ADCCTL2[CLKDIV4EN] = 1 $\rightarrow$ (ACQPS + 13 ) * 4 SYSCLKs                                                                                                                                      |  |

|                      | 5. Modify ADCCTL2[ADCNONOVERLAP] or write ADCCTL1[RESET].                                                                                                                                                                      |  |

|                      | An example code follows.                                                                                                                                                                                                       |  |

| Ad | <pre>lcRegs.ADCSOC0CTL.bit. TRIGSEL = 0;</pre>                            |

|----|---------------------------------------------------------------------------|

| Ad | lcRegs.ADCSOC1CTL.bit. TRIGSEL = 0;                                       |

| Ad | lcRegs.ADCSOC2CTL.bit. TRIGSEL = 0;                                       |

| Ad | <pre>lcRegs.ADCSOC3CTL.bit. TRIGSEL = 0;</pre>                            |

| Ad | lcRegs.ADCSOC4CTL.bit. TRIGSEL = 0;                                       |

| Ad | lcRegs.ADCSOC5CTL.bit. TRIGSEL = 0;                                       |

| Ad | lcRegs.ADCSOC6CTL.bit. TRIGSEL = 0;                                       |

| Ad | lcRegs.ADCSOC7CTL.bit. TRIGSEL = 0;                                       |

| Ad | lcRegs.ADCSOC8CTL.bit. TRIGSEL = 0;                                       |

| Ad | lcRegs.ADCSOC9CTL.bit. TRIGSEL = 0;                                       |

| Ad | lcRegs.ADCSOC10CTL.bit. TRIGSEL = 0;                                      |

| Ad | <pre>lcRegs.ADCSOC11CTL.bit. TRIGSEL = 0;</pre>                           |

| Ad | lcRegs.ADCSOC12CTL.bit. TRIGSEL = 0;                                      |

| Ad | lcRegs.ADCSOC13CTL.bit. TRIGSEL = 0;                                      |

| Ad | <pre>lcRegs.ADCSOC14CTL.bit. TRIGSEL = 0;</pre>                           |

| Ad | <pre>lcRegs.ADCSOC15CTL.bit. TRIGSEL = 0;</pre>                           |

| // | Set all ADCINTSOCSEL1/2 to 0.                                             |

|    | AdcRegs.ADCINTSOCSEL1.bit.SOC0 = 0;                                       |

|    | AdcRegs.ADCINTSOCSEL1.bit.SOC1 = 0;                                       |

|    | AdcRegs.ADCINTSOCSEL1.bit.SOC2 = 0;                                       |

|    | AdcRegs.ADCINTSOCSEL1.bit.SOC3 = 0;                                       |

|    | AdcRegs.ADCINTSOCSEL1.bit.SOC4 = 0;                                       |

|    | AdcRegs.ADCINTSOCSEL1.bit.SOC5 = 0;                                       |

|    | AdcRegs.ADCINTSOCSEL1.bit.SOC6 = 0;                                       |

|    | AdcRegs.ADCINTSOCSEL1.bit.SOC7 = 0;                                       |

|    | AdcRegs.ADCINTSOCSEL2.bit.SOC8 = 0;                                       |

|    | AdcRegs.ADCINTSOCSEL2.bit.SOC9 = 0;                                       |

|    | AdcRegs.ADCINTSOCSEL2.bit.SOC10 = 0;                                      |

|    | AdcRegs.ADCINTSOCSEL2.bit.SOC11 = 0;                                      |

|    | AdcRegs.ADCINTSOCSEL2.bit.SOC12 = 0;                                      |

|    | AdcRegs.ADCINTSOCSEL2.bit.SOC13 = 0;                                      |

|    | AdcRegs.ADCINTSOCSEL2.bit.SOC14 = 0;                                      |

|    | AdcRegs.ADCINTSOCSEL2.bit.SOC15 = 0;                                      |

|    | Ensure there is not another SOC pending                                   |

| wh | <pre>ile (AdcRegs.ADCSOCFLG1.all != 0x0);</pre>                           |

| // | Wait for conversions to complete                                          |

|    | Delay time based on ACQPS = 6 , ADCCTL2[CLKDIV2EN] = 1, ADCCTL2[CLKDIV4EN |

|    | 7 + 13 ADC Clocks = 20 ADCCLKS -> 40 SYSCLKS                              |

| as | sm(" RPT#40  NOP");                                                       |

|    | ADCCTL2[ADCNONOVERLAP] = <new value="">;</new>                            |

| // | ADCCTL1[RESET] = 1;                                                       |

| www.ti.com           | Usage Notes and Known Design Exceptions to Functional Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Advisory             | ADC: New ADC Control Bits Added to Revision A Silicon                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Revision(s) Affected | A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| Details              | The following bits/features have been added to the ADC control registers in the revision A silicon [see the Analog-to-Digital Converter and Comparator chapter in the <i>TMS320F2803x Piccolo Technical Reference Manual</i> for more information]:                                                                                                                                                                                                                                                           |  |  |

|                      | 1. Register ADCTL2 at address 0x7101, containing the following bits:                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|                      | • CLKDIV2EN, a /2 divide enable that scales CPU Clock by 1/2 for use by the ADC                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|                      | <ul> <li>ADCNONOVERLAP, a bit enable that removes the conversion/sample overlap timing</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|                      | 2. Addition of bit field ONESHOT in the existing ADCSOCPRIORITYCTL register. When enabled, the ONESHOT bit field will only let the first SOC complete if multiple SOCs are received at the same time. This is applicable for all SOCs that are in Round-Robin Priority. SOCs in High-Priority mode are not effected by this function.                                                                                                                                                                         |  |  |

| Workaround(s)        | Not applicable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Advisory             | ADC: Out-of-Specification Current Consumption on Power Up                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| Revision(s) Affected | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| Details              | When the ADC module is powered up for the first time, it can consume $2x$ the current listed ( $I_{DDA}$ ) in the data manual until a sample is initiated.                                                                                                                                                                                                                                                                                                                                                    |  |  |

| Workaround(s)        | Before the ADC is initially powered up, initiate a single conversion. Once the timing of the conversion has been satisfied, an ADC reset is recommended to restore the native state of the ADC before setting up the ADC as done before this addition. (Code is shown below.) If this amount of current can be tolerated by the system, then no change needs to be made to the setup code. Note that the current will go back to within data manual limits once the first conversion is processed by the ADC. |  |  |

|                      | EALLOW;<br>SysCtrlRegs.PCLKCR0.bit.ADCENCLK=1; //Enable Clocks to ADC module<br>AdcRegs.ADCSOCFRC1.bit.SOC0 = 1; //Issue dummy conversion<br>asm(" rpt #19    nop"); //Wait for conversion to propagate<br>AdcRegs.SOCPRICTL.bit.SOCPRIORITY = 1; //Change Priority Control to reset<br>AdcRegs.SOCPRICTL.bit.SOCPRIORITY = 0; //round robin pointer<br>EDIS;                                                                                                                                                 |  |  |

| Advisory             | Memory: Prefetching Beyond Valid Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Revision(s) Affected | 0, A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| Details              | The C28x CPU prefetches instructions beyond those currently active in its pipeline. If the prefetch occurs past the end of valid memory, then the CPU may receive an invalid opcode.                                                                                                                                                                                                                                                                                                           |  |  |

| Workaround           | The prefetch queue is 8 x16 words in depth. Therefore, code should not come within 8 words of the end of valid memory. This restriction applies to all memory regions and all memory types (flash, OTP, SARAM) on the device. Prefetching across the boundary between two valid memory blocks is all right.                                                                                                                                                                                    |  |  |

|                      | Example 1: M1 ends at address 0x7FF and is not followed by another memory block.<br>Code in M1 should be stored no farther than address 0x7F7. Addresses 0x7F8-0x7FF<br>should not be used for code.                                                                                                                                                                                                                                                                                           |  |  |

|                      | Example 2: M0 ends at address 0x3FF and valid memory (M1) follows it. Code in M0 can be stored up to and including address 0x3FF. Code can also cross into M1 up to and including address 0x7F7.                                                                                                                                                                                                                                                                                               |  |  |

| Advisory             | GPIO: GPIO Qualification                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Revision(s) Affected | 0, A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| Details              | If a GPIO pin is configured for "n" SYSCLKOUT cycle qualification period (where $1 \le n \le 510$ ) with "m" qualification samples (m = 3 or 6), it is possible that an input pulse of [n * m - (n - 1)] width may get qualified (instead of n * m). This depends upon the alignment of the asynchronous GPIO input signal with respect to the phase of the internal prescaled clock, and hence, is not deterministic. The probability of this kind of wrong qualification occurring is "1/n". |  |  |

|                      | Worst-case example:                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|                      | If n = 510, m = 6, a GPIO input width of (n * m) = 3060 SYSCLKOUT cycles is required to pass qualification. However, because of the issue described in this advisory, the minimum GPIO input width which may get qualified is $[n * m - (n - 1)] = 3060 - 509 = 2551$ SYSCLKOUT cycles.                                                                                                                                                                                                        |  |  |

| Workaround(s)        | None. Ensure a sufficient margin is in the design for input qualification.                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| Advisory             | Code Security Module: Memory Access Conflicts With Code Security Module<br>(CSM) PWL Registers                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Revision(s) Affected | 0, A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| Details              | Reads of addresses 0x3D 7FF8–0x3D 7FFF will activate the CSM, locking the device.                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Workaround(s)        | Do not read these addresses. If these addresses are read, causing the CSM to become active, the device can be unlocked either by first pulling reset or by setting the FORCESEC bit, and then performing the Password Match Flow described in the System Control chapter in the <i>TMS320F2803x Piccolo Technical Reference Manual</i> .                                                                                                                                                       |  |  |

|                      | <b>NOTE:</b> For TMS320F2803x devices, the PARTID register is located at 0x3D 7E80 (and not at 0x3D 7FFF, as on the TMS320F2802x devices).                                                                                                                                                                                                                                                                                                                                                     |  |  |

| www.ti.com           | Usage Notes and Known Design Exceptions to Functional Specifications                                                                                                                                                                                                                                                                                                                                |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advisory             | eCAN: Abort Acknowledge Bit Not Set                                                                                                                                                                                                                                                                                                                                                                 |

| Revision(s) Affected | 0, A                                                                                                                                                                                                                                                                                                                                                                                                |

| Details              | After setting a Transmission Request Reset (TRR) register bit to abort a message, there are some rare instances where the TRRn and TRSn bits will clear without setting the Abort Acknowledge (AAn) bit. The transmission itself is correctly aborted, but no interrupt is asserted and there is no indication of a pending operation.                                                              |

|                      | In order for this rare condition to occur, all of the following conditions must happen:                                                                                                                                                                                                                                                                                                             |

|                      | <ol> <li>The previous message was not successful, either because of lost arbitration or<br/>because no node on the bus was able to acknowledge it or because an error frame<br/>resulted from the transmission. The previous message need not be from the same<br/>mailbox in which a transmit abort is currently being attempted.</li> </ol>                                                       |

|                      | 2. The TRRn bit of the mailbox should be set in a CPU cycle immediately following the cycle in which the TRSn bit was set. The TRSn bit remaining set due to incompletion of transmission satisfies this condition as well; that is, the TRSn bit could have been set in the past, but the transmission remains incomplete.                                                                         |

|                      | 3. The TRRn bit must be set in the exact SYSCLKOUT cycle where the CAN module is in idle state for one cycle. The CAN module is said to be in idle state when it is not in the process of receiving/transmitting data.                                                                                                                                                                              |

|                      | If these conditions occur, then the TRRn and TRSn bits for the mailbox will clear $t_{clr}$ SYSCLKOUT cycles after the TRR bit is set where:                                                                                                                                                                                                                                                        |

| t <sub>cir</sub> =   | [(mailbox_number) * 2] + 3 SYSCLKOUT cycles                                                                                                                                                                                                                                                                                                                                                         |

|                      | The TAn and AAn bits will not be set if this condition occurs. Normally, either the TA or AA bit sets after the TRR bit goes to zero.                                                                                                                                                                                                                                                               |

| Workaround(s)        | When this problem occurs, the TRRn and TRSn bits will clear within $t_{clr}$ SYSCLKOUT cycles. To check for this condition, first disable the interrupts. Check the TRRn bit $t_{clr}$ SYSCLKOUT cycles after setting the TRRn bit to make sure it is still set. A set TRRn bit indicates that the problem did not occur.                                                                           |

|                      | If the TRRn bit is cleared, it could be because of the normal end of a message and the corresponding TAn or AAn bit is set. Check both the TAn and AAn bits. If either one of the bits is set, then the problem did not occur. If they are both zero, then the problem did occur. Handle the condition like the interrupt service routine would except that the AAn bit does not need clearing now. |

|                      | If the TAn or AAn bit is set, then the normal interrupt routine will happen when the interrupt is re-enabled.                                                                                                                                                                                                                                                                                       |

| Advisory             | eCAN: Unexpected Cessation of Transmit Operation                                                                                                                                                                                                                                                                                                                                                    |

| Revision(s) Affected | 0, A                                                                                                                                                                                                                                                                                                                                                                                                |

| Details              | In rare instances, the cessation of message transmission from the eCAN module has been observed (while the receive operation continues normally). This anomalous state may occur without any error frames on the bus.                                                                                                                                                                               |

| Workaround(s)        | The Time-out feature (MOTO) of the eCAN module may be employed to detect this condition. When this occurs, set and clear the CCR bit (using the CCE bit for verification) to remove the anomalous condition.                                                                                                                                                                                        |

| Advisory             | LIN: SCI Operation in Multi-Buffer Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected | 0, A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Details              | When the LIN node is in SCI multi-buffer mode and if the buffer length is configured as less than 8, then the first set of data (that is, programmed number of bytes) is transmitted correctly but the transmission of the first byte of subsequent sets of data is corrupted. The TX EMPTY flag gets set at the start of the STOP bit transmission instead of at the end of the STOP bit.                                                                                                                          |

|                      | This issue is applicable only for buffered SCI mode and for buffer length less than 8 bytes.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Workaround(s)        | When SCI Buffered mode is selected, always configure the buffer length to "8".                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Advisory             | LIN: Possible Data Corruption in Extended Frame Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Revision(s) Affected | 0, A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Details              | In Extended Frame Mode, during Single Buffer Mode transmission, when the TX Buffer (TD0) is loaded with new data during the STOP bit transmission of the previous data byte, transmission of the next data byte will be corrupted (that is, start bit of the next data byte will be corrupted (that is, start bit of the next data byte will be corrupted (that is, start bit of the next data byte will be corrupted (that byte will be corrupted).                                                                |

|                      | This issue is applicable only when the Extended Frame Mode is enabled and Single Buffer Mode transmission is selected. This problem will occur on both Master and Slave nodes.                                                                                                                                                                                                                                                                                                                                      |

| Workaround(s)        | In Extended Frame Mode, during Single Buffer Mode transmission, always wait for the TX_EMPTY flag before loading the TD0 buffer with the new data.                                                                                                                                                                                                                                                                                                                                                                  |

| Advisory             | LIN: LIN Transmission is Affected if Previous Transmission was not Complete due to Bit Error (BE) During Checksum Field in Single Buffer Mode                                                                                                                                                                                                                                                                                                                                                                       |

| Revision(s) Affected | 0, A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Details              | In Single Buffer Mode transmission, if Bit Error occurs during the transmission of the checksum byte, then after the reception of next header, there will be an idle period of 10 $T_{bit}$ times after the first data byte transmission. This results in the transmission of 1 byte less than the configured response length and also impacts the slave's No Response Error (NRE) count. This issue is applicable only during Single Buffer Mode transmission. This is applicable for both Master and Slave nodes. |

| Workaround(s)        | Issue a software reset upon bit error.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| www.ti.com           | Usage Notes and Known Design Exceptions to Functional Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advisory             | LIN: TOA3WUP Gets Flagged When New Header is Received During Wait Time of 1.5 s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |