# User Guide PD-IM-7618T4H and PD-IM-7618T4 Eight Port PoE Evaluation Boards

**Doc Version 1.0**

**Document Number PD-000395299**

# 1. Product Overview

The PD-IM-7618T4H and PD-IM-7618T4 evaluation boards are developed based on Microchip's PD69208T4and PD69210 chipset:

- The PD-IM-7618T4H demonstrates the operation of eight 4-pair ports (2 pairsets) according to IEEE802.3bt.

- The PD-IM-7618T4 demonstrates the operation of eight 2-pair ports (a single pairset).

Microchip's PD69208M/PD69208T4/PD69204T4 Power over Ethernet (PoE) manager IC integrates power, analog, and state-of-the-art logic into a single 56-pin, plastic QFN package. The device is used in Ethernet switches and midspans/injectors to allow network devices to share power and data over the same Ethernet cable.

The PD69208M/PD69208T4 device is an 8-port and PD69204T4 device is a 4-port, mixed-signal and high voltage PoE driver. Together with the PD69210 external MCU, it performs as a PSE system. Microchip's PD69210 PoE controller is a cost-effective and pre-programmed MCU designed to implement enhanced Mode PoE system.

The PD69208M/PD69208T4/PD69204T4 and PD69210 chipset supports PoE powered device (PD) detection, power-up, and protection according to IEEE802.3af/at/bt standards as well as legacy/pre-standard PD detection. It provides real-time PD protection through the following mechanisms: overload, under-load, over-voltage, over-temperature, and short-circuit, and enables operation in a standalone mode. It also executes all real-time functions as specified in IEEE802.3at and IEEE802.3bt standards, including PD detection (AF and AT).

The PD69208M/PD69208T4/PD69204T4 support supply voltages between 32 V and 57 V without additional power sources. A system that powers over 4 pairs is implemented by combining 2 ports of PD69208M/T4 and PD69204T4, enabling an extra feature for simple and low-cost high-power PD devices. Ongoing monitoring of system parameters for the host software is available through communication. For higher reliability, internal thermal protection is implemented in the chip. The PD69208M/PD69208T4/PD69204T4 is the most integrated PSE IC including internal MOSFET and sense resistor to achieve a low power dissipation.

The PD69210 features an eSPI bus for each PD69208M/PD69208T4/PD69204T4. It is based on the Microchip D21 family. The PD69210 utilizes an  $I^2C$  or UART interface to the host CPU. It is designed to support software field-upgradable through the communication interface. The evaluation system provides designers with the required environment to evaluate the performance.

The evaluation system has the following features.

- Two RJ45 gangs (each contains 4 RJ45 connectors)

- Switch domain isolated from PoE domain

- Switch domain USB interface to be connected to a PC with Microchip GUI

- PoE controller manual reset & serial communication setting

- LED status indication for all ports (LED stream)

- Requires single power source only

- 0 °C to 40 °C working temperature

- RoHS compliant

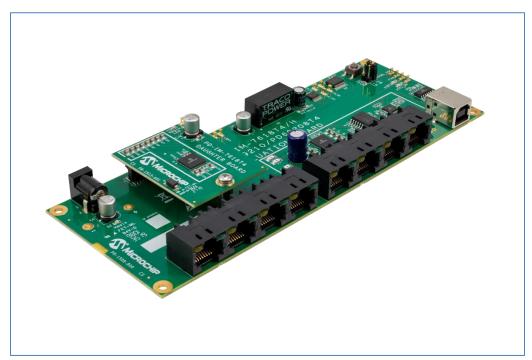

Figure 1 PD-IM-7618T4H (Main and Daughter card)

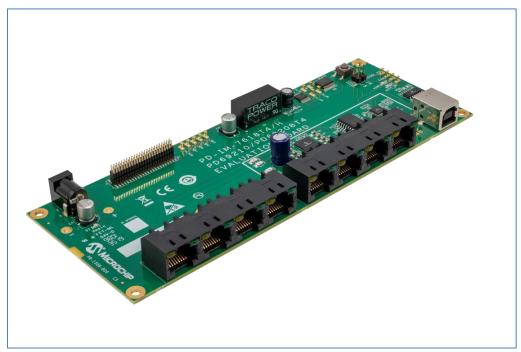

Figure 2 PD-IM-7618T4 (Main card only)

# 1.1. PD-IM-7618-T4H

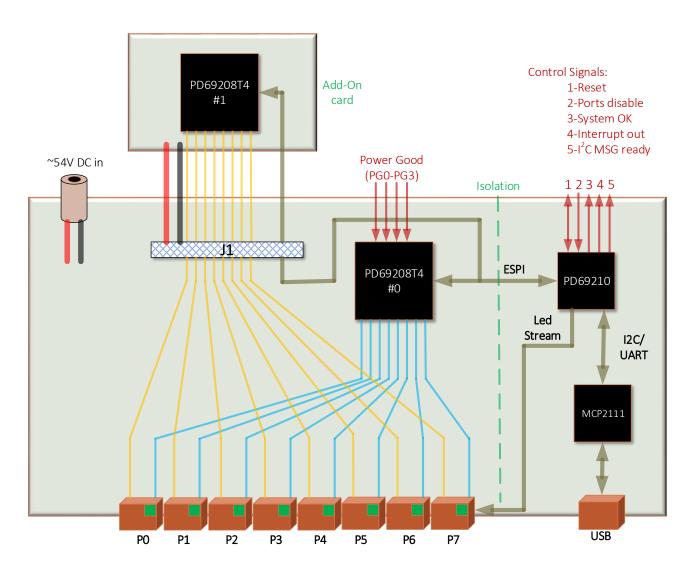

The PD-IM-7618-T4H demonstrates the operation of eight 4-pair ports, and is based on a PD69210 PSE controller and two PD69208T4 PSE managers.

The PD69210 and one PD69208T4 (#0) are assembled on the main board, the 2<sup>nd</sup> PD69208T4 (#1) is assembled on add-on card.

Connector J1 on the main board (J2 on the add-on card) carries the ports current, supply and all communication between the main board and add-on card.

Each PD69208T4 drives the power to a different pairset in the RJ45 connector:

PD69208T4 (#0) - Pairset B

PD69208T4 (#1) - Pairset A

Figure 3 • PD-IM-7618T4H Evaluation System Block Diagram

# 1.2. PD-IM-7618-T4

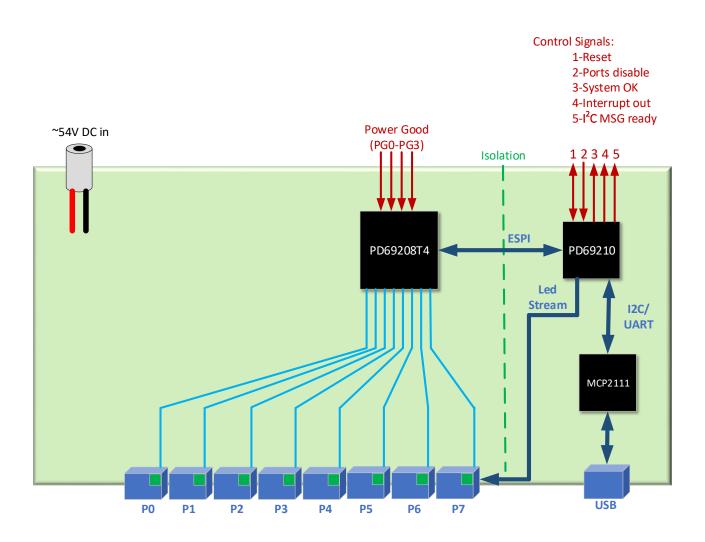

The PD-IM-7618-T4 demonstrates the operation of eight 2-pair ports, and is based on a PD69210 PSE controller and a PD69208T4 PSE manager.

The PD69210 and the PD69208T4 (#0) are assembled on the main board.

Figure 4 • PD-IM-7618T4 Evaluation System Block Diagram

# 1.3. Power

The EVB is powered by a single source via the DC connector J2\*

The input voltage level can be selected according to the IEEE802.3 POE standards:

IEEE802.3af: 44Vdc to 57Vdc.

IEEE802.3at: 50Vdc to 57Vdc.

• IEEE802.3bt: 50Vdc to 57Vdc for type 3.

52Vdc to 57Vdc for type 4.

The recommended voltage level is 55Vdc, which covers all POE standards.

The EVB has 2 power domains:

- POE domain, which is fed directly by the main supply, and it is the power domain provided by the RJ45.

- Isolated 3.3Vdc, which feeds the PD69210, LED stream and serial communication peripherals. The isolated 3.3Vdc is generated by U2 (a DC/DC module).

Test points 3.3V\_iso and GND\_ISO can be used for connecting external signals to control the PD69210.

# Important!

The EVB is polarity sensitive.

Please refer to Fig 3 for the correct polarity.

Figure 5 • DC connector J2 Polarity

#### Important!

\* DC connector J2 is limited to current level up to 4A.

If higher current is needed, the 2 via holes next to J2 can be used, by soldering a cable to it.

The 2 via holes support up to 10A to feed the whole EVB.

Figure 6 Power via holes

# 1.4. Interface and Control

#### **Serial communication:**

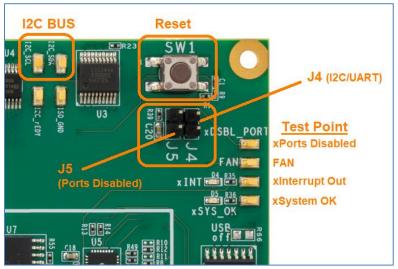

The EVB supports serial communication with the PD69210 (UART and I<sup>2</sup>C).

The serial communication is converted to USB, in order to allow the user-friendly experience using Microchip GUI.

If R66 is installed as 00hm, the USB converter (U10) is disabled, this allows the user to connect directly to the  $I^2C$  bus via the 2 test-points and control the EVB.

The ISO\_GND test-point is the GND for the I<sup>2</sup>C bus.

Please refer to Figure 4.

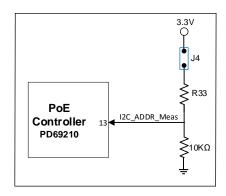

UART or I<sup>2</sup>C can be select by jumper J4:

- When Jumper J4 is <u>not installed</u>, the PD69210 is set to UART mode.

- When Jumper J4 is <u>installed</u>, the PD69210 is set to I<sup>2</sup>C mode.

In order to select I<sup>2</sup>C address, R33 should be installed according to table 1.

(R33 is located on the PCB bottom side, below the PD69210).

The EVB is set to  $I^2C$  address 0x2C (R33= 11K).

Table 1 • I<sup>2</sup>C address setting

| I <sup>2</sup> C Address | Address | R33  |

|--------------------------|---------|------|

|                          | (Hex)   | (kΩ) |

| #0                       | UART    | N.C  |

| #1                       | 0x4     | 147  |

| #2                       | 0x8     | 86.6 |

| #3                       | 0xC     | 57.6 |

| #4                       | 0x10    | 43.2 |

| #5                       | 0x14    | 34   |

| #6                       | 0x18    | 26.7 |

| #7                       | 0x1C    | 22.1 |

| #8                       | 0x20    | 18.2 |

| #9                       | 0x24    | 15.4 |

| #10                      | 0x28    | 13   |

| #11                      | 0x2C    | 11   |

| #12                      | 0x30    | 9.31 |

| #13                      | 0x34    | 7.87 |

| #14                      | 0x38    | 6.49 |

| #15                      | 0x3C    | 5.49 |

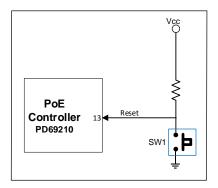

#### Reset Pushbutton:

The Pushbutton is connected to the Reset pin of the PD69210 (Pin 26) Pressing on SW1, will connect the reset pin to GND.

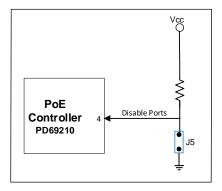

# POE ports disable:

J5 is connected to the Disable pin of the PD69210 (Pin 4) When the jumper J5 is installed, the Disable pin is connected to GND.

Figure 7 I<sup>2</sup>C bus test point & control signals

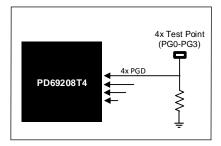

#### Power Good input (PGD0-PGD3):

The EVB supports feeding from up to 4 power-supplies, which means 16 power banks (bank0 to bank15). Each power supply should generate a digital signal (3.3Vdc), which indicates the power-supply is active. That signal should be connected to one of the PGD pins of the PD69208 (Pins 41, 46, 47, 56). On the EVB, the four PGD pins are pulled-down with a 10K resistor to DGND, which set the default power bar

On the EVB, the four PGD pins are pulled-down with a 10K resistor to DGND, which set the default power bank to 0x00.

In order to set a different bank then 0x00, the user can use the PG0-PG3 tests points, located next to U2. The four PGD signal are related to the POE domain, and can be used with the test point named **POE DGND**, next to it.

Figure 8 PGD0-PGD3 Test Points

# 1.5. RJ45 Connectors Polarity

The eight ports of J6 & J7 are 4-pair or 2-pair, the polarity of the port is listed in the following table.

Table 2 • RJ45 Connectors 4-pair Port (PD-IM-7618T4H)

| Pin Number (each RJ45) | Polarity       |

|------------------------|----------------|

| 1,2                    | Negative Alt A |

| 3,6                    | Positive Alt A |

| 4,5                    | Positive Alt B |

| 7,8                    | Negative Alt B |

Table 3 • RJ45 Connectors 2-pair Port (PD-IM-7618T4)

| Pin Number (each RJ45) | Polarity       |

|------------------------|----------------|

| 1,2                    | N.A            |

| 3,6                    | N.A            |

| 4,5                    | Positive Alt B |

| 7,8                    | Negative Alt B |

**Figure 9 Ports Numbering**

# 1.6. LED Indication

The evaluation board contains status indication LEDs, listed in the following table.

# Table 4 • LED list

| Designation | Function                                                                                                                                |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| D2          | Vmain ON                                                                                                                                |

| D3          | Isolated 3.3Vdc ON                                                                                                                      |

| D4          | Interrupt out (Active low)                                                                                                              |

| D5          | System OK (Active low)                                                                                                                  |

| Port (0-7)  | Green Led per port:<br>Led off→ Port is off<br>Led on→ Port is on<br>Led blinking→ Port is off due to error/under load/power management |

# 2. Installation and Setting

This section describes the steps required for installing and operating the PD-IM-7618T4/H Please take the following precautions before starting the installation:

- Ensure that the power supply of the board is turned-off before plugging in the DC connecter.

- After the DC connector is plugged-in, turn the main supply ON.

- If using the DC connector, please ensure that power banks are set to 250W.

- Ensure the correct polarity of the power supply cable. The polarity of the power supply cable is as shown in figure 3.

#### 2.1. Ports Matrix

Please make sure the ports matrix is configured according to the following table:

Table 5 • Ports Matrix PD-IM-76184TH

| Logical Port | Physical Port A | Physical Port B |

|--------------|-----------------|-----------------|

| 0            | 0               | 11              |

| 1            | 1               | 10              |

| 2            | 2               | 9               |

| 3            | 3               | 8               |

| 4            | 4               | 15              |

| 5            | 5               | 14              |

| 6            | 6               | 13              |

| 7            | 7               | 12              |

Table 6 • Ports Matrix PD-IM-76184T

| Logical Port | Physical Port A | Physical Port B |

|--------------|-----------------|-----------------|

| 0            | 0               | 0xFF            |

| 1            | 1               | 0xFF            |

| 2            | 2               | 0xFF            |

| 3            | 3               | 0xFF            |

| 4            | 4               | 0xFF            |

| 5            | 5               | 0xFF            |

| 6            | 6               | 0xFF            |

| 7            | 7               | 0xFF            |

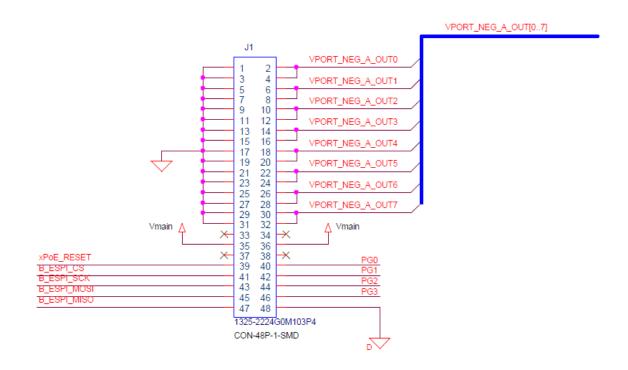

# 2.2. Connectors J1 and J2

The PD-IM-7618T4H contains 2 boards which are connected by J1 on the main card, and J2 on the daughter board.

J1 & J2 carry the POE high POE current, PGD signals for the PD69208, and the isolated ESPI signals.

Each signal named **VPORT\_NEG\_A\_OUTn** is connected to the physical port of the PD69208 located on the daughter board, the current via each signal named **VPORT\_NEG\_A\_OUTn** can reach up to 1Amp.

The AGND pins (1,3,...29, 31) carry the return current.

The drawing below describes the pinout of J1 and J2.

Pins 39, 41, 43, 45, 47, 48 are related to the isolated domain (PD69210), the rest of the pins are related to the POE domain (PD69208).

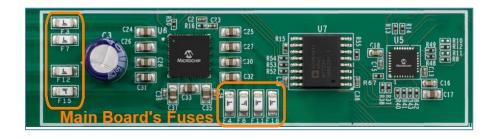

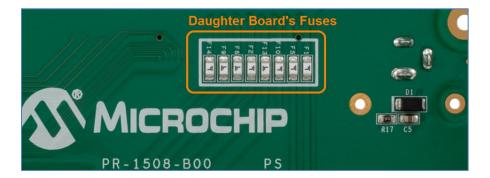

# 2.3. Fuses

On the main board there are 16 fuses: 8 fuses for the PD69208 (located on the main board, top side) and 8 for the PD69208 (located on the daughter board, bottom side).

Fuses per port are not required for use in circuits with a total power level of up to 3 kW, as the PD69208 is designed to fulfill limited power source (LPS) requirements per the latest editions of IEC60950-1 and EN60950-1. However, IEC62368-1 ED3 which was released in October 2018 and becomes effective December 2020 requires per port fuses for a system power supply greater than 250 W.

Figure 8 Fuses

# 2.4. Schematics

The full schematics of the EVB are available on the Microchip website: <a href="https://www.microsemi.com/product-directory/poe-pse-manager/4777-pd69200#resources">https://www.microsemi.com/product-directory/poe-pse-manager/4777-pd69200#resources</a>

a MICROCHIP company

Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA

Within the USA: +1 (800) 713-4113

Outside the USA: +1 (949) 380-6100

Fax: +1 (949) 215-4996

Support: my.microsemi.com

www.microsemi.com

©2020 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. The technology discussed in this document may be protected by one or more patent grants.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions; security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at <a href="https://www.microsemi.com">www.microsemi.com</a>.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.