# Using the TPS65910 EVM, A Multichannel Power-management IC, 3 Buck, 1 Boost, and 8 LDOs

# **User's Guide**

Literature Number: SWCU065F March 2010–Revised April 2013

# Introduction

# 1 Description

# **Device Description:**

The TPS65910 device is an integrated power-management IC available in 48-QFN package and is dedicated to applications powered by one Li-Ion or Li-Ion polymer battery cell, 3-series Ni-MH cells, or a 5 V input, and which requires multiple power rails. The device provides three step-down converters, one step-up converter, and eight low dropout voltage regulators (LDOs) and is designed to support the specific power requirements of OMAP<sup>™</sup> processors.

Two of the step-down converters provide power for dual processor cores and are controllable by a dedicated class-3 SmartReflex<sup>TM</sup> interface for optimum power savings. The third converter provides power for the I/Os and memory in the system. The device includes eight general-purpose LDOs providing a wide range of voltages and current capabilities. These LDOs can be controlled by the inter-integrated circuit  $(I^2C^{TM})$  interface.

In addition to the power resources, the device contains an embedded power controller (EPC) to manage the power sequencing requirements of OMAP processor and a real-time clock (RTC).

#### **EVM Kit Description:**

The TPS65910 evaluation module (EVM) is a stand-alone module that demonstrates the functions of the integrated power management IC. It uses a USB-to-GPIO interface card (not included in the kit) to control the standard I<sup>2</sup>C interfaces in the TPS65910 device. It includes Windows<sup>™</sup>-compatible software to interface with the device. The software is a simple graphical user interface (GUI) that simplifies registers access for the IC (software CD is not included in the kit, must be downloaded from product folder on ti.com).

# **EPROM Power-Up Sequence Description:**

This user guide is common for all TPS65910x parts. The only difference in these parts is the EEPROM sequence for power-up. Each part has a unique EEPROM sequence to satisfy the attached application processor. For details of the EEPROM sequence please refer to the corresponding user guide in the "Application Notes" section on the TPS65910x folder page.

# 1.1 Applications

- Embedded application processor power

- Handheld/portable systems

- 1.2 Features

- An EPC

- Two efficient step-down DCDC converters for processor cores

- One efficient step-down DCDC converter for I/O power

- One efficient step-up 5-V DCDC converter

- SmartReflex-compliant dynamic voltage management for processor cores

- Eight LDO voltage regulators and one RTC LDO (internal purpose)

- One high-speed I<sup>2</sup>C interface for general-purpose control command

- One high-speed I<sup>2</sup>C interface for SmartReflex (SR) class-3 control command

- Two enable signals multiplexed with SR-I2C, configurable to control any supply state and processor cores supply voltage

- Thermal shutdown protection and hot-die detection

- An RTC resource with:

- Oscillator for 32.768-kHz crystal or 32-kHz built-in RC oscillator

- Complete calendar capability

- Alarm capability

- One configurable general-purpose input/output (GPIO)

- DCDCs switching synchronization through internal or external 3-MHz clock

- Backup battery charger

| POWER RESOURCE | TYPE         | VOLTAGE RANGE (V)       | l <sub>max</sub> (mA) |

|----------------|--------------|-------------------------|-----------------------|

| VIO            | SMPS (buck)  | 1.5, 1.8, 2.5, 3.3      | 1000                  |

| VDD1           | SMPS (buck)  | 0.6, 1.1, 1.5, 2.2, 3.2 | 1500                  |

| VDD2           | SMPS (buck)  | 0.6, 1.1, 1.5, 2.2, 3.2 | 1500                  |

| VDD3           | SMPS (boost) | 5                       | 100                   |

| VDIG1          | LDO          | 1.2, 1.5, 1.8, 2.7      | 300                   |

| VDIG2          | LDO          | 1.0, 1.1, 1.2, 1.8      | 300                   |

| VAUX33         | LDO          | 1.8, 2.0, 2.8, 3.3      | 150                   |

| VMMC           | LDO          | 1.8, 2.8, 3.0, 3.3      | 300                   |

| VAUX1          | LDO          | 1.8, 2.5, 2.8, 2.85     | 300                   |

| VAUX2          | LDO          | 1.8, 2.8, 2.9, 3.3      | 150                   |

| VDAC           | LDO          | 1.8, 2.6, 2.8, 2.85     | 150                   |

| VPLL           | LDO          | 1.0, 1.1, 1.8, 2.5      | 50                    |

# 2 TPS65910 EVM Power Capabilities

For detailed electrical characteristics of SMPS and LDO supplies, refer to the product data sheet.

# 3 Schematic

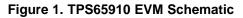

Figure 1 shows the TPS65910 EVM schematic.

#### Schematic

www.ti.com

# 4 Connector and Test Point Descriptions

# 4.1 Connector Descriptions

#### 4.1.1 Boot Pins

J16 and J17 are used to select the boot pin configuration for proper booting of the device. Table 2 shows the possible boot options.

| BOOT 0 | BOOT 1 | POWER UP OPTION  |

|--------|--------|------------------|

| 0      | 0      | AM35xx           |

| 0      | 1      | EEPROM boot mode |

| 1      | 0      | OMAP3x           |

| 1      | 1      | Test mode only   |

| Tahlo | 2  | Root | Configuration |

|-------|----|------|---------------|

| Iable | ۷. | BUUL | Connyuration  |

# 4.1.2 Backup Battery

J6 is used for the backup battery connection. The user can connect a backup battery between J6-2 and J6-3 or alternatively can use the onboard 0.2 F, 3.3 V capacitor by shorting J6-1 and J6-2.

# 4.1.3 VBAT

VBAT (J4) is the main input source to the device. Table 3 lists the minimum and maximum levels that can be applied to these pins. Use J5 for ground.

#### **Table 3. VBAT Minimum and Maximum Levels**

| VBAT | MIN (V) | TYP (V) | MAX (V) |

|------|---------|---------|---------|

| VDAT | 2.7     | 3.6     | 5.5     |

Ensure that the jumper settings for the jumpers listed in Table 4 are correct so the device is supplied by VBAT.

#### Table 4. VBAT Input Jumper Settings

| JUMPER CONNECTION | DEVICE INPUT PIN | USE                          |

|-------------------|------------------|------------------------------|

| J7 (1-2)          | VCC5             | Selects VBAT as power source |

| J8 (1-2)          | VCC3             | Selects VBAT as power source |

| J9 (1-2)          | VCC2, VCC4       | Selects VBAT as power source |

| J10 (2-3)         | VCC6             | Selects VBAT as power source |

#### 4.1.4 Default Jumper Settings for the Boost Converter

#### Table 5. Boost Converter Jumper Settings

| JUMPER ID | LABEL | USE                                 |

|-----------|-------|-------------------------------------|

| J21       | SW3   | Short jumper to use boost converter |

| J22       | VFB3  | Short jumper to use boost converter |

For correct functioning of VDD3, first VAUX33 must be enabled at 3.3V and then VDD3 should be enabled using the appropriate register settings.

# 4.1.5 I<sup>2</sup>C connector

TPS65910 has two slave I<sup>2</sup>C interfaces: one is a general-purpose interface to control the internal configuration registers, the second is dedicated to SmartReflex applications such as dynamic voltage frequency scaling (DVFS) or adaptive voltage scaling (AVS).

These interfaces support the standard slave mode (100 kbps), fast mode (400 kbps), and high-speed mode (3.4 Mbps).

| CONNECTOR NUMBER | PIN   | DESCRIPTION                                                           |

|------------------|-------|-----------------------------------------------------------------------|

| J1               | 9, 10 | General purpose I <sup>2</sup> C interface for register configuration |

| J2               | 9,10  | Dedicated I <sup>2</sup> C interface for SmartReflex                  |

| Table 6. I <sup>2</sup> C Connector |

|-------------------------------------|

|-------------------------------------|

J1 and J2 also have GPIO, SLEEP, and PWRHOLD signals that can be controlled from the GUI and USB-to-GPIO interface.

The SmartReflex can be programmed as enable signals of one or several supplies when the device is on. A resource assigned to either SmartReflex signal (SDASR\_EN2 or SCLSR\_EN1) automatically disables the serial control interface.

Connectors J1 and J2 are used for the USB adapter. Table 7 lists the signal mapping to control the signals on the EVM. The GPIO field on the GUI can be toggled to drive the following signals on the EVM.

| PIN NUMBER FOR J1 and J2 | GPIO ON GUI | TPS65910x SINGAL |

|--------------------------|-------------|------------------|

| Pin 1                    | GPIO7       | SLEEP            |

| Pin 2                    | GPIO6       | GPIO             |

| Pin 3                    | GPIO5       | PWRHOLD          |

#### Table 7. GPIO Mapping For GUI

# 4.1.6 3.3-V I/O for VDDIO

The USB-to-GPIO interface is on connectors J1 and J2. The USB-to-GPIO module generates 3.3 V, which is used as the I/O for the EVM. The following jumper configuration must be done for the I/O supply.

#### Table 8. Jumper for I/O Input Setting

| JUMPER CONNECTION | DEVICE INPUT PIN | USE                                                      |

|-------------------|------------------|----------------------------------------------------------|

| J11 (1-2)         | VDDIO            | Connects J1-5 (or J2-5) to VDDIO for 3.3-<br>V I/O input |

#### 4.1.7 Control Jumper Settings

TPS65910 has some control signals that can be configured using the on-board jumpers or by using the USB-to-GPIO connector.

#### Table 9. Control Signals

| Jumper connection | Signal Name | Use                                        |

|-------------------|-------------|--------------------------------------------|

| J18               | GPIO        | Jumper the three pin connector as required |

| J19               | SLEEP       | Jumper the three pin connector as required |

|     |           | (                                                                                                                                         |

|-----|-----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| J20 | PWRHOLD   | If PWRHOLD is low then the device will<br>not power-up. So, connect this to HI side<br>of the jumper. See important description<br>below. |

| J13 | SDASR_EN2 | Both these signals can be used to control                                                                                                 |

| J14 | SCLSR_EN1 | the LDO and SMPS power supplies.<br>Please refer details on programming the<br>internal register to achieve this function.                |

Table 9. Control Signals (continued)

If USB-to-GPIO connector is connected on J1 or J2 then the above signals can be controlled using the GPIO writes from the GUI. In this case the above jumpers should not be connected. Jumpers should be left open. In case of SLEEP and GPIO signals there will be contention for VDDIO supply. In case of PWRHOLD, the device will be damaged. This is because the PWRHOLD signal from USB-to-GPIO is at 3.3V. The HI side of J20 jumper is connected to VRRTC. If VRRTC is shorted to 3.3V then this will damage the device. When the adapter is connected all IOs should be at 3.3V, so ensure J11 is connected between VDDIO and 3.3V.

# 4.2 Test Point Descriptions

| Power Domain/Control | TP    | Label       | Use                           |

|----------------------|-------|-------------|-------------------------------|

| VIO                  | J39   | VIO_OUT     | Monitor VIO output voltage    |

| VDD1                 | J35   | VDD1        | Monitor VDD1 output voltage   |

| VDD2                 | J37   | VDD2        | Monitor VDD2 output voltage   |

| VDD3                 | J33   | VDD3        | Monitor VDD3 output voltage   |

| VPLL                 | J25   | VPLL        | Monitor VPLL output voltage   |

| VDAC                 | J24   | VDAC        | Monitor VDAC output voltage   |

| VAUX1                | J26   | VAUX1       | Monitor VAUX1 output voltage  |

| VAUX2                | J27   | VAUX2       | Monitor VAUX2 output voltage  |

| VMMC                 | J28   | VMMC        | Monitor VMMC output voltage   |

| VAUX33               | J29   | VAUX33      | Monitor VAUX33 output voltage |

| VDIG1                | J30   | VDIG1       | Monitor VDIG1 output voltage  |

| VDIG2                | J31   | VDIG2       | Monitor VDIG2 output voltage  |

| VREF                 | J15   | VREF        | Monitor VREF output voltage   |

| VRRTC                | J23   | VRRTC       | Monitor VRRTC output voltage  |

| PWRHOLD              | J20-2 | PWRHOLD     | Monitor PWRHOLD level         |

| PWON                 | S1    | POWER ON    | Power-on switch               |

| SLEEP                | J19-2 | SLEEP       | Control device status         |

| GPIO/CKSYN           | J18-2 | GPIO/CKSYNC | GPIO test point               |

| NRESPWRON            | TP5   | NRESPWON    | Reset to processor            |

| INT1                 | TP4   | INT1        | Interrupt to processor        |

| CLK32KOUT            | TP6   | CLK32KOUT   | 32KHz to processor            |

#### Table 10. Test Point Descriptions

Use J32 for all GND connections for measuring the LDO power supplies. J34, J36, J38, and J40 can be used for ground connections for measuring DCDC power supplies.

# 5 Test Set Up

# 5.1 Equipment

Recommended test equipments:

• Variable 6-V power supply capable of supplying 6 A current

Test Set Up

www.ti.com

- Voltmeter

- Oscilloscope

- Windows PC with a universal serial bus (USB) port

- USB-to-GPIO converter

# 6 GUI Information

The GUI accompanying this device is fairly simple. It runs on a Windows PC. Ensure that your machine supports Microsoft .NET Framework 3.5.

# 6.1 Installation Instructions:

To install the GUI follow these steps:

- 1. Download from site/Insert CD (based on how we package the GUI).

- 2. Create a new folder or unzip into any appropriate windows folder. If it is an exe, then select the location. The default is C:/xyz/.

# 6.2 Know the Files

GUI software consists of the following files:

- DLL

- EXE

- XML

The GUI can be opened by clicking the MS Installer, TPS65910.msi file. The .xml file is the main file that contains all the device registers. The registers in this file are categorized in blocks according to the functions. The .xml file also specifies the slave I<sup>2</sup>C address for the device.

# 6.3 GUI Description

GUI windows are divided into the following sections:

# 6.3.1 Register Properties

The following blocks are on the GUI on the left-side pane under Register Properties:

- Time and Calendar Registers

- RTC Registers

- Back-up Registers

- DCDC Control Registers

- LDO Control Registers

- Device Control Registers

- Interrupts and GPIO Registers

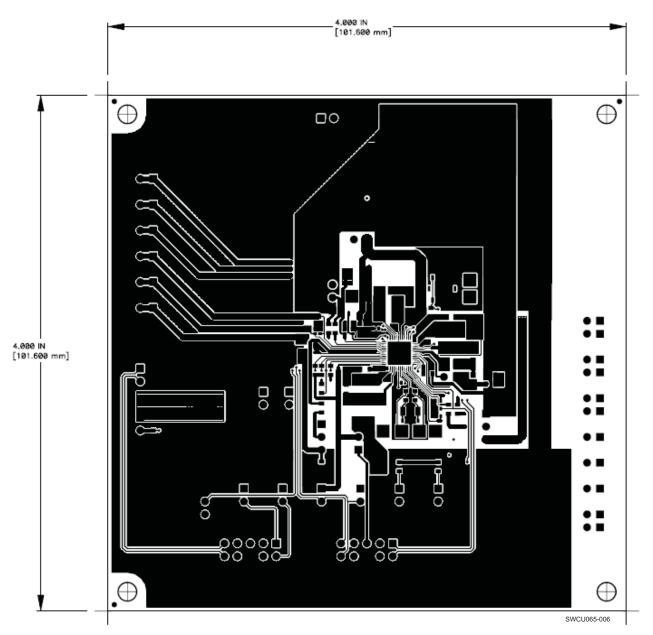

Figure 2 shows a sample snapshot of the GUI.

Each block can be selected independently so that it appears on the main GUI window. Each register instance appears in a separate block. See Figure 3.

The user can write to the registers through the l<sup>2</sup>C bus. Each bit in the 8-bit register can be written independently or the complete register can be written using an 8-bit hexadecimal value in the Value field. Individual bits can be toggled either by selecting the drop-down menu or by double-clicking the field.

**GUI** Information

#### GUI Information

🚼 EVM Test Bench - C:\Gandhar\MIS\Sup rt\Gaia\Docs\TP\$65910\EVM Process Test\FastEVM\FastEVM\_v\_21Jan2010\trial\_modified.xm X El Constanti de la Const Elle View I/O Help 0x0 | Protocol: I2C + | Read All | Write Data: C DAYS\_REG (0x30x1) MINUTES\_REG (0x1:0x0) HOURS\_REG (0x2.0x0) SECONDS\_REG (0x0.0x0) ≣≣⊉↓ ⊟Bits 81 **2**1 El 21 El Bits 🗆 Bits 7. Perserved

6: MIN1

5: MIN1

4: MIN1

3: MIN0

2: MIN0

1: MIN0

0: MIN0

Value

E Register

Register

Register 6: Reservi 5: DAY1 4: DAY1 3: DAY0 2: DAY0 1: DAY0 0: DAY0 0: DAY0 Value Register Register Value Begister B Register Address Read Interval Write Interval Address Read Interval Write Interval Read Interval Write Interval Read Interval Write Interval 7: Reserved\_7\_7 Read Only Reserved bit 7: Reserved\_7\_7 Read Only Reserved bit 7: PM\_nAM Read Only First digit of minutes (range is 0 up to 9) 7: Reserved\_7\_6 Read Only Reserved bit Read Write Read Write Read Write Read Write MONTHS REG (0x4:0x1) YEARS REG (0x5:0x0) WEEKS REG (0x6:0x0) ALARM SECONDS REG (0x8:0x0) 21 🖾 21 🔤 21 21 🔤 21 🖾 🗄 Bits 🗄 Bits 🖽 Bits 🕀 Bits 10.5456 (0.020 bd) 10.7456 (0.020 bd) D01.07.856 (0.020 bd) D01.07.856 (0.020 bd) D01.07.856 (0.020 bd) D01.07.856 (0.020 bd) D02.7456 (0.020 bd) D02 ontrol Registers REG (0x20:0x0) 6 ALARM\_SEC1 5 ALARM\_SEC1 4 ALARM\_SEC1 3 ALARM\_SEC1 2 ALARM\_SEC0 1: ALARM\_SEC0 0 ALARM\_SEC0 Value 5: Reserved 4: MONTH1 3: MONTH0 2: MONTH0 1: MONTH0 0: MONTH0 Value 3 Reserve 2 WEEK 1: WEEK 0 WEEK Value Value Begister Begister Begister Register 22 Read Interval Write Interval Block Read Interval Write Interval Read Interval Write Interval Read Interval Write Interval 7: YEAR1 Read Only Second digit of years (range is 0 up to 9) 7: Reserved\_7\_7 Read Only Reserved bit 7: Reserved\_7\_5 Read Only Reserved bit 7: Reserved\_7\_3 Read Only Reserved bit THERM\_REG (0x38:0xD) Read Write Read Write Read Write Read Write 8 Register Properties 📑 Register Map ALARM\_HOURS\_REG (0xA:0x0) ALARM\_DAYS\_REG (0x8:0x1) ALARM\_MONTHS\_REG (0xC:0x1) ALARM\_MINUTES\_REG (0x9.0x0) 21 🖂 🔠 **2** l 📨 21 🖂 21 Modes Log Texas Instruments SWCU065-002 ... DI.

Figure 2. GUI Snapshot – Register Properties

|   | NUTES_REG (0x1:0x0)—<br>                  |                             |

|---|-------------------------------------------|-----------------------------|

| _ | Bits                                      |                             |

|   | 7: Reserved_7_7                           | 0                           |

|   | 6: MIN1                                   | 0                           |

|   | 5: MIN1                                   | 0                           |

|   | 4: MIN1                                   | 0                           |

|   | 3: MIN0                                   | 0                           |

|   | 2: MIN0                                   | 0                           |

|   | 1: MIN0                                   | 0                           |

|   | 0: MINO                                   | 0                           |

|   | Value                                     | 0x0                         |

| Ξ | Register                                  |                             |

|   | Register                                  | MINUTES_REG                 |

|   | Address                                   | 0x1                         |

|   | Read Interval                             | 0                           |

|   | Write Interval                            | 0                           |

|   | Block                                     | Time and Calendar Registers |

| R | : Reserved_7_7<br>ead Only<br>eserved bit |                             |

|   | Read                                      | Write                       |

Figure 3. Single Register Instance

# 6.3.2 Register Map

Figure 4 shows the register map view. The Register Map tab provides an alternative way to access the device registers. Also in this view, the bits and complete words can be read or written through the l<sup>2</sup>C bus.

**GUI** Information

|                                                                                       | wort\Gaia\Docs\TP\$65910\EVM Process Test\FastEVM\FastEVM_v_2'           | 1                           |  |                     |

|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------|--|---------------------|

| File View D/O Help                                                                    | 00T1GalaW0CS11P5639101EYM Process_lest(rastEym\rastEym_v_z               | Jan 2010 (that_modified.xm) |  |                     |

|                                                                                       | s: 0x0 Protocol: I2C + Read All Write All Burst Read + Address:          | Data:                       |  |                     |

|                                                                                       | St. Did   Protocol: 12C +   Read Air   Write Air   Burst Read + Address: |                             |  |                     |

| Time and Calendar Registers     SECONDS_REG (0x0.0x0)                                 | RTC_CTRL_REG (0x10) 7 6 5 4 3 2 1 0                                      |                             |  |                     |

| MINUTES_REG (0x1:0x7F)                                                                | R W MO 0 0 0 0 0 0 0 0                                                   |                             |  |                     |

| - HOURS_REG (0x2:0x0)                                                                 |                                                                          |                             |  |                     |

| <ul> <li>DAYS_REG (0x3:0x1)</li> <li>MONTHS_REG (0x4:0x1)</li> </ul>                  | RTC_STATUS_REG (0x11) 7 6 5 4 3 2 1 0                                    |                             |  |                     |

| YEARS_REG (0x50x0)                                                                    | R W 0x80 1 0 0 0 0 0 0                                                   |                             |  |                     |

| WEEKS_REG (0x6:0x0)                                                                   | RTC_INTERRUPTS_RE                                                        |                             |  |                     |

| - ALARM_SECONDS_REG (0x8.0x0)<br>- ALARM MINUTES REG (0x8.0x0)                        | 7 6 5 4 3 2 1 0                                                          |                             |  |                     |

| ALARM_HOURS_REG (0xA-0x0)                                                             | R W M 0 0 0 0 0 0 0 0                                                    |                             |  |                     |

| ALARM_DAYS_REG (0x8:0x1)     ALARM_MONTHS_REG (0x6:0x1)                               | RTC_COMP_LSB_REG (0 7 6 5 4 3 2 1 0                                      |                             |  |                     |

| ALARM_MONTHS_HEG (000:0x1)                                                            |                                                                          |                             |  |                     |

| RTC Registers                                                                         |                                                                          |                             |  |                     |

| <ul> <li>RTC_CTRL_REG (0x10:0x0)</li> <li>RTC_STATUS_REG (0x11:0x80)</li> </ul>       | RTC_COMP_MSB_REG [ 7 6 5 4 3 2 1 0                                       |                             |  |                     |

| - RTC_INTERRUPTS_REG (0x12:0x0)                                                       | R W M 0 0 0 0 0 0 0 0                                                    |                             |  |                     |

| - RTC_COMP_LSB_REG (0x13:0x0)                                                         |                                                                          |                             |  |                     |

| <ul> <li>RTC_COMP_MSB_REG (0x14:0x0)</li> <li>RTC_RES_PROG_REG (0x15:0x27)</li> </ul> | RTC_RES_PROG_REG [ 7 6 5 4 3 2 1 0                                       |                             |  |                     |

| RTC_RESET_STATUS_REG (0x16:0x1                                                        | R W 0x27 0 0 1 0 0 1 1 1                                                 |                             |  |                     |

| Back-up Registers                                                                     | RTC_RESET_STATUS                                                         |                             |  |                     |

| <ul> <li>BCK1_REG (0x17:0x0)</li> <li>BCK2_REG (0x18:0x0)</li> </ul>                  | 7 6 5 4 3 2 1 0                                                          |                             |  |                     |

| BCK3_REG (0x19:0x0)                                                                   | R W M 0 0 0 0 0 0 0 0                                                    |                             |  |                     |

| <ul> <li>BCK4_REG (0x1A:0x0)</li> <li>BCK5 REG (0x1B:0x0)</li> </ul>                  | BCK1 REG (0x17) 7 6 5 4 3 2 1 0                                          |                             |  |                     |

| V PUADEN REG (0x10:0x9F)                                                              |                                                                          |                             |  |                     |

| - REF_REG (0x1D:0x1)                                                                  |                                                                          |                             |  |                     |

| VRTC_REG (0x1E:0x1)                                                                   | BCK2_REG (0x18) 7 6 5 4 3 2 1 0                                          |                             |  |                     |

| - VIO_REG (0x20:0x0)                                                                  | R W 040 0 0 0 0 0 0 0 0                                                  |                             |  |                     |

| <ul> <li>VDD1_REG (0x21:0xC)</li> <li>VDD1_OP_REG (0x22:0x0)</li> </ul>               |                                                                          |                             |  |                     |

| VDD1_0P_REG (0x22:00)                                                                 | BCK3_REG (0x19) 7 6 5 4 3 2 1 0                                          |                             |  |                     |

| - VDD2_REG (0x24:0x4)                                                                 | R W M 0 0 0 0 0 0 0 0 0                                                  |                             |  |                     |

| - VDD2_OP_REG (0x25.0x0)<br>- VDD2_SR_REG (0x26.0x0)                                  | BCK4 BEG (0:1A) 7 6 5 4 3 2 1 0                                          |                             |  |                     |

| VDD3_REG (0x27:0x4)                                                                   | BCK4_REG (0x1A) 7 6 5 4 3 2 1 0<br>R W 0x0 0 0 0 0 0 0 0 0 0             |                             |  |                     |

| UDO Control Registers                                                                 |                                                                          |                             |  |                     |

| <ul> <li>VDIG1_REG (0x30:0x0)</li> <li>VDIG2_REG (0x31:0x0)</li> </ul>                | BCK5_REG (0x1B) 7 6 5 4 3 2 1 0                                          |                             |  |                     |

| - VALX1_REG (0x32:0x0)                                                                | R W 0x0 0 0 0 0 0 0 0 0                                                  |                             |  |                     |

| <ul> <li>VALK2_REG (0x33:0x0)</li> <li>VALK33_REG (0x34:0x0)</li> </ul>               |                                                                          |                             |  |                     |

| VAUX33_HEG (0x34:0x0)                                                                 | PUADEN_REG (0x10) 7 6 5 4 3 2 1 0                                        |                             |  |                     |

| - VPLL_REG (0x36:0x0)                                                                 | R W 0x8F 1 0 0 1 1 1 1 1                                                 |                             |  |                     |

| VDAC_REG (0x37:0x0)                                                                   |                                                                          |                             |  |                     |

| - F THERM REG (0x38:0xD)                                                              | REF_REG (0x1D) 7 6 5 4 3 2 1 0                                           |                             |  |                     |

|                                                                                       | R W M 0 0 0 0 0 0 1                                                      |                             |  |                     |

| Register Properties                                                                   | VRTC_REG (0x1E) 7 6 5 4 3 2 1 0                                          |                             |  |                     |

|                                                                                       |                                                                          |                             |  |                     |

| Register Map                                                                          |                                                                          |                             |  |                     |

| Modes                                                                                 | VI0_REG (0x20) 7 6 5 4 3 2 1 0                                           |                             |  |                     |

| _ Log                                                                                 |                                                                          |                             |  | Log                 |

| evice Disconnected                                                                    | · ·                                                                      |                             |  | V Texas Instruments |

SWCU065-004

Figure 4. Register Map View

#### 6.3.3 Modes

This section is used for executing multiple register writes in a single step. For example, to configure the device in SLEEP state, multiple bits must be configured for SMPS and LDO supplies. An example is provided in the .xml file that comes with the GUI package.

Users can create their own sequences in the .xml file.

#### 6.3.4 I/O writes

Three control signals for the TPS65910 (SLEEP, PWRHOLD and GPIO) can be altered using the GUI. To select these signals, the user can use the I/O Flag tab on the menu bar. For mapping of the I/O lines, refer to the TPS65910 schematic and datasheet for the GPIO-to-USB adapter at http://focus.ti.com/docs/toolsw/folders/print/usb-to-gpio.html.

# 7 EVM Assembly Drawings and Layout

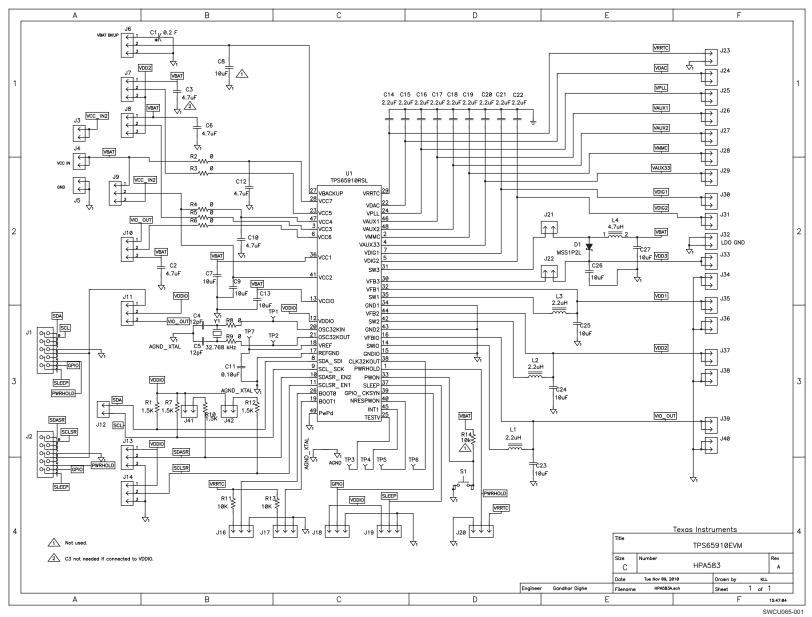

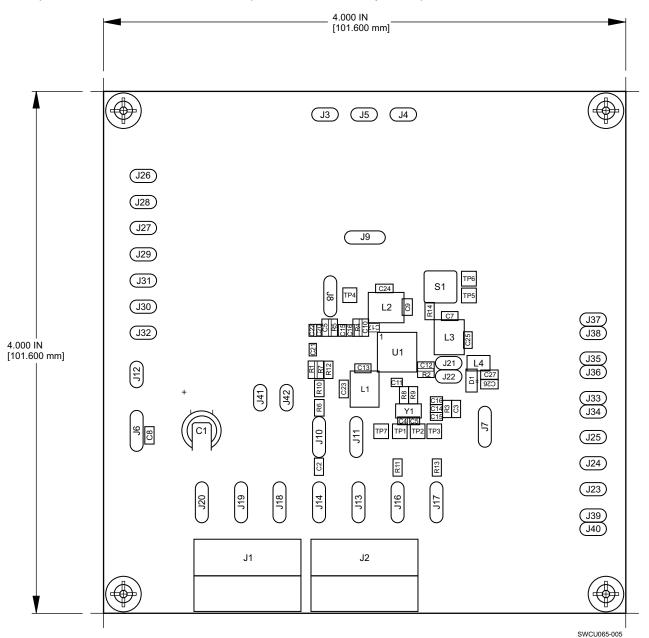

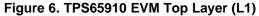

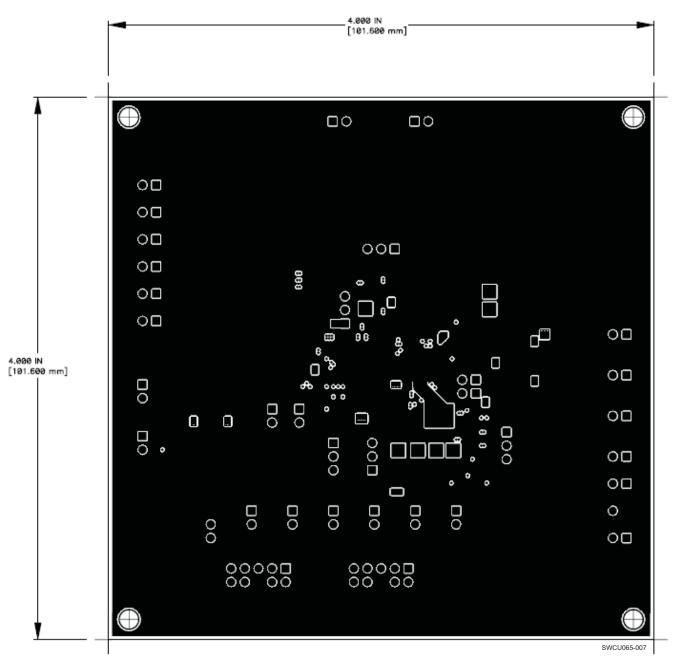

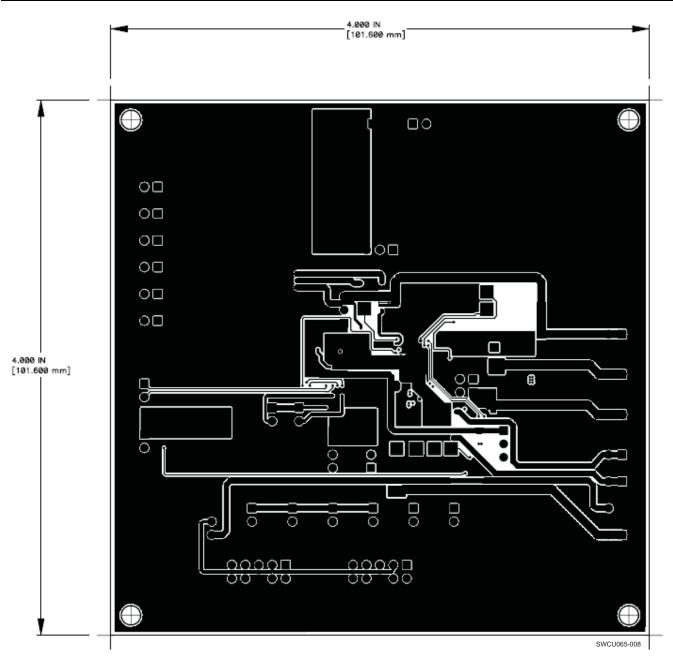

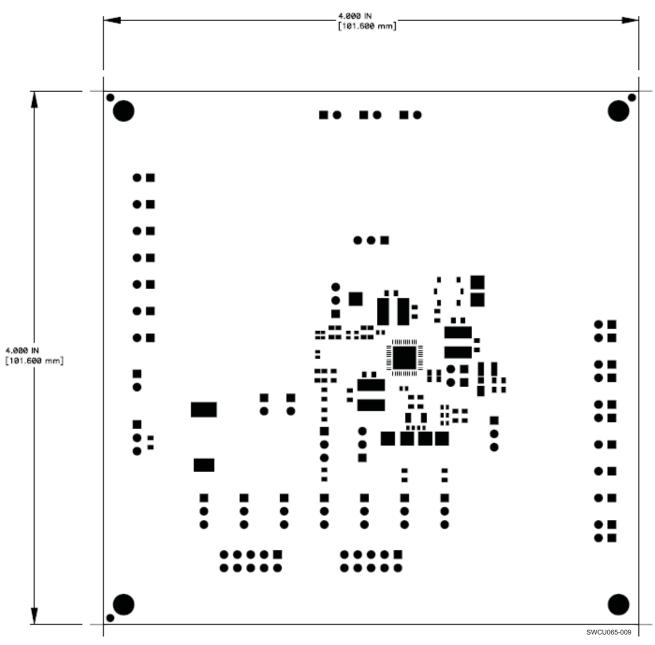

The following figures show the design of the TPS65910 EVM printed circuit board. The EVM has been designed using a 4-layer, 2-ounce, 4-inch × 4-inch copper-clad circuit board with all components on the top side and all active traces to the top to let the user easily view, probe, and evaluate the TPS65910 IC.

Figure 5. TPS65910 EVM Component Placement With Silkscreen Labels

List of Materials

# 8 List of Materials

Table 11 lists the EVM components as configured according to the schematic shown in Figure 1.

| COUNT | REFDES                                                                                                                                                | VALUE       | DESCRIPTION                                                           | SIZE                  | PART NUMBER                          | MFR         |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------|-----------------------|--------------------------------------|-------------|

| 1     | C1                                                                                                                                                    | 0.2 F       | Capacitor,<br>Electric Double<br>Layer                                | AK                    | EECEN0F204AK                         | Panasonic   |

| 1     | C11                                                                                                                                                   | 0.10 µF     | Capacitor,<br>Ceramic, 10 V,<br>X5R, 10%                              | 0402                  | STD                                  | {MFR}       |

| 9     | C14, C15, C16,<br>C17, C18, C19,<br>C20, C21, C22                                                                                                     | 2.2 µF      | Capacitor,<br>Ceramic, 6.3 V,<br>X5R, 20%                             | 0402                  | JMK105BJ225M<br>V-F                  | Taiyo Yuder |

| 5     | C2, C3, C6, C10,<br>C12                                                                                                                               | 4.7 μF      | Capacitor,<br>Ceramic, 6.3 V,<br>X5R, 20%                             | 0603                  | JMK107BJ475K<br>A-T                  | Taiyo Yuder |

| 2     | C4, C5                                                                                                                                                | 12 pF       | Capacitor,<br>Ceramic, vvV,<br>[temp], [tol]                          | 0402                  | {Part Number}                        | {MFR}       |

| 9     | C7, C8, C9, C13,<br>C23, C24, C25,<br>C26, C27                                                                                                        | 10 µF       | Capacitor,<br>Ceramic, 6.3 V,<br>X5R, 20%                             | 0603                  | C0603C106M9P<br>AC                   | Kemet       |

| 1     | D1                                                                                                                                                    | MSS1P2L     | Diode, Schottky,<br>20 V, 1 A                                         | MicroSMP              | MSS1P2L                              | Vishay      |

| 2     | J1, J2                                                                                                                                                | 2510-5002UB | Connector, Male<br>Right Angle<br>2x5 pin, 100 mil<br>spacing, 4 Wall | 0.100 inch x 2X5      | 2510-5002UB                          | ЗM          |

| 26    | J3, J4, J5, J12,<br>J21, J22, J23,<br>J24, J25, J26,<br>J27, J28, J29,<br>J30, J31, J32,<br>J33, J34, J35,<br>J36, J37, J38,<br>J39, J40, J41,<br>J42 | PEC02SAAN   | Header, Male 2-<br>pin, 100 mil<br>spacing                            | 0.100 inch x 2        | PEC02SAAN                            | Sullins     |

| 13    | J6, J7, J8, J9,<br>J10, J11, J13,<br>J14, J16, J17,<br>J18, J19, J20                                                                                  | PEC03SAAN   | Header, Male 3-<br>pin, 100 mil<br>spacing                            | 0.100 inch x 3        | PEC03SAAN                            | Sullins     |

| 3     | L1, L2, L3                                                                                                                                            | 2.2 µH      | Inductor, SMT,<br>2.6 A, 58 mΩ                                        | 0.157 x 0.157<br>inch | VLCF5020T-<br>2R2N2R6-3              | TDK         |

| 1     | L4                                                                                                                                                    | 4.7 µH      | Inductor, SMT<br>Multi-layer, 1 A,                                    | 2520 mm               | MIPF2520D4R7<br>S<br>Alternate part: | FDK         |

|       |                                                                                                                                                       |             | 110 mΩ                                                                |                       | LQM2HPN4R7M<br>G0L                   | Murata      |

| 4     | R1, R7, R10,<br>R12                                                                                                                                   | 1.5 kΩ      | Resistor, Chip,<br>1/16 W, 5%                                         | 0603                  | STD                                  | STD         |

| 2     | R11, R13                                                                                                                                              | 10 kΩ       | Resistor, Chip,<br>1/16 W, 5%                                         | 0603                  | STD                                  | STD         |

|       | R14                                                                                                                                                   | 10 kΩ       | Resistor, Chip,<br>1/16 W, 5%                                         | 0603                  | STD                                  | STD         |

| 7     | R2, R3, R4, R5,<br>R6, R8, R9                                                                                                                         | 0           | Resistor, Chip,<br>1/16 W, 5%                                         | 0603                  | STD                                  | STD         |

| 1     | S1                                                                                                                                                    | EVQ-PLHA15  | Switch, 1P1T, 50 mA, 12 V, 160 g                                      | 0.200 x 0.200<br>inch | EVQ-PLHA15                           | Panasonic   |

| 1     | SH1                                                                                                                                                   |             | Short jumper                                                          |                       |                                      |             |

# Table 11. TPS65910 EVM Bill of Materials

| COUNT | REFDES                                  | VALUE       | DESCRIPTION                           | SIZE           | PART NUMBER | MFR           |

|-------|-----------------------------------------|-------------|---------------------------------------|----------------|-------------|---------------|

| 7     | TP1, TP2, TP3,<br>TP4, TP5, TP6,<br>TP7 | PEC01SAAN   | Through Hole,<br>0.040 Diameter       |                | PEC01SAAN   | Sullins       |

| 1     | U1                                      | TPS65910RSL | IC, Integrated<br>Power<br>Management | QFN            | TPS65910RSL | TI            |

| 1     | Y1                                      | 32.768 kHz  | Crystal                               | 1.50 x 3.20 mm | FC-135      | Epson Toyocom |

Table 11. TPS65910 EVM Bill of Materials (continued)

NOTE: These assemblies are ESD sensitive, ESD precautions must be observed.

These assemblies must be clean and free from flux and all contaminants. Use of contaminated flux is not acceptable.

These assemblies must comply with workmanship standards IPC-A-610 Class 2.

Reference designators marked with an asterisk (\*\*) cannot be substituted. All other components can be substituted with equivalent manufacturer's components.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ectivity                      |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated