### OVERVOLTAGE AND OVERCURRENT PROTECTION IC AND Li+ CHARGER FRONT-END PROTECTION IC

Check for Samples: bq24300 bq24304 bq24305

#### **FEATURES**

- · Provides Protection for Three Variables:

- Input Overvoltage

- Input Overcurrent with Current Limiting

- Battery Overvoltage

- 30V Maximum Input Voltage

- Optional Input Reverse Polarity Protection

- High Immunity Against False Triggering Due to Voltage Spikes

- Robust Against False Triggering Due to Current Transients

- Thermal Shutdown

- Enable Function

- Small 2 mm x 2 mm 8-Pin SON Package

- LDO Mode Voltage Regulation Options:

- 5.5V on bq24300

- 4.5V on bq24304

- 5.0V on bq24305

#### **APPLICATIONS**

- · Bluetooth Headsets

- Low-Power Handheld Devices

#### DESCRIPTION

The bq24300 and bq24304 are highly integrated circuits designed to provide protection to Li-ion batteries from failures of the charging circuit. The IC continuously monitors the input voltage, the input current, and the battery voltage. The device operates like a linear regulator: for voltages up to the Input Overvoltage threshold, the output is held at 5.5V (bq24300), 5.0V (bq24305) or 4.5V (bq24304). In case of an input overvoltage condition, if the overvoltage condition persists for more than a few microseconds, the IC removes power from the charging circuit by turning off an internal switch. In the case of an overcurrent condition, it limits the current to a safe value for a blanking duration before turning the switch off. Additionally, the IC also monitors its own die temperature and switches off if it becomes too hot.

The IC also offers optional protection against reverse voltage at the input with an external P-channel MOSFET.

####

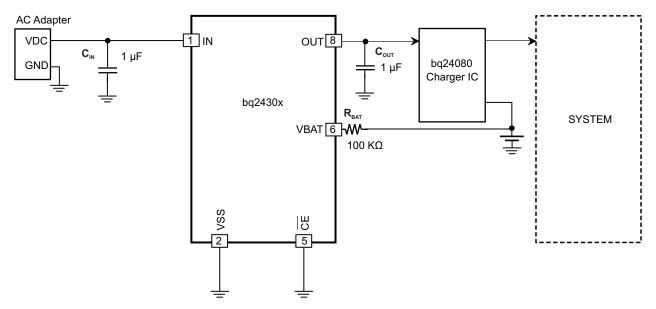

## APPLICATION SCHEMATIC AC Adapter VDC GND 1 μF 1

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### ORDERING INFORMATION(1)

| DEVICE <sup>(2)</sup> | OUTPUT REGULATION VOLTAGE | PACKAGE       | MARKING |

|-----------------------|---------------------------|---------------|---------|

| bq24300               | 5.5V                      | 2mm x 2mm SON | BZA     |

| bq24304               | 4.5V                      | 2mm x 2mm SON | CBS     |

| bq24305               | 5.0V                      | 2mm x 2mm SON | DSG     |

- (1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

- (2) To order a 3000 pcs reel add R to the part number, or to order a 250 pcs reel add T to the part number.

#### **PACKAGE DISSIPATION RATINGS**

| PACKAGE | $R_{\theta JC}$ | R <sub>eJA</sub> <sup>(1)</sup> |

|---------|-----------------|---------------------------------|

| DSG     | 5°C/W           | 75°C/W                          |

<sup>(1)</sup> This data is based on using the JEDEC High-K board and the exposed die pad is connected to a Cu pad on the board. The pad is connected to the ground plane by a 2x3 via matrix.

#### ABSOLUTE MAXIMUM RATINGS(1)

over operating free-air temperature range (unless otherwise noted)

| PARAMETER                            | PIN                                                                                    | VALUE                             | UNIT |

|--------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------|------|

|                                      | IN, PGATE (with respect to VSS)                                                        | -0.3 to 30                        | V    |

| Input voltage                        | OUT (with respect to VSS)                                                              | -0.3 to 12                        | V    |

|                                      | CE, VBAT (with respect to VSS)                                                         | -0.3 to 7                         | V    |

|                                      | All (Human Body Model per JESD22-A114-E)                                               | 2000                              | V    |

|                                      | All (Machine Model per JESD22-A115-A)                                                  | 200                               | V    |

| ESD Withstand voltage                | All (Charged Device Model per JESD22-C101-C)                                           | 500                               | V    |

|                                      | IN (IEC 61000-4-2) (with IN pin bypassed to VSS with 1.0-μF low-ESR ceramic capacitor) | 15 (Air Discharge) 8<br>(Contact) | kV   |

| Junction temperature, T <sub>J</sub> |                                                                                        | -40 to 150                        | °C   |

| Storage temperature, T <sub>S1</sub> | r <sub>G</sub>                                                                         | -65 to 150                        | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                 |                      | , |     |     |      |

|-----------------|----------------------|---|-----|-----|------|

|                 |                      |   | MIN | MAX | UNIT |

| $V_{\text{IN}}$ | Input voltage range  |   | 3.3 | 26  | V    |

| $T_{J}$         | Junction temperature |   | 0   | 125 | °C   |

Submit Documentation Feedback

#### **ELECTRICAL CHARACTERISTICS**

over junction temperature range  $0^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}$  and recommended supply voltage (unless otherwise noted)

|                          | PARAMETER                      |                     | TEST CONDITIONS                                                                                                                                               | MIN  | TYP  | MAX         | UNIT |

|--------------------------|--------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------------|------|

| POWER-ON-I               | RESET                          |                     |                                                                                                                                                               |      |      |             |      |

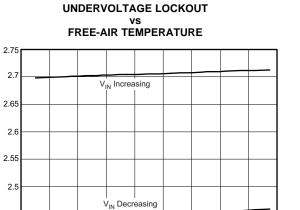

| UVLO                     | Under-voltage power detected   |                     | CE = Low, V <sub>IN</sub> increasing from 0V to 3V                                                                                                            | 2.5  | 2.7  | 2.8         | V    |

| V <sub>HYS-UVLO</sub>    | Hysteresis on                  | UVLO                | CE = Low, V <sub>IN</sub> decreasing from 3V to 0V                                                                                                            | 200  | 260  | 300         | mV   |

| t <sub>DGL(PGOOD)</sub>  | Deglitch time, detected status |                     | $\overline{\text{CE}}$ = Low, time measured from $V_{\text{IN}}$ 0V $\rightarrow$ 4V 1µs rise time, to output turning ON                                      |      | 8    |             | ms   |

| IN                       |                                |                     |                                                                                                                                                               |      |      |             |      |

|                          | Operating                      | bq24300             |                                                                                                                                                               |      | 340  | 400         |      |

| I <sub>DD</sub>          | current                        | bq24304,<br>bq24305 | $V_{IN} = 5V$ , $\overline{CE} = Low$ , no load on OUT pin                                                                                                    |      | 410  | 500         | μA   |

| I <sub>STDBY</sub>       | Standby currer                 | nt                  | $\overline{\text{CE}} = \text{High}, \ V_{\text{IN}} = 5\text{V}$                                                                                             |      | 65   | 95          | μΑ   |

| INPUT TO OU              | JTPUT CHARACT                  | TERISTICS           |                                                                                                                                                               |      |      |             |      |

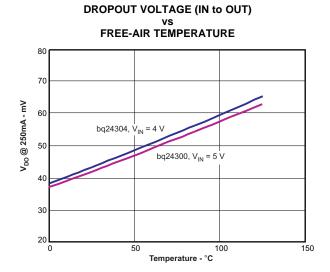

| $V_{DO}$                 | Drop-out voltag                | ge IN to OUT        | $\overline{\text{CE}}$ = Low, $V_{\text{IN}}$ = 4 V, $I_{\text{OUT}}$ = 250 mA                                                                                |      | 45   | 75          | mV   |

| OUTPUT VOL               | LTAGE REGULAT                  | TION                |                                                                                                                                                               |      |      |             |      |

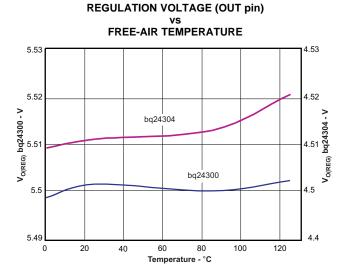

|                          | •                              | bq24300             |                                                                                                                                                               | 5.30 | 5.5  | 5.70        |      |

| $V_{O(REG)}$             | Output<br>voltage              | bq24304             | $\overline{\text{CE}}$ = Low, $V_{\text{IN}}$ = 6 V, $I_{\text{OUT}}$ = 250 mA                                                                                | 4.36 | 4.5  | 4.64        | V    |

|                          | vollago                        | bq24305             |                                                                                                                                                               | 4.85 | 5.0  | 5.15        |      |

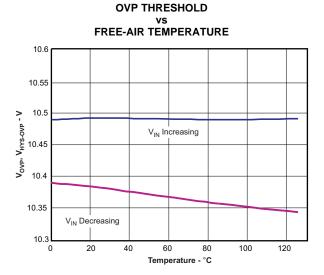

| INPUT OVER               | VOLTAGE PROT                   | ECTION              |                                                                                                                                                               |      |      |             |      |

| V <sub>OVP</sub>         | Input overvolta threshold      | age protection      | CE = Low, V <sub>IN</sub> increasing from 4V to 12V                                                                                                           | 10.2 | 10.5 | 10.8        | V    |

| V <sub>HYS-OVP</sub>     | Hysteresis on                  | OVP                 | CE = Low, V <sub>IN</sub> decreasing from 12V to 4V                                                                                                           | 60   | 100  | 160         | mV   |

| t <sub>BLANK(OVP)</sub>  | Blanking time,                 | on OVP              | $\overline{\text{CE}}$ = Low, Time measured from $V_{\text{IN}}$ 4V $\rightarrow$ 12V, 1 $\mu$ s rise time, to output turning OFF                             |      | 64   |             | μs   |

| t <sub>ON(OVP)</sub>     | Recovery time overvoltage co   |                     | $\overline{\text{CE}}$ = Low, Time measured from $V_{\text{IN}}$ 12V $\rightarrow$ 4V, 1µs fall time, to output turning ON                                    |      | 8    |             | ms   |

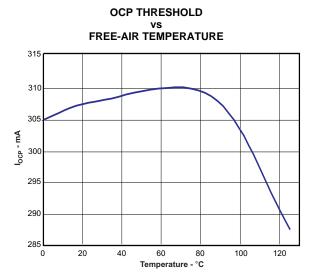

| INPUT OVER               | CURRENT PROT                   | ECTION              |                                                                                                                                                               |      |      |             |      |

| I <sub>OCP</sub>         | Input overcurre range          | ent protection      | $\overline{CE}$ = Low, V <sub>IN</sub> = 5 V                                                                                                                  | 250  | 300  | 350         | mA   |

| t <sub>BLANK</sub> (OCP) | Blanking time, overcurrent de  | •                   | CE = Low                                                                                                                                                      |      | 5    |             | ms   |

| t <sub>REC(OCP)</sub>    | Recovery time overcurrent co   |                     | CE = Low                                                                                                                                                      |      | 64   |             | ms   |

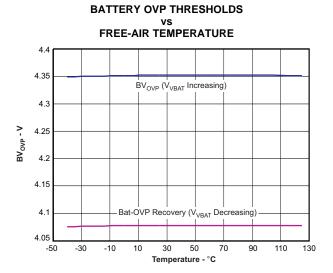

| BATTERY OV               | /ERVOLTAGE PF                  | ROTECTION           |                                                                                                                                                               |      |      |             |      |

| BV <sub>OVP</sub>        | Battery overvo protection thre |                     | $\overline{\text{CE}}$ = Low, V <sub>IN</sub> > 4.4V, V <sub>VBAT</sub> increasing from 4.2 V to 4.5 V                                                        | 4.30 | 4.35 | 4.40        | V    |

| V <sub>HYS-BOVP</sub>    | Hysteresis on                  | BV <sub>OVP</sub>   | $\overline{\text{CE}}$ = Low, V <sub>IN</sub> > 4.4V, V <sub>VBAT</sub> decreasing from 4.5 V to 3.9 V                                                        | 200  | 275  | 320         | mV   |

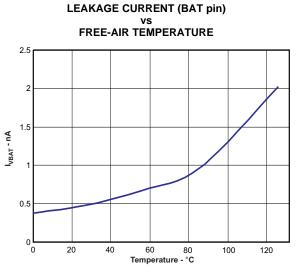

| I <sub>VBAT</sub>        | Input bias curre<br>VBAT pin   | ent on the          | V <sub>VBAT</sub> = 4.4 V, T <sub>J</sub> = 25°C                                                                                                              |      |      | 10          | nA   |

| t <sub>DGL(BOVP)</sub>   | Deglitch time, lovervoltage de |                     | $\overline{\text{CE}}$ = Low, V <sub>IN</sub> > 4.4V, time measured from V <sub>VBAT</sub> 4.2V $\rightarrow$ 4.5V, 1 $\mu$ s rise time to output turning OFF |      | 176  |             | μs   |

| P-FET GATE               | DRIVER                         |                     |                                                                                                                                                               |      |      |             |      |

| V <sub>GCLMP</sub>       | Gate driver cla                | imp voltage         | V <sub>IN</sub> > 17V                                                                                                                                         | 13   | 15   | 17          | V    |

| T <sub>J(OFF)</sub>      | Thermal shutd                  | own temperatui      | re                                                                                                                                                            |      | 140  | 150         | °C   |

| T <sub>J(OFF-HYS)</sub>  |                                | own hysteresis      |                                                                                                                                                               |      | 20   |             | °C   |

| LOGIC LEVE               |                                | ,                   |                                                                                                                                                               |      | -    |             |      |

| V <sub>IL</sub>          | Low-level inpu                 | t voltage           |                                                                                                                                                               | 0    |      | 0.4         | V    |

| V <sub>IH</sub>          | High-level inpu                |                     |                                                                                                                                                               | 1.4  |      | <b>0.</b> T | V    |

| · III                    | Low-level inpu                 |                     |                                                                                                                                                               |      |      | 1           | μA   |

#### **ELECTRICAL CHARACTERISTICS (continued)**

over junction temperature range 0°C ≤ T<sub>J</sub> ≤ 125°C and recommended supply voltage (unless otherwise noted)

| PARAMETER       |                          | TEST CONDITIONS        | MIN | TYP | MAX | UNIT |

|-----------------|--------------------------|------------------------|-----|-----|-----|------|

| I <sub>IH</sub> | High-level input current | V <sub>CE</sub> = 1.8V |     |     | 15  | μA   |

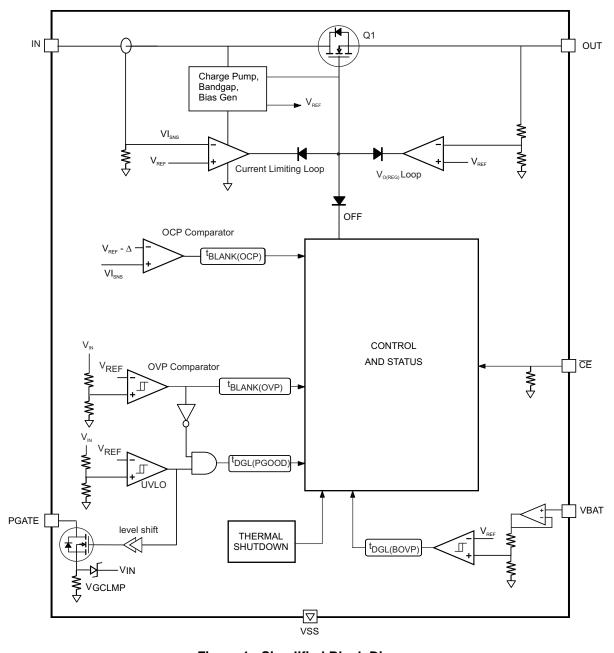

Figure 1. Simplified Block Diagram

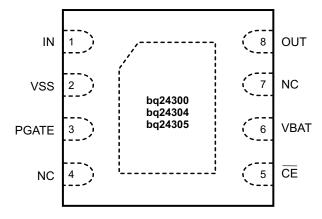

#### **TERMINAL FUNCTIONS**

| TERMINAL   |               | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                             |

|------------|---------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME       | NO.           | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                             |

| IN         | 1             | ı   | Input power, connect to external DC supply. Connect external 0.1µF (minimum) ceramic capacitor to VSS                                                                                                                                                                                                                                   |

| VSS        | 2             | -   | Ground terminal                                                                                                                                                                                                                                                                                                                         |

| PGATE      | 3             | 0   | Gate drive for optional external P-FET                                                                                                                                                                                                                                                                                                  |

| NC         | 4, 7          |     | Do not connect to any external circuit. These pins may have internal connections used for test purposes.                                                                                                                                                                                                                                |

| CE         | 5             | I   | Chip enable input. Active low. When $\overline{CE}$ = Hi, the input FET is off. Internally pulled down.                                                                                                                                                                                                                                 |

| VBAT       | 6             | 1   | Battery voltage sense input. Connect to pack positive terminal through a resistor.                                                                                                                                                                                                                                                      |

| OUT        | 8             | 0   | Output terminal to the charging system. Connect external 1µF capacitor (minimum) ceramic capacitor to VSS                                                                                                                                                                                                                               |

| Thermal PA | Thermal PAD – |     | There is an internal electrical connection between the exposed thermal pad and the VSS pin of the device. The thermal pad must be connected to the same potential as the VSS pin on the printed circuit board. Do not use the thermal pad as the primary ground input for the device. VSS pin must be connected to ground at all times. |

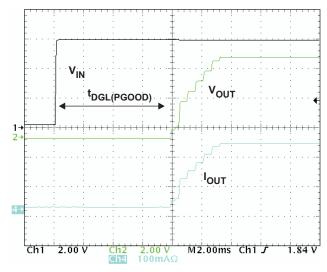

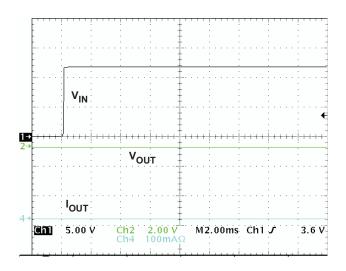

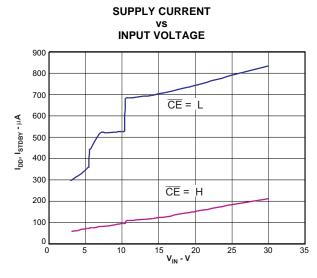

#### TYPICAL OPERATING PERFORMANCE

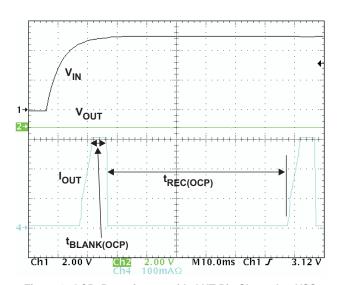

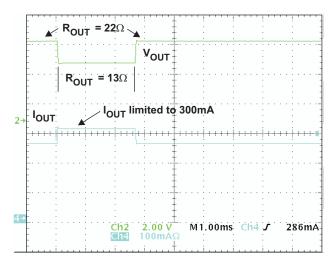

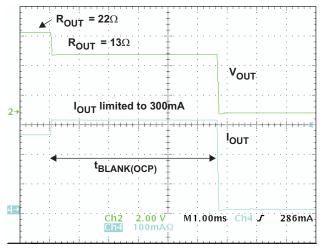

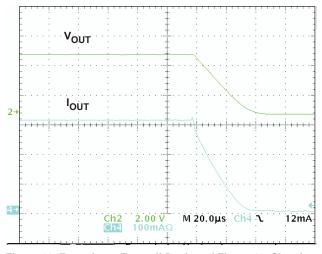

Test conditions (unless otherwise noted) for typical operating performance are:  $V_{IN} = 5$  V,  $C_{IN} = 1$   $\mu F$ ,  $C_{OUT} = 1\mu F$ ,  $R_{BAT} = 100$  k $\Omega$ ,  $R_{OUT} = 22\Omega$ ,  $R_{A} = 25$ °C (see Figure 22 - Typical Application Circuit)

Figure 2. Normal Power-On Showing Soft-Start.  $V_{IN}$  0 V to 6.0 V,  $t_R$  = 20  $\mu s$

Figure 3. Power-On with Input Overvoltage.  $V_{IN}$  0 V to 12.0 V,  $t_R$  = 50  $\mu s$

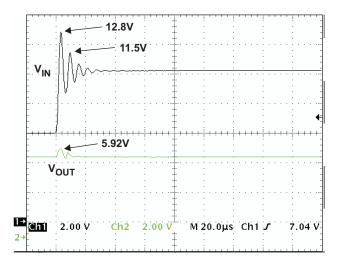

Figure 4. bq24300 OVP Response for Input Step.  $V_{IN}$  6.0 V to 10.3 V,  $t_R$  = 2 $\mu s$  . Shows Immunity to Ringing

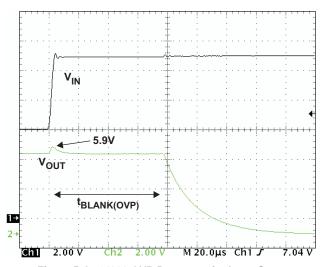

Figure 5. bq24300 OVP Response for Input Step.  $V_{IN}$  6.0 V to 11.0 V,  $t_R$  = 5µs. Shows OVP Blanking Time

#### TYPICAL OPERATING PERFORMANCE

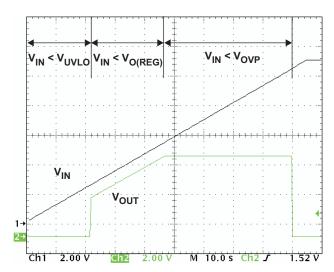

Figure 6. OUT Pin Response to Slow Input Ramp

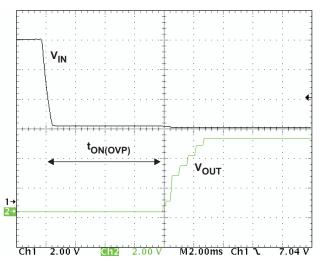

Figure 7. bq24300 Recovery from Input OVP.  $V_{IN}$  11.0 V to 5.0 V,  $t_F$  = 400  $\mu s$

Figure 8. OCP, Powering up with OUT Pin Shorted to VSS

Figure 9. OCP, Showing Current Limiting and OCP Blanking.  $R_{OUT}$  22 $\Omega$  to  $13\Omega$  for 2.6 ms to  $22\Omega$

#### **TYPICAL OPERATING PERFORMANCE (continued)**

Figure 10. OCP, Showing Current Limiting and OCP Blanking.  $R_{OUT}$  22 $\Omega$  to 13 $\Omega$

Figure 11. Zoom-in on Turn-off Region of Figure 10, Showing Soft-Stop

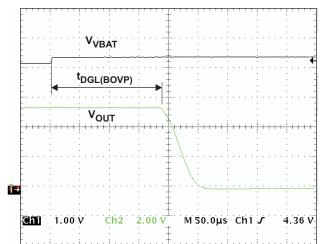

Figure 12. Battery OVP.  $V_{VBAT}$  Steps from 4.3 V to 4.5 V. Shows  $t_{DGL(BOVP)}$  and Soft-Stop

V<sub>UVLO</sub>, V<sub>HYS-UVLO</sub> - V

2.45

-50

-30

-10

#### **TYPICAL OPERATING PERFORMANCE (continued)**

Figure 13.

30 50

Temperature - °C

70

90

110

Figure 14.

Figure 15.

Figure 16.

#### **TYPICAL OPERATING PERFORMANCE (continued)**

Figure 17.

Figure 18.

Figure 19.

Figure 20.

#### **TYPICAL OPERATING PERFORMANCE (continued)**

# PGATE VOLTAGE VS INPUT VOLTAGE 18 16 14 12 2 0 0 5 10 15 V<sub>NIN</sub>-V

Figure 21.

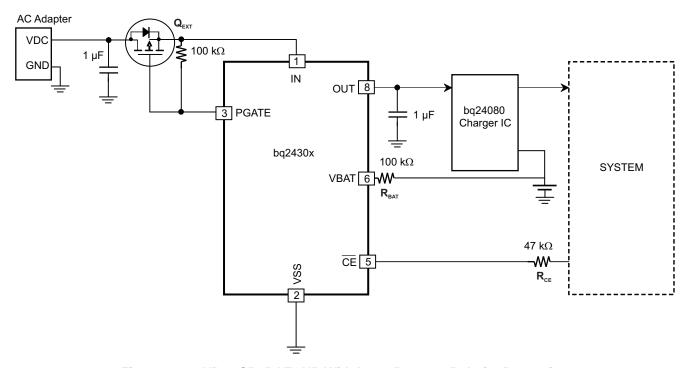

#### TYPICAL APPLICATION CIRCUITS

Figure 22. Overvoltage, Overcurrent, and Battery Overvoltage Protection

Figure 23. OVP, OCP, BATOVP With Input Reverse-Polarity Protection

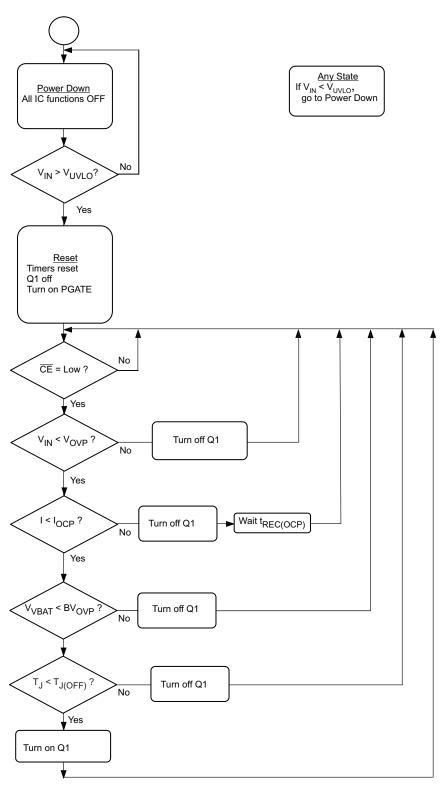

#### **DETAILED FUNCTIONAL DESCRIPTION**

The bq24300 and bq24304 are highly integrated circuits designed to provide protection to Li-ion batteries from failures of the charging circuit. The IC continuously monitors the input voltage, the input current and the battery voltage, and protects down-stream circuitry from damage if any of these parameters exceeds safe values. The IC also monitors its own die temperature and switches off if it becomes too hot.

The IC also offers optional protection against reverse voltage at the input with an external P-channel MOSFET.

#### **POWER DOWN**

The device remains in power down mode when the input voltage at the IN pin is below the under-voltage threshold  $V_{UVLO}$ . The FET Q1 (see Figure 1) connected between IN and OUT pins is off.

#### **POWER-ON RESET**

The device resets all internal timers when the input voltage at the IN pin exceeds the UVLO threshold. The gate driver for the external P-FET is enabled. The IC then waits for duration  $t_{DGL(PGOOD)}$  for the input voltage to stabilize. If, after  $t_{DGL(PGOOD)}$ , the input voltage and battery voltage are safe, FET Q1 is turned ON. The IC has a soft-start feature to control the inrush current. This soft-start minimizes voltage ringing at the input (the ringing occurs because the parasitic inductance of the adapter cable and the input bypass capacitor form a resonant circuit). Figure 2 shows the power-up behavior of the device. Because of the deglitch time at power-on, if the input voltage rises rapidly to beyond the OVP threshold, the device will not switch on at all, as shown in Figure 3.

#### **OPERATION**

The device continuously monitors the input voltage, the input current and the battery voltage as described in detail in the following sections:

#### Input Overvoltage Protection

As long as the input voltage is less than  $V_{O(REG)}$ , the output voltage tracks the input voltage (less the drop caused by  $R_{DS}ON$  of Q1). If the input voltage is greater than  $V_{O(REG)}$  (plus the  $R_{DS}ON$  drop) and less than  $V_{OVP}$ , the device acts like a series linear regulator, with the output voltage regulated to  $V_{O(REG)}$ . If the input voltage rises above  $V_{OVP}$ , the output voltage is clamped to  $V_{O(REG)}$  for a blanking duration  $t_{BLANK(OVP)}$ . If the input voltage returns below  $V_{OVP}$  within  $t_{BLANK(OVP)}$ , the device continues normal operation (see Figure 4). This provides protection against turning power off due to transient overvoltage spikes while still protecting the system. However, if the input voltage remains above  $V_{OVP}$  for more than  $t_{BLANK(OVP)}$ , the internal FET is turned off, removing power from the circuit (see Figure 5). When the input voltage comes back to a safe value, the device waits for  $t_{ON(OVP)}$  then switches on Q1 and goes through the soft-start routine (see Figure 7).

Figure 6 describes graphically the behavior of the OUT pin over the entire range of input voltage variation.

#### Input Overcurrent Protection

The device can supply load current up to  $I_{OCP}$  continuously. If the load current tries to exceed this threshold, the current is limited to  $I_{OCP}$  for a maximum duration of  $t_{BLANK(OCP)}$ . If the load current returns to less than  $I_{OCP}$  before  $t_{BLANK(OCP)}$  times out, the device continues to operate (see Figure 9). However, if the overcurrent situation persists for  $t_{BLANK(OCP)}$ , FET Q1 is turned off for a duration of  $t_{REC(OCP)}$ . It is then turned on again and the current is monitored all over again (see Figure 10 and Figure 8).

To prevent the input voltage from spiking up due to the inductance of the input cable, Q1 is not turned off rapidly in an overcurrent fault condition. Instead, the gate drive of Q1 is reduced slowly, resulting in a "soft-stop", as shown in Figure 11.

#### **Battery Overvoltage Protection**

The battery overvoltage threshold  $BV_{OVP}$  is internally set to 4.35V. If the battery voltage exceeds the  $BV_{OVP}$  threshold for longer than  $t_{DGL(BOVP)}$ , FET Q1 is turned off (see Figure 12). This switch-off is also a soft-stop. Q1 is turned ON (soft-start) once the battery voltage drops to  $BV_{OVP} - V_{HYS-BOVP}$ .

#### **Thermal Protection**

If the junction temperature of the device exceeds  $T_{J(OFF)}$ , FET Q1 is turned off. The FET is turned back on when the junction temperature falls below  $T_{J(OFF)} - T_{J(OFF-HYS)}$ .

#### **Enable Function**

The IC has an enable pin which can <u>be</u> used to enable or disable the device. When the  $\overline{\text{CE}}$  pin is driven high, the internal FET is turned off. When the  $\overline{\text{CE}}$  pin is low, the FET is turned on if other conditions are safe. The  $\overline{\text{CE}}$  pin has an internal pull-down resistor of 200 k $\Omega$  (typical) and can be left floating.

#### **PGATE Pin**

When used with an external P-Channel MOSFET, in addition to OVP, OCP and Battery-OVP, the device offers protection against input reverse polarity up to -30V. When operating with normal polarity, the IC first turns on due to current flow through the body-diode of the FET  $Q_{EXT}$ . The PGATE pin then goes low, turning ON  $Q_{EXT}$ . For input voltages larger than  $V_{GCLMP}$ , the voltage on the PGATE pin is driven to  $V_{IN} - V_{GCLMP}$ . This ensures that the gate to source voltage seen by  $Q_{EXT}$  does not exceed  $-V_{GCLMP}$ .

Figure 24. Flow Diagram

#### APPLICATION INFORMATION

#### Selection of R<sub>BAT</sub>:

It is strongly recommended that the battery not be tied directly to the VBAT pin of the device, as under some failure modes of the IC, the voltage at the IN pin may appear on the VBAT pin. This voltage can be as high as 30V, and applying 30V to the battery in case of the failure of the device can be hazardous. Connecting the VBAT pin through  $R_{BAT}$  prevents a large current from flowing into the battery in case of failure of the IC. In the interests of safety,  $R_{BAT}$  should have a very high value. The problem with a large  $R_{BAT}$  is that the voltage drop across this resistor because of the VBAT bias current  $I_{VBAT}$  causes an error in the  $BV_{OVP}$  threshold. This error is over and above the tolerance on the nominal 4.35V  $BV_{OVP}$  threshold.

Choosing  $R_{BAT}$  in the range  $100 K\Omega$  to  $470 k\Omega$  is a good compromise. In the case of IC failure, with  $R_{BAT}$  equal to  $100 k\Omega$ , the maximum current flowing into the battery would be  $(30V-3V)\div 100 k\Omega=270 \mu A$ , which is low enough to be absorbed by the bias currents of the system components.  $R_{BAT}$  equal to  $100 k\Omega$  would result in a worst-case voltage drop of  $R_{BAT}$  X  $I_{VBAT}\approx 1 mV$ . This is negligible compared to the internal tolerance of 50 mV on the  $BV_{OVP}$  threshold.

If the Bat-OVP function is not required, the VBAT pin should be connected to VSS.

#### Selection of R<sub>CE</sub>:

The  $\overline{\text{CE}}$  pin can be used to enable and disable the IC. If host control is not required, the  $\overline{\text{CE}}$  pin can be tied to ground or left un-connected, permanently enabling the device.

In applications where external control is <u>required</u>, the  $\overline{\text{CE}}$  pin can be controlled by a host processor. As in the case of the VBAT pin (see above), the  $\overline{\text{CE}}$  pin should be connected to the host GPIO pin through as large a resistor as possible. The limitation on the resistor value is that the <u>minimum VOH</u> of the host GPIO pin less the drop across the resistor should be greater than VIH of the bq2430x  $\overline{\text{CE}}$  pin. The drop across the resistor is given by  $R_{\text{CE}} \times I_{\text{IH}}$ .

#### **Selection of Input and Output Bypass Capacitors:**

The input capacitor  $C_{IN}$  in Figure 22 and Figure 23 is for decoupling, and serves an important purpose. Whenever there is a step change downwards in the system load current, the inductance of the input cable causes the input voltage to spike up.  $C_{IN}$  prevents the input voltage from overshooting to dangerous levels. It is strongly recommended that a ceramic capacitor of at least  $1\mu F$  be used at the input of the device. It should be located in close proximity to the IN pin.

$C_{\text{OUT}}$  in Figure 23 is also important: If a fast (< 1µs rise-time) overvoltage transient occurs at the input, the current that charges  $C_{\text{OUT}}$  causes the device's current-limiting loop to kick in, reducing the gate-drive to FET Q1. This results in improved performance for input overvoltage protection.  $C_{\text{OUT}}$  should also be a ceramic capacitor of at least 1µF, located close to the OUT pin.  $C_{\text{OUT}}$  also serves as the input decoupling capacitor for the charging circuit downstream of the protection IC.

#### **PCB Layout Guidelines:**

- 1. This device is a protection device, and is meant to protect down-stream circuitry from hazardous voltages. Potentially, high voltages may be applied to this IC. It has to be ensured that the edge-to-edge clearances of PCB traces satisfy the design rules for the maximum voltages expected to be seen in the system.

- 2. The device uses SON packages with a PowerPAD™. For good thermal performance, the PowerPAD should be thermally coupled with the PCB ground plane. In most applications, this will require a copper pad directly under the IC. This copper pad should be connected to the ground plane with an array of thermal vias.

- 3.  $C_{IN}$  and  $C_{OUT}$  should be located close to the IC. Other components like  $R_{BAT}$  should also be located close to the IC.

#### **REVISION HISTORY**

| Ch | nanges from Original (August 2007) to Revision A                                                                                                                             | Page     |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| •  | Changed the devices from Product Preview status to Production.                                                                                                               | 1        |

| Ch | nanges from Revision A (October 2007) to Revision B                                                                                                                          | Page     |

| •  | Added device bq24305 to the data sheet                                                                                                                                       | 1        |

| •  | Changed the bq24305 marking in the Ordering Information table From CHD To: DSG                                                                                               | 2        |

| •  | Changed Figure 22, Overvoltage, Overcurrent, and Battery Overvoltage Protection                                                                                              | 12       |

| •  | Changed Figure 23, OVP, OCP, BATOVP With Input Reverse-Polarity Protection                                                                                                   | 12       |

| •  | Deleted Lead temperature (soldering, 10 seconds) from the Abs Max table. This is covered in the Package                                                                      | 2        |

| •  | Deleted Lead temperature (soldering, 10 seconds) from the Abs Max table. This is covered in the Package information.                                                         | <u>2</u> |

| •  | Changed Recommended Operating Conditions, Input voltage range - MAX value From 30V To: 26V                                                                                   | <u>2</u> |

| •  | Changed $BV_{OVP}$ test conditions - From: $\overline{CE}$ = Low, $V_{IN}$ > 4.3V, $V_{VBAT}$ increasing To: $\overline{CE}$ = Low, $V_{IN}$ > 4.4V, $V_{VBAT}$ increasing   | 3        |

| •  | Changed $V_{HYS-BOVP}$ test conditions - From: $\overline{CE}$ = Low, $V_{IN}$ > 4.3V, $V_{VBAT}$ decreasing To: $\overline{CE}$ = Low, $V_{IN}$ > 4.4V, $V_{VI}$ decreasing | BAT      |

| •  | Changed the Gate driver clamp voltage Typ valur From: 14V To: 15V and the Max value From: 15V To: 17V                                                                        |          |

| •  | Changed Figure 23, OVP, OCP, BATOVP With Input Reverse-Polarity Protection                                                                                                   | 12       |

| •  | Changed section - Selection of $R_{BAT}$ text From: $(30V - 3V) \times 100k\Omega = 246\mu A$ To: battery would be $(30V - 3V) \div 100k\Omega = 270\mu A$                   | 16       |

6-Feb-2020

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|----------------------------|------------------|---------------------|--------------|----------------------|---------|

| BQ24300DSGR      | ACTIVE | WSON         | DSG                | 8    | 3000           | Green (RoHS<br>& no Sb/Br) | NIPDAU           | Level-2-260C-1 YEAR | 0 to 125     | BZA                  | Samples |

| BQ24300DSGT      | ACTIVE | WSON         | DSG                | 8    | 250            | Green (RoHS<br>& no Sb/Br) | NIPDAU           | Level-2-260C-1 YEAR | 0 to 125     | BZA                  | Samples |

| BQ24305DSGR      | ACTIVE | WSON         | DSG                | 8    | 3000           | Green (RoHS<br>& no Sb/Br) | NIPDAU           | Level-2-260C-1 YEAR | 0 to 125     | DSG                  | Samples |

| BQ24305DSGT      | ACTIVE | WSON         | DSG                | 8    | 250            | Green (RoHS<br>& no Sb/Br) | NIPDAU           | Level-2-260C-1 YEAR | 0 to 125     | DSG                  | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

#### **PACKAGE OPTION ADDENDUM**

6-Feb-2020

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

PACKAGE MATERIALS INFORMATION

www.ti.com 3-Aug-2017

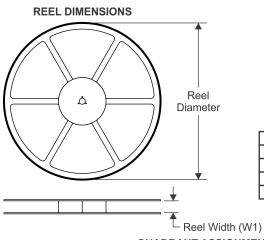

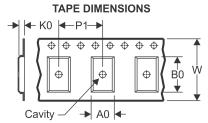

#### TAPE AND REEL INFORMATION

| Α0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

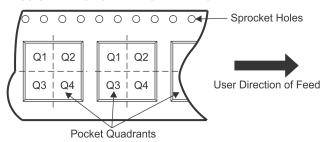

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| BQ24300DSGR | WSON            | DSG                | 8 | 3000 | 179.0                    | 8.4                      | 2.2        | 2.2        | 1.2        | 4.0        | 8.0       | Q2               |

| BQ24300DSGR | WSON            | DSG                | 8 | 3000 | 178.0                    | 8.4                      | 2.25       | 2.25       | 1.0        | 4.0        | 8.0       | Q2               |

| BQ24300DSGT | WSON            | DSG                | 8 | 250  | 178.0                    | 8.4                      | 2.25       | 2.25       | 1.0        | 4.0        | 8.0       | Q2               |

| BQ24300DSGT | WSON            | DSG                | 8 | 250  | 179.0                    | 8.4                      | 2.2        | 2.2        | 1.2        | 4.0        | 8.0       | Q2               |

| BQ24305DSGR | WSON            | DSG                | 8 | 3000 | 179.0                    | 8.4                      | 2.2        | 2.2        | 1.2        | 4.0        | 8.0       | Q2               |

| BQ24305DSGT | WSON            | DSG                | 8 | 250  | 179.0                    | 8.4                      | 2.2        | 2.2        | 1.2        | 4.0        | 8.0       | Q2               |

www.ti.com 3-Aug-2017

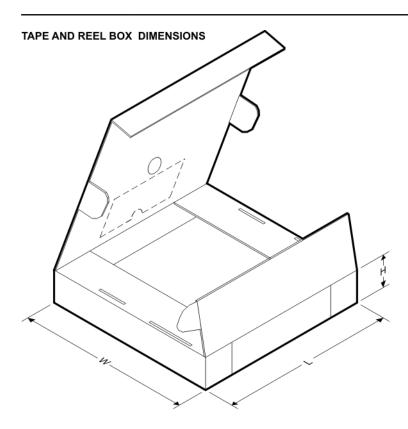

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| BQ24300DSGR | WSON         | DSG             | 8    | 3000 | 195.0       | 200.0      | 45.0        |

| BQ24300DSGR | WSON         | DSG             | 8    | 3000 | 205.0       | 200.0      | 33.0        |

| BQ24300DSGT | WSON         | DSG             | 8    | 250  | 205.0       | 200.0      | 33.0        |

| BQ24300DSGT | WSON         | DSG             | 8    | 250  | 195.0       | 200.0      | 45.0        |

| BQ24305DSGR | WSON         | DSG             | 8    | 3000 | 195.0       | 200.0      | 45.0        |

| BQ24305DSGT | WSON         | DSG             | 8    | 250  | 195.0       | 200.0      | 45.0        |

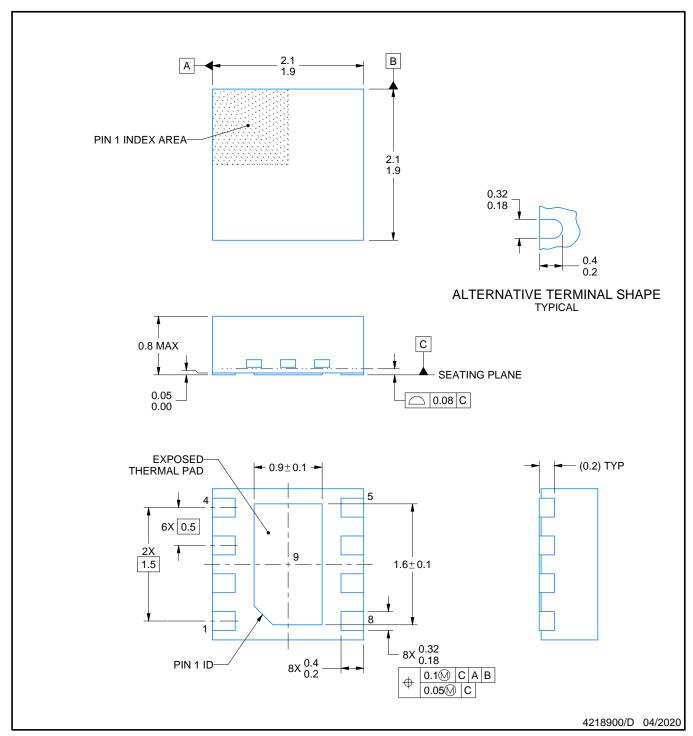

2 x 2, 0.5 mm pitch

PLASTIC SMALL OUTLINE - NO LEAD

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

PLASTIC SMALL OUTLINE - NO LEAD

#### NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

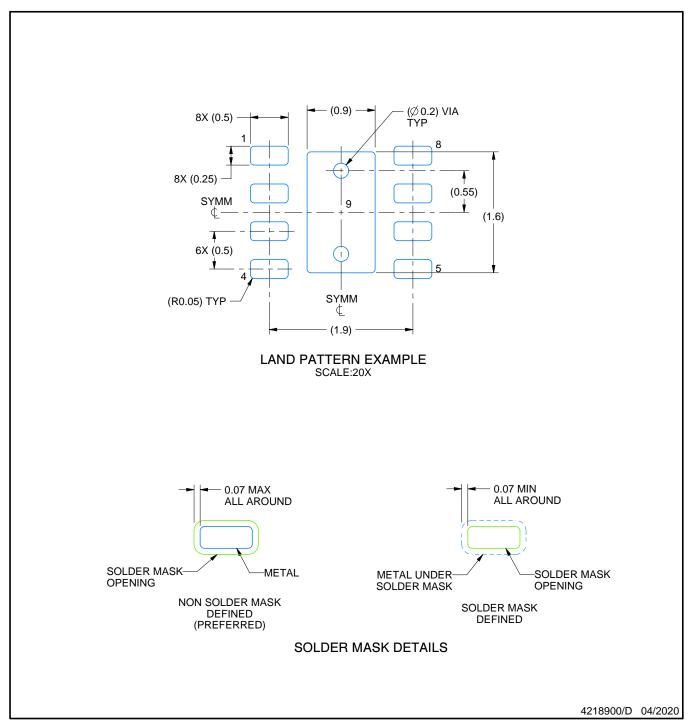

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

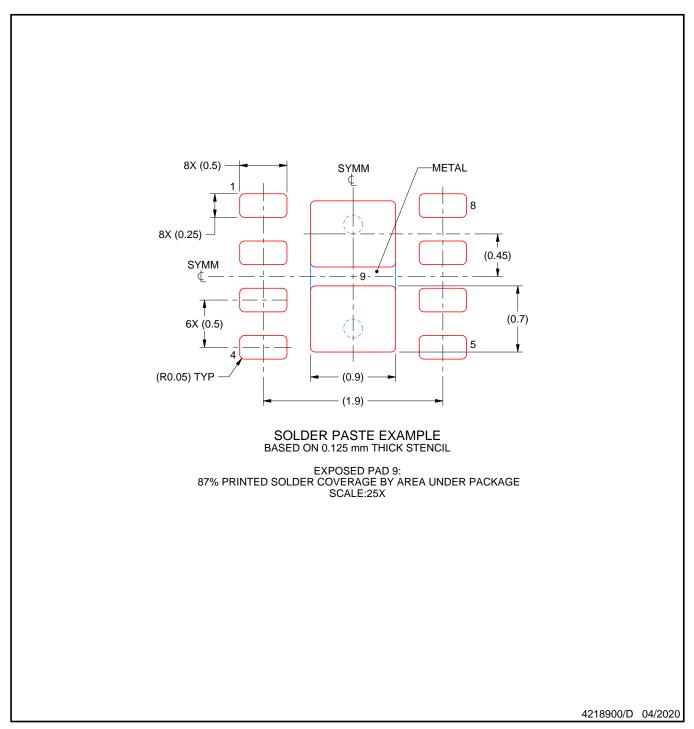

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

Tl's products are provided subject to Tl's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such Tl products. Tl's provision of these resources does not expand or otherwise alter Tl's applicable warranties or warranty disclaimers for Tl products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated