## Power management for automotive vision and radar systems

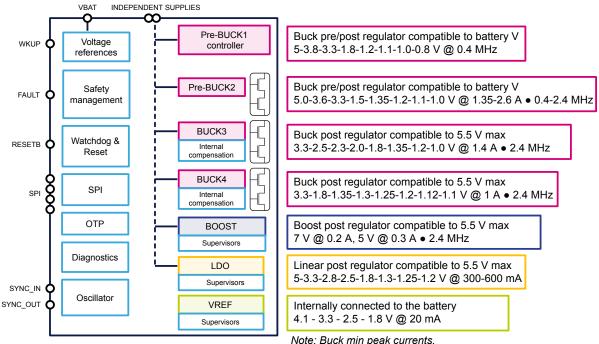

#### **Features**

- AEC-Q100 qualified

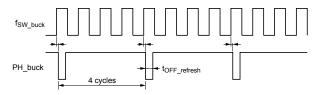

- Pre SMPS BUCK1 regulator controller, adjustable via OTP to 0.8 V, 1.0 V, 1.1 V, 1.2 V, 1.8 V, 3.3 V, 3.8 V, 5.0 V @ 0.4 MHz

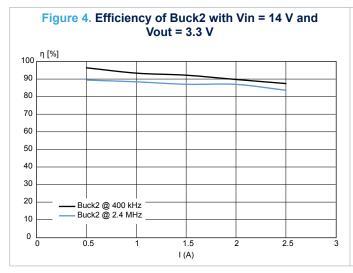

- Pre SMPS BUCK2 regulator, adjustable via OTP to 1.0 V, 1.1 V, 1.2 V, 1.35 V, 1.5 V, 3.3 V, 3.6 V, 5.0 V @ 1.35/2.6 A min peak current limit, 0.4/2.4 MHz

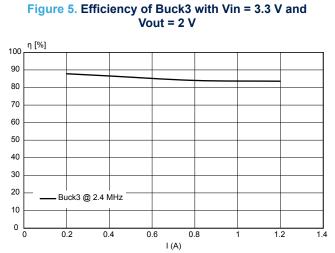

- Post SMPS BUCK3 regulator, adjustable via OTP to 1.0 V, 1.2 V, 1.35 V, 1.8 V, 2.0 V, 2.3 V, 2.5 V, 3.3 V @ 1.4 A min peak current limit, 2.4 MHz

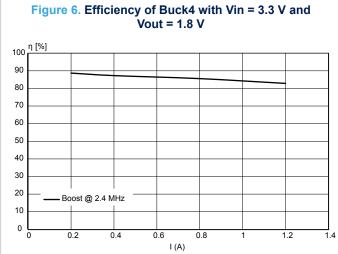

- Post SMPS BUCK4 regulator, adjustable via OTP to 1.1 V, 1.12 V, 1.2 V, 1.25 V, 1.3 V, 1.35 V, 1.8 V, 3.3 V @ 1 A min peak current limit, 2.4 MHz

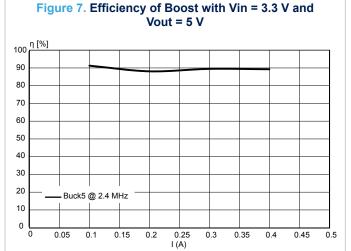

- Post SMPS BOOST regulator, adjustable via OTP to 5.0 V @ 0.3 A max load current, 7.0 V @ 0.2 A max load current, 2.4 MHz

- Post Linear regulator LDO, adjustable via OTP to 1.2 V, 1.25 V, 1.3 V, 1.8 V, 2.5 V, 2.8 V, 3.3 V, 5.0 V @ 300/600 mA max load current

- Precise Voltage reference, adjustable via OTP to 1.8 V, 2.5 V, 3.3 V, 4.1 V @ 20 mA max load current

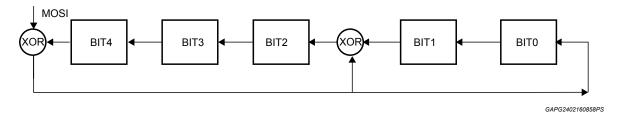

- · SPI interface with CRC

- · Programmable slew rate/soft start

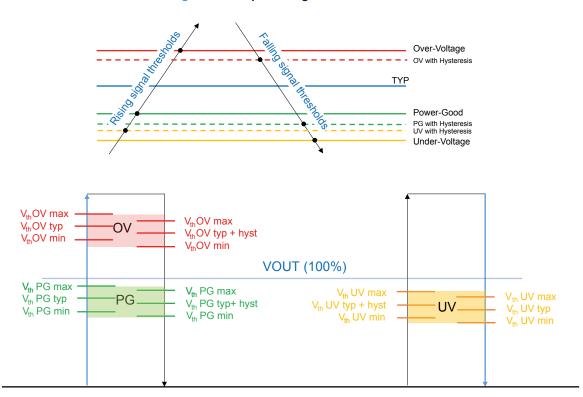

- · Voltage supervisors

- · Spread frequency spectrum

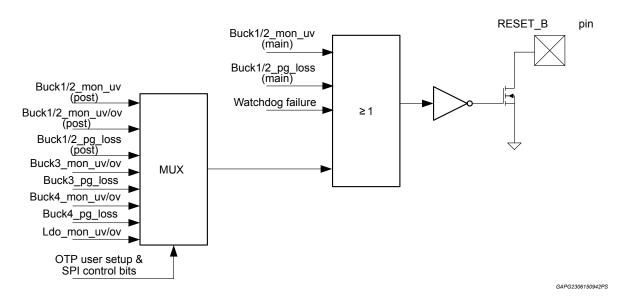

- Reset and reset activation list

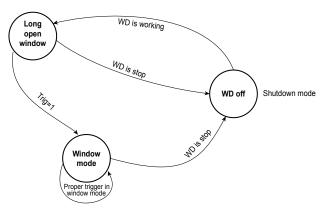

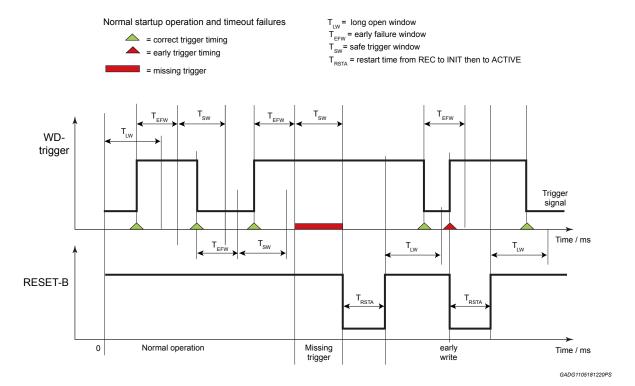

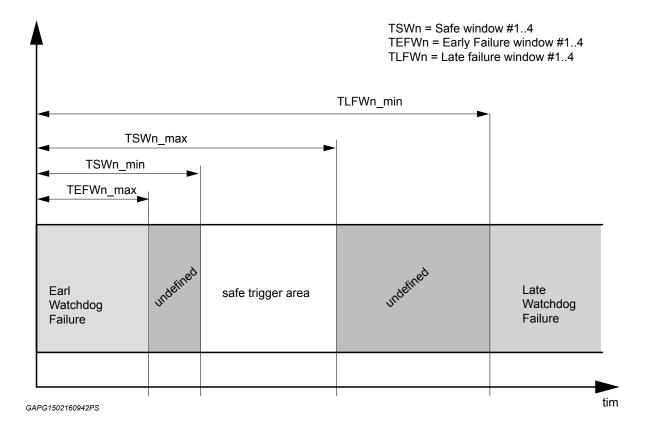

- Adjustable window watchdog supervisors

- Power up phase programmable via OTP

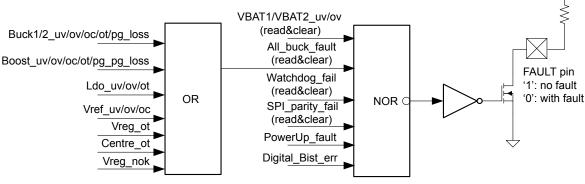

- Short circuit protected outputs and Fault detection pin to Microcontroller

- Low external components number

- Thermal shutdown junction temperature 175 °C

## Product status link

L5965

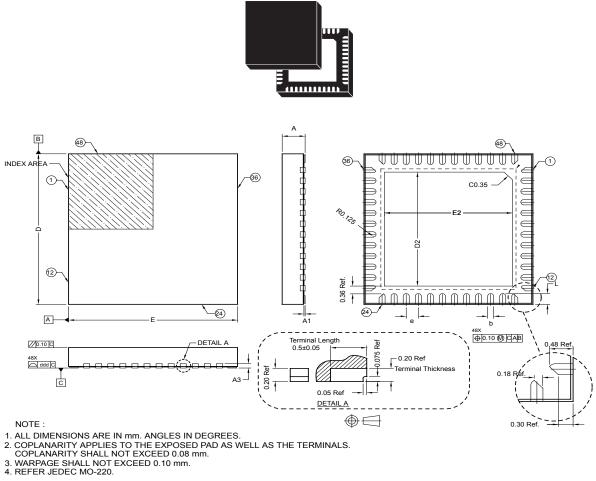

| Product summary |                        |               |  |  |  |  |

|-----------------|------------------------|---------------|--|--|--|--|

| Order code      | r code Package Packing |               |  |  |  |  |

| L5965SQ-V0Y     |                        | Tray          |  |  |  |  |

| L5965SQ-V0T     | VFQFPN-48              | Tape and reel |  |  |  |  |

## **Description**

L5965 is a multiple voltage regulator composed by two battery compatible BUCK preregulators (one of which is a controller), two BUCK post regulators with internal compensation, one BOOST, one LDO and a precise voltage reference regulator. All the regulators, except the BUCK1 pre-regulator, have internal power switches.

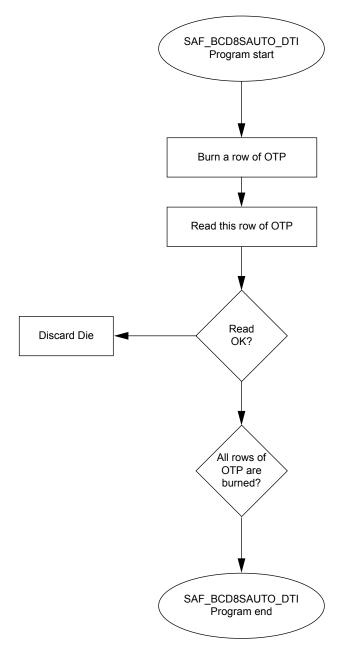

OTP (One Time Programmable) cells are used for the main device parameters programming (output voltages and currents, switching frequencies) and to configure power up sequence.

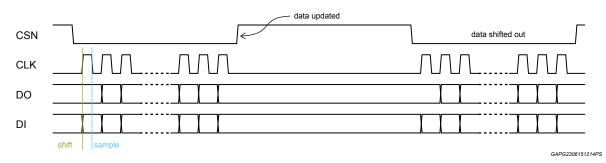

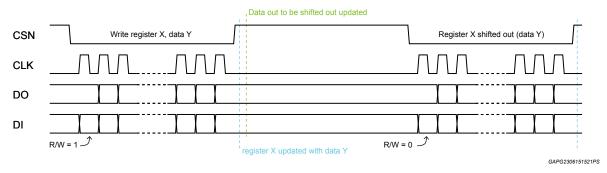

An SPI interface can be used to enable or disable the single voltage regulators, for diagnostic information and to program internal blocks parameters (monitor and Power Good thresholds, slew rate, etc.).

The device offers a set of features to support applications that need to fulfill functional safety requirements as defined by Automotive Safety Integrity Level (ASIL) A-B-C-D.

GAPG1005181515PS

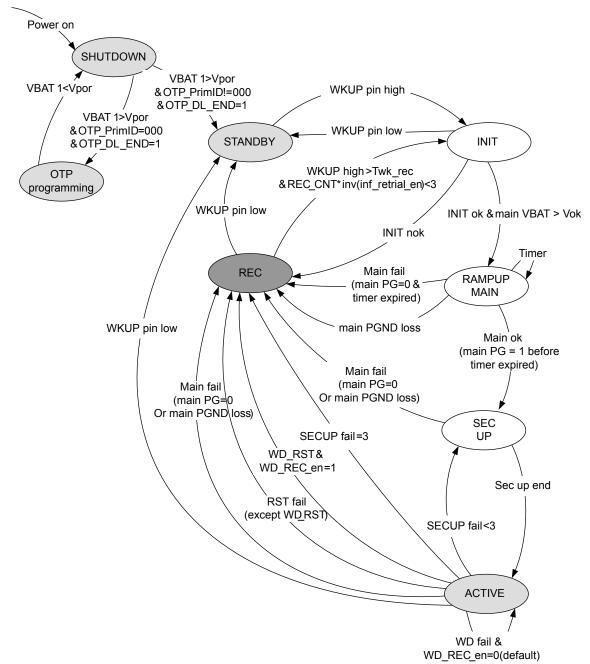

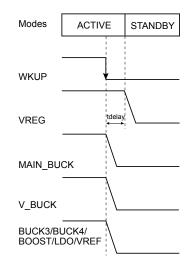

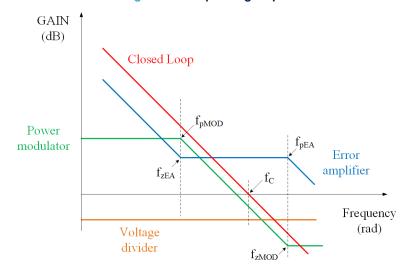

### 1 Overview

L5965 is a multichannel voltage regulator able to offer flexibility and ease to use, together with a set of features that make it compliant to car passenger applications that require a certain level of safety. The product includes input and output monitors, independent band-gaps, ground loss monitors, internal compensation networks, that also help reduce the BOM, digital and analog BIST, fault pin.

In this product, there are 7 different regulators. A first battery-compatible regulator, a controller that can supply several current flow thanks to the use of external MOSs. A second regulator with integrated MOS that can be used as a pre-regulator for currents up to about 2.6 A. Two bucks, post regulators, one boost that can be used to supply, for example, a CAN bus, one LDO and a 1% accurate reference voltage for the microcontroller.

All output voltages can be selected via memory cells (OTP) that can be programmed before using the PMIC. This guarantees precision and safety, since output voltages are not susceptible to variations due to the external environment. It also contributes to reducing the number of external components. Through the OTP it is also possible to decide the switching frequency of some regulators, the current limitation, select the main buck and the system power-on sequence.

Programming can also be done at customer's production line.

There is also an SPI bus, used to program the PMIC and to communicate with the microcontroller. Through this bus it is possible to set overvoltage and undervoltage thresholds, enable the spread spectrum, select the soft start time and many other things. The SPI is also used to communicate the status of the bucks in case of fault, overtemperature or other events.

The maximum free run switching frequency of the bucks is 2.4 MHz, modifiable through external synchronization signals.

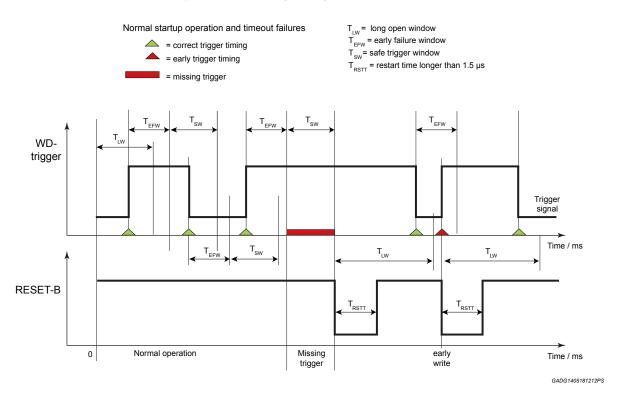

The PMIC can manage watchdog and reset signals.

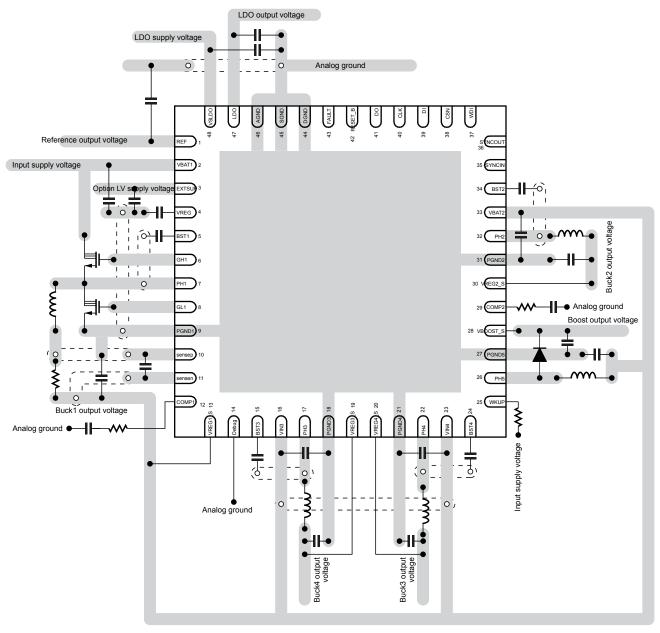

### 1.1 Simplified block diagram

Figure 1. Simplified block diagram

DS12567 - Rev 2 page 2/85

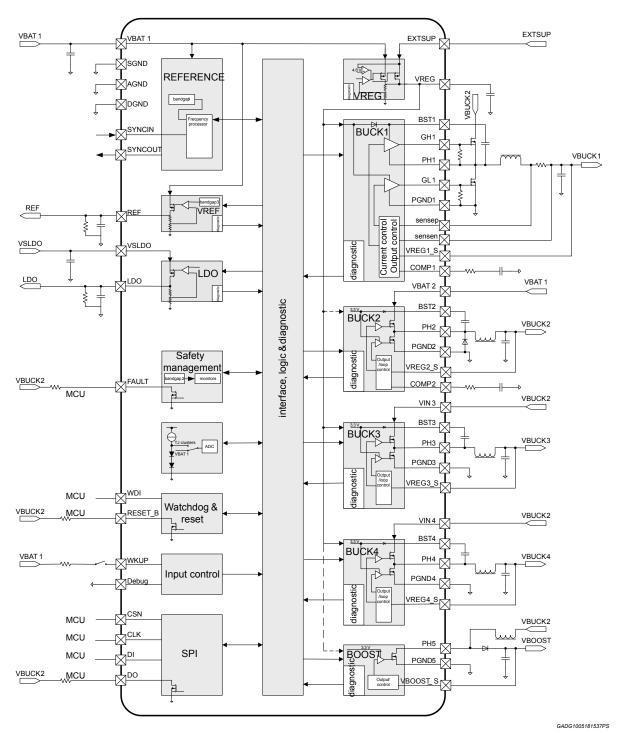

## 1.2 Functional block diagram

Figure 2. Functional block diagram

Application example with BUCK2 as main buck.

DS12567 - Rev 2 page 3/85

# 2 Pins description

**FAULT** REF SYNCOUT 35 ( ] VBAT1 SYNCIN EXTSUP BST2 VREG VBAT2 BST1 PH2 GH1 PGND2 PH1 VREG2\_S GL1 COMP2 VBOOST\_S PGND1 sensep PGND5 26 ( ] PH5 sensen COMP1 WKUP PGND3 VIN4 BST4

Figure 3. Pin out (top view)

GAPG2206151609PS

Table 1. Pin description and functions

| No. | Pin name | Pin type | Description                                                                |

|-----|----------|----------|----------------------------------------------------------------------------|

| 1   | REF      | 0        | Accurate reference voltage output                                          |

| 2   | VBAT1    | S        | VBAT1 for inner reference and supply for pre-BUCK1 external HS MOS         |

| 3   | EXTSUP   | S        | Optional LV input for BUCK1, BUCK3, BUCK4 gate driver supply               |

| 4   | VREG     | 0        | Internal regulator for BUCK1, BUCK3, BUCK4 gate driver supply (decoupling) |

| 5   | BST1     | I/O      | Boot-strap capacitor to supply BUCK1 high-side MOS gate-driver circuitry   |

| 6   | GH1      | 0        | Gate driver of external high-side MOS                                      |

| 7   | PH1      | 0        | Switching node BUCK1                                                       |

| 8   | GL1      | 0        | Gate driver of external low-side MOS                                       |

| 9   | PGND1    | G        | Ground for external low-side MOS driver circuitry                          |

| 10  | sensep   | I        | Positive differential current sense input for BUCK1                        |

| 11  | sensen   | I        | Negative differential current sense input for BUCK1                        |

| 12  | COMP1    | I/O      | BUCK1 Error Amplifier compensation network                                 |

| 13  | VREG1_S  | I        | BUCK1 regulated voltage output (to internal voltage monitors)              |

| 14  | Debug    | I        | Device debug. Keep floating or connect to ground when not used             |

DS12567 - Rev 2 page 4/85

| No. | Pin name | Pin type | Description                                                                 |

|-----|----------|----------|-----------------------------------------------------------------------------|

| 15  | BST3     | I/O      | Boot-strap capacitor to supply BUCK3 high-side MOS gate-driver circuitry    |

| 16  | VIN3     | S        | Input voltage supply for BUCK3                                              |

| 17  | PH3      | 0        | Switching node BUCK3                                                        |

| 18  | PGND3    | G        | BUCK3 Power ground                                                          |

| 19  | VREG3_S  | I        | BUCK3 regulated voltage output (to internal voltage monitors)               |

| 20  | VREG4_S  | I        | BUCK4 regulated voltage output (to internal voltage monitors)               |

| 21  | PGND4    | G        | BUCK4 Power ground                                                          |

| 22  | PH4      | 0        | Switching node BUCK4                                                        |

| 23  | VIN4     | S        | input voltage supply for BUCK4                                              |

| 24  | BST4     | I/O      | Boot-strap capacitor to supply BUCK4 high-side MOS gate-driver circuitry    |

| 25  | WKUP     | I        | Wake up input. Internal 200 k $\Omega$ pull-down                            |

| 26  | PH5      | 0        | BOOST switching node                                                        |

| 27  | PGND5    | G        | BOOST Power ground                                                          |

| 28  | VBOOST_S | ı        | BOOST regulated voltage output (to internal voltage monitors)               |

| 29  | COMP2    | I/O      | BUCK2 Error Amplifier compensation network                                  |

| 30  | VREG2_S  | I        | BUCK2 regulated voltage output (to internal voltage monitors)               |

| 31  | PGND2    | G        | BUCK2 Power ground                                                          |

| 32  | PH2      | 0        | Switching node BUCK2                                                        |

| 33  | VBAT2    | S        | Input voltage supply for BUCK2                                              |

| 34  | BST2     | I/O      | Boot-strap capacitor to supply BUCK2 high-side MOS gate-driver circuitry    |

| 35  | SYNCIN   | I        | PWM input frequency for synchronization purpose. Internal current pull-down |

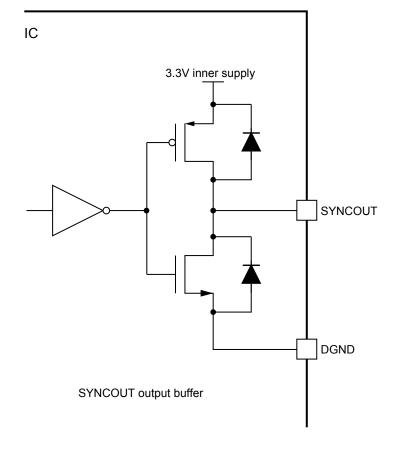

| 36  | SYNCOUT  | 0        | PWM output frequency of inner 2.4M oscillator, or SYNCIN if used            |

| 37  | WDI      | I        | Watchdog input. WDI is trigger input from MCU. Internal current pull-down   |

| 38  | CSN      | I        | SPI: chip select input. Active low. Internal current pull-up                |

| 39  | DI       | I        | SPI: serial data input. Internal current pull-down                          |

| 40  | CLK      | I        | SPI: serial clock input. Internal current pull-down                         |

| 41  | DO       | OD       | SPI: serial data output                                                     |

| 42  | RESET_B  | OD       | Reset                                                                       |

| 43  | FAULT    | OD       | Fault pin detection to MCU                                                  |

| 44  | DGND     | G        | Digital GND                                                                 |

| 45  | SGND     | G        | Signal ground for low noise circuitry                                       |

| 46  | AGND     | G        | Analog GND                                                                  |

| 47  | LDO      | 0        | Linear regulated output                                                     |

| 48  | VSLDO    | S        | Input voltage supply for LDO                                                |

DS12567 - Rev 2 page 5/85

# 3 Electrical specifications

# 3.1 Absolute maximum ratings & operating voltage

Table 2. Absolute maximum ratings & operating voltage

| Dia nome | Absolute  | Absolute maximum rating Operating voltage |      |           | Operating voltage |      |  |

|----------|-----------|-------------------------------------------|------|-----------|-------------------|------|--|

| Pin name | Min       | Max                                       | Unit | Min       | Max               | Unit |  |

| VBAT1    | -0.3      | 42                                        | V    | -0.3      | 32                | V    |  |

| SGND     | -0.3      | 0.3                                       | V    | 0         | 0                 | V    |  |

| AGND     | -0.3      | 0.3                                       | V    | 0         | 0                 | V    |  |

| DGND     | -0.3      | 0.3                                       | V    | 0         | 0                 | V    |  |

| REF      | -0.3      | 6.5                                       | V    | -0.3      | 5.5               | V    |  |

| VSLDO    | -0.3      | 13                                        | V    | -0.3      | 6                 | V    |  |

| LDO      | -0.3      | 7                                         | V    | -0.3      | 6                 | V    |  |

| WKUP     | -0.3      | 42                                        | V    | -0.3      | 32                | V    |  |

| RESET_B  | -0.3      | 6.5                                       | V    | -0.3      | 5.5               | V    |  |

| WDI      | -0.3      | 6.5                                       | V    | -0.3      | 5.5               | V    |  |

| CSN      | -0.3      | 6.5                                       | V    | -0.3      | 5.5               | V    |  |

| CLK      | -0.3      | 6.5                                       | V    | -0.3      | 5.5               | V    |  |

| DI       | -0.3      | 6.5                                       | V    | -0.3      | 5.5               | V    |  |

| DO       | -0.3      | 6.5                                       | V    | -0.3      | 5.5               | V    |  |

| FAULT    | -0.3      | 6.5                                       | V    | -0.3      | 5.5               | V    |  |

| SYNCOUT  | -0.3      | 4.6                                       | V    | -0.3      | 3.6               | V    |  |

| SYNCIN   | -0.3      | 6.5                                       | V    | -0.3      | 5.5               | V    |  |

| EXTSUP   | -0.3      | 13                                        | V    | -0.3      | 12                | V    |  |

| VREG     | -0.3      | 8                                         | V    | -0.3      | 6.6               | V    |  |

| BST1     | PH1-0.3   | PH1+10                                    | V    | PH1-0.3   | PH1+8             | V    |  |

| GH1      | PH1-0.3   | PH1+10                                    | V    | PH1-0.3   | PH1+8             | V    |  |

| PH1      | -1        | 42                                        | V    | -1        | 32                | V    |  |

| GL1      | PGND1-0.3 | PGND1+10                                  | V    | PGND1-0.3 | PGND1+8           | V    |  |

| 20200    | -0.3      | 6.5                                       | V    | -0.3      | 5.5               | V    |  |

| sensep   | sensen-2  | sensen+2                                  | V    | sensen-2  | sensen+2          | V    |  |

| sensen   | -0.3      | 6.5                                       | V    | -0.3      | 5.5               | V    |  |

| VREG1_S  | -0.3      | 6.5                                       | V    | -0.3      | 5.5               | V    |  |

| PGND1    | -0.3      | 0.3                                       | V    | -0.3      | 0.3               | V    |  |

| VBAT2    | -0.3      | 42                                        | V    | -0.3      | 32                | V    |  |

| BST2     | PH2-0.3   | PH2+4.6                                   | V    | PH2-0.3   | PH2+3.6           | V    |  |

| PH2      | -1        | 42                                        | V    | -1        | 32                | V    |  |

| VREG2_S  | -0.3      | 6.5                                       | V    | -0.3      | 5.5               | V    |  |

| PGND2    | -0.3      | 0.3                                       | V    | -0.3      | 0.3               | V    |  |

DS12567 - Rev 2 page 6/85

| Pin name | Absolute maximum rating |         |      | Oper    | ating voltage |      |  |

|----------|-------------------------|---------|------|---------|---------------|------|--|

| Pin name | Min                     | Max     | Unit | Min     | Max           | Unit |  |

| VIN3     | -0.3                    | 6.5     | V    | -0.3    | 5.5           | V    |  |

| BST3     | PH3-0.3                 | PH3+4.6 | V    | PH3-0.3 | PH3+3.6       | V    |  |

| PH3      | -1                      | 6.5     | V    | -1      | 5.5           | V    |  |

| VREG3_S  | -0.3                    | 4.6     | V    | -0.5    | 3.6           | V    |  |

| PGND3    | -0.3                    | 0.3     | V    | -0.3    | 0.3           | V    |  |

| VIN4     | -0.3                    | 6.5     | V    | -0.3    | 5.5           | V    |  |

| BST4     | PH4-0.3                 | PH4+4.6 | V    | PH4-0.3 | PH4+3.6       | V    |  |

| PH4      | -1                      | 6.5     | V    | -1      | 5.5           | V    |  |

| VREG4_S  | -0.3                    | 4.6     | V    | -0.5    | 3.6           | V    |  |

| PGND4    | -0.3                    | 0.3     | V    | -0.3    | 0.3           | V    |  |

| PH5      | -0.3                    | 9       | V    | -0.3    | 8             | V    |  |

| VBOOST_S | -0.3                    | 13      | V    | -0.3    | 7.5           | V    |  |

| PGND5    | -0.3                    | 0.3     | V    | -0.3    | 0.3           | V    |  |

| Debug    | -0.3                    | 42      | V    | -0.3    | 20            | V    |  |

| COMP1    | -0.3                    | 4.6     | V    | -0.3    | 3.6           | V    |  |

| COMP2    | -0.3                    | 4.6     | V    | -0.3    | 3.6           | V    |  |

## 3.2 Thermal data

## 3.2.1 Thermal resistance

Table 3. Operation junction temperature

| Symbol                    | Parameter                              | Board     | Value unit | Unit |

|---------------------------|----------------------------------------|-----------|------------|------|

| R <sub>th j-a-2s</sub>    |                                        | 2s        | 66         | °C/W |

| R <sub>th j-a-2s2p</sub>  | Thermal resistance junction-to-ambient | 2s2p      | 32         | °C/W |

| R <sub>th j-a-2s2pv</sub> |                                        | 2s2p+vias | 26         | °C/W |

| R <sub>th j-case</sub>    | Thermal resistance junction-to-case    |           | 2.2        | °C/W |

## 3.2.2 Thermal warning and protection

Table 4. Temperature thresholds

| Symbol                       | Parameter                | Test condition   | Min. | Тур. | Max. | Unit |

|------------------------------|--------------------------|------------------|------|------|------|------|

| T <sub>SD_TH</sub>           | Thermal Shutdown         | _                | 160  | 175  | 190  | °C   |

| T <sub>SD_hys</sub>          |                          | Hysteresis       | 0.5  | 4    | 8    | °C   |

| T <sub>OT_THx (x=1-7)</sub>  | Over temperature warning | _                | 140  | 155  | 170  | °C   |

| T <sub>OT_hysx (x=1-7)</sub> | Over temperature warning | Hysteresis       | 3    | 7    | 11   | °C   |

| T <sub>SD_filter</sub>       | Thermal Filter time      | _                | _    | 16   | _    | μs   |

| Tj                           | Junction temperature     | Tj               | -40  |      | 150  | °C   |

| T <sub>stg</sub>             | Storage temperature      | T <sub>stg</sub> |      |      | 150  | °C   |

DS12567 - Rev 2 page 7/85

According to the below formula and considering  $T_{SD\_TH}$  thermal shutdown minimum threshold at 160 °C, the maximum suggested power dissipation is:

$P_{DISS\_suggested} = (T_{SHD} - T_{AMB}) / R_{THJ-A}$

Table 5. Maximum suggested power

| Symbol                       | T <sub>amb</sub> 125 ° C | T <sub>amb</sub> 105 ° C | T <sub>amb</sub> 80 ° C |

|------------------------------|--------------------------|--------------------------|-------------------------|

| R <sub>th j-a-2s</sub>       | 0.53 W                   | 0.9 W                    | 1.2 W                   |

| R <sub>th j-a-2s2p</sub>     | 1.1 W                    | 1.8 W                    | 2.6 W                   |

| R <sub>th j-a-2s2pvias</sub> | 1.35 W                   | 2.3 W                    | 3.2 W                   |

## 3.3 Electrical characteristics

V<sub>BAT1</sub> supplies pre-BUCK1 circuitry the inner reference circuit (band-gap and oscillator) and VREF.

V<sub>BAT2</sub> supplies BUCK2, VSLDO supplies the LDO, VIN3 supplies BUCK3 and VIN4 supplies BUCK4.

$V_{BAT1,2}$  = 14 V,  $T_{amb}$  = -40 °C to 125 °C, unless otherwise specified.

**Table 6. Electrical characteristics**

| Symbol                   | Parameter                                                                 | Test condition                                                                                                         | Min. | Тур. | Max. | Unit |

|--------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| eneral characteristics   |                                                                           |                                                                                                                        |      |      |      |      |

| V <sub>BAT1</sub>        | Operating range                                                           | _                                                                                                                      | 4    | 14   | 32   | V    |

| V <sub>BAT2</sub>        | Operating range                                                           | _                                                                                                                      | 4    | 14   | 32   | V    |

| I <sub>STANDBY1</sub>    | STANDBY mode total current consumption on VBAT1                           | All regulators off, V <sub>BAT1</sub> = 14 V, non-<br>supply inputs floating, current<br>consumption from the supplies | _    | _    | 50   | μA   |

| I <sub>STANDBY2</sub>    | STANDBY mode total current consumption on VBAT2                           | All regulators off, V <sub>BAT2</sub> = 14 V, non-<br>supply inputs floating, current<br>consumption from the supplies | _    | _    | 1    | μА   |

| I <sub>ACTIVE</sub>      | ACTIVE mode total current consumption                                     | Main BUCK only, V <sub>BAT1-2</sub> = 14 V,<br>EXTSUP = 0 V                                                            | _    | 10   | _    | mA   |

| I <sub>ACTIVE_</sub> ALL | ACTIVE mode total current consumption                                     | All regulators ON, V <sub>BAT1-2</sub> = 14 V,<br>Rising slope < 0.1V*ms,<br>EXTSUP=0 V                                | _    | 40   | _    | mA   |

| ipply monitors           |                                                                           |                                                                                                                        |      |      |      |      |

| $V_{UV}$                 | Under-voltage threshold for $V_{\text{BAT1}}$ and $V_{\text{BAT2}}$       | Supply decreasing                                                                                                      | 5.3  | 5.8  | 6.3  | V    |

| V <sub>UV_HYS</sub>      | Under-voltage hysteresis                                                  | _                                                                                                                      | _    | 0.2  | 0.4  | V    |

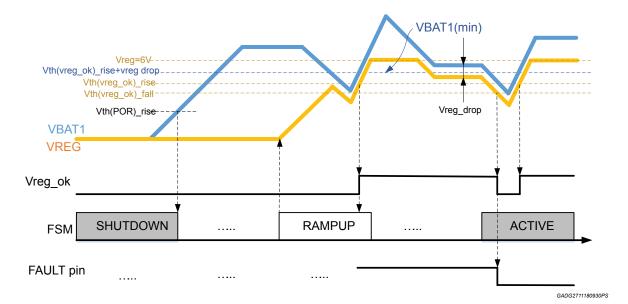

| V <sub>OK</sub>          | OK threshold for VBAT1 or VBAT2, depending on which is the main regulator | Supply increasing                                                                                                      | 5.5  | 6    | 6.5  | V    |

| V <sub>OK_HYS</sub>      | OK-voltage hysteresis                                                     | -                                                                                                                      | -    | 0.2  | 0.4  | V    |

| V <sub>OV</sub>          | Over-voltage threshold for $V_{BAT1}$ and $V_{BAT2}$                      | Supply increasing                                                                                                      | 30   | 32   | 34   | V    |

| V <sub>OV_HYS</sub>      | Over-voltage hysteresis                                                   | _                                                                                                                      | _    | 2    | 2.4  | V    |

| t <sub>UVOV_filter</sub> | Over/under voltage filter time                                            | _                                                                                                                      | 10   | 16   | -    | μs   |

| V <sub>RESETB</sub>      | RESETB pin low output voltage                                             | I <sub>RESET</sub> = 1 mA                                                                                              |      | 0.1  | 0.25 | V    |

| T <sub>RESETB</sub>      | RESETB pulse duration                                                     | _                                                                                                                      | 4    | 10   | 16   | μs   |

| V <sub>FAULT</sub>       | FAULT pin low output voltage                                              | I <sub>FAULT</sub> = 1 mA                                                                                              |      | 0.1  | 0.25 | V    |

DS12567 - Rev 2 page 8/85

| Symbol                    | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Test condition                                                | Min.  | Тур. | Max. | Unit |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-------|------|------|------|

| Power on reset            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                               |       |      |      |      |

| $V_{POR\_R}$              | V <sub>BAT1</sub> threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V <sub>BAT1</sub> rising                                      | 3     | 3.4  | 3.8  | V    |

| V <sub>POR_F</sub>        | V <sub>BAT1</sub> threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V <sub>BAT1</sub> falling                                     | 2.8   | 3.2  | 3.6  | V    |

| scillator                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                               |       |      |      |      |

| f <sub>osc</sub>          | Oscillator frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                             | 4.08  | 4.8  | 5.52 | MHz  |

| f <sub>IN</sub>           | Input frequency at SYNCIN pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                                                             | 1.8   | _    | 2.76 | MHz  |

| VH <sub>SYNC</sub>        | SYNCIN high threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                                                             | 2.1   | _    | _    | V    |

| VL <sub>SYNC</sub>        | SYNCIN low threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                             | _     | _    | 1    | V    |

| REG                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                               |       |      |      |      |

| $V_{VREG}$                | BUCK1 gate driver inner regulated supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I <sub>VREG</sub> = 0 mA~50 mA, EXTSUP = 6.3~12 V             | 5.8   | 6.0  | 6.2  | V    |

| V <sub>EXTSUP_TH</sub>    | Switch over threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I <sub>VREG</sub> = 5 mA~50 mA, EXTSUP rising, in ACTIVE mode | _     | 4.7  | _    |      |

| V <sub>EXTSUP_HYS</sub>   | Switch over hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _                                                             | _     | 0.2  | -    | V    |

| W                         | Daniel and Aller | I <sub>load</sub> = 50 mA, supplied by VBAT1                  | _     | _    | 0.25 | V    |

| V <sub>DROP_</sub> VREG   | Drop out voltage at VREG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I <sub>load</sub> = 50 mA, supplied by EXTSUP                 | _     | _    | 0.4  | V    |

| I <sub>LIM_REG</sub>      | VREG current limitation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Supplied by VBAT1/EXTSUP                                      | 60    | 85   | -    | mA   |

| C <sub>VREG</sub>         | Capacitive load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _                                                             | _     | 2.2  | _    | μF   |

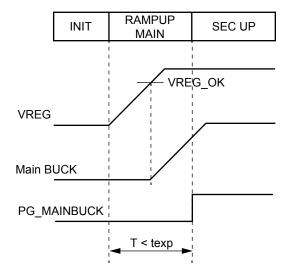

| V <sub>REG_OK</sub>       | VREG under voltage threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | VREG rising                                                   | _     | 4    | _    | V    |

| V <sub>REG_OK</sub>       | VREG under voltage threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Hysteresis                                                    | _     | 0.26 | _    | V    |

| UCK1                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                               |       |      |      |      |

| V <sub>IN_BUCK1</sub>     | Input voltage range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                                                             | 4     | _    | 32   | V    |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | OTP = 000                                                     |       | 5.0  |      | V    |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | OTP = 001                                                     |       | 3.8  |      | V    |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | OTP = 010                                                     |       | 3.3  |      | V    |