**Documents**

**ADS54J40**

SBAS714B - MAY 2015 - REVISED JANUARY 2017

# ADS54J40 Dual-Channel, 14-Bit, 1.0-GSPS Analog-to-Digital Converter

#### **Features**

14-Bit Resolution, Dual-Chanel, 1-GSPS ADC

Noise Floor: -158 dBFS/Hz

Spectral Performance ( $f_{IN} = 170 \text{ MHz at } -1 \text{ dBFS}$ ):

SNR: 69.0 dBFS

NSD: –155.9 dBFS/Hz

SFDR: 86 dBc

SFDR: 89 dBc (Except HD2, HD3, and

Interleaving Tones)

Spectral Performance ( $f_{IN} = 350 \text{ MHz at } -1 \text{ dBFS}$ ):

**SNR: 66.3 dBFS**

NSD: –153.3 dBFS/Hz

SFDR: 75 dBc

SFDR: 85 dBc (Except HD2, HD3, and

Interleaving Tones)

Channel Isolation: 100 dBc at f<sub>IN</sub> = 170 MHz

Input Full-Scale: 1.9 V<sub>PP</sub>

Input Bandwidth (3 dB): 1.2 GHz

On-Chip Dither

Integrated Wideband DDC Block

JESD204B Interface with Subclass 1 Support:

2 Lanes per ADC at 10.0 Gbps

4 Lanes per ADC at 5.0 Gbps

Support for Multi-Chip Synchronization

Power Dissipation: 1.35 W/ch at 1 GSPS

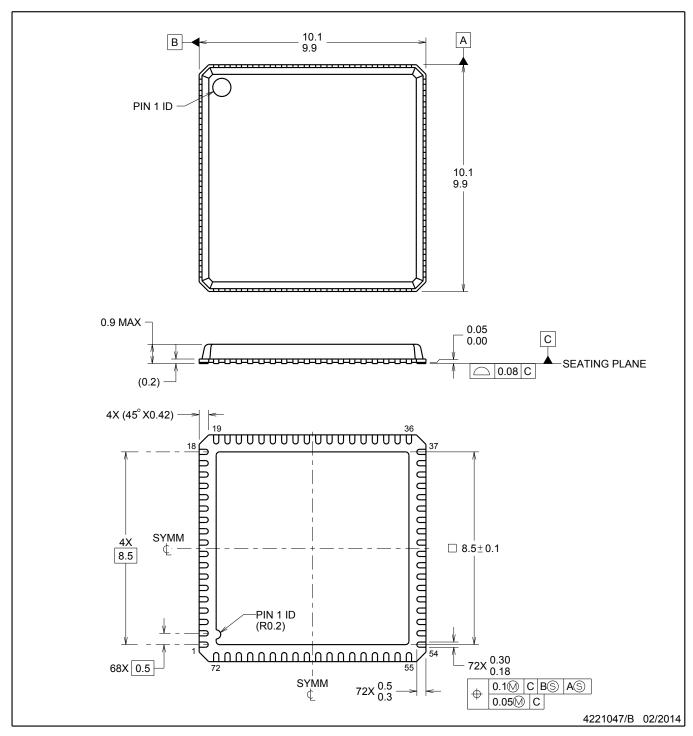

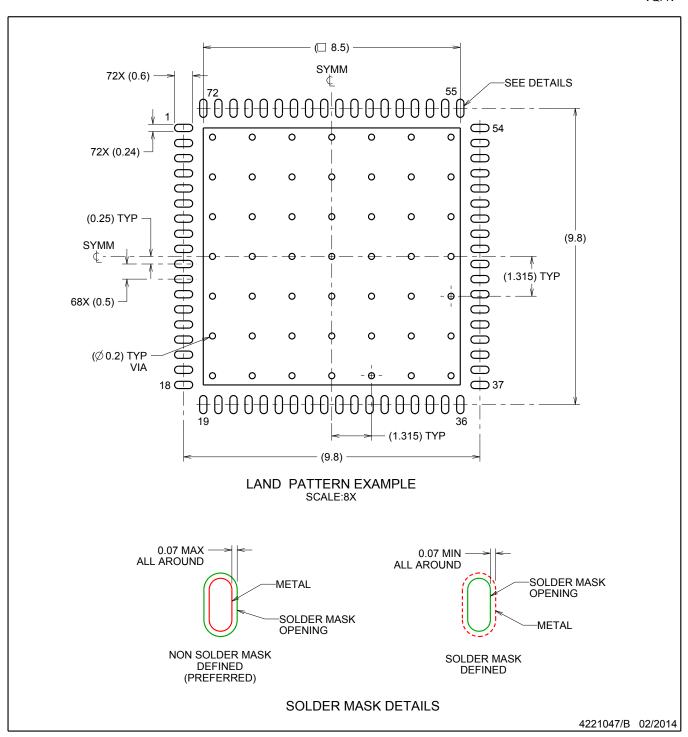

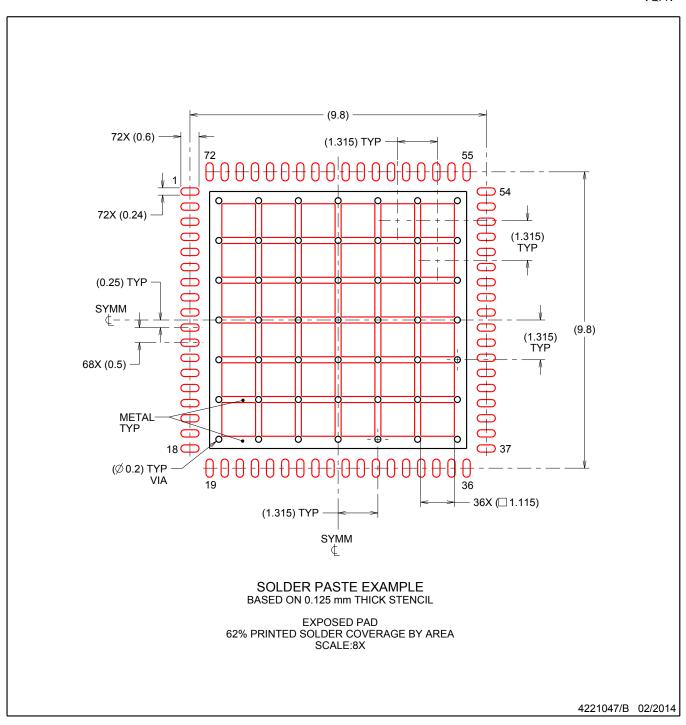

Package: 72-Pin VQFNP (10 mm x 10 mm)

## Applications

- Radar and Antenna Arrays

- **Broadband Wireless**

- Cable CMTS, DOCSIS 3.1 Receivers

- Communications Test Equipment

- Microwave Receivers

- Software Defined Radio (SDR)

- Digitizers

- Medical Imaging and Diagnostics

### 3 Description

The ADS54J40 is a low-power, wide-bandwidth, 14-1.0-GSPS, dual-channel, analog-to-digital converter (ADC). Designed for high signal-to-noise ratio (SNR), the device delivers a noise floor of -158 dBFS/Hz for applications aiming for highest dynamic range over a wide instantaneous bandwidth. The device supports the JESD204B serial interface with data rates up to 10.0 Gbps, supporting two or four lanes per ADC. The buffered analog input provides uniform input impedance across a wide frequency range and minimizes sample-and-hold glitch energy. Each ADC channel optionally can be connected to a wideband digital down-converter (DDC) block. The ADS54J40 provides excellent spurious-free dynamic range (SFDR) over a large input frequency range with very low power consumption.

The JESD204B interface reduces the number of interface lines, allowing high system integration density. An internal phase-locked loop (PLL) multiplies the ADC sampling clock to derive the bit clock that is used to serialize the 14-bit data from each channel.

#### **Device Information**

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)     |

|-------------|------------|---------------------|

| ADS54J40    | VQFNP (72) | 10.00 mm × 10.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

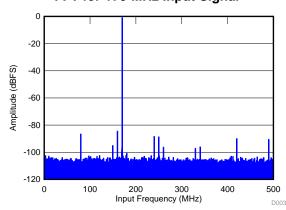

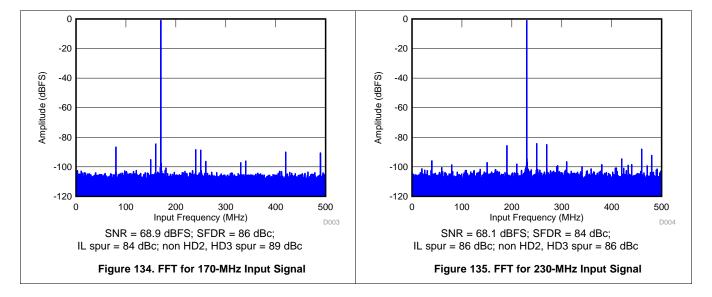

#### FFT for 170-MHz Input Signal

SNR = 69 dBFS; SFDR = 86 dBc;  $f_{IN}$  = 170 MHz, IL spur = 84 dBc; non HD2, HD3 spur = 89 dBc

### **Table of Contents**

| 1 | Features 1                           |    | 8.3 Feature Description                             | 24           |

|---|--------------------------------------|----|-----------------------------------------------------|--------------|

| 2 | Applications 1                       |    | 8.4 Device Functional Modes                         | 32           |

| 3 | Description 1                        |    | 8.5 Register Maps                                   | 43           |

| 4 | Revision History                     | 9  | Application and Implementation                      | . 68         |

| 5 | Device Comparison Table3             |    | 9.1 Application Information                         | 68           |

| 6 | Pin Configuration and Functions 4    |    | 9.2 Typical Application                             | 73           |

| 7 | Specifications                       | 10 | Power Supply Recommendations                        | . 75         |

| ′ | 7.1 Absolute Maximum Ratings         |    | 10.1 Power Sequencing and Initialization            | 76           |

|   | 7.1 Absolute Maximum Ratings         | 11 | Layout                                              | . 77         |

|   | 7.3 Recommended Operating Conditions |    | 11.1 Layout Guidelines                              | 77           |

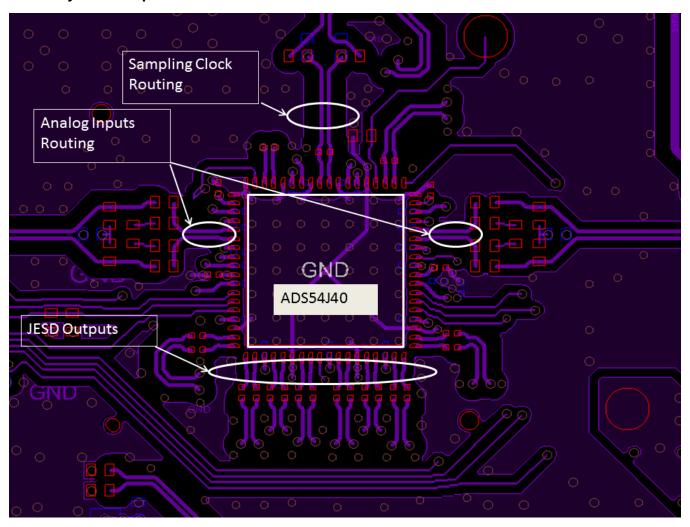

|   | 7.4 Thermal Information              |    | 11.2 Layout Example                                 |              |

|   | 7.5 Electrical Characteristics       | 12 | Device and Documentation Support                    | . 79         |

|   | 7.6 AC Characteristics               |    | 12.1 Documentation Support                          | 79           |

|   | 7.7 Digital Characteristics          |    | 12.2 Receiving Notification of Documentation Update | s 79         |

|   | 7.8 Timing Characteristics           |    | 12.3 Community Resources                            | 79           |

|   | 7.9 Typical Characteristics          |    | 12.4 Trademarks                                     | 79           |

| 8 | Detailed Description                 |    | 12.5 Electrostatic Discharge Caution                | 79           |

| Ū | 8.1 Overview                         |    | 12.6 Glossary                                       | 79           |

|   | 8.2 Functional Block Diagram         | 13 | Mechanical, Packaging, and Orderable Information    | . <b>7</b> 9 |

### 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Chai | nges from Revision A (October 2015) to Revision B                                                              | Page   |

|------|----------------------------------------------------------------------------------------------------------------|--------|

| • A  | Added Device Comparison Table                                                                                  | 4      |

|      | Added CDM row to ESD Ratings table                                                                             |        |

| • C  | Changed the minimum value for the input clock frequency in the Recommended Operating Conditions table          | 6      |

| • C  | Changed Sample Timing, Aperture jitter parameter typical specification in Timing Characteristics section       | 12     |

| • A  | Added the FOVR latency parameter to the Timing Characteristics table                                           | 12     |

| • C  | Changed Overview section                                                                                       | 23     |

| • C  | Changed Functional Block Diagram section: changed Control and SPI block and added dashed outline to FOVR trace | ces 23 |

| • C  | Changed SYSREF Signal section: changed Table 4 and added last paragraph                                        | 28     |

| • A  | Added SYSREF Not Present (Subclass 0, 2) section                                                               | 29     |

| • C  | Changed the number of clock cycles in the Fast OVR section                                                     | 30     |

| • D  | Deleted Lane Enable with Decimation subsection                                                                 | 39     |

| • A  | Added the Program Summary of DDC Modes and JESD Link Configuration tabletable                                  | 41     |

| • A  | Added Figure 80 to Register Maps section                                                                       | 43     |

| • C  | Changed the Register Map                                                                                       | 44     |

| • D  | Deleted register 39h, 3Ah, and 56h                                                                             | 44     |

| • A  | Added Table 53                                                                                                 | 61     |

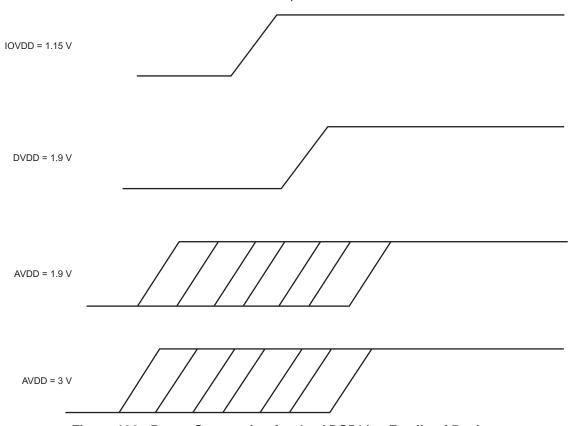

| • C  | Changed Power Supply Recommendations section                                                                   | 75     |

| • A  | Added the Power Sequencing and Initialization section                                                          | 76     |

| • A  | Added the Receiving Notification of Documentation Updates section                                              | 79     |

Changes from Original (May 2015) to Revision A

Page

# 5 Device Comparison Table

| PART NUMBER | SPEED GRADE (MSPS) | RESOLUTION (Bits) | CHANNEL |

|-------------|--------------------|-------------------|---------|

| ADS54J20    | 1000               | 12                | 2       |

| ADS54J42    | 625                | 14                | 2       |

| ADS54J40    | 1000               | 14                | 2       |

| ADS54J60    | 1000               | 16                | 2       |

| ADS54J66    | 500                | 14                | 4       |

| ADS54J69    | 500                | 16                | 2       |

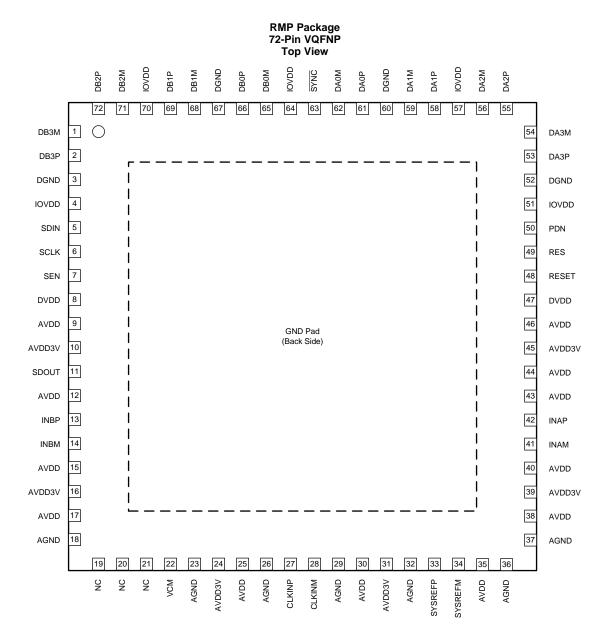

## 6 Pin Configuration and Functions

### **Pin Functions**

|            | PIN                                              |     |                                                                                                                                                                                                      |  |  |  |

|------------|--------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME       | NO.                                              | I/O | DESCRIPTION                                                                                                                                                                                          |  |  |  |

| CLOCK, SYS | REF                                              |     |                                                                                                                                                                                                      |  |  |  |

| CLKINM     | 28                                               | I   | Negative differential clock input for the ADC                                                                                                                                                        |  |  |  |

| CLKINP     | 27                                               | I   | Positive differential clock input for the ADC                                                                                                                                                        |  |  |  |

| SYSREFM    | 34                                               | ı   | Negative external SYSREF input                                                                                                                                                                       |  |  |  |

| SYSREFP    | 33                                               | ı   | Positive external SYSREF input                                                                                                                                                                       |  |  |  |

| CONTROL, S | ERIAL                                            |     |                                                                                                                                                                                                      |  |  |  |

| PDN        | 50                                               | I/O | Power down. Can be configured via an SPI register setting. Can be configured to fast overrange output for channel A via the SPI.                                                                     |  |  |  |

| RESET      | 48                                               | ı   | Hardware reset; active high. This pin has an internal 20-kΩ pulldown resistor.                                                                                                                       |  |  |  |

| SCLK       | 6                                                | ı   | Serial interface clock input                                                                                                                                                                         |  |  |  |

| SDIN       | 5                                                | ı   | Serial interface data input                                                                                                                                                                          |  |  |  |

| SDOUT      | 11                                               | 0   | Serial interface data output. Can be configured to fast overrange output for channel B via the SPI.                                                                                                  |  |  |  |

| SEN        | 7                                                | ı   | Serial interface enable                                                                                                                                                                              |  |  |  |

| DATA INTER | FACE                                             |     |                                                                                                                                                                                                      |  |  |  |

| DA0M       | 62                                               |     |                                                                                                                                                                                                      |  |  |  |

| DA1M       | 59                                               |     |                                                                                                                                                                                                      |  |  |  |

| DA2M       | 56                                               | 0   | JESD204B serial data negative outputs for channel A                                                                                                                                                  |  |  |  |

| DA3M       | 54                                               |     |                                                                                                                                                                                                      |  |  |  |

| DA0P       | 61                                               |     |                                                                                                                                                                                                      |  |  |  |

| DA1P       | 58                                               |     |                                                                                                                                                                                                      |  |  |  |

| DA2P       | 55                                               | 0   | JESD204B serial data positive outputs for channel A                                                                                                                                                  |  |  |  |

| DA3P       | 53                                               |     |                                                                                                                                                                                                      |  |  |  |

| DB0M       | 65                                               |     |                                                                                                                                                                                                      |  |  |  |

| DB1M       | 68                                               |     |                                                                                                                                                                                                      |  |  |  |

| DB2M       | 71                                               | 0   | JESD204B serial data negative outputs for channel B                                                                                                                                                  |  |  |  |

| DB3M       | 1                                                |     |                                                                                                                                                                                                      |  |  |  |

| DB0P       | 66                                               |     |                                                                                                                                                                                                      |  |  |  |

| DB1P       | 69                                               |     |                                                                                                                                                                                                      |  |  |  |

| DB2P       | 72                                               | 0   | JESD204B serial data positive outputs for channel B                                                                                                                                                  |  |  |  |

| DB3P       | 2                                                |     |                                                                                                                                                                                                      |  |  |  |

| SYNC       | 63                                               | ı   | Synchronization input for the JESD204B port                                                                                                                                                          |  |  |  |

| INPUT, COM | MON MODE                                         |     |                                                                                                                                                                                                      |  |  |  |

| INAM       | 41                                               | ı   | Differential analog negative input for channel A                                                                                                                                                     |  |  |  |

| INAP       | 42                                               | ı   | Differential analog positive input for channel A                                                                                                                                                     |  |  |  |

| INBM       | 14                                               | ı   | Differential analog negative input for channel B                                                                                                                                                     |  |  |  |

| INBP       | 13                                               | ļ   | Differential analog positive input for channel B                                                                                                                                                     |  |  |  |

| VCM        | 22                                               | 0   | Common-mode voltage, 2.1 V. Note that analog inputs are internally biased to this pin through 600 $\Omega$ (effective), no external connection from the VCM pin to the INxP or INxM pin is required. |  |  |  |

| POWER SUP  | PLY                                              |     |                                                                                                                                                                                                      |  |  |  |

| AGND       | 18, 23, 26, 29, 32, 36, 37                       | I   | Analog ground                                                                                                                                                                                        |  |  |  |

| AVDD       | 9, 12, 15, 17, 25, 30, 35, 38,<br>40, 43, 44, 46 | Ţ   | Analog 1.9-V power supply                                                                                                                                                                            |  |  |  |

| AVDD3V     | 10, 16, 24, 31, 39, 45                           | I   | Analog 3.0-V power supply for the analog buffer                                                                                                                                                      |  |  |  |

| DGND       | 3, 52, 60, 67                                    | 1   | Digital ground                                                                                                                                                                                       |  |  |  |

| DVDD       | 8, 47                                            | I   | Digital 1.9-V power supply                                                                                                                                                                           |  |  |  |

| IOVDD      | 4, 51, 57, 64, 70                                | 1   | Digital 1.15-V power supply for the JESD204B transmitter                                                                                                                                             |  |  |  |

| NC, RES    |                                                  |     |                                                                                                                                                                                                      |  |  |  |

| NC         | 19-21                                            | _   | Unused pins, do not connect                                                                                                                                                                          |  |  |  |

| RES        | 49                                               | I   | Reserved pin. Connect to DGND.                                                                                                                                                                       |  |  |  |

### 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                       |                                   | MIN  | MAX        | UNIT |

|---------------------------------------|-----------------------------------|------|------------|------|

|                                       | AVDD3V                            | -0.3 | 3.6        |      |

| Cumply voltage range                  | AVDD                              | -0.3 | 2.1        | V    |

| Supply voltage range                  | DVDD                              | -0.3 | 2.1        | V    |

|                                       | IOVDD                             | -0.2 | 1.4        |      |

| Voltage between AGND and I            | DGND                              | -0.3 | 0.3        | V    |

|                                       | INAP, INBP, INAM, INBM            | -0.3 | 3          |      |

| Valtage applied to input pine         | CLKINP, CLKINM                    | -0.3 | AVDD + 0.3 | V    |

| Voltage applied to input pins         | SYSREFP, SYSREFM                  | -0.3 | AVDD + 0.3 | V    |

|                                       | SCLK, SEN, SDIN, RESET, SYNC, PDN | -0.2 | 2.1        |      |

| Storage temperature, T <sub>stg</sub> |                                   | -65  | 150        | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

| V                  | Floatrootatio diocharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±1000 | \/   |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                          |                                                                                          |                       | MIN                | NOM                | MAX  | UNIT     |

|--------------------------|------------------------------------------------------------------------------------------|-----------------------|--------------------|--------------------|------|----------|

| Supply voltage range     | AVDD3V                                                                                   |                       | 2.85               | 3.0                | 3.6  |          |

|                          | AVDD                                                                                     |                       | 1.8                | 1.9                | 2.0  | V        |

| Supply voltage range     | DVDD                                                                                     |                       | 1.7                | 1.9                | 2.0  | V        |

|                          | IOVDD                                                                                    |                       | 1.1                | 1.15               | 1.2  |          |

|                          | Differential input voltage range                                                         |                       |                    | 1.9                |      | $V_{PP}$ |

| Analog inputs            | Input common-mode voltage                                                                |                       |                    | 2.0                |      | V        |

|                          | Maximum analog input frequency for 1.9-V <sub>PP</sub> input amplitude <sup>(3)(4)</sup> |                       |                    | 400                |      | MHz      |

|                          | Input clock frequency, device clock frequency                                            |                       | 250 <sup>(5)</sup> |                    | 1000 | MHz      |

|                          |                                                                                          | Sine wave, ac-coupled | 0.75               | 1.5                |      |          |

| Clock inputs             | Input clock amplitude differential (V <sub>CLKP</sub> – V <sub>CLKM</sub> )              | LVPECL, ac-coupled    | 0.8                | 1.6                |      | $V_{PP}$ |

|                          | (*CERP *CERIVI)                                                                          | LVDS, ac-coupled      |                    | 0.7                |      |          |

|                          | Input device clock duty cycle                                                            |                       | 45%                | 50%                | 55%  |          |

| Clock inputs Temperature | Operating free-air, T <sub>A</sub>                                                       |                       | -40                |                    | 85   | °C       |

|                          | Operating junction, T <sub>J</sub>                                                       |                       |                    | 105 <sup>(6)</sup> | 125  | ,<br>U   |

<sup>1)</sup> SYSREF must be applied for the device to initialize; see the SYSREF Signal section for details.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V HBM allows safe manufacturing with a standard ESD control process.

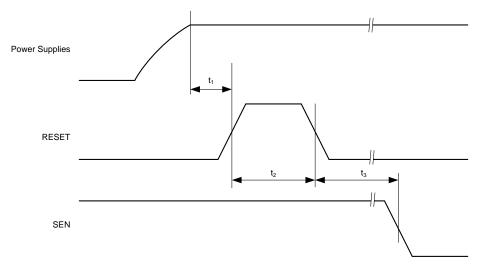

<sup>(2)</sup> After power-up, always use a hardware reset to reset the device for the first time; see Table 67 for details.

<sup>(3)</sup> Operating 0.5 dB below the maximum-supported amplitude is recommended to accommodate gain mismatch in interleaving ADCs.

<sup>4)</sup> At high frequencies, the maximum supported input amplitude reduces; see Figure 36 for details.

<sup>(5)</sup> See Table 10.

<sup>(6)</sup> Prolonged use above the nominal junction temperature can increase the device failure-in-time (FIT) rate.

#### 7.4 Thermal Information

|                      |                                              | ADS54J40    |      |

|----------------------|----------------------------------------------|-------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RMP (VQFNP) | UNIT |

|                      |                                              | 72 PINS     |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 22.3        | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 5.1         | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 2.4         | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.1         | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 2.3         | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 0.4         | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 7.5 Electrical Characteristics

Typical values are at  $T_A = 25$ °C, full temperature range is from  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, ADC sampling rate = 1.0 GSPS, 50% clock duty cycle, AVDD3V = 3.0 V, AVDD = DVDD = 1.9 V, IOVDD = 1.15 V, -1-dBFS differential input, and 0-dB digital gain (unless otherwise noted)

|                                 | PARAMETER                           | TEST CONDITIONS                                | MIN  | TYP  | MAX  | UNIT |

|---------------------------------|-------------------------------------|------------------------------------------------|------|------|------|------|

| GENERAL                         |                                     |                                                |      |      |      |      |

|                                 | ADC sampling rate                   |                                                |      |      | 1000 | MSPS |

|                                 | Resolution                          |                                                | 14   |      |      | Bits |

| POWER SUP                       | PLIES                               |                                                |      |      |      |      |

| AVDD3V                          | 3.0-V analog supply                 |                                                | 2.85 | 3.0  | 3.6  | V    |

| AVDD                            | 1.9-V analog supply                 |                                                | 1.8  | 1.9  | 2.0  | V    |

| DVDD                            | 1.9-V digital supply                |                                                | 1.7  | 1.9  | 2.0  | V    |

| IOVDD                           | 1.15-V SERDES supply                |                                                | 1.1  | 1.15 | 1.2  | V    |

| I <sub>AVDD3V</sub>             | 3.0-V analog supply current         | V <sub>IN</sub> = full-scale on both channels  |      | 334  | 360  | mA   |

| I <sub>AVDD</sub>               | 1.9-V analog supply current         | V <sub>IN</sub> = full-scale on both channels  |      | 359  | 510  | mA   |

| I <sub>DVDD</sub>               | 1.9-V digital supply current        | Eight lanes active (LMFS = 8224)               |      | 197  | 260  | mA   |

| I <sub>IOVDD</sub>              | 1.15-V SERDES supply current        | Eight lanes active (LMFS = 8224)               |      | 566  | 920  | mA   |

| P <sub>dis</sub>                | Total power dissipation             | Eight lanes active (LMFS = 8224)               |      | 2.71 | 3.1  | W    |

| I <sub>DVDD</sub>               | 1.9-V digital supply current        | Four lanes active (LMFS = 4244)                |      | 211  |      | mA   |

| I <sub>IOVDD</sub>              | 1.15-V SERDES supply current        | Four lanes active (LMFS = 4244)                |      | 618  |      | mA   |

| P <sub>dis</sub>                | Total power dissipation             | Four lanes active (LMFS = 4244)                |      | 2.80 |      | W    |

| I <sub>DVDD</sub>               | 1.9-V digital supply current        | Four lanes active (LMFS = 4222), 2X decimation |      | 197  |      | mA   |

| I <sub>IOVDD</sub>              | 1.15-V SERDES supply current        | Four lanes active (LMFS = 4222), 2X decimation |      | 593  |      | mA   |

| P <sub>dis</sub>                | Total power dissipation             | Four lanes active (LMFS = 4222), 2X decimation |      | 2.74 |      | W    |

| I <sub>DVDD</sub>               | 1.9-V digital supply current        | Two lanes active (LMFS = 2221), 4X decimation  |      | 176  |      | mA   |

| I <sub>IOVDD</sub>              | 1.15-V SERDES supply current        | Two lanes active (LMFS = 2221), 4X decimation  |      | 562  |      | mA   |

| P <sub>dis</sub> <sup>(1)</sup> | Total power dissipation             | Two lanes active (LMFS = 2221), 4X decimation  |      | 2.66 |      | W    |

|                                 | Global power-down power dissipation |                                                |      | 139  | 315  | mW   |

<sup>(1)</sup> See the *Power-Down Mode* section for details.

### **Electrical Characteristics (continued)**

Typical values are at  $T_A = 25$ °C, full temperature range is from  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, ADC sampling rate = 1.0 GSPS, 50% clock duty cycle, AVDD3V = 3.0 V, AVDD = DVDD = 1.9 V, IOVDD = 1.15 V, -1-dBFS differential input, and 0-dB digital gain (unless otherwise noted)

|                 | PARAMETER                             | TEST CONDITIONS                                                           | MIN | TYP  | MAX | UNIT            |

|-----------------|---------------------------------------|---------------------------------------------------------------------------|-----|------|-----|-----------------|

| ANALOG          | INPUTS (INAP, INAM, INBP, INBM)       |                                                                           |     |      |     |                 |

|                 | Differential input full-scale voltage |                                                                           |     | 1.9  |     | V <sub>PP</sub> |

| $V_{IC}$        | Common-mode input voltage             |                                                                           |     | 2.0  |     | V               |

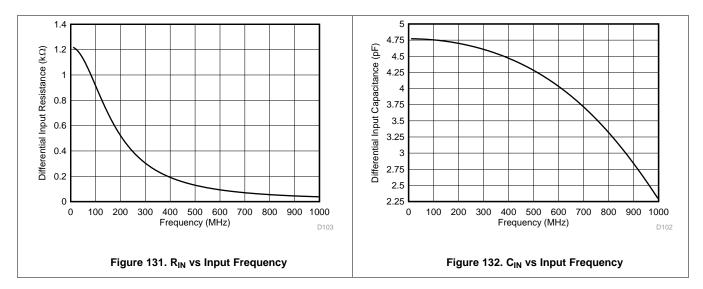

| R <sub>IN</sub> | Differential input resistance         | At 170-MHz input frequency                                                |     | 0.6  |     | $k\Omega$       |

| C <sub>IN</sub> | Differential input capacitance        | At 170-MHz input frequency                                                |     | 4.7  |     | рF              |

|                 | Analog input bandwidth (3 dB)         | 50- $\Omega$ source driving ADC inputs terminated with 50 $\Omega$        |     | 1.2  |     | GHz             |

| CLOCK IN        | IPUT (CLKINP, CLKINM)                 |                                                                           |     |      |     |                 |

|                 | Internal clock biasing                | CLKINP and CLKINM are connected to internal biasing voltage through 400 Ω |     | 1.15 |     | V               |

#### 7.6 AC Characteristics

Typical values are at  $T_A$  = 25°C, full temperature range is from  $T_{MIN}$  = -40°C to  $T_{MAX}$  = 85°C, ADC sampling rate = 1.0 GSPS, 50% clock duty cycle, AVDD3V = 3.0 V, AVDD = DVDD = 1.9 V, IOVDD = 1.15 V, -1-dBFS differential input, and 0-dB digital gain (unless otherwise noted)

|       | PARAMETER                            | TEST CONDITIONS                                      | MIN   | TYP   | MAX | UNIT    |

|-------|--------------------------------------|------------------------------------------------------|-------|-------|-----|---------|

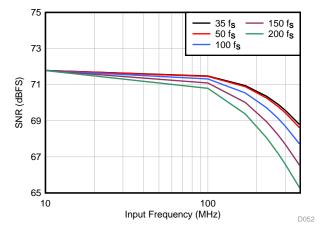

|       |                                      | $f_{IN} = 10 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$  |       | 69.7  |     |         |

|       |                                      | $f_{IN} = 100 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 69.5  |     |         |

|       |                                      | $f_{IN} = 170 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ | 66.2  | 68.9  |     |         |

| SNR   | Signal-to-noise ratio                | $f_{IN} = 230 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 68.4  |     | dBFS    |

| SINK  | Signal-to-hoise ratio                | $f_{IN} = 270 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 67.9  |     | UDFS    |

|       |                                      | $f_{IN} = 300 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 67.5  |     |         |

|       |                                      | $f_{IN} = 370 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 66.5  |     |         |

|       |                                      | $f_{IN} = 470 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 66    |     |         |

|       |                                      | $f_{IN} = 10 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$  |       | 156.7 |     |         |

|       |                                      | $f_{IN} = 100 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 156.5 |     | dBFS/Hz |

|       | Noise encetral density               | $f_{IN} = 170 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ | 153.2 | 155.9 |     |         |

| NSD   |                                      | $f_{IN} = 230 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 155.4 |     |         |

| NOD   | Noise spectral density               | $f_{IN} = 270 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 154.9 |     |         |

|       |                                      | $f_{IN} = 300 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 154.5 |     |         |

|       |                                      | $f_{IN} = 370 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 153.5 |     |         |

|       |                                      | $f_{IN} = 470 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 153.0 |     |         |

|       |                                      | $f_{IN} = 10 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$  |       | 69.6  |     |         |

|       |                                      | $f_{IN} = 100 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 69.3  |     |         |

|       |                                      | $f_{IN} = 170 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ | 65.2  | 68.8  |     |         |

| SINAD | Cional to maios and distantian votic | $f_{IN} = 230 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 68.3  |     | 4DEC    |

| SINAD | Signal-to-noise and distortion ratio | $f_{IN} = 270 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 67.6  |     | dBFS    |

|       |                                      | $f_{IN} = 300 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 67    |     |         |

|       |                                      | $f_{IN} = 370 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 65.5  |     |         |

|       |                                      | $f_{IN} = 470 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |       | 64.5  |     |         |

### **AC Characteristics (continued)**

Typical values are at  $T_A$  = 25°C, full temperature range is from  $T_{MIN}$  = -40°C to  $T_{MAX}$  = 85°C, ADC sampling rate = 1.0 GSPS, 50% clock duty cycle, AVDD3V = 3.0 V, AVDD = DVDD = 1.9 V, IOVDD = 1.15 V, -1-dBFS differential input, and 0-dB digital gain (unless otherwise noted)

|          | PARAMETER                         | TEST CONDITIONS                                      | MIN  | TYP  | MAX | UNIT |  |  |  |

|----------|-----------------------------------|------------------------------------------------------|------|------|-----|------|--|--|--|

|          |                                   | $f_{IN} = 10 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$  |      | 85   |     |      |  |  |  |

|          |                                   | $f_{IN} = 100 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |      | 83   |     |      |  |  |  |

|          | Spurious free dynamic range       | $f_{IN} = 170 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ | 76   | 86   |     | dBc  |  |  |  |

| CEDB     |                                   | $f_{IN} = 230 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |      | 85   |     |      |  |  |  |

|          | (excluding IL spurs)              | $f_{IN} = 270 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |      | 81   |     |      |  |  |  |

|          |                                   | $f_{IN} = 300 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |      | 78   |     |      |  |  |  |

|          |                                   | $f_{IN} = 370 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |      | 73   |     |      |  |  |  |

|          |                                   | $f_{IN} = 470 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |      | 69   |     |      |  |  |  |

|          |                                   | f <sub>IN</sub> = 10 MHz, A <sub>IN</sub> = -1 dBFS  |      | 85   |     |      |  |  |  |

|          |                                   | $f_{IN} = 100 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |      | 90   |     |      |  |  |  |

|          |                                   | $f_{IN} = 170 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ | 76   | 92   |     |      |  |  |  |

|          |                                   | $f_{IN} = 230 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |      | 85   |     | ın   |  |  |  |

| HD2      | Second-order harmonic distortion  | $f_{IN} = 270 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |      | 81   |     | dBc  |  |  |  |

|          |                                   | $f_{IN} = 300 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |      | 81   |     |      |  |  |  |

|          |                                   | f <sub>IN</sub> = 370 MHz, A <sub>IN</sub> = -1 dBFS |      | 76   |     |      |  |  |  |

|          |                                   | $f_{IN} = 470 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |      | 69   |     |      |  |  |  |

|          | Third-order harmonic distortion   | $f_{IN} = 10 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$  |      | 85   |     |      |  |  |  |

|          |                                   | $f_{IN} = 100 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |      | 83   |     | dBc  |  |  |  |

|          |                                   | f <sub>IN</sub> = 170 MHz, A <sub>IN</sub> = -1 dBFS | 76   | 86   |     |      |  |  |  |

|          |                                   | f <sub>IN</sub> = 230 MHz, A <sub>IN</sub> = -1 dBFS |      | 87   |     |      |  |  |  |

| HD3      |                                   | $f_{IN} = 270 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |      | 81   |     |      |  |  |  |

|          |                                   | $f_{IN} = 300 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |      | 78   |     |      |  |  |  |

|          |                                   | $f_{IN} = 370 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |      | 73   |     |      |  |  |  |

|          |                                   | f <sub>IN</sub> = 470 MHz, A <sub>IN</sub> = -1 dBFS |      | 70   |     |      |  |  |  |

|          |                                   | $f_{IN} = 10 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$  |      | 94   |     |      |  |  |  |

|          |                                   | $f_{IN} = 100 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |      | 97   |     |      |  |  |  |

|          |                                   | f <sub>IN</sub> = 170 MHz, A <sub>IN</sub> = -1 dBFS | 79   | 93   |     |      |  |  |  |

| Non      | Spurious-free dynamic range       | f <sub>IN</sub> = 230 MHz, A <sub>IN</sub> = -1 dBFS |      | 95   |     |      |  |  |  |

| HD2, HD3 | (excluding HD2, HD3, and IL spur) | f <sub>IN</sub> = 270 MHz, A <sub>IN</sub> = -1 dBFS |      | 95   |     | dBFS |  |  |  |

|          |                                   | f <sub>IN</sub> = 300 MHz, A <sub>IN</sub> = -1 dBFS |      | 91   |     |      |  |  |  |

|          |                                   | $f_{IN} = 370 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |      | 85   |     |      |  |  |  |

|          |                                   | $f_{IN} = 470 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |      | 88   |     |      |  |  |  |

|          |                                   | $f_{IN} = 10 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$  |      | 11.3 |     |      |  |  |  |

|          |                                   | $f_{IN} = 100 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |      | 11.2 |     |      |  |  |  |

|          |                                   | $f_{IN} = 170 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ | 10.5 | 11.1 |     |      |  |  |  |

|          |                                   | $f_{IN} = 230 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |      | 11.1 |     |      |  |  |  |

| ENOB     | Effective number of bits          | $f_{IN} = 270 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |      | 10.9 |     | dBFS |  |  |  |

|          |                                   | $f_{IN} = 300 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |      | 10.8 |     |      |  |  |  |

|          |                                   | $f_{IN} = 370 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |      | 10.6 |     |      |  |  |  |

|          |                                   | $f_{IN} = 470 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$ |      | 10.4 |     |      |  |  |  |

### **AC Characteristics (continued)**

Typical values are at  $T_A$  = 25°C, full temperature range is from  $T_{MIN}$  = -40°C to  $T_{MAX}$  = 85°C, ADC sampling rate = 1.0 GSPS, 50% clock duty cycle, AVDD3V = 3.0 V, AVDD = DVDD = 1.9 V, IOVDD = 1.15 V, -1-dBFS differential input, and 0-dB digital gain (unless otherwise noted)

|           | PARAMETER                                        | TEST CONDITIONS                                                                                                                           | MIN | TYP         | MAX | UNIT |

|-----------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|-----|------|

|           |                                                  | $f_{IN} = 10 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                                                                       |     | 82          |     |      |

|           |                                                  | $f_{IN} = 100 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                                                                      |     | 80          |     |      |

|           |                                                  | $f_{IN} = 170 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                                                                      | 73  | 83          |     |      |

| THD       | Total harmonic distortion                        | $f_{IN} = 230 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                                                                      |     | 82          |     | dBc  |

| טווו      | Total Harmonic distortion                        | $f_{IN} = 270 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                                                                      |     | 78          |     | ubc  |

|           |                                                  | $f_{IN} = 300 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                                                                      |     | 75          |     |      |

|           |                                                  | $f_{IN} = 370 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                                                                      |     | 70          |     |      |

|           |                                                  | $f_{IN} = 470 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                                                                      |     | 66          |     |      |

|           |                                                  | $f_{IN} = 10 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                                                                       |     | 84          |     |      |

|           | Interleaving spur                                | $f_{IN} = 100 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                                                                      |     | 85          |     | dBc  |

|           |                                                  | $f_{IN} = 170 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                                                                      | 69  | 84          |     |      |

| SFDR IL   |                                                  | $f_{IN} = 230 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                                                                      |     | 83          |     |      |

| OI DIX_IL | interieaving spur                                | $f_{IN} = 270 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                                                                      |     | 82          |     |      |

|           |                                                  | $f_{IN} = 300 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                                                                      |     | 81          |     |      |

|           |                                                  | $f_{IN} = 370 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                                                                      |     | 81          |     |      |

|           |                                                  | $f_{IN} = 470 \text{ MHz}, A_{IN} = -1 \text{ dBFS}$                                                                                      |     | 77          |     |      |

|           |                                                  | $\begin{aligned} f_{\text{IN1}} &= 185 \text{ MHz},  f_{\text{IN2}} = 190 \text{ MHz}, \\ A_{\text{IN}} &= -7 \text{ dBFS} \end{aligned}$ |     | -85         |     |      |

| IMD3      | Two-tone, third-order intermodulation distortion | $\begin{aligned} f_{\text{IN1}} &= 365 \text{ MHz},  f_{\text{IN2}} = 370 \text{ MHz}, \\ A_{\text{IN}} &= -7 \text{ dBFS} \end{aligned}$ |     | <b>-</b> 79 |     | dBFS |

|           |                                                  | $\begin{split} f_{\text{IN1}} &= 465 \text{ MHz},  f_{\text{IN2}} = 470 \text{ MHz}, \\ A_{\text{IN}} &= -7 \text{ dBFS} \end{split}$     |     | -75         |     |      |

| Crosstalk | Isolation between channel A and B                | Full-scale, 170-MHz signal on aggressor; idle channel is victim                                                                           |     | 100         |     | dB   |

### 7.7 Digital Characteristics

Typical values are at  $T_A = 25$ °C, full temperature range is from  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, ADC sampling rate = 1.0 GSPS, 50% clock duty cycle, AVDD3V = 3.0 V, AVDD = DVDD = 1.9 V, IOVDD = 1.15 V, -1-dBFS differential input, and 0-dB digital gain (unless otherwise noted)

|                       | PARAMETER                            | TEST CONDITIONS                                                    | MIN           | TYP  | MAX | UNITS     |

|-----------------------|--------------------------------------|--------------------------------------------------------------------|---------------|------|-----|-----------|

| DIGITAL I             | NPUTS (RESET, SCLK, SEN, SDIN, SYN   | IC, PDN) <sup>(1)</sup>                                            |               |      |     |           |

| V <sub>IH</sub>       | High-level input voltage             | All digital inputs support 1.2-V and 1.8-V logic levels            | 0.8           |      |     | V         |

| V <sub>IL</sub>       | Low-level input voltage              | All digital inputs support 1.2-V and 1.8-V logic levels            |               |      | 0.4 | V         |

|                       | High Invalidance comment             | SEN                                                                |               | 0    |     |           |

| I <sub>IH</sub>       | High-level input current             | RESET, SCLK, SDIN, PDN, SYNC                                       |               | 50   |     | μA        |

|                       | I am land in and amond               | SEN                                                                |               | 50   |     |           |

| I <sub>IL</sub>       | Low-level input current              | RESET, SCLK, SDIN, PDN, SYNC                                       |               | 0    |     | μA        |

| DIGITAL I             | NPUTS (SYSREFP, SYSREFM)             |                                                                    |               |      |     |           |

| V <sub>D</sub>        | Differential input voltage           |                                                                    | 0.35          | 0.45 | 1.4 | V         |

| V <sub>(CM_DIG)</sub> | Common-mode voltage for SYSREF       |                                                                    |               | 1.3  |     | V         |

| DIGITAL O             | OUTPUTS (SDOUT, PDN <sup>(2)</sup> ) |                                                                    |               |      |     |           |

| V <sub>OH</sub>       | High-level output voltage            |                                                                    | DVDD -<br>0.1 | DVDD |     | V         |

| V <sub>OL</sub>       | Low-level output voltage             |                                                                    |               |      | 0.1 | V         |

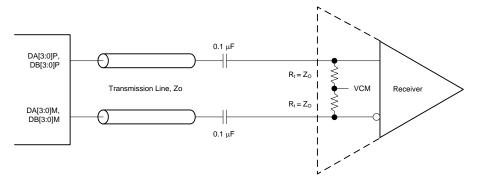

| DIGITAL O             | OUTPUTS (JESD204B Interface: DxP, Dx | кМ) <sup>(3)</sup>                                                 |               |      |     |           |

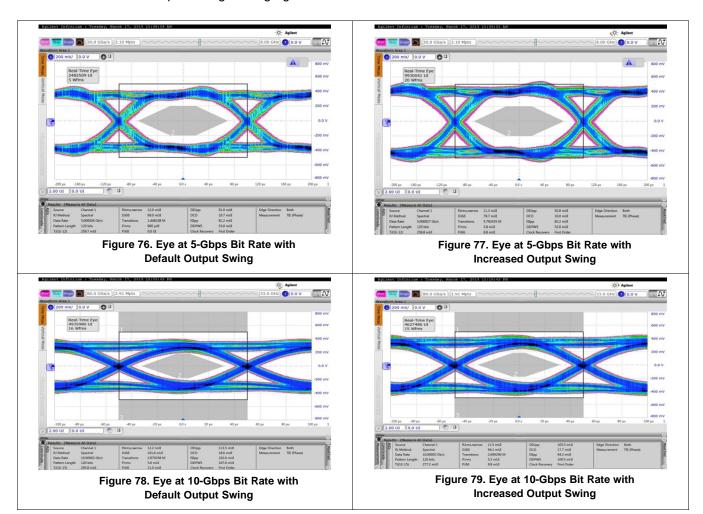

| V <sub>OD</sub>       | Output differential voltage          | With default swing setting                                         |               | 700  |     | $mV_{PP}$ |

| V <sub>oc</sub>       | Output common-mode voltage           |                                                                    |               | 450  |     | mV        |

|                       | Transmitter short-circuit current    | Transmitter pins shorted to any voltage between –0.25 V and 1.45 V | -100          |      | 100 | mA        |

| Z <sub>OS</sub>       | Single-ended output impedance        |                                                                    |               | 50   |     | Ω         |

|                       | Output capacitance                   | Output capacitance inside the device, from either output to ground |               | 2    |     | pF        |

<sup>(1)</sup> The RESET, SCLK, SDIN, and PDN pins have a 20-k $\Omega$  (typical) internal pulldown resistor to ground, and the SEN pin has a 20-k $\Omega$  (typical) pullup resistor to IOVDD.

<sup>(2)</sup> When functioning as an OVR pin for channel B.

<sup>(3)</sup>  $100-\Omega$  differential termination.

### 7.8 Timing Characteristics

Typical values are at  $T_A$  = 25°C, full temperature range is from  $T_{MIN}$  = -40°C to  $T_{MAX}$  = 85°C, ADC sampling rate = 1.0 GSPS, 50% clock duty cycle, AVDD3V = 3.0 V, AVDD = DVDD = 1.9 V, IOVDD = 1.15 V, and -1-dBFS differential input, unless otherwise noted.

|                                 |                                                                                                                                               | MIN  | TYP      | MAX | UNITS                    |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-----|--------------------------|

| SAMPLE T                        | IMING                                                                                                                                         |      |          |     |                          |

|                                 | Aperture delay                                                                                                                                | 0.75 |          | 1.6 | ns                       |

|                                 | Aperture delay matching between two channels on the same device                                                                               |      | ±70      |     | ps                       |

|                                 | Aperture delay matching between two devices at the same temperature and supply voltage                                                        |      | ±270     |     | ps                       |

|                                 | Aperture jitter                                                                                                                               |      | 120      |     | f <sub>S</sub> rms       |

| WAKE-UP                         | TIMING                                                                                                                                        |      |          |     |                          |

|                                 | Wake-up time to valid data after coming out of global power-down                                                                              |      | 150      |     | μs                       |

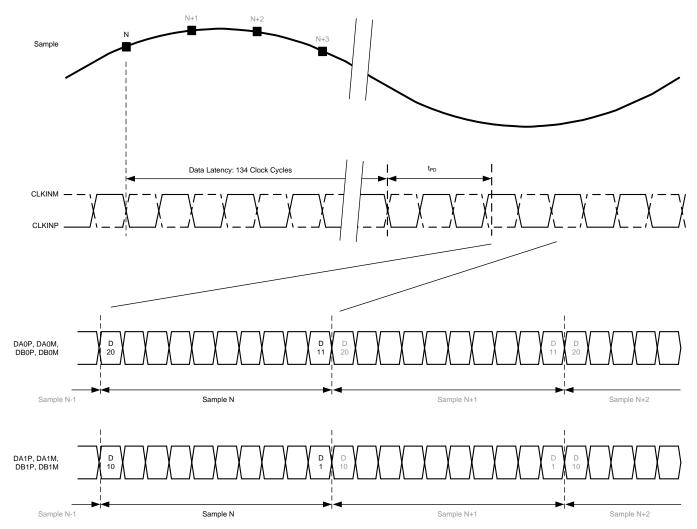

| LATENCY                         |                                                                                                                                               |      |          |     |                          |

|                                 | Data latency <sup>(1)</sup> : ADC sample to digital output                                                                                    |      | 134      |     | Input<br>clock<br>cycles |

|                                 | OVR latency: ADC sample to OVR bit                                                                                                            |      | 62       |     | Input<br>clock<br>cycles |

|                                 | FOVR latency: ADC sample to FOVR signal on pin                                                                                                | ,    | 8 + 4 ns |     | Input<br>clock<br>cycles |

| t <sub>PD</sub>                 | Propagation delay: logic gates and output buffers delay (does not change with f <sub>S</sub> )                                                |      | 4        |     | ns                       |

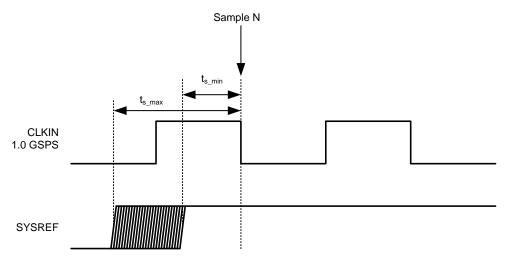

| SYSREF TI                       | MING                                                                                                                                          |      |          |     |                          |

| t <sub>SU_SYSREF</sub>          | Setup time for SYSREF, referenced to the input clock falling edge                                                                             | 300  |          | 900 | ps                       |

| t <sub>H_SYSREF</sub>           | Hold time for SYSREF, referenced to the input clock falling edge                                                                              | 100  |          |     | ps                       |

| JESD OUT                        | PUT INTERFACE TIMING CHARACTERISTICS                                                                                                          |      |          |     |                          |

|                                 | Unit interval                                                                                                                                 | 100  |          | 400 | ps                       |

|                                 | Serial output data rate                                                                                                                       | 2.5  |          | 10  | Gbps                     |

|                                 | Total jitter for BER of 1E-15 and lane rate = 10 Gbps                                                                                         |      | 26       |     | ps                       |

|                                 | Random jitter for BER of 1E-15 and lane rate = 10 Gbps                                                                                        |      | 0.75     |     | ps rms                   |

|                                 | Deterministic jitter for BER of 1E-15 and lane rate = 10 Gbps                                                                                 |      | 12       |     | ps, pk-pk                |

| t <sub>R</sub> , t <sub>F</sub> | Data rise time, data fall time: rise and fall times are measured from 20% to 80%, differential output waveform, 2.5 Gbps ≤ bit rate ≤ 10 Gbps |      | 35       |     | ps                       |

#### (1) Overall ADC latency = data latency + t<sub>PDI</sub>.

Figure 1. SYSREF Timing

Figure 2. Sample Timing Requirements

Submit Documentation Feedback

### 7.9 Typical Characteristics

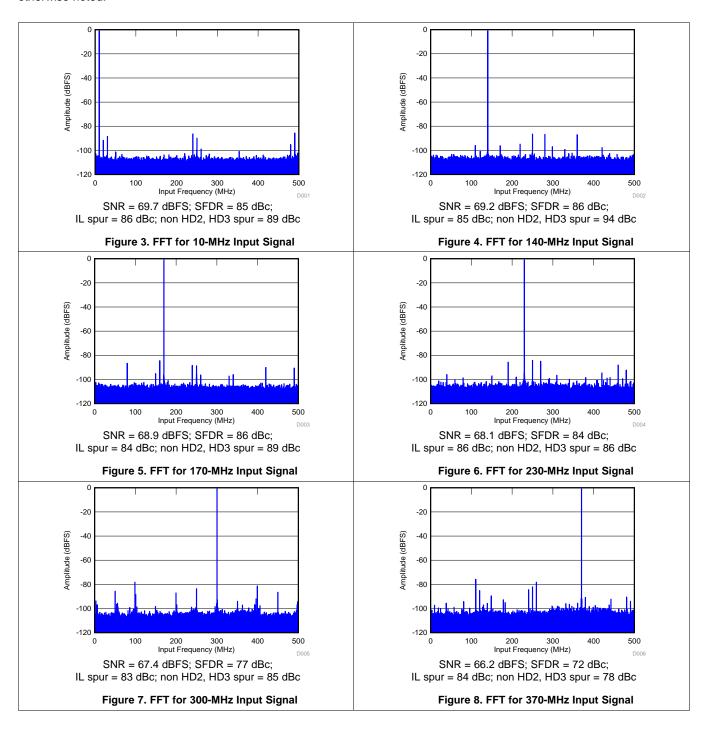

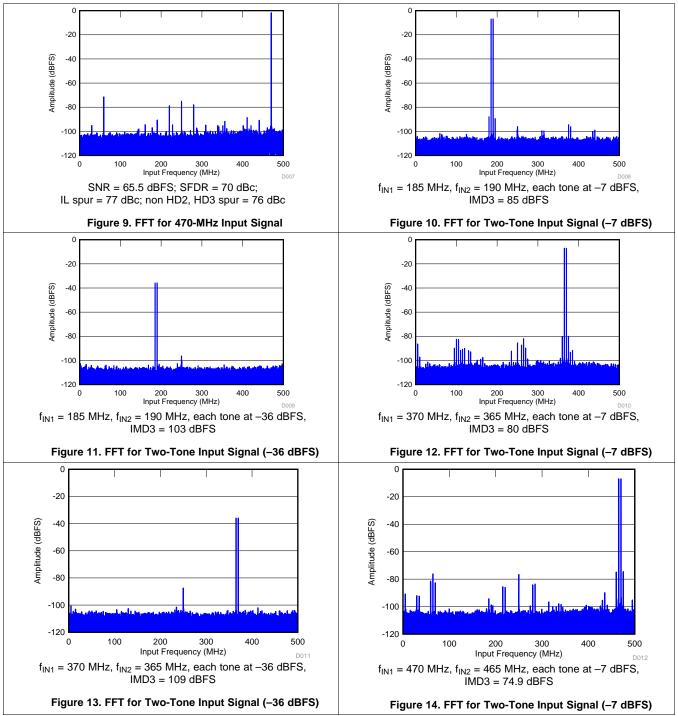

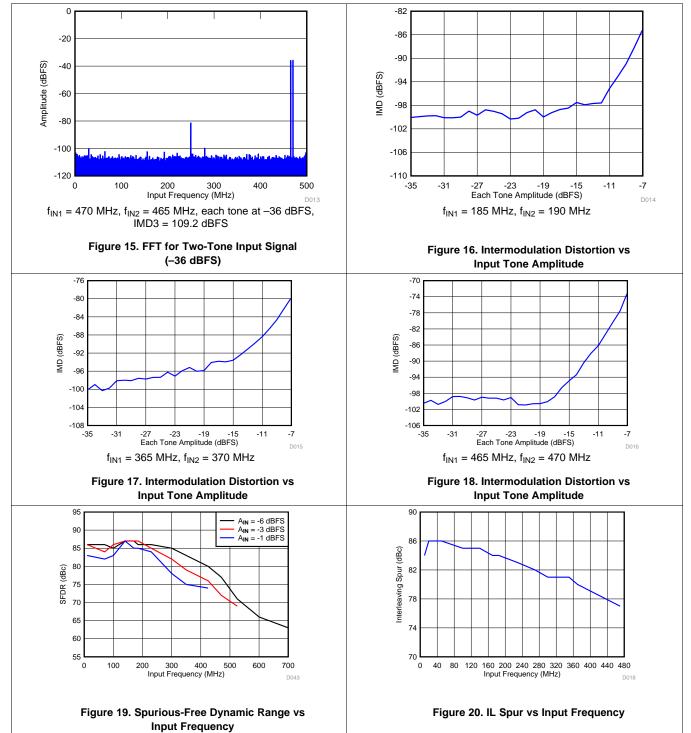

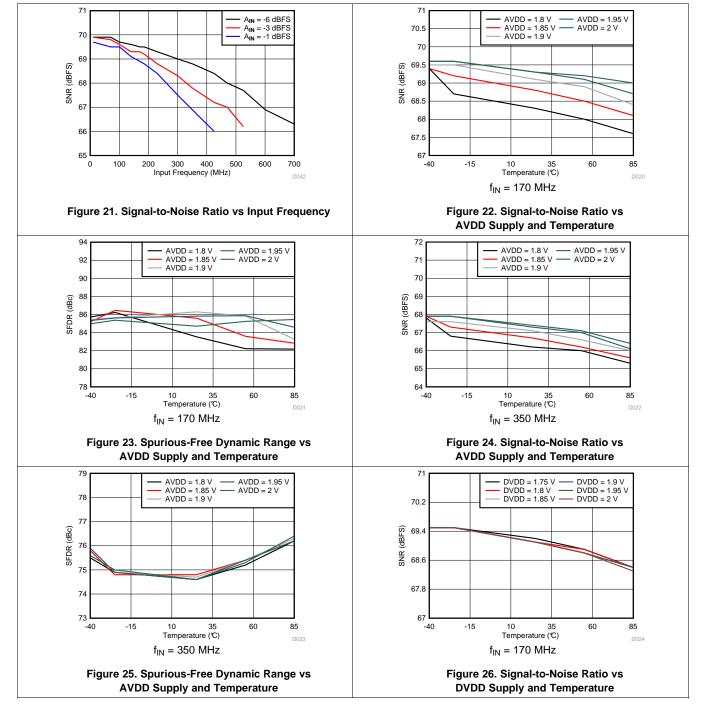

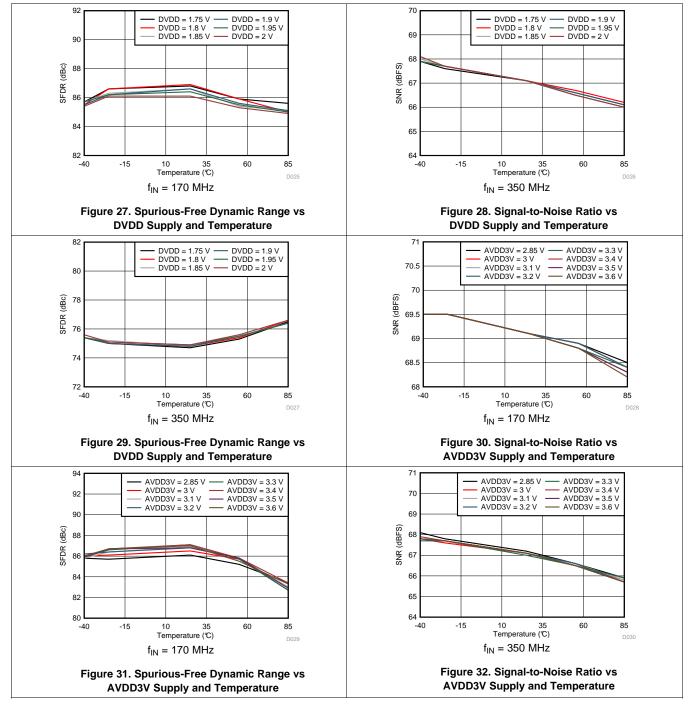

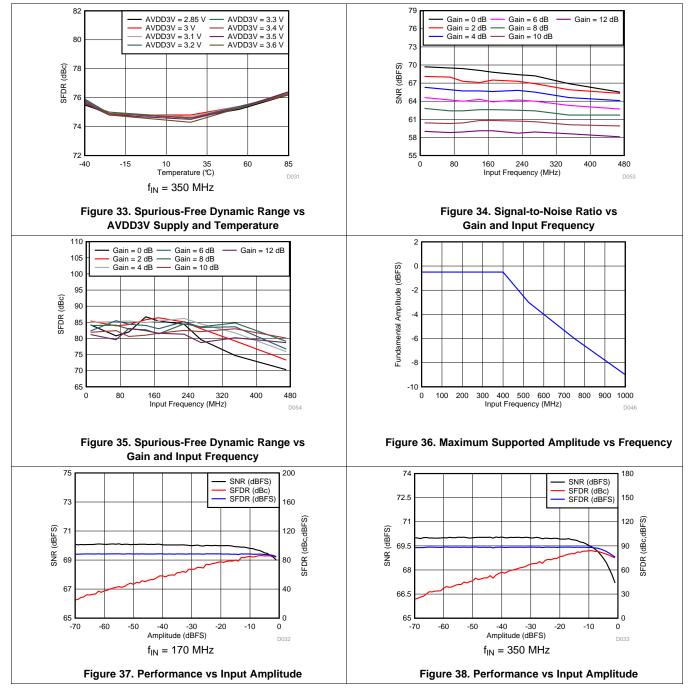

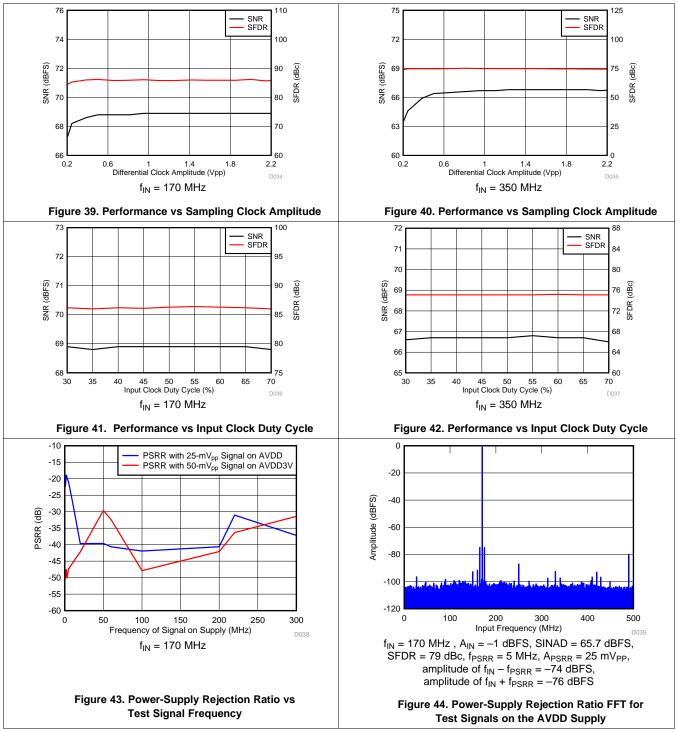

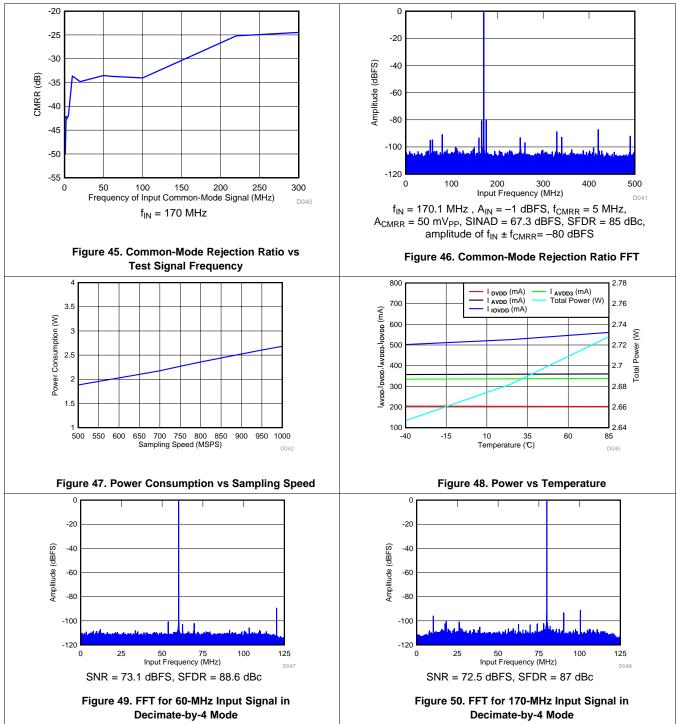

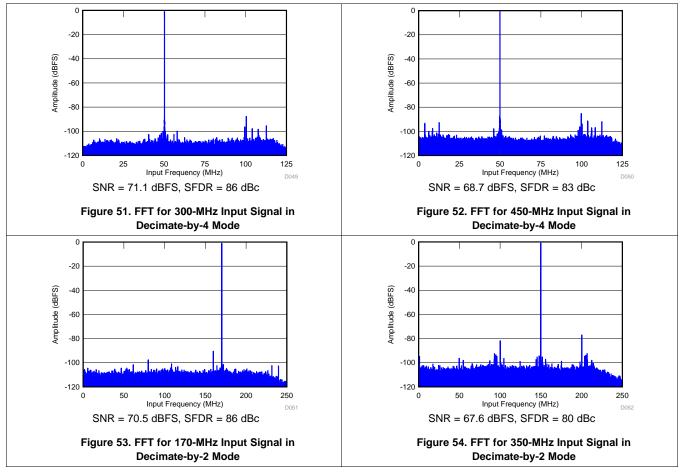

Typical values are at  $T_A = 25$ °C, full temperature range is from  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, ADC sampling rate = 1.0 GSPS, 50% clock duty cycle, AVDD3V = 3.0 V, AVDD = DVDD = 1.9 V, IOVDD = 1.15 V, and -1-dBFS differential input, unless otherwise noted.

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Typical values are at  $T_A = 25$ °C, full temperature range is from  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, ADC sampling rate = 1.0 GSPS, 50% clock duty cycle, AVDD3V = 3.0 V, AVDD = DVDD = 1.9 V, IOVDD = 1.15 V, and -1-dBFS differential input, unless otherwise noted.

Typical values are at  $T_A = 25$ °C, full temperature range is from  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, ADC sampling rate = 1.0 GSPS, 50% clock duty cycle, AVDD3V = 3.0 V, AVDD = DVDD = 1.9 V, IOVDD = 1.15 V, and -1-dBFS differential input, unless otherwise noted.

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Typical values are at  $T_A = 25$ °C, full temperature range is from  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, ADC sampling rate = 1.0 GSPS, 50% clock duty cycle, AVDD3V = 3.0 V, AVDD = DVDD = 1.9 V, IOVDD = 1.15 V, and -1-dBFS differential input, unless otherwise noted.

Product Folder Links: ADS54J40

Submit Documentation Feedback

Typical values are at  $T_A = 25$ °C, full temperature range is from  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, ADC sampling rate = 1.0 GSPS, 50% clock duty cycle, AVDD3V = 3.0 V, AVDD = DVDD = 1.9 V, IOVDD = 1.15 V, and -1-dBFS differential input, unless otherwise noted.

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Typical values are at  $T_A$  = 25°C, full temperature range is from  $T_{MIN}$  = -40°C to  $T_{MAX}$  = 85°C, ADC sampling rate = 1.0 GSPS, 50% clock duty cycle, AVDD3V = 3.0 V, AVDD = DVDD = 1.9 V, IOVDD = 1.15 V, and -1-dBFS differential input, unless otherwise noted.

Typical values are at  $T_A = 25$ °C, full temperature range is from  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, ADC sampling rate = 1.0 GSPS, 50% clock duty cycle, AVDD3V = 3.0 V, AVDD = DVDD = 1.9 V, IOVDD = 1.15 V, and -1-dBFS differential input, unless otherwise noted.

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Typical values are at  $T_A = 25$ °C, full temperature range is from  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, ADC sampling rate = 1.0 GSPS, 50% clock duty cycle, AVDD3V = 3.0 V, AVDD = DVDD = 1.9 V, IOVDD = 1.15 V, and -1-dBFS differential input, unless otherwise noted.

Submit Documentation Feedback

Typical values are at  $T_A$  = 25°C, full temperature range is from  $T_{MIN}$  = -40°C to  $T_{MAX}$  = 85°C, ADC sampling rate = 1.0 GSPS, 50% clock duty cycle, AVDD3V = 3.0 V, AVDD = DVDD = 1.9 V, IOVDD = 1.15 V, and -1-dBFS differential input, unless otherwise noted.

### 8 Detailed Description

#### 8.1 Overview

The ADS54J40 is a low-power, wide-bandwidth, 16-bit, 1.0-GSPS, dual-channel, analog-to-digital converter (ADC). The ADS54J40 employs four interleaving ADCs for each channel to achieve a noise floor of –159 dBFS/Hz. The ADS54J40 uses Tl's proprietary interleaving and dither algorithms to achieve a clean spectrum with a high spurious-free dynamic range (SFDR). The device also offers various programmable decimation filtering options for systems requiring higher signal-to-noise ratio (SNR) and SFDR over a wide range of frequencies.

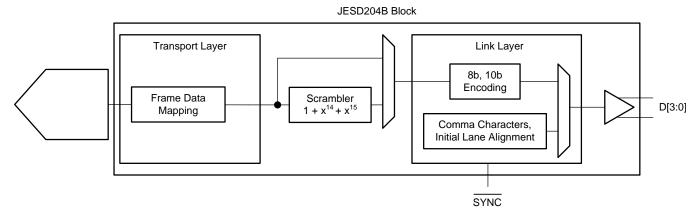

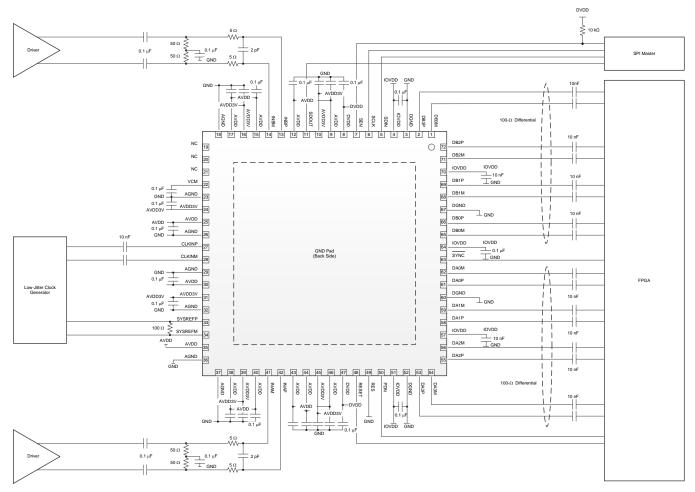

Analog input buffers isolate the ADC driver from glitch energy generated from sampling process, thereby simplify the driving network on-board. The JESD204B interface reduces the number of interface lines with two-lane and four-lane options, allowing a high system integration density. The JESD204B interface operates in subclass 1, enabling multi-chip synchronization with the SYSREF input.

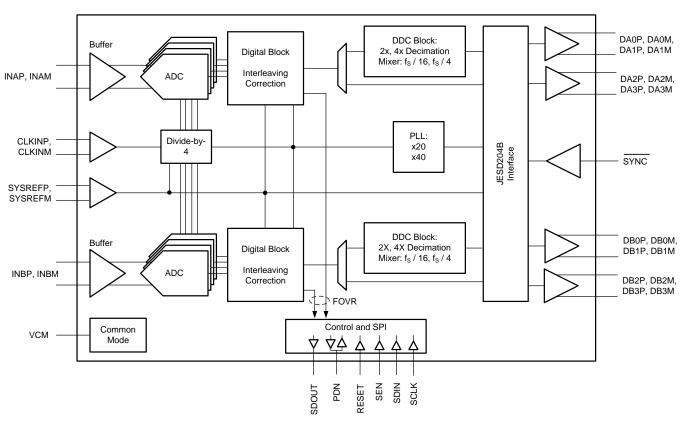

### 8.2 Functional Block Diagram

Copyright © 2017, Texas Instruments Incorporated

#### 8.3 Feature Description

### 8.3.1 Analog Inputs

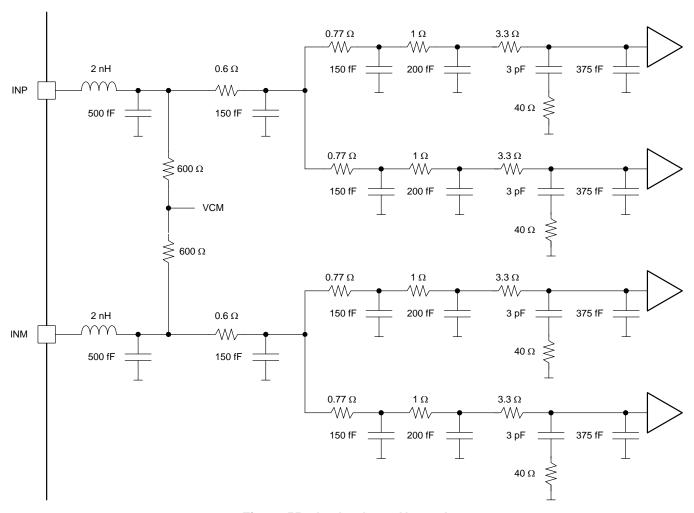

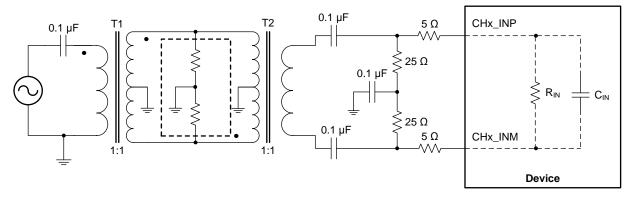

The ADS54J40 analog signal inputs are designed to be driven differentially. The analog input pins have internal analog buffers that drive the sampling circuit. As a result of the analog buffer, the input pins present a high impedance input across a very wide frequency range to the external driving source that enables great flexibility in the external analog filter design as well as excellent  $50-\Omega$  matching for RF applications. The buffer also helps isolate the external driving circuit from the internal switching currents of the sampling circuit, resulting in a more constant SFDR performance across input frequencies.

The common-mode voltage of the signal inputs is internally biased to VCM using  $600-\Omega$  resistors, allowing for accoupling of the input drive network. Each input pin (INP, INM) must swing symmetrically between (VCM + 0.475 V) and (VCM - 0.475 V), resulting in a 1.9-V<sub>PP</sub> (default) differential input swing. The input sampling circuit has a 3-dB bandwidth that extends up to 1.2 GHz. An equivalent analog input network diagram is shown in Figure 55.

Figure 55. Analog Input Network

### **Feature Description (continued)**

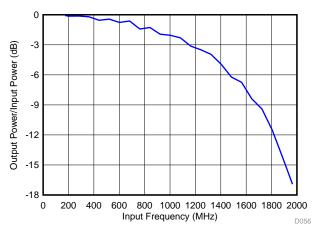

The input bandwidth shown in Figure 56 is measured with respect to a  $50-\Omega$  differential input termination at the ADC input pins.

Figure 56. Transfer Function versus Frequency

Copyright © 2017, Texas Instruments Incorporated

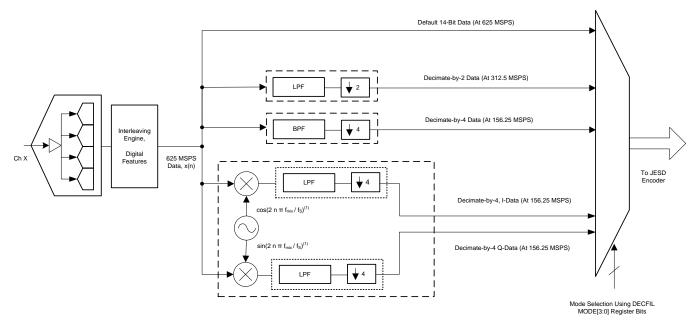

(1) In IQ decimate-by-4 mode, the mixer frequency is fixed at  $f_{mix} = f_S / 4$ . For  $f_S = 1$  GSPS and  $f_{mix} = 250$  MHz.

Figure 57. DDC Block

### **Feature Description (continued)**

#### 8.3.2 DDC Block

The ADS54J40 has an optional DDC block that can be enabled via an SPI register write. Each ADC channel is followed by a DDC block consisting of three different decimate-by-2 and decimate-by-4 finite impulse response (FIR) half-band filter options. The different decimation filter options can be selected via SPI programming.

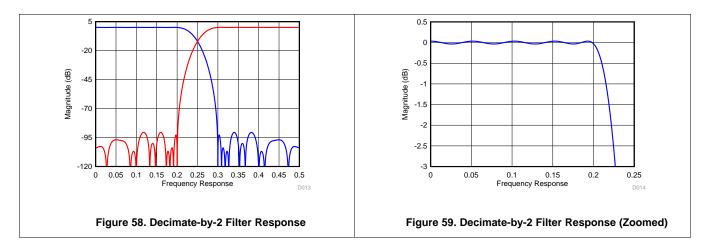

#### 8.3.2.1 Decimate-by-2 Filter

This decimation filter has 41 taps. The stop-band attenuation is approximately 90 dB and the pass-band flatness is ±0.05 dB. Table 1 shows corner frequencies for low-pass and high-pass filter options.

Table 1. Corner Frequencies for the Decimate-by-2 Filter

| CORNERS (dB) | LOW PASS                      | HIGH PASS                     |

|--------------|-------------------------------|-------------------------------|

| -0.1         | 0.202 <b>x</b> f <sub>S</sub> | 0.298 × f <sub>S</sub>        |

| -0.5         | 0.210 × f <sub>S</sub>        | 0.290 × f <sub>S</sub>        |

| -1           | 0.215 × f <sub>S</sub>        | 0.285 <b>x</b> f <sub>S</sub> |

| -3           | 0.227 <b>x</b> f <sub>S</sub> | 0.273 × f <sub>S</sub>        |

Figure 58 and Figure 59 show the frequency response of decimate-by-2 filter from dc to f<sub>S</sub> / 2.

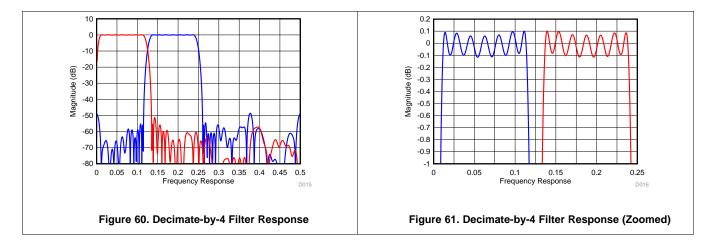

#### 8.3.2.2 Decimate-by-4 Filter Using a Digital Mixer

This band-pass decimation filter consists of a digital mixer and three concatenated FIR filters with a combined latency of approximately 28 output clock cycles. The alias band attenuation is approximately 55 dB and the pass-band flatness is  $\pm 0.1$  dB. By default after reset, the band-pass filter is centered at  $f_S$  / 16. Using the SPI, the center frequency can be programmed at N ×  $f_S$  / 16 (where N = 1, 3, 5, or 7). Table 2 shows corner frequencies for two extreme options.

Table 2. Corner frequencies for the Decimate-by-4 Filter

| CORNERS (dB) | CORNER FREQUENCY AT LOWER SIDE (Center Frequency f <sub>S</sub> / 16) | CORNER FREQUENCY AT HIGHER SIDE (Center Frequency f <sub>S</sub> / 16) |

|--------------|-----------------------------------------------------------------------|------------------------------------------------------------------------|

| -0.1         | 0.011 × f <sub>S</sub>                                                | 0.114 x f <sub>S</sub>                                                 |

| -0.5         | 0.010 × f <sub>S</sub>                                                | 0.116 × f <sub>S</sub>                                                 |

| -1           | 0.008 × f <sub>S</sub>                                                | 0.117 x f <sub>S</sub>                                                 |

| -3           | 0.006 × f <sub>S</sub>                                                | 0.120 × f <sub>S</sub>                                                 |

Figure 60 and Figure 61 show the frequency response of the decimate-by-4 filter for center frequencies  $f_S$  / 16 and 3 ×  $f_S$  / 16 (N = 1 and N = 3, respectively).

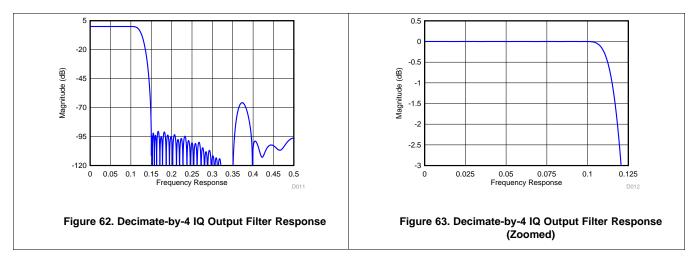

#### 8.3.2.3 Decimate-by-4 Filter with IQ Outputs

In this configuration, the DDC block includes a fixed digital  $f_{\rm S}$  / 4 mixer. Thus, the IQ pass band is approximately  $\pm 110$  MHz, centered at  $f_{\rm S}$  / 4. This decimation filter has 41 taps with a latency of approximately ten output clock cycles. The stop-band attenuation is approximately 90 dB and the pass-band flatness is  $\pm 0.05$  dB. Table 3 shows the corner frequencies for a low-pass, decimate-by-4 IQ filter.

Table 3. Corner Frequencies for a Decimate-by-4 IQ Output Filter

| CORNERS (dB) | LOW PASS               |

|--------------|------------------------|

| -0.1         | 0.107 × f <sub>S</sub> |

| -0.5         | 0.112 × f <sub>S</sub> |

| -1           | 0.115 × f <sub>S</sub> |

| -3           | 0.120 × f <sub>S</sub> |

Figure 62 and Figure 63 show the frequency response of a decimate-by-4 IQ output filter from dc to f<sub>S</sub> / 2.

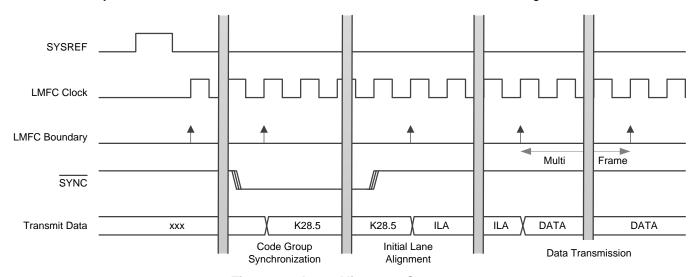

#### 8.3.3 SYSREF Signal

The SYSREF signal is a periodic signal that is sampled by the ADS54J40 device clock and used to align the boundary of the local multi-frame clock inside the data converter. SYSREF is required to be a sub-harmonic of the local multiframe clock (LMFC) internal timing. To meet this requirement, the timing of SYSREF is dependent on the device clock frequency and the LMFC frequency, as determined by the selected DDC decimation and frames per multi-frame settings. The SYSREF signal is recommended to be a low-frequency signal in the range of 1 MHz to 5 MHz to reduce coupling to the signal path both on the printed circuit board (PCB) as well as internal in the device.

The external SYSREF signal must be a sub-harmonic of the internal LMFC clock, as shown in Equation 1 and Table 4.

SYSREF = LMFC / 2N

where

•

$$N = 0, 1, 2$$

, and so forth. (1)

**Table 4. Local Multi-Frame Clock Frequency**

| LMFS CONFIGURATION | DECIMATION | LMFC CLOCK <sup>(1)(2)</sup> |

|--------------------|------------|------------------------------|

| 4211               | _          | f <sub>S</sub> / K           |

| 4244               | _          | (f <sub>S</sub> / 4) / K     |

| 8224               | _          | (f <sub>S</sub> / 4) / K     |

| 4222               | 2X         | (f <sub>S</sub> / 4) / K     |

| 2242               | 2X         | (f <sub>S</sub> / 4) / K     |

| 2221               | 4X         | (f <sub>S</sub> / 4) / K     |

| 2441               | 4X (IQ)    | (f <sub>S</sub> / 4) / K     |

| 4421               | 4X (IQ)    | (f <sub>S</sub> / 4) / K     |

| 1241               | 4X         | (f <sub>S</sub> / 4) / K     |

<sup>(1)</sup> K = Number of frames per multi frame (JESD digital page 6900h, address 06h, bits 4-0).

Submit Documentation Feedback

<sup>(2)</sup>  $f_S = \text{sampling (device) clock frequency.}$

For example, if LMFS = 8224 then the programmed value of K is 9 (the actual value is 9 + 1 = 10 because the actual value for K = the value set in the SPI register +1). If the device clock frequency is  $f_S = 1000$  MSPS, then the local multi-frame clock frequency becomes (1000 / 4) / 10 = 25 MHz. The SYSREF signal frequency can be chosen as the LMFC frequency / 8 = 3.125 MHz.

### 8.3.3.1 SYSREF Not Present (Subclass 0, 2)

A SYSREF pulse is required by the ADS54J40 to reset internal counters. If SYSREF is not present, as can be the case in subclass 0 or 2, this pulse can be done by doing the following register writes shown in Table 5.

Table 5. Internally Pulsing SYSREF Twice Using Register Writes

| ADDRESS (Hex) | DATA (Hex) | COMMENT              |

|---------------|------------|----------------------|

| 0-011h        | 80h        | Set the master page  |

| 0-054h        | 80h        | Enable manual SYSREF |

| 0-053h        | 01h        | Set SYSREF high      |

| 0-053h        | 00h        | Set SYSREF low       |

| 0-053h        | 01h        | Set SYSREF high      |

| 0-053h        | 00h        | Set SYSREF low       |

#### 8.3.4 Overrange Indication

The ADS54J40 provides a fast overrange indication that can be presented in the digital output data stream via SPI configuration. Alternatively, if not used, the SDOUT (pin 11) and PDN (pin 50) pins can be configured via the SPI to output the fast OVR indicator.

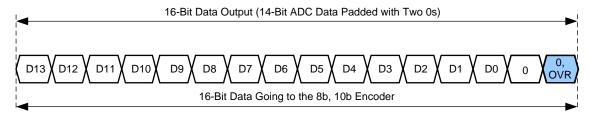

JESD 8b/10b encoder receives 16-bit data that is formed by 14-bit ADC data padded with two 0s as LSBs. When the FOVR indication is embedded in the output data stream, it replaces the LSB of the 16-bit data stream going to the 8b/10b encoder, as shown in Figure 64.

Figure 64. Overrange Indication in a Data Stream

#### 8.3.4.1 Fast OVR

The fast OVR is triggered if the input voltage exceeds the programmable overrange threshold and is presented after only 18 clock cycles +  $t_{PD}$  ( $t_{PD}$  of the gates and buffers is approximately 4 ns), thus enabling a quicker reaction to an overrange event.

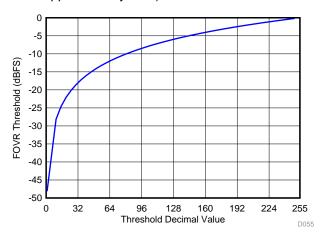

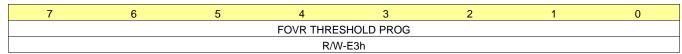

The input voltage level that the overload is detected at is referred to as the *threshold*. The threshold is programmable using the FOVR THRESHOLD bits, as shown in Figure 65. The FOVR is triggered 18 clock cycles  $+ t_{PD}$  ( $t_{PD}$  of the gates and buffers is approximately 4 ns) after the overload condition occurs.

Figure 65. Programming Fast OVR Thresholds

The input voltage level that the fast OVR is triggered at is defined by Equation 2: Full-Scale × [Decimal Value of the FOVR Threshold Bits] / 255)

(2)

The default threshold is E3h (227d), corresponding to a threshold of -1 dBFS.

In terms of full-scale input, the fast OVR threshold can be calculated as Equation 3: 20log (FOVR Threshold / 255)

(3)

Submit Documentation Feedback

#### 8.3.5 Power-Down Mode

The ADS54J40 provides a highly-configurable power-down mode. Power-down can be enabled using the PDN pin or SPI register writes.

A power-down mask can be configured that allows a trade-off between wake-up time and power consumption in power-down mode. Two independent power-down masks can be configured: MASK 1 and MASK 2, as shown in Table 6. See the master page registers in Table 17 for further details.

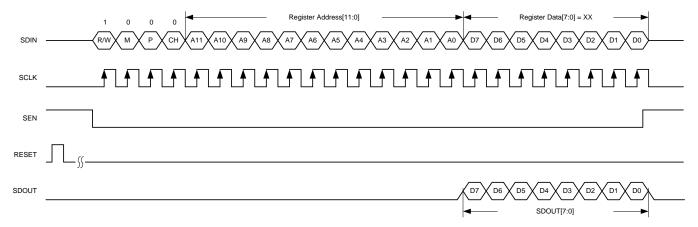

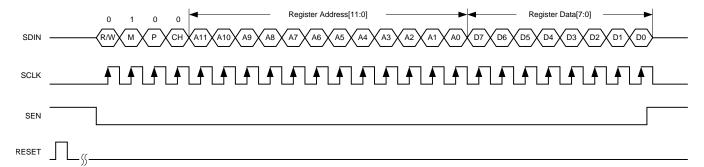

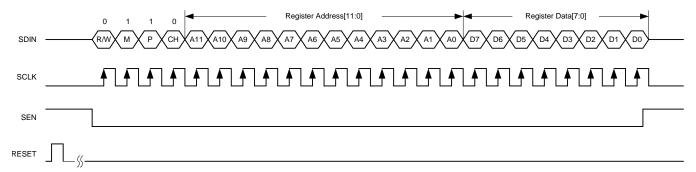

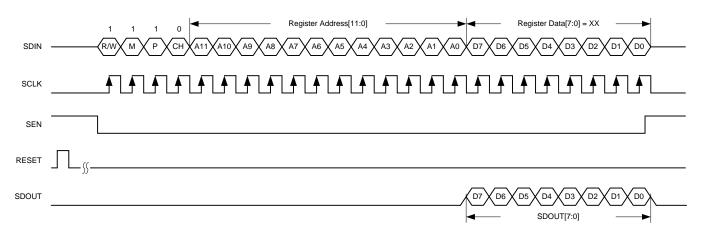

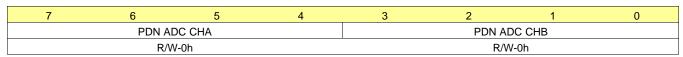

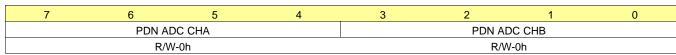

Table 6. Register Address for Power-Down Modes