# ANALOG Evaluation Board for 12-/10-Bit, 8 Channel DEVICES Parallel Ands with a Sequencer Parallel ADCs with a Sequencer

## EVAL-AD7938CB/EVAL-AD7939CB/EVAL-AD7938-6CB

#### **FEATURES**

Full featured evaluation boards for the AD7938, AD7939, and AD7938-6 devices

**Evaluation control board (EVAL-CONTROL-BRD2) compatible** Standalone capability

On-board analog buffering and voltage reference On-board single-ended-to-differential conversion Various linking options

PC software for control and data analysis when used with **EVAL-CONTROL-BRD2**

#### **GENERAL DESCRIPTION**

This data sheet describes the evaluation boards used to test the AD7938, AD7939, and AD7938-6 devices. These devices are 12and 10-bit, high speed, low power successive approximation ADCs. These parts operate from a single 2.7 V to 5.25 V power supply and feature throughput rates of up to 1.5 MSPS.

The AD7938/AD7939 and AD7938-6 device data sheets should be used in conjunction with this data sheet.

On-board components for this evaluation board include:

- One AD780, which is a pin-programmable +2.5 V or +3 V ultra high precision band gap reference

- One AD713 quad op amp

- One AD8022 dual op amp

- Six AD8021 single op amps

- Two AD8138 differential amplifiers

- One P174FCT digital buffer

Various link options are provided in Table 1.

This evaluation board has a 96-way connector, which is compatible with the EVAL-CONTROL-BRD2, which is also available from Analog Devices, Inc. External sockets are provided for various signals, including the VREF input, analog inputs, and digital inputs and outputs. Note that the EVAL-CONTROL-BRD2 operates with all Analog Devices evaluation boards with part numbers ending in the letters CB.

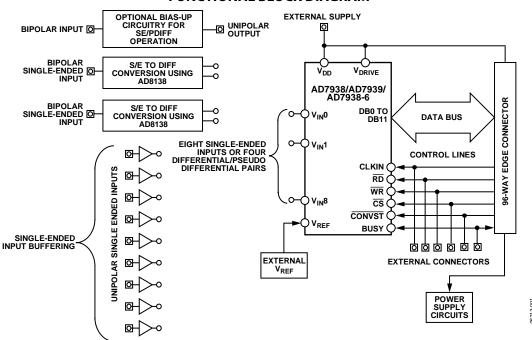

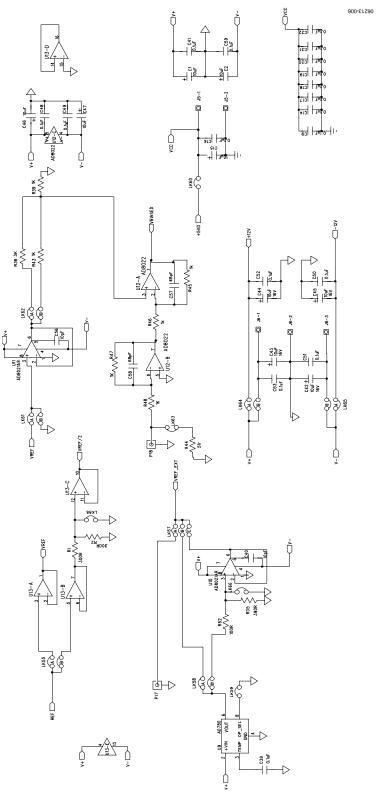

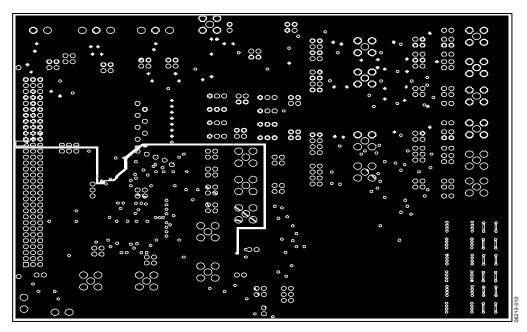

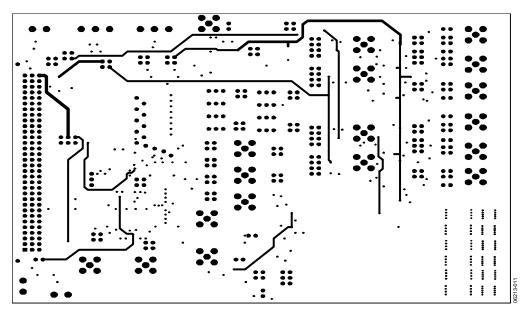

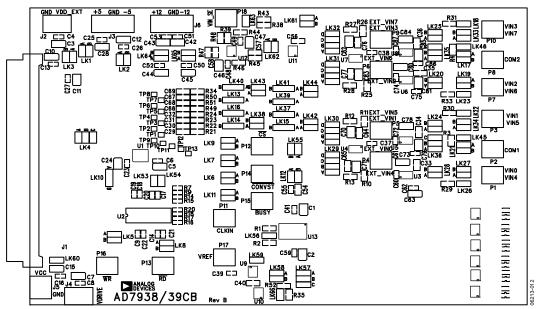

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

## Rev. 0

Evaluation boards are only intended for device evaluation and not for production purposes Evaluation boards as supplied "as is" and without warranties of any kind, express, implied, or statutory including, but not limited to, any implied warranty of merchantability or fitness for a particular purpose. No license is granted by implication or otherwise under any patents or other intellectual property by application or use of evaluation boards. Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Analog Devices reserves the right to change devices or specifications at any time without notice. Trademarks and registered trademarks are the property of their respective owners. Evaluation boards are not authorized to be used in life support devices or systems.

Fax: 781.461.3113 ©2006 Analog Devices, Inc. All rights reserved.

## **TABLE OF CONTENTS**

| Features                          |     |

|-----------------------------------|-----|

| General Description               |     |

| Functional Block Diagram          |     |

| Revision History                  |     |

| Evaluation Board Hardware         | 3   |

| Initial Setup Conditions          |     |

| Differential Mode                 |     |

| Single-Ended Mode                 | 10  |

| Pseudo Differential Mode          | 12  |

| Using the Bias Up Circuit         | 12  |

| Standalone Mode                   | 13  |

| Interfacing the Evaluation Boards | 15  |

| Test Points                       | 10  |

| Connectors                        | 1,4 |

| 50CKCt5                                 | 10 |

|-----------------------------------------|----|

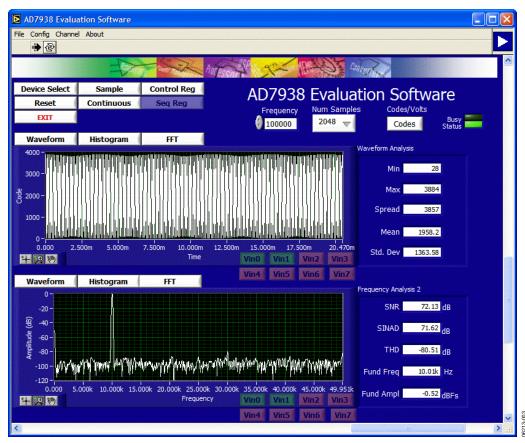

| Evaluation Board Software               | 17 |

| Installing the Software                 | 17 |

| Software Overview                       | 17 |

| Checking the EVAL-CONTROL-BRD2          | 19 |

| Using the Software                      | 19 |

| Taking Samples                          | 20 |

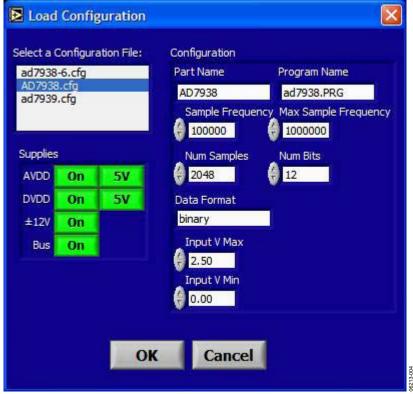

| Software Configuration Files:           | 20 |

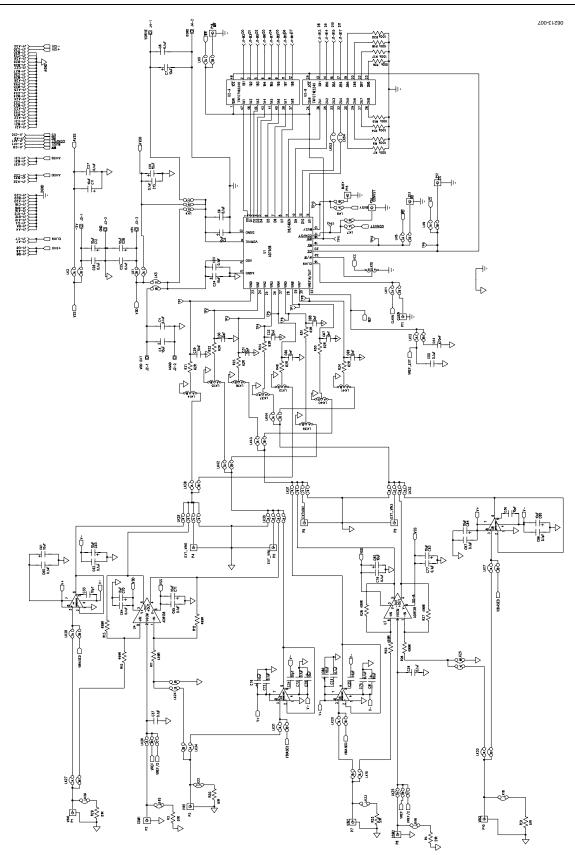

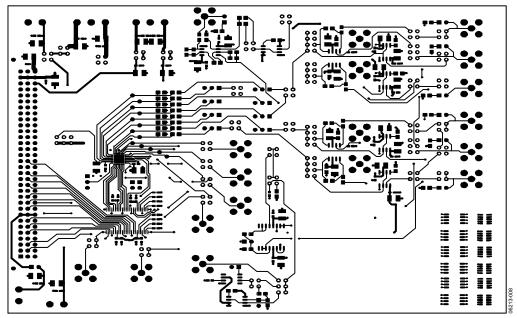

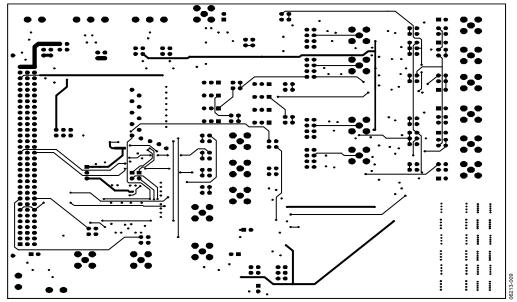

| Evaluation Board Schematics and Artwork | 21 |

| Ordering Information                    | 26 |

| Bill of Materials                       | 26 |

| Ordering Guide                          | 27 |

| FSD Caution                             | 27 |

#### **REVISION HISTORY**

10/06—Revision 0: Initial Version

### **EVALUATION BOARD HARDWARE**

Before applying power and signals to the evaluation board, ensure that all links are properly set per the required operating mode.

The evaluation board has over 60 available link options. These options must be set for the required operating configuration. The functions of the options are outlined in Table 1.

**Table 1. Link Option Functions**

| Tuble 1. L | e 1. Link Option Functions                                                                                                            |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Link No.   | Function                                                                                                                              |  |  |

| LK1        | Selects the source of the $V_{DD}$ +5 V supply used to supply the AD8138 differential amplifiers.                                     |  |  |

|            | In Position A, the $V_{DD}$ is supplied from the EVAL-CONTROL-BRD2.                                                                   |  |  |

|            | In Position B, the $V_{DD}$ must be supplied from an external source via the power connector J3.                                      |  |  |

| LK2        | This link option selects the source of the VSS –5 V supply used to supply the AD8138 differential amplifiers.                         |  |  |

|            | In Position A, the V <sub>SS</sub> is supplied from the EVAL-CONTROL-BRD2.                                                            |  |  |

|            | In Position B, the $V_{SS}$ must be supplied from an external source via the power connector J3.                                      |  |  |

| LK3        | This link option selects the source of the V <sub>DD</sub> supply for the AD7938/AD7939/AD7938-6.                                     |  |  |

|            | In Position A, V <sub>DD</sub> is supplied from the EVAL-CONTROL-BRD2.                                                                |  |  |

|            | In Position B, VDD must be supplied from an external source via J2.                                                                   |  |  |

| LK4        | This link option selects the source of the V <sub>DRIVE</sub> supply for the digital interface.                                       |  |  |

|            | In Position A, V <sub>DRIVE</sub> is tied to V <sub>DD</sub> .                                                                        |  |  |

|            | In Position B, V <sub>DRIVE</sub> is supplied via the EVAL-CONTROL-BRD2.                                                              |  |  |

|            | In Position C, V <sub>DRIVE</sub> must be supplied from an external source via J4.                                                    |  |  |

| LK5        | This link selects the source of the WR input to the ADC.                                                                              |  |  |

|            | In Position A, $\overline{\text{WR}}$ is supplied by the EVAL-CONTROL-BRD2.                                                           |  |  |

|            | In Position B, WR must be supplied from an external source via P16.                                                                   |  |  |

| LK6        | This link selects where the BUSY output from the ADC appears.                                                                         |  |  |

|            | In Position A, the BUSY output may be read by the EVAL-CONTROL-BRD2.                                                                  |  |  |

|            | In Position B, the BUSY may be read via the external socket, P15.                                                                     |  |  |

| LK7        | This link selects the source of the CONVST input to the ADC.                                                                          |  |  |

|            | In Position A, CONVST is supplied by the EVAL-CONTROL-BRD2.                                                                           |  |  |

|            | In Position B, CONVST must be supplied from an external source via P14.                                                               |  |  |

| LK8        | This link selects the source of the RD input to the ADC.                                                                              |  |  |

|            | In Position A, RD is supplied by the EVAL-CONTROL-BRD2.                                                                               |  |  |

|            | In Position B, RD must be supplied from an external source via P13.                                                                   |  |  |

| LK9        | This link selects the source of the CS input to the ADC.                                                                              |  |  |

|            | In Position A, CS is supplied by the EVAL-CONTROL-BRD2.                                                                               |  |  |

|            | In Position B, CS must be supplied from an external source via P12.                                                                   |  |  |

| LK10       | This link selects the state of the $W/B$ input.                                                                                       |  |  |

|            | In Position A, W/B is tied low.                                                                                                       |  |  |

|            | In Position B, W/B is tied high.                                                                                                      |  |  |

| LK11       | This link selects the source of the CLKIN input to the ADC.                                                                           |  |  |

| LIVII      | In Position A, CLKIN is supplied by the EVAL-CONTROL-BRD2.                                                                            |  |  |

|            | In Position B, CLKIN must be supplied from an external source via P11.                                                                |  |  |

| LV12       | If an external reference is being used, place this link in Position A.                                                                |  |  |

| LK12       | If an internal reference is being used, place this link in Position B.                                                                |  |  |

| I V 1 2    |                                                                                                                                       |  |  |

| LK13       | This link selects the input to the V <sub>IN</sub> 4 pin on the ADC.                                                                  |  |  |

|            | In Position A, the input is coming from Pin V <sub>IN</sub> 4, either in singled-ended mode or as one channel of a differential pair. |  |  |

| 1144       | In Position B, the input to the ADC is tied to ground.                                                                                |  |  |

| LK14       | This link selects the input to V <sub>IN</sub> 0 pin on the ADC.                                                                      |  |  |

|            | In Position A, the input is coming from Pin $V_{IN}$ 0, either in singled-ended mode or as one channel of a differential pair.        |  |  |

|            | In Position B, the input to the ADC is tied to ground.                                                                                |  |  |

| Link No. | Function                                                                                                                                                                                                                                                          |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LK15     | This link selects the input to V <sub>IN</sub> 1 on the ADC.                                                                                                                                                                                                      |

|          | In Position A, the input is coming from V <sub>IN</sub> 1, either in singled-ended mode or as one channel of a differential pair.                                                                                                                                 |

|          | In Position B, the input to the ADC is tied to ground.                                                                                                                                                                                                            |

| LK16     | This link selects the input to V <sub>IN</sub> 2 on the ADC                                                                                                                                                                                                       |

|          | In Position A, the input is coming from V <sub>IN</sub> 2, either in singled-ended mode or as one channel of a differential pair.                                                                                                                                 |

|          | In Position B, the input to the ADC is tied to ground.                                                                                                                                                                                                            |

| LK17     | This link selects the analog input to be applied to the buffer, U8, which is used when operating in single-ended mode and when using $V_{IN}3$ to $V_{IN}7$ .                                                                                                     |

|          | If the single-ended input applied to $V_{IN}3$ to $V_{IN}7$ is unipolar, this link should be in Position A, and the analog input should be applied at P10 with LK33 in Position B.                                                                                |

|          | If the single-ended input applied to V <sub>IN</sub> 3 to V <sub>IN</sub> 7 is bipolar, this link should be in Position B and the analog input should be biased up using the bias circuit by applying it to P18.                                                  |

| LK18     | This link option adds a 50 $\Omega$ termination to AGND at the V <sub>IN</sub> 3 to V <sub>IN</sub> 7 socket (P10) for the single-ended input.                                                                                                                    |

|          | This link should be inserted if a 50 $\Omega$ termination is required on the analog input.                                                                                                                                                                        |

| LK19     | This link is used to choose between a single-ended analog input or a fully differential pair.                                                                                                                                                                     |

|          | If the analog input applied to $V_{IN}$ 2 to $V_{IN}$ 6 is a single-ended analog input, then LK19 should be in Position B as this input is applied to the op amp buffer.                                                                                          |

|          | If the analog input applied to V <sub>IN</sub> 2 through V <sub>IN</sub> 6 is part of a differential pair with V <sub>IN</sub> 3 through V <sub>IN</sub> 7, then LK19 should be in Position A as this input is applied to the AD8138 differential amplifier (U7). |

| LK20     | This link selects the analog input to be applied to the buffer, U6, which is used when operating in single-ended mode or pseudo differential mode and when using V <sub>IN</sub> 2 through V <sub>IN</sub> 6.                                                     |

|          | If the single-ended input applied to $V_{IN}2$ through $V_{IN}6$ is unipolar, this link should be in Position A, and the analog input should be applied at P7 with LK19 in Position B.                                                                            |

|          | If the single-ended input applied to $V_{IN}2$ is bipolar, this link should be in Position B and the analog input should be biased up using the bias circuit by applying it to P18.                                                                               |

| LK21     | This link selects the analog input to be applied to the buffer, U5, which is used when operating in single-ended mode and when using $V_{IN}$ 1 through $V_{IN}$ 5.                                                                                               |

|          | If the single-ended input applied to $V_{IN}1$ through $V_{IN}5$ is unipolar, this link should be in Position A, and the analog input should be applied at P3 with LK34 in Position A.                                                                            |

|          | If the single-ended input applied to $V_{IN}1$ is bipolar, this link should be in Position B and the analog input should be biased up using the bias circuit by applying it to P18.                                                                               |

| LK22     | This link option adds a 50 $\Omega$ termination to AGND at the V <sub>IN</sub> 1 through V <sub>IN</sub> 5 socket (P3) for the single-ended input. This link should be inserted if a 50 $\Omega$ termination is required on the analog input.                     |

| LK23     | This link option adds a 50 $\Omega$ termination to AGND at the V <sub>IN</sub> 2 through V <sub>IN</sub> 6 socket (P7) for the single-ended input.                                                                                                                |

|          | This link should be inserted if a 50 $\Omega$ termination is required on the analog input.                                                                                                                                                                        |

| LK24     | This link selects the input to the input of the AD8138 differential amplifier (U4).                                                                                                                                                                               |

|          | If the user applies a fully differential signal to $V_{IN}0$ and $V_{IN}1$ or $V_{IN}4$ and $V_{IN}5$ , and only requires buffering of this signal before its applied to the ADC, then LK24 should be in Position A.                                              |

|          | When applying a single-ended input to $V_{IN}0$ through $V_{IN}4$ requiring the use of the AD8138 to perform single-ended-to-differential conversion, this link should be in Position B. In this case, no input is applied to $V_{IN}1$ through $V_{IN}5$ .       |

| LK25     | This link selects the input to the input of the AD8138 differential amplifier (U7).                                                                                                                                                                               |

|          | If the user applies a fully differential signal to $V_{IN}2$ and $V_{IN}3$ or $V_{IN}6$ and $V_{IN}7$ , and only requires buffering of this signal before its applied to the ADC, then Link 16 should be in Position A.                                           |

|          | When applying a single-ended input to $V_{IN}2$ through $V_{IN}6$ requiring the use of the AD8138 to perform single-ended-to-differential conversion, this link should be in Position B. In this case, no input is applied to $V_{IN}3$ .                         |

| LK26     | This link option adds a 50 $\Omega$ termination to AGND at the V <sub>IN</sub> 1 through V <sub>IN</sub> 5 socket (P1) for the single-ended input.                                                                                                                |

|          | This link should be inserted if a 50 $\Omega$ termination is required on the analog input.                                                                                                                                                                        |

| LK27     | This link is used to choose between a single-ended analog input or a fully differential pair.                                                                                                                                                                     |

|          | If the analog input applied to $V_{\mathbb{N}}0$ through $V_{\mathbb{N}}4$ is a single-ended analog input then LK27 should be in Position A as this input is applied to the op amp buffer.                                                                        |

|          | If the analog input applied to $V_{IN}0$ through $V_{IN}4$ is part of a differential pair with $V_{IN}1$ through $V_{IN}5$ , then LK27 should be in Position B as this input is applied to the AD8138 differential amplifier (U4).                                |

| Link No. | Function                                                                                                                                                                                                                        |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LK28     | This link selects the analog input to be applied to the buffer, U2, which is used when operating in single-ended mode or                                                                                                        |

|          | pseudo differential mode and when using V <sub>IN</sub> 0 through V <sub>IN</sub> 4.                                                                                                                                            |

|          | If the single-ended input applied to $V_{IN}0$ through $V_{IN}4$ is unipolar, this link should be in Position A, and the analog input should be applied at P1 with LK27 in Position A.                                          |

|          | If the single-ended input applied to V <sub>IN</sub> O is bipolar, this link should be in Position B and the analog input should be biased up using the bias circuit by applying it to P18.                                     |

| LK29     | This link option selects the source of the $V_{IN}0$ through $V_{IN}4$ analog input to be applied to the ADC.                                                                                                                   |

|          | In Position A, a single-ended, buffered signal is applied to V <sub>IN</sub> 0 through V <sub>IN</sub> 4.                                                                                                                       |

|          | In Position B, V <sub>IN</sub> 0 through V <sub>IN</sub> 4 is supplied from the positive output of the AD8138 (U4) differential amplifier to provide half a differential pair with V <sub>IN</sub> 1 through V <sub>IN</sub> 5. |

|          | In Position C, an external $V_{IN}0$ through $V_{IN}4$ is applied to the ADC via P4.                                                                                                                                            |

|          | In Position D, $V_{IN}0$ through $V_{IN}4$ is tied to AGND. Do this when $V_{IN}0$ through $V_{IN}4$ is not being used and when power supplies are first applied to the board.                                                  |

| LK30     | This link option selects the source of the $V_{IN}1$ through $V_{IN}5$ analog input to be applied to the ADC.                                                                                                                   |

|          | In Position A, a single-ended, buffered signal is applied to $V_{IN}1$ through $V_{IN}5$ .                                                                                                                                      |

|          | In Position B, $V_{IN}1$ through $V_{IN}5$ is supplied from the negative output of the AD8138 (U4) differential amplifier to provide half a differential pair with $V_{IN}0$ through $V_{IN}4$ .                                |

|          | In Position C, an external $V_{IN}$ 1 through $V_{IN}$ 5 is applied to the ADC via P5.                                                                                                                                          |

|          | In Position D, $V_{IN}1$ through $V_{IN}5$ is tied to AGND. Do this when $V_{IN}1$ through $V_{IN}5$ is not being used and when power supplies are first applied to the board.                                                  |

| LK31     | This link option selects the source of the $V_{IN}2$ through $V_{IN}6$ analog input to be applied to the ADC.                                                                                                                   |

|          | In Position A, a single-ended, buffered signal is applied to V <sub>IN</sub> 2 through V <sub>IN</sub> 6.                                                                                                                       |

|          | In Position B, V <sub>IN</sub> 2 through V <sub>IN</sub> 6 is supplied from the positive output of the AD8138 (U7) differential amplifier to provide half a differential pair with V <sub>IN</sub> 3 through V <sub>IN</sub> 7. |

|          | In Position C, an external V <sub>IN</sub> 2 through V <sub>IN</sub> 6 is applied to the ADC via P6.                                                                                                                            |

|          | In Position D, $V_{IN}2$ through $V_{IN}6$ is tied to AGND. Do this when $V_{IN}2$ through $V_{IN}6$ is not being used and when power supplies are first applied to the board.                                                  |

| LK32     | This link option selects the source of the $V_{IN}3$ through $V_{IN}7$ analog input to be applied to the ADC. In Position A, a single-ended, buffered signal is applied to $V_{IN}3$ through $V_{IN}7$ .                        |

|          | In Position B, V <sub>IN</sub> 3 through V <sub>IN</sub> 7 is supplied from the negative output of the AD8138 (U7) differential amplifier to provide half a                                                                     |

|          | differential pair with $V_{IN}$ 2 through $V_{IN}$ 6.                                                                                                                                                                           |

|          | In Position C, an external $V_{IN}3$ through $V_{IN}7$ is applied to the ADC via P9.                                                                                                                                            |

|          | In Position D, $V_{IN}3$ through $V_{IN}7$ is tied to AGND. Do this when $V_{IN}3$ through $V_{IN}7$ is not being used and when power supplies are first applied to the board.                                                  |

| LK33     | This link is used to choose between a single-ended analog input or a fully differential pair.                                                                                                                                   |

|          | If the analog input applied to $V_{IN}3$ through $V_{IN}7$ is part of a differential pair with $V_{IN}2$ through $V_{IN}6$ , then LK33 should be in Position A as this input is applied to the AD8138 differential amplifier.   |

|          | If the analog input applied to $V_{IN}3$ through $V_{IN}7$ is a single-ended analog input then LK33 should be in Position B as this input is applied to the op amp buffer.                                                      |

| LK34     | This link is used to choose between a single-ended analog input or a fully differential pair.                                                                                                                                   |

|          | If the analog input applied to $V_{IN}1$ through $V_{IN}5$ is a single-ended analog input then LK34 should be in Position A as this input is applied to the op amp buffer.                                                      |

|          | If the analog input applied to $V_{IN}1$ through $V_{IN}5$ is part of a differential pair with $V_{IN}0$ , then LK34 should be in Position B as this input is applied to the AD8138 differential amplifier.                     |

| LK35     | This link selects the input to the V <sub>OCM</sub> pin (common-mode input) of the AD8138 differential amplifier (U7).                                                                                                          |

|          | When in Position A, an external common-mode input must be applied via P8.                                                                                                                                                       |

|          | When in Position B, VREF is applied to the V <sub>OCM</sub> pin of the AD8138 (U7).                                                                                                                                             |

| 11/2 (   | When in Position C, VREF/2 is applied to the V <sub>OCM</sub> pin of the AD8138 (U7).                                                                                                                                           |

| LK36     | This link selects the input to the V <sub>OCM</sub> pin (common-mode input) of the AD8138 differential amplifier (U4).                                                                                                          |

|          | When in Position A, an external common-mode input must be applied via P2.  When in Position B. VPEE is applied to the Vest pin of the AD\$138 (U4)                                                                              |

|          | When in Position B, VREF is applied to the Voca pin of the AD8138 (U4).  When in Position C, VREF/2 is applied to the Voca pin of the AD8138 (U4).                                                                              |

|          | When in Position C, VREF/2 is applied to the V <sub>OCM</sub> pin of the AD8138 (U4).                                                                                                                                           |

| Link No. | Function                                                                                                                                                                                   |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LK37     | This link selects the input to V <sub>IN</sub> 3 pin on the ADC.                                                                                                                           |

| LN37     | In Position A, the input is coming from V <sub>IN</sub> 3, either in singled-ended mode or as one channel of a differential pair.                                                          |

|          | In Position B, the input to the ADC is tied to ground.                                                                                                                                     |

| LK38     | This link selects whether the signal is applied to $V_{IN}0$ or $V_{IN}4$ .                                                                                                                |

| LINGO    | In Position A, the signal is applied to V <sub>IN</sub> O.                                                                                                                                 |

|          | In Position B, the signal is applied to V <sub>N</sub> 4.                                                                                                                                  |

| LK39     | This link selects the input to $V_{IN}$ 5 on the ADC.                                                                                                                                      |

| LIND     | In Position A, the input is coming from $V_{IN}S$ , either in singled-ended mode or as one channel of a differential pair.                                                                 |

|          | In Position B, the input to the ADC is tied to ground.                                                                                                                                     |

| LK40     | This link selects the input to $V_{IN}6$ pin on the ADC.                                                                                                                                   |

| Livio    | In Position A, the input is coming from V <sub>IN</sub> 6, either in single-ended mode or as one channel of a differential pair.                                                           |

|          | In Position B, the input to the ADC is tied to ground.                                                                                                                                     |

| LK41     | This link selects the input to V <sub>IN</sub> 7 pin on the ADC.                                                                                                                           |

|          | In Position A, the input is coming from V <sub>IN</sub> 7, either in single-ended mode or as one channel of a differential pair.                                                           |

|          | In Position B, the input to the ADC is tied to ground.                                                                                                                                     |

| LK42     | This link selects whether the signal is applied to V <sub>IN</sub> 1 or V <sub>IN</sub> 5.                                                                                                 |

|          | In Position A, the signal is applied to V <sub>IN</sub> 1.                                                                                                                                 |

|          | In Position B, the signal is applied to V <sub>IN</sub> 5.                                                                                                                                 |

| LK43     | This link selects whether the signal is applied to $V_{IN}2$ or $V_{IN}6$ .                                                                                                                |

|          | In Position A, the signal is applied to V <sub>IN</sub> 2.                                                                                                                                 |

|          | In Position B, the signal is applied to V <sub>IN</sub> 6.                                                                                                                                 |

| LK44     | This link selects whether the signal is applied to V <sub>IN</sub> 3 or V <sub>IN</sub> 7.                                                                                                 |

|          | In Position A, the signal is applied to V <sub>IN</sub> 3.                                                                                                                                 |

|          | In Position B, the signal is applied to V <sub>IN</sub> 7.                                                                                                                                 |

| LK45     | This link option adds a 50 $\Omega$ termination to AGND at the COM1 socket (P2) for the input to $V_{OCM}$ pin (common-mode input) of the AD8138 differential amplifier (U4).              |

|          | This link should be inserted if a 50 $\Omega$ termination is required on the input to $V_{OCM}$ pin (common-mode input) of the AD8138 differential amplifier (U4) with LK36 in Position A. |

| LK46     | This link option adds a 50 $\Omega$ termination to AGND at the COM2 socket (P2) for the input to $V_{OCM}$ pin (common-mode input) of the AD8138 differential amplifier (U4).              |

|          | This link should be inserted if a 50 $\Omega$ termination is required on the input to $V_{OCM}$ pin (common-mode input) of the AD8138 differential amplifier (U4) with LK35 in Position A. |

| LK53     | Always insert.                                                                                                                                                                             |

| LK54     | Always insert.                                                                                                                                                                             |

| LK55     | In Position A, REF is buffered to supply VREF to the common-mode voltage of the differential amplifier and to the bias up circuit.                                                         |

|          | In Position B, REF is divided down by two, and then buffered to supply VREF/2 to the common-mode voltage of the AD8138 differential amplifier.                                             |

| LK56     | When VREF/2 is not used, insert LK56 to ensure that the inputs to U13-C are not floating.                                                                                                  |

| LK57     | This link chooses the source of an external reference input.                                                                                                                               |

|          | In Position A, an external reference should be applied via P17.                                                                                                                            |

|          | In Position B, the V <sub>OUT</sub> of the AD780 reference chip is applied to the VREF circuit.                                                                                            |

|          | In Position C, three-quarters of the AD780 V <sub>OUT</sub> is applied to the VREF circuit. The resistors R35 and R52 can be changed if the user requires an alternative reference input.  |

| LK58     | This link determines whether the output of the AD780 reference chip is applied directly to LK57 or if it is divided down before being applied to LK57.                                     |

|          | In Position A, the output of the AD780 is applied to LK57.                                                                                                                                 |

|          | In Position B, the output of the AD780 is divided down before being applied to LK57.                                                                                                       |

| LK59     | This link option controls the program pin of the AD780 reference.                                                                                                                          |

|          | When this pin is inserted, the AD780 output voltage is set to 3 V.                                                                                                                         |

|          | When this pin is removed, the AD780 output voltage is set to 2.5 V.                                                                                                                        |

| Link No. | Function                                                                                                                                                             |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LK60     | This link option determines the source of the VCC (+5 V) digital supply.                                                                                             |

|          | When inserted, VCC is supplied via the EVAL-CONTROL-BRD2.                                                                                                            |

|          | When removed, VCC must be supplied to the external connector, J5.                                                                                                    |

| LK61     | This link selects the dc voltage to be applied to the bias up circuit, which is used when a single-ended, bipolar signal needs to be converted to a unipolar signal. |

|          | In Position A, VREF is applied to the bias up circuit.                                                                                                               |

|          | In Position B, the dc input to the bias up circuit is tied to AGND. Do this if the bias up circuit is not being used.                                                |

| LK62     | This link selects which portion of the VREF input is applied to the bias up circuit. The choice depends on the nature of the user's analog input signal.             |

|          | In Position A, one-fourth of the reference is applied to the bias up circuit                                                                                         |

|          | In Position B, one-half of the reference is applied to the bias up circuit. If the bias up circuit is not used, then this link can be removed.                       |

| LK63     | This link option adds a 50 $\Omega$ termination to AGND if a 50 $\Omega$ termination is required on the analog input.                                                |

| LK64     | This link option selects the source of the +12 V power supply.                                                                                                       |

|          | In Position A, the +12 V is supplied by the EVAL-CONTROL-BRD2.                                                                                                       |

|          | In Position B, the +12 V must be supplied from an external source via J6.                                                                                            |

| LK65     | This link option selects the source of the –12 V power supply.                                                                                                       |

|          | In Position A, the –12 V is supplied via the EVAL-CONTROL-BRD2.                                                                                                      |

|          | In Position B, the –12 V must be supplied from an external source via J6.                                                                                            |

| LK66     | When the reference output of the AD780 is not being divided down, this link should be inserted so that the input of U10 is not floating.                             |

#### **INITIAL SETUP CONDITIONS**

This evaluation board can be operated in different modes. For example, the evaluation board can be operated with the EVAL-CONTROL-BRD2 or it can be used it as a standalone board. The board can either be setup to accept eight single-ended inputs, four differential inputs, four pseudo differential inputs, or seven pseudo differential inputs. The link settings for the different modes of operation are detailed in Table 2 through Table 6.

The AD7938/AD7939/AD7938-6 can accept four fully differential analog input pairs. These can either be applied as two pairs to P1, P3 and P7, P10 or single-ended-to-differential

conversion can be performed on a single-ended input applied to P1 and P7.

#### **DIFFERENTIAL MODE**

The link positions described in Table 2 are required for operating the evaluation board in differential mode.

Table 2 outlines the default positions of all links when the board is shipped. All the links are set so that all power supplies and control signals are supplied by the EVAL-CONTROL-BRD2. Initially, all analog inputs are tied to ground to ensure that they are not floating on power up. Change these link positions depending upon which analog inputs are used.

Table 2. Differential Mode — Powered and Controlled by the EVAL-CONTROL-BRD2

| Link No. | Position | Function                                                                                                                                                                                                                    |

|----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LK1      | A        | VDD for the AD8138 amplifiers is supplied by the EVAL-CONTROL-BRD2.                                                                                                                                                         |

| LK2      | Α        | VSS for the AD8138 amplifiers is supplied by the EVAL-CONTROL-BRD2.                                                                                                                                                         |

| LK3      | Α        | VDD for the AD7938/AD7939/AD7938-6 ADCs is supplied by the EVAL-CONTROL-BRD2.                                                                                                                                               |

| LK4      | В        | VDRIVE is supplied by the EVAL-CONTROL-BRD2.                                                                                                                                                                                |

| LK5      | Α        | WB is supplied by the EVAL-CONTROL-BRD2.                                                                                                                                                                                    |

| LK6      | Α        | BUSY is read by the EVAL-CONTROL-BRD2.                                                                                                                                                                                      |

| LK7      | Α        | CONVST is supplied by the EVAL-CONTROL-BRD2.                                                                                                                                                                                |

| LK8      | Α        | RD is supplied by the EVAL-CONTROL-BRD2.                                                                                                                                                                                    |

| LK9      | Α        | CS is supplied by the EVAL-CONTROL-BRD2.                                                                                                                                                                                    |

| LK10     | В        | ADC is set up to operate in word mode.                                                                                                                                                                                      |

| LK11     | Α        | CLKIN is supplied by the EVAL-CONTROL-BRD2.                                                                                                                                                                                 |

| LK12     | Α        | An external reference is supplied to the V <sub>OUT</sub> pin from the AD780.                                                                                                                                               |

| LK13     | Α        | With LK13 in position A, a single-ended input or half a differential input is applied to V <sub>IN</sub> 4. If V <sub>IN</sub> 4 is not used, ground V <sub>IN</sub> 4 by installing LK13 in Position B.                    |

| LK14     | Α        | With LK14 in position A, a single-ended input or half a differential input is applied to $V_{IN}0$ . If $V_{IN}0$ is not used, ground $V_{IN}0$ by installing LK14 in Position B.                                           |

| LK15     | Α        | With LK15 in position A, a single-ended input or half a differential input is applied to $V_{IN}1$ . If $V_{IN}1$ is not used, ground $V_{IN}1$ by installing LK15 in Position B.                                           |

| LK16     | Α        | With LK16 in position A, a single-ended input or half a differential input is applied to $V_{IN}2$ . If $V_{IN}2$ is not used, ground $V_{IN}2$ by installing LK13 in Position B.                                           |

|          |          | LK16 should be in Position B if V <sub>IN</sub> 2 is not in use.                                                                                                                                                            |

| LK17     | В        | The input to U8 is tied to Vbiased, so it is not floating.                                                                                                                                                                  |

| LK18     | Inserted | On power-up, the inputs to the op amps are tied to ground so they are not floating. Once a signal is applied to P10, LK18 can be removed if a 50 $\Omega$ termination is not required.                                      |

| LK19     | Α        | If either a single-ended input or half a differential input is applied to $V_{IN}2$ through $V_{IN}6$ (P7).                                                                                                                 |

| LK20     | В        | The input to U6 is tied to Vbiased, so it is not floating.                                                                                                                                                                  |

| LK21     | В        | The input to U5 is tied to Vbiased, so it is not floating.                                                                                                                                                                  |

| LK22     | Inserted | On power-up, the inputs to the op amps are tied to ground so they are not floating. Once a signal is applied to P3, LK22 can be removed if a 50 $\Omega$ termination is not required.                                       |

| LK23     | Inserted | On power-up, the inputs to the op amps are tied to ground so they are not floating. Once a signal is applied to P7, LK23 can be removed if a 50 $\Omega$ termination is not required.                                       |

| LK24     | В        | If single-ended-to-differential conversion is being performed on a single-ended input applied to $V_{IN}0$ through $V_{IN}4$ (P1). This link should be placed in Position A if half a differential input is applied to P3.  |

| LK25     | В        | If single-ended-to-differential conversion is being performed on a single-ended input applied to $V_{IN}2$ through $V_{IN}6$ (P7). This link should be placed in Position A if half a differential input is applied to P10. |

| LK26     | Inserted | On power-up, the inputs to the op amps are tied to ground so they are not floating. Once a signal is applied to P1, LK26 can be removed if a 50 $\Omega$ termination is not required.                                       |

| LK27     | В        | If either a single-ended input or half a differential input is applied to $V_{IN}0$ through $V_{IN}4$ (P1).                                                                                                                 |

| LK28     | В        | The input to U3 is tied to Vbiased, so it is not floating.                                                                                                                                                                  |

| Link No. | Position | Function                                                                                                                                                                                                                                                                                                                                          |

|----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LK29     | D        | On power-up, the analog input applied to $V_{IN}0$ and/or $V_{IN}4$ of the ADC is tied to AGND so that it is not floating. Once an analog input signal is applied to P1, $V_{IN}0$ through $V_{IN}4$ of the ADC should be connected to the positive output of the AD8138 amplifier by placing LK29 in Position B.                                 |

| LK30     | D        | On power-up, the analog input applied to $V_{IN}1$ and/or $V_{IN}5$ of the ADC is tied to AGND so that it is not floating. Once an analog input signal is applied to P3, $V_{IN}1$ through $V_{IN}5$ of the ADC should be connected to the positive output of the AD8138 amplifier by placing LK30 in Position B.                                 |

| LK31     | D        | On power-up, the analog input applied to $V_{\mathbb{N}}2$ and/or $V_{\mathbb{N}}6$ of the ADC is tied to AGND so that it is not floating. Once an analog input signal is applied to P7, $V_{\mathbb{N}}2$ through $V_{\mathbb{N}}6$ of the ADC should be connected to the positive output of the AD8138 amplifier by placing LK31 in Position B. |

| LK32     | D        | On power-up, the analog input applied to $V_{IN}3$ and/or $V_{IN}7$ of the ADC is tied to AGND so that it is not floating. Once an analog input signal is applied to P10, $V_{IN}3$ through $V_{IN}7$ of the ADC should be connected to the positive output of the AD8138 amplifier by placing LK32 in Position B.                                |

| LK33     | Removed  | If single-ended-to-differential conversion is being performed on a single-ended input applied to $V_{IN}2$ through $V_{IN}6$ (P7). This link should be placed in Position A if half a differential input is applied to P10.                                                                                                                       |

| LK34     | Removed  | If single-ended-to-differential conversion is being performed on a single-ended input applied to $V_{IN}0$ through $V_{IN}4$ (P1). This link should be placed in Position B if half a differential input is applied to P3.                                                                                                                        |

| LK35     | В        | VREF is applied to the V <sub>OCM</sub> pin of the AD8138 differential amplifier to set up the common-mode voltage.                                                                                                                                                                                                                               |

| LK36     | В        | VREF is applied to the $V_{\text{OCM}}$ pin of the AD8138 differential amplifier to set up the common-mode voltage.                                                                                                                                                                                                                               |

| LK37     | Α        | With LK37 in position A, a single-ended input or half a differential input is applied to $V_{IN}3$ . If $V_{IN}3$ is not used, ground $V_{IN}3$ by installing LK37 in Position B.                                                                                                                                                                 |

| LK38     | A and B  | Both A and B are inserted in LK38 when applying half a differential input signal to $V_{IN}0$ and $V_{IN}4$ .                                                                                                                                                                                                                                     |

| LK39     | Α        | With LK39 in position A, a single-ended input or half a differential input is applied to $V_{IN}5$ . If $V_{IN}5$ is not used, ground $V_{IN}5$ by installing LK39 in Position B.                                                                                                                                                                 |

| LK40     | Α        | With LK40 in position A, a single-ended input or half a differential input is applied to V <sub>IN</sub> 6. If V <sub>IN</sub> 6 is not used, ground V <sub>IN</sub> 6 by installing LK40 in Position B.                                                                                                                                          |

| LK41     | Α        | With LK41 in position A, a single-ended input or half a differential input is applied to $V_{IN}7$ . If $V_{IN}7$ is not used, ground $V_{IN}4$ by installing LK41 in Position B.                                                                                                                                                                 |

| LK42     | A and B  | Both A and B are inserted in LK42 when applying half a differential input signal to V <sub>IN</sub> 1 and V <sub>IN</sub> 5.                                                                                                                                                                                                                      |

| LK43     | A and B  | Both A and B are inserted in LK43 when applying half a differential input signal to V <sub>IN</sub> 2 and V <sub>IN</sub> 6.                                                                                                                                                                                                                      |

| LK44     | A and B  | Both A and B are inserted in LK44 when applying half a differential input signal to V <sub>IN</sub> 3 and V <sub>IN</sub> 7.                                                                                                                                                                                                                      |

| LK45     | Removed  | This link should be inserted if a 50 $\Omega$ termination is required on the input to $V_{OCM}$ pin (common-mode input) of the AD8138 differential amplifier (U4) with LK36 in Position A.                                                                                                                                                        |

| LK46     | Removed  | This link should be inserted if a 50 $\Omega$ termination is required on the input to $V_{OCM}$ pin (common-mode input) of the AD8138 differential amplifier (U7) with LK35 in Position A.                                                                                                                                                        |

| LK53     | Inserted | Always insert.                                                                                                                                                                                                                                                                                                                                    |

| LK54     | Inserted | Always insert.                                                                                                                                                                                                                                                                                                                                    |

| LK55     | A and B  | The inputs to U13-A-and-U13-B are not floating.                                                                                                                                                                                                                                                                                                   |

| LK56     | Inserted | The input to U13-C is not floating.                                                                                                                                                                                                                                                                                                               |

| LK57     | В        | VREF is supplied by the $V_{OUT}$ pin from the AD780.                                                                                                                                                                                                                                                                                             |

| LK58     | Α        | The output of the AD780 supplies the reference to the ADC.                                                                                                                                                                                                                                                                                        |

| LK59     | Removed  | The output of the AD780 is 2.5 V.                                                                                                                                                                                                                                                                                                                 |

| LK60     | Inserted | VCC is supplied by the EVAL-CONTROL-BRD2.                                                                                                                                                                                                                                                                                                         |

| LK61     | В        | DC input to the bias up circuit is tied to AGND .as it is not used in this mode.                                                                                                                                                                                                                                                                  |

| LK62     | Removed  | Bias up circuit not used in this mode.                                                                                                                                                                                                                                                                                                            |

| LK63     | Inserted | Analog input to the bias up circuit is tied to AGND as it is not used in this mode.                                                                                                                                                                                                                                                               |

| LK64     | Α        | +12 V is supplied by the EVAL-CONTROL-BRD2.                                                                                                                                                                                                                                                                                                       |

| LK65     | Α        | –12 V is supplied by the EVAL-CONTROL-BRD2.                                                                                                                                                                                                                                                                                                       |

| LK66     | Inserted | The output of the AD780 is not divided down so the input to U10 is tied to AGND.                                                                                                                                                                                                                                                                  |

#### **SINGLE-ENDED MODE**

The AD7938/AD7938-6 can operate with eight single-ended analog inputs. To operate the evaluation board in single-ended mode, change the link positions as shown in Table 3. Initially, all analog inputs are tied to ground to ensure that they are not floating on power up. Change the link positions depending on which analog inputs the links are using.

Table 3. Single-Ended Mode — Powered and Controlled by the EVAL-CONTROL-BRD2

| Table 3. Single-Ended Mode — Powered and Controlled by the EVAL-CONTROL-BRD2 |          |                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Link No.                                                                     | Position | Function                                                                                                                                                                                                                                                                                                           |

| LK1                                                                          | Α        | VDD for the AD8138 amplifiers is supplied by the EVAL-CONTROL-BRD2.                                                                                                                                                                                                                                                |

| LK2                                                                          | Α        | VSS for the AD8138 amplifiers is supplied by the EVAL-CONTROL-BRD2.                                                                                                                                                                                                                                                |

| LK3                                                                          | Α        | VDD for the AD7938/AD7939/AD7938-6 ADC is supplied by the EVAL-CONTROL-BRD2.                                                                                                                                                                                                                                       |

| LK4                                                                          | В        | VDRIVE is supplied by the EVAL-CONTROL-BRD2.                                                                                                                                                                                                                                                                       |

| LK5                                                                          | Α        | WR is supplied by the EVAL-CONTROL-BRD2.                                                                                                                                                                                                                                                                           |

| LK6                                                                          | Α        | BUSY is read by the EVAL-CONTROL-BRD2.                                                                                                                                                                                                                                                                             |

| LK7                                                                          | Α        | CONVST is supplied by the EVAL-CONTROL-BRD2.                                                                                                                                                                                                                                                                       |

| LK8                                                                          | Α        | RD is supplied by the EVAL-CONTROL-BRD2.                                                                                                                                                                                                                                                                           |

| LK9                                                                          | Α        | CS is supplied by the EVAL-CONTROL-BRD2.                                                                                                                                                                                                                                                                           |

| LK10                                                                         | В        | ADC is set up to operate in word mode.                                                                                                                                                                                                                                                                             |

| LK11                                                                         | Α        | CLKIN is supplied by the EVAL-CONTROL-BRD2.                                                                                                                                                                                                                                                                        |

| LK12                                                                         | Α        | An external reference is supplied to the Vout pin from the AD780.                                                                                                                                                                                                                                                  |

| LK13                                                                         | Α        | With LK13 in position A, a single-ended input or half a differential input is applied to V <sub>IN</sub> 4. If V <sub>IN</sub> 4 is not used, ground V <sub>IN</sub> 4 by installing LK13 in Position B.                                                                                                           |

| LK14                                                                         | А        | With LK14 in position A, a single-ended input or half a differential input is applied to $V_{IN}0$ . If $V_{IN}0$ is not used, ground $V_{IN}0$ by installing LK14 in Position B.                                                                                                                                  |

| LK15                                                                         | Α        | With LK15 in position A, a single-ended input or half a differential input is applied to $V_{IN}1$ . If $V_{IN}1$ is not used, ground $V_{IN}1$ by installing LK15 in Position B.                                                                                                                                  |

| LK16                                                                         | Α        | With LK16 in position A, a single-ended input or half a differential input is applied to $V_{IN}2$ . If $V_{IN}2$ is not used, ground $V_{IN}2$ by installing LK16 in Position B.                                                                                                                                  |

| LK17                                                                         | Α        | A single-ended, unipolar input must be supplied to $V_{IN}3$ through $V_{IN}7$ (P10) and is buffered by U8.                                                                                                                                                                                                        |

| LK18                                                                         | Inserted | On power-up, the inputs to the op amps are tied to ground so they are not floating. Once a signal is applied to P10, LK18 can be removed if a 50 $\Omega$ termination is not required.                                                                                                                             |

| LK19                                                                         | В        | The analog input signal applied to P7 is applied to the single buffer (U6).                                                                                                                                                                                                                                        |

| LK20                                                                         | Α        | A single-ended, unipolar input must be supplied to $V_{IN}2$ through $V_{IN}6$ (P7) and is buffered by U6.                                                                                                                                                                                                         |

| LK21                                                                         | Α        | A single-ended, unipolar input must be supplied to $V_{IN}1$ through $V_{IN}5$ (P3) and is buffered by U5.                                                                                                                                                                                                         |

| LK22                                                                         | Inserted | On power-up, the inputs to the op amps are tied to ground so they are not floating. Once a signal is applied to P3, LK22 can be removed if a 50 $\Omega$ termination is not required.                                                                                                                              |

| LK23                                                                         | Inserted | On power- up, the inputs to the op amps are tied to ground so they are not floating. Once a signal is applied to P7, LK23 can be removed if a 50 $\Omega$ termination is not required.                                                                                                                             |

| LK24                                                                         | В        | The negative input to the AD8138 is tied to AGND.                                                                                                                                                                                                                                                                  |

| LK25                                                                         | В        | The negative input to the AD8138 is tied to AGND.                                                                                                                                                                                                                                                                  |

| LK26                                                                         | Inserted | On power-up, the inputs to the op amps are tied to ground so they are not floating. Once a signal is applied to P1, LK26 can be removed if a 50 $\Omega$ termination is not required.                                                                                                                              |

| LK27                                                                         | Α        | The analog input signal applied to P1 is applied to the single buffer (U3).                                                                                                                                                                                                                                        |

| LK28                                                                         | Α        | A single-ended, unipolar input must be supplied to $V_{IN}0$ through $V_{IN}4$ (P1) and is buffered by U3.                                                                                                                                                                                                         |