SLLS919A-DECEMBER 2008-REVISED JANUARY 2009

# 1080p - Deep Color 3-to-1 HDMI/DVI Switch with Adaptive Equalization

### FEATURES

- 3:1 Switch Supporting DVI Above 1920 × 1200 and HDMI HDTV Resolutions up to 1080p With 16-bit Color Depth

- **Designed for Signaling Rates up to 3 Gbps**

- HDMI1.3a Spec Compliant .

- Adaptive Equalization to Support up to 20-m • **HDMI** Cable

- **TMDS Input Clock-Detect Circuit**

- **DDC Repeater Function** .

- <2 mW Low-Power Mode

- Local I<sup>2</sup>C or GPIO Configurable

- Enhanced ESD. HBM: 10 kV on All Input TMDS, DDC I<sup>2</sup>C, HPD Pins

- **3.3-Volt Power Supply**

## DESCRIPTION

- Temperature Range: 0°C to 70°C •

- 64-Pin TQFP Package: Pin-Compatible With • **TMDS351**

- **Robust TMDS Receive Stage That Can Work** With Non-Compliant Input Common-Mode **HDMI Signal**

### APPLICATIONS

- **High-Definition Digital TV**

- LCD

- Plasma

- **DLP<sup>®</sup>**

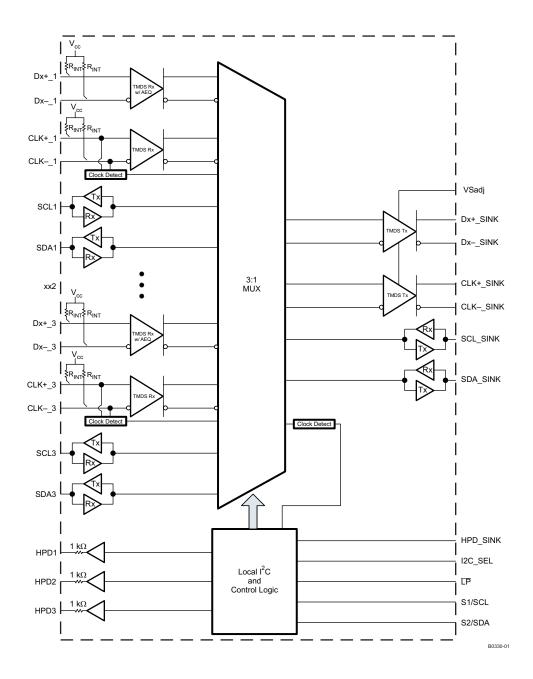

The TMDS361 is a three-port digital video interface (DVI) or high-definition multimedia interface (HDMI) switch that allows up to three DVI or HDMI ports to be switched to a single display terminal. Four TMDS channels, one hot-plug detector, and a digital display control (DDC) interface are supported on each port. Each TMDS channel supports signaling rates up to 3 Gbps to allow 1080p resolution in 16-bit color depth.

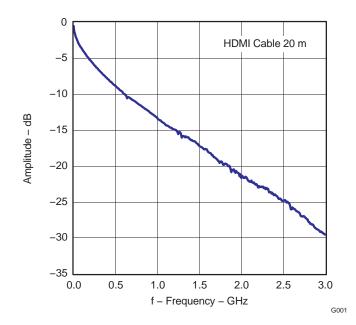

The TMDS361 provides an adaptive equalizer for different ranges of cable lengths. The equalizer automatically compensates for intersymbol interference [ISI] loss of an HDMI/DVI cable for up to 20 dB at 3 Gbps (see Figure 15).

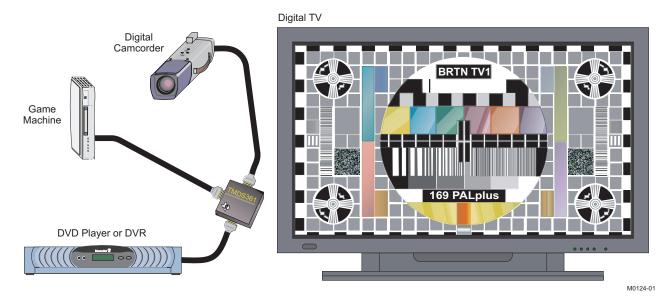

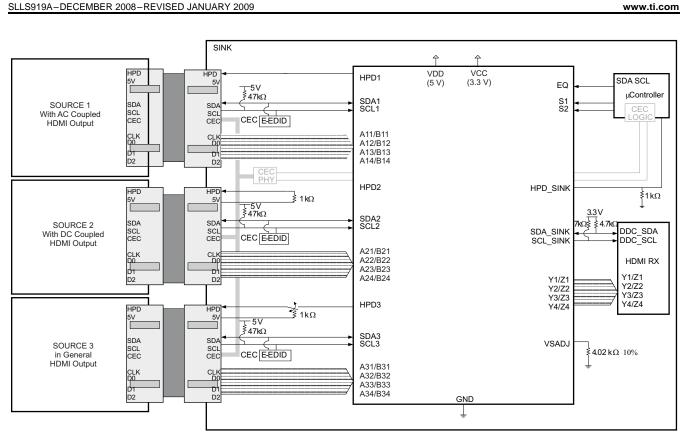

### **TYPICAL APPLICATION**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. DLP is a registered trademark of Texas Instruments.

Æ

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## **DESCRIPTION (CONTINUED)**

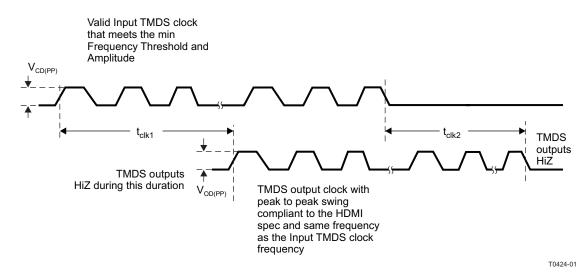

When any of the input ports are selected, the integrated terminations ( $50-\Omega$  termination resistors pulled up to VCC) are switched on for the TMDS clock channel, the TMDS clock-detection circuit is enabled, and the DDC repeater is enabled. After a valid TMDS clock is detected, the integrated termination resistors for the data lines are enabled, and the output TMDS lines are enabled. When an input port is not selected, the integrated terminations are switched off, the TMDS receivers are disabled, and the DDC repeater is disabled. Clock-detection circuitry provides an automatic power-management feature, because if no valid TMDS clock is detected, the terminations on the input TMDS data lines are disconnected and the TMDS outputs are placed in a high-impedance state.

The TMDS361 is designed to be controlled via a local I<sup>2</sup>C interface or GPIO interface based on the status of the I2C\_SEL pin. The local I<sup>2</sup>C interface in TMDS361 is a slave-only I<sup>2</sup>C interface. (See the I2C INTERFACE NOTES section.)

**I<sup>2</sup>C Mode**: When the I2C\_SEL pin is set low, the device is in I<sup>2</sup>C mode. With local I<sup>2</sup>C, the interface port status can be read and the advanced configurations of the device such as TMDS output edge rate control, DDC I<sup>2</sup>C buffer output-voltage-select (OVS) settings (See the DDC I2C Function Description for detailed description on DDC I<sup>2</sup>C buffer description and OVS description), device power management, TMDS clock-detect feature and TMDS input-port selection can be set. See Table 8 through Table 11.

**GPIO mode:** When the I2C\_SEL pin is set high, the device is in GPIO control mode. The <u>port</u> selection is controlled with source selectors, S1 and S2. The power-saving mode is controlled through the LP pin. In GPIO mode, the default TMDS output edge rate that is the fastest setting of rise and fall time is set, and the default DDC I<sup>2</sup>C buffer OVS setting (OVS3) is set. See Table 8 and the DDC I<sup>2</sup>C Function Description for detailed description of the DDC I<sup>2</sup>C buffer.

Following are some of the key features (advantages) that TMDS361 provides to the overall sink-side system (HDTV).

- 3x1 switch that supports TMDS data rates up to 3 Gbps on all three input ports.

- ESD: Built-in support for high ESD protection (up to 10 kV on the HDMI source side). The HDMI source-side pins on the TMDS361 are connected via the HDMI/DVI exterior connectors and cable to the HDMI/DVI sources (e.g., DVD player). In TV applications, it can be expected that the source side may be subjected to higher ESD stresses compared to the sink side that is connected internally to the HDMI receiver.

- Adaptive equalization: The built-in adaptive equalization support compensates for intersymbol interference [ISI] loss of up to 20 dB, which represents a typical 20-m HDMI/DVI cable at 3 Gbps. Adaptive equalization adjusts the equalization gain **automatically**, based on the cable length and the incoming TMDS data rate.

- TMDS clock-detect circuitry: This feature provides an automatic power-management feature and also ensures that the TMDS output port is turned on only if there is a valid TMDS input signal. TMDS clock-detect feature can be by-passed in I<sup>2</sup>C Mode, See Table 10 and Table 11. It is recommended to enable TMDS clock-detect circuitry during normal operation. However, for HDMI compliance testing (TMDS Termination Voltage Test), the clock detect feature should be disabled by using the I2C mode control. If the customer requires to pass TMDS Termination Voltage Test in GPIO mode with default TMDS clock-detect circuitry enabled, then a valid TMDS clock should be provided for this complaince test, so that the terminations on the TMDS data pair can be connected and thus customer can pass the TMDS Termination Voltage Test.

- DDC I<sup>2</sup>C buffer: This feature provides isolation on the source side and sink side DDC I<sup>2</sup>C capacitance, thus helping the sink system to pass system-level compliance.

- Robust TMDS receive stage: This feature ensures that the TMDS361 can work with TMDS input signals having common-mode voltage levels that can be either compliant or non-compliant with HDMI/DVI specifications.

- VSadj: This feature adjusts the TMDS output swing and can help the sink system to tune the output TMDS swing of the TMDS361 (if needed) based on the system requirements.

- GPIO or local I<sup>2</sup>C interface to control the device features.

- TMDS output edge-rate control: This feature adjusts the TMDS361 TMDS output rise and fall times. There are four settings of the rise and fall times that can be chosen. The default setting is the fastest rise and fall

time; the other three settings are slower. Slower edge transitions can potentially help the sink system (HDTV) in passing regulatory EMI compliance.

### FUNCTIONAL BLOCK DIAGRAM

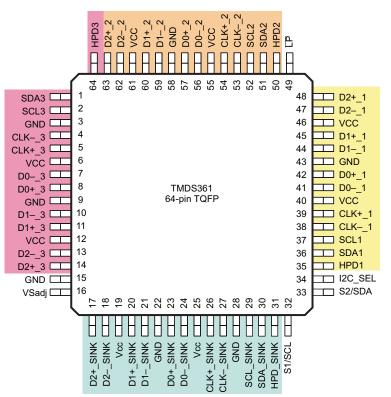

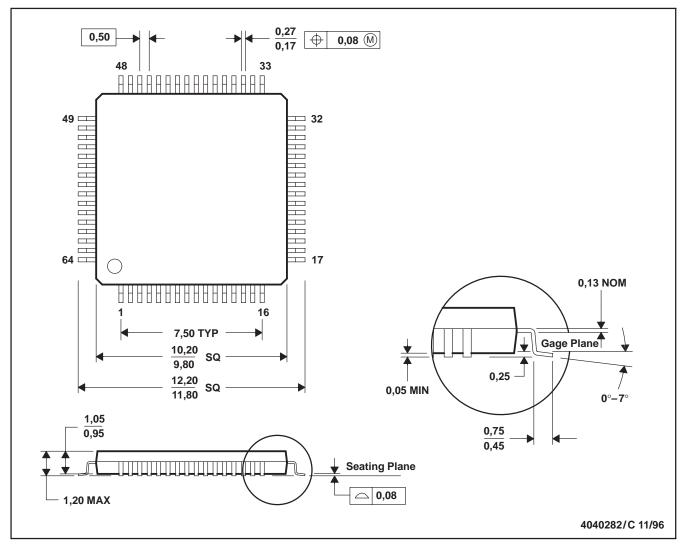

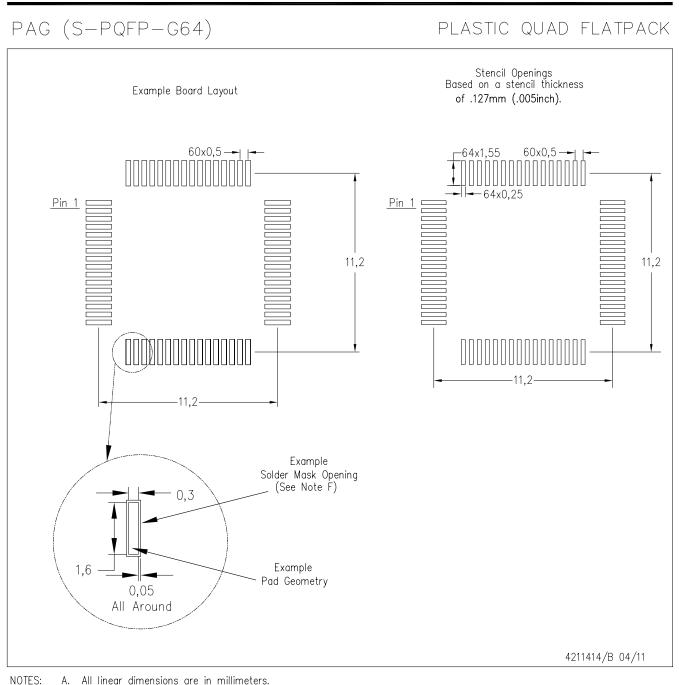

## PAG PACKAGE

PAG-64 (Top View)

P0010-03

### **TERMINAL FUNCTIONS**

| TERMINAL                     |                                  |     | DECODIDION                                                 |

|------------------------------|----------------------------------|-----|------------------------------------------------------------|

| SIGNAL                       | NO.                              | I/O | DESCRIPTION                                                |

|                              | <u>.</u>                         |     | TMDS INPUT PINS                                            |

| CLK+_1<br>CLK1               | 39<br>38                         | I   | Port-1 TMDS differential clock                             |

| D[0:2]+_1<br>D[0:2]1         | 42, 45, 48<br>41, 44, 47         | I   | Port-1 TMDS differential data inputs                       |

| CLK+_2<br>CLK2               | 54<br>53                         | I   | Port-2 TMDS differential clock                             |

| D[0:2]+_2<br>D[0:2]2         | 57, 60, 63<br>56, 59, 62         | I   | Port-2 TMDS differential data inputs                       |

| CLK+_3<br>CLK3               | 5<br>4                           | I   | Port-3 TMDS differential clock                             |

| D[0:2]+_3<br>D[0:2]3         | 8, 11, 14<br>7, 10, 13           | I   | Port-3 TMDS differential data inputs                       |

|                              | L.                               | 1   | TMDS OUTPUT PINS                                           |

| CLK+_SINK<br>CLK–_SINK       | 26<br>27                         | 0   | TMDS sink differential clock                               |

| D[0:2]+_SINK<br>D[0:2]–_SINK | 23, 20, 17<br>24, 21, 18         | 0   | TMDS sink differential data outputs                        |

|                              |                                  |     | HOT-PLUG-DETECT STATUS PINS                                |

| HPD[1:3]                     | 35, 50, 64                       | 0   | Source port hot-plug-detect output                         |

| HPD_SINK                     | 31                               | I   | Sink hot-plug-detect input                                 |

|                              |                                  | 1   | DDC PINS                                                   |

| SCL[1:3]                     | 37, 52, 2                        | I/O | TMDS port bidirectional DDC clock                          |

| SDA[1:3]                     | 36, 51, 1                        | I/O | TMDS port bidirectional DDC data                           |

| SCL_SINK                     | 29                               | I/O | TMDS sink-side bidirectional DDC clock                     |

| SDA_SINK                     | 30                               | I/O | TMDS sink-side bidirectional DDC data                      |

|                              | 1                                | 1   | CONTROL PINS                                               |

| LP                           | 49                               | I   | Low-power select bar                                       |

| I2C_SEL                      | 34                               | I   | GPIO/local I <sup>2</sup> C control select                 |

| S1/SCL                       | 32                               | I   | Source select 1(GPIO) / local I <sup>2</sup> C clock (I2C) |

| S2/SDA                       | 33                               | I/O | Source select 2 (GPIO) / local I <sup>2</sup> C data (I2C) |

| VSadj                        | 16                               | I   | TMDS-compliant voltage swing control                       |

|                              |                                  |     | SUPPLY AND GROUND PINS                                     |

| VCC                          | 6, 12, 19, 25,<br>40, 46, 55, 61 |     | 3.3-V supply                                               |

| GND                          | 3, 9, 15, 22,<br>28, 43, 58      |     | Ground                                                     |

TMDS361 SLLS919A-DECEMBER 2008-REVISED JANUARY 2009 TEXAS INSTRUMENTS

www.ti.com

| CONTR | OL PINS | I/O SELE                                                            | CTED                                                                | HOT      | HOT-PLUG DETECT STATUS |          |              |  |

|-------|---------|---------------------------------------------------------------------|---------------------------------------------------------------------|----------|------------------------|----------|--------------|--|

| S2    | S1      | Port Selected                                                       | SCL_SINK<br>SDA_SINK                                                | HPD1     | HPD2                   | HPD3     |              |  |

| Н     | Н       | Port 1<br>Terminations of<br>port 2 and port 3<br>are disconnected. | SCL1<br>SDA1                                                        | HPD_SINK | L                      | L        | Normal mode  |  |

| Н     | L       | Port 2<br>Terminations of<br>port 1 and port 3<br>are disconnected. | SCL2<br>SDA2                                                        | L        | HPD_SINK               | L        | Normal mode  |  |

| L     | L       | Port 3<br>Terminations of<br>port 1 and port 2<br>are disconnected. | SCL3<br>SDA3                                                        | L        | L                      | HPD_SINK | Normal mode  |  |

| L     | Н       | None (Z)<br>All terminations are<br>disconnected.                   | None (Z)<br>Are pulled HIGH<br>by external<br>pullup<br>termination | HPD_SINK | HPD_SINK               | HPD_SINK | Standby mode |  |

## Table 1. Source Selection Lookup<sup>(1)</sup>

(1) H: Logic high; L: Logic low; X: Don't care; Z: High impedance

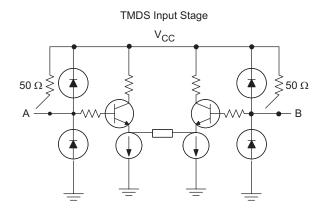

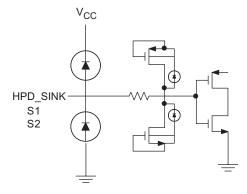

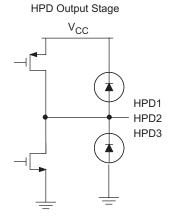

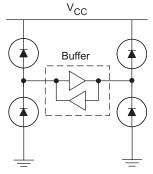

### EQUIVALENT INPUT AND OUTPUT SCHEMATIC DIAGRAMS

TMDS Output Stage

Status and Source Selector

DDC Buffer

S0386-01

TMDS361 SLLS919A-DECEMBER 2008-REVISED JANUARY 2009

www.ti.com

**INSTRUMENTS**

EXAS

| SIGNAL         | LEVEL STATE |      | STATE                       | DESCRIPTION                                                                                                                                                                                               |

|----------------|-------------|------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LP             | ł           | 4    | Normal mode                 | Normal operational mode for device. If $\overline{\text{LP}}$ is left floating, then a weak internal pullup to VCC pulls it to VCC.                                                                       |

| LF             | L           |      | Low-power<br>mode           | Device is forced into a low-power state, causing the inputs and outputs to go to a high-impedance state. All other inputs are ignored.                                                                    |

|                | S2          | S1   |                             |                                                                                                                                                                                                           |

|                | Н           | Н    | Port 1                      | Port 1 is selected as the active port; all other ports are low.                                                                                                                                           |

| S[2:1]<br>GPIO | Н           | L    | Port 2                      | Port 2 is selected as the active port; all other ports are low.                                                                                                                                           |

| mode           | L           | L    | Port 3                      | Port 3 is selected as the active port; all other ports are low.                                                                                                                                           |

|                | L           | н    | HPD[1:3] follow<br>HPD_SINK | Standby mode: HPD[1:3] follow HPD_sink.                                                                                                                                                                   |

|                |             |      | l <sup>2</sup> C            | Device is configured by I <sup>2</sup> C logic.                                                                                                                                                           |

| I2C_SEL        | ł           | 4    | GPIO                        | Device is configured by GPIO. If the I2C_SEL pin is left floating, then a weak internal pullup to VCC pulls the I2C_SEL pin high.                                                                         |

| VSadj 4.02 kΩ  |             | 2 kΩ | Compliant<br>voltage        | Driver output voltage swing precision control to aid with system compliance. The VSadj resistor value can be selected to be 4.02 k $\Omega$ ±10% based on the system requirement to pass HDMI compliance. |

### Table 2. Control-Pin Lookup Table<sup>(1)</sup>

(1) (H) Logic high; (L) Logic low

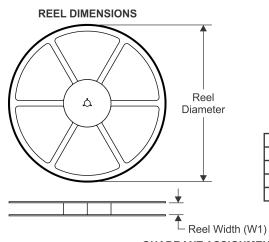

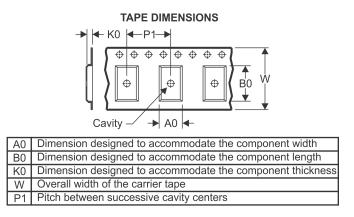

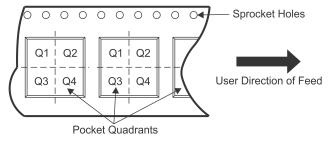

### ORDERING INFORMATION<sup>(1)</sup>

| PART NUMBER | PART MARKING | PACKAGE                  |

|-------------|--------------|--------------------------|

| TMDS361PAGR | TMDS361      | 64-pin TQFP reel (large) |

| TMDS361PAG  | TMDS361      | 64-pin TQFP tray         |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI Web site at www.ti.com.

### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                          |                                                                                                                        | VALUE                                                  | UNIT       |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------|

| Supply voltage range <sup>(2)</sup>      | VCC                                                                                                                    | -0.3 to 3.6                                            | V          |

|                                          | TMDS I/O                                                                                                               | -0.3 to 4                                              |            |

| Voltage range                            | HPD and DDC I/O                                                                                                        | -0.3 to 5.5                                            | V          |

|                                          | Control and status I/O                                                                                                 | -0.3 to 3.6<br>-0.3 to 4<br>-0.3 to 5.5<br>-0.3 to 5.5 |            |

|                                          | Human body model <sup>(3)</sup> on SCL[1:3], SDA[1:3], HPD[1:3], D[0:2]+_[1:3], D[0:2][1:3], CLK+_[1:3], CLK[1:3] pins | ±10,000                                                |            |

| Voltage range<br>Electrostatic discharge | Human body model <sup>(3)</sup> on all other pins                                                                      | ±9,000                                                 |            |

|                                          | Charged-device model <sup>(4)</sup>                                                                                    | ±1500                                                  | V          |

| -                                        | Machine model <sup>(5)</sup>                                                                                           | ±200                                                   | -          |

|                                          | IEC 61000-4-2 <sup>(6)</sup> , contact discharge                                                                       | ±8,000                                                 | -          |

|                                          | IEC 61000-4-2 <sup>(6)</sup> , air discharge                                                                           | ±15,000                                                |            |

| Continuous power dissipa                 | ation                                                                                                                  | See Dissipation Rat                                    | ings table |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values, except differential voltages, are with respect to network ground terminal.

(3) Tested in accordance with JEDEC Standard 22, Test Method A114-B

(4) Tested in accordance with JEDEC Standard 22, Test Method C101-A

(5) Tested in accordance with JEDEC Standard 22, Test Method A115-A

(6) Tested in accordance with IEC EN 61000-4-2

### **DISSIPATION RATINGS**

| PACKAGE           | PCB JEDEC STANDARD | T <sub>A</sub> ≤ 25°C | DERATING FACTOR <sup>(1)</sup><br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING |

|-------------------|--------------------|-----------------------|---------------------------------------------------------------|---------------------------------------|

| 64-pin TQFP (PAG) | Low-K              | 1066 mW               | 10.66 mW/°C                                                   | 586 mW                                |

|                   | High-K             | 1481 mW               | 14.8 mW/°C                                                    | 814 mW                                |

(1) This is the inverse of the junction-to-ambient thermal resistance when board-mounted and with no air flow.

## THERMAL CHARACTERISTICS

over operating free-air temperature range (unless otherwise noted)

|                   | PARAMETER                                                               | TEST CONDITIONS                                                                                                                                       | MIN | TYP   | MAX <sup>(1)</sup> | UNIT |

|-------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|--------------------|------|

| $R_{\theta JB}$   | Junction-to-board thermal resistance                                    |                                                                                                                                                       |     | 37.13 |                    | °C/W |

| $R_{\thetaJC}$    | Junction-to-case thermal resistance                                     |                                                                                                                                                       |     | 15.3  |                    | °C/W |

| P <sub>D(1)</sub> | Device power dissipation in normal mode                                 | $\overline{\text{LP}}$ = HIGH TMDS: V <sub>ID(pp)</sub> = 1200 mV, 3 Gbps<br>TMDS data pattern; HPD_SINK = HIGH, S1/S2 = LOW/LOW, LOW/HIGH, HIGH/HIGH |     | 560   | 780                | mW   |

| P <sub>D(2)</sub> | Device power dissipation in standby mode                                | $\overline{\text{LP}}$ = HIGH, TMDS: V <sub>ID(pp)</sub> = 1200 mV, 3 Gbps<br>TMDS data pattern; HPD_SINK = HIGH, S1 =<br>HIGH, S2 = LOW              |     | 10    | 20                 | mW   |

| P <sub>SD</sub>   | Device power dissipation in low-power mode                              | <u>LP</u> = LOW                                                                                                                                       |     | 1     | 2                  | mW   |

| P <sub>NCLK</sub> | Device power dissipation in normal mode with no active TMDS input clock | IP       = HIGH, No TMDS input clock, HPD_SINK         =HIGH, S1/S2       = LOW/LOW, LOW/HIGH,         HIGH/HIGH                                      |     | 40    | 65                 | mW   |

(1) The maximum rating is simulated under 3.6V VCC across worse case temperature and process variation, Typical conditions are simulated at 3.3V VCC, 25 °C with nominal process material.

### **RECOMMENDED OPERATING CONDITIONS**

|                     |                                                  | MIN       | NOM  | MAX        | UNIT |

|---------------------|--------------------------------------------------|-----------|------|------------|------|

| VCC                 | Supply voltage                                   | 3         | 3.3  | 3.6        | V    |

| T <sub>A</sub>      | Operating free-air temperature                   | 0         |      | 70         | °C   |

| TMDS D              | IFFERENTIAL OUTPUT PINS                          |           |      |            |      |

| V <sub>ID(pp)</sub> | Peak-to-peak input differential voltage          | 0.15      |      | 1.56       | V    |

| V <sub>IC</sub>     | Input common-mode voltage                        | VCC - 0.4 | ١    | /CC + 0.01 | V    |

| AVCC                | TMDS output termination voltage                  | 3         | 3.3  | 3.6        | V    |

| d <sub>R</sub>      | Data rate                                        |           |      | 3          | Gbps |

| R <sub>VSadj</sub>  | Resistor for TMDS-compliant voltage output swing | 3.66      | 4.02 | 4.47       | kΩ   |

| R <sub>T</sub>      | Termination resistance                           | 45        | 50   | 55         | Ω    |

| DDC PIN             | IS                                               |           |      |            |      |

| VI                  | Input voltage                                    | 0         |      | 5.5        | V    |

| d <sub>R(I2C)</sub> | I <sup>2</sup> C data rate                       |           |      | 100        | Kbps |

| HPD AN              | D CONTROL PINS                                   | 1         |      |            |      |

| V <sub>IH</sub>     | High-level input voltage                         | 2         |      | 5.5        | V    |

| V <sub>IL</sub>     | Low-level input voltage                          | 0         |      | 0.8        | V    |

### DEVICE POWER

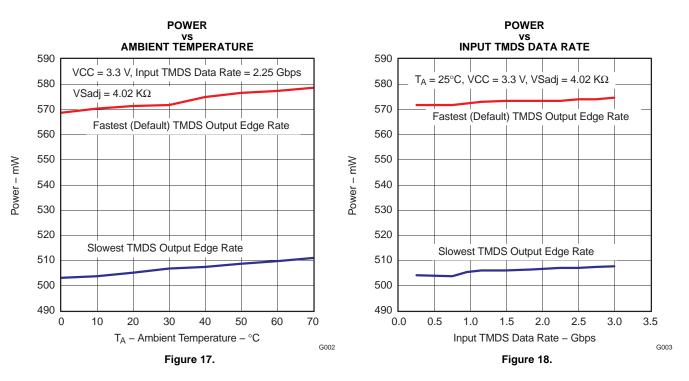

The TMDS361 is designed to operate from a single 3.3-V supply voltage. The TMDS361 has three power modes of operation. These three modes are referred to as normal mode, standby mode, and low-power mode.

Normal mode is designed to be used during typical operating conditions. In normal mode, the device is fully functional and consumes the greatest amount of power.

Standby mode is designed to be used when reduced power is desired, but DDC and HPD communication must be maintained. Standby mode can be enabled via the I<sup>2</sup>C interface (See Table 8 through Table 11). or GPIO interface (See Table 1). In standby mode, the high-speed TMDS data and clock channels are disabled to reduce power consumption. The internal I<sup>2</sup>C logic and DDC function normally. HPD[1:3] follow HPD\_SINK.

Low-power mode is designed to consume the least possible amount of power while still applying 3.3 V to the device. Low-power mode can be enabled by either the LP pin or by local  $I^2C$  (See Table 8 through Table 11). In low-power mode, all of the inputs and outputs are disabled with the exception of the internal  $I^2C$  logic and LP pin.

The clock-detect feature in the TMDS361 provides an automatic power-management feature in normal mode. if no valid TMDS clock is detected, the terminations on the input TMDS data lines are disconnected, and the TMDS outputs are high-Z. As soon as a valid TMDS clock is detected, the terminations on the TMDS data lines are connected, the TMDS outputs come out of high-Z, and the device is fully functional and consumes the greatest amount of power.

### **ELECTRICAL CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted)

|                   | PARAMETER                                                  | TEST CONDITIONS                                                                                                                                    |  | TYP | MAX | UNIT |

|-------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|-----|-----|------|

| I <sub>CC</sub>   | Normal-mode supply current                                 | $\overline{\text{LP}}$ = HIGH TMDS: $V_{\text{ID}(pp)}$ = 1200 mV, 3 Gbps TMDS data pattern; HPD_SINK = HIGH, S1/S2 = LOW/LOW, LOW/HIGH, HIGH/HIGH |  | 170 | 216 | mA   |

| I <sub>STBY</sub> | Standby supply current                                     | <u>LP</u> = HIGH, TMDS: V <sub>ID(pp)</sub> = 1200 mV, 3 Gbps TMDS data<br>pattern; HPD_SINK = HIGH, S1 = HIGH, S2 = LOW                           |  | 3   | 5.5 | mA   |

| I <sub>SD</sub>   | Shutdown current                                           | <u>LP</u> = LOW                                                                                                                                    |  | 300 | 555 | μA   |

| I <sub>NCLK</sub> | Normal-mode supply current, with no active TMDS input cloc | IP       HIGH, No TMDS input clock, HPD_SINK =HIGH, S1/S2 =         LOW/LOW, LOW/HIGH, HIGH/HIGH                                                   |  | 12  | 18  | mA   |

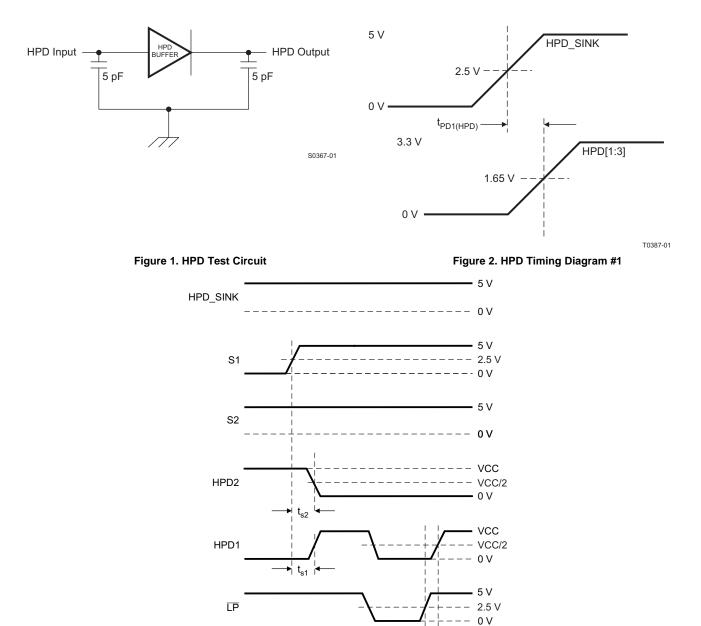

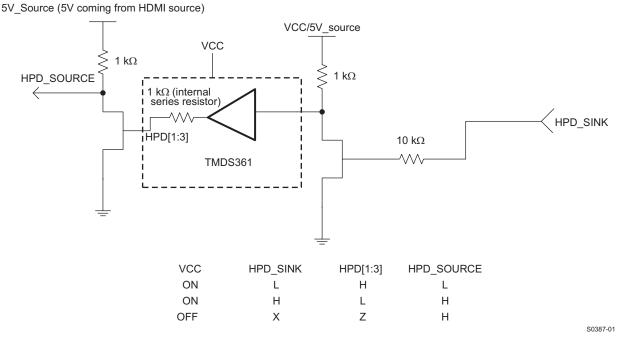

### HOT-PLUG DETECT

The TMDS361 is designed to support the hot-plug indication to the input ports (HDMI/DVI sources connected to TMDS361) via the HPD[1:3] output pins. The state of the hot-plug output of the selected source follows the state of the hot-plug input (HPD\_SINK input pin) from the sink side. The state of the hot-plug output for the non-selected source goes low (See Table 1).

The maximum  $V_{OH}$  of the HPD depends on VCC. It is recommended that if  $V_{OH}$  greater than 3.6 V is needed on HPD, then an external circuit can be used to drive the  $V_{OH}$  off of the +5 V from the HDMI source connected (as shown in Figure 33).

### ELECTRICAL CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

|                      | PARAMETER                 | TEST CONDITIONS                    | MIN | TYP  | MAX  | UNIT |

|----------------------|---------------------------|------------------------------------|-----|------|------|------|

| V <sub>OH(HPD)</sub> | High-level output voltage | I <sub>OH</sub> = 100 μA           | 2   |      | VCC  | V    |

| V <sub>OL(HPD)</sub> | Low-level output voltage  | I <sub>OL</sub> = 100 μA           | 0   |      | 0.4  | V    |

| I <sub>H</sub>       | High-level input current  | V <sub>IH</sub> = 2 V, VCC = 3.6 V | -10 |      | 10   | μA   |

| IL                   | Low-level input current   | $V_{IL} = 0.8 V, VCC = 3.6 V$      | -10 |      | 10   | μA   |

| RL                   | Output source impedance   |                                    | 800 | 1000 | 1200 | Ω    |

## SWITCHING CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

|                       | PARAMETER                                 | TEST CONDITIONS      | MIN | TYP | MAX | UNIT |

|-----------------------|-------------------------------------------|----------------------|-----|-----|-----|------|

| t <sub>PD1(HPD)</sub> | HPD_SINK propagation delay                | HPD_SINK to HPD[1:3] |     | 12  | 20  | ns   |

| t <sub>S1(HPD)</sub>  | Selecting port HPD switch time            | S[1:2] to HPD[1:3]   |     | 17  | 30  | ns   |

| t <sub>S2(HPD)</sub>  | Deselecting port HPD switch time          | S[1:2] to HPD[1:3]   |     | 14  | 22  | ns   |

| t <sub>Z(HPD)</sub>   | Low-power to high-level propagation delay | LP to HPD[1:3]       |     | 13  | 20  | ns   |

Figure 3. HPD Timing Diagram #2

T0423-01

## **TMDS361**

SLLS919A-DECEMBER 2008-REVISED JANUARY 2009

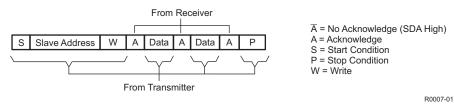

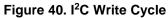

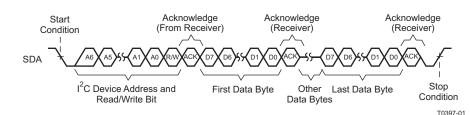

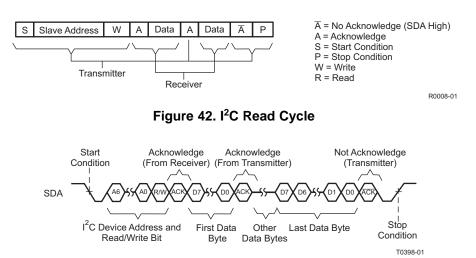

## TMDS DDC and Local I<sup>2</sup>C Pins

**DDC I<sup>2</sup>C Buffer or Repeater:** The TMDS361 provides buffering on the DDC I<sup>2</sup>C interface for each of the input ports connected. This feature isolates the capacitance on the source side from the sink side and thus helps in passing system-level compliance. See the DDC I<sup>2</sup>C Function Description section for a detailed description on how the DDC I<sup>2</sup>C buffer operates. Note that a key requirement on the sink side is that the V<sub>IL(Sink)</sub> (input to TMDS361) should be less than 0.4 V. This requirement should be met for the DDC I<sup>2</sup>C buffer to function properly. There are three settings of V<sub>IL(Sink)</sub> and V<sub>OL(Sink)</sub> that can be chosen based on OVS settings (See Table 8 through Table 11).

**Local I<sup>2</sup>C Interface:** The TMDS361 includes a slave I<sup>2</sup>C interface to control device features like TMDS input port selection, TMDS output edge-rate control, power management, DDC buffer OVS settings, etc. See Table 8 through Table 11.

The TMDS361 is designed to be controlled via a local  $I^2C$  interface or GPIO interface, based on the status of the I2C\_SEL pin. The local  $I^2C$  interface in the TMDS361 is only a slave  $I^2C$  interface. See the I2C INTERFACE NOTES section for a detailed description of  $I^2C$  functionality.

### **ELECTRICAL CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted)

|                        | PARAMETER                |                | TEST CONDITIONS                                | MIN  | TYP MAX | UNIT |

|------------------------|--------------------------|----------------|------------------------------------------------|------|---------|------|

| IL                     | Low-level input current  |                | VCC = 3.6 V, V <sub>1</sub> = 0 V              | -10  | 10      | μA   |

| IIkg(Sink)             | Input leakage current    | Sink pins      | VCC = 3.6 V, V <sub>I</sub> = 4.95 V           | -10  | 10      | μA   |

| C <sub>IO(Sink)</sub>  | Input/output capacitance | Sink pins      | DC bias = 2.5 V, AC = 3.5 Vp-p,<br>f = 100 kHz |      | 15      | pF   |

| V <sub>IH(Sink)</sub>  | High-level input voltage | Sink pins      |                                                | 2.1  | 5.5     | V    |

| VIL1(Sink)             | Low-level input voltage  | Sink pins      | OVS 1                                          | -0.2 | 0.4     | V    |

| V <sub>OL1(Sink)</sub> | Low-level output voltage | Sink pins      | I <sub>O</sub> = 3 mA, OVS = HIGH              | 0.6  | 0.7     | V    |

| VIL2(Sink)             | Low-level input voltage  | Sink pins      | OVS 2                                          | -0.2 | 0.4     | V    |

| V <sub>OL2(Sink)</sub> | Low-level output voltage | Sink pins      | I <sub>O</sub> = 3 mA, OVS = LOW               | 0.5  | 0.6     | V    |

| V <sub>IL3(Sink)</sub> | Low-level input voltage  | Sink pins      | OVS 3                                          | -0.2 | 0.3     | V    |

| V <sub>OL3(Sink)</sub> | Low-level output voltage | Sink pins      | I <sub>O</sub> = 3 mA, OVS = high-Z            | 0.4  | 0.5     | V    |

| I <sub>lkg(I2C)</sub>  | Input leakage current    | Port[1:3] pins | VCC = 3.6 V, V <sub>I</sub> = 4.95 V           | -10  | 10      | μA   |

| C <sub>IO(I2C)</sub>   | Input/output capacitance | Port[1:3] pins | DC bias = 2.5 V, AC = 3.5 Vp-p,<br>f = 100 kHz |      | 15      | pF   |

| V <sub>IH(I2C)</sub>   | High-level input voltage | Port[1:3] pins |                                                | 2.1  | 5.5     | V    |

| V <sub>IL(I2C)</sub>   | Low-level input voltage  | Port[1:3] pins |                                                | -0.2 | 1.5     | V    |

| V <sub>OL(I2C)</sub>   | Low-level output voltage | Port[1:3] pins | I <sub>O</sub> = 3 mA                          |      | 0.2     | V    |

# SWITCHING CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

|                      | PARAMETER                                              | TEST CONDITIONS        | MIN | TYP MA | X UNIT |

|----------------------|--------------------------------------------------------|------------------------|-----|--------|--------|

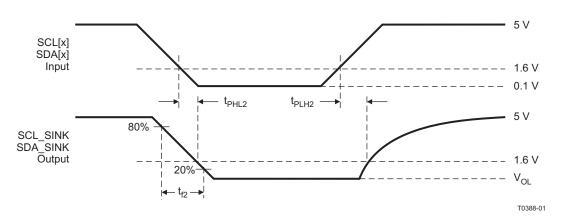

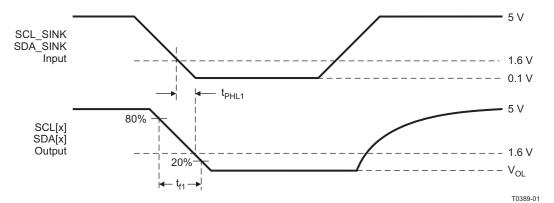

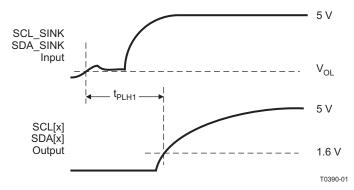

| t <sub>PLH1</sub>    | Propagation delay time, low to high                    | Source to sink         | 80  | 2      | 51 ns  |

| t <sub>PHL1</sub>    | Propagation delay time, high to low                    | Source to sink         | 35  | 20     | 00 ns  |

| t <sub>PLH2</sub>    | Propagation delay time, low to high                    | Sink to source         | 204 | 4      | i9 ns  |

| t <sub>PHL2</sub>    | Propagation delay time, high to low                    | Sink to source         | 35  | 20     | 00 ns  |

| t <sub>f1</sub>      | Output signal fall time                                | Sink side              | 20  | •      | '2 ns  |

| t <sub>f2</sub>      | Output-signal fall time                                | Source side            | 20  | •      | '2 ns  |

| f <sub>SCL</sub>     | SCL clock frequency for internal register              | Local I <sup>2</sup> C |     | 10     | 00 kHz |

| t <sub>W(L)</sub>    | Clock LOW period for I <sup>2</sup> C register         | Local I <sup>2</sup> C | 4.7 |        | μs     |

| t <sub>W(H)</sub>    | Clock HIGH period for internal register                | Local I <sup>2</sup> C | 4   |        | μs     |

| t <sub>SU1</sub>     | Internal register setup time, SDA to SCL               | Local I <sup>2</sup> C | 250 |        | ns     |

| t <sub>h(1)</sub> *1 | Internal register hold time, SCL to SDA                | Local I <sup>2</sup> C | 0   |        | μs     |

| t <sub>(buf)</sub>   | Internal register bus free time between STOP and START | Local I <sup>2</sup> C | 4.7 |        | μs     |

| t <sub>su(2)</sub>   | Internal register setup time, SCL to START             | Local I <sup>2</sup> C | 4.7 |        | μs     |

| t <sub>h(2)</sub>    | Internal register hold time, START to SCL              | Local I <sup>2</sup> C | 4   |        | μs     |

| t <sub>su(3)</sub>   | Internal register hold time, SCL to STOP               | Local I <sup>2</sup> C | 4   |        | μs     |

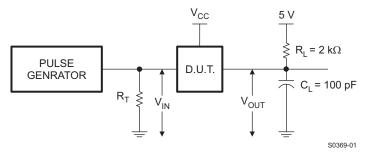

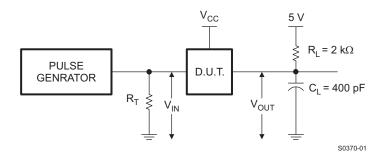

Figure 4. Sink-Side Test Circuit

Figure 5. Source-Side Test Circuit

Figure 6. Source-Side Output AC Measurements

Figure 7. Sink-Side Output AC Measurements

Figure 8. Source-Side Output AC Measurements (Continued)

### **TMDS Main Link Pins**

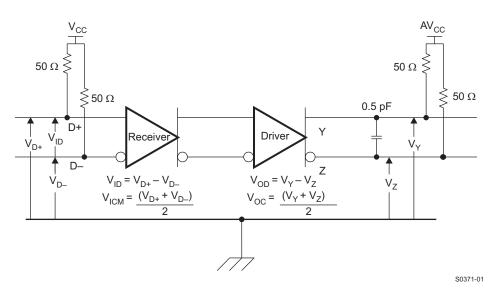

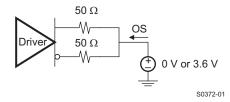

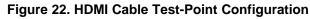

The TMDS port of the TMDS361 is designed to be compliant with the Digital Video Interface (DVI) 1.0 and High Definition Multimedia Interface (HDMI) 1.3 specifications. The differential output voltage swing can be fine-tuned with the VSadj resistor.

## **ELECTRICAL CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted)

|                     | PARAMETER                                                              | TEST CONDITIONS                                                         | MIN        | TYP | MAX       | UNIT |

|---------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------|------------|-----|-----------|------|

| V <sub>OH</sub>     | Single-ended HIGH-level output voltage                                 |                                                                         | AVCC - 10  |     | AVCC + 10 | mV   |

| V <sub>OL</sub>     | Single-ended LOW-level output voltage                                  | *                                                                       | AVCC - 600 | A   | VCC - 400 | mV   |

| V <sub>SWING</sub>  | Single-ended output voltage swing                                      | *                                                                       | 400        |     | 600       | mV   |

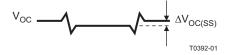

| V <sub>OC(SS)</sub> | Change in steady-state common-mode output voltage between logic states | AVCC = 3.3 V, R <sub>T</sub> = 50 Ω                                     |            |     | 5         | mV   |

| V <sub>OD(pp)</sub> | Peak-to-peak output differential voltage                               | *                                                                       | 800        |     | 1200      | mV   |

| V <sub>(O)SBY</sub> | Single-ended standby output voltage                                    |                                                                         | AVCC - 10  |     | AVCC + 10 | mV   |

| I <sub>(O)OFF</sub> | Single-ended power-down output current                                 | 0 V $\leq$ VCC $\leq$ 1.5 V, AVCC = 3.3 V, R <sub>T</sub> = 50 $\Omega$ | -10        |     | 10        | μA   |

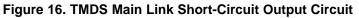

| I <sub>OS</sub>     | Short-circuit output current                                           | See Figure 16                                                           | -15        | 12  | 15        | mA   |

| V <sub>CD(pp)</sub> | Minimum valid clock differential voltage (peak-to-peak)                | Input TMDS clock frequency = 300<br>MHz                                 | 100        |     |           | mV   |

### SWITCHING CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

|                       | PARAMETER                                                            | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                   | MIN | TYP <sup>(1)</sup> | MAX | UNIT |

|-----------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|-----|------|

| t <sub>PLH</sub>      | Propagation delay time                                               |                                                                                                                                                                                                                                                                                                                                                                                                   | 250 |                    | 800 | ps   |

| t <sub>PHL</sub>      | Propagation delay time                                               |                                                                                                                                                                                                                                                                                                                                                                                                   | 250 |                    | 800 | ps   |

| t <sub>R1</sub>       | Rise time, fastest mode (default setting):<br>Fastest Setting        |                                                                                                                                                                                                                                                                                                                                                                                                   | 84  | 110                | 140 | ps   |

| t <sub>F1</sub>       | Fall time, fastest mode (default setting):<br>Fastest Setting        |                                                                                                                                                                                                                                                                                                                                                                                                   | 84  | 110                | 140 | ps   |

| t <sub>R2</sub>       | Rise time, fastest mode + 50 ps<br>(approximately)                   |                                                                                                                                                                                                                                                                                                                                                                                                   | 142 | 160                | 190 | ps   |

| t <sub>F2</sub>       | Fall time, fastest mode + 50 ps<br>(approximately)                   | AVCC = 3.3 V, $R_T$ = 50 $\Omega$ . See Figure 9 and Figure 10.                                                                                                                                                                                                                                                                                                                                   | 142 | 160                | 190 | ps   |

| t <sub>R3</sub>       | Rise time, fastest mode + 100 ps<br>(approximately)                  |                                                                                                                                                                                                                                                                                                                                                                                                   | 187 | 210                | 230 | ps   |

| t <sub>F3</sub>       | Fall time, fastest mode + 100 ps<br>(approximately)                  |                                                                                                                                                                                                                                                                                                                                                                                                   | 187 | 210                | 230 | ps   |

| t <sub>R4</sub>       | Rise time, fastest mode + 120 ps<br>(approximately): Slowest Setting |                                                                                                                                                                                                                                                                                                                                                                                                   | 216 | 230                | 260 | ps   |

| t <sub>F4</sub>       | Fall time, fastest mode + 120 ps<br>(approximately): Slowest Setting |                                                                                                                                                                                                                                                                                                                                                                                                   | 216 | 230                | 260 | ps   |

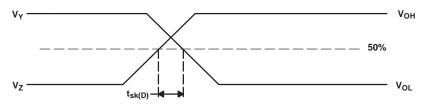

| t <sub>SK(P)</sub>    | Pulse skew (see <sup>(2)</sup> )                                     |                                                                                                                                                                                                                                                                                                                                                                                                   |     | 8                  | 15  | ps   |

| t <sub>SK(D)</sub>    | Intra-pair skew                                                      | AVCC = 3.3 V, $R_T$ = 50 $\Omega$ . See Figure 11.                                                                                                                                                                                                                                                                                                                                                |     | 10                 | 30  | ps   |

| t <sub>SK(O)</sub>    | Inter-pair skew (see <sup>(3)</sup> )                                |                                                                                                                                                                                                                                                                                                                                                                                                   |     |                    | 100 | ps   |

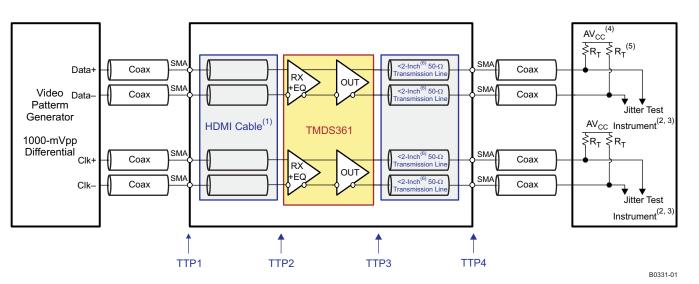

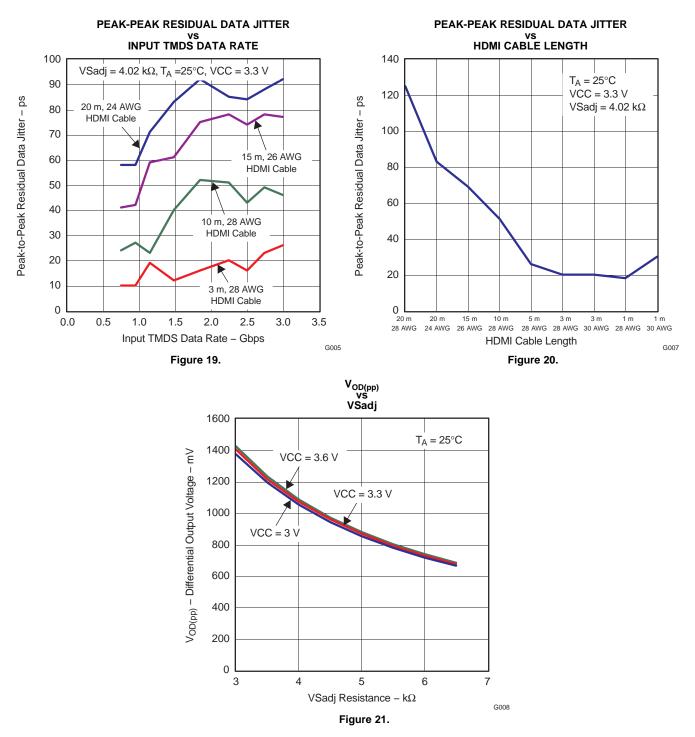

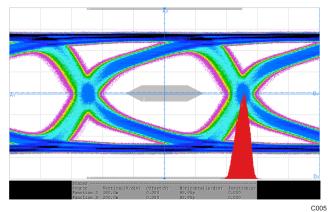

| t <sub>JITD(PP)</sub> | Peak-to-peak output residual data jitter                             | AVCC = 3.3 V, $R_T = 50 \Omega$ , $dR = 2.25$ Gbps.<br>See Figure 14 for measurement setup;<br>residual jitter is the total jitter measured at<br>TTP4 minus the jitter measured at TTP1. See<br>Figure 15 for the loss profile of the cable used<br>for t <sub>JITD(PP)</sub> measurement. Also see Typical<br>Curves for t <sub>JITD(PP)</sub> across cable length and<br>input TMDS data rate. |     | 40                 | 88  | ps   |

- All typical values are at 25°C and with a 3.3-V supply.

t<sub>sk(p)</sub> is the magnitude of the time difference between t<sub>PLH</sub> and t<sub>PHL</sub> of a specified terminal.

t<sub>sk(o)</sub> is the magnitude of the difference in propagation delay times between any specified terminals of a sink-port bank when inputs of the active source port are tied together.

SLLS919A-DECEMBER 2008-REVISED JANUARY 2009

www.ti.com

## SWITCHING CHARACTERISTICS (continued)

over recommended operating conditions (unless otherwise noted)

|                   | PARAMETER                                   | TEST CONDITIONS                                                                                                                                                                                                                                                                                            | MIN | TYP <sup>(1)</sup> | MAX | UNIT |

|-------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|-----|------|

| tjitc(PP)         | Peak-to-peak output residual clock jitter   | AVCC = 3.3 V, $R_T = 50 \Omega$ , input TMDS clock<br>frequency = 225 MHz. See Figure 14for<br>measurement setup; residual jitter is the total<br>jitter measured at TTP4 minus the jitter<br>measured at TTP1. See Figure 15 for the loss<br>profile of the cable used for $t_{JITC(PP)}$<br>measurement. |     | 10                 | 35  | ps   |

| t <sub>CLK1</sub> | Valid clock-detect enable time              | AVCC = 3.3 V, $R_T$ = 50 $\Omega$ , input TMDS clock frequency = 300 MHz. See Figure 13.                                                                                                                                                                                                                   |     | 300                | 500 | ns   |

| t <sub>CLK2</sub> | Invalid clock-detect disable time           | AVCC = 3.3 V, $R_T$ = 50 $\Omega$ , input TMDS clock frequency = 1 MHz. See Figure 13.                                                                                                                                                                                                                     |     | 500                | 800 | ns   |

| t <sub>SEL1</sub> | Port selection time (see <sup>(4)</sup>     | AVCC = 3.3 V, $R_T$ = 50 $\Omega$                                                                                                                                                                                                                                                                          |     | 300                | 500 | ns   |

| t <sub>SEL2</sub> | Port deselection time (see <sup>(5)</sup> ) | AVCC = 3.3 V, $R_T$ = 50 $\Omega$                                                                                                                                                                                                                                                                          |     | 40                 | 50  | ns   |

| f <sub>CD</sub>   | Clock-detect frequency                      | AVCC = 3.3 V, $R_T$ = 50 $\Omega$ . See Figure 13.                                                                                                                                                                                                                                                         | 25  |                    | 300 | MHz  |

(4)  $t_{SEL1}$  includes the time for the valid clock detect enable time and  $t_{S1(HPD)}$ , because the  $t_{S1(HPD)}$  event happens in parallel with  $t_{SEL1}$ ; thus, the  $t_{SEL1}$  time is primarily the  $t_{CLK1}$  time.

(5)  $t_{SEL2}$  is primarily the  $t_{S2(HPD)}$  time.

Figure 9. TMDS Main-Link Test Circuit

- 3.3 V V ID 2.8 V  $V_{ID^+}$ 0 V ID(pp)  $V_{ID-}$ t<sub>PLH</sub> t<sub>PHL</sub> 80% 80% v V<sub>OD(pp)</sub> OD 20% 20% t<sub>f</sub> T0391-01

Figure 10. TMDS Main-Link Timing Measurements

Figure 11. Definition of Intra-Pair Differential Skew

Figure 12. TMDS Main-Link Common-Mode Measurements

SLLS919A-DECEMBER 2008-REVISED JANUARY 2009

- (1) The HDMI cable between TTP1 and TTP2 is 20 m. See Figure 15 for the loss profile of the cable.

- (2) All jitter is measured at a BER of 10<sup>-12</sup>.

- (3) Residual jitter is the total jitter measured at TTP4 minus the jitter measured at TTP1.

- (4) AVCC = 3.3 V.

- (5)  $R_T = 50 \Omega$ .

- (6) 2 inches = 5.08 cm.

Figure 14. TMDS Jitter Measurements

Figure 15. Loss Profile of 20-m HDMI Cable

Texas INSTRUMENTS

www.ti.com

### **TYPICAL CHARACTERISTICS**

AVCC = 3.3 V,  $R_T$  = 50  $\Omega$

## **TYPICAL CHARACTERISTICS (continued)**

AVCC = 3.3 V,  $R_T$  = 50  $\Omega$

**TYPICAL CHARACTERISTICS (continued)**

AVCC = 3.3 V,  $R_T$  = 50  $\Omega$

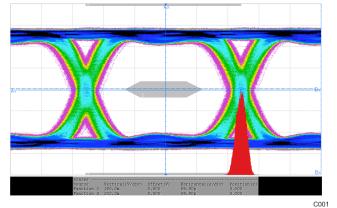

Figure 23. Eye at TP3 (output of TMDS361) with 20 m, 24 AWG HDMI cable, 2.25 Gbps Input TMDS data Rate, Fastest Rise and Fall Time Setting on TMDS outputs

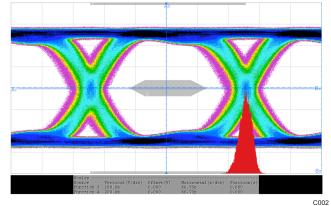

Figure 24. Eye at TP3 (output of TMDS361) with 20 m, 24 AWG HDMI cable, 3 Gbps Input TMDS data Rate, Fastest Rise and Fall Time Setting on TMDS outputs

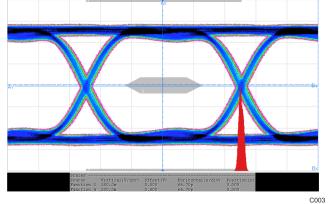

Figure 25. Eye at TP3 (output of TMDS361) with 3 m, 28 AWG HDMI cable, 3 Gbps Input TMDS data Rate, Fastest Rise and Fall Time Setting on TMDS outputs

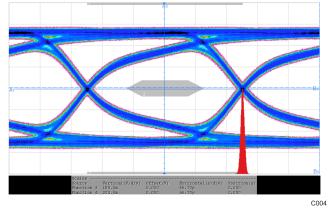

Figure 26. Eye at TP3 (output of TMDS361) with 3 m, 28 AWG HDMI cable, 3 Gbps Input TMDS data Rate, Slowest Rise and Fall Time Setting on TMDS outputs

## **TYPICAL CHARACTERISTICS (continued)**

AVCC = 3.3 V,  $R_T$  = 50  $\Omega$

Figure 27. Eye at TP3 (output of TMDS361) with 20 m, 24 AWG HDMI cable, 2.25 Gbps Input TMDS data Rate, Slowest Rise and Fall Time Setting on TMDS outputs

## **APPLICATION INFORMATION**

### Table 3. TMDS361 vs TMDS351 Pinout

| PIN NUMBER     | I/O | TMDS351                                                 | TMDS361                                                                                       |

|----------------|-----|---------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| Pins 32 and 33 | Ι   | GPIO mode: S1 and S2 configured as source selector pins | GPIO mode: S1 and S2 configured as source selector pins (same as TMDS351)                     |

|                |     |                                                         | $\rm I^2C$ mode: S1 and S2 configured as SCL and SDA for local slave $\rm I^2C$ communication |

| Pin 34         | I   | EQ: TMDS input equalization control select              | I2C_SEL: GPIO / local I <sup>2</sup> C control select                                         |

|                |     | EQ = Low – HDMI 1.3 compliant cable                     | I2C_SEL = High – Device is configured by GPIO logic.                                          |

|                |     | EQ = High – 10-m 28 AWG HDMI cable                      | I2C_SEL= Low – Device is configured by I <sup>2</sup> C logic.                                |

| Pin 49         | _   | VDD: HPD/DDC power supply                               | LP: Low-power mode select bar                                                                 |

|                |     |                                                         | LP = High – Normal operational mode                                                           |

|                |     |                                                         | $\overline{\text{LP}}$ = Low – Device goes into low-power state.                              |

Based on the differences listed in Table 3, attention must be given to pin 34, which determines whether the device uses  $I^2C$  or GPIO control.

### Supply Voltage

The TMDS361 is powered up with a single power source that is 3.3-V VCC for the TMDS circuitry for HPD, DDC, and most of the control logic.

### TMDS Input Fail-Safe

The TMDS361 incorporates clock-detect circuitry. If there is no valid TMDS clock from the connected HDMI/DVI source, the TMDS361 does not switch on the terminations on the source-side data channels. Additionally, the TMDS outputs are placed in the high-impedance state. This prevents the TMDS361 from turning on its outputs if there is no valid incoming HDMI/DVI data.

### TMDS Outputs

A 10% precision resistor, 4.02-k $\Omega$ , is recommended to control the output swing to the HDMI-compliant 800-mV to 1200-mV range V<sub>OD(pp)</sub> (1000 mV typical). The TMDS outputs are high-impedance under standby mode operation, S1 = H and S2 = L.

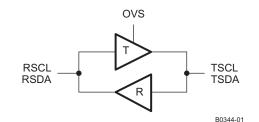

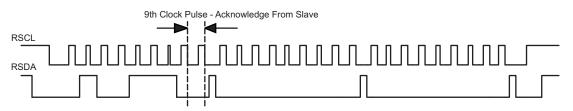

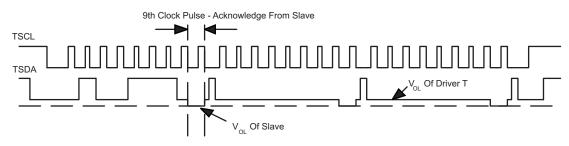

### DDC I<sup>2</sup>C Function Description

The TMDS361 provides buffers on the DDC I<sup>2</sup>C lines on all three input ports. This section explains the operation of the buffer. For representation, the source side of the TMDS361 is represented by RSCL/RSDA, and the sink side is represented by TSCL/TSDA. The buffers on the RSCL/RSDA and TSCL/TSDA pins are 5-V tolerant when the device is powered off and high-impedance under low supply voltage, 1.5 V or below. If the device is powered up, the driver T (see Figure 28) is turned on or off depending on the corresponding R-side voltage level.

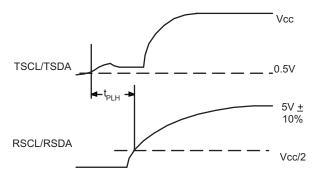

When the R side is pulled low below 1.5 V, the corresponding T-side driver turns on and pulls the T side down to a low level output voltage,  $V_{OL}$ . The value of  $V_{OL}$  and  $V_{IL}$  on the T side or the sink side of the TMDS361 switch depends on the output-voltage select (OVS) control settings. OVS control can be changed by the slave I<sup>2</sup>C, see Table 8. When the OVS1 setting is selected,  $V_{OL}$  is typically 0.7 V and  $V_{IL}$  is typically 0.4 V. When the OVS2 setting is selected,  $V_{OL}$  is typically 0.4 V. When OVS3 setting (default) is selected,  $V_{OL}$  is typically 0.5 V and  $V_{IL}$  is typically 0.3 V.  $V_{OL}$  is always higher than the driver-R input threshold,  $V_{IL}$  on the T side or the sink side, preventing lockup of the repeater loop. The TMDS361 is targeted primarily as a switch in the HDTV market and is expected to be a companion chip to an HDMI receiver; thus, the OVS control has been provided on the sink side, so that the requirement of  $V_{IL}$  to be less than 0.4 V can be met. The  $V_{OL}$  value can be selected to improve or optimize noise margins between  $V_{OL}$  and  $V_{IL}$  of the repeater itself or  $V_{IL}$  of some external device connected on the T side.

When the R side is pulled up, above 1.5 V, the T-side driver turns off and the T-side pin is high-impedance.

Copyright © 2008–2009, Texas Instruments Incorporated

### Figure 28. I<sup>2</sup>C Drivers in the TMDS361 (R Side Is the HDMI Source Side, T Side Is the HDMI Sink Side)

When the T side is pulled below 0.4 V by an external  $I^2C$  driver, both drivers R and T are turned on. Driver R pulls the R side to near 0 V, and driver T is on, but is overridden by the external  $I^2C$  driver. If driver T is already on, due to a low on the R side, driver R just turns on.

When the T side is released by the external I<sup>2</sup>C driver, driver T is still on, so the T side is only able to rise to the  $V_{OL}$  of driver T. Driver R turns off, because  $V_{OL}$  is above its 0.4-V  $V_{IL}$  threshold, releasing the R side. If no external I<sup>2</sup>C driver is keeping the R side low, the R side rises, and driver T turns off once the R side rises above 1.5 V, see Figure 29.

Figure 29. Waveform of Driver T Turning Off

It is important that any external  $I^2C$  driver on the T side is able to pull the bus below 0.4 V to achieve full operation. If the T side cannot be pulled below 0.4 V, driver R may not recognize and transmit the low value to the R side.

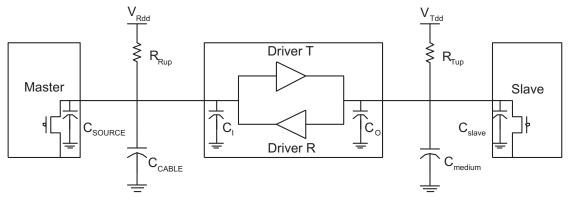

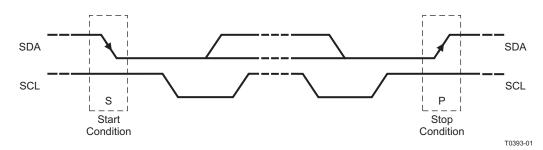

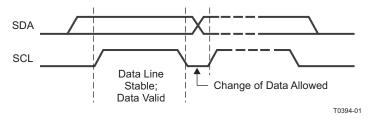

### DDC I<sup>2</sup>C Behavior

The typical application of the TMDS361 is as a  $3\times1$  switch in a TV connecting up to three HDMI input sources to an HDMI receiver. The I<sup>2</sup>C repeater is 5-V tolerant, and no additional circuitry is required to translate between 3.3-V and 5-V bus voltages. In the following example, the system master is running on an R-side I<sup>2</sup>C-bus while the slave is connected to a T-side bus. Both buses run at 100 kHz, supporting standard-mode I<sup>2</sup>C operation. Master devices can be placed on either bus.

### **Figure 30. Typical Application**

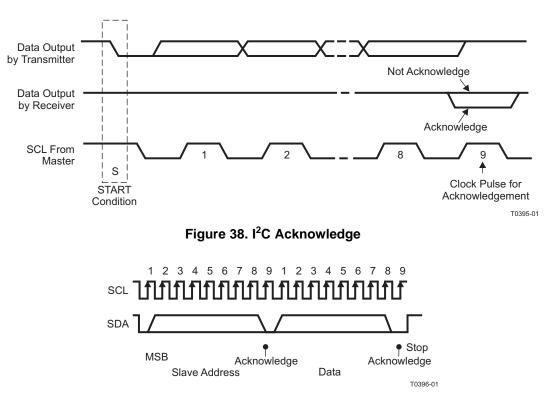

Figure 31 illustrates the waveforms seen on the R-side I<sup>2</sup>C-bus when the master writes to the slave through the I<sup>2</sup>C repeater circuit of the TMDS361. This looks like a normal I<sup>2</sup>C transmission, and the turnon and turnoff of the acknowledge signals are slightly delayed.

Figure 31. Bus-R Waveform

Figure 32 illustrates the waveforms seen on the T-side I<sup>2</sup>C-bus under the same operation as in Figure 31. On the T-side of the I<sup>2</sup>C repeater, the clock and data lines would have a positive offset from ground equal to the  $V_{OL}$  of the driver T. After the 8th clock pulse, the data line is pulled to the  $V_{OL}$  of the slave device, which is very close to ground in this example. At the end of the acknowledge, the slave device releases and the bus level rises back to the  $V_{OL}$  set by the driver until the R-side rises above VCC/2, after which it continues to be high. It is important to note that any arbitration or clock-stretching events require that the low level on the T-side bus at the input of the TMDS361 I<sup>2</sup>C repeater is below 0.4 V to be recognized by the device and then transmitted to the R-side I<sup>2</sup>C bus.

Figure 32. Bus T Waveform

### I<sup>2</sup>C Pullup Resistors

The pullup resistor value is determined by two requirements:

1. The maximum sink current of the I<sup>2</sup>C buffer:

The maximum sink current is 3 mA or slightly higher for an  $I^2C$  driver supporting standard-mode  $I^2C$  operation.

$R_{up(min)} = V_{DD}/Isink$

2. The maximum transition time on the bus:

The maximum transition time, T, of an  $I^2C$  bus is set by an RC time constant, where R is the pullup resistor value and C is the total load capacitance. The parameter, k, can be calculated from Equation 3 by solving for t, the times at which certain voltage thresholds are reached. Different input threshold combinations introduce different values of t. Table 4 summarizes the possible values of k under different threshold combinations.

$$T = k \times RC$$

$$V(t) = V_{DD}(1 - e^{-t/RC})$$

<sup>(2)</sup>

(3)

(1)

# INSTRUMENTS

www.ti.com

|                                    |                     |                      |                     |                      |                     |                      | - J - J             |                      |                     |

|------------------------------------|---------------------|----------------------|---------------------|----------------------|---------------------|----------------------|---------------------|----------------------|---------------------|

| V <sub>th-</sub> \V <sub>th+</sub> | 0.7 V <sub>DD</sub> | 0.65 V <sub>DD</sub> | 0.6 V <sub>DD</sub> | 0.55 V <sub>DD</sub> | 0.5 V <sub>DD</sub> | 0.45 V <sub>DD</sub> | 0.4 V <sub>DD</sub> | 0.35 V <sub>DD</sub> | 0.3 V <sub>DD</sub> |

| 0.1 V <sub>DD</sub>                | 1.0986              | 0.9445               | 0.8109              | 0.6931               | 0.5878              | 0.4925               | 0.4055              | 0.3254               | 0.2513              |

| 0.15 V <sub>DD</sub>               | 1.0415              | 0.8873               | 0.7538              | 0.6360               | 0.5306              | 0.4353               | 0.3483              | 0.2683               | 0.1942              |

| 0.2 V <sub>DD</sub>                | 0.9808              | 0.8267               | 0.6931              | 0.5754               | 0.4700              | 0.3747               | 0.2877              | 0.2076               | 0.1335              |

| 0.25 V <sub>DD</sub>               | 0.9163              | 0.7621               | 0.6286              | 0.5108               | 0.4055              | 0.3102               | 0.2231              | 0.1431               | 0.0690              |

| 0.3 V <sub>DD</sub>                | 0.8473              | 0.6931               | 0.5596              | 0.4418               | 0.3365              | 0.2412               | 0.1542              | 0.0741               |                     |

### Table 4. Value of k for Different Input Threshold Voltages

From Equation 1,  $R_{up(min)} = 5.5 \text{ V/3 mA} = 1.83 \text{ k}\Omega$  to operate the bus under a 5-V pullup voltage and provide less than 3 mA when the  $l^2C$  device is driving the bus to a low state. If a higher sink current, for example 4 mA, is allowed,  $R_{up(min)}$  can be as low as 1.375 k $\Omega$ .

Given a 5-V I<sup>2</sup>C device with input low and high threshold voltages at 0.3 V<sub>dd</sub> and 0.7 V<sub>dd</sub>, respectively, the value of k is 0.8473 from Table 4. Taking into account the 1.83-k $\Omega$  pullup resistor, the maximum total load capacitance is C<sub>(total-5V)</sub> = 645 pF. C<sub>cable(max)</sub> should be restricted to be less than 545 pF if C<sub>source</sub> and C<sub>i</sub> can be as high as 50 pF. Here the C<sub>i</sub> is treated as C<sub>sink</sub>, the load capacitance of a sink device.

Fixing the maximum transition time from Table 4, T = 1  $\mu$ s, and using the k values from Table 4, the recommended maximum total resistance of the pullup resistors on an I<sup>2</sup>C bus can be calculated for different system setups.

To support the maximum load capacitance specified in the HDMI spec,  $C_{cable(max)} = 700 \text{ pF/}C_{source} = 50 \text{ pF/}C_i = 50 \text{ pF}, R_{(max)}$  can be calculated as shown in Table 5.

| V <sub>th-</sub> \V <sub>th+</sub> | 0.7 V <sub>DD</sub> | 0.65 V <sub>DD</sub> | 0.6 V <sub>DD</sub> | 0.55 V <sub>DD</sub> | 0.5 V <sub>DD</sub> | 0.45 V <sub>DD</sub> | 0.4 V <sub>DD</sub> | 0.35 V <sub>DD</sub> | 0.3 V <sub>DD</sub> | UNIT |

|------------------------------------|---------------------|----------------------|---------------------|----------------------|---------------------|----------------------|---------------------|----------------------|---------------------|------|

| 0.1 V <sub>DD</sub>                | 1.14                | 1.32                 | 1.54                | 1.80                 | 2.13                | 2.54                 | 3.08                | 3.84                 | 4.97                | kΩ   |

| 0.15 V <sub>DD</sub>               | 1.20                | 1.41                 | 1.66                | 1.97                 | 2.36                | 2.87                 | 3.59                | 4.66                 | 6.44                | kΩ   |

| 0.2 V <sub>DD</sub>                | 1.27                | 1.51                 | 1.80                | 2.17                 | 2.66                | 3.34                 | 4.35                | 6.02                 | 9.36                | kΩ   |

| 0.25 V <sub>DD</sub>               | 1.36                | 1.64                 | 1.99                | 2.45                 | 3.08                | 4.03                 | 5.60                | 8.74                 | 18.12               | kΩ   |

| 0.3 V <sub>DD</sub>                | 1.48                | 1.80                 | 2.23                | 2.83                 | 3.72                | 5.18                 | 8.11                | 16.87                |                     | kΩ   |

### Table 5. Pullup Resistor for Different Threshold Voltages and 800-pF Load

Or, limiting the maximum load capacitance of each cable to 400 pF to accommodate with I<sup>2</sup>C spec version 2.1.  $C_{cable(max)} = 400 \text{ pF/C}_{source} = 50 \text{ pF/C}_i = 50 \text{ pF}$ , the maximum values of  $R_{(max)}$  are calculated as shown in Table 6.

| V <sub>th-</sub> \V <sub>th+</sub> | $0.7 V_{DD}$ | 0.65 V <sub>DD</sub> | 0.6 V <sub>DD</sub> | 0.55 V <sub>DD</sub> | $0.5 V_{DD}$ | 0.45 V <sub>DD</sub> | 0.4 V <sub>DD</sub> | 0.35 V <sub>DD</sub> | 0.3 V <sub>DD</sub> | UNIT |

|------------------------------------|--------------|----------------------|---------------------|----------------------|--------------|----------------------|---------------------|----------------------|---------------------|------|

| 0.1 V <sub>DD</sub>                | 1.82         | 2.12                 | 2.47                | 2.89                 | 3.40         | 4.06                 | 4.93                | 6.15                 | 7.96                | kΩ   |

| 0.15 V <sub>DD</sub>               | 1.92         | 2.25                 | 2.65                | 3.14                 | 3.77         | 4.59                 | 5.74                | 7.46                 | 10.30               | kΩ   |

| 0.2 V <sub>DD</sub>                | 2.04         | 2.42                 | 2.89                | 3.48                 | 4.26         | 5.34                 | 6.95                | 9.63                 | 14.98               | kΩ   |

| $0.25 V_{DD}$                      | 2.18         | 2.62                 | 3.18                | 3.92                 | 4.93         | 6.45                 | 8.96                | 13.98                | 28.99               | kΩ   |

| 0.3 V <sub>DD</sub>                | 2.36         | 2.89                 | 3.57                | 4.53                 | 5.94         | 8.29                 | 12.97               | 26.99                | _                   | kΩ   |

Table 6. Pullup Resistor Upon Different Threshold Voltages and 500-pF Loads

Obviously, to accommodate the 3-mA drive current specification, a narrower threshold voltage range is required to support a maximum 800-pF load capacitance for a standard-mode I<sup>2</sup>C bus.

When the input low- and high-level threshold voltages,  $V_{th-}$  and  $V_{th+}$ , are 0.7 V and 1.9 V, respectively, which is 0.15  $V_{DD}$  and 0.4  $V_{DD}$ , approximately. With  $V_{DD} = 5$  V from Table 5, the maximum pullup resistor is 3.59 k $\Omega$ . The allowable pullup resistor is in the range of 1.83 k $\Omega$  and 3.59 k $\Omega$ .

### **HPD Pins**

The HPD circuits are powered by the 3.3-V VCC supply. This provides maximum  $V_{OH} = VCC$  and maximum  $V_{OL} = 0.4$ -V output signals to the SOURCE with a typical 1-k $\Omega$  output resistance. An external 1-k $\Omega$  resistor is not needed here. The HPD output of the selected source port follows the logic level of the HPD\_SINK input. Unselected HPD outputs are kept low. When the device is in standby mode, all HPD outputs follow HPD\_SINK.

If  $V_{OH}$  greater than VCC is desired, then an external circuit as shown in Figure 33 can be used. In this case, the max  $V_{OH}$  can be equal to the 5 V coming from the HDMI source.

Figure 33. External Circuit to Drive 5-V V<sub>OH</sub> on HPD[1:3]

### Layout Considerations

The high-speed differential TMDS inputs are the most critical paths for the TMDS361. There are several considerations to minimize discontinuities on these transmission lines between the connectors and the device:

- Maintain  $100-\Omega$  differential transmission line impedance into and out of the TMDS361.

- Keep an uninterrupted ground plane beneath the high-speed I/Os.

- Keep the ground-path vias to the device as close as possible to allow the shortest return current path.

- Keep the trace lengths of the TMDS signals between connector and device as short as possible.

### Using the TMDS361 in Systems with Different CEC Link Requirements

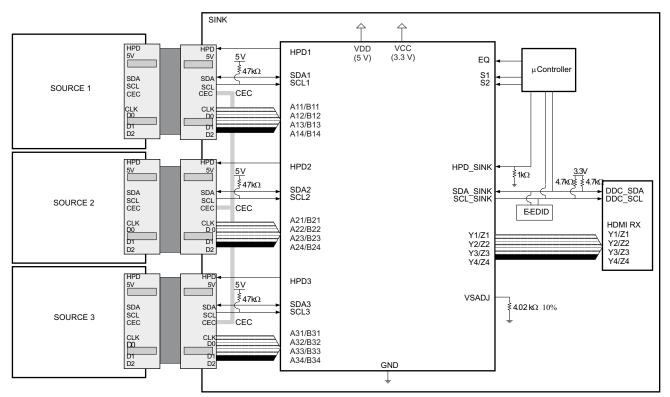

The TMDS361 supports a DTV with up to three HDMI inputs when used in conjunction with a signal-port HDMI receiver. Figure 34 and Figure 35 show simplified application block diagrams for the TMDS361 in different DTVs with different consumer electronic control (CEC) requirements. The CEC is an optional feature of the HDMI interface for centralizing and simplifying user control instructions from multiple audio/video products in an interconnected system, even when all the audio/video products are from different manufacturers. This feature minimizes the number of remote controls in a system, as well as reducing the number of times buttons must be pressed.

SLLS919A-DECEMBER 2008-REVISED JANUARY 2009

### A DTV Supporting a Passive CEC Link

In Figure 34, the DTV does not have the capability of handling CEC signals, but allows CEC signals to pass over the CEC bus. The source selection is done by the control command of the DTV. The user cannot force the command from any audio/video product on the CEC bus. The selected source reads the E-EDID data after receiving an asserted HPD signal. The microcontroller loads different CEC physical addresses while changing the source by means of the S1 and S2 pins.

### E-EDID Reading Configurations in Standby Mode

When the DTV system is in standby mode, the sources do not read the E-EDID memory because the  $1-k\Omega$  pulldown resistor keeping the HPD\_SINK input at logic low forces all HPD pins to output logic-low to all sources. The source does not read the E-EDID data with a low on HPD signal. However, if reading the E-EDID data in the system standby mode is preferred, then TMDS361 can still support this need.

The recommended configuration sequences are:

- 1. Apply the same 3.3-V power to the VCC of TMDS361 and the TMDS line termination at the HDMI receiver

- 2. Because the TMDS361 has clock-detect circuitry and there is no valid input TMDS clock in the standby mode, TMDS361 draws significantly less current.

- 3. Set S1 and S2 to select the source port which is allowed to read the E-EDID memory.

Note that if the source has a time-out limitation between the 5-V and the HPD signals, the foregoing configuration is not applicable. Uses individual EEPROMs assigned for each input port, see Figure 35. The solution uses E-EDID data to be readable during system power-off or standby-mode operations.

Figure 34. Three-Port HDMI-Enabled DTV With TMDS361 – CEC Commands Passing Through

### A DTV Supporting an Active CEC Link

In Figure 35, the CEC PHY and CEC LOGIC functions are added. The DTV can initiate and/or react to CEC signals from its remote control or other audio/video products on the same CEC bus. All sources must have their own CEC physical address to support the full functionality of the CEC link.

A source reads its CEC physical address stored its E-EDID memory after receiving a logic-high from the HPD feedback. When HPD is high, the sink-assigned CEC physical address should be maintained. Otherwise, when HPD is low, the source sets CEC physical address value to (F.F.F.F).

### Case 1 – AC-Coupled Source (See Figure 35, Port 1)

When the source TMDS lines are ac-coupled or when the source cannot detect the TMDS termination provided in the connected sink, the indication of the source selection can only come from the HPD signal. The TMDS361 HPD1 pin should be applied directly as the HPD signal back to the source.

### Case 2 – DC-Coupled Source (See Figure 35, Port 2)

When the source TMDS lines are dc-coupled, there are two methods to inform the source that it is the active source to the sink. One is checking the HPD signal from the sink, and the other is checking the termination condition in the sink.