Order

Now

## **TPS53681**

SLUSCT1B-JUNE 2017-REVISED JANUARY 2019

Support &

Community

20

# TPS53681 Dual-Channel (6-Phase + 2-Phase) or (5-Phase + 3-Phase) D-CAP+<sup>™</sup> Step-Down Multiphase Controller with NVM and PMBus<sup>™</sup>

Technical

Documents

#### 1 Features

- Conversion Input Voltage Range: 4.5 V to 17 V

- 8-Bit DAC with Selectable 5 mV or 10 mV Resolution and Output Ranges from 0.25 V to 1.52 V or 0.5 to 2.8125 V for Dual Channels

- Phase Configurations

- Maximum (6-Phase + 2-Phase) or (5-Phase + 3-Phase)

- Minimum (1-Phase + 1-Phase)

- Driverless Configuration for Efficient High-Frequency Switching

- Dynamic Output Voltage Transitions with Programmable Slew Rates via PMBus Interface

- Frequency Selections with Closed-loop Frequency Control: 300 kHz to 1 MHz

- Programmable Internal Loop Compensations

- Configurable with Non-Volatile Memory (NVM) for Low External Component Counts

- Individual Phase Current Calibrations and Reports

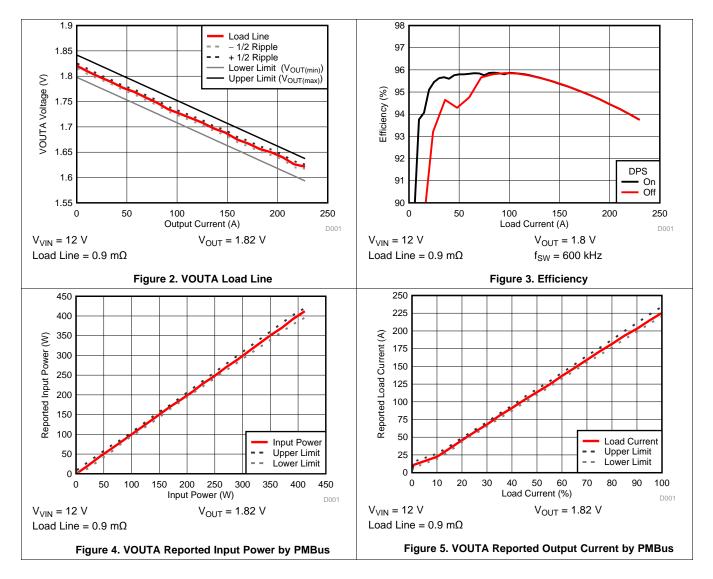

- **Dynamic Phase Shedding with Programmable** Current Threshold for Optimizing Efficiency at Light and Heavy Loads

- Fast Phase-Adding for Undershoot Reduction (USR)

- Fully Compatible with TI NexFET<sup>™</sup> Power Stage for High-Density Solutions

- Accurate, Adjustable Voltage Positioning

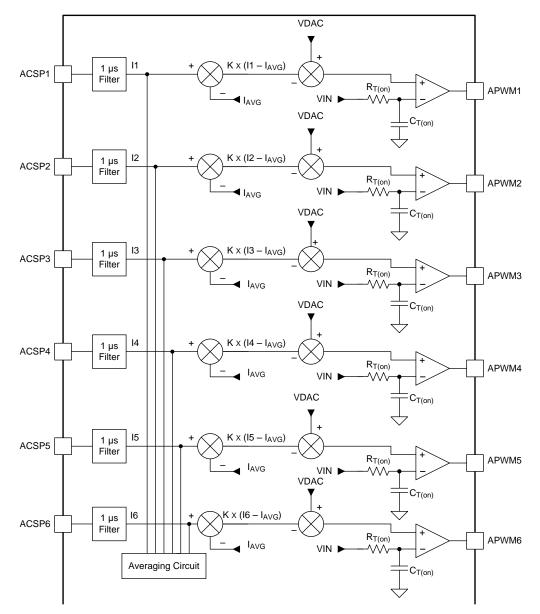

- Patented AutoBalance<sup>™</sup> Phase Balancing

- Selectable, 16-level Per-Phase Current Limit

- PMBus<sup>™</sup> System Interface for Telemetry of Voltage, Current, Power, Temperature, and Fault Conditions

- Low Quiescent Current

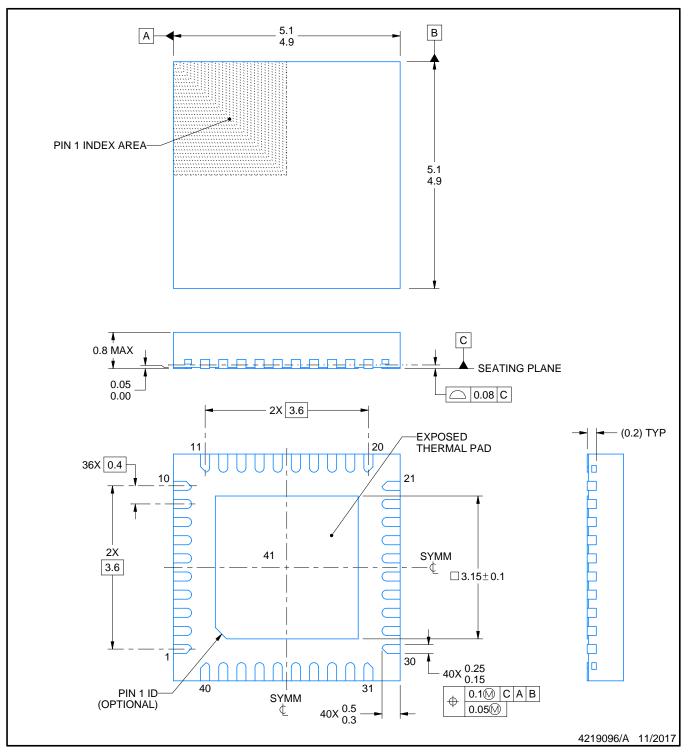

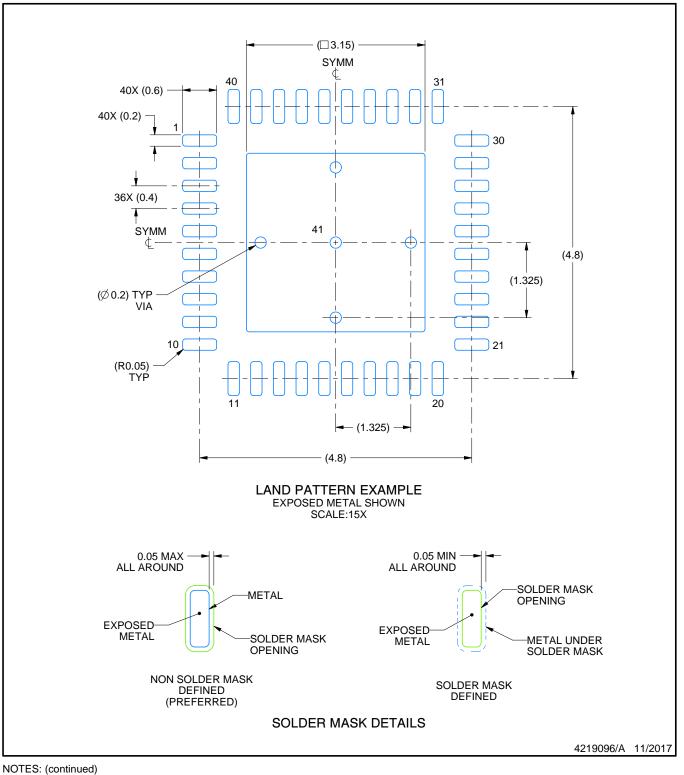

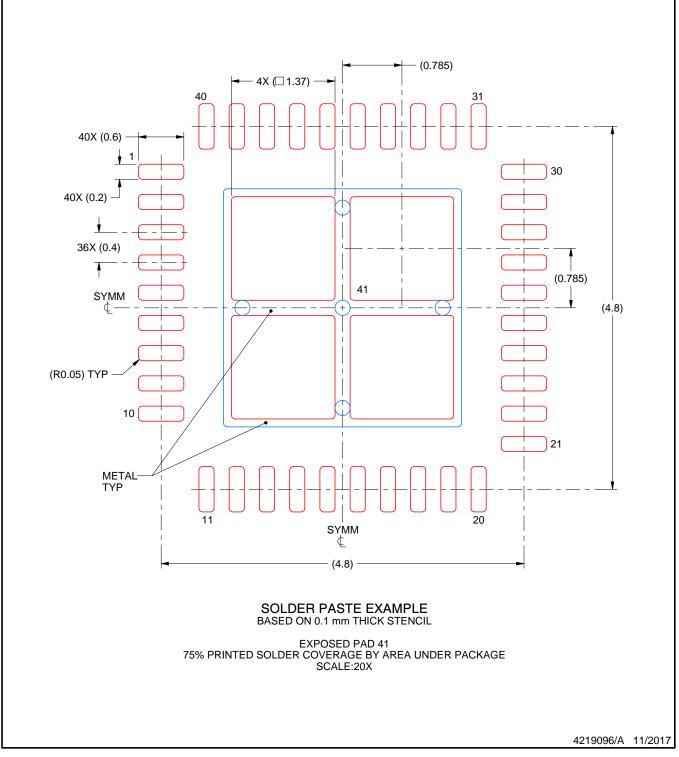

- 5 mm × 5 mm, 40-Pin, QFN PowerPad™ Package

#### Applications 2

- Networking Processor Power (Broadcom<sup>®</sup>, Cavium<sup>®</sup>)

- Datacenter, Campus, and Branch Switches

- Core and Edge Routers

- High-Current FPGA Power (Intel<sup>®</sup>, Xilinx<sup>®</sup>)

## 3 Description

Tools &

Software

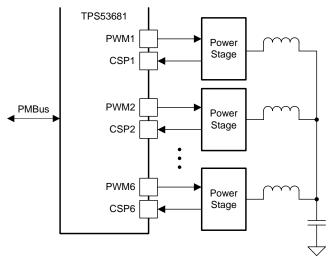

The TPS53681 is a multiphase step-down controller with dual channels, built-in non-volatile memory (NVM), and PMBus<sup>™</sup> interface, and is fully compatible with TI NexFET <sup>™</sup>power stage. Advanced control features such as D-CAP+™ architecture with undershoot reduction (USR) provide fast transient low output capacitance, response. and high efficiency. The device also provides novel phase interleaving strategy and dynamic phase shedding for efficiency improvement at different loads. The device supports fast dynamic voltage transitions with adjustable slew rate. In addition, the device supports the PMBus communication interface for reporting the telemetry of voltage, current, power, temperature, and fault conditions to the systems. All programmable parameters can be configured by the PMBus interface and can be stored in NVM as the new default values to minimize the external component count.

The TPS53681 device is offered in a thermally enhanced 40-pin QFN packaged and is rated to operate from -40°C to 125°C.

Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE  | BODY SIZE (NOM) |

|-------------|----------|-----------------|

| TPS53681    | QFN (40) | 5 mm × 5 mm     |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

## Figure 1. Simplified Application

Copyright © 2017, Texas Instruments Incorporated

## **Table of Contents**

| 1 | Feat | ures 1                                          |

|---|------|-------------------------------------------------|

| 2 | Арр  | lications 1                                     |

| 3 | Des  | cription 1                                      |

| 4 |      | ision History2                                  |

| 5 |      | Configuration and Functions                     |

| 6 |      | cifications6                                    |

|   | 6.1  | Absolute Maximum Ratings6                       |

|   | 6.2  | ESD Ratings 6                                   |

|   | 6.3  | Recommended Operating Conditions                |

|   | 6.4  | Thermal Information                             |

|   | 6.5  | Supply: Currents, UVLO, and Power-On Reset 7    |

|   | 6.6  | References: DAC and VREF 8                      |

|   | 6.7  | Voltage Sense: AVSP and BVSP, AVSN and          |

|   |      | BVSN                                            |

|   | 6.8  | Telemetry                                       |

|   | 6.9  | Input Current Sensing 10                        |

|   | 6.10 | · · · g· · · · · · · · · · · · · · · ·          |

|   | 6.11 | Current Sense and Calibration15                 |

|   | 6.12 | Logic Interface Pins: AVR_EN, AVR_RDY,          |

|   |      | BVR_EN, BVR_RDY, RESET, VR_FAULT, VR_HOT        |

|   | 6.13 |                                                 |

|   | 6.14 | -                                               |

|   | 6.15 | Overcurrent Limit Thresholds                    |

|   | 6.16 |                                                 |

|   | 6.17 |                                                 |

|   | 6.18 | 0                                               |

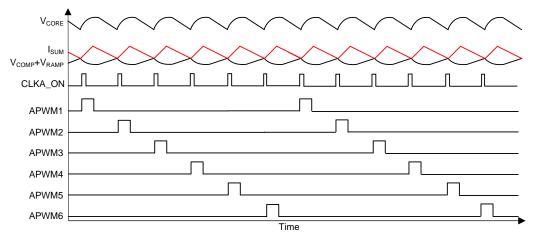

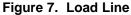

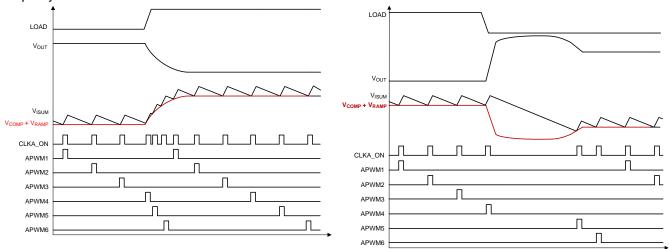

|   | 6.19 | Dynamic Integration and Undershoot Reduction 20 |

|   | 6.20 | , ,                                             |

|   | 0.20 |                                                 |

|    | 6.21 | Protections: OVP and UVP                 | 22       |

|----|------|------------------------------------------|----------|

|    | 6.22 | Protections: ATSEN and BTSEN Pin Voltage | e Levels |

|    |      | and Fault                                |          |

|    | 6.23 | PWM: I/O Voltage and Current             | 23       |

|    | 6.24 | Dynamic Phase Add and Drop               | 24       |

|    | 6.25 | Typical Characteristics                  | 34       |

| 7  | Deta | iled Description                         | 35       |

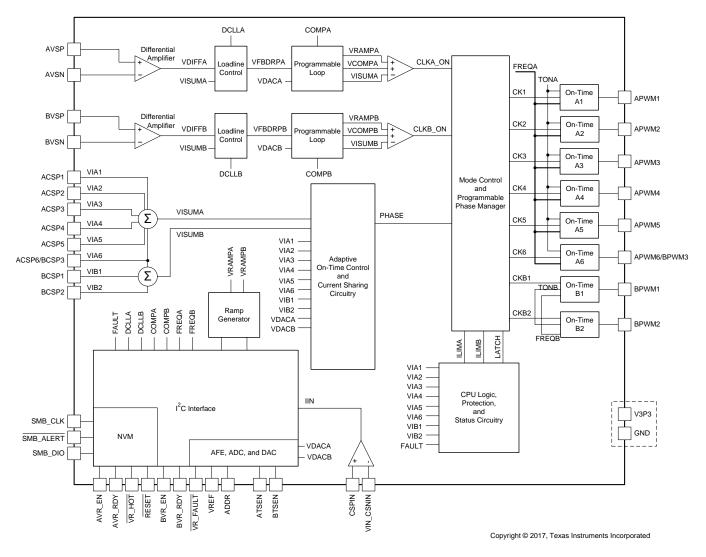

|    | 7.1  | Overview                                 | 35       |

|    | 7.2  | Functional Block Diagram                 | 35       |

|    | 7.3  | Feature Description                      | 35       |

|    | 7.4  | Device Functional Modes                  | 43       |

|    | 7.5  | Programming                              | 43       |

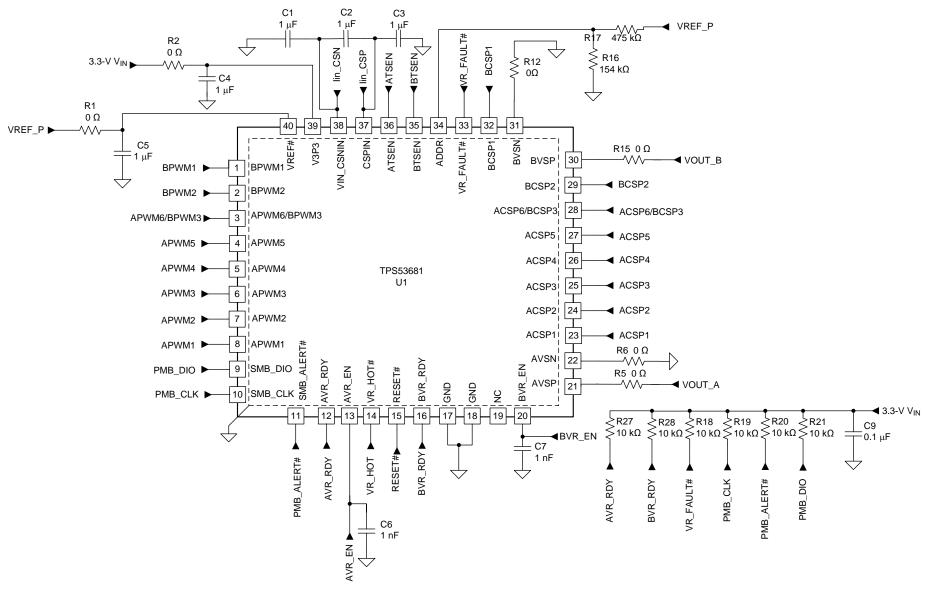

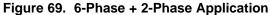

| 8  | App  | lications, Implementation, and Layout    | 105      |

|    | 8.1  | Application Information                  | 105      |

|    | 8.2  | Typical Application                      | 105      |

| 9  | Pow  | er Supply Recommendations                | 116      |

| 10 |      | out                                      |          |

| -  | 10.1 | Layout Guidelines                        |          |

|    | 10.2 | Layout Examples                          |          |

| 11 |      | ice and Documentation Support            |          |

| •• | 11.1 |                                          |          |

|    |      | Updates                                  | 120      |

|    | 11.2 | Community Resources                      | 120      |

|    | 11.3 | Trademarks                               | 120      |

|    | 11.4 | Electrostatic Discharge Caution          | 120      |

|    | 11.5 | Glossary                                 | 120      |

| 12 | Mec  | hanical, Packaging, and Orderable        |          |

|    |      | rmation                                  | 121      |

|    |      |                                          |          |

## **4** Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Ch | anges from Revision A (November 2018) to Revision B                              | Page |

|----|----------------------------------------------------------------------------------|------|

| •  | Updated the device NVM default values in Supported Commands                      | 45   |

| Ch | anges from Original (June 2017) to Revision A                                    | Page |

| •  | Updated Application listing                                                      | 1    |

| •  | Added (21h) VOUT_COMMAND register table in Output Voltage Margin Testing section | 67   |

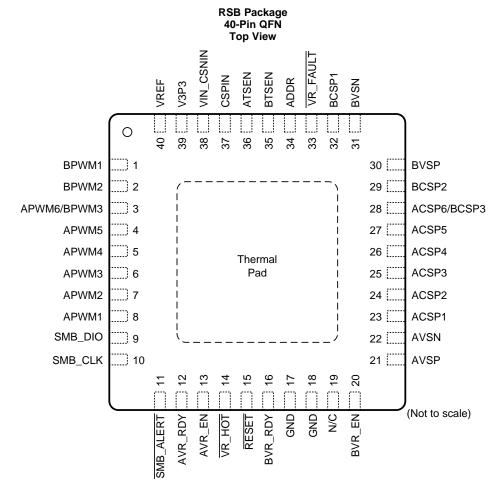

## 5 Pin Configuration and Functions

Thermal pad acts as AGND.

NC = not connected

#### **Pin Functions**

| PIN         |    | 1/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                             |  |  |  |

|-------------|----|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME NO.    |    | 1/0 ( /            | DESCRIPTION                                                                                                                                                                             |  |  |  |

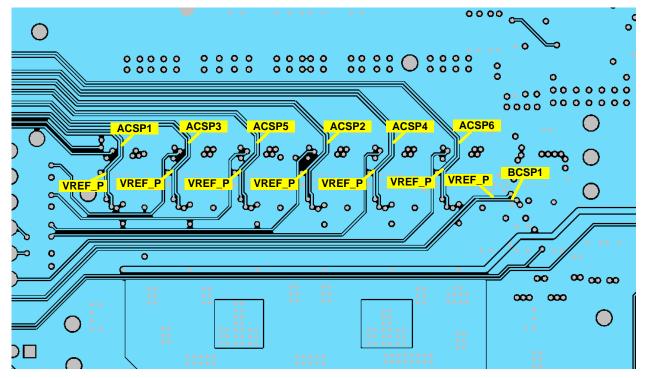

| ACSP1       | 23 |                    |                                                                                                                                                                                         |  |  |  |

| ACSP2       | 24 |                    | Current sense input for the channel A. Connect to the IOUT pin of TI smart power stages. Tie the                                                                                        |  |  |  |

| ACSP3       | 25 |                    | ACSP5, ACSP4, ACSP3, or ACSP2 pin to the V3P3 pin according to Table 1 to disable the                                                                                                   |  |  |  |

| ACSP4 26    |    | I                  | corresponding phase.                                                                                                                                                                    |  |  |  |

| ACSP5       | 27 |                    |                                                                                                                                                                                         |  |  |  |

| ACSP6/BCSP3 | 28 |                    | Current sense inputs for channel A or channel B based on NVM option. Connect to the IOUT pin of smart power stages. Tie ACSP6/BCSP3 to the 3.3-V supply to disable corresponding phase. |  |  |  |

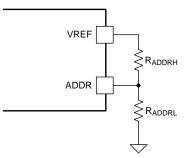

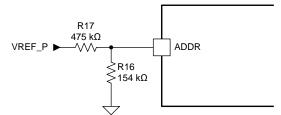

| ADDR 34 I   |    | I                  | Voltage divider to VREF and GND. The voltage level sets the 7-bit PMBus address with an ADC. Address is latched at 3.3-V power up.                                                      |  |  |  |

| APWM1       | 8  | 0                  | PWM signal for phase 1 of channel A.                                                                                                                                                    |  |  |  |

| APWM2       | 7  | 0                  | PWM signal for phase 2 of channel A.                                                                                                                                                    |  |  |  |

| APWM3 6 O   |    | 0                  | PWM signal for phase 3 of channel A.                                                                                                                                                    |  |  |  |

| APWM4       | 5  | 0                  | PWM signal for phase 4 of channel A.                                                                                                                                                    |  |  |  |

| APWM5       | 4  | 0                  | PWM signal for phase 5 of channel A.                                                                                                                                                    |  |  |  |

(1) G = ground, I = input, O = output, P = power input

Copyright © 2017–2019, Texas Instruments Incorporated

TPS53681 SLUSCT1B – JUNE 2017 – REVISED JANUARY 2019

www.ti.com

NSTRUMENTS

Texas

## Pin Functions (continued)

| PIN         |          | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|-------------|----------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME        | NO.      | 1000               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| APWM6/BPWM3 | 3        | 0                  | PWM signal for phase 6 of channel A, or phase 3 of channel B, based on the NVM option.                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

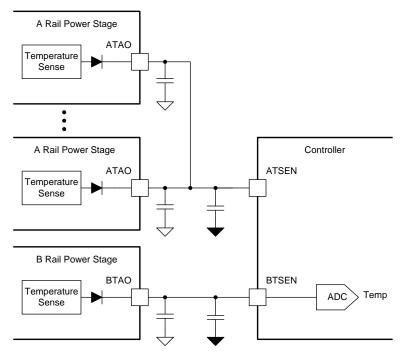

| ATSEN       | 36       | 0                  | Connect to TAO pin of TI smart power stages of Channel A to sense the highest temperature of the power stages and to sense the built-in fault signal from power stages                                                                                                                                                                                                                                                                                                          |  |  |

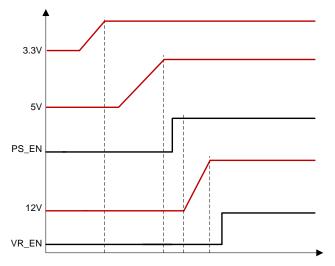

| AVR_EN      | 13       | I                  | Active high enable input for channel A. Asserting the AVR_EN pin activates channel A. Re-cycling BVR_EN pin clears the faults of channel A.                                                                                                                                                                                                                                                                                                                                     |  |  |

| AVR_RDY     | 12       | 0                  | Power good open-drain output signal of channel A. This open drain output requires an external pull-<br>up resistor. The AVR_RDY pin is pulled low when a shutdown fault occurs.                                                                                                                                                                                                                                                                                                 |  |  |

| AVSN        | 22       | I                  | Negative input of the remote voltage sense of channel A.                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| AVSP        | 21       | I                  | Positive input of the remote voltage sense of channel A.                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| BCSP1       | 32       | I                  | Current sense input for channel B. Connect to the IOUT pins of TI smart power stages. If channel B is not used, then connect the BCSP1 pin to GND.                                                                                                                                                                                                                                                                                                                              |  |  |

| BCSP2       | 29       | I                  | Current sense input for channel B. Connect to the IOUT pins of TI smart power stages. Tie the BCSP2 pin to the V3P3 pin according to Table 1 to disable the corresponding phase.                                                                                                                                                                                                                                                                                                |  |  |

| BPWM1       | 1        | 0                  | PWM signal for phase 1 of channel B                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| BPWM2       | 2        | 0                  | PWM signal for phase 2 of channel B                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| BTSEN       | 35       | 0                  | Connect to TAO pin of TI smart power stages of Channel B to sense the highest temperature of the power stages and to sense the built-in fault signal from power stages                                                                                                                                                                                                                                                                                                          |  |  |

| BVR_EN      | 20       | I                  | Active high enable input for channel B. Asserting the BVR_EN pin activates channel B. Re-cycling BVR_EN pin clears the faults of channel B.                                                                                                                                                                                                                                                                                                                                     |  |  |

| BVR_RDY     | 16       | 0                  | Power good open-drain output signal of channel B. This open drain output requires an external pull-<br>up resistor. BVR_RDY is pulled low when a shutdown fault occurs.                                                                                                                                                                                                                                                                                                         |  |  |

| BVSN        | 31       | I                  | Negative input of the remote voltage sense of channel B. If channel B is not used, connect BVSN to GND.                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| BVSP        | 30       | I                  | Positive input of the remote voltage sense of channel B. If channel B is not used, connect BVSP to GND.                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| CSPIN       | 37       | I                  | Input voltage from the positive terminal connecting to the input current sensing shunt. When input current sensing is not used, short CSPIN to VIN_CSNIN and connect to the converter input voltage (example: 12 V).                                                                                                                                                                                                                                                            |  |  |

| GND         | 17<br>18 | G                  | Connect to GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| NC          | 19       | _                  | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

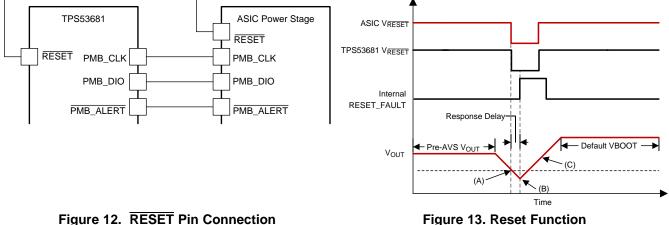

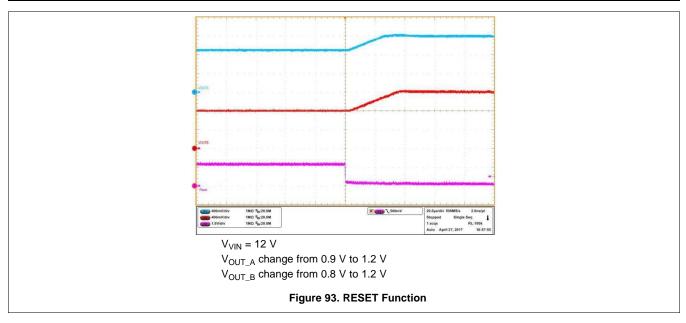

| RESET       | 15       | I/O                | Resets the output voltage to BOOT voltage                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| SMB_ALERT   | 11       | I/O                | SMBus or I <sup>2</sup> C bi-directional ALERT pin interface. (Open drain)                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| SMB_CLK     | 10       | I                  | SMBus or I <sup>2</sup> C serial clock interface. (Open drain)                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| SMB_DIO     | 9        | I/O                | SMBus or I <sup>2</sup> C bi-directional serial data interface. (Open drain)                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

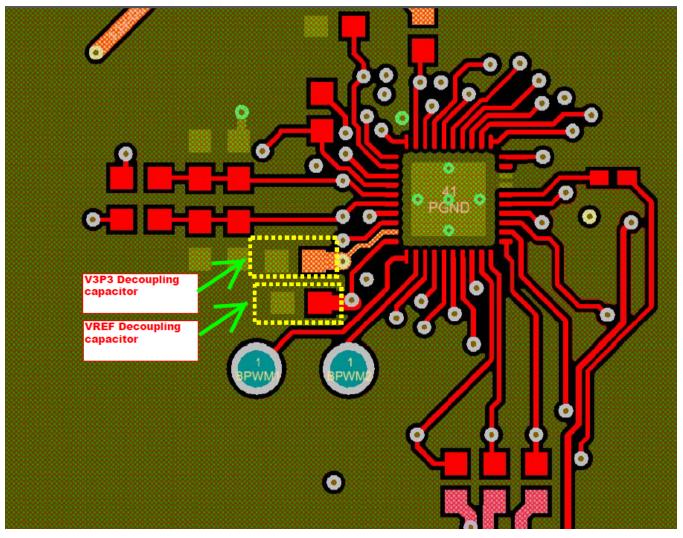

| V3P3        | 39       | Р                  | 3.3-V power input. Bypass to GND with a ceramic capacitor with a value greater than or equal to 1 $\mu$ F. Used to power all digital logic circuits.                                                                                                                                                                                                                                                                                                                            |  |  |

| VIN_CSNIN   | 38       | Р                  | Input voltage sensing for on-time control and telemetry. Serves as the negative terminal connecting to the input current sensing shunt. When input current sensing is not used, short VIN_CSNIN to CSPIN and connect to the converter input voltage (example: 12 V).                                                                                                                                                                                                            |  |  |

| VR_FAULT    | 33       | 0                  | VR fault indicator. (Open-drain). The failures include the high-side FETs short, over-voltage, over-<br>temperature, and the input over-current conditions. Use the fault signal on the platform to remove the<br>power source by turning off the AC power supply. When the failure occurs, the $VR\_FAULT$ pin is<br>LOW, and put the controller into latch-off mode. One NVM bit is used to select whether or not the<br>faults from channel B asserts the $VR\_FAULT$ . pin. |  |  |

| VREF        | 40       | 0                  | 1.7-V LDO reference voltage. Bypass to GND with 1-µF ceramic capacitor. Connect the VREF pin to the REFIN pin of the TI smart power stages as the current sense common-mode voltage.                                                                                                                                                                                                                                                                                            |  |  |

| VR_HOT      | 14       | 0                  | Active low external temperature indicator.                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| Thermal Pad |          | G                  | Analog ground pad. Connect to GND plan with vias.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Active<br>Phase<br>Channel |   | ACSP1  | ACSP2  | ACSP3  | ACSP4  | ACSP5  | ACSP6  | BSCP1  | BSCP2  |

|----------------------------|---|--------|--------|--------|--------|--------|--------|--------|--------|

| Α                          | В |        |        |        |        |        |        |        |        |

| 1                          | 0 | AIOUT1 | V3P3   | n/a    | n/a    | n/a    | n/a    | GND    | V3P3   |

| 2                          | 1 | AIOUT1 | AIOUT2 | V3P3   | n/a    | n/a    | n/a    | BIOUT1 | V3P3   |

| 3                          | 1 | AIOUT1 | AIOUT2 | AIOUT3 | V3P3   | n/a    | n/a    | BIOUT1 | V3P3   |

| 4                          | 1 | AIOUT1 | AIOUT2 | AIOUT3 | AIOUT4 | V3P3   | n/a    | BIOUT1 | V3P3   |

| 5                          | 1 | AIOUT1 | AIOUT2 | AIOUT3 | AIOUT4 | AIOUT5 | V3P3   | BIOUT1 | V3P3   |

| 6                          | 0 | AIOUT1 | AIOUT2 | AIOUT3 | AIOUT4 | AIOUT5 | AIOUT6 | GND    | V3P3   |

| 6 <sup>(1)</sup>           | 1 | AIOUT1 | AIOUT2 | AIOUT3 | AIOUT4 | AIOUT5 | AIOUT6 | BIOUT1 | V3P3   |

| 6                          | 2 | AIOUT1 | AIOUT2 | AIOUT3 | AIOUT4 | AIOUT5 | AIOUT6 | BIOUT1 | BIOUT2 |

| 5                          | 2 | AIOUT1 | AIOUT2 | AIOUT3 | AIOUT4 | AIOUT5 | V3P3   | BIOUT1 | BIOUT2 |

| 5 <sup>(1)</sup>           | 3 | AIOUT1 | AIOUT2 | AIOUT3 | AIOUT4 | AIOUT5 | BIOUT3 | BIOUT1 | BIOUT2 |

#### Table 1. Current Sense Inputs for Active Phases

(1) For *n*+1 or *n*+3 applications, the NVM setting must be changed. See also the *Phase Configuration for Channel B* section.

EXAS STRUMENTS

www.ti.com

## 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)

|                                  |                                                                                                                                                   | MIN  | MAX | UNIT |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|

|                                  | CSPIN, VIN_CSNIN                                                                                                                                  | -0.3 | 19  | V    |

| Input voltage <sup>(1) (2)</sup> | ACSP1, ACSP2, ACSP3, ACSP4, ACSP5, ACSP6/BCSP3, ADDR, ATSEN,<br>AVR_EN, AVSP, BCSP1, BCSP2, BTSEN, BVR_EN, BVSP, RESET, SMB_CLK,<br>SMB_DIO, V3P3 | -0.3 | 3.6 | V    |

| (4) (2)                          | AGND, AVSN, BVSN                                                                                                                                  | -0.3 | 0.3 | V    |

| Output voltage (1) (2)           | APWM1, APWM2, APWM3, APWM4, APWM5, APWM6/BPWM3, BPWM2,<br>AVR_RDY, BPWM1, BVR_RDY, SMB_ALERT, VREF, VR_FAULT, VR_HOT                              | -0.3 | 3.6 | V    |

| Operating junction tem           | perating junction temperature, T <sub>J</sub>                                                                                                     |      | 150 | °C   |

| Storage temperature, 7           | STG                                                                                                                                               | -55  | 150 | °C   |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

All voltage values are with respect to the network ground terminal GND unless otherwise noted. (2)

#### 6.2 ESD Ratings

|                    |                            |                                                                              | VALUE | UNIT |

|--------------------|----------------------------|------------------------------------------------------------------------------|-------|------|

|                    | Flootroototio              | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>            | ±3000 |      |

| V <sub>(ESD)</sub> | Electrostatic<br>discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 $^{\rm (2)}$ | ±1500 | V    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. (1)

(2)

#### 6.3 Recommended Operating Conditions

|                     |                                                                                                                                                   | MIN  | NOM | MAX  | UNIT |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

|                     | CSPIN, VIN_CSNIN                                                                                                                                  | 4.5  | 12  | 17   |      |

|                     | V3P3                                                                                                                                              | 2.97 | 3.3 | 3.5  |      |

| Input voltage       | ACSP1, ACSP2, ACSP3, ACSP4, ACSP5, ACSP6/BSCP3, ADDR,<br>ATSEN, AVR_EN, AVSP, BCSP1, BCSP2, BTSEN, BVR_EN, BVSP,<br>RESET, SMB_CLK, SMB_DIO, V3P3 | -0.1 |     | 3.5  | V    |

|                     | AGND, AVSN, BVSN                                                                                                                                  | -0.1 |     | 0.1  |      |

|                     | VREF                                                                                                                                              | -0.1 |     | 1.72 |      |

| Output voltage      | APWM1, APWM2, APWM3, APWM4, APW <u>M5, APWM6</u> /BPWM3,<br><u>BPWM2, AVR_RDY</u> , BPWM1, BVR_RDY, SMB_ALERT, VREF,<br>VR_FAULT, VR_HOT          | -0.1 |     | 3.5  | V    |

| Ambient temperature | ə, T <sub>A</sub>                                                                                                                                 | -40  |     | 125  | °C   |

## 6.4 Thermal Information

|                       |                                              | TPS53681   |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RSB (WQFN) | UNIT |

|                       |                                              | 40 PINS    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 34.1       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 16.6       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 5.8        | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.2        | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 5.7        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.9        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 6.5 Supply: Currents, UVLO, and Power-On Reset

$V_{\text{VIN}\_\text{CSNIN}} = 12.0 \text{ V}, \text{ } V_{\text{V3P3}} = 3.3 \text{ V}, \text{ } V_{\text{AVSN}} = \text{GND}, \text{ } V_{\text{BVSN}} = \text{GND}, \text{ } V_{\text{AVSP}} = V_{\text{OUTA}}, \text{ } V_{\text{BVSP}} = V_{\text{OUTB}} \text{ (Unless otherwise noted)}.$

|                      | PARAMETER                    | TEST CONDITIONS                            | MIN   | TYP     | MAX               | UNIT |

|----------------------|------------------------------|--------------------------------------------|-------|---------|-------------------|------|

| Supply: Curr         | ents, UVLO, and Power-On Res | et                                         |       |         |                   |      |

| I <sub>V3P3</sub>    | V3P3 supply current          | VDAC < VSP < VDAC + 100m V, ENABLE = 'HI ' |       | 13      | 18                | mA   |

| I <sub>V3P3SBY</sub> | V3P3 standby current         | ENABLE = 'LO '                             |       | 9       | 13.5              | mA   |

| V <sub>3NORMAL</sub> | V3P3 normal range            | Normal operation                           | 2.97  |         | 3.5               | V    |

| V <sub>3UVLOH</sub>  | V3P3 UVLO 'OK ' threshold    | Ramp up                                    | 2.85  |         | 2.95              | V    |

| V <sub>3UVLOL</sub>  | V3P3 UVLO fault threshold    | Ramp down                                  | 2.65  |         | 2.75              | V    |

|                      |                              | VIN_ON = 0xF010                            | 3.75  | 4       | 4.25              | V    |

|                      |                              | VIN_ON = 0xF015                            | 5     | 5.25    | 5.5               | V    |

|                      |                              | VIN_ON = 0xF019                            | 6     | 6.25    | 6.5               | V    |

|                      |                              | VIN_ON = 0xF01D                            | 7     | 7.25    | 7.5               | V    |

| V <sub>12ON</sub>    | V12 UVLO 'OK ' threshold     | VIN_ON = 0xF021                            | 8     | 8.25    | 8.5               | V    |

|                      |                              | VIN_ON = 0xF025                            | 9     | 9.25    | 25 9.5<br>25 10.5 | V    |

|                      |                              | VIN_ON = 0xF029                            | 10    | 10.25   |                   | V    |

|                      |                              | VIN_ON = 0xF02D                            | 11    | 11.25   | 11.5              | V    |

|                      |                              | VIN_ON = others                            |       | invalid |                   |      |

|                      |                              | VIN_UV_FAULT_LIMIT = 0xF011                | 4     | 4.25    | 4.48              | V    |

|                      |                              | VIN_UV_FAULT_LIMIT = 0xF80B                | 5.25  | 5.5     | 5.78              | V    |

|                      |                              | VIN_UV_FAULT_LIMIT = 0xF80D                | 6.25  | 6.5     | 6.78              | V    |

|                      |                              | VIN_UV_FAULT_LIMIT = 0xF80F                | 7.25  | 7.5     | 7.78              | V    |

| V <sub>12UVF</sub>   | V12 UVLO fault threshold     | VIN_UV_FAULT_LIMIT = 0xF811                | 8.25  | 8.5     | 8.78              | V    |

|                      |                              | VIN_UV_FAULT_LIMIT = 0xF813                | 9.25  | 9.5     | 9.78              | V    |

|                      |                              | VIN_UV_FAULT_LIMIT = 0xF815                | 10.25 | 10.5    | 10.78             | V    |

|                      |                              | VIN_UV_FAULT_LIMIT = 0xF817                | 11.25 | 11.5    | 11.8              | V    |

|                      |                              | VIN_UV_FAULT_LIMIT = others                |       | invalid |                   |      |

STRUMENTS

**EXAS**

## 6.6 References: DAC and VREF

over recommended operating conditions (unless otherwise noted)

|                        | PARAMETER                     | TEST CONDITIONS                                                                     | MIN    | TYP   | MAX    | UNIT          |

|------------------------|-------------------------------|-------------------------------------------------------------------------------------|--------|-------|--------|---------------|

| M                      | VID step size                 | 10 mV DAC: Change VID0 HI to LO to HI                                               |        | 10    |        | mV            |

| V <sub>VIDSTP</sub>    | VID step size                 | 5 mV DAC: Change VID0 HI to LO to HI                                                |        | 5     |        | mV            |

| V <sub>DAC0</sub>      | VSP tolerance                 | 10 mV DAC : $0.50 \le V_{VSP} \le 0.99 V$ ,<br>I <sub>CORE</sub> = 0 A              | -10    |       | 10     | mV            |

|                        |                               | 5 mV DAC: $0.25 \le V_{VSP} \le 0.795$ V,<br>I <sub>CORE</sub> = 0 A                |        |       | 0      |               |

| V <sub>DAC1</sub>      | VSP tolerance                 | 10 mV DAC: 1.00 V $\leq$ V <sub>VSP</sub> $\leq$ 1.49 V,<br>I <sub>CORE</sub> = 0 A | 8      |       | 8      | mV<br>mV<br>% |

| V <sub>DAC2</sub>      | VSP tolerance                 | 5 mV DAC: $0.8 \le V_{VSP} \le 0.995$ V,<br>I <sub>CORE</sub> = 0 A                 | -5     |       | 5      | mV            |

|                        | VSP tolerance                 | 5mV DAC: $1.00V \le VSP \le 1.52 V$ ,<br>$I_{CORE} = 0 A$                           | 0.5    |       | 0.5    | mV            |

| V <sub>DAC3</sub>      | VSP tolerance                 | 10 mV DAC: 1.50 V $\leq$ V <sub>VSP</sub> $\leq$ 2.50 V,<br>I <sub>CORE</sub> = 0 A | -0.5   |       | 0.5    |               |

| V <sub>VREF</sub>      | VREF output deeper sleep      | $2.97V \le V_{V3P3} \le 3.5 V$ , $I_{VREF} = 0 A$                                   | 1.692  | 1.7   | 1.708  | V             |

| V <sub>VREFSRC</sub>   | VREF output source            | $0 \text{ A} \leq I_{\text{VREF}} = 2 \text{ mA}$                                   | -8     |       |        | mV            |

| V <sub>VREFSNK</sub>   | VREF output sink              | $-2 \text{ mA} \le I_{\text{VREF}} = 0 \text{ A}$                                   |        |       | 8      | mV            |

| V                      | Voltogo dividor rotio         | VOUT_SCALE_LOOP = 0xe809,<br>VOUT_SCALE_MONITOR = 0xe809                            |        | 1.125 |        |               |

| K <sub>RATIO</sub>     | Voltage divider ratio         | VOUT_SCALE_LOOP = 0xe808,<br>VOUT_SCALE_MONITOR = 0xe808                            |        | 1     |        |               |

| V <sub>OUT_TRIML</sub> | V <sub>OUT</sub> offset LSB   | MFR_SPECIFIC_05 = 0x01                                                              | 0      | 1.25  | 2.5    | mV            |

|                        |                               | MFR_SPECIFIC_05 = 0x1F                                                              | 37.5   | 38.75 | 40     |               |

| 、 <i>/</i>             | V offect renge                | MFR_SPECIFIC_05 = 0xA0                                                              | -43.25 | -40   | -37.75 | ~\/           |

| V <sub>OUT_TRIMR</sub> | V <sub>OUT</sub> offset range | MFR_SPECIFIC_05 = 0x5F                                                              | 56.25  | 58.75 | 61.25  | mV            |

|                        |                               | MFR_SPECIFIC_05 = 0xE0                                                              | -63    | -60   | -57    |               |

## 6.7 Voltage Sense: AVSP and BVSP, AVSN and BVSN

|                   | PARAMETER               | TEST CONDITIONS                                                                 | MIN | TYP | MAX | UNIT |

|-------------------|-------------------------|---------------------------------------------------------------------------------|-----|-----|-----|------|

| I <sub>AVSP</sub> | AVSP input bias current | Not in Fault, Disable or UVLO; $V_{VSP} = V_{VDAC}$<br>= 2.3 V, $V_{VSN} = 0$ V |     |     | 75  | μA   |

| I <sub>AVSN</sub> | AVSN input bias current | Not in Fault, Disable or UVLO; $V_{VSP} = V_{VDAC}$<br>= 2.3 V, $V_{VSN} = 0$ V | -75 |     |     | μA   |

| I <sub>BVSP</sub> | BVSP input bias current | Not in Fault, Disable or UVLO; $V_{VSP} = V_{VDAC}$<br>= 1.0 V, $V_{VSN} = 0$ V |     |     | 75  | μA   |

| I <sub>BVSN</sub> | BVSN input bias current | Not in Fault, Disable or UVLO; $V_{VSP} = V_{VDAC}$<br>= 1.0 V, $V_{VSN} = 0$ V | -75 |     |     | μA   |

## 6.8 Telemetry

|                        | PARAMETER                                               | TEST CONDITIONS                                                                                                | MIN    | TYP MAX | UNIT |

|------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------|---------|------|

| V <sub>READ_VOUT</sub> | MFR_READ_VOUT Accuracy                                  | 5 mV DAC : 0.25 V $\leq$ V <sub>VSP</sub> $\leq$ 1.52 V<br>10 mV DAC: 0.5 $\leq$ V <sub>VSP</sub> $\leq$ 2.4 V | -12    | 12      | mV   |

| V <sub>READ_VIN</sub>  | READ_VIN Accuracy                                       | $4.50 \text{ V} \leq \text{V}_{\text{IN}} \leq 17 \text{ V}$                                                   | -2.25% | 2.25%   |      |

|                        |                                                         | 6-phase, I <sub>CC(max)</sub> = 228 A, I <sub>OUT</sub> = 22.8 A                                               | -7.3%  | 7.3%    |      |

|                        |                                                         | 6-phase, I <sub>CC(max)</sub> = 228 A, I <sub>OUT</sub> = 45.6 A                                               | -4.2%  | 4.2%    |      |

|                        |                                                         | 6-phase, I <sub>CC(max)</sub> = 228 A, I <sub>OUT</sub> = 68.4 A                                               | -3.1%  | 3.1%    |      |

|                        | Digital current monitor                                 | 6-phase, I <sub>CC(max)</sub> = 228 A, I <sub>OUT</sub> = 91.2 A                                               | -2.5%  | 2.5%    |      |

| MON_ACC                | accuracy, Rail A (READ_IOUT)                            | 6-phase, I <sub>CC(max)</sub> = 228 A, I <sub>OUT</sub> = 114 A                                                | -2.3%  | 2.3%    |      |

|                        |                                                         | 6-phase, I <sub>CC(max)</sub> = 228 A, I <sub>OUT</sub> = 136.8 A                                              | -2%    | 2%      |      |

|                        |                                                         | 6-phase, I <sub>CC(max)</sub> = 228 A, I <sub>OUT</sub> = 228 A                                                | -1.6%  | 1.6%    |      |

|                        |                                                         | 6-phase, I <sub>CC(max)</sub> = 228 A, I <sub>OUT</sub> = 255 A                                                | -1.5%  | 1.5%    |      |

|                        |                                                         | 5-phase, I <sub>CC(max)</sub> = 228 A, I <sub>OUT</sub> = 22.8 A                                               | -6.4%  | 6.4%    |      |

|                        |                                                         | 5-phase, I <sub>CC(max)</sub> = 228 A, I <sub>OUT</sub> = 45.6 A                                               | -3.7%  | 3.7%    |      |

|                        |                                                         | 5-phase, I <sub>CC(max)</sub> = 228 A, I <sub>OUT</sub> = 68.4 A                                               | -2.9%  | 2.9%    |      |

| MON_ACC                | Digital current monitor<br>accuracy, Rail A (READ_IOUT) | 5-phase, I <sub>CC(max)</sub> = 228 A, I <sub>OUT</sub> = 91.2 A                                               | -2.3%  | 2.3%    |      |

|                        |                                                         | 5-phase, I <sub>CC(max)</sub> = 228 A, I <sub>OUT</sub> = 114 A                                                | -2.1%  | 2.1%    |      |

|                        |                                                         | 5-phase, I <sub>CC(max)</sub> = 228 A, I <sub>OUT</sub> = 136.8 A                                              | -1.9%  | 1.9%    |      |

|                        |                                                         | 5-phase, I <sub>CC(max)</sub> = 228 A, I <sub>OUT</sub> = 228 A                                                | -1.5%  | 1.5%    |      |

|                        |                                                         | 4-phase, I <sub>CC(max)</sub> = 200 A, I <sub>OUT</sub> = 20 A                                                 | -6.5%  | 6.5%    |      |

|                        |                                                         | 4-phase, I <sub>CC(max)</sub> = 200 A, I <sub>OUT</sub> = 40 A                                                 | -3.7%  | 3.7%    |      |

|                        |                                                         | 4-phase, I <sub>CC(max)</sub> = 200 A, I <sub>OUT</sub> = 60 A                                                 | -2.8%  | 2.8%    |      |

| MON_ACC                | Digital current monitor                                 | 4-phase, I <sub>CC(max)</sub> = 200 A, I <sub>OUT</sub> = 80 A                                                 | -2.3%  | 2.3%    |      |

|                        | accuracy, Rail A (READ_IOUT)                            | 4-phase, I <sub>CC(max)</sub> = 200 A, I <sub>OUT</sub> = 100 A                                                | -2.1%  | 2.1%    |      |

|                        |                                                         | 4-phase, I <sub>CC(max)</sub> = 200 A, I <sub>OUT</sub> = 120 A                                                | -1.9%  | 1.9%    |      |

|                        |                                                         | 4-phase, I <sub>CC(max)</sub> = 200 A, I <sub>OUT</sub> = 200 A                                                | -1.5%  | 1.5%    |      |

|                        |                                                         | 3-phase, I <sub>CC(max)</sub> = 82 A, I <sub>OUT</sub> = 8.2 A                                                 | -11.4% | 11.4%   |      |

|                        |                                                         | 3-phase, I <sub>CC(max)</sub> = 82 A, I <sub>OUT</sub> = 16.4 A                                                | -6.1%  | 6.1%    |      |

|                        |                                                         | 3-phase, I <sub>CC(max)</sub> = 82 A, I <sub>OUT</sub> = 24.6 A                                                | -4.6%  | 4.6%    |      |

| MON_ACC                | Digital current monitor<br>accuracy, Rail B (READ_IOUT) | 3-phase, I <sub>CC(max)</sub> = 82 A, I <sub>OUT</sub> = 32.8 A                                                | -3.4%  | 3.4%    |      |

|                        |                                                         | 3-phase, I <sub>CC(max)</sub> = 82 A, I <sub>OUT</sub> = 41 A                                                  | -3%    | 3%      |      |

|                        |                                                         | 3-phase, I <sub>CC(max)</sub> = 82 A, I <sub>OUT</sub> = 49.2 A                                                | -2.8%  | 2.8%    |      |

|                        |                                                         | 3-phase, I <sub>CC(max)</sub> = 82 A, I <sub>OUT</sub> = 82 A                                                  | -2%    | 2%      |      |

|                        |                                                         | 2-phase, I <sub>CC(max)</sub> = 82 A, I <sub>OUT</sub> = 8.2 A                                                 | -8.7%  | 8.7%    |      |

|                        |                                                         | 2-phase, I <sub>CC(max)</sub> = 82 A, I <sub>OUT</sub> = 16.4 A                                                | -4.7%  | 4.7%    |      |

|                        |                                                         | 2-phase, I <sub>CC(max)</sub> = 82 A, I <sub>OUT</sub> = 24.6 A                                                | -3.7%  | 3.7%    |      |

| MON_ACC                | Digital current monitor<br>accuracy, Rail B (READ_IOUT) | 2-phase, I <sub>CC(max)</sub> = 82 A, I <sub>OUT</sub> = 32.8 A                                                | -2.7%  | 2.7%    |      |

|                        | accuracy, Rail D (READ_1001)                            | 2-phase, I <sub>CC(max)</sub> = 82 A, I <sub>OUT</sub> = 41 A                                                  | -2.5%  | 2.5%    |      |

|                        |                                                         | 2-phase, I <sub>CC(max)</sub> = 82 A, I <sub>OUT</sub> = 49.2 A                                                | -2.4%  | 2.4%    |      |

|                        |                                                         | 2-phase, I <sub>CC(max)</sub> = 82 A, I <sub>OUT</sub> = 82 A                                                  | -1.8%  | 1.8%    |      |

| Temp                   | READ_TEMP1                                              | 0.28 V (–40°C) ≤ TSEN ≤ 1.8 V (150°C)                                                                          | -2     | 0 2     | °C   |

SLUSCT1B-JUNE 2017-REVISED JANUARY 2019

www.ti.com

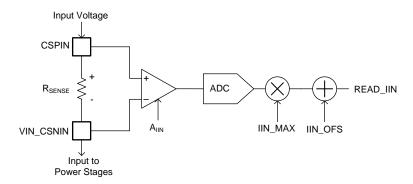

## 6.9 Input Current Sensing

|                 | PARAMETER         | TEST CONDITIONS                                                                                                                         | MIN  | TYP MAX | UNIT |

|-----------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------|---------|------|

| I <sub>IN</sub> |                   | $\begin{array}{l} (V_{CSPIN}-V_{CSNIN})=2.5\ \text{mV},\ I_{IN}=5\ \text{A},\\ R_{SENSE}=0.5\ \text{m}\Omega \end{array}$               | -10% | 10%     |      |

|                 | READ_IIN accuracy | $      (V_{CSPIN} - V_{CSNIN}) = 5 \text{ mV}, \text{ I}_{\text{IN}} = 10 \text{ A}, \\ \text{R}_{\text{SENSE}} = 0.5 \text{ m}\Omega $ | -6%  | 6%      |      |

|                 |                   | $\begin{array}{l} (V_{CSPIN}-V_{CSNIN}) = 15 \text{ mV}, \ I_{IN} = 30 \text{ A}, \\ R_{SENSE} = 0.5 \text{ m}\Omega \end{array}$       | -3%  | 3%      |      |

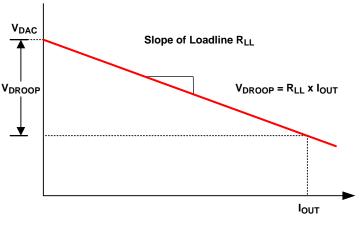

## 6.10 Programmable Loadline Settings

|                           | PARAMETER                | TEST CONDITIONS     | MIN    | TYP    | MAX    | UNIT  |

|---------------------------|--------------------------|---------------------|--------|--------|--------|-------|

|                           |                          | VOUT_DROOP = 0xD000 |        | 0      |        | mΩ    |

|                           |                          | VOUT_DROOP = 0xD008 | 0.1125 | 0.125  | 0.1395 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD010 | 0.2412 | 0.25   | 0.2587 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD014 | 0.3031 | 0.3125 | 0.3218 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD018 | 0.3637 | 0.375  | 0.3872 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD01C | 0.4265 | 0.4375 | 0.4484 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD020 | 0.4875 | 0.5    | 0.5125 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD024 | 0.5484 | 0.5625 | 0.5765 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD028 | 0.6093 | 0.625  | 0.6406 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD030 | 0.6855 | 0.7031 | 0.7207 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD033 | 0.7769 | 0.7969 | 0.8168 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD034 | 0.7921 | 0.8125 | 0.8328 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD035 | 0.8073 | 0.8281 | 0.8488 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD036 | 0.8227 | 0.8438 | 0.8648 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD037 | 0.8379 | 0.8594 | 0.8808 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD038 | 0.8531 | 0.875  | 0.8968 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD039 | 0.8683 | 0.8906 | 0.9128 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD03A | 0.8836 | 0.9063 | 0.9289 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD03B | 0.8988 | 0.9219 | 0.9449 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD03C | 0.9140 | 0.9375 | 0.9609 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD03D | 0.9292 | 0.9531 | 0.9769 | mΩ    |

|                           | DC loadline settings for | VOUT_DROOP = 0xD03E | 0.9445 | 0.9688 | 0.9930 | mΩ    |

| OCLL <sub>Channel A</sub> | Channel A                | VOUT_DROOP = 0xD03F | 0.9597 | 0.9844 | 1.0090 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD040 | 0.975  | 1      | 1.025  | mΩ    |

|                           |                          | VOUT_DROOP = 0xD041 | 0.9902 | 1.0156 | 1.0409 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD042 | 1.0055 | 1.0313 | 1.0570 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD043 | 1.0207 | 1.0469 | 1.0730 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD044 | 1.0359 | 1.0625 | 1.0890 | mΩ    |

|                           |                          | VOUT DROOP = 0xD048 | 1.0968 | 1.125  | 1.1531 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD050 | 1.2187 | 1.25   | 1.2812 | mΩ    |

|                           |                          | VOUT DROOP = 0xD058 | 1.3406 | 1.375  | 1.4093 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD060 | 1.4625 | 1.5    | 1.5375 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD068 | 1.5843 | 1.625  | 1.6656 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD070 | 1.7062 | 1.75   | 1.7937 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD078 | 1.8281 | 1.875  | 1.9218 | mΩ    |

|                           |                          | VOUT DROOP = 0xD07C | 1.8890 | 1.9375 | 1.9859 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD080 | 1.95   | 2      | 2.05   | mΩ    |

|                           |                          | VOUT_DROOP = 0xD084 | 2.0109 | 2.0625 | 2.1141 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD088 | 2.0718 | 2.125  | 2.1781 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD08C | 2.1328 | 2.1875 | 2.2421 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD090 | 2.1937 | 2.1075 | 2.3062 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD090 | 2.2698 | 2.328  | 2.3002 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD098 | 2.3612 | 2.328  | 2.3802 | mΩ    |

|                           |                          | VOUT_DROOP = 0xD09B | 2.3012 | 2.7210 | 2.4023 | 11152 |

## **Programmable Loadline Settings (continued)**

|                           | PARAMETER                | TEST CONDITIONS     | MIN    | TYP    | MAX    | UNIT |

|---------------------------|--------------------------|---------------------|--------|--------|--------|------|

|                           |                          | VOUT_DROOP = 0xD09D | 2.3917 | 2.4531 | 2.5144 | mΩ   |

|                           |                          | VOUT_DROOP = 0xD09E | 2.4069 | 2.4687 | 2.5304 | mΩ   |

|                           |                          | VOUT_DROOP = 0xD09F | 2.4221 | 2.4843 | 2.5464 | mΩ   |

|                           |                          | VOUT_DROOP = 0xD0A0 | 2.4375 | 2.5    | 2.5625 | mΩ   |

|                           |                          | VOUT_DROOP = 0xD0A1 | 2.4527 | 2.5156 | 2.5784 | mΩ   |

|                           |                          | VOUT_DROOP = 0xD0A2 | 2.4679 | 2.5312 | 2.5944 | mΩ   |

|                           |                          | VOUT_DROOP = 0xD0A3 | 2.4831 | 2.5468 | 2.6104 | mΩ   |

|                           |                          | VOUT_DROOP = 0xD0A4 | 2.4984 | 2.5625 | 2.6265 | mΩ   |

|                           |                          | VOUT_DROOP = 0xD0A5 | 2.5136 | 2.5781 | 2.6425 | mΩ   |

|                           | DC loadline settings for | VOUT_DROOP = 0xD0A6 | 2.5288 | 2.5937 | 2.6585 | mΩ   |

| DCLL <sub>Channel</sub> A | Channel A                | VOUT_DROOP = 0xD0A7 | 2.5437 | 2.609  | 2.6742 | mΩ   |

|                           |                          | VOUT_DROOP = 0xD0A8 | 2.5593 | 2.625  | 2.6906 | mΩ   |

|                           |                          | VOUT_DROOP = 0xD0A9 | 2.5745 | 2.6406 | 2.7066 | mΩ   |

|                           |                          | VOUT_DROOP = 0xD0AA | 2.5897 | 2.6562 | 2.7226 | mΩ   |

|                           |                          | VOUT_DROOP = 0xD0AB | 2.6050 | 2.6718 | 2.7385 | mΩ   |

|                           |                          | VOUT_DROOP = 0xD0AC | 2.6203 | 2.6875 | 2.7546 | mΩ   |

|                           |                          | VOUT_DROOP = 0xD0B0 | 2.6812 | 2.75   | 2.8187 | mΩ   |

|                           |                          | VOUT_DROOP = 0xD0B8 | 2.8031 | 2.875  | 2.9468 | mΩ   |

|                           |                          | VOUT_DROOP = 0xD0C0 | 2.925  | 3      | 3.075  | mΩ   |

|                           |                          | VOUT_DROOP = 0xD0C8 | 3.0468 | 3.125  | 3.2031 | mΩ   |

|                           |                          | VOUT_DROOP = 0xD000 |        | 0      |        | mΩ   |

|                           |                          | VOUT_DROOP = 0xD008 | 0.1125 | 0.125  | 0.1395 | mΩ   |

|                           |                          | VOUT_DROOP = 0xD010 | 0.2355 | 0.25   | 0.2625 | mΩ   |

|                           |                          | VOUT_DROOP = 0xD014 | 0.297  | 0.3125 | 0.3234 | mΩ   |

|                           |                          | VOUT_DROOP = 0xD018 | 0.3637 | 0.375  | 0.395  | mΩ   |

|                           |                          | VOUT_DROOP = 0xD01C | 0.4244 | 0.4375 | 0.454  | mΩ   |

|                           |                          | VOUT_DROOP = 0xD020 | 0.4875 | 0.5    | 0.517  | mΩ   |

|                           | DC Loadline settings for | VOUT_DROOP = 0xD024 | 0.5464 | 0.5625 | 0.5786 | mΩ   |

| DCLL <sub>Channel B</sub> | Channel B                | VOUT_DROOP = 0xD028 | 0.6093 | 0.625  | 0.648  | mΩ   |

|                           |                          | VOUT_DROOP = 0xD030 | 0.6855 | 0.7031 | 0.7207 | mΩ   |

|                           |                          | VOUT_DROOP = 0xD033 | 0.7769 | 0.7969 | 0.8168 | mΩ   |

|                           |                          | VOUT_DROOP = 0xD034 | 0.7921 | 0.8125 | 0.8335 | mΩ   |

|                           |                          | VOUT_DROOP = 0xD035 | 0.8073 | 0.8281 | 0.852  | mΩ   |

|                           |                          | VOUT_DROOP = 0xD036 | 0.8227 | 0.8438 | 0.8648 | mΩ   |

|                           |                          | VOUT_DROOP = 0xD037 | 0.8379 | 0.8594 | 0.8815 | mΩ   |

|                           |                          | VOUT_DROOP = 0xD038 | 0.8531 | 0.875  | 0.8968 | mΩ   |

## **Programmable Loadline Settings (continued)**

over recommended operating conditions (unless otherwise noted)

|      | PARAMETER                                      | TEST CONDITIONS        | MIN    | TYP    | MAX    | UNIT |

|------|------------------------------------------------|------------------------|--------|--------|--------|------|

|      |                                                | MFR_SPECIFIC_07 = 0x00 |        | 0      |        | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x01 | 0.1125 | 0.125  | 0.1395 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x02 | 0.2412 | 0.25   | 0.2587 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x03 | 0.3031 | 0.3125 | 0.3218 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x04 | 0.3637 | 0.375  | 0.3862 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x05 | 0.4265 | 0.4375 | 0.4484 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x06 | 0.4875 | 0.5    | 0.5125 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x07 | 0.5484 | 0.5625 | 0.5765 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x08 | 0.6093 | 0.625  | 0.6406 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x09 | 0.7312 | 0.75   | 0.7687 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x0A | 0.7769 | 0.7969 | 0.8168 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x0B | 0.7921 | 0.8125 | 0.8328 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x0C | 0.8073 | 0.8281 | 0.8488 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x0D | 0.8227 | 0.8438 | 0.8648 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x0E | 0.8379 | 0.8594 | 0.8808 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x0F | 0.8531 | 0.875  | 0.8968 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x10 | 0.8683 | 0.8906 | 0.9128 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x11 | 0.8836 | 0.9063 | 0.9289 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x12 | 0.8988 | 0.9219 | 0.9449 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x13 | 0.9140 | 0.9375 | 0.9609 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x14 | 0.9292 | 0.9531 | 0.9769 | mΩ   |

| ACLL | AC Loadline settings for<br>both Channel A and | MFR_SPECIFIC_07 = 0x15 | 0.9445 | 0.9688 | 0.9930 | mΩ   |

| AULL | Channel B <sup>(1)</sup>                       | MFR_SPECIFIC_07 = 0x16 | 0.9597 | 0.9844 | 1.0090 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x17 | 0.975  | 1      | 1.025  | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x18 | 0.9902 | 1.0156 | 1.0409 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x19 | 1.0055 | 1.0313 | 1.0570 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x1A | 1.0207 | 1.0469 | 1.0730 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x1B | 1.0359 | 1.0625 | 1.0890 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x1C | 1.0968 | 1.125  | 1.1531 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x1D | 1.2187 | 1.25   | 1.2812 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x1E | 1.3406 | 1.375  | 1.4093 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x1F | 1.4625 | 1.5    | 1.5375 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x20 | 1.5843 | 1.625  | 1.6656 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x21 | 1.7062 | 1.75   | 1.7937 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x22 | 1.8281 | 1.875  | 1.9218 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x23 | 1.8890 | 1.9375 | 1.9859 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x24 | 1.95   | 2      | 2.05   | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x25 | 2.0109 | 2.0625 | 2.1140 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x26 | 2.0718 | 2.125  | 2.1781 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x27 | 2.1328 | 2.1875 | 2.2421 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x28 | 2.1937 | 2.25   | 2.3062 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x29 | 2.3156 | 2.375  | 2.4343 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x2A | 2.3612 | 2.4218 | 2.4823 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x2B | 2.3765 | 2.4375 | 2.4984 | mΩ   |

(1) Specified by design. Not production tested.

## **Programmable Loadline Settings (continued)**

|      | PARAMETER                                      | TEST CONDITIONS          | MIN    | TYP    | MAX    | UNIT |

|------|------------------------------------------------|--------------------------|--------|--------|--------|------|

|      |                                                | MFR_SPECIFIC_07 = 0x2C   | 2.3917 | 2.4531 | 2.5144 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x2D   | 2.4069 | 2.4687 | 2.5304 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x2E   | 2.4221 | 2.4843 | 2.5464 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x2F   | 2.4375 | 2.5    | 2.5625 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x30   | 2.4527 | 2.5156 | 2.5784 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x31   | 2.4679 | 2.5312 | 2.5944 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x32   | 2.4831 | 2.5468 | 2.6104 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x33   | 2.4984 | 2.5625 | 2.6265 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x34   | 2.5136 | 2.5781 | 2.6425 | mΩ   |

|      | AC Loadline settings for                       | MFR_SPECIFIC_07 = 0x35   | 2.5288 | 2.5937 | 2.6585 | mΩ   |

| ACLL | both Channel A and<br>Channel B <sup>(1)</sup> | MFR_SPECIFIC_07 = 0x36   | 2.5437 | 2.609  | 2.6742 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x37   | 2.5593 | 2.625  | 2.6906 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x38   | 2.5745 | 2.6406 | 2.7066 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x39   | 2.5897 | 2.6562 | 2.7226 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x3A   | 2.6050 | 2.6718 | 2.7385 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x3B   | 2.6203 | 2.6875 | 2.7546 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x3C   | 2.6812 | 2.75   | 2.8187 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x3D   | 2.8031 | 2.875  | 2.9468 | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x3E   | 2.925  | 3      | 3.075  | mΩ   |

|      |                                                | MFR_SPECIFIC_07 = 0x3F   | 3.0468 | 3.125  | 3.2031 | mΩ   |

|      |                                                | MFR_SPEC_7<11:8> = 0000b |        | 5      |        | μs   |

|      |                                                | MFR_SPEC_7<11:8> = 0001b |        | 10     |        | μs   |

|      |                                                | MFR_SPEC_7<11:8> = 0010b |        | 15     |        | μs   |

|      |                                                | MFR_SPEC_7<11:8> = 0011b |        | 20     |        | μs   |

|      |                                                | MFR_SPEC_7<11:8> = 0100b |        | 25     |        | μs   |

|      |                                                | MFR_SPEC_7<11:8> = 0101b |        | 30     |        | μs   |

|      |                                                | MFR_SPEC_7<11:8> = 0110b |        | 35     |        | μs   |

|      | (1)                                            | MFR_SPEC_7<11:8> = 0111b |        | 40     |        | μs   |

| INT  | Integration time constant <sup>(1)</sup>       | MFR_SPEC_7<11:8> = 1000b |        | 1      |        | μs   |

|      |                                                | MFR_SPEC_7<11:8> = 1001b |        | 2      |        | μs   |

|      |                                                | MFR_SPEC_7<11:8> = 1010b |        | 3      |        | μs   |

|      |                                                | MFR_SPEC_7<11:8> = 1011b |        | 4      |        | μs   |

|      |                                                | MFR_SPEC_7<11:8> = 1100b |        | 5      |        | μs   |

|      |                                                | MFR_SPEC_7<11:8> = 1101b |        | 6      |        | μs   |

|      |                                                | MFR_SPEC_7<11:8> = 1110b |        | 7      |        | μs   |

|      |                                                | MFR_SPEC_7<11:8> = 1111b |        | 8      |        | μs   |

#### 6.11 Current Sense and Calibration

over recommended operating conditions (unless otherwise noted)

|                             | PARAMETER                                                         | TEST CONDITIONS                            | MIN | TYP    | MAX | UNIT |

|-----------------------------|-------------------------------------------------------------------|--------------------------------------------|-----|--------|-----|------|

| I <sub>ACSP1</sub>          | ACSP1 leakage current                                             | V <sub>ACSP1</sub> = 2.5 V                 | 0   |        | 20  | μA   |

| I <sub>ACSP2</sub>          | ACSP2 leakage current                                             | V <sub>ACSP2</sub> = 2.5 V                 | 0   |        | 20  | μA   |

| I <sub>ACSP3</sub>          | ACSP3 leakage current                                             | V <sub>ACSP3</sub> = 2.5 V                 | 0   |        | 20  | μA   |

| I <sub>ACSP4</sub>          | ACSP4 leakage current                                             | V <sub>ACSP4</sub> = 2.5 V                 | 0   |        | 20  | μA   |

| I <sub>ACSP5</sub>          | ACSP5 leakage current                                             | V <sub>ACSP5</sub> = 2.5 V                 | 0   |        | 20  | μA   |

| I <sub>ACSP6</sub>          | ACSP6 leakage current                                             | V <sub>ACSP6</sub> = 2.5 V                 | 0   |        | 20  | μA   |

| I <sub>BCSP1</sub>          | BCSP1 leakage current                                             | V <sub>BCSP1</sub> = 2.5 V                 | 0   |        | 20  | μA   |

| I <sub>BCSP2</sub>          | BCSP2 leakage current                                             | V <sub>BCSP2</sub> = 2.5 V                 | 0   |        | 20  | μA   |

| IMON_CAL_OF1                | Current monitor calibration offset LSB (per-phase) <sup>(1)</sup> | IOUT_CAL_OFFSET resolution (per-<br>phase) |     | 0.125  |     | А    |

|                             | Current monitor calibration offset                                | IOUT_CAL_OFFSET = 0xE808 (per-<br>phase)   |     | 1      |     | А    |

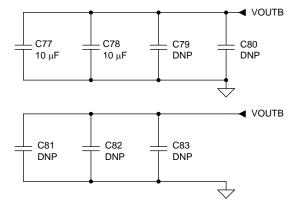

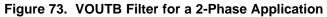

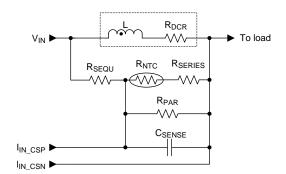

| MON_CAL_OF2                 | range (per-phase)                                                 | IOUT_CAL_OFFSET = 0xEFF9 (per-<br>phase)   | -   | -0.875 |     | А    |