**TPS2549**

SLUSCP2-SEPTEMBER 2016

## TPS2549 USB Charging Port Controller and Power Switch With Cable Compensation

#### Features

- 4.5-V to 6.5-V Operating Range

- 47-mΩ (typical) High-Side MOSFET

- 3-A Maximum Continuous Output Current

- ±5% CS Output for Cable Compensation

- CDP Mode per USB Battery Charging Specification 1.2

- Automatic DCP Modes Selection:

- Shorted Mode per BC1.2 and YD/T 1591-2009

- 2.7-V Divider 3 Mode

- 1.2-V Mode

- D+ and D- Client Mode for System Update

- D+ and D- Short-to-V<sub>BUS</sub> Protection

- D+ and D- ±8-kV Contact and ±15-kV Air Discharge ESD Rating (IEC 61000-4-2)

- UL Recognition and CB Certification Pending

- -40°C to 125°C Junction Operating Temperature

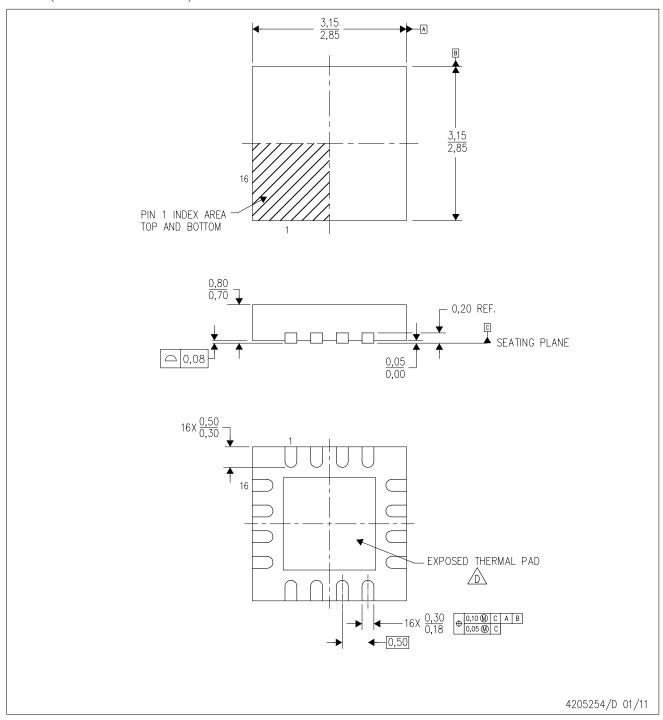

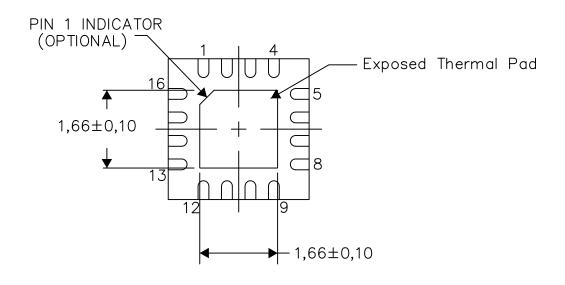

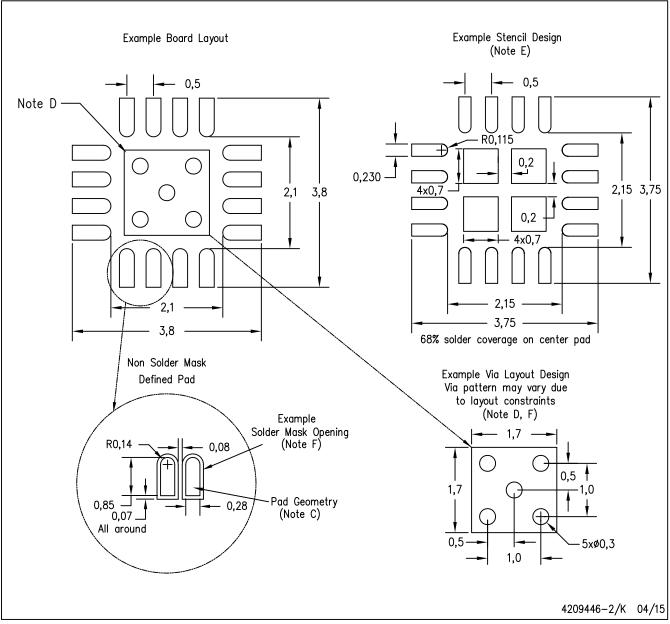

- 16-Pin QFN (3-mm × 3-mm) Package

### **Applications**

- USB Ports (Host and Hubs)

- Wall Charging Adapters

- Aftermarket Automotive Chargers

#### Description 3

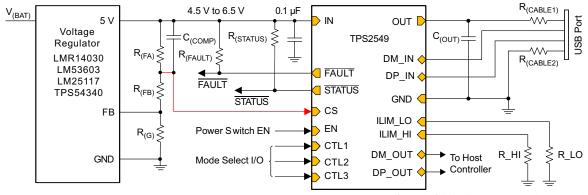

The TPS2549 device is a USB charging port controller and power switch with a current-sense output that is able to control an upstream supply. This allows it to maintain 5 V at the USB port even with heavy charging currents. This is important in systems with long USB cables where significant voltage drops can occur while fast-charging portable devices.

The TP2549 47-m $\Omega$  power switch has two selectable, programmable current limits that support port power management by providing a lower current limit that can be used when adjacent ports are experiencing heavy loads. This is important in systems with multiple ports and an upstream supply unable to provide full current to all ports simultaneously.

The DCP\_Auto scheme detects and selects the proper D+ and D- settings to communicate with the attached device, so that it can fast-charge at full current. The integrated CDP detection enables up to 1.5-A fast charging of most portable devices with simultaneous data communication.

The unique client-mode feature allows software updates to client devices, but avoids power conflicts by turning off the internal power switch while keeping the data line connection.

Additionally, the TPS2549 device integrates short-to-V<sub>BUS</sub> protection for D+ and D- to prevent damage when D+ and/or D- unexpectedly short to V<sub>BUS</sub>. To save space in the application, the TPS2549 device also integrates ESD protection to pass IEC61000-4-2 without external circuitry on D+ and D-.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| TPS2549     | WQFN (16) | 3.00 mm × 3.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

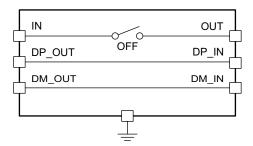

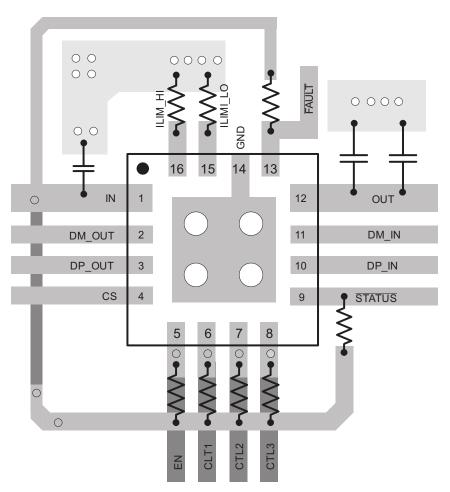

#### Simplified Schematic

Copyright © 2016, Texas Instruments Incorporated

## **Table of Contents**

| 1 | Features 1                           |    | 8.3 Feature Description                             | 17     |

|---|--------------------------------------|----|-----------------------------------------------------|--------|

| 2 | Applications 1                       |    | 8.4 Device Functional Modes                         | 24     |

| 3 | Description 1                        | 9  | Application and Implementation                      | 28     |

| 4 | Revision History2                    |    | 9.1 Application Information                         | 28     |

| 5 | Pin Configuration and Functions      |    | 9.2 Typical Application                             | 28     |

| 6 | Specifications4                      | 10 | Power Supply Recommendations                        | 33     |

| • | 6.1 Absolute Maximum Ratings         | 11 | Layout                                              | 33     |

|   | 6.2 ESD Ratings                      |    | 11.1 Layout Guidelines                              | 33     |

|   | 6.3 Recommended Operating Conditions |    | 11.2 Layout Example                                 | 34     |

|   | 6.4 Thermal Information              | 12 | Device and Documentation Support                    | 35     |

|   | 6.5 Electrical Characteristics       |    | 12.1 Documentation Support                          | 35     |

|   | 6.6 Switching Characteristics        |    | 12.2 Receiving Notification of Documentation Update | tes 35 |

|   | 6.7 Typical Characteristics          |    | 12.3 Community Resources                            | 35     |

| 7 | Parameter Measurement Information 14 |    | 12.4 Trademarks                                     | 35     |

| 8 | Detailed Description 15              |    | 12.5 Electrostatic Discharge Caution                | 35     |

| • | 8.1 Overview                         |    | 12.6 Glossary                                       | 35     |

|   | 8.2 Functional Block Diagram         | 13 | Mechanical, Packaging, and Orderable Information    | 36     |

## 4 Revision History

| DATE           | REVISION | NOTES            |  |

|----------------|----------|------------------|--|

| September 2016 | *        | Initial release. |  |

www.ti.com

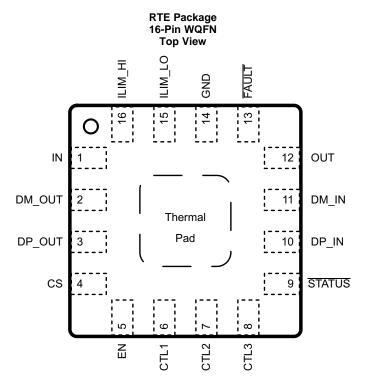

# 5 Pin Configuration and Functions

**Pin Functions**

| PI          | N   | TYPE <sup>(1)</sup> | DECORPORTION                                                                                                                                                                         |

|-------------|-----|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | NO. | IYPE                | DESCRIPTION                                                                                                                                                                          |

| CS          | 4   | 0                   | Provide sink current proportional to output current. For cable compensation, connect to the feedback divider of the up-stream voltage regulator.                                     |

| CTL1        | 6   | 1                   |                                                                                                                                                                                      |

| CTL2        | 7   | 1                   | Logic-level control inputs for controlling the charging mode and the signal switches; (see Table 2). These pins tie directly to IN or GND without a pullup or pulldown resistor.     |

| CTL3        | 8   | I                   | Tuble 2). These pins he directly to it of cits without a pullap of pullacent resistor.                                                                                               |

| DM_IN       | 11  | I/O                 | D– data line to downstream connector                                                                                                                                                 |

| DM_OUT      | 2   | I/O                 | D– data line to upstream USB host controller                                                                                                                                         |

| DP_IN       | 10  | I/O                 | D+ data line to downstream connector                                                                                                                                                 |

| DP_OUT      | 3   | I/O                 | D+ data line to upstream USB host controller                                                                                                                                         |

| EN          | 5   | I                   | Logic-level control input for turning the power switch and the signal switches on/off. When EN is low, the device is disabled, the signal and power switches are OFF.                |

| FAULT       | 13  | 0                   | Active-low open-drain output, asserted during overtemperature, overcurrent, and DP_IN and DM_IN overvoltage conditions. See Table 1.                                                 |

| GND         | 14  | _                   | Ground connection; should be connected externally to the thermal pad.                                                                                                                |

| ILIM_HI     | 16  | I                   | Connect external resistor to ground to set the high current-limit threshold.                                                                                                         |

| ILIM_LO     | 15  | 1                   | Connect external resistor to ground to set the low current-limit threshold and the load-detection current threshold.                                                                 |

| IN          | 1   | PWR                 | Input supply voltage; connect a 0.1 $\mu F$ or greater ceramic capacitor from IN to GND as close to the IC as possible.                                                              |

| OUT         | 12  | PWR                 | Power-switch output                                                                                                                                                                  |

| STATUS      | 9   | 0                   | Active-low open-drain output, asserted when the load exceeds the load-detection threshold                                                                                            |

| Thermal pad | _   | _                   | Thermal pad on bottom of package. The thermal pad is internally connected to GND and is used to heat-sink the device to the circuit board. Connect the thermal pad to the GND plane. |

(1) I = Input, O = Output, I/O = Input and output, PWR = Power

#### 6 Specifications

#### 6.1 Absolute Maximum Ratings

Voltages are with respect to GND unless otherwise noted (1)

|                    |                                                  |                                                                    | MIN                | MAX                | UNIT |

|--------------------|--------------------------------------------------|--------------------------------------------------------------------|--------------------|--------------------|------|

|                    |                                                  | CS, CTL1, CTL2, CTL3, EN, FAULT, ILIM_HI, ILIM_LO, IN, OUT, STATUS | -0.3               | 7                  | ٧    |

|                    | Voltage range                                    | DM_IN, DM_OUT, DP_IN, DP_OUT                                       | -0.3               | 5.7                | ٧    |

|                    |                                                  | IN to OUT                                                          | -7                 | 7                  | V    |

|                    | Continuous current in SDP,<br>CDP or client mode | DP_IN to DP_OUT or DM_IN to DM_OUT                                 | -100               | 100                | mA   |

|                    | Continuous current in BC1.2<br>DCP mode          | DP_IN to DM_IN                                                     | -35                | 35                 | mA   |

|                    | Continuous output current                        | OUT                                                                | Inter              | rnally limited     | Α    |

| I <sub>(SRC)</sub> | Continuous output source current                 | ILIM_HI, ILIM_LO                                                   | Inter              | rnally limited     | Α    |

|                    | Continuous autout aink aurrent                   | FAULT, STATUS                                                      |                    | 25                 | mA   |

| I(SNK)             | Continuous output sink current                   | CS                                                                 | Internally limited |                    | Α    |

| TJ                 | Operating junction temperature                   |                                                                    | -40                | Internally limited | °C   |

| T <sub>stg</sub>   | Storage temperature                              |                                                                    | -65                | 150                | °C   |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 ESD Ratings

|                    |               |                                                                                                                                              |                                                 | VALUE   | UNIT |

|--------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------|------|

|                    |               | Human-bod                                                                                                                                    | y model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)   | ±2,000  |      |

| .,                 | Electrostatic | Charged-device model (CDM),per JEDEC specification JESD22-C101 <sup>(2)</sup>                                                                |                                                 | ±750    | \/   |

| V <sub>(ESD)</sub> | discharge     | discharge IEC <sup>(3)</sup> IEC <sup>(3)</sup> IEC61000-4-2 contact discharge, DP_IN and DM_IN  IEC61000-4-2 air discharge, DP_IN and DM_IN | IEC61000-4-2 contact discharge, DP_IN and DM_IN | ±8,000  | V    |

|                    |               |                                                                                                                                              | IEC61000-4-2 air discharge, DP_IN and DM_IN     | ±15,000 |      |

<sup>1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.3 Recommended Operating Conditions

Voltages are with respect to GND unless otherwise noted.

|                        |                                               |                                     | MIN  | NOM MAX | UNIT |

|------------------------|-----------------------------------------------|-------------------------------------|------|---------|------|

| $V_{(IN)}$             | Supply voltage                                | IN                                  | 4.5  | 6.5     | V    |

|                        | l                                             | CTL1, CTL2, CTL3, EN                | 0    | 6.5     | V    |

|                        | Input voltage                                 | DM_IN, DM_OUT, DP_IN, DP_OUT        | 0    | 3.6     | V    |

| I <sub>(OUT)</sub>     | Output continuous current                     | OUT (-40°C ≤ T <sub>A</sub> ≤ 85°C) |      | 3       | Α    |

|                        | Continuous current in SDP, CDP or client mode | DP_IN to DP_OUT or DM_IN to DM_OUT  | -30  | 30      | mA   |

|                        | Continuous current in BC1.2 DCP mode          | DP_IN to DM_IN                      | -15  | 15      | mA   |

|                        | Continuous output sink current                | FAULT, STATUS                       |      | 10      | mA   |

| R <sub>(ILIM_xx)</sub> | Current limit-set resistors                   |                                     | 15.4 | 1000    | kΩ   |

| $T_{J}$                | Operating junction temperature                |                                     | -40  | 125     | °C   |

<sup>(3)</sup> Surges per IEC61000-4-2, 1999 applied between DP\_IN/DM\_IN and output ground of the TPS2549Q1EVM-729 (SLVUAK6) evaluation module.

www.ti.com

#### 6.4 Thermal Information

|                        |                                              | TPS2549    |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RTE (WQFN) | UNIT |

|                        |                                              | 16 PINS    |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 44.9       | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 53.3       | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 17.6       | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 1          | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 17.6       | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 4.1        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

### 6.5 Electrical Characteristics

Unless otherwise noted,  $-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}$  and  $4.5 \text{ V} \le \text{V}_{\text{(IN)}} \le 6.5 \text{ V}, \text{V}_{\text{(EN)}} = \text{V}_{\text{(IN)}}, \text{V}_{\text{(CTL1)}} = \text{V}_{\text{(CTL2)}} = \text{V}_{\text{(IN)}}. \text{ R}_{\text{(FAULT)}} = \text{R}_{\text{(STATUS)}} = 10 \text{ k}\Omega, \text{ R}_{\text{(ILIM\_LO)}} = 19.1 \text{ k}\Omega, \text{ R}_{\text{(ILIM\_LO)}} = 80.6 \text{ k}\Omega. \text{ Positive currents are into pins. Typical values are at 25°C. All voltages are with respect to GND.}$

|                       | PARAMETER                                 | TEST CONDITIONS                                                                                                                     | MIN  | TYP  | MAX  | UNIT      |

|-----------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-----------|

| OUT – POW             | ER SWITCH                                 |                                                                                                                                     |      |      |      |           |

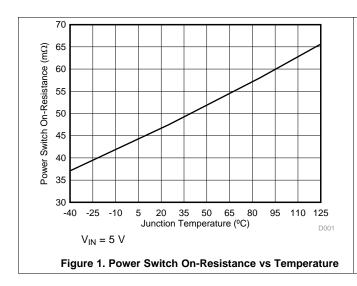

|                       |                                           | T <sub>J</sub> = 25°C                                                                                                               |      | 47   | 57   |           |

| r <sub>DS(on)</sub>   | On-resistance <sup>(1)</sup>              | -40°C ≤ T <sub>J</sub> ≤ 85°C                                                                                                       |      | 47   | 72   | $m\Omega$ |

|                       |                                           | -40°C ≤T <sub>J</sub> ≤ 125°C                                                                                                       |      | 47   | 80   |           |

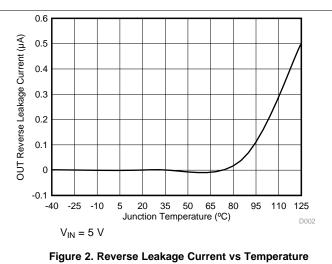

| I <sub>lkg(OUT)</sub> | Reverse leakage current on OUT pin        | $V_{OUT} = 6.5 \text{ V}, V_{IN} = V_{EN} = 0 \text{ V}, -40^{\circ}\text{C} \le T_{J} \le 85^{\circ}\text{C},$ measure $I_{(OUT)}$ |      |      | 2    | μA        |

| OUT - DISCH           | HARGE                                     |                                                                                                                                     |      |      |      |           |

| R <sub>(DCHG)</sub>   | OUT discharge resistance                  |                                                                                                                                     | 400  | 500  | 630  | Ω         |

| EN, CTL1, C           | TL2, CTL3 INPUTS                          |                                                                                                                                     |      |      | ·    |           |

|                       | Input pin rising logic threshold voltage  |                                                                                                                                     | 1    | 1.35 | 2    | ٧         |

|                       | Input pin falling logic threshold voltage |                                                                                                                                     | 0.85 | 1.15 | 1.65 | ٧         |

|                       | Hysteresis (2)                            |                                                                                                                                     |      | 200  |      | mV        |

|                       | Input current                             | Pin voltage = 0 V or 6.5 V                                                                                                          | -1   |      | 1    | μΑ        |

| CURRENT L             | IMIT                                      |                                                                                                                                     |      |      | •    |           |

|                       |                                           | $R_{(ILIM\_LO)} = 210 \text{ k}\Omega$                                                                                              | 205  | 255  | 305  |           |

|                       |                                           | $R_{(ILIM\_LO)} = 80.6 \text{ k}\Omega$                                                                                             | 600  | 660  | 720  |           |

|                       |                                           | $R_{(ILIM\_LO)} = 23.2 \text{ k}\Omega$                                                                                             | 2145 | 2300 | 2455 |           |

| Ios                   | OUT short-circuit current limit           | $R_{(ILIM\_HI)} = 20 \text{ k}\Omega$                                                                                               | 2500 | 2670 | 2840 | mA        |

|                       |                                           | $R_{(ILIM\_HI)} = 19.1 \text{ k}\Omega$                                                                                             | 2620 | 2800 | 2975 |           |

|                       |                                           | $R_{\text{(ILIM\_HI)}} = 15.4 \text{ k}\Omega$                                                                                      | 3255 | 3470 | 3685 |           |

|                       |                                           | R <sub>(ILIM_HI)</sub> shorted to GND                                                                                               | 5500 | 7000 | 8000 |           |

| SUPPLY CU             | RRENT                                     | ,                                                                                                                                   |      |      |      |           |

| I <sub>(IN_OFF)</sub> | Disabled IN supply current                | $V_{(EN)} = 0 \text{ V}, V_{(OUT)} = 0 \text{ V}, -40^{\circ}\text{C} \le T_{J} \le 85^{\circ}\text{C}$                             |      | 0.1  | 5    | μΑ        |

|                       |                                           | $V_{(CTL)1} = V_{(CTL2)} = V_{(CTL3)} = V_{(IN)}$                                                                                   |      | 220  | 300  |           |

| Lun on                | Enabled IN supply current                 | $V_{(CTL1)} = V_{(CTL2)} = 0 \text{ V}, V_{(CTL3)} = V_{(IN)}$                                                                      |      | 226  | 300  | μA        |

| I <sub>(IN_ON)</sub>  | Enabled III Supply culterit               | $V_{(CTL2)} = V_{(IN)}, V_{(CTL1)} = V_{(CTL3)} = 0 V$                                                                              |      | 150  | 220  | μΛ        |

|                       |                                           | $V_{(CTL1)} = V_{(IN)}, V_{(CTL2)} = V_{(CTL3)} = 0 V$                                                                              |      | 115  | 190  |           |

<sup>(1)</sup> Pulse-testing techniques maintain junction temperature close to ambient temperature. Thermal effects must be taken into account separately.

<sup>(2)</sup> These parameters are provided for reference only and do not constitute part of TI's published device specifications for purposes of TI's product warranty.

#### **Electrical Characteristics (continued)**

Unless otherwise noted,  $-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}$  and  $4.5 \text{ V} \le \text{V}_{\text{(IN)}} \le 6.5 \text{ V}, \text{V}_{\text{(EN)}} = \text{V}_{\text{(IN)}}, \text{V}_{\text{(CTL1)}} = \text{V}_{\text{(CTL2)}} = \text{V}_{\text{(IN)}}. \text{ R}_{\text{(FAULT)}} = \text{R}_{\text{(STATUS)}} = 10 \text{ k}\Omega, \text{ R}_{\text{(ILIM\_HI)}} = 19.1 \text{ k}\Omega, \text{ R}_{\text{(ILIM\_LO)}} = 80.6 \text{ k}\Omega. \text{ Positive currents are into pins. Typical values are at 25°C. All voltages are with respect to GND.}$

|                          | PARAMETER                                   | TEST CONDITIONS                                                     | MIN | TYP | MAX  | UNIT |

|--------------------------|---------------------------------------------|---------------------------------------------------------------------|-----|-----|------|------|

| UNDERVOLTA               | GE LOCKOUT, IN                              |                                                                     |     |     |      |      |

| V <sub>(UVLO)</sub>      | IN rising UVLO threshold voltage            |                                                                     | 3.9 | 4.1 | 4.3  | V    |

|                          | Hysteresis (3)                              | $T_J = 25$ °C                                                       |     | 100 |      | mV   |

| FAULT                    | ·                                           |                                                                     | ·   |     |      |      |

|                          | Output low voltage                          | I <sub>(FAULT)</sub> = 1 mA                                         |     |     | 100  | mV   |

|                          | Off-state leakage                           | V <sub>(FAULT)</sub> = 6.5 V                                        |     |     | 2    | μΑ   |

| STATUS                   |                                             |                                                                     |     |     |      |      |

|                          | Output low voltage                          | I <sub>(STATUS)</sub> = 1 mA                                        |     |     | 100  | mV   |

|                          | Off-state leakage                           | V <sub>(STATUS)</sub> = 6.5 V                                       |     |     | 2    | μΑ   |

| THERMAL SHU              | JTDOWN                                      |                                                                     | •   |     | •    |      |

| T <sub>(OTSD2)</sub>     | Thermal shutdown threshold                  |                                                                     | 155 |     |      | °C   |

| T <sub>(OTSD1)</sub>     | Thermal shutdown threshold in current-limit |                                                                     | 135 |     |      | °C   |

|                          | Hysteresis (3)                              |                                                                     |     | 20  |      | °C   |

| LOAD DETECT              | $(V_{CTL1} = V_{CTL2} = V_{CTL3} = V_{IN})$ |                                                                     | ·   |     |      |      |

| I <sub>(LD)</sub>        | I <sub>OUT</sub> load detection threshold   | $R_{(ILIM\_LO)}$ = 80.6 kΩ, rising load current                     | 630 | 700 | 770  | mA   |

|                          | Hysteresis (3)                              |                                                                     |     | 50  |      | mA   |

| DP_IN AND DN             | I_IN SHORT-TO-V <sub>BUS</sub> PROTEC       | CTION                                                               |     |     |      |      |

| V <sub>(OV)</sub>        | Overvoltage protection trip threshold       | DP_IN and DM_IN rising                                              | 3.7 | 3.9 | 4.15 | V    |

|                          | Hysteresis (3)                              |                                                                     |     | 100 |      | mV   |

| R <sub>(DCHG_Data)</sub> | Discharge resistance after OVP              | $V_{(DP\_IN)} = V_{(DM\_IN)} = 5 \text{ V}$                         | 160 | 210 | 240  | kΩ   |

| CABLE COMPI              | ENSATION                                    |                                                                     |     |     |      |      |

|                          |                                             | Load = 3 A, $2.5 \text{ V} \le \text{V}_{(CS)} \le 6.5 \text{ V}$   | 214 | 225 | 236  |      |

|                          | Cial aumant                                 | Load = 2.4 A, $2.5 \text{ V} \le \text{V}_{(CS)} \le 6.5 \text{ V}$ | 171 | 180 | 189  |      |

| I <sub>(CS)</sub>        | Sink current                                | Load = 2.1 A, 2.5 V $\leq$ V <sub>(CS)</sub> $\leq$ 6.5 V           | 149 | 158 | 166  | μA   |

|                          |                                             | Load = 1 A, 2.5 V ≤ V <sub>(CS)</sub> ≤ 6.5 V                       | 70  | 75  | 80   |      |

<sup>(3)</sup> These parameters are provided for reference only and do not constitute part of TI's published device specifications for purposes of TI's product warranty.

#### **Electrical Characteristics (continued)**

Unless otherwise noted,  $-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}$  and  $4.5 \text{ V} \le \text{V}_{(\text{IN})} \le 6.5 \text{ V}$ ,  $\text{V}_{(\text{EN})} = \text{V}_{(\text{IN})}$ ,  $\text{V}_{(\text{CTL1})} = \text{V}_{(\text{CTL2})} = \text{V}_{(\text{CTL3})} = \text{V}_{(\text{IN})}$ .  $\text{R}_{(\text{FAULT})} = \text{R}_{(\text{STATUS})} = 10 \text{ k}\Omega$ ,  $\text{R}_{(\text{ILIM\_HI})} = 19.1 \text{ k}\Omega$ ,  $\text{R}_{(\text{ILIM\_LO})} = 80.6 \text{ k}\Omega$ . Positive currents are into pins. Typical values are at 25°C. All voltages are with respect to GND.

|                            | PARAMETER                                                              | TEST CONDITIONS                                                                                                        | MIN  | TYP  | MAX  | UNIT  |

|----------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| HIGH-BANDWID               | TH ANALOG SWITCH                                                       |                                                                                                                        |      |      |      |       |

| D                          | DP and DM switch on-                                                   | $V_{(DP\_OUT)} = V_{(DM\_OUT)} = 0 \text{ V}, I_{(DP\_IN)} = I_{(DM\_IN)} = 0 \text{ M}$                               |      | 2    | 4    | 0     |

| R <sub>(HS_ON)</sub>       | resistance                                                             | $V_{(DP\_OUT)} = V_{(DM\_OUT)} = 2.4 \text{ V}, I_{(DP\_IN)} = I_{(DM\_IN)} = -15 \text{ mA}$                          |      | 2.9  | 6    | Ω     |

| IAD I                      | Switch resistance mismatch                                             | $V_{(DP\_OUT)} = V_{(DM\_OUT)} = 0 \text{ V}, I_{(DP\_IN)} = I_{(DM\_IN)} = 30 \text{ mA}$                             |      | 0.05 | 0.15 | 0     |

| $ \Delta R_{(HS\_ON)} $    | between DP and DM channels                                             | $V_{(DP\_OUT)} = V_{(DM\_OUT)} = 2.4 \text{ V}, I_{(DP\_IN)} = I_{(DM\_IN)} = -15 \text{ mA}$                          |      | 0.05 | 0.15 | Ω     |

| C <sub>(IO_OFF)</sub>      | DP/DM switch off-state capacitance (4)                                 | $V_{EN} = 0 \text{ V}, V_{(DP\_IN)} = V_{(DM\_IN)} = 0.3 \text{ V},$<br>$Vac = 0.03 \text{ V}_{PP}, f = 1 \text{ MHz}$ |      | 6.7  |      | pF    |

| C <sub>(IO_ON)</sub>       | DP/DM switch on-state capacitance <sup>(4)</sup>                       | $V_{(DP\_IN)} = V_{(DM\_IN)} = 0.3 \text{ V},$<br>Vac = 0.03 $V_{PP}$ , f = 1 MHz                                      |      | 10   |      | pF    |

|                            | Off-state isolation <sup>(4)</sup>                                     | V <sub>EN</sub> = 0 V, f = 250 MHz                                                                                     |      | 27   |      | dB    |

|                            | On-state cross-channel isolation (4)                                   | f = 250 MHz                                                                                                            |      | 23   |      | dB    |

| I <sub>lkg(OFF)</sub>      | Off-state leakage current, DP_OUT and DM_OUT                           | $V_{EN} = 0 \text{ V}, V_{(DP\_IN)} = V_{(DM\_IN)} = 3.6 \text{ V}, V_{(DP\_OUT)}$<br>= $V_{(DM\_OUT)} = 0 \text{ V}$  |      | 0.1  | 1.5  | μΑ    |

| BW                         | Bandwidth (-3 dB) <sup>(4)</sup>                                       | $R_{(L)} = 50 \Omega$                                                                                                  |      | 925  |      | MHz   |

| CHARGING DOV               | WNSTREAM PORT DETECT                                                   |                                                                                                                        |      |      |      |       |

| $V_{(DM\_SRC)}$            | DM_IN CDP output voltage                                               | $V_{(DP_{-}IN)} = 0.6 \text{ V}, -250  \mu\text{A} < I_{(DM_{-}IN)} < 0  \mu\text{A}$                                  | 0.5  | 0.6  | 0.7  | >     |

| $V_{(DAT\_REF)}$           | DP_IN rising lower window threshold for V <sub>DM_SRC</sub> activation |                                                                                                                        | 0.36 |      | 0.4  | ٧     |

|                            | Hysteresis (4)                                                         |                                                                                                                        |      | 50   |      | mV    |

| V <sub>(LGC_SRC)</sub>     | DP_IN rising upper window threshold for VDM_SRC de-activation          |                                                                                                                        | 0.8  |      | 0.88 | ٧     |

| V <sub>(LGC_SRC_HYS)</sub> | Hysteresis (4)                                                         |                                                                                                                        |      | 100  |      | mV    |

| I <sub>(DP_SINK)</sub>     | DP_IN sink current                                                     | V <sub>(DP_IN)</sub> = 0.6 V                                                                                           | 40   | 75   | 100  | μΑ    |

| BC1.2 DCP MOD              | DE                                                                     |                                                                                                                        |      |      |      |       |

| R <sub>(DPM_SHORT)</sub>   | DP_IN and DM_IN shorting resistance                                    |                                                                                                                        |      | 125  | 200  | Ω     |

| DIVIDER3 MODE              | <b>.</b>                                                               |                                                                                                                        |      |      |      |       |

| V <sub>(DP_DIV3)</sub>     | DP_IN output voltage                                                   |                                                                                                                        | 2.57 | 2.7  | 2.84 | V     |

| V <sub>(DM_DIV3)</sub>     | DM_IN output voltage                                                   |                                                                                                                        | 2.57 | 2.7  | 2.84 | V     |

| R <sub>(DP_DIV3)</sub>     | DP_IN output impedance                                                 | $I_{(DP\_IN)} = -5 \mu A$                                                                                              | 24   | 30   | 36   | kΩ    |

| $R_{(DM\_DIV3)}$           | DM_IN output impedance                                                 | $I_{(DM\_IN)} = -5 \mu A$                                                                                              | 24   | 30   | 36   | kΩ    |

| 1.2-V MODE                 |                                                                        |                                                                                                                        |      |      |      |       |

| V <sub>(DP_1.2V)</sub>     | DP_IN output voltage                                                   |                                                                                                                        | 1.12 | 1.2  | 1.26 | V     |

| $V_{(DM\_1.2V)}$           | DM_IN output voltage                                                   |                                                                                                                        | 1.12 | 1.2  | 1.26 | ٧     |

| R <sub>(DP_1.2V)</sub>     | DP_IN output impedance                                                 | $I_{(DP\_IN)} = -5 \mu A$                                                                                              | 84   | 100  | 126  | kΩ    |

| $R_{(DM\_1.2V)}$           | DM_IN output impedance                                                 | $I_{(DM\_IN} = -5 \mu A$                                                                                               | 84   | 100  | 126  | 1/2.2 |

<sup>(4)</sup> These parameters are provided for reference only and do not constitute part of TI's published device specifications for purposes of TI's product warranty.

#### 6.6 Switching Characteristics

Unless otherwise noted  $-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}$  and  $4.5 \text{ V} \le \text{V}_{\text{(IN)}} \le 6.5 \text{ V}, \text{V}_{\text{(EN)}} = \text{V}_{\text{(IN)}}, \text{V}_{\text{(CTL1)}} = \text{V}_{\text{(CTL2)}} = \text{V}_{\text{(CTL3)}} = \text{V}_{\text{(IN)}}. \text{ R}_{\text{(FAULT)}} = \text{R}_{\text{(STATUS)}} = 10 \text{ k}\Omega, \text{ R}_{\text{(ILIM\_HI)}} = 19.1 \text{ k}\Omega, \text{ R}_{\text{(ILIM\_LO)}} = 80.6 \text{ k}\Omega. \text{ Positive current is into pins. Typical value is at 25°C. All voltages are with respect to GND.}$

| F                       | PARAMETER                                                                                               | TEST CONDITIONS                                                                                    | MIN | TYP  | MAX  | UNIT |

|-------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----|------|------|------|

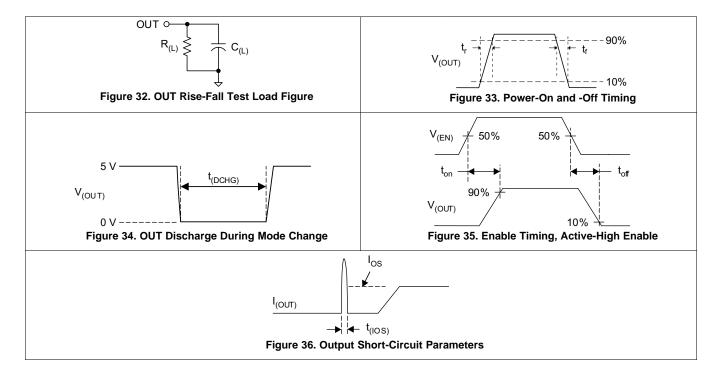

| t <sub>r</sub>          | OUT voltage rise time                                                                                   | $V_{(IN)} = 5 \text{ V}, C_{(L)} = 1 \mu\text{F}, R_{(L)} = 100 \Omega \text{ (see}$               | 0.7 | 1.14 | 2    | ms   |

| t <sub>f</sub>          | OUT voltage fall time                                                                                   | Figure 32 and Figure 33)                                                                           | 0.2 | 0.35 | 0.6  | ms   |

| t <sub>on</sub>         | OUT voltage turnon time                                                                                 | $V_{(IN)} = 5 \text{ V, } C_{(L)} = 1  \mu\text{F, } R_{(L)} = 100 \Omega \text{ (see}$            |     | 4.15 | 6    | ms   |

| t <sub>off</sub>        | OUT voltage turnoff time                                                                                | Figure 32 and Figure 35)                                                                           |     | 1.8  | 3    | ms   |

| t(DCHG_L)               | Long OUT discharge hold<br>time (SDP, CDP, or client<br>mode to DCP_Auto)                               | Time V <sub>(OUT)</sub> < 0.7 V (see Figure 34)                                                    | 1.1 | 2    | 2.9  | s    |

| t(DCHG_S)               | Short OUT discharge hold time (DCP_Auto to SDP, CDP, or client mode)                                    | Time V <sub>(OUT)</sub> < 0.7 V (see Figure 34)                                                    | 186 | 320  | 450  | ms   |

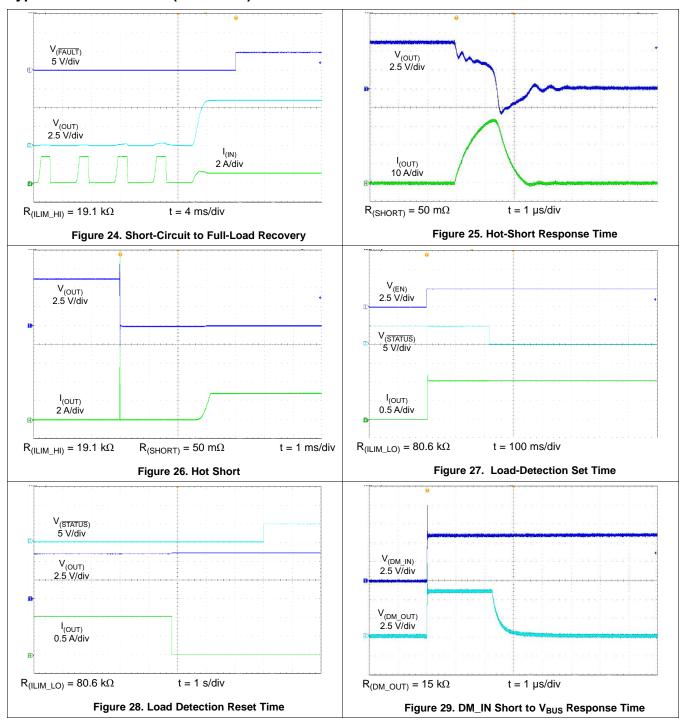

| t <sub>(IOS)</sub>      | OUT short-circuit response time (1)                                                                     | $V_{(IN)} = 5 \text{ V}, R_{(SHORT)} = 50 \text{ m}\Omega \text{ (see Figure 25)}$                 |     | 2    |      | μs   |

| t(OC_OUT_FAULT)         | OUT FAULT deglitch time                                                                                 | Bidirectional deglitch applicable to current limit condition only (no deglitch assertion for OTSD) | 5.5 | 8    | 11.5 | ms   |

| t <sub>pd</sub>         | Analog switch propagation delay (1)                                                                     | V <sub>(IN)</sub> = 5 V                                                                            |     | 0.14 |      | ns   |

| t <sub>(SK)</sub>       | Analog switch skew between opposite transitions of the same port $\left(t_{PHL} - t_{PLH}\right)^{(1)}$ | V <sub>(IN)</sub> = 5 V                                                                            |     | 0.02 |      | ns   |

| t <sub>(LD_SET)</sub>   | Load-detect set time                                                                                    | V <sub>(IN)</sub> = 5 V (See Figure 27)                                                            | 120 | 210  | 280  | ms   |

| t <sub>(LD_RESET)</sub> | Load-detect reset time                                                                                  | V <sub>(IN)</sub> = 5 V (See Figure 28)                                                            | 1.8 | 3    | 4.2  | s    |

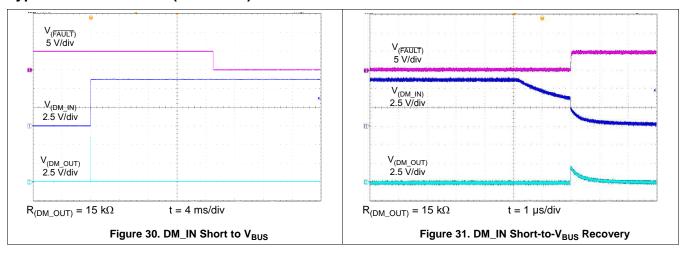

| t <sub>(OV_D)</sub>     | DP_IN and DM_IN over-<br>voltage protection response<br>time                                            | V <sub>(OUT)</sub> = 5 V (See Figure 29)                                                           |     | 2    |      | μs   |

| t(OV_D_FAULT)           | DP_IN and DM_IN FAULT degltich time                                                                     | V <sub>(OUT)</sub> = 5 V (See Figure 30)                                                           | 11  | 16   | 23   | ms   |

<sup>(1)</sup> These parameters are provided for reference only and do not constitute part of TI's published device specifications for purposes of TI's product warranty.

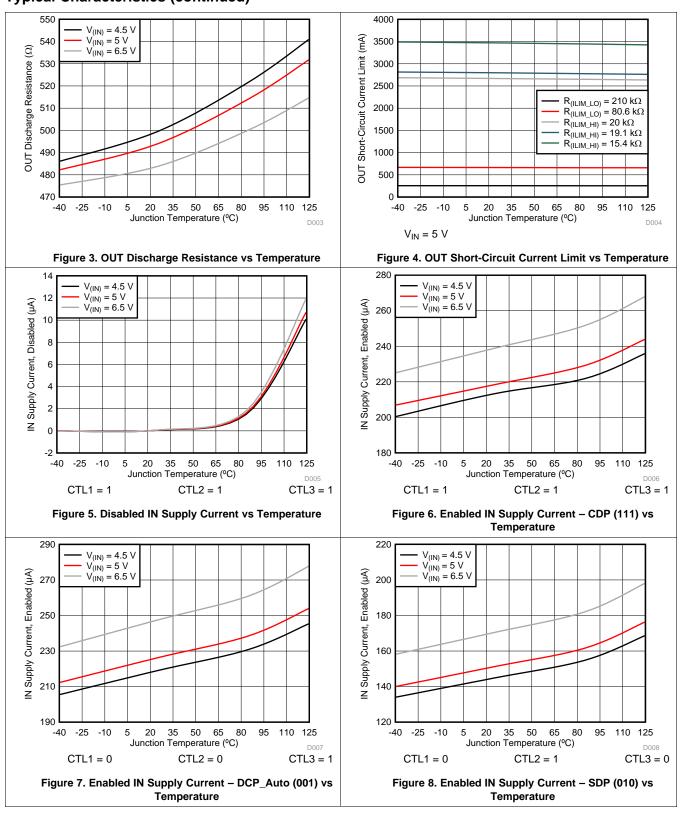

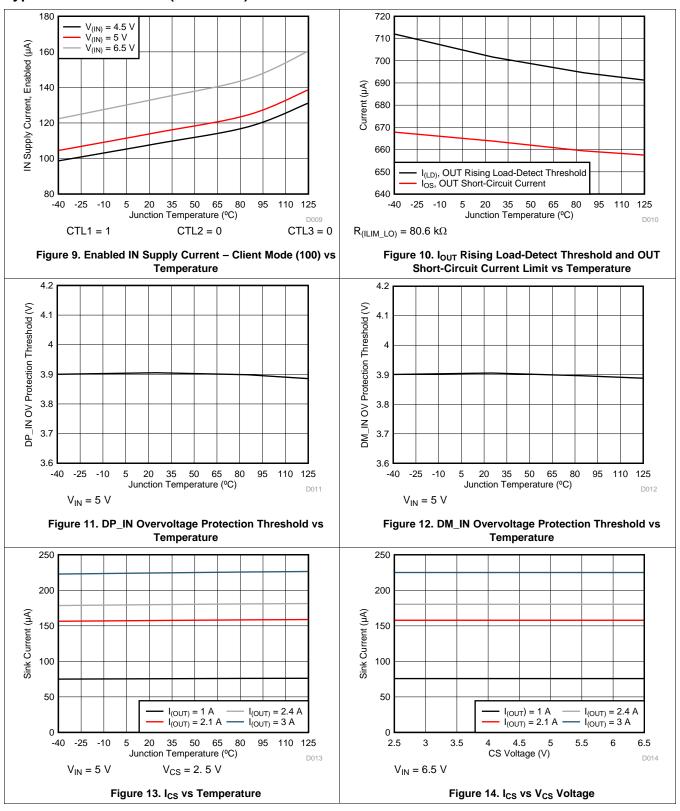

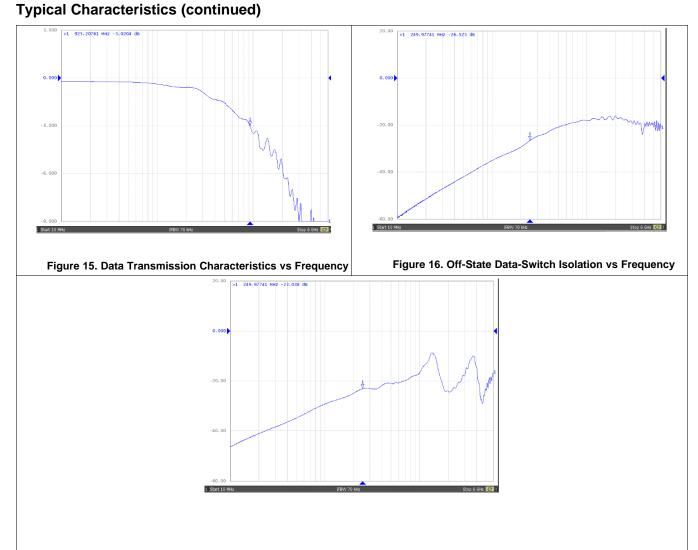

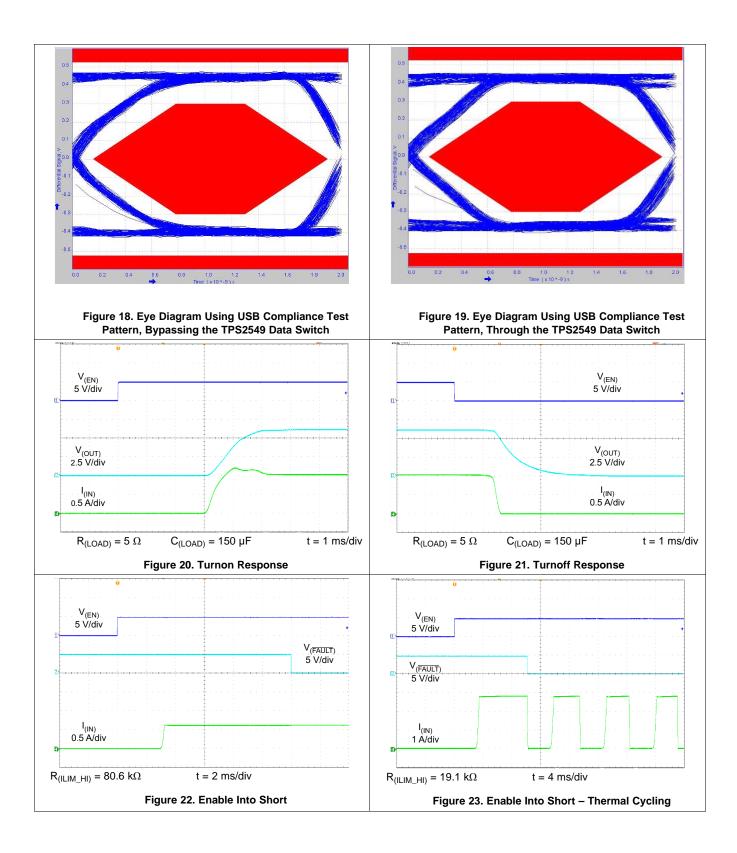

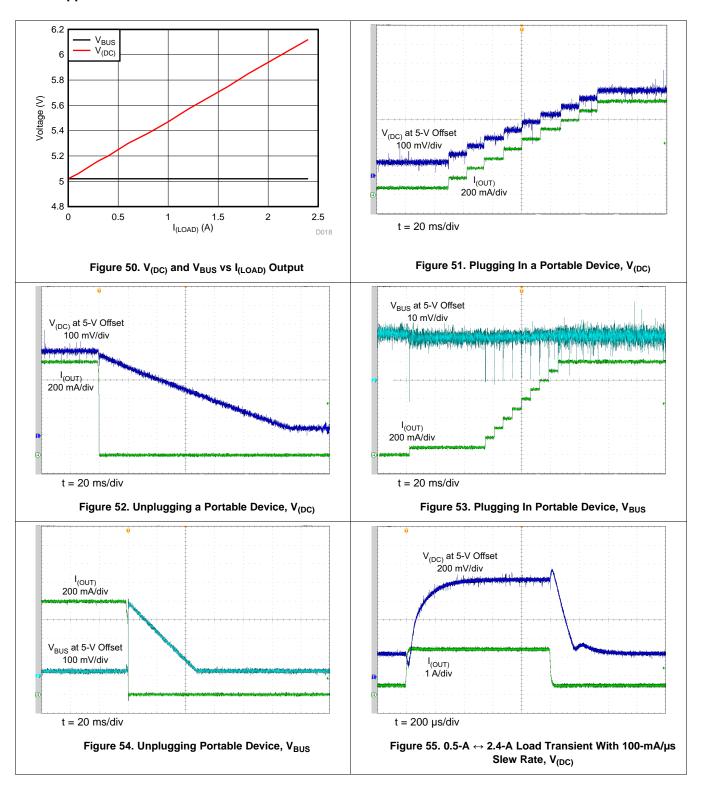

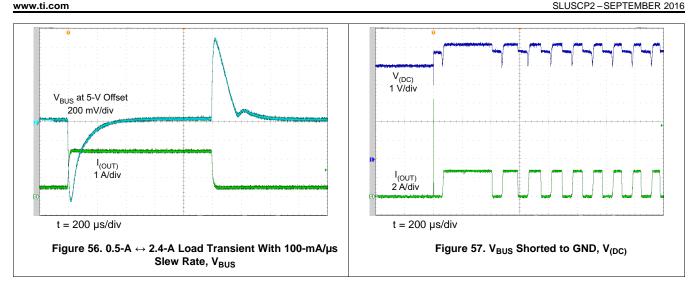

#### 6.7 Typical Characteristics

www.ti.com

### **Typical Characteristics (continued)**

#### **Typical Characteristics (continued)**

Submit Documentation Feedback

Copyright © 2016, Texas Instruments Incorporated

www.ti.com

Figure 17. On-State Cross-Channel Isolation vs Frequency

Copyright © 2016, Texas Instruments Incorporated

#### **Typical Characteristics (continued)**

#### **Typical Characteristics (continued)**

#### **Typical Characteristics (continued)**

#### 7 Parameter Measurement Information

Submit Documentation Feedback

#### 8 Detailed Description

#### 8.1 Overview

www.ti.com

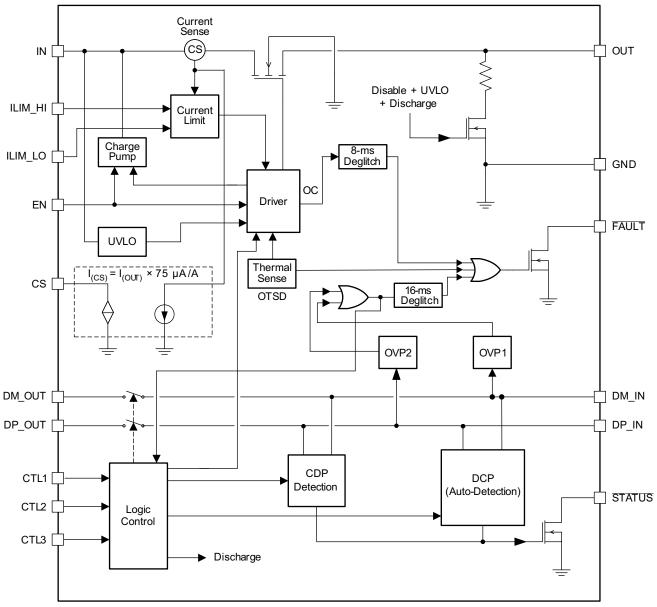

The TPS2549 device is a USB charging controller and power switch which integrates D+ and D- short to  $V_{BUS}$  protection, cable compensation and IEC ESD protection, and is suitable for USB charging and USB port-protection applications.

The TPS2549 device integrates a current-limited, power-distribution switch using N-channel MOSFETs for applications where short circuits or heavy capacitive loads can be encountered. The device allows the user to program the current-limit threshold via an external resistor. The device enters constant-current mode when the load exceeds the current limit threshold.

The TPS2549 device also integrates CDP mode, defined in the BC1.2 specification, to enable up to 1.5-A fast charging of most of portable devices, meanwhile supporting data communication. In addition, the device integrates the DCP-auto feature to enable fast-charging of most portable devices including pads, tablets, and smart phones.

The TPS2549 device integrates a cable compensation (CS) feature to compensate the voltage drop in long cables and keep the remote USB port output voltage constant.

Additionally, the device integrates an IEC ESD cell to provide ESD protection up to  $\pm 8$  kV (contact discharge) and  $\pm 15$  kV (air discharge) per IEC 61000-4-2 on DP\_IN and DM\_IN, and integrates short-to-V<sub>BUS</sub> overvoltage protection on DP\_IN and DM\_IN to protect the upstream USB transceiver.

#### 8.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

#### 8.3 Feature Description

#### 8.3.1 FAULT Response

The device features an active-low, open-drain fault output.  $\overline{\mathsf{FAULT}}$  goes low when there is a fault condition. Fault detection includes overtemperature, overcurrent, or DP\_IN, DM\_IN overvoltage. Connect a 10-k $\Omega$  pullup resistor from FAULT to IN.

Table 1 summarizes the conditions that generate a fault and actions taken by the device.

**Table 1. Fault Conditions**

| EVENT                             | CONDITION                                                                      | ACTION                                                                                                                                                                                                                                                                 |

|-----------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Overcurrent on V <sub>(OUT)</sub> | I <sub>(OUT)</sub> > I <sub>OS</sub>                                           | The device regulates switch current at I <sub>OS</sub> until thermal cycling occurs. The fault indicator asserts and de-asserts with an 8-ms deglitch (The device does not assert FAULT on overcurrent in SDP1 and DCP1 modes).                                        |

| Overvoltage on the data lines     | DP_IN or DM_IN > 3.9 V                                                         | The device immediately shuts off the USB data switches. The fault indicator asserts with a 16-ms deglitch, and deasserts without deglitch.                                                                                                                             |

| Overtemperature                   | $T_J > OTSD2$ in non-current-limited or $T_J > OTSD1$ in current-limited mode. | The device immediately shuts off the internal power switch and the USB data switches. The fault indicator asserts immediately when the junction temperature exceeds OTSD2 or OTSD1 while in a current-limiting condition. The device has a thermal hysteresis of 20°C. |

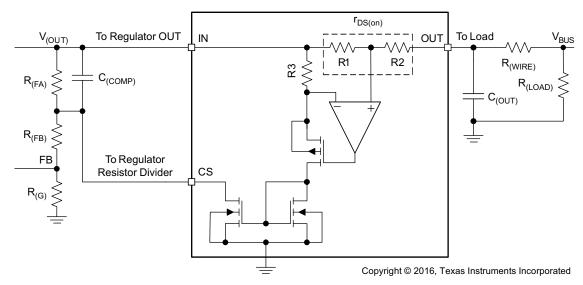

#### 8.3.2 Cable Compensation

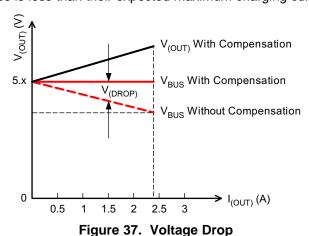

When a load draws current through a long or thin wire, there is an IR drop that reduces the voltage delivered to the load. In the vehicle from the voltage regulator 5-V output to the VPD\_IN (input voltage of portable device), the total resistance of power switch  $r_{DS(on)}$  and cable resistance causes an IR drop at the PD input.. So the charging current of most portable devices is less than their expected maximum charging current.

TPS2549 device detects the load current and generates a proportional sink current that can be used to adjust output voltage of the upstream regulator to compensate the IR drop in the charging path. The gain  $G_{(CS)}$  of the sink current proportional to load current is 75  $\mu$ A/A.

Figure 38. Cable Compensation Equivalent Circuit

#### 8.3.2.1 Design Procedure

To start the procedure, the total resistance, including power switch  $r_{DS(on)}$  and wire resistance  $R_{(WIRE)}$ , must to be known.

- 1. Choose R<sub>(G)</sub> following the voltage-regulator feedback resistor-divider design guideline.

- 2. Calculate R<sub>(FA)</sub> according to Equation 1.

$$R_{FA} = (r_{DS(on)} + R_{(WIRE)}) / G_{(CS)}$$

(1)

3. Calculate R<sub>(FB)</sub> according to Equation 2.

$$R_{(FB)} = \frac{V_{(OUT)}}{V_{(FB)} / R_{(G)}} - R_{(G)} - R_{(FA)}$$

(2)

4.  $C_{(COMP)}$  in parallel with  $R_{(FA)}$  is needed to stablilize  $V_{(OUT)}$  when  $C_{(OUT)}$  is large. Start with  $C_{(COMP)} \ge 3 \times G_{(CS)} \times C_{(OUT)}$ , then adjust  $C_{(COMP)}$  to optimize the load transient of the voltage regulator output.  $V_{(OUT)}$  stability should always be verified in the end application circuit.

#### 8.3.3 D+ and D- Protection

D+ and D- protection consists of ESD and OVP (overvoltage protection). The DP\_IN and DM\_IN pins integrate an IEC ESD cell to provide ESD protection up to ±15 kV air discharge and ±8 kV contact discharge per IEC 61000-4-2 (See the *ESD Ratings* section for test conditions). Overvoltage protection (OVP) is provided for short-to-V<sub>BUS</sub> conditions in the vehicle harness to prevent damaging the upstream USB transceiver. Short-to-GND protection for D+ and D- is provided by the upstream USB transceiver.

The ESD stress seen at DP\_IN and DM\_IN is impacted by many external factors like the parasitic resistance and inductance between ESD test points and the DP\_IN and DM\_IN pins. For air discharge, the temperature and humidity of the environment can cause some difference, so the IEC performance should always be verified in the end-application circuit.

#### 8.3.4 Output and D+ or D- Discharge

To allow a charging port to renegotiate current with a portable device, the TPS2549 device uses the OUT discharge function. This function turns off the power switch while discharging OUT with a  $500-\Omega$  resistance, then turns the power switches to back on reassert the OUT voltage.

For DP\_IN and DM\_IN, when OVP is triggered, the device turns on an internal discharge path with  $210-\Omega$  resistance. On removal of OVP, this path can discharge the remnant charges to automatically turn on analog switch and turn off this discharge path, thus back into normal mode.

www.ti.com

005 D (D 14 //D

#### 8.3.5 Port Power Management (PPM)

PPM is the intelligent and dynamic allocation of power. PPM is for systems that have multiple charging ports but cannot power them all simultaneously.

#### 8.3.5.1 Benefits of PPM

The benefits of PPM include the following:

- Delivers better user experience

- Prevents overloading of system power supply

- Allows for dynamic power limits based on system state

- Allows every port to potentially be a high-power charging port

- Allows for smaller power-supply capacity because loading is controlled

#### 8.3.5.2 PPM Details

All ports are <u>allowed</u> to broadcast high-current charging. The current-limit is based on ILIM\_HI. The system <u>monitors</u> the <u>STATUS</u> pin to see when high-current loads are present. Once the allowed number of ports asserts <u>STATUS</u>, the remaining ports are toggled to a non-charging port. The non-charging port current-limit is based on the ILIM\_LO setting. The non-charging ports are automatically toggled back to charging ports when a charging port de-asserts <u>STATUS</u>.

<u>STATUS</u> asserts in a charging port when the load current is above ILIM\_LO + 40 mA for 210 ms (typical). STATUS de-asserts in a charging-port when the load current is below ILIM\_LO - 10 mA for 3 seconds (typical).

SLUSCP2 – SEPTEMBER 2016 www.ti.com

# TEXAS INSTRUMENTS

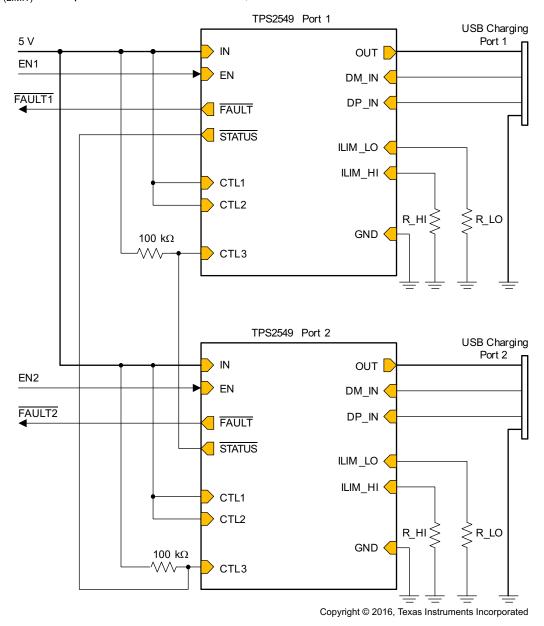

#### 8.3.5.3 Implementing PPM in a System With Two Charging Ports (CDP and SDP1)

Figure 39 shows the implementation of the two charging ports with data communication, each with a TPS2549 device and configured in CDP mode. In this example, the 5-V power supply for the two charging ports is rated at less than 3.5 A. Both TPS2549 devices have ILIM\_LO of 1 A and ILIM\_HI of 2.4 A. In this implementation, the system can support only one of the two ports at 2.4-A charging current, whereas the other port is set to SDP1 mode and  $I_{(LIMIT)}$  corresponds to 1 A. In SDP1 mode, FAULT does not assert for overcurrent.

Figure 39. PPM With CDP and SDP1

www.ti.com

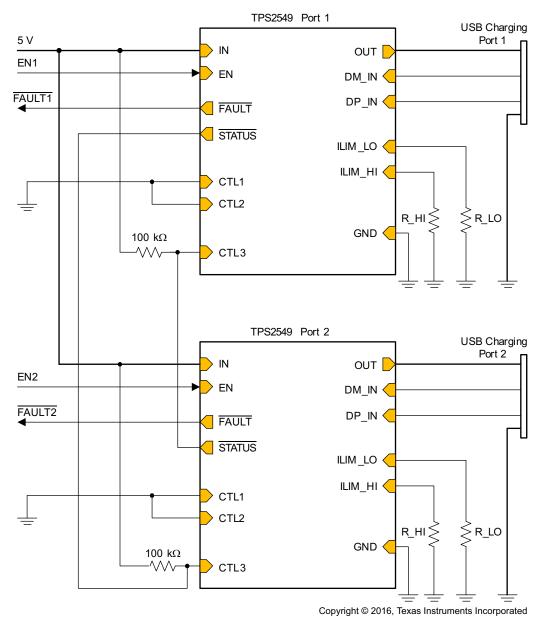

#### 8.3.5.4 Implementing PPM in a System With Two Charging Ports (DCP and DCP1)

Figure 40 shows the implementation of the two charging-only ports, each with a TPS2549 device and configured in DCP mode. In this example, the 5-V power supply for the two charging ports is rated at less than 3.5 A. Both TPS2549 devices have ILIM LO of 1 A and ILIM HI of 2.4 A. In this implementation, the system can support only one of the two ports at 2.4-A charging current, whereas the other port is set to DCP1 mode and I<sub>(LMIT)</sub> corresponds to 1 A. In DCP1 mode, FAULT does not assert for overcurrent.

Figure 40. PPM With DCP and DCP1

#### 8.3.6 CDP and SDP Auto Switch

Copyright © 2016, Texas Instruments Incorporated

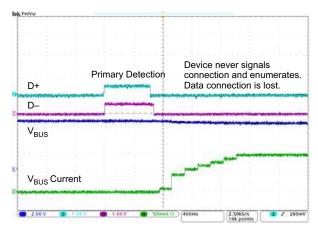

The TPS2549 device is equipped with a CDP and SDP auto-switch feature to support some popular phones in the market. These popular phones do not comply with the BC1.2 specification because they fail to establish a data connection in CDP mode. These phones use primary detection (used to distinguish between an SDP and different types of charging ports) to only identify ports as SDP (data, no charge) or DCP (no data, charge). These phones do not recognize CDP (data, charge) ports. When connected to a CDP port, these phones classify the port as a DCP and only charge the battery. Because the charging ports are configured as CDP, users do not receive the expected data connection.

Figure 41. CDP and SDP Auto-Switch

To remedy this problem, the TPS2549 device employs a CDP and SDP auto-switch scheme to ensure these BC1.2 noncompliant phones establish data connection using the following steps.

- 1. The TPS2549 device determines when a noncompliant phone has wrongly classified a CDP port as a DCP port and has not made a data connection.

- 2. The TPS2549 device automatically completes an OUT ( $V_{BUS}$ ) discharge and reconfigures the port as an SDP.

- 3. When reconfigured as an SDP, the phone detects a connection to an SDP and establishes a data connection.

- 4. The TPS2549 device then switches automatically back to a CDP without doing an OUT (V<sub>BUS</sub>) discharge.

- 5. The phone continues to operate as if connected to an SDP because OUT (V<sub>BUS</sub>) was not interrupted. The port is now ready in CDP if a new device is attached.

#### 8.3.7 Overcurrent Protection

When an overcurrent condition is detected, the device maintains a constant output current and reduces the output voltage accordingly. Two possible overload conditions can occur. In the first condition, the output is shorted before the device enables or before the application of  $V_{(IN)}$ . The TPS2549 device senses the short and immediately switches into a constant-current output. In the second condition, a short or an overload occurs while the device is enabled. At the instant the overload occurs, high currents flow for 2  $\mu$ s (typical) before the current-limit circuit reacts. The device operates in constant-current mode after the current-limit circuit has responded. Complete shutdown occurs only if the fault is presented long enough to activate overtemperature protection. The device remains off until the junction temperature cools to approximately 20°C and then restarts. The device continues to cycle on and off until the overcurrent condition is removed.

#### 8.3.8 Undervoltage Lockout

The undervoltage-lockout (UVLO) circuit disables the device until the input voltage reaches the UVLO turnon threshold. Built-in hysteresis prevents unwanted oscillations on the output due to input voltage drop from large current surges.

#### 8.3.9 Thermal Sensing

Two independent thermal-sensing circuits protect the TPS2549 device if the temperature exceeds recommended operating conditions. These circuits monitor the operating temperature of the power-distribution switch and disable operation. The device operates in constant-current mode during an overcurrent condition, which increases the voltage drop across power switch. The power dissipation in the package is proportional to the voltage drop across the power switch, so the junction temperature rises during an overcurrent condition. When the device is in a current-limiting condition, the first thermal sensor turns off the power switch when the die

temperature exceeds OTSD1. If the device is not in a current-limiting condition, the second thermal sensor turns off the power switch when the die temperature exceeds OTSD2. Hysteresis is built into both thermal sensors, and the switch turns on after the device has cooled by approximately 20°C. The switch continues to cycle off and then on until the fault is removed. The open-drain false-reporting output, FAULT, is asserted (low) during an overtemperature shutdown condition.

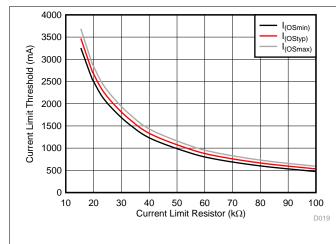

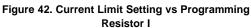

#### 8.3.10 Current Limit Setting

The TPS2549 has two independent current-limit settings that are each programmed externally with a resistor. The ILIM\_HI setting is programmed with  $R_{(ILIM\_HI)}$  connected between ILIM\_HI and GND. The ILIM\_LO setting is programmed with  $R_{(ILIM\_LO)}$  connected between ILIM\_LO and GND. Consult the device truth table (Table 2) to see when each current limit is used. Both settings have the same relation between the current limit and the programming resistor.

R<sub>(ILIM LO)</sub> is optional and the ILIM\_LO pin may be left unconnected if the following conditions are met:

- The TPS2549 device is configured as DCP(001) or CDP(111).

- Load detection is not used.

The following equation calculates the value of resistor for programming the typical current limit:

$$I_{(OSnom)}(mA) = \frac{53762 (V)}{R_{(ILIM_xx)}^{1.0021} (k\Omega)}$$

(3)

$R_{(ILIM\_xx)}$  corresponds to either  $R_{(ILIM\_HI)}$  or  $R_{(ILIM\_LO)}$ , as appropriate.

Many applications require that the current limit meet specific tolerance limits. When designing to these tolerance limits, both the tolerance of the TPS2549 current limit and the tolerance of the external programming resistor must be taken into account. The following equations approximate the TPS2549 minimum and maximum current limits to within a few milliamperes and are appropriate for design purposes. The equations do not constitute part of TI's published device specifications for purposes of TI's product warranty. These equations assume an ideal—no variation—external programming resistor. To take resistor tolerance into account, first determine the minimum and maximum resistor values based on its tolerance specifications and use these values in the equations. Because of the inverse relation between the current limit and the programming resistor, use the maximum resistor value in the  $I_{(OS\ min)}$  equation and the minimum resistor value in the  $I_{(OS\ max)}$  equation.

$$I_{(OSmin)} (mA) = \frac{50409 (V)}{R_{(ILIM_{xx})}^{0.9982} (k\Omega)} - 35$$

$$I_{(OSmax)} (mA) = \frac{57813 (V)}{R_{(ILIM_{xx})}^{1.0107} (k\Omega)} + 41$$

(5)

$$I_{(OSmax)} (mA) = \frac{37613 (V)}{R_{(ILIM_xx)}^{1.0107} (k\Omega)} + 41$$

(5)

Figure 43. Current Limit Setting vs Programming Resistor II

The routing of the traces to the  $R_{(ILIM\_xx)}$  resistors should have a sufficiently low resistance so as to not affect the current-limit accuracy. The ground connection for the  $R_{(ILIM\_xx)}$  resistors is also very important. The resistors must reference back to the TPS2549 GND pin. Follow normal board layout practices to ensure that current flow from other parts of the board does not impact the ground potential between the resistors and the TPS2549 GND pin.

#### 8.4 Device Functional Modes

#### 8.4.1 Device Truth Table (TT)

The device truth table (Table 2) lists all valid combinations for the three control pins (CTL1 through CTL3), and the corresponding charging mode of each pin combination. The TPS2549 device monitors the CTL inputs and transitions to whichever charging mode it is commanded to go to. For example, if the USB port is a charging-only port, then the user must set the CTL pins of the TPS2549 device to correspond to the DCP-auto charging mode. However, when the USB port requires data communication, then the user must set control pins to correspond to the SDP or CDP mode, and so on.

**STATUS FAULT** CURRENT OUTPUT **OUTPUT CS FOR CABLE** CTL1 CTL2 CTL3 LIMIT MODE NOTES (ACTIVE-(ACTIVE-COMPENSATION **SETTING** LOW) LOW) 0 DCP1<sup>(1)</sup> OFF ON<sup>(2)</sup> ON DCP includes divider 3. 0 0 Lo 1.2-V mode, and BC1.2 mode DCP(1) 0 Hi ON DCP includes divider 3. n 1 ON ON 1.2-V mode, and BC1.2 mode Χ SDP OFF ON Standard SDP port 0 1 Lo ON No current limit, power 0 Χ 1 NA Client mode **OFF OFF OFF** switch disabled, data switch bypassed ON<sup>(2)</sup> SDP1 (3) **OFF** ON Standard SDP port 1 1 0 Lo CDP(3) 1 1 1 Hi ON ON ON CDP-SDP auto switch mode

**Table 2. Truth Table**

#### 8.4.2 USB Specification Overview

The following overview references various industry standards. TI recommends consulting the most up-to-date standards to ensure the most recent and accurate information. Rechargeable portable equipment requires an external power source to charge batteries. USB ports are a convenient location for charging because of an available 5-V power source. Universally accepted standards are required to ensure host and client-side devices operate together in a system to ensure power-management requirements are met. Traditionally, host ports following the USB-2.0 specification must provide at least 500 mA to downstream client-side devices. Because multiple USB devices can be attached to a single USB port through a bus-powered hub, the client-side device sets the power allotment from the host to ensure the total current draw does not exceed 500 mA. In general, each USB device is granted 100 mA and can request more current in 100-mA unit steps up to 500 mA. The host grants or denies additional current based on the available current. A USB-3.0 host port not only provides higher data rate than a USB-2.0 port but also raises the unit load from 100 mA to 150 mA. Providing a minimum current of 900 mA to downstream client-side devices is required.

Additionally, the success of USB has made the micro-USB and mini-USB connectors a popular choice for wall-adapter cables. A micro-USB or mini-USB allows a portable device to charge from both a wall adapter and USB port with only one connector. As USB charging has gained popularity, the 500-mA minimum defined by USB 2.0, or 900 mA for USB 3.0, has become insufficient for many handset and personal media players, which require a higher charging rate. Wall adapters provide much more current than 500 or 900 mA. Several new standards have been introduced defining protocol handshaking methods that allow host and client devices to acknowledge and draw additional current beyond the 500-mA and 900-mA minimum defined by USB 2.0 and USB 3.0, respectively, while still using a single micro-USB or mini-USB input connector.

<sup>(1)</sup> No OUT discharge when changing between 000 and 001

<sup>(2)</sup> FAULT not asserted on overcurrent

<sup>(3)</sup> No OUT discharge when changing between 110 and 111

SLUSCP2-SEPTEMBER 2016

The TPS2549 device supports four of the most-common USB-charging schemes found in popular hand-held media and cellular devices.

- USB Battery Charging Specification BC1.2

- Chinese Telecommunications Industry Standard YD/T 1591-2009

- Divider 3 mode

- 1.2-V mode

The BC1.2 specification includes three different port types:

- Standard downstream port (SDP)

- Charging downstream port (CDP)

- Dedicated charging port (DCP)

BC1.2 defines a charging port as a downstream-facing USB port that provides power for charging portable equipment. Under this definition, CDP and DCP are defined as charging ports.

Table 3 lists the difference between these port types.

**Table 3. Operating Modes Table**

| PORT TYPE     | SUPPORTS USB2.0 COMMUNICATION | MAXIMUM ALLOWABLE CURRENT<br>DRAWN BY PORTABLE EQUIPMENT (A) |

|---------------|-------------------------------|--------------------------------------------------------------|

| SDP (USB 2.0) | YES                           | 0.5                                                          |

| SDP (USB 3.0) | YES                           | 0.9                                                          |

| CDP           | YES                           | 1.5                                                          |

| DCP           | NO                            | 1.5                                                          |

#### 8.4.3 Standard Downstream Port (SDP) Mode — USB 2.0 and USB 3.0

An SDP is a traditional USB port that follows USB 2.0 or USB 3.0 protocol. A USB 2.0 SDP supplies a minimum of 500 mA per port and supports USB 2.0 communications. A USB 3.0 SDP supplies a minimum of 900 mA per port and supports USB 3.0 communications. For both types, the host controller must be active to allow charging.

#### 8.4.4 Charging Downstream Port (CDP) Mode

A CDP is a USB port that follows USB BC1.2 and supplies a minimum of 1.5 A per port. A CDP provides power and meets the USB 2.0 requirements for device enumeration. USB-2.0 communication is supported, and the host controller must be active to allow charging. The difference between CDP and SDP is the host-charge handshaking logic that identifies this port as a CDP. A CDP is identifiable by a compliant BC1.2 client device and allows for additional current draw by the client device.

The CDP handshaking process occurs in two steps. During step one, the portable equipment outputs a nominal 0.6-V output on the D+ line and reads the voltage input on the D- line. The portable device detects the connection to an SDP if the voltage is less than the nominal data-detect voltage of 0.3 V. The portable device detects the connection to a CDP if the D- voltage is greater than the nominal data detect voltage of 0.3 V and optionally less than 0.8 V.

The second step is necessary for portable equipment to determine whether the equipment is connected to a CDP or a DCP. The portable device outputs a nominal 0.6-V output on the D-line and reads the voltage input on the D+ line. The portable device concludes the equipment is connected to a CDP if the data line being read remains less than the nominal data detects voltage of 0.3 V. The portable device concludes it is connected to a DCP if the data line being read is greater than the nominal data detect voltage of 0.3 V.

#### 8.4.5 Dedicated Charging Port (DCP) Mode

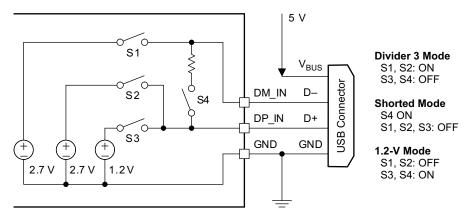

A DCP only provides power and does not support data connection to an upstream port. As shown in the following sections, a DCP is identified by the electrical characteristics of the data lines. The TPS2549 only emulates one state, DCP-auto state. In the DCP-auto state, the device charge-detection state machine is activated to selectively implement charging schemes involved with the shorted, divider3 and 1.2 v modes. The shorted DCP mode complies with BC1.2 and Chinese Telecommunications Industry Standard YD/T 1591-2009, whereas the divider3 and 1.2 V modes are employed to charge devices that do not comply with the BC1.2 DCP standard.

SLUSCP2 – SEPTEMBER 2016 www.ti.com

#### 8.4.5.1 DCP BC1.2 and YD/T 1591-2009

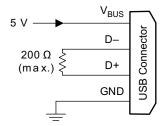

Both standards specify that the D+ and D- data lines must be connected together with a maximum series impedance of 200  $\Omega$ , as shown in Figure 44.

Figure 44. DCP Supporting BC1.2 and YD/T 1591-2009

#### 8.4.5.2 DCP Divider-Charging Scheme

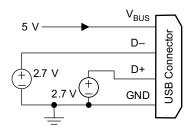

The device supports divider3, as shown in Figure 45. In the Divider3 charging scheme the device applies 2.7 V and 2.7 V to D+ and D- data lines.

Figure 45. Divider 3 Mode

#### 8.4.5.3 DCP 1.2-V Charging Scheme

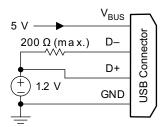

The DCP 1.2-V charging scheme is used by some hand-held devices to enable fast charging at 2 A. The TPS2549 device supports this scheme in DCP-auto state before the device enters BC1.2 shorted mode. To simulate this charging scheme, the D+ and D- lines are shorted and pulled up to 1.2 V for a fixed duration. Then the device moves to DCP shorted mode as defined in the BC1.2 specification and as shown in Figure 46.

Figure 46. 1.2-V Mode

#### 8.4.6 DCP Auto Mode

As previously discussed, the TPS2549 device integrates an auto-detect state machine that supports all the DCP charging schemes. The auto-detect state machine starts in the Divider3 scheme. However, if a BC1.2 or YD/T 1591-2009 compliant device is attached, the TPS2549 device responds by turning the power switch back on without output discharge and operating in 1.2-V mode briefly before entering BC1.2 DCP mode. Then the auto-detect state machine stays in that mode until the device releases the data line, in which case the auto-detect state machine goes back to the Divider3 scheme. When a Divider3-compliant device is attached, the TPS2549 device stays in the Divider3 state.

www.ti.com SLUSCP2 – SEPTEMBER 2016

Figure 47. DCP Auto Mode

#### 8.4.7 Client Mode

The TPS2549 device integrates client mode as shown in Figure 48. The internal power switch is OFF and only the data analog switch is ON to block OUT power. This mode can be used for some software programming via the USB port.

Figure 48. Client-Mode Equivalent Circuit

#### 8.4.8 High-Bandwidth Data-Line Switches

The TPS2549 device passes the D+ and D- data lines through the device to enable monitoring and handshaking while supporting the charging operation. A wide-bandwidth signal switch allows data to pass through the device without corrupting signal integrity. The data-line switches are turned on in any of the CDP, SDP, or client operating modes. The EN input must be at logic high for the data line switches to be enabled.

#### **NOTE**

- While in CDP mode, the data switches are ON, even during CDP handshaking.

- The data line switches are OFF if EN is low, or if in DCP mode. The switches are not automatically turned off if the power switch (IN to OUT) is in current-limit.

- The data switches are only for a USB-2.0 differential pair. In the case of a USB-3.0 host, the super-speed differential pairs must be routed directly to the USB connector without passing through the TPS2549 device.

- Data switches are OFF during OUT (V<sub>BUS</sub>) discharge.

SLUSCP2 – SEPTEMBER 2016 www.ti.com

#### 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 9.1 Application Information

The TPS2549 device is a USB charging-port controller and power switch with cable compensation. It is typically used for USB port protection and as a USB charging controller. The following design procedure can be used to select components for the TPS2549 device. This section presents a simplified discussion of how to design cable compensation.

#### 9.2 Typical Application

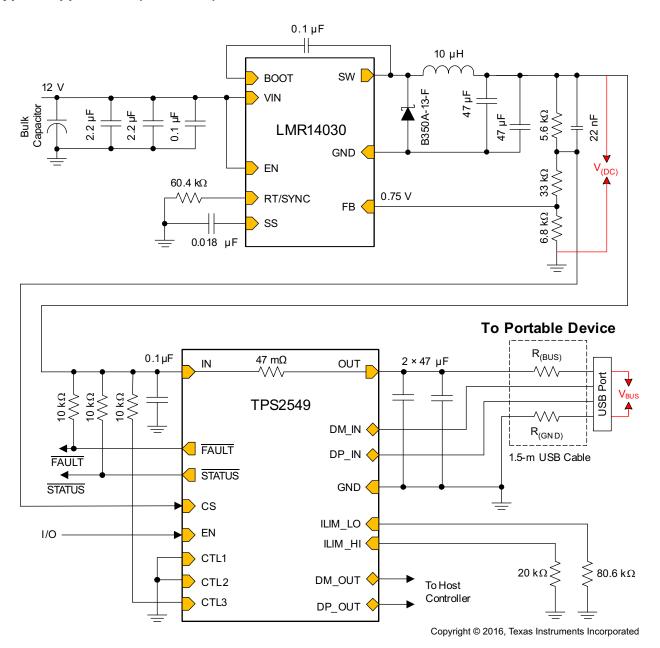

USB port charging requires a voltage regulator to convert battery voltage to 5-V  $V_{BUS}$  output. Because the  $V_{BUS}$ , D+, and D- pins of a USB port are exposed, there is a need for a protection device that has  $V_{BUS}$  overcurrent and D+ and D- ESD protection. An additional need is a charging controller with integrated CDP and DCP charging protocols on D+ and D- to support fast charging. A schematic of an application circuit with cable compensation is shown in Figure 49. An LMR14030 device is used as the voltage regulator, and the TPS2549 device is used as the charging controller with protection features.

### **Typical Application (continued)**

Figure 49. Typical Application Schematic: USB Port Charging With Cable Compensation

#### 9.2.1 Design Requirements

For this design example, use the following as the input parameters.

| DESIGN PARAMETER                                                 | EXAMPLE VALUE  |

|------------------------------------------------------------------|----------------|

| Input voltage, V <sub>(IN)</sub>                                 | 12 V           |

| Output voltage, V <sub>(DC)</sub>                                | 5 V            |

| Total parasitic resistance including TPS2549 r <sub>DS(on)</sub> | 420 mΩ         |

| Maximum continuous output current, I <sub>(OUT)</sub>            | 2.4 A          |

| Current limit, I <sub>(LIM)</sub>                                | 2.5 A to 2.9 A |

SLUSCP2 – SEPTEMBER 2016 www.ti.com

# TEXAS INSTRUMENTS

#### 9.2.2 Detailed Design Procedure

To begin the design process, a few parameters must be decided upon. The designer needs to know the following:

- Total resistance including power switch r<sub>DS(on)</sub>, cable resistance, and the contact resistance of connectors

- The maximum continuous output current for the charging port. The minimum current-limit setting of TPS2549 device must be higher than this current.

- The maximum output current of the upstream dc-dc converter. The maximum current-limit setting of TPS2549 device must be lower than this current.

#### 9.2.2.1 Input and Output Capacitance

Input and output capacitance improves the performance of the device; the actual capacitance should be optimized for the particular application. All protection circuits including the TPS2549 device have the potential for input voltage droop, overshoot, and output-voltage undershoot.

For all applications, TI recommends a 0.1-µF or greater ceramic bypass capacitor between IN and GND, placed as close as possible to the device for the local noise decoupling.

The TPS2549 device is used for 5-V power rail protection when a hot-short occurs on the output or when plugging in a capacitive load. Due to the limited response time of the upstream power supply, a large load transient can deplete the charge on the output capacitor of the power supply, causing a voltage droop. If the power supply is shared with other loads, ensure that voltage droop from current surges of the other loads do not force the TPS2549 device into UVLO. Increasing the upstream power supply output capacitor can reduce this droop. Shortening the connection impedance (resistance and inductance) between the TPS2549 device and the upstream power supply can also help reduce the voltage droop and overshoot on the TPS2549 input power bus.

Input voltage overshoots can be caused by either of two effects. The first cause is an abrupt application of input voltage in conjunction with input power-bus inductance and input capacitance when the IN terminal is in the high-impedance state (before turnon). Theoretically, the peak voltage is 2 times the applied voltage. The second cause is due to the abrupt reduction of output short-circuit current when the TPS2549 device turns off and energy stored in the input inductance drives the input voltage high. Applications with large input inductance (for example, connecting the evaluation board to the bench power supply through long cables) may require large input capacitance to prevent the voltage overshoot from exceeding the absolute maximum voltage of the device.

For output capacitance, consider the following three application situations.