## UCC28710, UCC28711, UCC28712, UCC28713

SLUSB86C - NOVEMBER 2012-REVISED JUNE 2017

# UCC2871x Constant-Voltage, Constant-Current Controller With Primary-Side Regulation

## **Features**

- < 10-mW No-Load Power

- Primary-Side Regulation (PSR) Eliminates Opto-Coupler

- ±5% Voltage and Current Regulation Across Line and Load

- 700-V Start-Up Switch

- 100-kHz Maximum Switching Frequency Enables High-Power Density Charger Designs

- Resonant Valley-Switching Operation for Highest Overall Efficiency

- Frequency Jitter to Ease EMI Compliance

- Wide VDD Range Allows Small Bias Capacitor

- Clamped Gate-Drive Output for MOSFET

- Overvoltage, Low-Line, and Overcurrent **Protection Functions**

- Programmable Cable Compensation (UCC28710)

- NTC Resistor Interface (UCC28711, UCC28712 and UCC28713) with Fixed Cable Compensation **Options**

- SOIC-7 Package

- Create a Custom Design Using the UCC28710 With the WEBENCH® Power Designer

# 2 Applications

- USB-Compliant Adapters and Chargers for Consumer Electronics

- **Smart Phones**

- **Tablet Computers**

- Cameras

- Standby Supply for TV and Desktop

- White Goods

# 3 Description

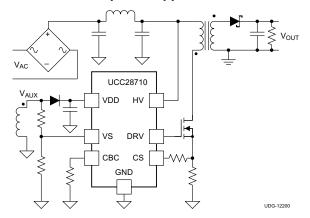

The UCC2871x family of flyback power supply controllers provides isolated-output Constant-Voltage (CV) and Constant-Current (CC) output regulation without the use of an optical coupler. The devices process information from the primary power switch and an auxiliary flyback winding for precise control of output voltage and current.

An internal 700-V start-up switch, dynamicallycontrolled operating states and a tailored modulation profile support ultra-low standby power without sacrificing start-up time or output transient response.

Control algorithms in the UCC28710 family allow operating efficiencies to meet or exceed applicable standards. The output drive interfaces to a MOSFET power switch. Discontinuous conduction mode (DCM) with valley switching reduces switching losses. Modulation of switching frequency and primary current peak amplitude (FM and AM) keeps the conversion efficiency high across the entire load and line ranges.

The controllers have a maximum switching frequency of 100 kHz and always maintain control of the peakprimary current in the transformer. Protection features help keep primary and secondary component stresses in check. The UCC28710 allow the cable compensation to be programmed. The UCC28711, UCC28712 and UCC28713 devices allow remote temperature sensing using a negative temperature coefficient (NTC) resistor while providing fixed cablecompensation levels.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE  | BODY SIZE (NOM)   |

|-------------|----------|-------------------|

| UCC28710    |          |                   |

| UCC28711    | SOIC (7) | 4.04              |

| UCC28712    | SOIC (7) | 4.91 mm × 3.90 mm |

| UCC28713    |          |                   |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

#### Simplified Application

# **Table of Contents**

| 1 | Features 1                           |    | 8.4 Device Functional Modes                         | 12   |

|---|--------------------------------------|----|-----------------------------------------------------|------|

| 2 | Applications 1                       | 9  | Application and Implementation                      | 17   |

| 3 | Description 1                        |    | 9.1 Application Information                         | 17   |

| 4 | Revision History2                    |    | 9.2 Typical Application                             | 17   |

| 5 | Device Comparison Table3             | 10 | Power Supply Recommendations                        | 23   |

| 6 | Pin Configuration and Functions      | 11 | Layout                                              | . 23 |

| 7 | Specifications4                      |    | 11.1 Layout Guidelines                              | 23   |

| • | 7.1 Absolute Maximum Ratings         |    | 11.2 Layout Example                                 | 25   |

|   | 7.2 ESD Ratings                      | 12 | Device and Documentation Support                    | 26   |

|   | 7.3 Recommended Operating Conditions |    | 12.1 Device Support                                 | 26   |

|   | 7.4 Thermal Information              |    | 12.2 Documentation Support                          | 28   |

|   | 7.5 Electrical Characteristics       |    | 12.3 Receiving Notification of Documentation Update | s 28 |

|   | 7.6 Typical Characteristics 6        |    | 12.4 Community Resources                            | 28   |

| 8 | Detailed Description9                |    | 12.5 Trademarks                                     | 28   |

| • | 8.1 Overview                         |    | 12.6 Electrostatic Discharge Caution                | 29   |

|   | 8.2 Functional Block Diagram9        |    | 12.7 Glossary                                       | 29   |

|   | 8.3 Feature Description              | 13 | Mechanical, Packaging, and Orderable Information    | 29   |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Cl | nanges from Revision B (July 2015) to Revision C                                                                                                                                                                                                                                                                             | Page |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •  | Deleted all references to the UCC28714, UCC28715, and UCC28716 devices                                                                                                                                                                                                                                                       | 1    |

| •  | Deleted quasi from quasi-resonant                                                                                                                                                                                                                                                                                            | 1    |

| •  | Added the Development Support, Receiving Notification of Documentation Updates, and Community Resources sections                                                                                                                                                                                                             | 26   |

| CI | nanges from Revision A (December 2014) to Revision B                                                                                                                                                                                                                                                                         | Page |

| •  | Updated Layout Guidelines section                                                                                                                                                                                                                                                                                            | 23   |

| Cł | nanges from Original (November 2012) to Revision A                                                                                                                                                                                                                                                                           | Page |

| •  | Added Pin Configuration and Functions section, ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section |      |

# 5 Device Comparison Table

| PART NUMBER <sup>(1)</sup> | MINIMUM SWITCHING FREQUENCY | OPTIONS <sup>(2)</sup>                                |

|----------------------------|-----------------------------|-------------------------------------------------------|

| UCC28710                   |                             | Programmable cable compensation                       |

| UCC28711                   | 680 Hz                      | NTC option, 0-mV (at 5-V output) cable compensation   |

| UCC28712                   | 00U FIZ                     | NTC option, 150-mV (at 5-V output) cable compensation |

| UCC28713                   |                             | NTC option, 300-mV (at 5-V output) cable compensation |

- (1) See Mechanical, Packaging, and Orderable Information section for specific device ordering information.

- (2) For other fixed cable compensation options, call TI.

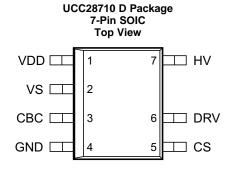

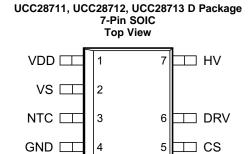

# 6 Pin Configuration and Functions

#### Pin Functions

|      | PIN      |                                  |     |                                                                                                                                                                                                                                                                                                                        |  |

|------|----------|----------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME | UCC28710 | UCC28711<br>UCC28712<br>UCC28713 | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                            |  |

| СВС  | 3        | _                                | I   | Cable compensation is a programming pin for compensation of cable voltage drop. Cable compensation is programmed with a resistor to GND.                                                                                                                                                                               |  |

| cs   | 5        | 5                                | I   | Current sense input connects to a ground-referenced current-sense resistor in series with the power switch. The resulting voltage is used to monitor and control the peak primary current. A series resistor can be added to this pin to compensate the peak switch current levels as the AC-mains input varies.       |  |

| DRV  | 6        | 6                                | 0   | Drive is an output used to drive the gate of an external high voltage MOSFET switching ransistor.                                                                                                                                                                                                                      |  |

| GND  | 4        | 4                                | _   | The ground pin is both the reference pin for the controller and the low-side return for the drive output. Special care should be taken to return all AC decoupling capacitors as close as possible to this pin and avoid any common trace length with analog signal return paths.                                      |  |

| HV   | 7        | 7                                | I   | The high-voltage pin connects directly to the rectified bulk voltage and provides charge to the VDD capacitor for start-up of the power supply.                                                                                                                                                                        |  |

| NTC  | _        | 3                                | I   | NTC an interface to an external negative temperature coefficient resistor for remote temperature sensing. Pulling this pin low shuts down PWM action.                                                                                                                                                                  |  |

| VDD  | 1        | 1                                | I   | VDD is the bias supply input pin to the controller. A carefully-placed bypass capacitor to GND is required on this pin.                                                                                                                                                                                                |  |

| VS   | 2        | 2                                | ı   | Voltage sense is an input used to provide voltage and timing feedback to the controller. This pin is connected to a voltage divider between an auxiliary winding and GND. The value of the upper resistor of this divider is used to program the AC-mains run and stop thresholds and line compensation at the CS pin. |  |

Copyright © 2012–2017, Texas Instruments Incorporated

# 7 Specifications

## 7.1 Absolute Maximum Ratings

See (1).

|                  |                                |                 |        | MIN         | MAX           | UNIT |

|------------------|--------------------------------|-----------------|--------|-------------|---------------|------|

| $V_{HV}$         | Start-up pin voltage, HV       |                 |        |             | 700           | V    |

| $V_{VDD}$        | Bias supply voltage, VDD       | D               |        |             | 38            | V    |

| I <sub>DRV</sub> | Continuous gate current        | sink            |        |             | 50            | mA   |

| I <sub>DRV</sub> | Continuous gate current        | source          |        |             | Self-limiting | mA   |

| I <sub>VS</sub>  | Peak current, VS               |                 |        |             | -1.2          | mA   |

| $V_{DRV}$        | Gate drive voltage at DR       | RV              |        | -0.5        | Self-limiting | V    |

|                  | Voltage                        | VS              |        | -0.75       | 7             | V    |

|                  | Voltage                        | CS, CB          | C, NTC | -0.5        | 5             | V    |

| TJ               | Operating junction temperating | erature         |        | <b>-</b> 55 | 150           | °C   |

|                  | Lead temperature 0.6 mr        | m from case for | 10 s   |             | 260           | °C   |

| T <sub>stg</sub> | Storage temperature            |                 |        | -65         | 150           | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltages are with respect to GND. Currents are positive into, negative out of the specified terminal. These ratings apply over the operating ambient temperature ranges unless otherwise noted.

## 7.2 ESD Ratings

|                    |               |                                                                     | VALUE | UNIT |

|--------------------|---------------|---------------------------------------------------------------------|-------|------|

| V                  | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±2000 | V    |

| V <sub>(ESD)</sub> | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  |                                | MIN   | NOM MAX | UNIT |

|------------------|--------------------------------|-------|---------|------|

| VDD              | Bias supply operating voltage  | 9     | 35      | V    |

| $C_{VDD}$        | VDD bypass capacitor           | 0.047 | 1       | μF   |

| R <sub>CBC</sub> | Cable-compensation resistance  | 10    |         | kΩ   |

| I <sub>VS</sub>  | VS pin current                 | -1    |         | mA   |

| TJ               | Operating junction temperature | -40   | 125     | °C   |

### 7.4 Thermal Information

|                      | THERMAL METRIC <sup>(1)</sup>                | D (SOIC) 7 PINS | UNIT |

|----------------------|----------------------------------------------|-----------------|------|

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 141.5           | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 73.8            | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 89              | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 23.5            | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 88.2            | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. .

## 7.5 Electrical Characteristics

over operating free-air temperature range,  $V_{VDD}$  = 25 V, HV = open,  $R_{CBC(NTC)}$  = open,  $T_A$  = -40 °C to 125 °C,  $T_A$  =  $T_J$  (unless otherwise noted)

|                       | PARAMETER                         | TEST CONDITIONS                                                      | MIN   | TYP  | MAX  | UNIT |

|-----------------------|-----------------------------------|----------------------------------------------------------------------|-------|------|------|------|

| HIGH-VOL              | TAGE START UP                     |                                                                      |       |      |      |      |

| I <sub>HV</sub>       | Start-up current out of VDD       | V <sub>HV</sub> = 100 V, V <sub>VDD</sub> = 0 V, start state         | 100   | 250  | 500  | μΑ   |

| I <sub>HVLKG</sub>    | Leakage current at HV             | V <sub>HV</sub> = 400 V, run state                                   |       | 0.1  | 1    | μΑ   |

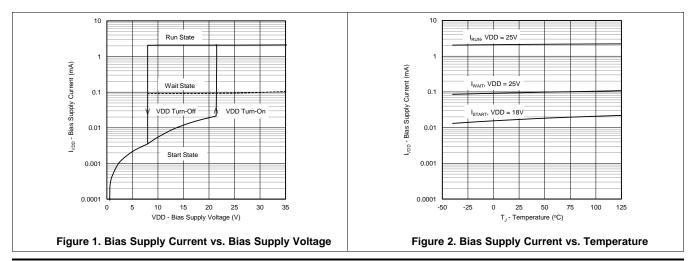

| BIAS SUP              | PLY INPUT                         |                                                                      |       |      |      |      |

| I <sub>RUN</sub>      | Supply current, run               | I <sub>DRV</sub> = 0, run state                                      |       | 2    | 2.65 | mA   |

| I <sub>WAIT</sub>     | Supply current, wait              | I <sub>DRV</sub> = 0, wait state                                     |       | 95   | 120  | μΑ   |

| I <sub>START</sub>    | Supply current, start             | $I_{DRV} = 0$ , $V_{VDD} = 18$ V, start state, $I_{HV} = 0$          |       | 18   | 30   | μΑ   |

| I <sub>FAULT</sub>    | Supply current, fault             | I <sub>DRV</sub> = 0, fault state                                    |       | 95   | 125  | μΑ   |

| UNDERVO               | OLTAGE LOCKOUT                    |                                                                      |       |      |      |      |

| V <sub>VDD(on)</sub>  | VDD turnon threshold              | V <sub>VDD</sub> low to high                                         | 19    | 21   | 23   | V    |

| $V_{VDD(off)}$        | VDD turnoff threshold             | V <sub>VDD</sub> high to low                                         | 7.7   | 8.1  | 8.5  | V    |

| VS INPUT              |                                   |                                                                      |       |      |      |      |

| $V_{VSR}$             | Regulating level                  | Measured at no-load condition, T <sub>J</sub> = 25 °C <sup>(1)</sup> | 4.01  | 4.05 | 4.09 | V    |

| V <sub>VSNC</sub>     | Negative clamp level              | $I_{VS} = -300 \mu\text{A}$ , volts below ground                     | 190   | 250  | 325  | mV   |

| I <sub>VSB</sub>      | Input bias current                | V <sub>VS</sub> = 4 V                                                | -0.25 | 0    | 0.25 | μΑ   |

| CS INPUT              |                                   |                                                                      | •     |      |      |      |

| V <sub>CST(max)</sub> | Maximum CS threshold voltage      | V <sub>VS</sub> = 3.7 V                                              | 738   | 780  | 810  | mV   |

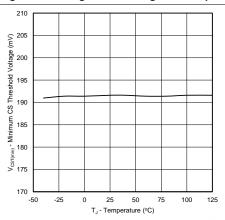

| V <sub>CST(min)</sub> | Minimum CS threshold voltage      | V <sub>VS</sub> = 4.35 V                                             | 175   | 195  | 215  | mV   |

| K <sub>AM</sub>       | AM control ratio                  | V <sub>CST(max)</sub> / V <sub>CST(min)</sub>                        | 3.6   | 4    | 4.4  | V/V  |

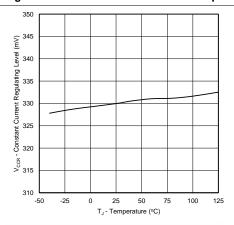

| V <sub>CCR</sub>      | Constant current regulating level | CC regulation constant                                               | 318   | 330  | 343  | mV   |

| K <sub>LC</sub>       | Line compensation current ratio   | $I_{VSLS} = -300 \mu A$ , $I_{VSLS}$ / current out of CS pin         | 24    | 25   | 28.6 | A/A  |

| T <sub>CSLEB</sub>    | Leading-edge blanking time        | DRV output duration, V <sub>CS</sub> = 1 V                           | 180   | 235  | 280  | ns   |

| DRIVERS               |                                   |                                                                      |       |      |      |      |

| I <sub>DRS</sub>      | DRV source current                | V <sub>DRV</sub> = 8 V, V <sub>VDD</sub> = 9 V                       | 20    | 25   |      | mA   |

| R <sub>DRVLS</sub>    | DRV low-side drive resistance     | I <sub>DRV</sub> = 10 mA                                             |       | 6    | 12   | Ω    |

| V <sub>DRCL</sub>     | DRV clamp voltage                 | V <sub>VDD</sub> = 35 V                                              |       | 14   | 16   | ٧    |

| R <sub>DRVSS</sub>    | DRV pulldown in start state       |                                                                      | 150   | 190  | 230  | kΩ   |

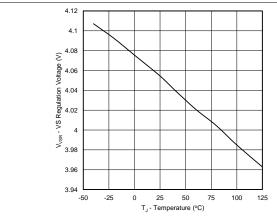

<sup>(1)</sup> The regulating level at VS decreases with temperature by 0.8 mV/°C. This compensation is included to reduce the power supply output voltage variance over temperature.

Copyright © 2012–2017, Texas Instruments Incorporated

# **Electrical Characteristics (continued)**

over operating free-air temperature range,  $V_{VDD}$  = 25 V, HV = open,  $R_{CBC(NTC)}$  = open,  $T_A$  = -40 °C to 125 °C,  $T_A$  =  $T_J$  (unless otherwise noted)

|                        | PARAMETER                          | TEST CONDITIONS                                                     |                                              | MIN  | TYP  | MAX  | UNIT |

|------------------------|------------------------------------|---------------------------------------------------------------------|----------------------------------------------|------|------|------|------|

| TIMING                 |                                    |                                                                     |                                              |      |      |      |      |

| f <sub>SW(max)</sub>   | Maximum switching frequency        | V <sub>VS</sub> = 3.7 V                                             |                                              | 92   | 100  | 106  | kHz  |

| f <sub>SW(min)</sub>   | Minimum switching frequency        | V <sub>VS</sub> = 4.35 V                                            | UCC28710<br>UCC28711<br>UCC28712<br>UCC28713 | 600  | 680  | 755  | Hz   |

| t <sub>ZTO</sub>       | Zero-crossing timeout delay        |                                                                     |                                              | 1.8  | 2.1  | 2.55 | μs   |

| PROTECT                | TION                               |                                                                     |                                              |      |      |      |      |

| $V_{OVP}$              | Overvoltage threshold              | At VS input, $T_J = 25  ^{\circ}C^{(1)}$                            |                                              | 4.55 | 4.6  | 4.71 | V    |

| $V_{OCP}$              | Overcurrent threshold              | At CS input                                                         |                                              | 1.4  | 1.5  | 1.6  | V    |

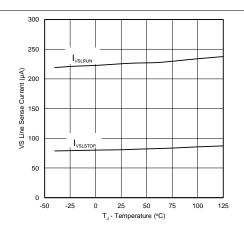

| I <sub>VSL(run)</sub>  | VS line-sense run current          | Current out of VS pin increasing                                    |                                              | 190  | 225  | 275  | μΑ   |

| I <sub>VSL(stop)</sub> | VS line-sense stop current         | Current out of VS pin decreasing                                    |                                              | 70   | 80   | 100  | μΑ   |

| $K_{VSL}$              | VS line sense ratio                | I <sub>VSL(run)</sub> / I <sub>VSL(stop)</sub>                      |                                              | 2.45 | 2.8  | 3.05 | A/A  |

| $T_{J(stop)}$          | Thermal shut-down temperature      | Internal junction temperature                                       |                                              |      | 165  |      | °C   |

| CABLE C                | OMPENSATION                        |                                                                     |                                              |      |      |      |      |

| $V_{\text{CBC(max)}}$  | Cable compensation maximum voltage | Voltage at CBC at full load                                         | UCC28710                                     | 2.9  | 3.2  | 3.5  | V    |

| $V_{\text{CVS(min)}}$  | Compensation at VS                 | V <sub>CBC</sub> = open, change in VS regulating level at full load | UCC28710                                     | -55  | -15  | 25   | mV   |

| $V_{\text{CVS(max)}}$  | Maximum compensation at VS         | V <sub>CBC</sub> = 0 V, change in VS regulating level at full load  | UCC28710                                     | 275  | 320  | 375  | mV   |

|                        |                                    |                                                                     | UCC28711                                     | -55  | -15  | 25   |      |

| $V_{CVS}$              | Compensation at VS                 | Change in VS regulating level at full load                          | UCC28712                                     |      | 103  |      | mV   |

|                        |                                    | load                                                                | UCC28713                                     |      | 206  |      |      |

| NTC INPU               | JT                                 |                                                                     |                                              |      |      |      |      |

| V <sub>NTCTH</sub>     | NTC shut-down threshold            | Fault UVLO cycle when below this threshold                          | UCC28711<br>UCC28712<br>UCC28713             | 0.9  | 0.95 | 1    | V    |

| I <sub>NTC</sub>       | NTC pullup current                 | Current out of pin                                                  | UCC28711<br>UCC28712<br>UCC28713             | 90   | 105  | 125  | μΑ   |

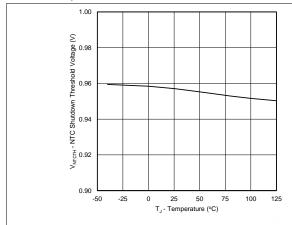

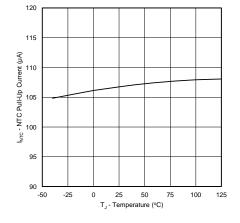

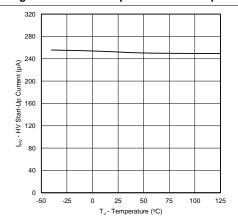

# 7.6 Typical Characteristics

VDD = 25 V, unless otherwise noted.

Submit Documentation Feedback

Copyright © 2012–2017, Texas Instruments Incorporated

# **Typical Characteristics (continued)**

VDD = 25 V, unless otherwise noted.

Figure 3. VS Regulation Voltage vs. Temperature

Figure 4. VS Line Sense Current vs. Temperature

Figure 5. Minimum CS Threshold vs. Temperature

Figure 6. Constant Current Regulating Level vs.

Temperature

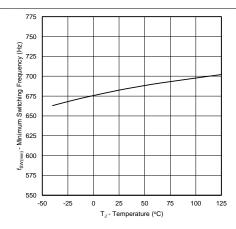

Figure 7. Minimum Switching Frequency vs. Temperature

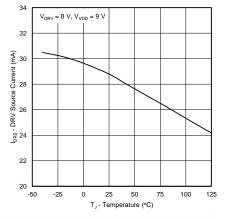

$V_{DRV} = 8 V$   $V_{VDD} = 9 V$

Figure 8. DRV Source Current vs. Temperature

# **Typical Characteristics (continued)**

VDD = 25 V, unless otherwise noted.

Figure 10. NTC Pull-Up Current vs. Temperature

Figure 11. VS Overvoltage Threshold vs. Temperature

Figure 12. HV Start-Up Current vs. Temperature

## 8 Detailed Description

#### 8.1 Overview

The UCC2871x family is a flyback power supply controller which provides accurate voltage and constant current regulation with primary-side feedback, eliminating the need for opto-coupler feedback circuits. The controller operates in discontinuous conduction mode with valley-switching to minimize switching losses. The modulation scheme is a combination of frequency and primary peak current modulation to provide high conversion efficiency across the load range. The control law provides a wide-dynamic operating range of output power which allows the power designer to achieve the <10-mW stand-by power requirement.

During low-power operating ranges the device has power management features to reduce the device operating current at operating frequencies below 33 kHz. The UCC2871x family includes features in the modulator to reduce the EMI peak energy of the fundamental switching frequency and harmonics. Accurate voltage and constant current regulation, fast dynamic response, and fault protection are achieved with primary-side control. A complete charger solution can be realized with a straightforward design process, low cost and low component count.

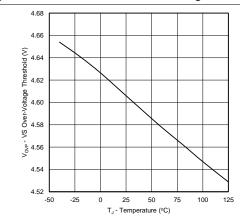

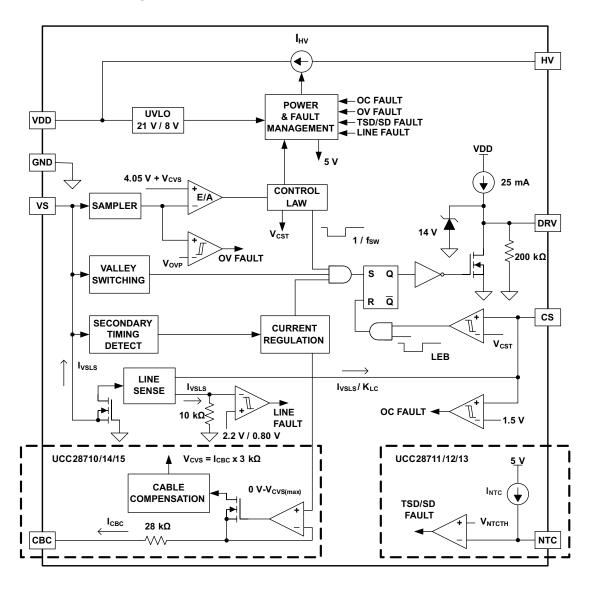

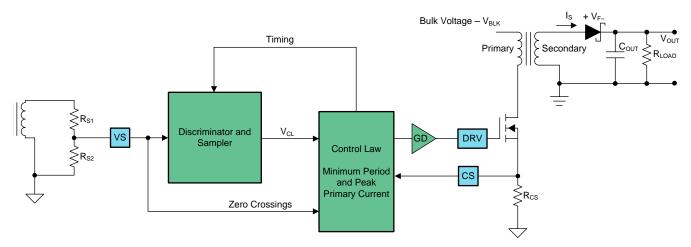

## 8.2 Functional Block Diagram

(1)

## 8.3 Feature Description

## 8.3.1 Detailed Pin Description

## 8.3.1.1 VDD (Device Bias Voltage Supply)

The VDD pin is connected to a bypass capacitor to ground and a start-up resistance to the input bulk capacitor (+) terminal. The VDD turnon UVLO threshold is 21 V and turnoff UVLO threshold is 8.1 V, with an available operating range up to 35 V. The USB charging specification requires the output current to operate in constant-current mode from 5 V to a minimum of 2 V; this is easily achieved with a nominal VDD of approximately 25 V. The additional VDD headroom up to 35 V allows for VDD to rise due to the leakage energy delivered to the VDD capacitor in high-load conditions. Also, the wide VDD range provides the advantage of selecting a relatively small VDD capacitor and high-value start-up resistance to minimize no-load stand-by power loss in the start-up resistor.

## 8.3.1.2 GND (Ground)

This is a single ground reference external to the device for the gate drive current and analog signal reference. Place the VDD bypass capacitor close to GND and VDD with short traces to minimize noise on the VS and CS signal pins.

## 8.3.1.3 VS (Voltage-Sense)

The VS pin is connected to a resistor divider from the auxiliary winding to ground. The output-voltage feedback information is sampled at the end of the transformer secondary current demagnetization time to provide an accurate representation of the output voltage. Timing information to achieve valley-switching and to control the duty cycle of the secondary transformer current is determined by the waveform on the VS pin. Avoid placing a filter capacitor on this input which would interfere with accurate sensing of this waveform.

The VS pin also senses the bulk capacitor voltage to provide for AC-input run and stop thresholds, and to compensate the current-sense threshold across the AC-input range. This information is sensed during the MOSFET on-time. For the AC-input run/stop function, the run threshold on VS is 220  $\mu$ A and the stop threshold is 80  $\mu$ A. The values for the auxilliary voltage divider upper-resistor R<sub>S1</sub> and lower-resistor R<sub>S2</sub> can be determined by the equations below.

$$R_{S1} = \frac{V_{IN(run)} \times \sqrt{2}}{N_{PA} \times I_{VSL(run)}}$$

#### where

- N<sub>PA</sub> is the transformer primary-to-auxiliary turns ratio,

- V<sub>IN(run)</sub> is the AC RMS voltage to enable turnon of the controller (run),

$$R_{S2} = \frac{R_{S1} \times V_{VSR}}{N_{AS} \times \left(V_{OCV} + V_{F}\right) - V_{VSR}}$$

#### where

- V<sub>OCV</sub> is the converter regulated output voltage,

- V<sub>F</sub> is the output rectifier forward drop at near-zero current,

- N<sub>AS</sub> is the transformer auxiliary to secondary turns ratio,

- R<sub>S1</sub> is the VS divider high-side resistance,

- V<sub>VSR</sub> is the CV regulating level at the VS input (see the *Electrical Characteristics* table).

## Feature Description (continued)

#### 8.3.1.4 DRV (Gate Drive)

The DRV pin is connected to the MOSFET gate pin, usually through a series resistor. The gate driver provides a gate-drive signal limited to 14 V. The turnon characteristic of the driver is a 25-mA current source which limits the turnon dv/dt of the MOSFET drain and reduces the leading-edge current spike, but still provides gate-drive current to overcome the Miller plateau. The gate-drive turnoff current is determined by the low-side driver  $R_{DS(on)}$  and any external gate-drive resistance. The user can reduce the turnoff MOSFET drain dv/dt by adding external gate resistance.

### 8.3.1.5 CS (Current Sense)

The current-sense pin is connected through a series resistor ( $R_{LC}$ ) to the current-sense resistor ( $R_{CS}$ ). The current-sense threshold is 0.75 V for  $I_{PP(max)}$  and 0.25 V for  $I_{PP(min)}$ . The series resistor  $R_{LC}$  provides the function of feed-forward line compensation to eliminate change in  $I_{PP}$  due to change in di/dt and the propagation delay of the internal comparator and MOSFET turnoff time. There is an internal leading-edge blanking time of 235 ns to eliminate sensitivity to the MOSFET turnon current spike. It should not be necessary to place a bypass capacitor on the CS pin. The value of  $R_{CS}$  is determined by the target output current in constant-current (CC) regulation. The values of  $R_{CS}$  and  $R_{LC}$  can be determined by the equations below. The term  $\eta_{XFMR}$  is intended to account for the energy stored in the transformer but not delivered to the secondary. This includes transformer resistance and core loss, bias power, and primary-to-secondary leakage ratio.

**Example:** With a transformer core and winding loss of 5%, primary-to-secondary leakage inductance of 3.5%, and bias power to output power ratio of 1.5%. The  $\eta_{XFMR}$  value is approximately: 1 - 0.05 - 0.035 - 0.015 = 0.9.

$$R_{CS} = \frac{V_{CCR} \times N_{PS}}{2I_{OCC}} \times \sqrt{\eta_{XFMR}}$$

where

- V<sub>CCR</sub> is a current regulation constant (see the *Electrical Characteristics* table),

- N<sub>PS</sub> is the transformer primary-to-secondary turns ratio (a ratio of 13 to 15 is recommended for 5-V output),

- I<sub>OCC</sub> is the target output current in constant-current regulation,

$$R_{LC} = \frac{K_{LC} \times R_{S1} \times R_{CS} \times T_{D} \times N_{PA}}{L_{P}}$$

where

- R<sub>S1</sub> is the VS pin high-side resistor value,

- R<sub>CS</sub> is the current-sense resistor value,

- T<sub>D</sub> is the current-sense delay including MOSFET turnoff delay, add ~50 ns to MOSFET delay,

- N<sub>PA</sub> is the transformer primary-to-auxiliary turns ratio,

- L<sub>P</sub> is the transformer primary inductance,

- K<sub>LC</sub> is a current-scaling constant (see the *Electrical Characteristics* table).

## 8.3.1.6 CBC (Cable Compensation), Pin 1 UCC28700

The cable compensation pin is connected to a resistor to ground to program the amount of output voltage compensation to offset cable resistance. The cable compensation block provides a 0-V to 3-V voltage level on the CBC pin corresponding to 0 to  $I_{OCC}$  output current. The resistance selected on the CBC pin programs a current mirror that is summed into the VS feedback divider therefore increasing the output voltage as  $I_{OUT}$  increases. There is an internal series resistance of 28 k $\Omega$  to the CBC pin which sets a maximum cable compensation of a 5-V output to 400 mV when CBC is shorted to ground. The CBC resistance value can be determined by the equation below.

$$R_{CBC} = \frac{V_{CBC(max)} \times 3 \text{ k}\Omega \times (V_{OCV} + V_F)}{V_{VSR} \times V_{OCBC}} - 28 \text{ k}\Omega$$

(4)

(5)

## Feature Description (continued)

#### where

- V<sub>O</sub> is the output voltage,

- V<sub>F</sub> is the diode forward voltage,

- V<sub>OCBC</sub> is the target cable compensation voltage at the output terminals,

- V<sub>CBC(max)</sub> is the maximum voltage at the cable compensation pin at the maximum converter output current (see the *Electrical Characteristics* table),

- V<sub>VSR</sub> is the CV regulating level at the VS input (see the *Electrical Characteristics* table).

### 8.3.1.7 NTC (NTC Thermistor Shut-down), Pin 1 UCC28701/2/3

These versions of the UCC28700 family utilize pin 1 for an external NTC thermistor to allow user-programmable external thermal shut-down. The shut-down threshold is 0.95 V with an internal 105- $\mu$ A current source which results in a 9.05- $k\Omega$  thermistor shut-down threshold. These controllers have either zero or fixed internal cable compensation.

#### 8.3.2 Fault Protection

There is comprehensive fault protection. Protection functions include:

- Output overvoltage fault

- · Input undervoltage fault

- · Internal overtemperature fault

- Primary overcurrent fault

- · CS pin fault

- VS pin fault

A UVLO reset and restart sequence applies for all fault protection events.

The output overvoltage function is determined by the voltage feedback on the VS pin. If the voltage sample on VS exceeds 115% of the nominal  $V_{OUT}$ , the device stops switching and the internal current consumption is  $I_{FAULT}$  which discharges the VDD capacitor to the UVLO turnoff threshold. After that, the device returns to the start state and a start-up sequence ensues.

The UCC2871x family always operates with cycle-by-cycle primary peak current control. The normal operating range of the CS pin is 0.78 V to 0.195 V. There is additional protection if the CS pin reaches 1.5 V. This results in a UVLO reset and restart sequence.

The line input run and stop thresholds are determined by current information at the VS pin during the MOSFET on-time. While the VS pin is clamped close to GND during the MOSFET on-time, the current through  $R_{\rm S1}$  is monitored to determine a sample of the bulk capacitor voltage. A wide separation of run and stop thresholds allows clean start-up and shut-down of the power supply with the line voltage. The run current threshold is 225  $\mu$ A and the stop current threshold is 80  $\mu$ A.

The internal over-temperature protection threshold is 165°C. If the junction temperature reaches this threshold the device initiates a UVLO reset cycle. If the temperature is still high at the end of the UVLO cycle, the protection cycle repeats.

Protection is included in the event of component failures on the VS pin. If complete loss of feedback information on the VS pin occurs, the controller stops switching and restarts.

#### 8.4 Device Functional Modes

## 8.4.1 Primary-Side Voltage Regulation

Figure 13 illustrates a simplified flyback convertor with the main voltage regulation blocks of the device shown. The power train operation is the same as any DCM flyback circuit but accurate output voltage and current sensing is the key to primary-side control.

Figure 13. Simplified Flyback Convertor (With the Main Voltage Regulation Blocks)

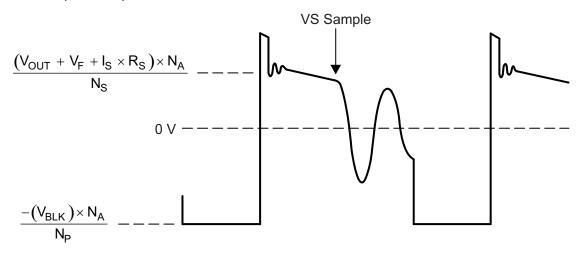

In primary-side control, the output voltage is sensed on the auxiliary winding during the transfer of transformer energy to the secondary. As shown in Figure 14 it is clear there is a down slope representing a decreasing total rectifier  $V_F$  and resistance voltage drop ( $I_SR_S$ ) as the secondary current decreases to zero. To achieve an accurate representation of the secondary output voltage on the auxiliary winding, the discriminator reliably blocks the leakage inductance reset and ringing, continuously samples the auxiliary voltage during the down slope after the ringing is diminished, and captures the error signal at the time the secondary winding reaches zero current. The internal reference on VS is 4.05 V. Temperature compensation on the VS reference voltage of -0.8-mV/ $^{\circ}$ C offsets the change in the output rectifier forward voltage with temperature. The resistor divider is selected as outlined in the VS pin description.

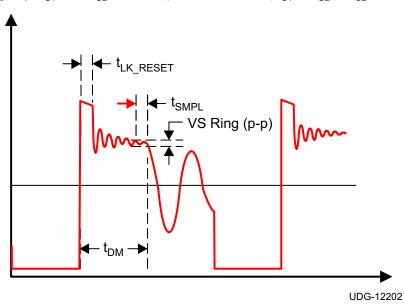

Figure 14. Auxiliary Winding Voltage

The UCC2871x family includes a VS signal sampler that signals discrimination methods to ensure an accurate sample of the output voltage from the auxiliary winding. There are however some details of the auxiliary winding signal to ensure reliable operation, specifically the reset time of the leakage inductance and the duration of any subsequent leakage inductance ring. Refer to Figure 15 below for a detailed illustration of waveform criteria to ensure a reliable sample on the VS pin. The first detail to examine is the duration of the leakage inductance reset pedestal,  $t_{LK\_RESET}$  in Figure 15. Because this can mimic the waveform of the secondary current decay, followed by a sharp downslope, it is important to keep the leakage reset time less than 600 ns for  $t_{PRI}$  minimum, and less

than 2.2 µs for  $I_{PRI}$  maximum. The second detail is the amplitude of ringing on the  $V_{AUX}$  waveform following  $t_{LK\_RESET}$ . The peak-to-peak voltage at the VS pin should be less than approximately 100 mV<sub>p-p</sub> at least 200 ns before the end of the demagnetization time,  $t_{DM}$ . If there is a concern with excessive ringing, it usually occurs during light or no-load conditions, when  $t_{DM}$  is at the minimum. The tolerable ripple on VS is scaled up to the auxiliary winding voltage by  $R_{S1}$  and  $R_{S2}$ , and is equal to 100 mV x ( $R_{S1} + R_{S2}$ ) /  $R_{S2}$ .

Figure 15. Auxiliary Waveform Details

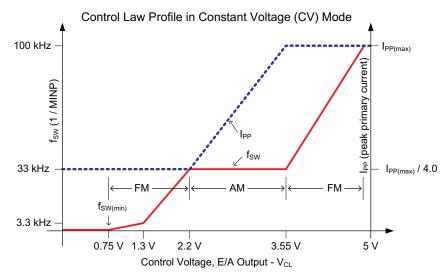

During voltage regulation, the controller operates in frequency modulation mode and amplitude modulation mode as illustrated in Figure 16 below. The internal operating frequency limits of the device are 100 kHz maximum and  $f_{SW(min)}$ . The transformer primary inductance and primary peak current chosen sets the maximum operating frequency of the converter. The output preload resistor and efficiency at low power determines the converter minimum operating frequency. There is no stability compensation required for the UCC2871x family.

Figure 16. Frequency and Amplitude Modulation Modes (During Voltage Regulation)

### 8.4.2 Primary-Side Current Regulation

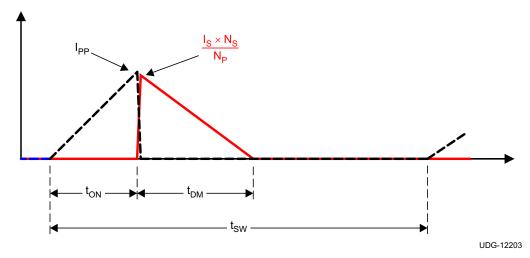

Timing information at the VS pin and current information at the CS pin allow accurate regulation of the secondary average current. The control law dictates that as power is increased in CV regulation and approaching CC regulation the primary-peak current is at  $I_{PP(max)}$ . Referring to Figure 17 below, the primary-peak current, turns ratio, secondary demagnetization time  $(t_{DM})$ , and switching period  $(t_{SW})$  determine the secondary average output current. Ignoring leakage inductance effects, the average output current is given by Equation 6. When the average output current reaches the regulation reference in the current control block, the controller operates in frequency modulation mode to control the output current at any output voltage at or below the voltage regulation target as long as the auxiliary winding can keep VDD above the UVLO turnoff threshold.

Figure 17. Transformer Currents

Figure 18. Typical Target Output V-I Characteristic

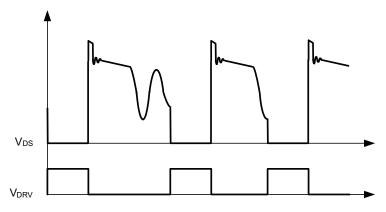

## 8.4.3 Valley Switching

The UCC2871x family utilizes valley switching to reduce switching losses in the MOSFET, to reduce induced-EMI, and to minimize the turnon current spike at the sense resistor. The controller operates in valley-switching in all load conditions unless the  $V_{DS}$  ringing has diminished.

Copyright © 2012–2017, Texas Instruments Incorporated

Referring to Figure 19 below, the UCC2871x family operates in a valley-skipping mode in most load conditions to maintain an accurate voltage or current regulation point and still switch on the lowest available  $V_{DS}$  voltage.

Figure 19. Valley-Skipping Mode

#### 8.4.4 Start-Up Operation

The internal high-voltage start-up switch connected to the bulk capacitor voltage ( $V_{BLK}$ ) through the HV pin charges the VDD capacitor. During start up there is typically 300  $\mu$ A available to charge the VDD capacitor. When VDD reaches the 21-V UVLO turnon threshold, the controller is enabled, the converter starts switching and the start-up switch is turned off. The initial three cycles are limited to  $I_{PP(min)}$ . After the initial three cycles at minimum  $I_{PP(min)}$ , the controller responds to the condition dictated by the control law. The converter will remain in discontinuous mode during charging of the output capacitor(s), maintaining a constant output current until the output voltage is in regulation.

# 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

# 9.1 Application Information

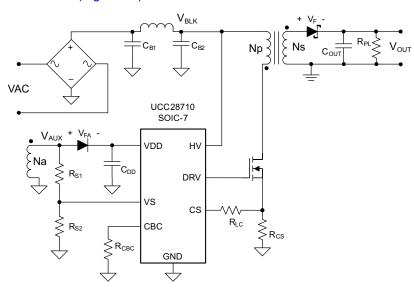

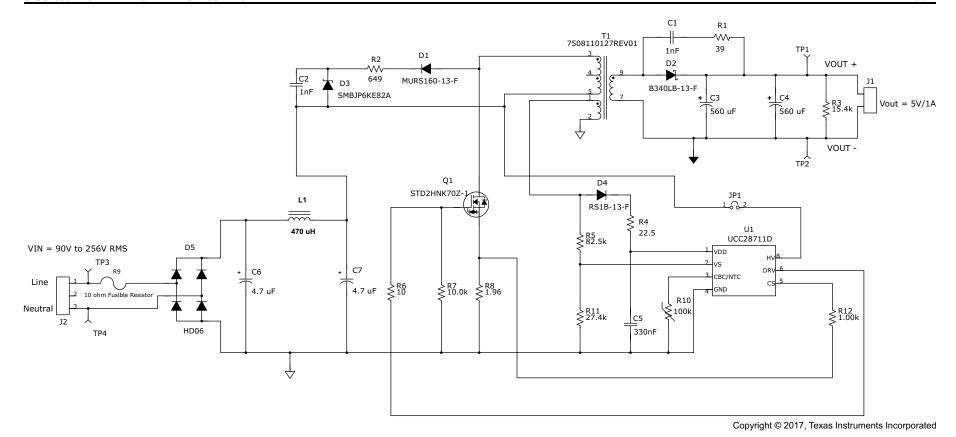

The UCC2871x family of flyback power supply controllers provides constant voltage (CV) and constant current (CC) output regulation to help meet USB-compliant adaptors and charger requirements. These devices use the information obtained from auxiliary winding sensing (VS) to control the output voltage and do not require optocoupler/TL431 feedback circuitry. Eliminating the optocoupler feedback reduces component count and makes the design more cost effective. Refer to Figure 20 for details.

## 9.2 Typical Application

The procedure in the *Detailed Design Procedure* section outlines the steps to design a constant-voltage, constant-current flyback converter using the UCC2871x family of controllers. Refer to the typical application schematic for component location (Figure 20) and the *Device Nomenclature* section for variable definitions.

Figure 20. Design Procedure Application Example

### 9.2.1 Design Requirements

**Table 1. Design Parameters**

|                      | PARAMETER             | NOTES AND CONDITIONS                        | MIN  | NOM     | MAX  | UNIT |

|----------------------|-----------------------|---------------------------------------------|------|---------|------|------|

| INPUT C              | HARACTERISTICS        |                                             |      |         |      |      |

| V <sub>IN</sub>      | Input Voltage         |                                             | 100  | 115/230 | 240  | V    |

| f <sub>LINE</sub>    | Line Frequency        |                                             | 47   | 50/60   | 64   | Hz   |

| P <sub>SB_CONV</sub> | No Load Input Power   | $V_{IN} = Nom, I_O = 0 A$                   |      |         | 10   | mW   |

| V <sub>IN(RUN)</sub> | Brownout Voltage      | I <sub>O</sub> = Nom                        |      | 70      |      | V    |

| OUTPUT               | CHARACTERISTICS       |                                             |      |         | ·    |      |

| Vo                   | Output Voltage        | V <sub>IN</sub> = Nom, I <sub>O</sub> = Nom | 4.75 | 5       | 5.25 | V    |

| V <sub>RIPPLE</sub>  | Output Voltage Ripple | V <sub>IN</sub> = Nom, I <sub>O</sub> = Max |      |         | 0.1  | V    |

| lo                   | Output Current        | V <sub>IN</sub> = Min to Max                |      | 1       | 1.05 | Α    |

Copyright © 2012–2017, Texas Instruments Incorporated

# **Typical Application (continued)**

Table 1. Design Parameters (continued)

|                         | PARAMETER                                  | NOTES AND CONDITIONS                                                                                            | MIN | NOM  | MAX | UNIT |  |

|-------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----|------|-----|------|--|

| $V_{OVP}$               | Output OVP                                 | I <sub>OUT</sub> = Min to Max                                                                                   |     | 5.75 |     | V    |  |

|                         | Transient Response                         |                                                                                                                 |     |      |     |      |  |

| V <sub>OΔ</sub>         | Load Step (V <sub>O</sub> = 4.1 V to 6 V)  | (0.1 to 0.6 A) or (0.6 to 0.1 A) $V_{O\Delta} = 0.9 \text{ V for } C_{OUT}$ calculation in applications section | 4.1 | 5    | 6   | А    |  |

| SYSTEMS CHARACTERISTICS |                                            |                                                                                                                 |     |      |     |      |  |

|                         | Switching Frequency                        |                                                                                                                 |     |      | 90  | kHz  |  |

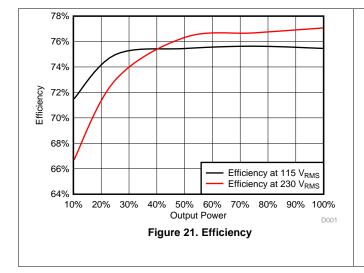

| η                       | Full Load Efficiency (115/230 V RMS Input) | I <sub>O</sub> = 1 A                                                                                            | 74% |      | 76% |      |  |

# 9.2.2 Detailed Design Procedure

### 9.2.2.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the UCC28710 device with the WEBENCH® Power Designer.

- 1. Start by entering the input voltage (V<sub>IN</sub>), output voltage (V<sub>OUT</sub>), and output current (I<sub>OUT</sub>) requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- 3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- Run electrical simulations to see important waveforms and circuit performance

- Run thermal simulations to understand board thermal performance

- Export customized schematic and layout into popular CAD formats

- Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

## 9.2.2.2 Stand-by Power Estimate

Assuming no-load stand-by power is a critical design parameter, determine estimated no-load power based on target converter maximum switching frequency and output power rating.

The following equation estimates the stand-by power of the converter.

$$P_{SB\_CONV} = \frac{P_{OUT} \times f_{MIN}}{\eta_{SB} \times K_{AM}^2 \times f_{MAX}}$$

(7)

For a typical USB charger application, the bias power during no-load is approximately 2.5 mW. This is based on 25-V VDD and 100- $\mu$ A bias current. The output preload resistor can be estimated by V<sub>OCV</sub> and the difference in the converter stand-by power and the bias power. The equation for output preload resistance accounts for bias power estimated at 2.5 mW.

$$R_{PL} = \frac{V_{OCV}^2}{P_{SB\_CONV} - 2.5 \text{ mW}}$$

(8)

The capacitor bulk voltage for the loss estimation is the highest voltage for the stand-by power measurement, typically 325  $V_{DC}$ .

For the total stand-by power estimation add an estimated 2.5 mW for snubber loss to the converter stand-by power loss.

$$P_{SB} = P_{SB\_CONV} + 2.5 \,\text{mW} \tag{9}$$

### 9.2.2.3 Input Bulk Capacitance and Minimum Bulk Voltage

Determine the minimum voltage on the input capacitance,  $C_{B1}$  and  $C_{B2}$  total, in order to determine the maximum Np to Ns turns ratio of the transformer. The input power of the converter based on target full-load efficiency, minimum input RMS voltage, and minimum AC input frequency are used to determine the input capacitance requirement.

Maximum input power is determined based on V<sub>OCV</sub>, I<sub>OCC</sub>, and the full-load efficiency target.

$$P_{IN} = \frac{V_{OCV} \times I_{OCC}}{\eta}$$

(10)

The below equation provides an accurate solution for input capacitance based on a target minimum bulk capacitor voltage. To target a given input capacitance value, iterate the minimum capacitor voltage to achieve the target capacitance.

$$C_{BULK} = \frac{2P_{IN} \times \left(0.25 + \frac{1}{2\Pi} \times arcsin\left(\frac{V_{BULK(min)}}{\sqrt{2} \times V_{IN(min)}}\right)\right)}{\left(2V_{IN(min)}^2 - V_{BULK(min)}^2\right) \times f_{LINE}}$$

(11)

#### 9.2.2.4 Transformer Turns Ratio, Inductance, Primary-Peak Current

The maximum primary-to-secondary turns ratio can be determined by the target maximum switching frequency at full load, the minimum input capacitor bulk voltage, and the estimated DCM resonant time.

Initially determine the maximum available total duty cycle of the on time and secondary conduction time based on target switching frequency and DCM resonant time. For DCM resonant time, assume 500 kHz if you do not have an estimate from previous designs. For the transition mode operation limit, the period required from the end of secondary current conduction to the first valley of the  $V_{DS}$  voltage is ½ of the DCM resonant period, or 1  $\mu$ s assuming 500-kHz resonant frequency.  $D_{MAX}$  can be determined using the equation below.

$$D_{MAX} = 1 - \left(\frac{t_{R}}{2} \times f_{MAX}\right) - D_{MAGCC}$$

(12)

Once  $D_{MAX}$  is known, the maximum turns ratio of the primary to secondary can be determined with the equation below.  $D_{MAGCC}$  is defined as the secondary diode conduction duty cycle during constant-current, CC, operation. It is set internally by the UCC2871x family at 0.425. The total voltage on the secondary winding needs to be determined; which is the sum of  $V_{OCV}$ , the secondary rectifier  $V_F$ , and the cable compensation voltage ( $V_{OCBC}$ ). For the 5-V USB charger applications, a turns ratio range of 13 to 15 is typically used.

$$N_{PS(max)} = \frac{D_{MAX} \times V_{BULK(min)}}{D_{MAGCC} \times (V_{OCV} + V_F + V_{OCBC})}$$

(13)

Once an optimum turns ratio is determined from a detailed transformer design, use this ratio for the following parameters.

The UCC2871x family constant-current regulation is achieved by maintaining a maximum  $D_{MAG}$  duty cycle of 0.425 at the maximum primary current setting. The transformer turns ratio and constant-current regulating voltage determine the current sense resistor for a target constant current.

Since not all of the energy stored in the transformer is transferred to the secondary, a transformer efficiency term is included. This efficiency number includes the core and winding losses, leakage inductance ratio, and bias power ratio to rated output power. For a 5-V, 1-A charger example, bias power of 1.5% is a good estimate. An overall transformer efficiency of 0.9 is a good estimate to include 3.5% leakage inductance, 5% core and winding loss, and 1.5% bias power.

$$R_{CS} = \frac{V_{CCR} \times N_{PS}}{2I_{OCC}} \times \sqrt{\eta_{XFMR}}$$

(14)

The primary transformer inductance can be calculated using the standard energy storage equation for flyback transformers. Primary current, maximum switching frequency and output and transformer power losses are included in the equation below. Initially determine transformer primary current.

Primary current is simply the maximum current sense threshold divided by the current sense resistance.

$$I_{PP(max)} = \frac{V_{CST(max)}}{R_{CS}}$$

(15)

$$L_{P} = \frac{2(V_{OCV} + V_{F} + V_{OCBC}) \times I_{OCC}}{\eta_{XFMR} \times I_{PP(max)}^{2} \times f_{MAX}}$$

(16)

The secondary winding to auxiliary winding transformer turns ratio (NAS) is determined by the lowest target operating output voltage in constant-current regulation and the VDD UVLO of the UCC2871x family. There is additional energy supplied to VDD from the transformer leakage inductance energy which allows a lower turns ratio to be used in many designs.

$$N_{AS} = \frac{V_{DD(off)} + V_{FA}}{V_{OCC} + V_{F}}$$

(17)

#### 9.2.2.5 Transformer Parameter Verification

The transformer turns ratio selected affects the MOSFET VDS and secondary rectifier reverse voltage so these should be reviewed. The UCC2871x family does require a minimum on time of the MOSFET (t<sub>ON</sub>) and minimum D<sub>MAG</sub> time (t<sub>DMAG</sub>) of the secondary rectifier in the high line, minimum load condition. The selection of f<sub>MAX</sub>, L<sub>P</sub> and  $R_{CS}$  affects the minimum  $t_{ON}$  and  $t_{DMAG}$ .

The secondary rectifier and MOSFET voltage stress can be determined by the equations below.

$$V_{REV} = \frac{V_{IN(max)} \times \sqrt{2}}{N_{PS}} + V_{OCV} + V_{OCBC}$$

(18)

For the MOSFET V<sub>DS</sub> voltage stress, an estimated leakage inductance voltage spike (V<sub>LK</sub>) needs to be included.

$$V_{DSPK} = \left(V_{IN(max)} \times \sqrt{2}\right) + \left(V_{OCV} + V_F + V_{OCBC}\right) \times N_{PS} + V_{LK}$$

(19)

Equation 20 and Equation 21 are used to determine if the minimum ton target of 300 ns and minimum ton ton the minimum ton the minimum ton ton the minimum ton ton the minimum ton the mini target of 1.2 µs is achieved.

$$t_{ON(min)} = \frac{L_{P}}{V_{IN(max)} \times \sqrt{2}} \times \frac{I_{PP(max)} \times V_{CST(min)}}{V_{CST(max)}}$$

(20)

$$t_{DMAG(min)} = \frac{t_{ON} \times V_{IN(max)} \times \sqrt{2}}{N_{PS} \times (V_{OCV} + V_F)}$$

(21)

#### 9.2.2.6 Output Capacitance

The output capacitance value is typically determined by the transient response requirement from no-load. For example, in some USB charger applications there is a requirement to maintain a minimum V<sub>O</sub> of 4.1 V with a load-step transient of 0 mA to 500 mA. The equation below assumes that the switching frequency can be at the UCC2871x family's minimum of f<sub>SW(min)</sub>.

$$C_{OUT} = \frac{I_{TRAN} \left( \frac{1}{f_{SW(min)}} + 150 \ \mu s \right)}{V_{O\Delta}}$$

(22)

Another consideration of the output capacitor(s) is the ripple voltage requirement which is reviewed based on secondary peak current and ESR. A margin of 20% is added to the capacitor ESR requirement in the equation below.

$$R_{ESR} = \frac{V_{RIPPLE} \times 0.8}{I_{PP(max)} \times N_{PS}}$$

(23)

### 9.2.2.7 VDD Capacitance, Con

The capacitance on VDD needs to supply the device operating current until the output of the converter reaches the target minimum operating voltage in constant-current regulation. At this time the auxiliary winding can sustain the voltage to the UCC2871x family. The total output current available to the load and to charge the output capacitors is the constant-current regulation target. The equation below assumes the output current of the flyback is available to charge the output capacitance until the minimum output voltage is achieved. There is an estimated 1 mA of gate-drive current in the equation and 1 V of margin added to VDD.

$$C_{DD} = \frac{\left(I_{RUN} + 1 \,\text{mA}\right) \times \frac{C_{OUT} \times V_{OCC}}{I_{OCC}}}{\left(V_{DD(on)} - V_{DD(off)}\right) - 1 \,V}$$

(24)

## 9.2.2.8 VS Resistor Divider, Line Compensation, and Cable Compensation

The VS divider resistors determine the output voltage regulation point of the flyback converter, also the high-side divider resistor ( $R_{S1}$ ) determines the line voltage at which the controller enables continuous DRV operation.  $R_{S1}$  is initially determined based on transformer auxiliary to primary turns ratio and desired input voltage operating threshold.

$$R_{S1} = \frac{V_{IN(run)} \times \sqrt{2}}{N_{PA} \times I_{VSL(run)}}$$

(25)

The low-side VS pin resistor is selected based on desired V<sub>O</sub> regulation voltage.

$$R_{S2} = \frac{R_{S1} \times V_{VSR}}{N_{AS} \times (V_{OCV} + V_F) - V_{VSR}}$$

(26)

The UCC2871x family can maintain tight constant-current regulation over input line by utilizing the line compensation feature. The line compensation resistor ( $R_{LC}$ ) value is determined by current flowing in  $R_{S1}$  and expected gate drive and MOSFET turnoff delay. Assume a 50-ns internal delay in the UCC2871x family.

$$R_{LC} = \frac{K_{LC} \times R_{S1} \times R_{CS} \times t_D \times N_{PA}}{L_P}$$

(27)

On the UCC28710, which has adjustable cable compensation, the resistance for the desired compensation level at the output terminals can be determined using Equation 28.

$$R_{CBC} = \frac{V_{CBC(max)} \times 3 \text{ k}\Omega \times \left(V_{OCV} + V_{F}\right)}{V_{VSR} \times V_{OCBC}} - 28 \text{ k}\Omega$$

(28)

#### 9.2.3 Application Curves

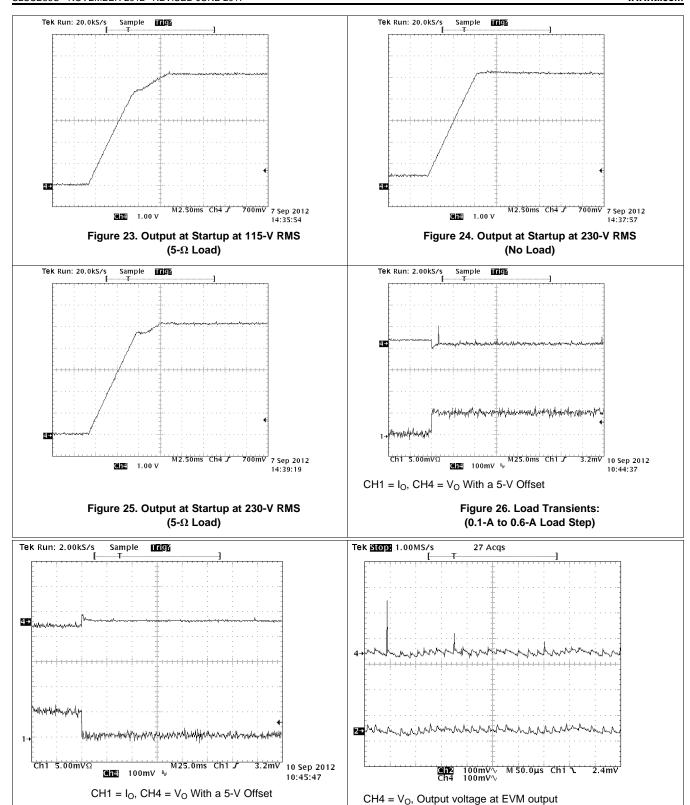

Figure 22. Output at Startup at 115-V RMS (No Load)

Figure 27. Load Transients: (0.6-A to 0.1-A Load Step)

CH2 =  $V_O$ , Output voltage measured at the end of the 3M of cable in parallel with a 1-uF capacitor. The output voltage has less than 50 mV of output ripple at the end of the cable.

Figure 28. Output Ripple Voltage at Full Load

# 10 Power Supply Recommendations

The UCC2871x family is intended for AC/DC adapters and chargers with input voltage range of 85  $V_{AC(rms)}$  to 265  $V_{AC(rms)}$  using Flyback topology. It can be used in other applications and converter topologies with different input voltages. Be sure that all voltages and currents are within the recommended operating conditions and absolute maximum ratings of the device. To maintain output current regulation over the entire input voltage range, design the converter to operate close to  $f_{MAX}$  when in full-load conditions. To improve thermal performance increase the copper area connected to GND pins.

## 11 Layout

## 11.1 Layout Guidelines

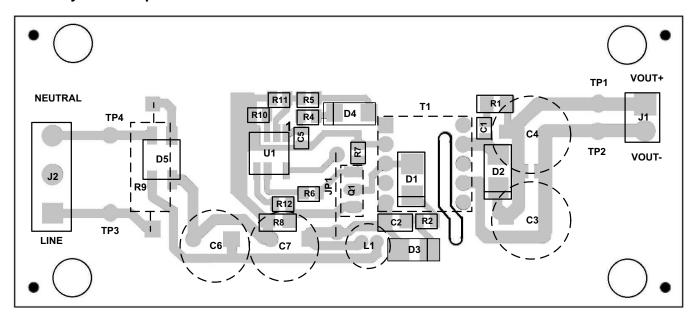

- High frequency bypass Capacitor C5 should be placed across Pin 1 and 4 as close as you can get it to the pins.

- Resistor R4 and C5 form a low pass filter and the connection of R4 and C5 should be as close to the VDD pin as possible.

- The VS pin controls the output voltage through the transformer turns ratio and the voltage divider of R5 and R11. Note the trace length between the R5, R11 and VS pin should be as short as possible to reduce or eliminate possible EMI coupling.

- Note the IC ground and power ground should meet at the bulk capacitor's (C6 and C7) return. Try to ensure

that high frequency/high current from the power stage does not go through the signal ground.

- The high frequency/high current path that you need to be cautious of on the primary is C7 +, T1 (P5, P3),

Q1d, Q1s, R8 to the return of C6 and C7. Try to keep all high current loops as short as possible.

- Try to keep all high current loops as short as possible.

- Keep all high current/high frequency traces away from or perpendicular to other traces in the design.

- Traces on the voltage clamp formed by D1, R2, D3 and C2 as short as possible.

- C6 return needs to be as close to the bulk capacitor supply as possible. This reduces the magnitude of dv/dt caused by large di/dt.

- Avoid mounting semiconductors under magnetics.

No value means not populated.

Figure 29. 5-W USB Adapter Schematic

# 11.2 Layout Example

Figure 30. Layout Example Schematic

# 12 Device and Documentation Support

## 12.1 Device Support

### 12.1.1 Development Support

For design tools see the UCC2871x Calculator, UCC2871x PSpice Transient Model, UCC2871x TINA-TI Transient Spice Model, and UCC2871x TINA-TI Transient Reference Design.

## 12.1.1.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the UCC28710 device with the WEBENCH® Power Designer.

- 1. Start by entering the input voltage (V<sub>IN</sub>), output voltage (V<sub>OUT</sub>), and output current (I<sub>OUT</sub>) requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- 3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- Run electrical simulations to see important waveforms and circuit performance

- · Run thermal simulations to understand board thermal performance

- Export customized schematic and layout into popular CAD formats

- · Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

#### 12.1.2 Device Nomenclature

## 12.1.2.1 Capacitance Terms in Farads

- C<sub>BULK</sub>: total input capacitance of C<sub>B1</sub> and C<sub>B2</sub>.

- C<sub>DD</sub>: minimum required capacitance on the VDD pin.

- C<sub>OUT</sub>: minimum output capacitance required.

#### 12.1.2.2 Duty Cycle Terms

- D<sub>MAGCC</sub>: secondary diode conduction duty cycle in CC, 0.425.

- D<sub>MAX</sub>: MOSFET on-time duty cycle.

#### 12.1.2.3 Frequency Terms in Hertz

- f<sub>LINE</sub>: minimum line frequency.

- f<sub>MAX</sub>: target full-load maximum switching frequency of the converter.

- f<sub>MIN</sub>: minimum switching frequency of the converter, add 15% margin over the f<sub>SW(min)</sub> limit of the device.

- f<sub>SW(min)</sub>: minimum switching frequency (see *Electrical Characteristics*).

### 12.1.2.4 Current Terms in Amperes

- locc: converter output constant-current target.

- I<sub>PP(max)</sub>: maximum transformer primary current.

- I<sub>START</sub>: start-up bias supply current (see *Electrical Characteristics*).

- I<sub>TRAN</sub>: required positive load-step current.

- I<sub>VSL(run)</sub>: VS pin run current (see Electrical Characteristics).

## 12.1.2.5 Current and Voltage Scaling Terms

- K<sub>AM</sub>: maximum-to-minimum peak primary current ratio (see Electrical Characteristics).

- K<sub>LC</sub>: current-scaling constant (see Electrical Characteristics).

## **Device Support (continued)**

#### 12.1.2.6 Transformer Terms

- L<sub>P</sub>: transformer primary inductance.

- N<sub>AS</sub>: transformer auxiliary-to-secondary turns ratio.

- N<sub>PA</sub>: transformer primary-to-auxiliary turns ratio.

- N<sub>PS</sub>: transformer primary-to-secondary turns ratio.

#### 12.1.2.7 Power Terms in Watts

- P<sub>IN</sub>: converter maximum input power.

- Pout: full-load output power of the converter.

- P<sub>RSTR</sub>: VDD start-up resistor power dissipation.

- P<sub>SB</sub>: total stand-by power.

- P<sub>SB CONV</sub>: P<sub>SB</sub> minus start-up resistor and snubber losses.

#### 12.1.2.8 Resistance Terms in $\Omega$

- R<sub>cs</sub>: primary current programming resistance.

- R<sub>ESR</sub>: total ESR of the output capacitor(s).

- R<sub>PL</sub>: preload resistance on the output of the converter.

- R<sub>S1</sub>: high-side VS pin resistance.

- R<sub>S2</sub>: low-side VS pin resistance.

## 12.1.2.9 Timing Terms in Seconds

- t<sub>D</sub>: current-sense delay including MOSFET turn-off delay; add 50 ns to MOSFET delay.

- t<sub>DMAG(min)</sub>: minimum secondary rectifier conduction time.

- t<sub>ON(min)</sub>: minimum MOSFET on time.

- t<sub>R</sub>: resonant frequency during the DCM (discontinuous conduction mode) time.

## 12.1.2.10 Voltage Terms in Volts

- V<sub>BLK</sub>: highest bulk capacitor voltage for stand-by power measurement.

- V<sub>BULK(min)</sub>: minimum voltage on C<sub>B1</sub> and C<sub>B2</sub> at full power.

- V<sub>OCBC</sub>: target cable compensation voltage at the output terminals.

- V<sub>CBC(max)</sub>: maximum voltage at the CBC pin at the maximum converter output current (see *Electrical Characteristics*).

- **V<sub>CCR</sub>**: constant-current regulating voltage (see *Electrical Characteristics*).

- V<sub>CST(max)</sub>: CS pin maximum current-sense threshold (see Electrical Characteristics).

- V<sub>CST(min)</sub>: CS pin minimum current-sense threshold (see Electrical Characteristics).

- V<sub>DD(off)</sub>: UVLO turn-off voltage (see *Electrical Characteristics*).

- V<sub>DD(on)</sub>: UVLO turn-on voltage (see Electrical Characteristics).

- V<sub>OA</sub>: output voltage drop allowed during the load-step transient.

- V<sub>DSPK</sub>: peak MOSFET drain-to-source voltage at high line.

- V<sub>F</sub>: secondary rectifier forward voltage drop at near-zero current.

- V<sub>FA</sub>: auxiliary rectifier forward voltage drop.

- V<sub>LK</sub>: estimated leakage inductance energy reset voltage.

- V<sub>ocv</sub>: regulated output voltage of the converter.

- V<sub>occ</sub>: target lowest converter output voltage in constant-current regulation.

- V<sub>REV</sub>: peak reverse voltage on the secondary rectifier.

- V<sub>RIPPI F</sub>: output peak-to-peak ripple voltage at full-load.

- V<sub>VSR</sub>: CV regulating level at the VS input (see Electrical Characteristics).

## 12.1.2.11 AC Voltage Terms in V<sub>RMS</sub>

V<sub>IN(max)</sub>: maximum input voltage to the converter.

## **Device Support (continued)**

- $V_{IN(min)}$ : minimum input voltage to the converter.

- **V**<sub>IN(run)</sub>: converter input start-up (run) voltage.

## 12.1.2.12 Efficiency Terms

- $\eta_{SB}$ : estimated efficiency of the converter at no-load condition, not including start-up resistance or bias losses. For a 5-V USB charger application, 60% to 65% is a good initial estimate.

- n: converter overall efficiency.

- $\eta_{XFMR}$ : transformer primary-to-secondary power transfer efficiency.

## 12.2 Documentation Support

#### 12.2.1 Related Documentation

For related documentation see the following:

- Choosing Standard Recovery Diode or Ultra-Fast Diode in Snubber

- Control Challenges for Low Power AC/DC Converters

- Troubleshooting TI PSR Controllers

- Using the UCC28711 EVM-160, Evaluation Module

- Leakage Current Measurement Reference Design for Determining Insulation Resistance

- 100-V/200-V AC Input 30-W Flyback Isolated Power Supply Reference Design for Servo Drives

#### 12.2.2 Related Links

The table below lists quick access links. Categories include technical documents, support and community resources, tools and software, and quick access to sample or buy.

**TECHNICAL TOOLS & SUPPORT & PARTS** PRODUCT FOLDER **ORDER NOW DOCUMENTS SOFTWARE** COMMUNITY UCC28710 Click here Click here Click here Click here Click here UCC28711 Click here Click here Click here Click here Click here UCC28712 Click here Click here Click here Click here Click here UCC28713 Click here Click here Click here Click here Click here

Table 2. Related Links

### 12.3 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on Alert me to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

#### 12.4 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community T's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

Design Support TI's Design Support Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 12.5 Trademarks

E2E is a trademark of Texas Instruments.

WEBENCH is a registered trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

28 Submit Documentation Feedback Copyright © 2012-2017, Texas Instruments Incorporated

## 12.6 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## 12.7 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

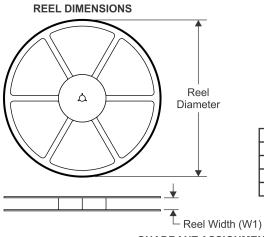

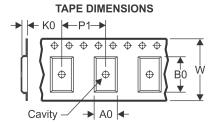

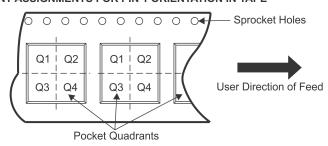

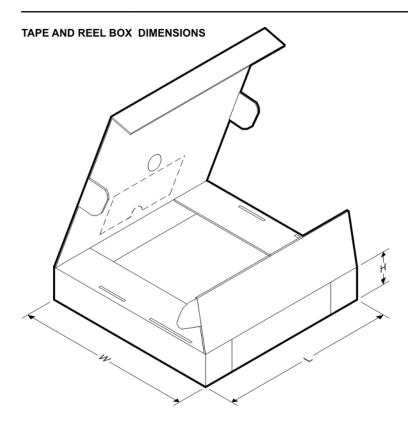

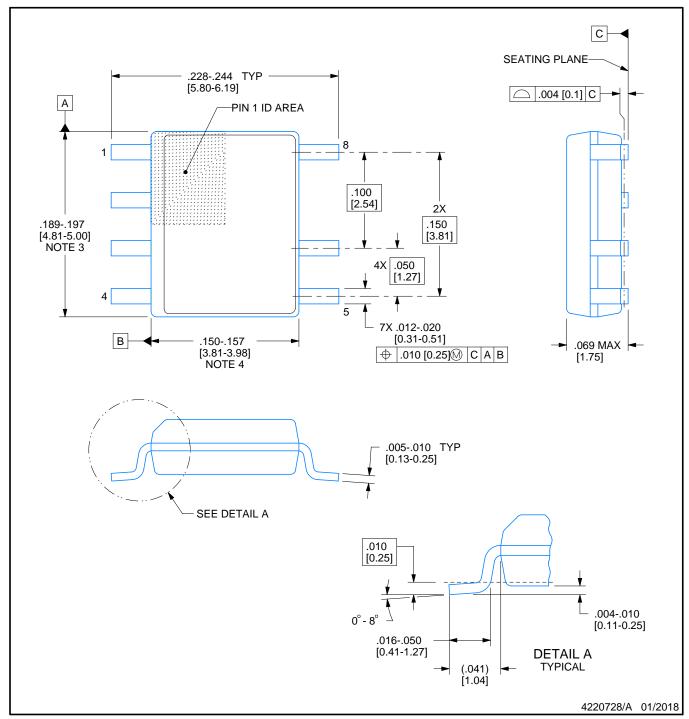

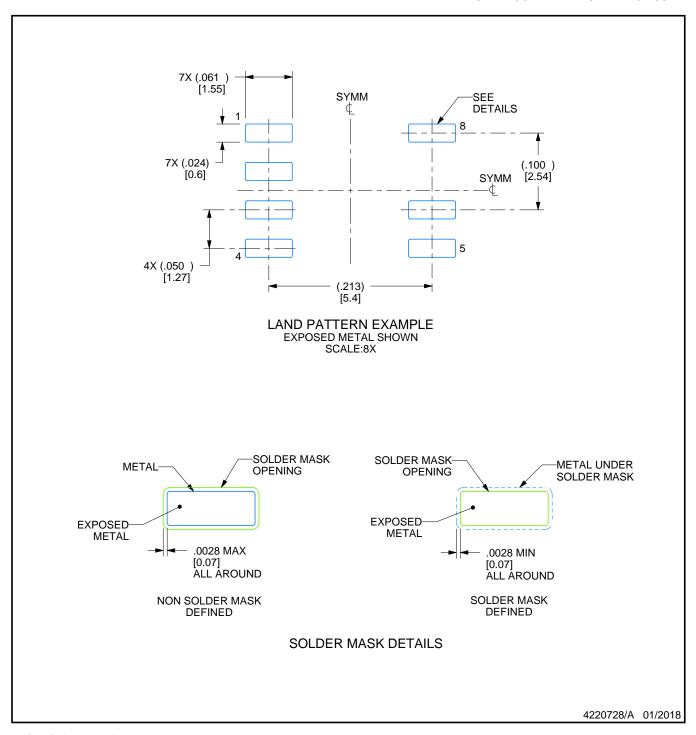

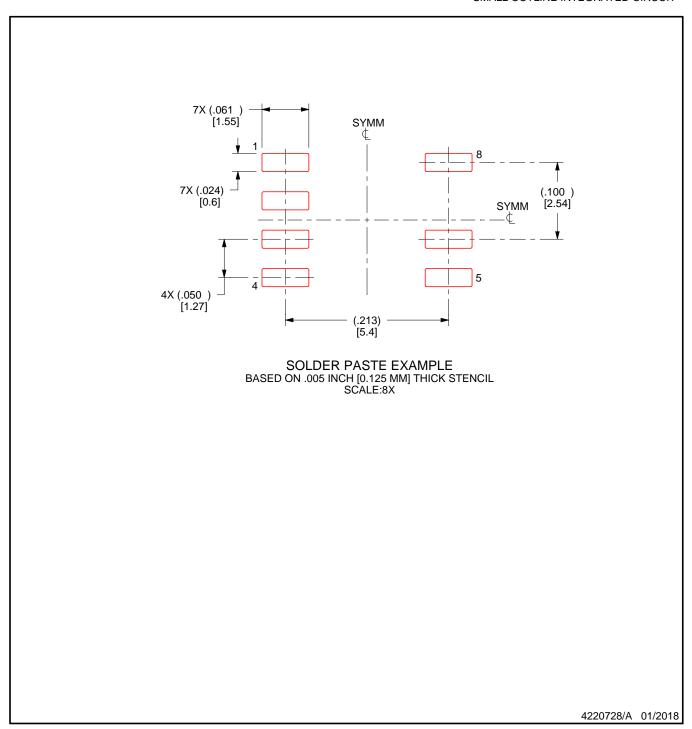

# 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Copyright © 2012–2017, Texas Instruments Incorporated

6-Feb-2020

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package | Pins | Package | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|---------|----------------------------|------------------|--------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty     | (2)                        | (6)              | (3)                |              | (4/5)          |         |

| UCC28710D        | ACTIVE | SOIC         | D       | 7    | 75      | Green (RoHS<br>& no Sb/Br) | NIPDAU           | Level-1-260C-UNLIM | -40 to 125   | U28710         | Samples |

| UCC28710DR       | ACTIVE | SOIC         | D       | 7    | 2500    | Green (RoHS<br>& no Sb/Br) | NIPDAU           | Level-1-260C-UNLIM | -40 to 125   | U28710         | Samples |

| UCC28711D        | ACTIVE | SOIC         | D       | 7    | 75      | Green (RoHS<br>& no Sb/Br) | NIPDAU           | Level-1-260C-UNLIM | -40 to 125   | U28711         | Samples |

| UCC28711DR       | ACTIVE | SOIC         | D       | 7    | 2500    | Green (RoHS<br>& no Sb/Br) | NIPDAU           | Level-1-260C-UNLIM | -40 to 125   | U28711         | Samples |

| UCC28712D        | ACTIVE | SOIC         | D       | 7    | 75      | Green (RoHS<br>& no Sb/Br) | NIPDAU           | Level-1-260C-UNLIM | -40 to 125   | U28712         | Samples |

| UCC28712DR       | ACTIVE | SOIC         | D       | 7    | 2500    | Green (RoHS<br>& no Sb/Br) | NIPDAU           | Level-1-260C-UNLIM | -40 to 125   | U28712         | Samples |

| UCC28713D        | ACTIVE | SOIC         | D       | 7    | 75      | Green (RoHS<br>& no Sb/Br) | NIPDAU           | Level-1-260C-UNLIM | -40 to 125   | U28713         | Samples |

| UCC28713DR       | ACTIVE | SOIC         | D       | 7    | 2500    | Green (RoHS<br>& no Sb/Br) | NIPDAU           | Level-1-260C-UNLIM | -40 to 125   | U28713         | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.