# MP2695

# I<sup>2</sup>C-Controlled, Single-Cell Switching Charger with JEITA Profile

# DESCRIPTION

The MP2695 is a highly integrated, flexible, switch-mode battery charging management device designed for a single-cell Li-ion and Lipolymer battery used in a wide range of portable applications.

The MP2695 integrates three battery-charging phases: pre-charge, constant-current, and constant-voltage charge. This device also manages the input power source by input current limit regulation and minimum input voltage regulation.

Using an I<sup>2</sup>C interface, the host can flexibly program the charge parameters. The device operating status can also be read in the registers.

Safety features include input over-voltage protection, battery under-voltage protection, thermal shutdown, and JEITA battery temperature monitoring.

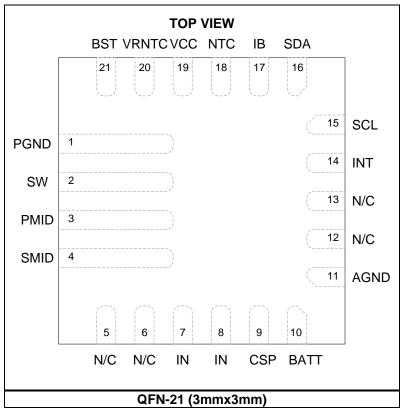

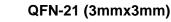

The MP2695 is available in a 21-pin QFN (3mmx3mm) package.

## **FEATURES**

- 4.0V to 11V Operation Voltage Range

- Up to 16V Sustainable Input Voltage

- 500mA to 3.6A Programmable Charge Current

- 3.6V to 4.45V Programmable Charge Regulation Voltage with ±0.5% Accuracy

- 100mA to 3A Programmable Input Current Limit with ±10% Accuracy

- Minimum Input Voltage Loop for Maximum Adapter Power Tracking

- Ultra-Low 25µA Battery Discharge Current in Idle Mode

- Comprehensive Safety Features:

- Fully-Customizable JEITA Profile with Programmable Temperature Threshold

- Charge Safety Timer

- Input Over-Voltage Protection

- Thermal Shutdown

- Analog Voltage Output IB Pin for Battery Current Monitor

- Status and Fault Monitoring

- Available in a Small QFN-21 (3mmx3mm) Package

# **APPLICATIONS**

- Bluetooth Speakers

- Mobile Devices

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are registered trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

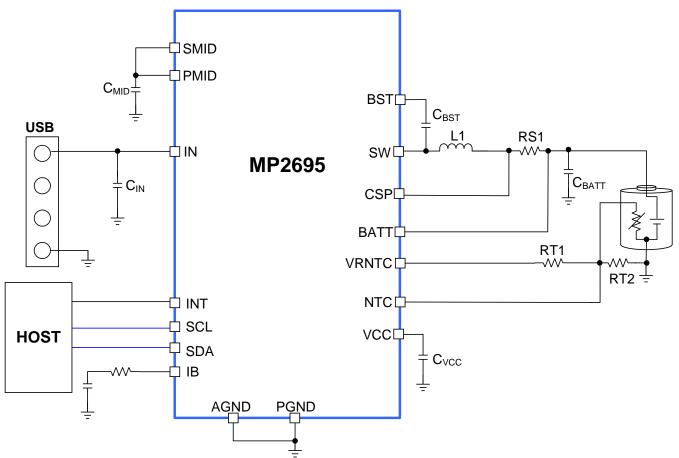

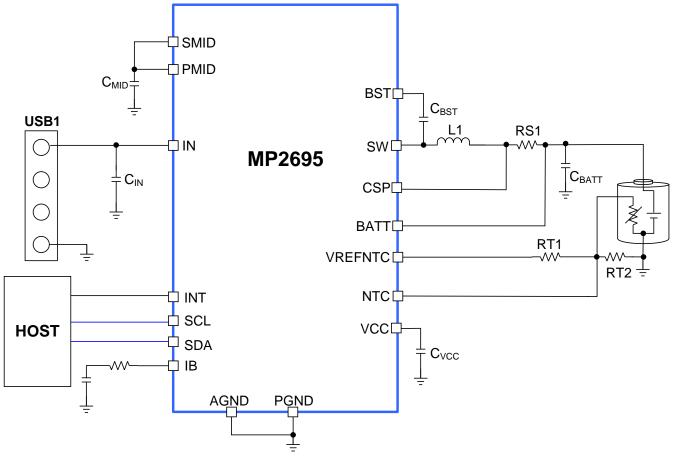

# **TYPICAL APPLICATION**

## **ORDERING INFORMATION**

| Part Number*    | Package         | Top Marking |

|-----------------|-----------------|-------------|

| MP2695GQ-0000** | QFN21 (3mmx3mm) | See Below   |

| EVKT-MP2695     | Evaluation kit  |             |

\* For Tape & Reel, add suffix –Z (e.g. MP2695GQ-xxxx–Z).

\*\* "xxxx" is the register setting option. The factory default is "0000." This content can be viewed in the I<sup>2</sup>C register map. Please contact an MPS FAE to obtain a value for "xxxx."

## **TOP MARKING**

## BHXY

## $\mathbf{LLL}$

BHX: Product code of MP2695GQ Y: Year code LLL: Lot number

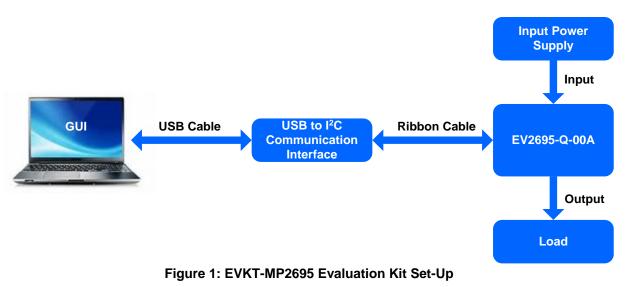

## **EVALUATION KIT EVKT-MP2695**

EVKT-MP2695 kit contents (items below can be ordered separately):

| # | Part Number        | Item                                                                                              | Quantity |

|---|--------------------|---------------------------------------------------------------------------------------------------|----------|

| 1 | EV2695-Q-00A       | MP2695 evaluation board                                                                           | 1        |

| 2 | EVKT-USBI2C-02-BAG | Includes one USB to I <sup>2</sup> C communication interface, one USB cable, and one ribbon cable | 1        |

| 3 | Online resources   | Includes: datasheet, user guide, product brief, and GUI                                           | 1        |

## Order directly from MonolithicPower.com or our distributors.

## **PACKAGE REFERENCE**

# **PIN FUNCTIONS**

| Package<br>Pin # | Name  | I/O   | Description                                                                                                                                                                                                                 |

|------------------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | PGND  | Power | Power ground.                                                                                                                                                                                                               |

| 2                | SW    | Power | Switching output node. Connect SW to the inductor.                                                                                                                                                                          |

| 3                | PMID  | Power | <b>High-side switching MOSFET drain.</b> Bypass PMID with ceramic capacitors from PMID to PGND as close to the IC as possible.                                                                                              |

| 4                | SMID  | Power | Connected to the drain of Q1 and Q2. Short SMID to PMID on the PCB.                                                                                                                                                         |

| 5, 6,<br>12, 13  | N/C   | /     | No connection. Must be left open.                                                                                                                                                                                           |

| 7, 8             | IN    | Power | Power input of the IC. Place ceramic capacitors from IN to PGND.                                                                                                                                                            |

| 9                | CSP   | -     | Battery charge current-sense positive input.                                                                                                                                                                                |

| 10               | BATT  | I     | Battery positive terminal.                                                                                                                                                                                                  |

| 11               | AGND  | Power | Analog ground. Short to PGND on the PCB.                                                                                                                                                                                    |

| 14               | INT   | 0     | <b>Open-drain interrupt output.</b> Connect INT to the logic rail through a $10k\Omega$ resistor.                                                                                                                           |

| 15               | SCL   | I/O   | I <sup>2</sup> C interface clock. Connect SCL to the logic rail through a 10kΩ resistor.                                                                                                                                    |

| 16               | SDA   | I/O   | I <sup>2</sup> C interface data. Connect SDA to the logic rail through a 10kΩ resistor.                                                                                                                                     |

| 17               | IB    | Ι     | <b>Battery current indicator.</b> The voltage at IB indicates the charge current to the battery.                                                                                                                            |

| 18               | NTC   | Ι     | <b>Temperature-sense input.</b> Connect NTC to a negative temperature coefficient thermistor. Program the temperature window with a resistor divider from VRNTC to NTC to GND. Programmable JEITA thresholds are supported. |

| 19               | VCC   | Ι     | <b>Internal circuit and the switch driver power supply.</b> Bypass to AGND with a ceramic capacitor as close to the IC as possible.                                                                                         |

| 20               | VRNTC | 0     | Reference voltage output for powering up NTC.                                                                                                                                                                               |

| 21               | BST   | Ι     | <b>Bootstrap.</b> Connect a 470nF bootstrap capacitor between BST and SW to form a floating supply across the high-side power switch driver.                                                                                |

## **ABSOLUTE MAXIMUM RATINGS** (1)

| IN, PMID SMID to PGND    | 0.3V to +16V                                  |

|--------------------------|-----------------------------------------------|

| SW to PGND               | -0.3V (-2V for 20ns) to                       |

|                          | +14V (16V for 20ns)                           |

| BST to PGND              | SW to SW + 5V                                 |

| All other pins to AGND   | 0.3V to +5.0V                                 |

| Continuous power dissipa | ation ( $T_A = +25^{\circ}C$ ) <sup>(2)</sup> |

|                          |                                               |

| Junction temperature     | 150°C                                         |

| Lead temperature (solder | )260°C                                        |

| Storage temperature      | 65°C to +150°C                                |

| Recommended Opera        | ting Conditions (3)                           |

| Supply voltage (VIN)     | 4.5V to +11V                                  |

|                          |                                               |

| I <sub>IN</sub>                               | Up to 3A    |

|-----------------------------------------------|-------------|

| Icc                                           | .Up to 3.6A |

| V <sub>BATT</sub>                             | .Up to 4.5V |

| Operating junction temp (T <sub>J</sub> )40°C | to +125°C   |

| Thermal Resistance (4) | <b>Ө</b> ЈА | θις     |

|------------------------|-------------|---------|

| QFN-21 (3mmx3mm)       | 50          | 12 °C/W |

# ESD RATINGS

| Human body model (HBM) <sup>(5)</sup> | 2000V |

|---------------------------------------|-------|

| Charged device model (CDM) (6)        | 250V  |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX) - T<sub>A</sub>) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

- 5) Per ANSI/ESDA/JEDEC JS-001.

- 6) Per JESD22-C101.

# **ELECTRICAL CHARACTERISTICS**

## $V_{IN}$ = 5.0V, $V_{BATT}$ = 3.5V, RS1 = 10m $\Omega$ , $T_A$ = +25°C, unless otherwise noted.

| Parameters Symbol Condit                  |                     | Condition                                                                              | Min  | Тур  | Max  | Units |

|-------------------------------------------|---------------------|----------------------------------------------------------------------------------------|------|------|------|-------|

| Quiescent Current                         | •<br>•              |                                                                                        |      |      |      |       |

| Battery discharge current in idle mode    | IBATT_IDLE          | Idle mode                                                                              |      | 25   | 36   | μA    |

| Input quiescent current without switching | Iin_q               | $V_{IN} > V_{IN\_UVLO}, V_{IN} > V_{BATT} + V_{HDRM}, charge disabled$                 |      | 0.6  | 1    | mA    |

| Input quiescent current when switching    | I <sub>IN_QSW</sub> | $V_{IN} > V_{IN}_{UVLO}$ , $V_{IN} > V_{BATT} + V_{HDRM}$ , charge enabled, BATT float |      | 1    |      | mA    |

| Power On/Off                              |                     | ·                                                                                      |      |      |      |       |

| IN operating range                        | VIN_OP              | Converter switching                                                                    | 4    |      | 11   | V     |

| Input under-voltage lockout               | VIN_UV              | V <sub>IN</sub> falling                                                                | 2.95 | 3.10 | 3.25 | V     |

| Input under-voltage lockout hysteresis    |                     | V <sub>IN</sub> rising                                                                 |      | 305  |      | mV    |

| Input vs. battery headroom                | Vhdrm               | V <sub>IN</sub> rising                                                                 |      | 200  | 310  | mV    |

| input vs. battery neadroom                |                     | V <sub>IN</sub> falling                                                                | 10   | 80   |      | mV    |

| VCC LDO output voltage                    | V <sub>VCC</sub>    | $V_{IN} = 5V$ , $I_{VCC} = 30mA$                                                       | 3.3  | 3.55 | 3.8  | V     |

| VCC under-voltage lockout                 | Vcc_uv              | VCC rising                                                                             | 1.9  | 2.1  | 2.3  | V     |

| VCC under-voltage lockout hysteresis      |                     |                                                                                        |      | 80   |      | mV    |

| Power Path                                |                     |                                                                                        |      |      |      |       |

| IN to PMID FET (Q1) on resistance         | R <sub>ON_Q1</sub>  |                                                                                        |      | 25   |      | mΩ    |

| High-side FET (Q2) on resistance          | Ron_Hs              |                                                                                        |      | 15   |      | mΩ    |

| Low-side FET (Q3) on resistance           | Ron_ls              |                                                                                        |      | 14   |      | mΩ    |

| Peak current limit for high-side          |                     | CC charge mode                                                                         |      | 6.5  |      | А     |

| FET                                       | IHS_PK              | Pre-charge mode                                                                        |      | 1.3  |      | А     |

| Switching frequency                       | fsw                 | SW_FREQ = 700kHz                                                                       |      | 720  |      | kHz   |

|                                           | ISW                 | SW_FREQ = 1200kHz                                                                      |      | 1200 |      | kHz   |

# ELECTRICAL CHARACTERISTICS (continued)

$V_{IN}$  = 5.0V,  $V_{BATT}$  = 3.5V, RS1 = 10m $\Omega$ ,  $T_A$  = +25°C, unless otherwise noted.

| Parameters                            | Symbol                | Condition                                   | Min   | Тур  | Max   | Units |

|---------------------------------------|-----------------------|---------------------------------------------|-------|------|-------|-------|

| Charge Mode                           | •                     |                                             | •     |      |       |       |

|                                       |                       | BATT_REG range (7)                          | 3.6   |      | 4.45  | V     |

|                                       |                       | BATT_REG[2:0] = 3.6V                        | 3.582 | 3.6  | 3.618 | V     |

|                                       |                       | BATT_REG[2:0] = 4.1V                        | 4.080 | 4.1  | 4.120 | V     |

|                                       | .,                    | BATT_REG[2:0] = 4.2V                        | 4.179 | 4.2  | 4.221 | V     |

| Charge voltage regulation             | V <sub>BATT_REG</sub> | BATT_REG[2:0] = 4.3V                        | 4.279 | 4.3  | 4.321 | V     |

|                                       |                       | BATT_REG[2:0] = 4.35V                       | 4.328 | 4.35 | 4.372 | V     |

|                                       |                       | BATT_REG[2:0] = 4.4V                        | 4.378 | 4.40 | 4.422 | V     |

|                                       |                       | BATT_REG[2:0] = 4.45V                       | 4.428 | 4.45 | 4.472 | V     |

|                                       |                       | ICC[4:0] = 3A                               | 2.7   | 3    | 3.4   | А     |

| Fast charge current                   | lcc                   | ICC[4:0] = 1.5A                             | 1.35  | 1.5  | 1.7   | А     |

| -                                     |                       | ICC[4:0] = 0.5A                             | 0.41  | 0.5  | 0.6   | А     |

|                                       |                       | ITERM[1:0] = 100mA                          | 40    | 100  | 160   | mA    |

| Charge termination current            | I <sub>TERM</sub>     | ITERM[1:0] = 200mA                          | 100   | 200  | 300   | mA    |

| Recharge threshold below<br>VBATT_REG | V <sub>RECH</sub>     | V <sub>BATT</sub> falling                   | 100   | 200  | 320   | mV    |

| Pre-charge to fast charge threshold   | VBATT_PRE             | VBATT rising                                | 2.9   | 3.0  | 3.1   | V     |

| Pre-charge to fast charge hysteresis  |                       | VBATT falling                               |       | 290  |       | mV    |

| Dra akanan ayanant                    | I <sub>PRE</sub>      | IPRE[1:0] = 150mA, V <sub>BATT</sub> = 1.8V |       | 150  |       | mA    |

| Pre-charge current                    |                       | IPRE[1:0] = 350mA, V <sub>BATT</sub> = 1.8V |       | 350  |       | mA    |

| Safety timer for charging cycle       |                       |                                             |       | 20   |       | hours |

| Input Regulation                      | •                     |                                             |       |      |       |       |

| Input minimum voltage                 |                       | VINMIN[2:0] = 4.5V                          | 4.41  | 4.51 | 4.61  | V     |

| regulation                            | Vin_min               | VINMIN[2:0] = 4.65V                         | 4.56  | 4.66 | 4.76  | V     |

|                                       |                       | IINLIM[2:0] = 3A                            | 2.7   | 2.85 | 3     | А     |

| Input current limit                   | I <sub>IN_LIM</sub>   | IINLIM[2:0] = 1.5A                          | 1.3   | 1.4  | 1.5   | А     |

|                                       |                       | IINLIM[2:0] = 0.5A                          | 0.4   | 0.45 | 0.5   | А     |

| Protection                            |                       |                                             |       |      |       |       |

| Battery over-voltage threshold        | VBATT_OVP             |                                             | 102   | 104  | 106   | %     |

| BATT over-voltage hysteresis          |                       |                                             |       | 1.5  |       | %     |

|                                       |                       | V <sub>IN</sub> rising, VIN_OVP = 6V        | 5.8   | 6    | 6.2   | V     |

| IN over-voltage protection            | Vin_ov                | V <sub>IN</sub> rising, VIN_OVP = 11V       | 10.6  | 11   | 11.4  | V     |

| IN over-voltage protection hysteresis |                       | V <sub>IN</sub> falling                     |       | 300  |       | mV    |

| Thermal Shutdown And Tempe            | erature Cor           | htrol                                       |       |      |       |       |

| Thermal shutdown rising threshold (7) | T <sub>J_SHDN</sub>   | T <sub>J</sub> rising                       |       | 150  |       | °C    |

| Thermal shutdown hysteresis (7)       |                       |                                             |       | 20   | 1     | °C    |

# ELECTRICAL CHARACTERISTICS (continued)

## $V_{IN}$ = 5.0V, $V_{BATT}$ = 3.5V, RS1 = 10m $\Omega$ , $T_A$ = +25°C, unless otherwise noted.

| Parameters                                 | Symbol                  | Condition                                               | Min  | Тур  | Max  | Units |

|--------------------------------------------|-------------------------|---------------------------------------------------------|------|------|------|-------|

| VRNTC voltage                              | VVRNTC                  | $V_{IN} = 5V$ , $I_{VRNTC} = 100\mu A$                  |      | 3.5  |      | V     |

| NTC low-temp rising threshold              | Vcold                   | As percentage of V <sub>VRNTC</sub><br>VCOLD[1:0] = 72% | 72   | 73.1 | 74.3 | %     |

| NTC low-temp rising threshold hysteresis   |                         | As percentage of VVRNTC                                 |      | 1.6  |      | %     |

| NTC cool-temp rising threshold             | V <sub>COOL</sub>       | As percentage of V <sub>VRNTC</sub><br>VCOOL[1:0] = 60% | 59.7 | 61   | 62.2 | %     |

| NTC cool-temp rising threshold hysteresis  |                         | As percentage of VVRNTC                                 |      | 1.6  |      | %     |

| NTC warm-temp falling threshold            | Vwarm                   | As percentage of V <sub>VRNTC</sub><br>VWARM[1:0] = 40% | 39.4 | 40.6 | 42   | %     |

| NTC warm-temp falling threshold hysteresis |                         | As percentage of VVRNTC                                 |      | 1.6  |      | %     |

| NTC hot-temp falling threshold             | VHOT                    | As percentage of V <sub>VRNTC</sub><br>VHOT[1:0] = 36%  | 35.3 | 36.6 | 37.9 | %     |

| NTC hot-temp falling threshold hysteresis  |                         | As percentage of V <sub>VRNTC</sub>                     |      | 1.6  |      | %     |

| I <sup>2</sup> C Interface                 |                         |                                                         |      |      |      |       |

| Input high threshold level                 |                         | SDA and SCL                                             | 1.3  |      |      | V     |

| Input low threshold level                  |                         | SDA and SCL                                             |      |      | 0.4  | V     |

| Output low threshold level                 |                         | Isink = 5mA                                             |      |      | 0.3  | V     |

| I <sup>2</sup> C clock frequency           | <b>f</b> <sub>SCL</sub> |                                                         |      |      | 400  | kHz   |

| Battery Current Indicator                  |                         |                                                         |      |      |      |       |

| IB voltage output                          |                         | Icc = 1A in charge mode                                 | 0.33 | 0.35 | 0.37 | V     |

Note:

7) Guaranteed by design.

# **TYPICAL CHARACTERISTICS**

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2019 MPS. All Rights Reserved.

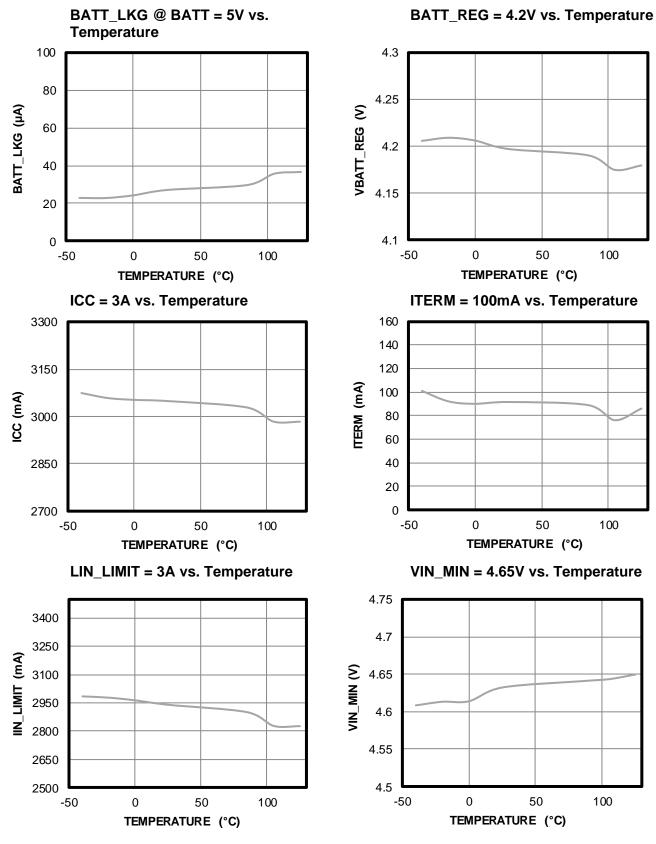

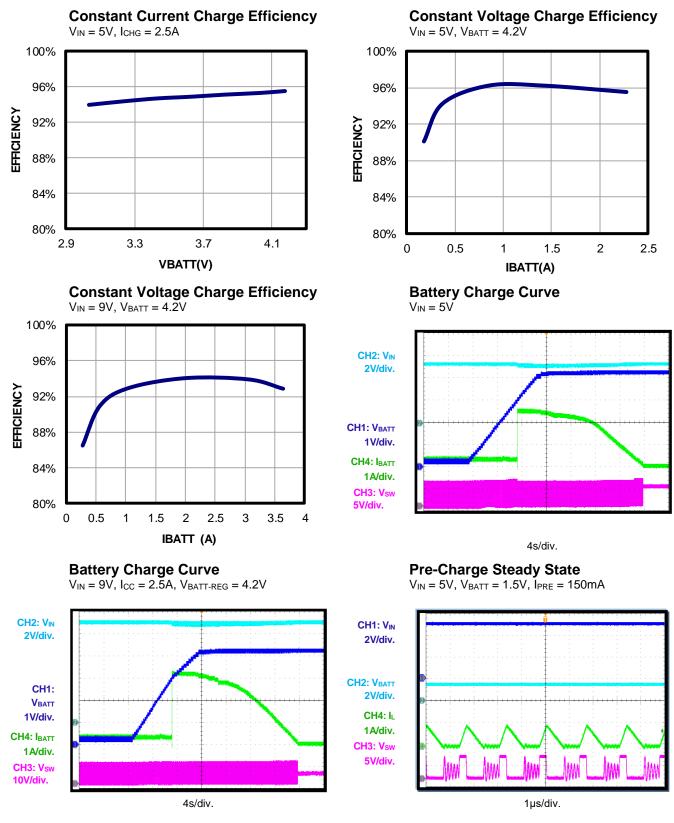

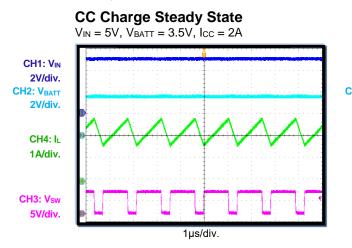

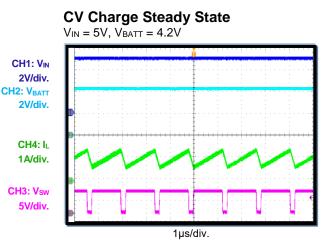

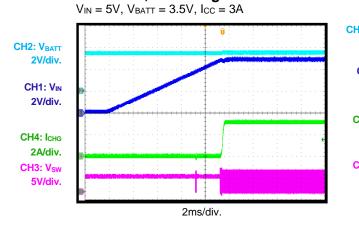

# **TYPICAL PERFORMANCE CHARACTERISTICS**

T<sub>A</sub> = 25°C, battery simulator load, unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$T_A = 25^{\circ}C$ , battery simulator load, unless otherwise noted.

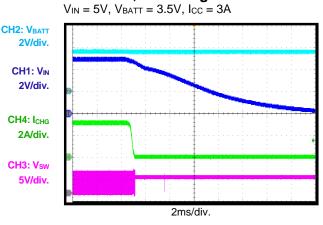

Power On, CC Charge Mode

Power Off, CC Charge Mode

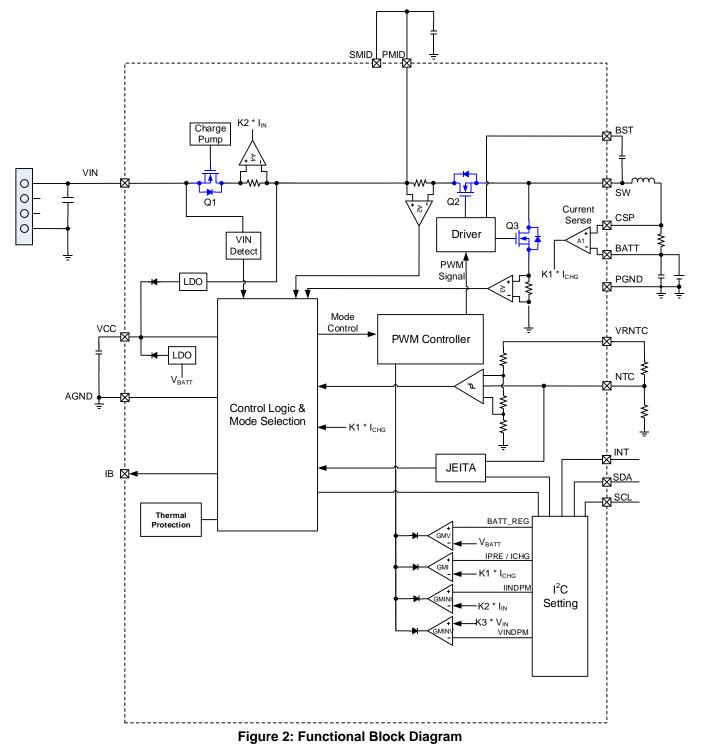

## FUNCTIONAL BLOCK DIAGRAM

## **OPERATION**

#### Introduction

The MP2695 is an I<sup>2</sup>C-controlled switching charger. The IC supports a precision Li-ion or Lipolymer charging system for single-cell applications. When no input is present, the IC operates at a low current to reduce power consumption from the battery.

#### **VCC Power Supply**

VCC provides power for the internal bias circuit and the low-side switch driver. VCC is powered by whichever voltage is highest between PMID and BATT. When the VCC voltage rises above the  $V_{VCC_UV}$  threshold, the I<sup>2</sup>C interface is ready for communication, and all the registers reset to the default value. When the device is switching, VCC can provide up to 30mA for the external load.

#### **Battery Charging Profile**

The IC can run a charging cycle autonomously without host involvement. The host can also control the charge operations and parameters via the registers.

A new charge cycle can start when the following conditions are met:

- V<sub>IN</sub> is above V<sub>IN\_UV</sub>

- VIN is below VIN\_OV

- V<sub>IN</sub> is above V<sub>BATT</sub> + V<sub>HDRM</sub>

- NTC voltage is in the proper range (if NTC\_STOP bit is set to 1)

- No charge timer fault

- Charging is enabled (CHG\_EN = 1)

- No battery over-voltage

After the charge cycle has completed, unplug and re-insert VIN or toggle the CHG\_EN bit to start a new charge cycle.

#### **Charge Cycle**

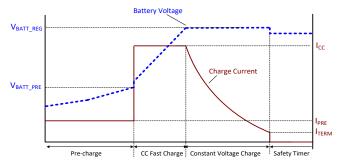

The IC checks the battery voltage to provide three main charging phases: pre-charge, constantcurrent (CC) charge, and constant-voltage (CV) charge (see Figure 3).

The IC regulates the voltage drop on the currentsensing resistor (RS1) for the battery pre-charge and constant-current charge current. Table 1 shows the default value for a  $10m\Omega$  resistor.

| Table 1: Charge Current vs. Battery Voltage |

|---------------------------------------------|

| (RS1 = 10mΩ)                                |

| Battery<br>Voltage | Charge<br>Current | Default<br>Value | CHG_STAT |

|--------------------|-------------------|------------------|----------|

| BATT < 3V          | IPRE[1:0]         | 150mA            | 01       |

| BATT > 3V          | ICC[4:0]          | ЗA               | 10       |

The charge current can be scaled by implementing different current-sensing resistor values, calculated with Equation (1) and Equation (2):

$$I_{cc} = \frac{ICC[4:0] * 10m\Omega}{RS1}$$

(1)

$$I_{PRE} = \frac{IPRE[4:0]*10m\Omega}{RS1}$$

(2)

Note that the soldering tin for the current-sensing resistor has resistance that must be compensated for.

During the entire charging process, the actual charge current may be less than the register setting due to other loop regulations, such as the input current limit or the input voltage limit.

#### **Charge Termination**

Charging terminates if the following conditions occur:

- The charge current is below the termination threshold for 20ms

- The IC works in a constant-voltage charge loop

- The IC is not in the input current loop or input voltage loop

After termination, the status register CHG\_STAT is set to 11, and an INT pulse is generated.

Figure 3: Battery Charge Profile

#### **Automatic Recharge**

When the battery is fully charged and charging is terminated, the battery may be discharged because of system consumption or self-discharge. When the battery voltage is discharged below the recharge threshold ( $V_{BATT_REG} - 200 \text{mV}$ ), the IC starts a new charging cycle automatically if the input power is valid. The timer resets when the auto-recharge cycle begins.

#### **Safety Timer**

The IC provides a safety timer to prevent extended charging cycles due to abnormal battery conditions. The safety timer feature can be disabled via the  $I^2C$ .

The safety timer resets at the beginning of a new charging cycle. The following actions can restart the safety timer:

- A new charge cycle starts

- The EN\_TIMER bit is toggled

- Write 1 to the REG\_RST bit

The IC automatically suspends the timer when any fault occurs. The timer is suspended if an NTC hot or cold fault is detected.

If the safety timer expires before the charge is done, an INT pulse generates and the charge cycle stops.

#### Input Voltage Based and Input Current Based Power Management

The IC features both input current and input voltage based power management by continuously monitoring the input current and input voltage.

When the input current reaches the limit set by IINLIM[2:0], the charge current tapers off to keep the input current from increasing further.

If the preset input current limit is higher than the rating of the adapter, the backup input voltage based power management also works to prevent the input source from being overloaded. When the input voltage falls below the input voltage regulation threshold (set by VINMIN[2:0]) due to a heavy load, the charge current is also reduced to keep the input voltage from dropping further.

An INT pulse generates once the device enters a VINPPM or IINPPM condition.

#### **Thermistor Qualification**

VRNTC is driven to match the VCC voltage when the IC is in charge mode. The IC continuously monitors the battery's temperature by measuring the voltage at the NTC pins. The NTC function can be disabled by setting EN\_NTC = 0.

When NTC\_STOP is set to 1, the NTC voltage should be within the VHOT to VCOLD range for both charge operations. The IC resumes switching when the NTC voltage returns to within the VHOT to VCOLD range.

When NTC\_STOP is set to 0, the IC only generates an interrupt signal and reports the NTC pin status if the NTC\_FAULT[2:0] bits have any changes.

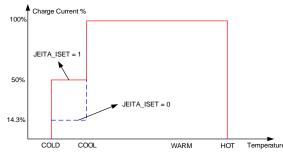

The JEITA profile is supported when the JEITA\_DIS bit is set to 0.

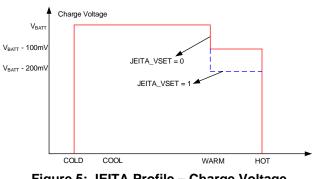

At a cool temperature (VCOLD to VCOOL) range, the charge current is reduced according to the JEITA\_ISET[1:0] setting (see Figure 4).

Figure 4: JEITA Profile – Charge Current

At a warm temperature (VWARM to VHOT) range, the charge voltage is reduced according to the JEITA\_VSET[1:0] setting (see Figure 5).

Figure 5: JEITA Profile – Charge Voltage

The HOT and COLD thresholds have two options in the register. The WARM and COOL thresholds

have four options in the register, which offers accurate and flexible JEITA control.

## Interrupt to Host (INT)

A 50µs interrupt pulse is generated on the opendrain INT pin when any of the following events occur:

- A good input source is detected

- Status register 05H changes

- Fault resister 06H changes

## **Battery Over-Voltage Protection**

When the battery voltage exceeds 104% of  $V_{BATT_REG}$ , the IC immediately suspends charging, the BATT\_OVP bit is set to 1, and an INT is generated. An 800µA current source discharges the battery until it returns to the normal range.

Battery over-voltage protection can be disabled by setting the BATT\_OVP\_DIS bit to 1.

#### Input Over-Voltage Protection

Once IN senses a voltage higher than the VIN\_OVP threshold, the DC/DC converter stops immediately.

The input over-voltage protection threshold can be selected as 6V or 11V by VIN\_OVP bit.

#### **Thermal Shutdown**

The IC continuously monitors the internal junction temperature to maximize power delivery and avoid overheating the chip. When the junction temperature reaches 150°C, the converter shuts down. Normal operation resumes when the junction temperature drops to 120°C.

## **Battery Current Analog Output**

The IC has an IB pin to get the real-time battery current. The voltage at IB ( $V_{IB}$ ) is a fraction of the battery current. It indicates the current flowing into of the battery.

For a  $10m\Omega$  current-sensing resistor in charge mode, calculate V<sub>IB</sub> with Equation (3):

$$V_{IB} = I_{CHG} \times 0.36(V)$$

(3)

Note that scaling the current-sensing resistor also scales the gain of IB.

#### **Series Interface**

The IC uses an I<sup>2</sup>C-compatible interface for flexible charging parameter settings and instantaneous device status reporting. The I<sup>2</sup>C is

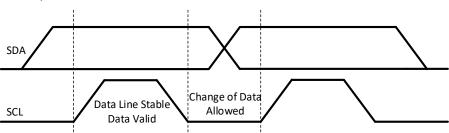

a bidirectional, 2-wire serial interface. Only two bus lines are required: a serial data line (SDA) and serial clock line (SCL).

The I<sup>2</sup>C interface supports both standard mode (up to 100kb) and fast mode (up to 400kb). Both SDA and SCL are bi-directional lines, connecting to the positive supply voltage via a current source or pull-up resistor. When the bus is free, both lines are HIGH. SDA and SCL are open drain.

The data on the SDA line must be stable during the clock's HIGH period. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW. One clock pulse is generated for each data bit transferred.

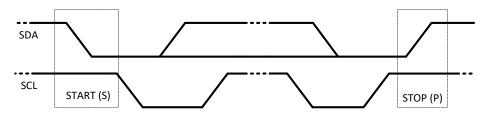

All transactions begin with a START (S) and can be terminated by a STOP (P). A HIGH to LOW transition on the SDA line when SCL is HIGH defines a START condition. A LOW to HIGH transition on the SDA line when SCL is HIGH defines a STOP condition.

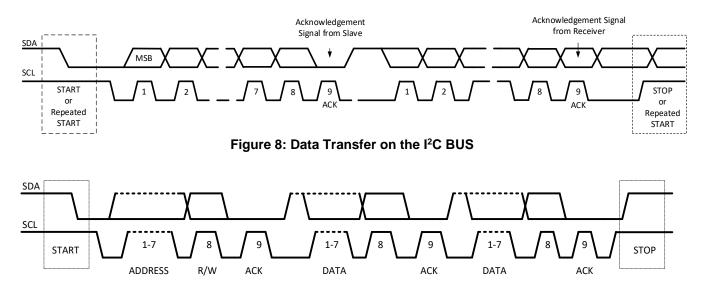

START and STOP conditions are always generated by the master. The bus is considered busy after the START condition, and free after the STOP condition. Every byte on the SDA line must be 8 bits long. The number of bytes to be transmitted per transfer is unrestricted. Each byte must be followed by an acknowledge bit. Data is transferred with the most significant bit (MSB) first. If a slave cannot receive or transmit another complete byte of data until it has performed some other function, it can hold the clock line SCL low to force the master into a wait state (clock stretching). The data transfer continues when the slave is ready for another byte of data and releases the clock line SCL.

An acknowledge bit takes place after every byte. The acknowledge bit allows the receiver to signal to the transmitter that the byte was successfully received; then another byte may be sent. All clock pulses, including the acknowledge ninth clock pulse, are generated by the master.

The transmitter releases the SDA line during the acknowledge clock pulse so the receiver can pull the SDA line LOW. It remains HIGH during the ninth clock pulse; this is not the acknowledge signal. The master can then generate either a STOP to abort the transfer, or a repeated START to begin a new transfer.

After the START, a slave address is sent. This address is 7 bits long, followed by the eighth data direction bit (bit R/W). A 0 indicates a transmission (WRITE), and a 1 indicates a request for data (READ).

If the register address is not defined, the IC sends back negative acknowledgment (NACK) and returns to an idle state.

Figure 6: Bit Transfer on the I<sup>2</sup>C Bus

Figure 7: START and STOP Conditions

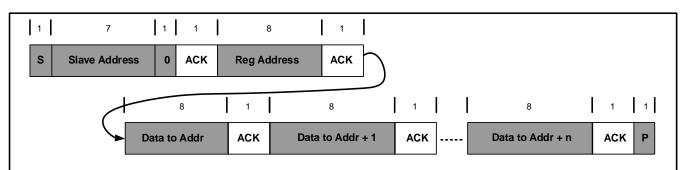

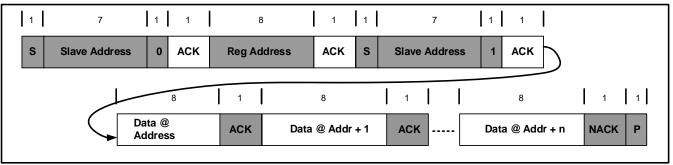

Figure 9: Complete Data Transfer

| 1 | 7             | 1 | 1   | 8           | 1   | 8            | 1   | 1 |

|---|---------------|---|-----|-------------|-----|--------------|-----|---|

| s | Slave Address | 0 | ACK | Reg Address | ACK | Data Address | АСК | Р |

| 5 | Slave Address | 0 | ACK | Reg Address | AUK |              | ACK | P |

Figure 10: Single Write

| 1 | 7             | 1 | 1   | 8           | 1   | 1 | 7             | 1 | 1   | 8    | 1 1    |

|---|---------------|---|-----|-------------|-----|---|---------------|---|-----|------|--------|

| s | Slave Address | 0 | ACK | Reg Address | АСК | s | Slave Address | 1 | ACK | Data | NACK P |

#### Figure 11: Single Read

#### Figure 12: Multi Write

Figure 13: Multi Read

# I<sup>2</sup>C REGISTER MAP

## IC Address: 6BH

| Register Name | Address | R/W | Description                                                       |  |

|---------------|---------|-----|-------------------------------------------------------------------|--|

| REG00         | 0x00    | R/W | Input voltage regulation setting and input current limit setting. |  |

| REG01         | 0x01    | R/W | Charge current setting and pre-charge current setting.            |  |

| REG02         | 0x02    | R/W | Battery regulation voltage and termination current setting.       |  |

| REG05         | 0x05    | R   | Status register.                                                  |  |

| REG06         | 0x06    | R   | Fault register.                                                   |  |

| REG07         | 0x07    | R/W | Miscellaneous control.                                            |  |

| REG08         | 0x08    | R/W | JEITA control.                                                    |  |

#### REG 00H

| Bit | Name      | POR | Reset by<br>REG_RST | R/W | Description                               | Comment                                                                                 |  |  |

|-----|-----------|-----|---------------------|-----|-------------------------------------------|-----------------------------------------------------------------------------------------|--|--|

| 7   | REG_RST   | 0   | Y                   | R/W | 0: Keep current setting<br>1: Reset       | Reset all registers to default.<br>After reset, this bit returns to 0<br>automatically. |  |  |

| 6   | EN_TIMER  | 1   | Y                   | R/W | 0: Disable<br>1: Enable                   | Charge safety timer control.<br>Default: Enable                                         |  |  |

| 5   | VINMIN[2] | 1   | Y                   | R/W | 200mV                                     | Input voltage dynamic                                                                   |  |  |

| 4   | VINMIN[1] | 0   | Y                   | R/W | 100mV                                     | regulation.<br>Offset: 4.45V                                                            |  |  |

| 3   | VINMIN[0] | 0   | Y                   | R/W | 50mV                                      | Range: 4.45V to 4.8V<br>Default: 200mV (4.65V)                                          |  |  |

| 2   | IINLIM[2] | 0   | Y                   | R/W | 000: 100mA<br>001: 500mA<br>010: 1000mA   |                                                                                         |  |  |

| 1   | IINLIM[1] | 0   | Y                   | R/W | 011: 1500mA<br>100: 1800mA                | Input current limit<br>Default: 500mA                                                   |  |  |

| 0   | IINLIM[0] | 1   | Y                   | R/W | 101: 2100mA<br>110: 2400mA<br>111: 3000mA |                                                                                         |  |  |

#### REG 01H

| Bit | Name    | POR | Reset by<br>REG_RST | R/W | Description             | Comment                                                           |

|-----|---------|-----|---------------------|-----|-------------------------|-------------------------------------------------------------------|

| 7   | ICC[4]  | 0   | Y                   | R/W | 1600mA                  | Charge current setting for a                                      |

| 6   | ICC[3]  | 0   | Y                   | R/W | 800mA                   | 10mΩ sensing resistor.<br>Offset: 500mA                           |

| 5   | ICC[2]  | 1   | Y                   | R/W | 400mA                   | Range: 500mA to 3.6A                                              |

| 4   | ICC[1]  | 0   | Y                   | R/W | 200mA                   | Default: 1A<br>A scaling sensing resistor scales                  |

| 3   | ICC[0]  | 1   | Y                   | R/W | 100mA                   | the setting at the same ratio.                                    |

| 2   | EN_NTC  | 1   | Y                   | R/W | 0: Disable<br>1: Enable | Default: Enable                                                   |

| 1   | IPRE[1] | 0   | Y                   | R/W | 01: 150mA               | Pre-charge current setting for a                                  |

| 0   | IPRE[0] | 1   | Y                   | R/W | 10: 250mA<br>11: 350mA  | 10mΩ sensing resistor.<br>Range: 150mA to 350mA<br>Default: 150mA |

## REG 02H

| Bit | Name                   | POR                         | Reset by<br>REG_RST | R/W                                                                   | Description                                                                                                                                      | Comment                                        |

|-----|------------------------|-----------------------------|---------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| 7   | BATT_OVP_DIS           | 0                           | Y                   | R/W                                                                   | 0: Enable battery OVP<br>function<br>1: Disable battery OVP<br>function                                                                          | Default: Enable                                |

| 6   | BATT_REG[2]            | 0                           | Y                   | R/W                                                                   | 000: 3.6V<br>001: 4.1V                                                                                                                           |                                                |

| 5   | BATT_REG[1]            | ATT_REG[1] 1 Y R/W 011: 4.3 |                     | 010: 4.2V<br>011: 4.3V<br>100: 4.35V                                  | Charge voltage regulation.<br>Default: 4.2V                                                                                                      |                                                |

| 4   | BATT_REG[0]            | 0                           | Y                   | R/W                                                                   | 101: 4.4V<br>110: 4.45V                                                                                                                          |                                                |

| 3   | JEITA_DIS              | 1                           | Y                   | R/W                                                                   | 0: JEITA enabled, NTC<br>warm/cool decrease ICC<br>or V <sub>BATT_REG</sub><br>1: JEITA disabled, NTC<br>warm/cool only report<br>status and INT | Default: JEITA disabled                        |

| 2   | ITERM[1]               | 0                           | Y                   | R/W                                                                   | 200mA                                                                                                                                            | Charge termination<br>current for 10mΩ sensing |

| 1   | ITERM[0] 0 Y R/W 100mA |                             | 100mA               | resistor.<br>Offset: 100mA<br>Range: 100mA to 400mA<br>Default: 100mA |                                                                                                                                                  |                                                |

| 0   | CHG_EN                 | 1                           | Y                   | R/W                                                                   | 0: Disable charge<br>1: Enable charge                                                                                                            | Default: Enable charge                         |

| Bit | Name         | POR | Reset by REG_RST | R/W                                                  | Description                            | Comment                 |

|-----|--------------|-----|------------------|------------------------------------------------------|----------------------------------------|-------------------------|

| 7   | Reserved     | N/A | N/A              | A N/A N/A                                            |                                        |                         |

| 6   | Reserved     | N/A | N/A              | N/A                                                  | N/A                                    |                         |

| 5   | CHG_STAT [1] | 0   | Υ                | R                                                    | 00: Not charging<br>01: Pre-charge     |                         |

| 4   | CHG_STAT [0] | 0   | Υ                | R                                                    | 10: CC or CV charge<br>11: Charge done |                         |

| 3   | VPPM_STAT    | 0   | Y                | R                                                    | 0: No VINPPM<br>1: VINPPM              |                         |

| 2   | IPPM_STAT    | 0   | Y                | R                                                    | 0: No IINPPM<br>1: IINPPM              |                         |

| 1   | USB1_PLUG_IN | 0   | Y                | R 0: USB1 is not plugged in<br>1: USB1 is plugged in |                                        | V <sub>IN</sub> > 3.45V |

| 0   | Reserved     | 0   | Y                | R                                                    |                                        |                         |

#### REG 05H

An interrupt is asserted when any bit of this REG changes.

#### REG 06H

| Bit | Name          | POR | Reset by<br>REG_RST | R/W | Description                                | Comment                                                                                                           |

|-----|---------------|-----|---------------------|-----|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| 7   | BATT_UVLO     | 0   | Y                   | R   | 0: Battery not ULVO<br>1: Battery UVLO     | If battery UVLO is<br>touched, bit is set to 1.<br>When the battery is<br>charged again, this bit<br>resets to 0. |

| 6   | Reserved      | N/A | N/A                 | N/A | N/A                                        |                                                                                                                   |

| 5   | Reserved      | N/A | N/A                 | N/A | N/A                                        |                                                                                                                   |

| 4   | CHG_FAULT [1] | 0   | Y                   | R   | 00: Normal<br>01: USB1 UV                  |                                                                                                                   |

| 3   | CHG_FAULT [0] | 0   | Y                   | R   | 10: USB1 OV<br>11: Safety timer expiration |                                                                                                                   |

| 2   | NTC_FAULT [2] | 0   | Y                   | R   | 000: Normal                                |                                                                                                                   |

| 1   | NTC_FAULT [1] |     | Y                   | R   | 001: Warm<br>010: Cool                     |                                                                                                                   |

| 0   | NTC_FAULT [0] | 0   | Y                   | R   | 011: Cold<br>100: Hot                      |                                                                                                                   |

An interrupt signal is asserted when any bit of this REG changes.

MP2695 Rev. 1.0 4/11/2019

## REG 07H

| Bit | Name     | POR | Reset<br>by<br>REG_R<br>ST | R/W | Description                                                                                                                      | Comment         |

|-----|----------|-----|----------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 7   | Reserved | N/A | N/A                        | N/A | N/A                                                                                                                              |                 |

| 6   | Reserved | N/A | N/A                        | N/A | N/A                                                                                                                              |                 |

| 5   | BATT_OVP | 0   | Y                          | R   | 0: Battery normal<br>1: Battery OVP                                                                                              |                 |

| 4   | NTC_STOP | 1   | Y                          | R/W | <ul><li>0: NTC out of window only report<br/>in register</li><li>1: NTC out of window suspend the<br/>charge operation</li></ul> |                 |

| 3   | VIN_OVP  | 0   | Y                          | R/W | 0: VIN_OVP = 6V<br>1: VIN_OVP = 11V                                                                                              |                 |

| 2   | SW_FREQ  | 0   | Y                          | R/W | 0: 700kHz<br>1: 1200kHz                                                                                                          | Default: 700kHz |

| 1   | Reserved | N/A | N/A                        | N/A | N/A                                                                                                                              |                 |

| 0   | Reserved | N/A | N/A                        | N/A | N/A                                                                                                                              |                 |

#### REG 08H

| Bit | Name       | POR | Reset by<br>REG_RST | R/W | Description                                                                  | Comment                                    |  |

|-----|------------|-----|---------------------|-----|------------------------------------------------------------------------------|--------------------------------------------|--|

| 7   | JEITA_VSET | 1   | Y                   | R/W | 0: V <sub>BATT_REG</sub> minus 100mV<br>1: V <sub>BATT_REG</sub> minus 200mV | Default: VBATTFULL minus 200mV             |  |

| 6   | JEITA_ISET | 1   | Y                   | R/W | 0: 14.3% of ICC<br>1: 50% of ICC                                             | Default: 50% of ICC                        |  |

| 5   | VHOT       | 1   | Y                   | R/W | 0: 34%<br>1: 36%                                                             | Hot threshold setting default: 36%         |  |

| 4   | VWARM[1]   | 0   | Y                   | R/W | 00: 44%<br>01: 40%                                                           | Warm threshold setting                     |  |

| 3   | VWARM[0]   | 1   | Y                   | R/W | 10: 38%<br>11: 36%                                                           | Default: 40%                               |  |

| 2   | VCOOL[1]   | 1   | Y                   | R/W | 00: 72%<br>01: 68%                                                           | Cool threshold setting                     |  |

| 1   | VCOOL[0]   | 1   | Y                   | R/W | 10: 64%<br>11: 60%                                                           | Default: 60%                               |  |

| 0   | VCOLD      | 0   | Y                   | R/W | 0: 72%<br>1: 68%                                                             | Cold threshold setting<br>Default: 72% (0) |  |

#### REG 0AH (8)

| Bit | Name     | POR | Reset by<br>REG_RST | R/W | Description                                                      | Comment                                      |

|-----|----------|-----|---------------------|-----|------------------------------------------------------------------|----------------------------------------------|

| 7   | TMR      | 0   | N/A                 | N/A | 0: Charge timer is 20hrs<br>1: Charge timer is 10hrs             | Default:<br>0: Charge timer is 20hrs         |

| 6   | Reserved | N/A | N/A                 | N/A | N/A                                                              |                                              |

| 5   | Reserved | N/A | N/A                 | N/A | N/A                                                              |                                              |

| 4   | Reserved | N/A | N/A                 | N/A | N/A                                                              |                                              |

| 3   | VPRE     | 0   | N/A                 | N/A | 0: Pre-charge threshold is 3V<br>1: Pre-charge threshold is 2.5V | Default:<br>0: Pre-charge threshold<br>is 3V |

| 2   | Reserved | N/A | N/A                 | N/A | N/A                                                              |                                              |

| 1   | Reserved | N/A | N/A                 | N/A | N/A                                                              |                                              |

| 0   | Reserved | N/A | N/A                 | N/A | N/A                                                              |                                              |

#### Note:

8) Register 0AH is for OTP only and not accessible to users.

## **OTP MAP**

| #    | Bit7 | Bit6 | Bit5       | Bit4         | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------------|--------------|------|------|------|------|

| 0x02 | N/A  | BAT  | T_REG: 3.6 | V to 4.45V   | N/A  | N/A  | N/A  | N/A  |

| 0x07 | N/A  | N/A  | N/A        | N/A NTC_STOP |      | N/A  | N/A  | N/A  |

| 0x0A | TMR  | N/A  | N/A        | N/A          | VPRE | N/A  | N/A  | N/A  |

#### **OTP DEFAULT**

| OTP items     | Default                                 |  |

|---------------|-----------------------------------------|--|

| BATT_REG[2:0] | T_REG[2:0] 4.2V                         |  |

| NTC_STOP      | 1: NTC out of window suspend the charge |  |

| VIN_OVP       | 0: VIN_OVP = 6V                         |  |

| TMR           | 0: Charge timer is 20hrs                |  |

| VPRE          | 0: Pre-charge threshold is 3V           |  |

## **APPLICATION INFORMATION**

#### **NTC Function**

The JEITA profile is supported for the battery temperature management. For a given NTC thermistor, select an appropriate  $R_{T1}$  and  $R_{T2}$  to set the NTC window, calculated with Equation (4) and Equation (5):

$$R_{T1} = \frac{R_{NTC\_HOT} \times R_{NTC\_COLD} \times (V_{COLD} - V_{HOT})}{V_{COLD} \times V_{HOT} \times (R_{NTC\_COLD} - R_{NTC\_HOT})}$$

(4)

$$R_{T_{2}} = \frac{R_{NTC\_HOT} \times R_{NTC\_COLD} \times (V_{COLD} - V_{HOT})}{V_{HOT} \times (1 - V_{COLD}) \times R_{NTC\_COLD} - V_{COLD} \times (1 - V_{HOT}) \times R_{NTC\_HOT}}$$

(5)

Where  $R_{NTC\_HOT}$  is the value of the NTC resistor at the upper bound of its operating temperature range, and  $R_{NTC\_COLD}$  is the value at its lower bound.  $V_{COLD}$  is the hot temperature threshold percentage, which can be selected as 72% or 68%.  $V_{HOT}$  is the cold temperature threshold percentage, which can be selected as 34% or 36%.

The warm and cool temperature threshold can be calculated using Equation (6) and Equation (7):

$$V_{\text{WARM}} = \frac{R_{\text{T2}} // R_{\text{NTC}_{\text{WARM}}}}{R_{\text{T1}} + R_{\text{T2}} // R_{\text{NTC}_{\text{WARM}}}}$$

(6)

$$V_{\text{COOL}} = \frac{R_{T2} //R_{\text{NTC}_{\text{COOL}}}}{R_{T1} + R_{T2} //R_{\text{NTC}_{\text{COOL}}}}$$

(7)

Choose the nearest warm/cool threshold in REG08H using the results from the calculations above.

If no external NTC is available, connect  $R_{T1}$  and  $R_{T2}$  to keep the voltage on NTC within the valid NTC window (e.g.  $R_{T1} = R_{T2} = 10k\Omega$ ).

#### Selecting the Inductor

Inductor selection requires a tradeoff between cost, size, and efficiency. A lower inductance value means a smaller size, but results in higher current ripple, magnetic hysteretic losses, and output capacitances. A higher inductance value offers lower ripple current and smaller output filter capacitors, but results in higher inductor DC resistance (DCR) loss.

Table 2 shows the recommended values to choose the best inductor for the desired application.

| RS1(mΩ) | Max Icc (A) | L (µH) |  |

|---------|-------------|--------|--|

| 10      | 3.6         | 1      |  |

| 20      | 1.8         | 2.2    |  |

| 30      | 1.2         | 3.3    |  |

| 50      | 0.72        | 4.7    |  |

**Table 2: Inductance Selection Guide**

Choose an inductor that does not saturate under the worst-case load condition.

## Selecting the PMID Capacitor (C<sub>PMID</sub>)

Select the PMID capacitor ( $C_{PMID}$ ) based on the demand of the PMID current ripple.

In charge mode,  $C_{PMID}$  acts as the input capacitor of the buck converter. The input current ripple is calculated using Equation (8):

$$I_{\text{RMS}_{\text{MAX}}} = I_{\text{CC}_{\text{MAX}}} \times \frac{\sqrt{V_{\text{BATT}} \times (V_{\text{IN}} - V_{\text{BATT}})}}{V_{\text{IN}}} \quad (8)$$

Select the PMID capacitors based on the ripple current temperature rise not exceeding 10°C. For best results, use ceramic capacitors with X5R dielectrics, low ESR, and small temperature coefficients.

# Compensating in the Current-Sensing Resistor

The soldering tin has resistance. For a  $10m\Omega$  resistor soldered on the PCB, the total resistance between resistor pads is about  $11m\Omega$  to  $12m\Omega$ .

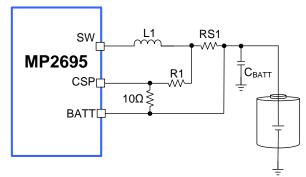

One effective compensation method is to apply a resistor divider for the CSP/BATT pins (see Figure 14).

Figure 14: Current-Sensing Compensation

After the PCB is assembled, apply a 2A DC current source between SW and BATT. Measure the voltage drop across the current-sensing

resistor on its PCB pads, which is  $V_{CS}$ . R1 can then be calculated using Equation (9):

$$R1 = \frac{Vcs - 2 \times RS1}{2 \times RS1} \times 10\Omega$$

(9)

#### **PCB Layout Guidelines**

Efficient PCB layout is critical to meet specified noise, efficiency, and stability requirements. For the best performance, follow the guidelines below:

- 1. Place the PMID capacitor as close as possible to PMID and PGND.

- 2. Keep the PMID capacitor's return trace to the IC's PMID and PGND pins as short as possible.

- 3. Connect AGND to the ground of the PMID capacitor.

- 4. Keep the switching node short.

- 5. Connect the power pads for VIN, PMID, and PGND to as many coppers planes on the board as possible to improve thermal performance by conducting heat to the PCB.

# **TYPICAL APPLICATION CIRCUITS**

Figure 15: Typical Application Circuit for Power Bank

| Qty | Ref              | Value | Description                         | Package | Manufacture |

|-----|------------------|-------|-------------------------------------|---------|-------------|

| 1   | CIN              | 1µF   | Ceramic capacitor, 16V, X5R or X7R  | 0603    | Any         |

| 1   | C <sub>MID</sub> | 10µF  | Ceramic capacitor, 16V, X5R or X7R  | 0805    | Any         |

| 1   | Сватт            | 22µF  | Ceramic capacitor, 10V, X5R or X7R  | 0805    | Any         |

| 1   | Cvcc             | 2.2µF | Ceramic capacitor, 6.3V, X5R or X7R | 0603    | Any         |

| 1   | CBST             | 470nF | Ceramic capacitor, 16V, X5R or X7R  | 0603    | Any         |

| 1   | L1               | 1µH   | Inductor, 1µH, low DCR              | SMD     | Any         |

| 1   | RS1              | 10mΩ  | Film resistor, 1%                   | 1206    | Any         |

#### Table 3: Key BOM of Figure 15

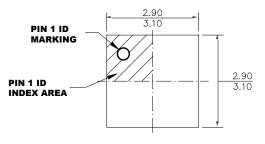

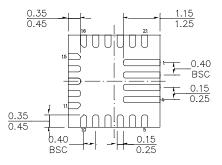

## PACKAGE INFORMATION

TOP VIEW

SIDE VIEW

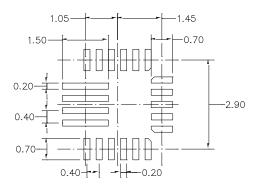

#### RECOMMENDED LAND PATTERN

#### NOTE:

ALL DIMENSIONS ARE IN MILLIMETERS.

LEAD COPLANARITY SHALL BE 0.08 MILLIMETERS MAX.

JEDEC REFERENCE IS MO-220.

DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third-party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.