mEZDPD1620AS-84D7

mEZ20A-12Vin-2.5Vout-15A

## DESCRIPTION

This is a fully integrated power module with a PMBus interface. This device offers a complete power solution with excellent load and line regulation over a wide input voltage range. It operates with high efficiency over a wide load range and can be paralleled to deliver a higher load current.

This power module adopts MPS's proprietary, multi-phase constant-on-time (MCOT) control, which provides ultra-fast transient response and simple loop compensation. The PMBus interface provides module configurations and monitoring of key parameters.

## **SPECIFICATION OVERVIEW**

| Гоит                    | 15A  |

|-------------------------|------|

| Vout                    | 2.5V |

| Typical V <sub>IN</sub> | 12V  |

| V <sub>IN</sub> Min     | 9V   |

| V <sub>IN</sub> Max     | 15V  |

# **FEATURES**

- Auto-Interleaving for Multi-Phase Operation

- Auto-Compensation with Adaptive MCOT for Ultra-Fast Transient Response

- 1% Reference Voltage over 0°C to +70°C Junction Temperature Range

- True Remote Sense of Output Voltage

- PMBus 1.3 Compliant

- Telemetry Readback, Including VIN, VOUT, IOUT, Temperature, and Faults

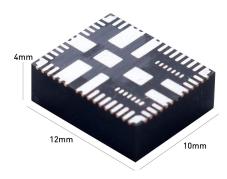

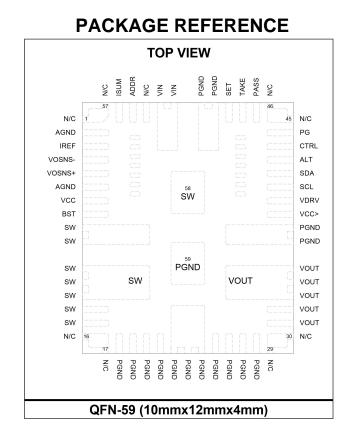

- Available in a QFN-59 (10mmx12mmx4mm) Package

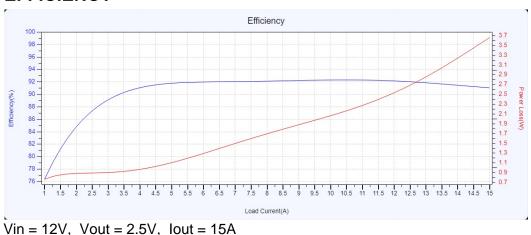

# EFFICIENCY

12/19/2019

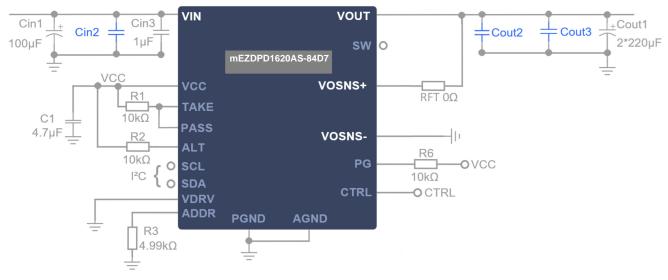

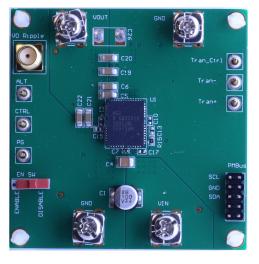

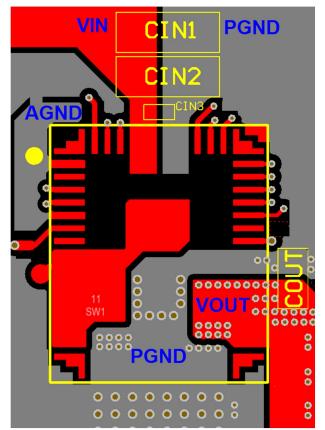

# **TYPICAL APPLICATION**

## BOM

12/19/2019

| Reference Quantity Value |   | Value                                                   | Description Package                            |        | Manufacturer       | Part Number        |  |

|--------------------------|---|---------------------------------------------------------|------------------------------------------------|--------|--------------------|--------------------|--|

| Cin1                     | 1 | 100uF                                                   | Cap, Electrolytic, 35V SMD NIPPON<br>CHEMI-CON |        | EMZJ350ADA101MF80G |                    |  |

| Cin2                     | 4 | 4.7uF                                                   | Cap,Ceramic,50V,X7R(material)                  | '1206' | MuRata             | GRM31CR71H475K     |  |

| Cin3                     | 1 | 1uF                                                     | Cap, Ceramic, 25V, X7R                         | '0603' | Murata             | GRM188R71E105KA12D |  |

| Cout1                    | 2 | 220uF                                                   | Cap, Electrolytic, 6.3V, Tantalum              | D2     | Panasonic          | EEFCX0J221R        |  |

| Cout2                    | 6 | 47uF                                                    | Cap,Ceramic,16V,X5R(material)                  | '1210' | MuRata             | GRM32ER61C476K     |  |

| Cout3                    |   | NS                                                      | NS                                             |        |                    |                    |  |

| C1                       | 1 | 4.7uF                                                   | Cap, Ceramic, 25V, X7R                         | '0603' | Murata             | GRM188R61E475KE11D |  |

| C2                       | 1 | 4.7uF                                                   | Cap, Ceramic, 25V, X7R                         | '0603' | Murata             | GRM188R61E475KE11D |  |

| R1                       | 1 | 10kohm                                                  | Film Res,1%                                    | '0603' | YAGEO              | RC0603FR-0710KL    |  |

| R2                       | 1 | 10kohm                                                  | Film Res,1%                                    | '0603' | YAGEO              | RC0603FR-0710KL    |  |

| R3                       | 1 | 4.99kohm                                                | Film Res,1%                                    | '0603' | YAGEO              | RC0603FR-074K99L   |  |

| R6                       | 1 | 10kohm                                                  | Film Res,1%                                    | '0603' | YAGEO              | RC0603FR-074K99L   |  |

| RFT                      | 1 | 0ohm                                                    | Film Res,1%                                    | '0603' | YAGEO              | RC0603FR-070RL     |  |

|                          |   | Programmable 16V DC/DC Power<br>module supply up to 20A | QFN-59<br>(10x12x4mm)                          | MPS    | mEZDPD1620AS       |                    |  |

# ORDERING INFORMATION

| Part Number       | Finalize Design to Order                          |

|-------------------|---------------------------------------------------|

| mEZDPD1620AS-84D7 | https://www.monolithicpower.com/mezdpd1620as.html |

# **OTHER ORDERING OPTIONS**

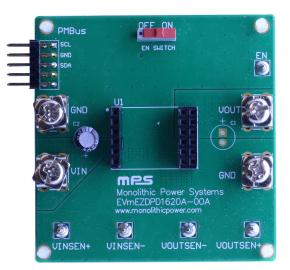

## **Evaluation Board for Surface Mount Device**

The evaluation board is designed to demonstrate the capabilities of your custom MPS mEZDPD1620AS-84D7.

The EVB device is programmed with custom configuration.

| Part Number        |  |

|--------------------|--|

| EVmEZDPD1620AS-00A |  |

## **DIP Mount (Pin Out Version)**

The mEZDPD1620AS-84D7 is your custom device on a DIP mount for an easy-to-use, plug-and-play form factor.

The pin out module device is programmed with custom configuration.

| Part Number |  |

|-------------|--|

| mEZDPD1620A |  |

## Socket Evaluation Board for DIP Mount

DIP mount socket only. For easy evaluation of pin out module.

| Part Number       |  |

|-------------------|--|

| EVmEZDPD1620A-00A |  |

All EVB schematic and layout files can be found at: https://www.monolithicpower.com/mezdpd1620as.html

# **PIN FUNCTIONS**

| PIN #                                   | Name   | Description                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2, 6                                    | AGND   | Analog ground. Reference point of the control circuit.                                                                                                                                                                                                                                                                                                                     |

| 3                                       | IREF   | Current reference output. Keep this pin floating.                                                                                                                                                                                                                                                                                                                          |

| 4                                       | VOSNS- | <b>Output voltage sense negative return.</b> Connect directly to the GND sense point of the load. Short to GND if remote sense is not used.                                                                                                                                                                                                                                |

| 5                                       | VOSNS+ | <b>Output voltage sense positive return.</b> Connect this pin to the positive sense point of the output voltage to provide feedback voltage to the system.                                                                                                                                                                                                                 |

| 7                                       | VCC    | <b>Output of the internal 3.3V LDO.</b> The driver and control circuits are powered by this voltage. Must be connected to pin 38.                                                                                                                                                                                                                                          |

| 8                                       | BST    | Bootstrap. Keep this pin floating.                                                                                                                                                                                                                                                                                                                                         |

| 9, 10, 11,<br>12, 13, 14,<br>15, 58     | SW     | Switch node. Keep them floating.                                                                                                                                                                                                                                                                                                                                           |

| 31, 32, 33,<br>34, 35                   | VOUT   | Module output voltage node. Connect with wide PCB copper plane.                                                                                                                                                                                                                                                                                                            |

| 18-28, 36,<br>37, 50, 51,<br>59         | PGND   | <b>Power ground.</b> This pin is the reference point of the regulated output voltage. Connect with PCB copper planes as wide as possible.                                                                                                                                                                                                                                  |

| 38                                      | VCC>   | Input of driver circuit. Must be connected to pin 7.                                                                                                                                                                                                                                                                                                                       |

| 39                                      | VDRV   | Decoupling pin for 3.3V driver power supply.                                                                                                                                                                                                                                                                                                                               |

| 40                                      | SCL    | PMBus serial clock.                                                                                                                                                                                                                                                                                                                                                        |

| 41                                      | SDA    | PMBus serial data.                                                                                                                                                                                                                                                                                                                                                         |

| 42                                      | ALT    | <b>PMBus alert.</b> Open-drain output, active low. A pull-up resistor must be connected to a 3.3V rail.                                                                                                                                                                                                                                                                    |

| 43                                      | CTRL   | <b>Converter control.</b> CTRL is a digital input that turns the regulator on or off. Drive CTRL high to turn the regulator on, drive it low to turn the regulator off. Do not float this pin.                                                                                                                                                                             |

| 44                                      | PG     | <b>Multi-purpose power good output.</b> This pin can be configured as an output pin for single-phase operation, or as an input and output pin for multi-phase configuration. A pull-up resistor connected to a DC voltage must indicate high if the output voltage exceeds 90% of the nominal voltage. See the Application Information section for detailed configuration. |

| 47                                      | PASS   | <b>Passes run signal to the next phase.</b> See the Applications Information section for connection details.                                                                                                                                                                                                                                                               |

| 48                                      | TAKE   | <b>Receives run signal from the previous phase.</b> See the Typical Application on page 2 for connection details.                                                                                                                                                                                                                                                          |

| 49                                      | SET    | <b>PWM signal.</b> The set signal turns on the HS-FET when a run signal appears. For multi-phase operation, tie the SET pins of all the phases together.                                                                                                                                                                                                                   |

| 52, 53                                  | VIN    | <b>Supply voltage.</b> This pin provides power to the module. Decoupling capacitors must be connected between VIN and GND. Connect VIN with a wide copper plane.                                                                                                                                                                                                           |

| 55                                      | ADDR   | <b>PMBus slave address setting pin.</b> Connect a resistor between this pin and AGND to set the address of this device.                                                                                                                                                                                                                                                    |

| 56                                      | ISUM   | <b>Reference current output.</b> For single-phase operation, keep this pin floating. For multi-phase operation, connect the ISUM pins of all phases together.                                                                                                                                                                                                              |

| 1, 16, 17,<br>29, 30, 45,<br>46, 54, 57 | NC     | No internal connection.                                                                                                                                                                                                                                                                                                                                                    |

## **ABSOLUTE MAXIMUM RATINGS** (1)

| Supply voltage (V <sub>IN</sub> )                                    |

|----------------------------------------------------------------------|

| $V_{SW(DC)}$ 0.3V to $V_{IN}$ + 0.3V                                 |

| V <sub>SW</sub> (25ns) <sup>(2)</sup> 3V to +25V                     |

| V <sub>SW</sub> (25ns)5V to +25V                                     |

| V <sub>OUT</sub> 5.5V                                                |

| V <sub>BST</sub> V <sub>SW</sub> + 4V                                |

| V <sub>CC</sub>                                                      |

| CTRL current (I <sub>CTRL</sub> ) 2.5mA                              |

| All other pins0.3V to +4.3V                                          |

| Continuous power dissipation ( $T_A = +25^{\circ}C$ ) <sup>(3)</sup> |

| 5W                                                                   |

| Junction temperature 170°C                                           |

| Lead temperature                                                     |

| Storage temperature65°C to +170°C                                    |

#### **Recommended Operating Conditions** <sup>(4)</sup>

| Supply voltage (V <sub>IN</sub> )         | 4V to 16V |

|-------------------------------------------|-----------|

| Output voltage (Vout)                     |           |

| External V <sub>CC</sub> bias             |           |

| CTRL current (I <sub>CTRL</sub> )         | 1mA       |

| Operating junction temp (T <sub>J</sub> ) |           |

####

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) Measured by using differential oscilloscope probe.

- 3) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX) - T<sub>A</sub>) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 5) Measured on EVM3695-25-RF-02A, 6-layer demo board PCB.

12/19/2019

# **PROGRAMMABLE ELECTRICAL CHARACTERISTICS**

| Parameters                                                    | Symbol               | Condition        | Min | Тур    | Max | Units |

|---------------------------------------------------------------|----------------------|------------------|-----|--------|-----|-------|

| Input Voltage                                                 |                      |                  |     |        |     |       |

| Input voltage range                                           | V <sub>IN</sub>      | Programmed value |     | 9      |     | V     |

| Input over-voltage fault limit                                |                      | Programmed value |     | 16.5   |     | V     |

| Input over-voltage warning<br>limit                           |                      | Programmed value |     | 16.5   |     | V     |

| Input voltage under-voltage<br>warning limit                  |                      | Programmed value |     | 4      |     | V     |

| Output Voltage                                                |                      |                  |     |        |     |       |

| V <sub>OUT</sub> command <sup>(6)</sup>                       | Vout                 | Programmed value |     | 2.5    |     | V     |

| Output voltage scale                                          | VOUT_SCALE           | Programmed value |     | 0.25   |     |       |

| Output voltage margin high                                    | Vout_margin_<br>High | Programmed value |     | 2.688  |     | V     |

| Output voltage margin low                                     | VOUT_MARGIN_<br>LOW  | Programmed value |     | 2.132  |     | V     |

| Output voltage min                                            | Vout_min             | Programmed value |     | 0.5    |     | V     |

| Output voltage max                                            | Vout_max             | Programmed value |     | 6      |     | V     |

| Output voltage step                                           | VOUT_STEP            | Programmed value |     | 10     |     | µs/m∖ |

| Current Limit                                                 |                      |                  |     |        |     |       |

| Valley current limit                                          | LIM_VALLEY           | Programmed value |     | 39     |     | A     |

| Min valley current limit<br>programmable value <sup>(6)</sup> | ILIM_ VALLEY _MIN    | Programmed value |     | 0      |     | A     |

| Max current limit<br>programmable value <sup>(6)</sup>        | ILIM_VALLEY_MAX      | Programmed value |     | 46.5   |     | A     |

| Low-side negative current<br>limit in OVP                     | ILIM_NEG_OVP         | Programmed value |     | -10    |     | A     |

| Delay time after low-side<br>negative current limit in OVP    | tdelay_nocp          | Programmed value |     | 100    |     | ns    |

| Output current limit (DC)                                     | ILIM_DC              | Programmed value |     | 38.962 |     | A     |

| Output over-current warning<br>(DC)                           | Iwarn_dc             | Programmed value |     | 35.09  |     | A     |

| Over-current fault hiccup<br>interval time                    | titv_hiccup          | Programmed value |     | 0      |     | ms    |

| Frequency                                                     |                      |                  |     |        |     |       |

| Switching frequency                                           | fsw                  | Programmed value |     | 800    |     | kHz   |

| Output Over-Voltage and Un                                    | der-Voltage Pr       | otection         |     |        |     |       |

| OVP threshold                                                 | Vovp                 | Programmed value |     | 115%   |     | VREF  |

| UVP threshold                                                 | VUVP                 | Programmed value |     | 50%    |     | VREF  |

| Soft Start and Turn On/Off D                                  | elay                 |                  |     |        |     |       |

| Soft-start time                                               | tss                  | Programmed value |     | 2      |     | ms    |

| Turn-on delay <sup>(6)</sup>                                  | ton_delay            | Programmed value |     | 0      |     | ms    |

| Turn-off delay                                                | toff_delay           | Programmed value |     | 0      |     | ms    |

| Under-Voltage Lockout (UVL                                 | 0)                          |                                             |      |                  |

|------------------------------------------------------------|-----------------------------|---------------------------------------------|------|------------------|

| Input programmable turn-on voltage                         | VIN_ON                      | Programmed value                            | 8    | V                |

| Input programmable turn-off voltage                        | $V_{\text{IN}\_\text{OFF}}$ | Programmed value                            | 5    | V                |

| Min input programmable turn-<br>on voltage                 | VIN_ON_MIN                  | Programmed value,<br>V <sub>CC</sub> = 3.3V | 3    | V                |

| Max input programmable<br>turn-on voltage                  | VIN_ON_MAX                  | Programmed value                            | 15   | V                |

| Min input programmable turn-<br>off voltage <sup>(6)</sup> | VIN_OFF_MIN                 | Programmed value, $V_{CC} = 3.3V$           | 2.75 | V                |

| Max input programmable turn-<br>off voltage                | VIN_OFF_MAX                 | Programmed value                            | 7.75 | V                |

| Power Good                                                 |                             |                                             |      |                  |

| Power good high threshold,<br>PG_ON                        | PG <sub>Vth_Hi</sub>        | Programmed value                            | 90%  | V <sub>REF</sub> |

| Power good low threshold,<br>PG_OFF                        | PG <sub>Vth_Lo</sub>        | Programmed value                            | 70%  | V <sub>REF</sub> |

| Power good low-to-high<br>delay, PG delay                  | $PG_{Td}$                   | Programmed value                            | 1    | ms               |

| Thermal Protection (TP)                                    |                             |                                             |      |                  |

| TP fault rising threshold <sup>(6)</sup>                   | T <sub>SD_RISE</sub>        | Programmed value                            | 155  | °C               |

| TP warning rising threshold <sup>(6)</sup>                 | Twarn_rise                  | Programmed value                            | 145  | °C               |

| TP hysteresis                                              |                             | Programmed value                            | 20   | °C               |

| Compensation                                               |                             |                                             |      | 4                |

| Ramp                                                       |                             | Programmed value                            | 5.6  | mV               |

# **PROGRAMMABLE OPERATION SETTINGS**

| Name                         | Selected<br>Mode                                                                                                                                                                                                       | Description                                                                                                                                                                                              | Notes |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Output Voltage               |                                                                                                                                                                                                                        |                                                                                                                                                                                                          |       |

| Output voltage diseberge     |                                                                                                                                                                                                                        | 0: No active                                                                                                                                                                                             |       |

| Output voltage discharge     | 1                                                                                                                                                                                                                      | 1: At CTRL low                                                                                                                                                                                           |       |

| Output voltage range         | 10                                                                                                                                                                                                                     | Chooses the internal voltage divider ratio.<br>00: External divider (0.5~0.672V)<br>01: Internal divider2:1 (0.5~1.344V)<br>10: Internal divider4:1 (0.7~2.688V)<br>11: Internal divider8:1 (1.3~5.376V) |       |

| Light-Load Operation Mode    |                                                                                                                                                                                                                        |                                                                                                                                                                                                          |       |

| Skip CCM (SYNC)              | 1                                                                                                                                                                                                                      | 0: Pulse skip mode<br>1: Forced CCM                                                                                                                                                                      |       |

| Protection Response          |                                                                                                                                                                                                                        |                                                                                                                                                                                                          |       |

| Over-current response        | 0                                                                                                                                                                                                                      | 0: Latch-off<br>1: Retry                                                                                                                                                                                 |       |

| Output over-voltage response | over-voltage response 0: Latch-off with output discharge<br>1: Latch-off without output discharge<br>2: HICCUP with output discharge<br>3: HICCUP without output discharge                                             |                                                                                                                                                                                                          |       |

| TP response                  | 0                                                                                                                                                                                                                      | 0: Latch-off<br>1: Retry                                                                                                                                                                                 |       |

| Compensation                 |                                                                                                                                                                                                                        |                                                                                                                                                                                                          |       |

| Slave Fault Detection 1      |                                                                                                                                                                                                                        | Enable or disable the slave fault detection function<br>through the PG pin.<br>0: Enable<br>1: Disable                                                                                                   |       |

| Operation                    |                                                                                                                                                                                                                        |                                                                                                                                                                                                          |       |

| Operation                    | Operation is a paged register. The operation<br>command turns the converter output on/off in<br>conjunction with input from the CTRL pin. It also sets<br>the output voltage to the upper or lower MARGIN<br>voltages. |                                                                                                                                                                                                          |       |

| <b>On/Off Configuration</b> |   |                                                                                                                                                                                                                                                                                                                                                                                                    |      |

|-----------------------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| PON                         | 1 | <ul> <li>0: Enable converter (converter powers up any time the input voltage is present regardless of the state of the CTRL pin)</li> <li>1: Disable converter (converter does not power up until commanded by the CTRL pin and operation command)</li> </ul>                                                                                                                                      |      |

| OP                          | 1 | <ul><li>0: Ignore (converter ignores the "on" bit in the operation command from the PMBus)</li><li>1: Response (converter responses the "on" bit in the operation command from the PMBus)</li></ul>                                                                                                                                                                                                |      |

| EN                          | 1 | 0: Ignore CTRL pin (on/off controlled only by the operation command)<br>1: Require CTRL pin                                                                                                                                                                                                                                                                                                        |      |

| POL                         | 1 | <ul><li>0: Active low (Pull the CTRL pin low to start the converter)</li><li>1: Active high (Pull the CTRL pin high to start the converter)</li></ul>                                                                                                                                                                                                                                              |      |

| Write Protect               |   |                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| Write protect 0             |   | Controls writing to the converter.<br>0: Enable all<br>1: Disable function 1 (disable all writes except to the<br>WRITE_PROTECT, OPERATION, PAGE,<br>ON_OFF_CONFIG and VOUT_COMMAND<br>commands)<br>2: Disable function 2 (disable all writes except to the<br>WRITE_PROTECT, OPERATION and PAGE<br>commands)<br>3: Disable function 3 (disable all writes except to the<br>WRITE_PROTECT command) |      |

| Address PMBus               |   |                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| Enable                      | 0 | Address selection method<br>0: The address is decided by the ADDR pin<br>1: The address is decided by MFR_ADDR_PMBUS                                                                                                                                                                                                                                                                               |      |

| Address                     | 0 | Device Address                                                                                                                                                                                                                                                                                                                                                                                     | ADDR |

| Extra Functions             |   |                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| Total OC hiccup interval    | 0 | 0: Fixed OCP hiccup interval<br>1: Adjustable OCP hiccup                                                                                                                                                                                                                                                                                                                                           |      |

| OSM                         | 0 | 0: Enable OSM (output sink mode)<br>1: Disable OSM                                                                                                                                                                                                                                                                                                                                                 |      |

| Phase operation             | 0 | 0: For single-phase operation<br>1: For multi-phase operation                                                                                                                                                                                                                                                                                                                                      |      |

# **ELECTRICAL CHARACTERISTICS**

## $V_{IN} = 12V$ , $V_{EN} = 2V$ , $T_A = -40^{\circ}C$ to $125^{\circ}C$ , typical values refer to $T_J = 25^{\circ}C$ , unless otherwise noted.

| Parameters                                       | Symbol             | Condition                                                 | Min | Тур             | Max  | Units  |

|--------------------------------------------------|--------------------|-----------------------------------------------------------|-----|-----------------|------|--------|

| V <sub>IN</sub> Supply Current                   | •                  |                                                           |     |                 |      |        |

| Supply current (shutdown)                        | l <sub>IN</sub>    | V <sub>CTRL</sub> = 0V                                    |     | 2.5             | 4    | mA     |

| Output Voltage                                   | 1                  | 1                                                         |     |                 | L    | 1      |

| Load regulation <sup>(6)</sup>                   | VOUT_DC_LOAD       | IOUT from 0A to 25A                                       |     | ±0.5            |      | % Vout |

| Line regulation <sup>(6)</sup>                   | VOUT_DC_LINE       | V <sub>IN</sub> from 4V to 16V,<br>I <sub>OUT</sub> = 20A |     | ±0.5            |      | % Vout |

| CTRL                                             | ·                  |                                                           |     |                 |      |        |

| CTRL on threshold                                | CTRLON             |                                                           |     | 2.04            | 2.2  | V      |

| CTRL off threshold                               | CTRLOFF            |                                                           |     | 1.66            |      | V      |

| Frequency and Timer                              | ÷.                 |                                                           |     |                 |      |        |

| Minimum on time <sup>(6)</sup>                   | ton_min            | f <sub>sw</sub> = 1000kHz, V <sub>0</sub> = 0.6V          |     | 50              |      | ns     |

| Minimum off time (6)                             | toff_min           | V <sub>FB</sub> = 580mV                                   |     | 220             |      | ns     |

| Output Over-Voltage and Und                      | er-Voltage Pro     | otection                                                  |     |                 |      |        |

| OSM threshold rising                             | Vosm_rise          |                                                           |     | 104%            |      | VREF   |

| OSM threshold falling                            | Vosm_Fall          |                                                           |     | 102%            |      | VREF   |

| ADC <sup>(6)</sup>                               | 1                  | -                                                         |     |                 |      |        |

| Voltage range                                    |                    |                                                           | 0   |                 | 1.28 | V      |

| ADC resolution                                   |                    |                                                           |     | 10              |      | Bits   |

| DNL                                              |                    |                                                           |     | 1               |      | LSB    |

| Sample rate                                      |                    |                                                           |     | 3               |      | kHz    |

| DAC (Feedback Voltage)                           |                    |                                                           |     |                 |      |        |

| Range                                            |                    |                                                           | 500 | 600             | 672  | mV     |

| Feedback accuracy                                | V <sub>FB</sub>    | T <sub>J</sub> = 25°C                                     | 594 | 600             | 606  | mV     |

| Feedback accuracy                                | V <sub>FB</sub>    | T <sub>J</sub> = -40°C to +125°C                          | 591 | 600             | 609  | mV     |

| Resolution <sup>(6)</sup>                        |                    | Per LSB                                                   |     | 2               |      | mV     |

| Feedback voltage with margin high <sup>(6)</sup> | Vfb_mg_high        |                                                           |     | 672             |      | mV     |

| Feedback voltage with margin low <sup>(6)</sup>  | VFB_MG_LOW         |                                                           |     | 500             |      | mV     |

| Error Amplifier                                  |                    |                                                           | 1   |                 |      |        |

| Feedback current                                 | I <sub>FB</sub>    | V <sub>FB</sub> = V <sub>REF</sub>                        |     | 50              | 100  | nA     |

| Soft Shutdown                                    |                    |                                                           |     |                 |      |        |

| Soft shutdown discharge FET                      | Ron_disch          |                                                           |     | 60              |      | Ω      |

| Under-Voltage Lockout (UVLC                      | ))                 |                                                           |     |                 |      |        |

| VCC under-voltage lockout threshold rising       | VCC <sub>Vth</sub> | Default setting                                           | 2.6 | 2.75            | 2.9  | V      |

| VCC under-voltage lockout threshold hysteresis   | VCC <sub>HYS</sub> | Default setting                                           | 200 | Default setting |      | mV     |

# ELECTRICAL CHARACTERISTICS (continued)

## $V_{IN}$ = 12V, $T_J$ = -40°C to +125°C, unless otherwise noted.

| Parameters                                  | Symbol                | Condition                                                                                          | Min  | Тур  | Max  | Units |

|---------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------|------|------|------|-------|

| Power Good                                  |                       |                                                                                                    |      |      |      |       |

| Power good sink current capability          | V <sub>PG</sub>       | I <sub>PG</sub> = 10mA                                                                             |      |      | 0.3  | V     |

| Power good leakage current                  | IPG LEAK              | V <sub>PG</sub> = 3V                                                                               |      | 1.5  |      | μA    |

| Power good low-level output                 | V <sub>OL 100</sub>   | $V_{IN}$ = 0V, pull PGOOD up to<br>3.3V through a 100k $\Omega$<br>resistor, T <sub>J</sub> = 25°C |      | 600  | 720  | mV    |

| voltage                                     | Vol 10                | $V_{IN} = 0V$ , pull PGOOD up to<br>3.3V through a $10k\Omega$ resistor,<br>$T_J = 25^{\circ}C$    |      | 700  | 820  |       |

| Monitoring Parameters                       |                       |                                                                                                    |      |      |      |       |

| Output voltage monitor accuracy             | M <sub>VOUT</sub> ACC | V <sub>O</sub> = 0.6V                                                                              | -2%  | 0.6  | 2%   | V     |

| Output voltage bit resolution               |                       |                                                                                                    |      | 1.5  |      | mV    |

| Output current monitor accuracy             | MIOUT ACC             | $V_{O}$ = 1.2V, f <sub>SW</sub> = 600kHz,<br>I <sub>O</sub> = 20A                                  | -10% | 20   | 10%  | А     |

| Output current bit resolution (6)           |                       |                                                                                                    |      | 62.5 |      | mA    |

| Input voltage monitor accuracy              | MIN ACC               |                                                                                                    | -2%  | 12   | 2%   | V     |

| Input voltage bit resolution <sup>(7)</sup> |                       |                                                                                                    |      | 25   |      | mV    |

| PMBus DC Characteristics (SDA               | SCL. ALE              | RT) (6)                                                                                            |      |      |      |       |

| Input high voltage                          | V <sub>IH</sub>       |                                                                                                    |      |      | 2.1  | V     |

| Input low voltage                           | VIL                   |                                                                                                    | 0.8  |      |      | V     |

| Output low voltage                          | Vol                   | I <sub>OL</sub> = 1mA                                                                              |      |      | 0.4  | V     |

| Input leakage current                       | I <sub>LEAK</sub>     | SDA, SCL, ALERT = 3.3V                                                                             | -10  |      | 10   | μA    |

| Maximum voltage (SDA, SCL,<br>ALERT, CTRL)  | V <sub>MAX</sub>      | Transient voltage including<br>ringing                                                             | -0.3 | 3.3  | 3.6  | V     |

| Pin capacitance on SDA,SCL                  | C <sub>PIN</sub>      |                                                                                                    |      |      | 10   | pF    |

| PMBus Timing Characteristics (              | 7)                    |                                                                                                    |      |      |      |       |

| Min operating frequency                     |                       |                                                                                                    |      | 10   |      | kHz   |

| Max operating frequency                     |                       |                                                                                                    |      | 1000 |      | kHz   |

| Bus free time                               |                       | Between stop and start<br>conditions                                                               | 4.7  |      |      | μs    |

| Holding time                                |                       |                                                                                                    | 4.0  |      |      | μs    |

| Repeated start condition set-up time        |                       |                                                                                                    | 4.7  |      |      | μs    |

| Stop condition set-up time                  |                       |                                                                                                    | 4.0  |      |      | μs    |

| Data hold time                              |                       |                                                                                                    | 300  |      |      | ns    |

| Data set-up time                            |                       |                                                                                                    | 250  |      |      | ns    |

| Clock low time out                          |                       |                                                                                                    | 25   |      | 35   | ms    |

| Clock low period                            |                       |                                                                                                    | 4.7  |      |      | μs    |

| Clock high period                           |                       |                                                                                                    | 4.0  |      | 50   | μs    |

| Clock/data fall time                        |                       |                                                                                                    |      |      | 300  | ns    |

| Clock/data rise time                        |                       |                                                                                                    |      |      | 1000 | ns    |

Notes:

6) Guaranteed by design, not tested in production. The parameter is tested during parameters characterization.

7) Typical Performance Characteristics.

# **TYPICAL PERFORMANCE CHARACTERISTICS**

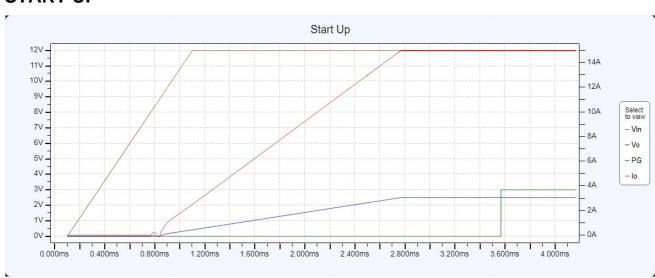

All waveforms simulated.

# EFFICIENCY

Vin = 12V, Vout = 2.5V, Iout = 15A

# **START UP**

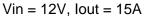

# **VIN SHUTDOWN**

Vin = 12V, lout = 15A

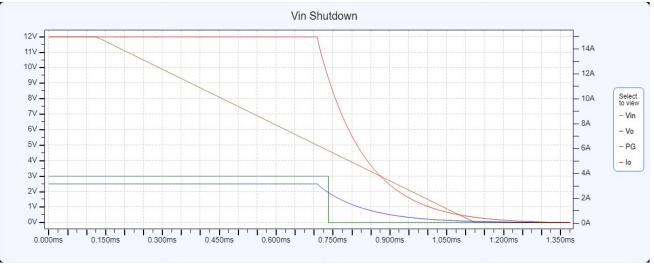

# **STEADY STATE RIPPLE**

Vin = 12V, lout = 15A

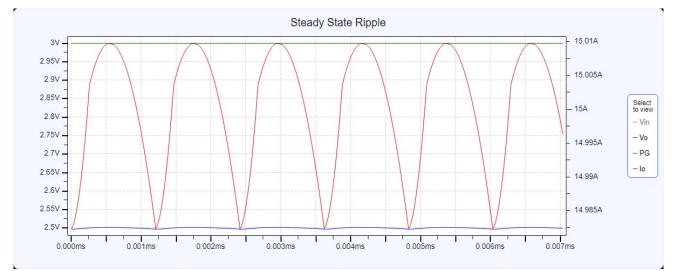

# LOAD TRANSIENT

Vin = 12V, Ihigh = 15A, Ilow =7.5A, Slew rate =  $1A/\mu s$

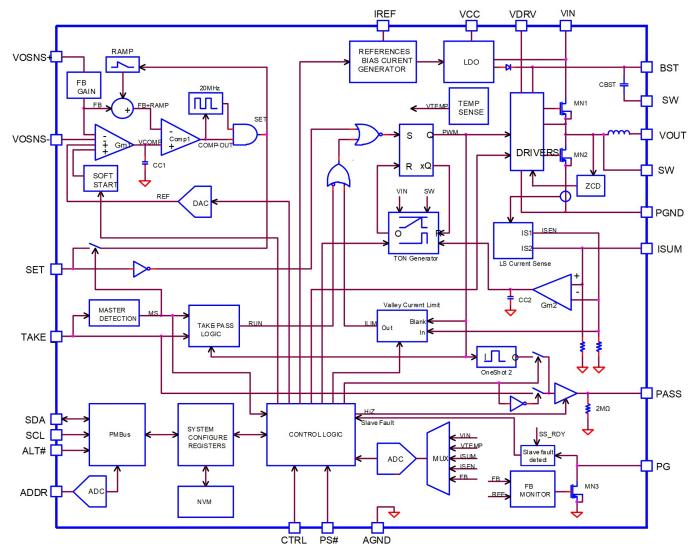

## FUNCTIONAL BLOCK DIAGRAM

Figure 1: Functional Block Diagram

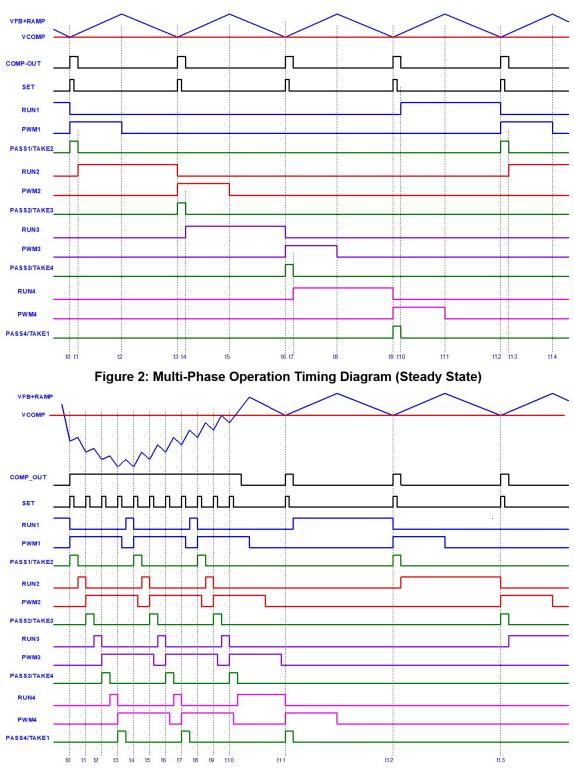

Figure 3: Multi-Phase Operation Timing Diagram (Transient)

## **OPERATION**

This device is a fully integrated power solution in a 10mmx12mmx4mm QFN package. For higher current applications, this device can be connected in parallel to provide a higher output current. This device employs constant-on-time (COT) control to provide fast transient response. The internal ramp compensation guarantees stable operation for applications using zero-ESR ceramic output capacitors.

#### **RAMP** Compensation

12/19/2019

This device guarantees stable operation with zero-ESR ceramic output capacitors by using internal RAMP compensation. A triangular RAMP signal is generated internally, and is superimposed on the FB signal. The triangular RAMP signal starts to rise once RAMP+FB drops below the REF signal, and a SET pulse is generated. The rise time of the RAMP signal is fixed. The amplitude of the RAMP compensation is selectable through the PMBus command of D0h[3:1] to support wide operation configurations. There is a trade-off between the stability and load transient response. A larger RAMP signal provides higher stability, but a slower load transient response, and vice versa. Consequently, it is necessary to optimize the RAMP compensation selection based on the design criteria for each application.

#### **APPLICATION INFORMATION**

#### **Operation Mode Selection**

This device provides both forced CCM and pulse-skip operation in a light-load condition.

#### **Output Voltage Setting**

A feedback resistor divider is required to set the proper feedback gain. The values of the feedback resistors are determined using Equation (1):

$$\mathsf{R}_{2}(\mathsf{k}\Omega) = \frac{0.6}{\mathsf{V}_{0} - 0.6} \times \mathsf{R}_{1}(\mathsf{k}\Omega) \tag{1}$$

where  $V_0$  is the output voltage. The output voltage feedback gain is determined with Equation (2):

$$G_{FB} = \frac{R_2}{R_1 + R_2}$$

(2)

To optimize the load transient response, a feedforward capacitor ( $C_{FF}$ ) must be placed in parallel with R1. Table 1 lists the values of the feedback resistors and the feed-forward capacitor for common output voltages.

Table 1: Common Output Voltages

| Vo  | R₁ (kΩ) | R₂ (kΩ) | C <sub>FF</sub> (nF) |

|-----|---------|---------|----------------------|

| 0.9 | 0.5     | 1       | 33                   |

| 1.2 | 1       | 1       | 33                   |

| 1.8 | 2       | 1       | 33                   |

| 3.3 | 4.53    | 1       | 4.7                  |

| 5   | 7.32    | 1       | 4.7                  |

This device offers output voltage programmability through the PMBus. In addition, the output voltage can be adjusted within a certain range through the PMBus by adjusting the internal reference voltage of the PMW controller ( $V_{REF}$ ). The reference voltage, which has a default value of 0.6V, can be adjusted between 0.5V and 0.672V. For a given feedback resistor network, the upper and lower limits of the output voltage are determined with Equation (3a) and Equation (3b):

$$V_{o,max} = \frac{0.672}{G_{FB}}$$

(3a)

$$V_{o,min} = \frac{0.5}{G_{FB}}$$

(3b)

Two steps must be followed to program the output voltage through the PMBus:

- Write the G<sub>FB</sub> value determined by Equation (2) to register VOUT\_SCALE\_LOOP (29h).

- 2. Write the output voltage command to register VOUT\_COMMAND (21h).

$V_{\text{REF}}$  is updated automatically based on the output voltage command and  $G_{\text{FB}}$ .

Output voltage monitoring through the PMBus is enabled by setting the register VOUT\_SCALE\_LOOP (29h) with a value that matches the  $G_{FB}$  value from Equation (2).

For applications where a PMBus interface is not required,  $V_{REF} = 0.6V$  is used by default, and operates in analog mode. The feedback resistors should be determined based on Equation (1).

#### Soft Start

The soft-start (SS) time can be programmed through the PMBus.

#### Pre-Bias Start-Up

The device is designed for monotonic start-up into pre-biased loads. If the output voltage is pre-biased to a certain voltage during start-up, both the high-side and low-side switches are disabled until the internal reference voltage exceeds the sensed output voltage at FB.

#### **Output Voltage Discharge**

The output voltage discharge mode is enabled if the device is disabled through the CTRL pin. In such a case, both the high-side and low-side switches are latched off. A discharge FET connected between SW and GND turns on to discharge the output capacitor. A typical on resistance of the discharge FET is  $60\Omega$ . Once the FB voltage drops below 10% of the reference output voltage, the discharge FET turns off.

This feature can be enabled or disabled through the MFR\_CTRL\_VOUT (D1h) command.

# Current Sense and Over-Current Protection (OCP)

This device features on-die current sense and a programmable positive current limit threshold.

The device provides both inductor valley current limits (set by register D7h).

# Inductor Valley Over-Current Protection (D7h)

During the LS-FET on state, the inductor current is sensed and monitored cycle by cycle. The HS-FET is only be allowed to turn on if over-current is not detected during the LS-FET on state. If 31 consecutive cycles of an OC condition are detected, OCP is triggered.

During an over-current condition or output short-circuit condition, if the output voltage drops below the under-voltage protection (UVP) threshold, the device enters OCP immediately.

Once OCP is triggered, it either enters hiccup mode or latch-off mode, depending on the register. It should be noted that  $V_{CC}$  or CTRL must be power recycled to re-enable the device once it latches off.

The inductor valley over-current limit can be programmed through register D7h, which sets the per-phase inductor valley current limit for both single-phrase and multi-phase operation.

#### **Negative Inductor Current limit**

When the LS-FET detects a negative current lower than the limit set through register D5h[2], the part turns off its LS-FET for a period of time to limit the negative current. The period is set through register D5h[3].

#### **Under-Voltage Protection (UVP)**

The device monitors the output voltage through the FB pin to detect an under-voltage condition. If the FB voltage drops below the UVP threshold (set through register VOUT\_UV\_FAULT\_LIMIT), UVP is triggered. After UVP is triggered, the device enters either hiccup or latch-off mode, depending on the PMBus selection. Please note that  $V_{CC}$  or CTRL must be power recycled to re-enable the device once it latches off.

## **Over-Voltage Protection (OVP)**

The device monitors the output voltage using the FB pin connected to the tap of a resistor divider to detect an over-voltage condition. See the register VOUT\_OV\_FAULT\_RESPONSE section for additional information on OVP.

## Output Sinking Mode (OSM)

The device enters OSM when the output voltage is more than 5% above the reference and below the OVP threshold. Once OSM is triggered, the device runs in forced CCM. The

device exits OSM when the HS-FET turns back on.

#### **Over-Temperature Protection (OTP)**

The device monitors the junction temperature. If the junction temperature exceeds the threshold value (set by register OT\_FAULT\_LIMIT), the converter enters either hiccup or latch-off mode depending on the PMBus selection. Please note that  $V_{CC}$  or CTRL must be power recycled to re-enable the device once it latches off.

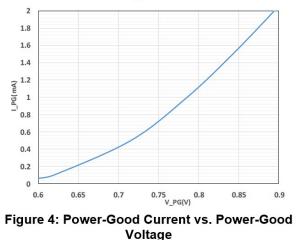

#### Power Good (PG)

The device has an open-drain power-good (PG) output. The PG pin can be configured as an output only, or as an input and output pin by bit [0] of register MRF\_CTRL\_COMP (D0h). For single-phase configuration, PG should be configured as output-only. For multi-phase operation, PG should be configured as an input and output pin to detect faults from the slave phases. PG must be pulled high to V<sub>CC</sub> or a voltage source with less than 3.6V through a pull-up resistor (typically 100k $\Omega$ ).

PG is pulled low initially once input voltage is applied to the device. After the FB voltage reaches the threshold set by register POWER\_GOOD\_ON, and a delay set by the register MFR\_CTRL\_VOUT, PG is pulled high.

PG is latched low if any fault occurs, and the relevant protection feature is triggered (e.g. UV, OV, OT, UVLO, etc.). After PG is latched low, it cannot be pulled high again unless a new soft start is initialized.

If the input supply fails to power the device, PG is latched low. Figure 4 shows the relationship between the PG voltage and the pull-up current.

#### **Input Capacitor**

The buck converter has a discontinuous input current, and requires a capacitor to supply the AC current to the step-down module while maintaining the DC input voltage. Use ceramic capacitors for the best performance. During layout, place the input capacitors as close to the IN pin as possible.

The capacitance can vary significantly with temperature. It is recommended to use capacitors with X5R and X7R ceramic dielectrics, because they are fairly stable over a wide temperature range.

The capacitors must also have a ripple current rating that exceeds the converter's maximum input ripple current. Estimate the input ripple current using Equation (4):

$$I_{CIN} = I_{OUT} \times \sqrt{\frac{V_{OUT}}{V_{IN}} \times (1 - \frac{V_{OUT}}{V_{IN}})}$$

(4)

The worst-case condition occurs at  $V_{IN} = 2V_{OUT}$ , calculated with Equation (5):

$$I_{CIN} = \frac{I_{OUT}}{2}$$

(5)

For simplification, choose an input capacitor with an RMS current rating that exceeds half the maximum load current.

The input capacitance value determines the converter input voltage ripple. Select a capacitor value that meets any input voltage ripple requirements.

Estimate the input voltage ripple using Equation (6):

$$\Delta V_{\rm IN} = \frac{I_{\rm OUT}}{F_{\rm SW} \times C_{\rm IN}} \times \frac{V_{\rm OUT}}{V_{\rm IN}} \times (1 - \frac{V_{\rm OUT}}{V_{\rm IN}})$$

(6)

The worst-case condition occurs at  $V_{IN} = 2V_{OUT}$ , calculated with Equation (7):

$$\Delta V_{\rm IN} = \frac{1}{4} \times \frac{I_{\rm OUT}}{F_{\rm SW} \times C_{\rm IN}}$$

(7)

#### **Output Capacitor**

The output capacitor maintains the DC output voltage. Use ceramic capacitors or POSCAPs. Estimate the output voltage ripple using Equation (8):

$$\Delta V_{OUT} = \frac{V_{OUT}}{F_{SW} \times L} \times (1 - \frac{V_{OUT}}{V_{IN}}) \times (R_{ESR} + \frac{1}{8 \times F_{SW} \times C_{OUT}})$$

(8)

Where the module internal inductor is 0.36µH.

When using ceramic capacitors, the capacitance dominates the impedance at the switching frequency. The capacitance also dominates the output voltage ripple. For simplification, estimate the output voltage ripple using Equation (9):

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{8 \times F_{\text{SW}}^2 \times L \times C_{\text{OUT}}} \times (1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}) \quad (9)$$

The ESR dominates the impedance at the switching frequency for POSCAPs, so the output voltage ripple is determined by the ESR value.

For simplification, the output ripple can be approximated using Equation (10):

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{F_{\text{SW}} \times L} \times (1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}) \times R_{\text{ESR}}$$

(10)

#### **PCB Layout Guidelines**

PCB layout plays an important role to achieve stable operation. For optimal performance, refer to Figure 5 and follow the guidelines below:

- 1. Place the input ceramic capacitors as close to the VIN and PGND pins as possible on the same layer of the DEVICE.

- 2. Maximize the VIN and PGND copper plane to minimize the parasitic impedance.

- 3. Place VIN vias at least 1cm from the part to minimize noise coupling from input pulsating current.

- 4. Connect AGND to a solid ground plane through a single point.

- 5. Place sufficient output GND vias close to the GND pins to minimize both parasitic impedance and thermal resistance.

- 6. Keep the ISUM trace as short as possible. The ISUM trace should be away from the VIN copper in a multi-phase configuration. Vias should be avoided whenever possible.

- 7. The keep-out area must be kept clean.

- 8. Signal traces should avoid the area directly beneath the SW pad unless a PGND layer is used to provide shielding.

Figure 5: Example Layout - Top Layer

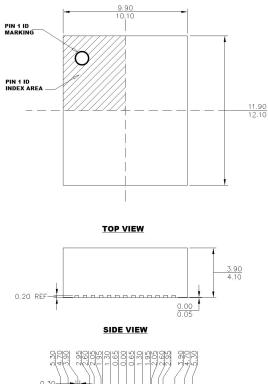

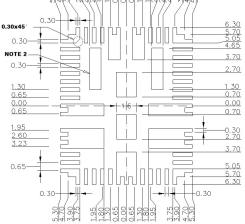

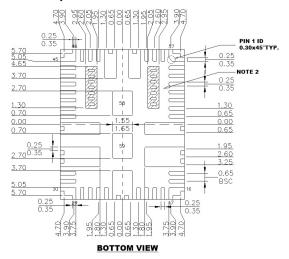

# PACKAGE INFORMATION

#### QFN-59 (10mmx12mmx4mm)

RECOMMENDED LAND PATTERN

#### NOTE:

1) ALL DIMENSIONS ARE IN MILLIMETERS. 2) SHADED AREA IS THE KEEP-OUT ZONE. ANY PCB METAL TRACE AND VIA ARE NOT ALLOWED TO CONNECT TO THIS AREA ELECTRICALLY OR MECHANICALLY. 3) LEAD COPLANARITY SHALL BE 0.08 MILLIMETERS MAX. 4) JEDEC REFERENCE IS MO-220. 5) DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third-party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.