# ARM Cortex®-M0 32-bit Microcontroller

## NuMicro<sup>®</sup> Family NUC121/125 Series Technical Reference Manual

The information described in this document is the exclusive intellectual property of Nuvoton Technology Corporation and shall not be reproduced without permission from Nuvoton.

Nuvoton is providing this document only for reference purposes of NuMicro microcontroller based system design. Nuvoton assumes no responsibility for errors or omissions.

All data and specifications are subject to change without notice.

For additional information or questions, please contact: Nuvoton Technology Corporation.

www.nuvoton.com

| т | Δ | R | ı | F | 0 | F | C | O | N  | т | F | N | Т | S |

|---|---|---|---|---|---|---|---|---|----|---|---|---|---|---|

|   | _ | ш | _ | _ | u |   | • | u | ıw |   | _ | v |   | • |

| 1 GE   | NERAL DESCRIPTION                                       | 18 |

|--------|---------------------------------------------------------|----|

| 1.1    | Key Features Support Table                              | 18 |

| 2 FE   | ATURES                                                  | 19 |

| 2.1    | NuMicro® NUC121/125 Features                            | 19 |

| 3 Abl  | breviationsbreviations                                  | 25 |

| 3.1    | Abbreviations                                           | 25 |

| 4 PA   | RTS INFORMATION LIST AND PIN CONFIGURATION              | 27 |

| 4.1    | NuMicro® NUC121/125 Selection Guide                     | 27 |

| 4.1.1  | NuMicro <sup>®</sup> NUC121/125 Naming Rule             | 27 |

| 4.1.2  | NuMicro® NUC121 USB Series Selection Guide              | 28 |

| 4.1.3  | NuMicro® NUC125 USB Series Selection Guide              | 28 |

| 4.2    | Pin Configuration                                       | 29 |

| 4.2.1  | NuMicro® NUC121 QFN 33-Pin Diagram                      | 29 |

| 4.2.2  | NuMicro® NUC121 QFN 33-Pin Function Diagram             | 30 |

| 4.2.3  | NuMicro® NUC121 LQFP 48-Pin Diagram                     | 31 |

| 4.2.4  | NuMicro® NUC121 LQFP 48-Pin Function Diagram            | 32 |

| 4.2.5  | NuMicro® NUC121 LQFP 64-Pin Diagram                     | 33 |

| 4.2.6  | NuMicro® NUC121 LQFP 64-Pin Function Diagram            | 34 |

| 4.2.7  | NuMicro <sup>®</sup> NUC125 QFN 33-Pin Diagram          | 35 |

| 4.2.8  | NuMicro <sup>®</sup> NUC125 QFN 33-Pin Function Diagram | 36 |

| 4.2.9  | NuMicro <sup>®</sup> NUC125 LQFP 48-Pin Diagram         | 37 |

| 4.2.10 | NuMicro® NUC125 LQFP 48-Pin Function Diagram            | 38 |

| 4.2.11 |                                                         |    |

| 4.2.12 | NuMicro® NUC125 LQFP 64-Pin Function Diagram            | 40 |

| 4.3    | Pin Description                                         | 41 |

| 4.3.1  | NUC121 USB Series QFN33 Pin Description                 | 41 |

| 4.3.2  | NUC121 USB Series LQFP48 Pin Description                | 45 |

| 4.3.3  | NUC121 USB Series LQFP64 Pin Description                | 51 |

| 4.3.4  | NUC125 USB Series QFN33 Pin Description                 | 59 |

| 4.3.5  | NUC125 USB Series LQFP48 Pin Description                | 63 |

| 4.3.6  | NUC125 USB Series LQFP64 Pin Description                | 69 |

| 4.3.7  | GPIO Multi-function Pin Summary                         | 77 |

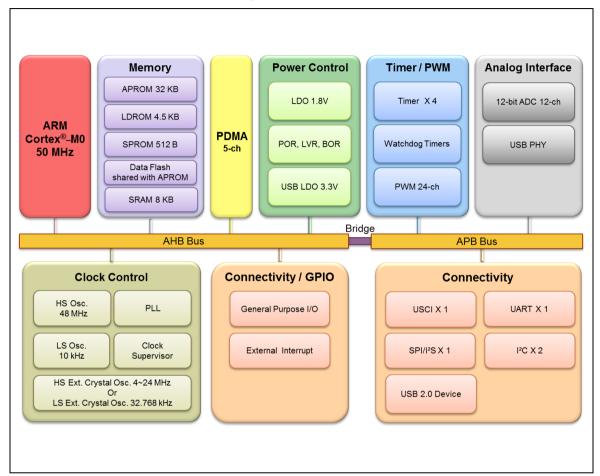

| 5 BL   | OCK DIAGRAM                                             | 83 |

| 5.1    | NuMicro® NUC121/125 Block Diagram                       | 83 |

| 6 | FUI    | NCTIONAL DESCRIPTION                           | 84  |

|---|--------|------------------------------------------------|-----|

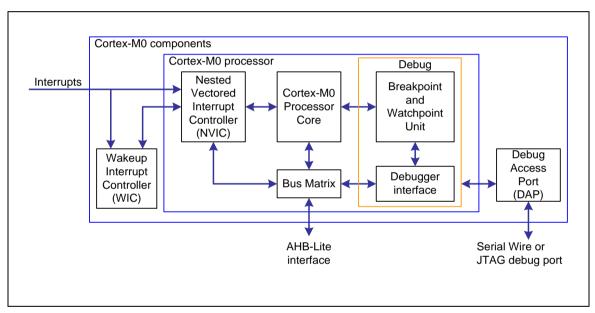

|   | 6.1    | ARM® Cortex®-M0 Core                           | 84  |

|   | 6.2    | System Manager                                 | 86  |

|   | 6.2.1  | Overview                                       | 86  |

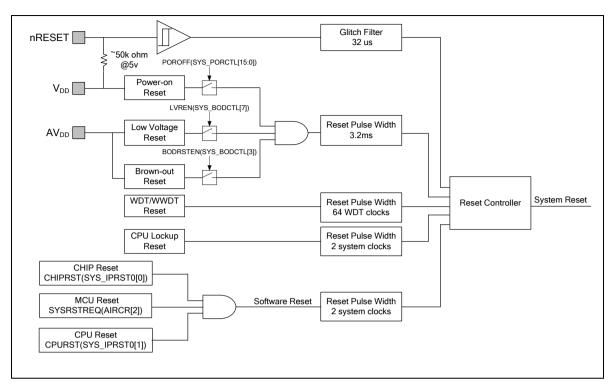

|   | 6.2.2  | System Reset                                   | 86  |

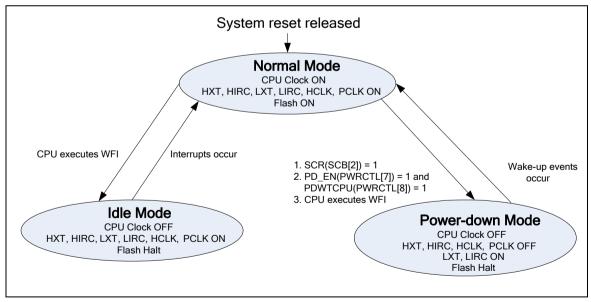

|   | 6.2.3  | Power Modes and Wake-up Sources                | 93  |

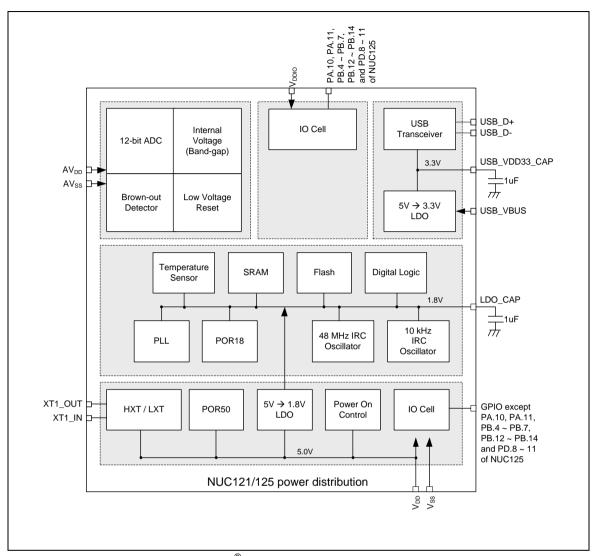

|   | 6.2.4  | System Power Distribution                      | 95  |

|   | 6.2.5  | System Memory Map                              | 97  |

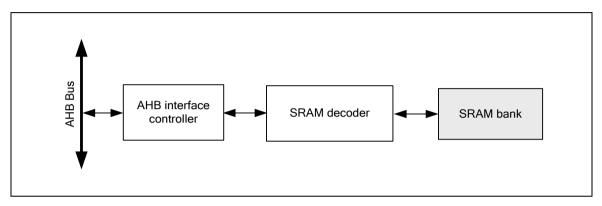

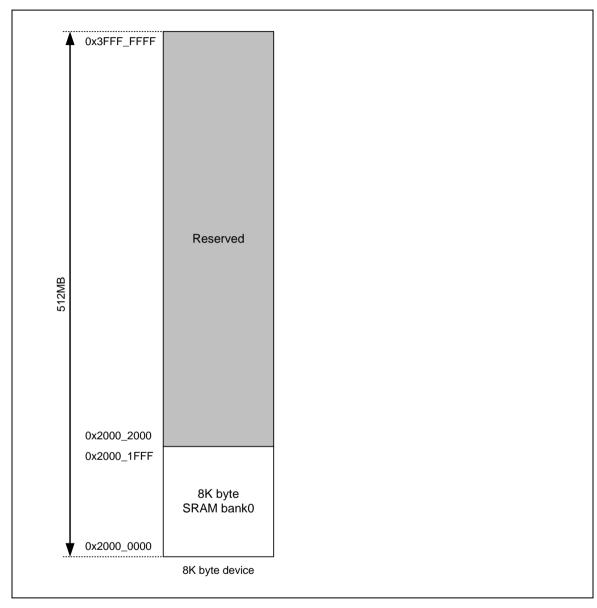

|   | 6.2.6  | SRAM Memory Orginization                       | 98  |

|   | 6.2.7  | Register Lock                                  | 99  |

|   | 6.2.8  | Auto Trim                                      | 100 |

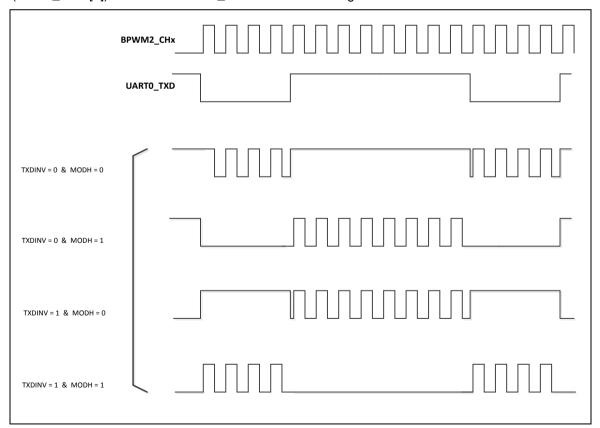

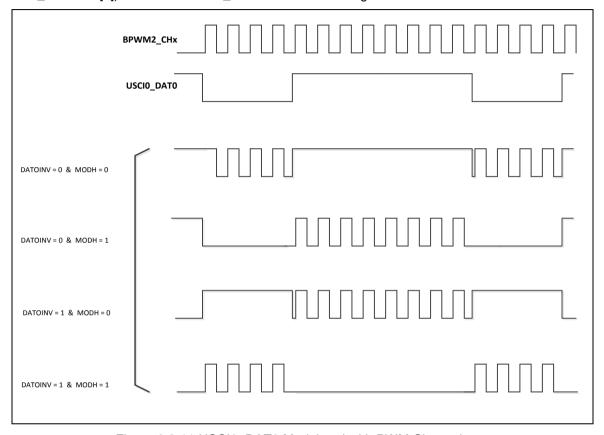

|   | 6.2.9  | UART0_TXD and USCI0_DAT0 Modulation with BPWM2 | 100 |

|   | 6.2.10 | Register Map                                   | 102 |

|   | 6.2.11 | Register Description                           | 103 |

|   | 6.2.12 | System Timer (SysTick)                         | 133 |

|   | 6.2.13 | Nested Vectored Interrupt Controller (NVIC)    | 137 |

|   | 6.2.14 | System Control                                 | 161 |

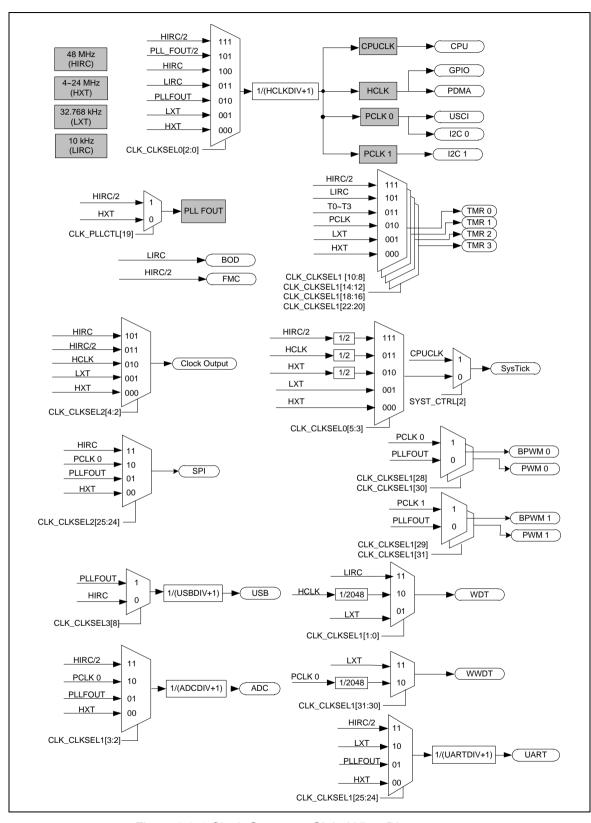

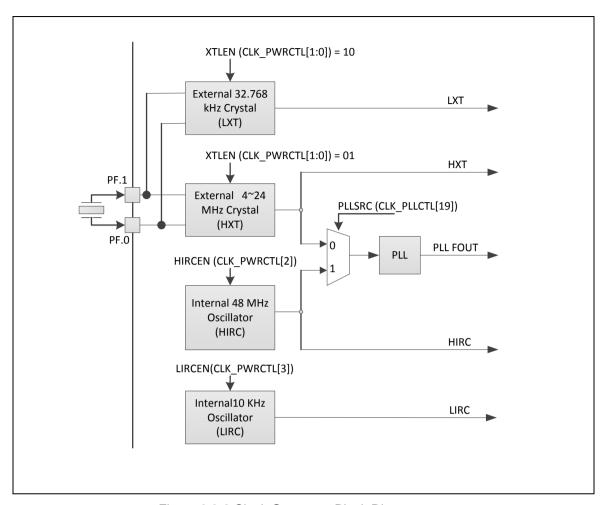

|   | 6.3    | Clock Controller                               | 169 |

|   | 6.3.1  | Overview                                       | 169 |

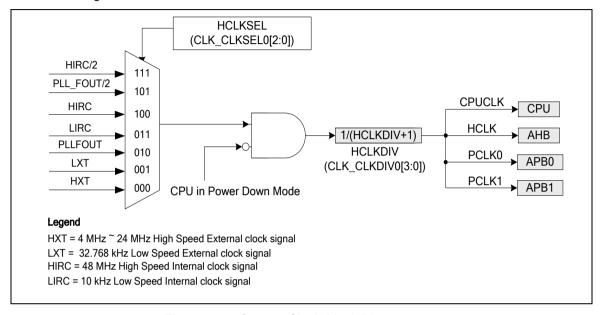

|   | 6.3.2  | Clock Generator                                | 171 |

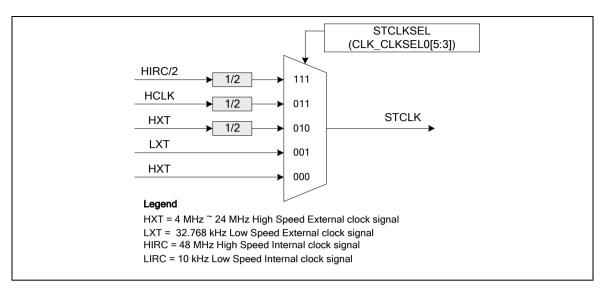

|   | 6.3.3  | System Clock and SysTick Clock                 | 173 |

|   | 6.3.4  | Peripherals Clock                              | 175 |

|   | 6.3.5  | Power-down Mode Clock                          | 175 |

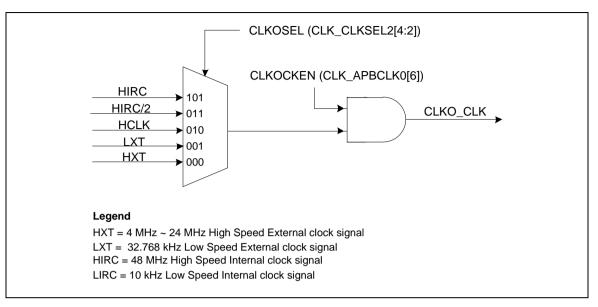

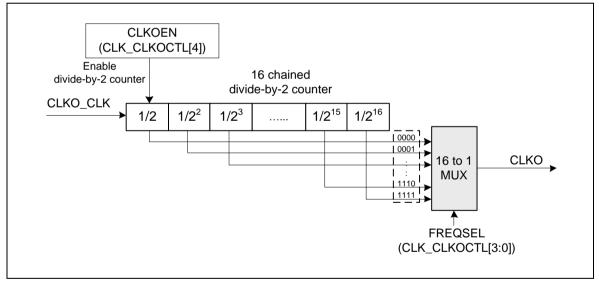

|   | 6.3.6  | Clock Output                                   | 175 |

|   | 6.3.7  | Register Map                                   | 177 |

|   | 6.3.8  | Register Description                           | 178 |

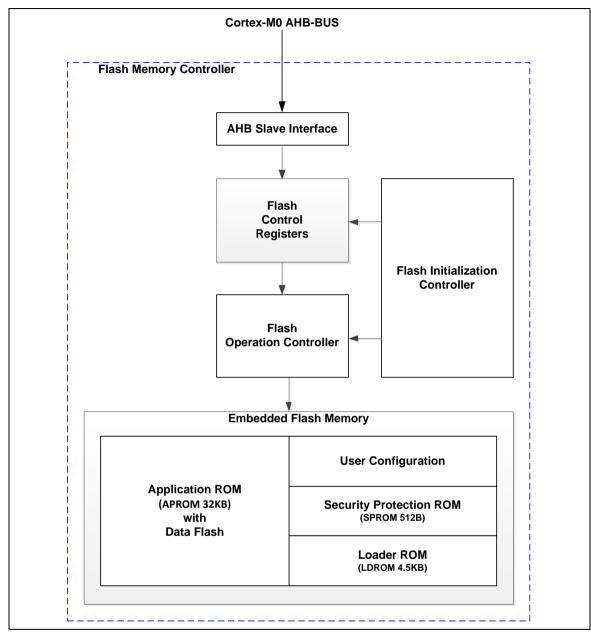

|   | 6.4    | Flash Memory Controller (FMC)                  | 202 |

|   | 6.4.1  | Overview                                       | 202 |

|   | 6.4.2  | Features                                       | 202 |

|   | 6.4.3  | Block Diagram                                  | 202 |

|   | 6.4.4  | Functional Description                         | 204 |

|   | 6.4.5  | Flash Control Register Map                     | 221 |

|   | 6.4.6  | Flash Control Register Description             | 222 |

|   | 6.5    | General Purpose I/O (GPIO)                     | 232 |

|   | 6.5.1  | Overview                                       | 232 |

| 6.5.2 | Features                                     | 232      |

|-------|----------------------------------------------|----------|

| 6.5.3 | Block Diagram                                | 233      |

| 6.5.4 | Basic Configuration                          | 234      |

| 6.5.5 | Functional Description                       | 235      |

| 6.5.6 | Register Map                                 | 238      |

| 6.5.7 | Register Description                         | 241      |

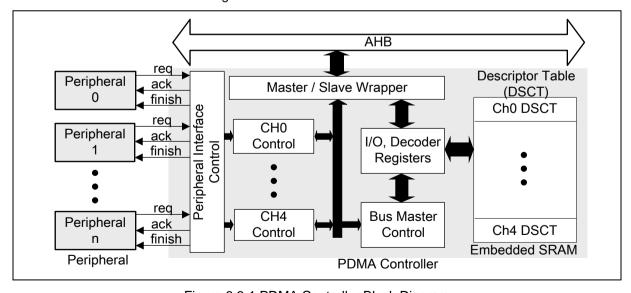

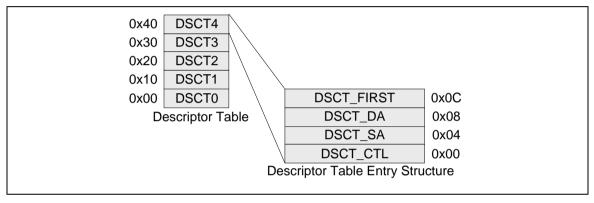

| 6.6   | PDMA Controller (PDMA)                       | 257      |

| 6.6.1 | Overview                                     | 257      |

| 6.6.2 | Features                                     | 257      |

| 6.6.3 | Block Diagram                                | 257      |

| 6.6.4 | Basic Configuration                          | 257      |

| 6.6.5 | Functional Description                       | 258      |

| 6.6.6 | Register Map                                 | 265      |

| 6.6.7 | Register Description                         | 267      |

| 6.7   | Timer Controller (TMR)                       | 294      |

| 6.7.1 | Overview                                     | 294      |

| 6.7.2 | Features                                     | 294      |

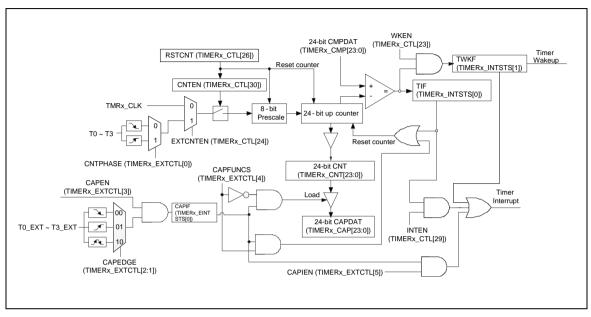

| 6.7.3 | Block Diagram                                | 295      |

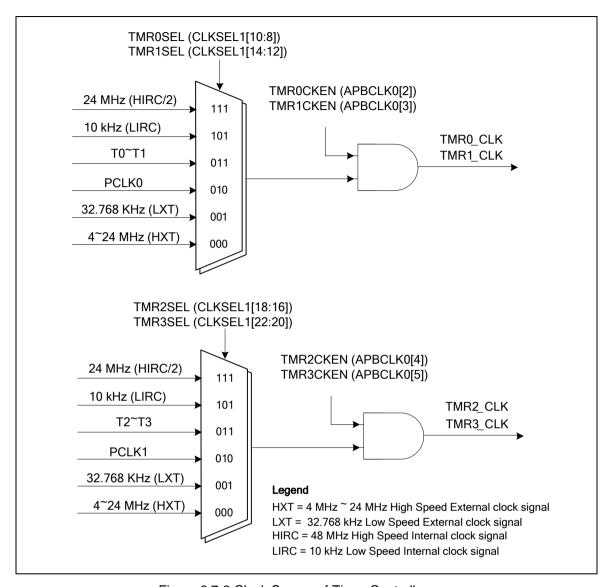

| 6.7.4 | Basic Configuration                          | 296      |

| 6.7.5 | Functional Description                       | 296      |

| 6.7.6 | Register Map                                 | 303      |

| 6.7.7 | Register Description                         | 305      |

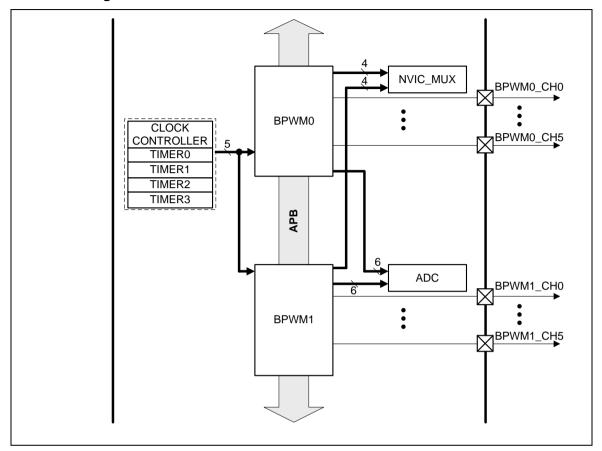

| 6.8   | Basic PWM Generator and Capture Timer (BPWM) | 315      |

| 6.8.1 | Overview                                     | 315      |

| 6.8.2 | Features                                     | 315      |

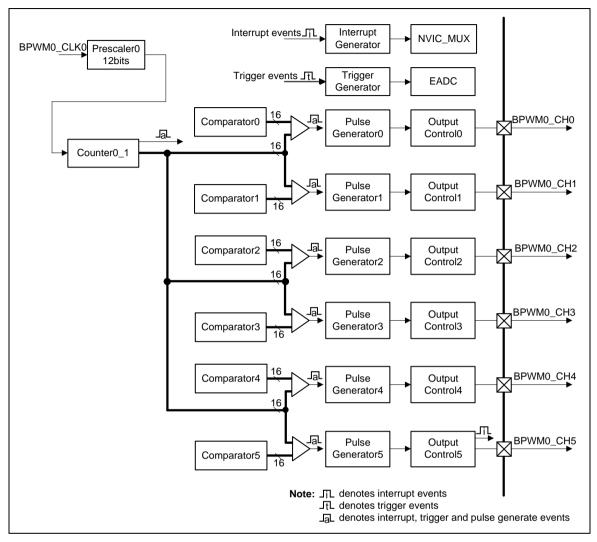

| 6.8.3 | Block Diagram                                | 316      |

| 6.8.4 | Basic Configuration                          | 318      |

| 6.8.5 | Functional Description                       | 318      |

| 6.8.6 | Register Map                                 | 333      |

| 6.8.7 | Register Description                         | 336      |

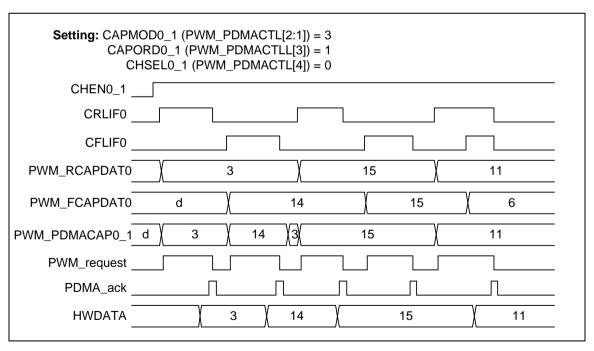

| 6.9   | PWM Generator and Capture Timer (PWM)        | 370      |

| 6.9.1 | Overview                                     | 370      |

| 6.9.2 | Features                                     | 370      |

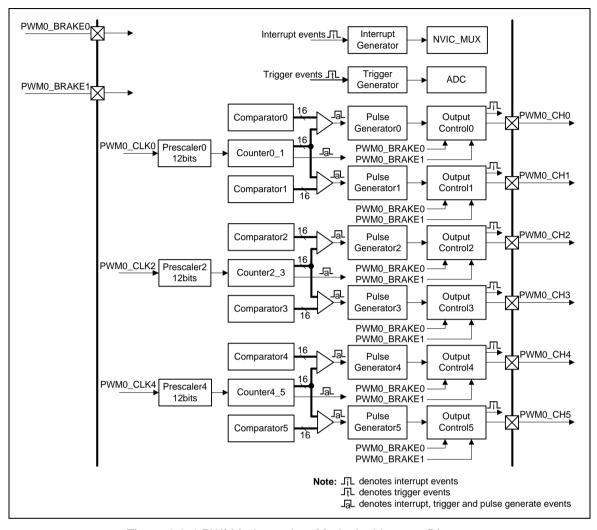

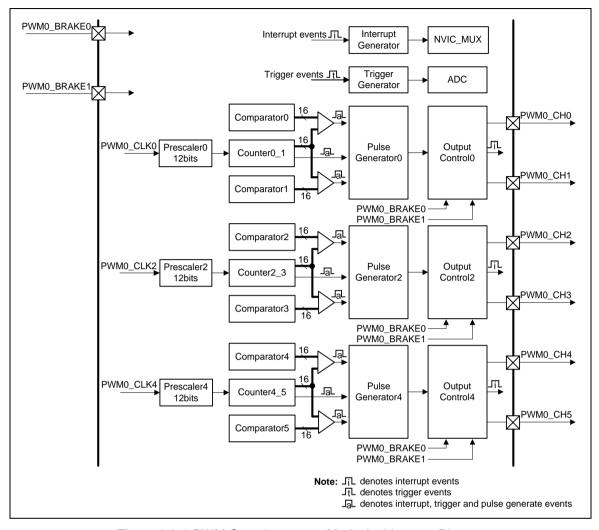

| 6.9.3 | Block Diagram                                | 371      |

| 6.9.4 | Basic Configuration                          | 374      |

| 6.9.5 | Functional Description                       | 374      |

| 17    | 0010 Dago <b>4</b> of 904                    | Pov 1 02 |

|   | 6.9.6  | Register Map                                         | 396 |

|---|--------|------------------------------------------------------|-----|

|   | 6.9.7  | Register Description                                 | 400 |

| 6 | .10 \  | Vatchdog Timer (WDT)                                 | 453 |

|   | 6.10.1 | Overview                                             | 453 |

|   | 6.10.2 | Features                                             | 453 |

|   | 6.10.3 | Block Diagram                                        | 453 |

|   | 6.10.4 | Clock Control                                        | 453 |

|   | 6.10.5 | Basic Configuration                                  | 454 |

|   | 6.10.6 | Functional Description                               | 454 |

|   | 6.10.7 | Register Map                                         | 457 |

|   | 6.10.8 | Register Description                                 | 458 |

| 6 | .11 \  | Vindow Watchdog Timer (WWDT)                         | 463 |

|   | 6.11.1 | Overview                                             | 463 |

|   | 6.11.2 | Features                                             | 463 |

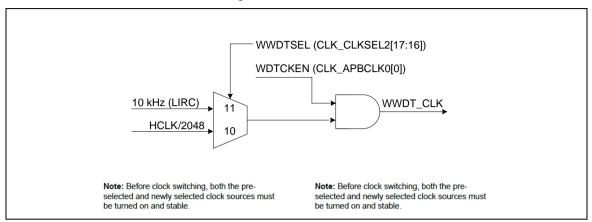

|   | 6.11.3 | Block Diagram                                        | 463 |

|   | 6.11.4 | Clock Control                                        | 464 |

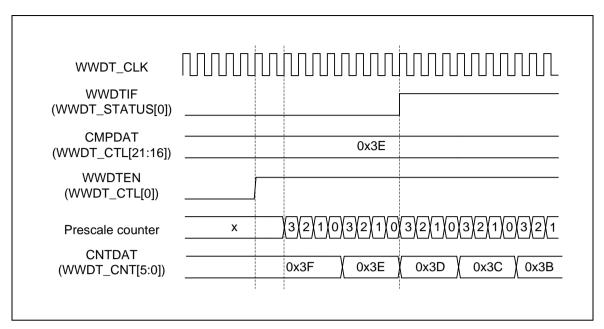

|   | 6.11.5 | Basic Configuration                                  | 464 |

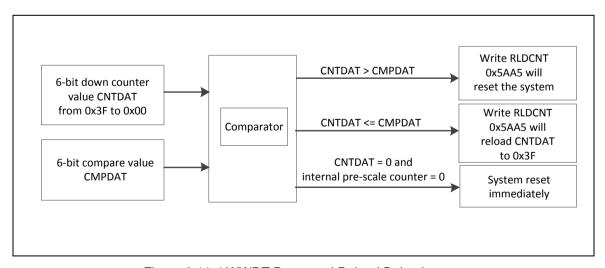

|   | 6.11.6 | Functional Description                               | 464 |

|   | 6.11.7 | Register Map                                         | 469 |

|   | 6.11.8 | Register Description                                 | 470 |

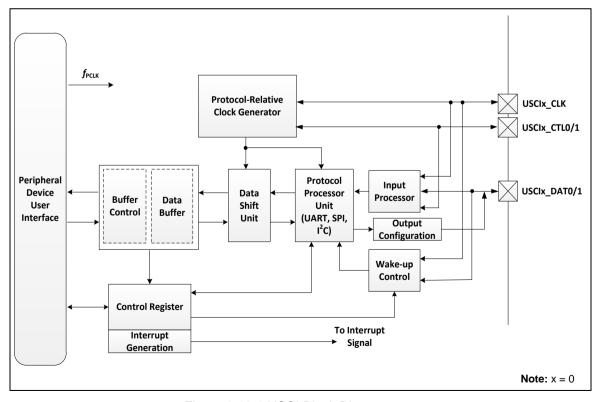

| 6 | .12 l  | JSCI - Universal Serial Control Interface Controller | 475 |

|   | 6.12.1 | Overview                                             | 475 |

|   | 6.12.2 | Features                                             | 475 |

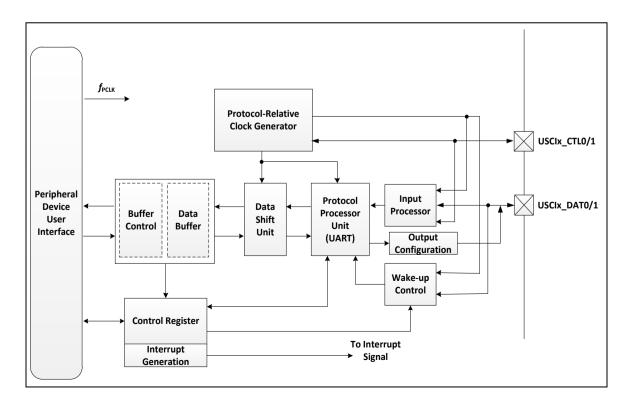

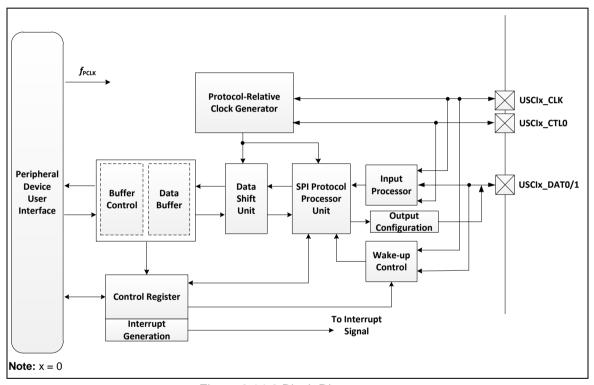

|   | 6.12.3 | Block Diagram                                        | 475 |

|   | 6.12.4 | Functional Description                               | 476 |

| 6 | .13 l  | JSCI - UART Mode                                     | 488 |

|   | 6.13.1 | Overview                                             | 488 |

|   | 6.13.2 | Features                                             | 488 |

|   | 6.13.3 | Block Diagram                                        | 488 |

|   | 6.13.4 | Basic Configuration                                  | 489 |

|   | 6.13.5 | Functional Description                               | 489 |

|   | 6.13.6 | Register Map                                         | 499 |

|   | 6.13.7 | Register Description                                 | 500 |

| 6 | .14 l  | JSCI - SPI Mode                                      | 522 |

|   | 6.14.1 | Overview                                             | 522 |

|   | 6.14.2 | Features                                             | 522 |

|   |        |                                                      |     |

|    | 6.14.3            | Block Diagram                                    | 523 |

|----|-------------------|--------------------------------------------------|-----|

|    | 6.14.4            | Basic Configuration                              | 523 |

|    | 6.14.5            | Functional Description                           | 524 |

|    | 6.14.6            | Register Map                                     | 537 |

|    | 6.14.7            | Register Description                             | 539 |

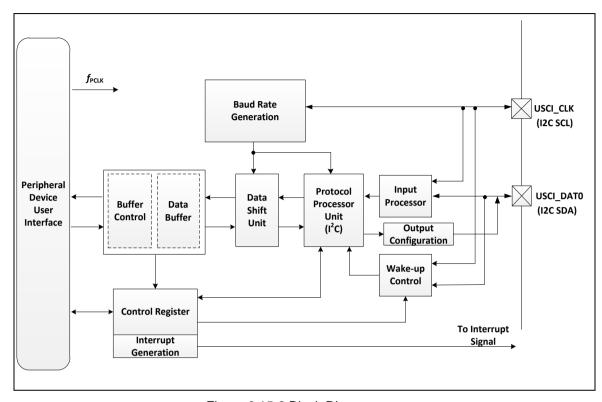

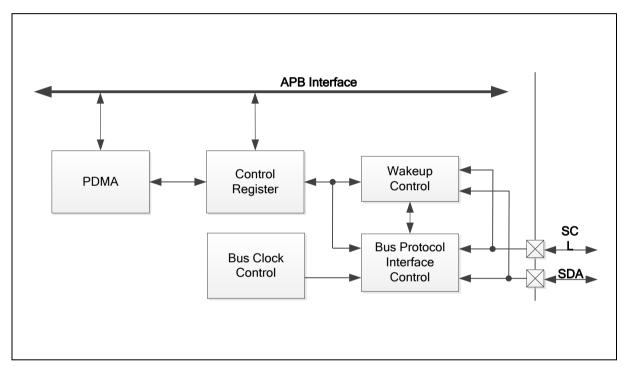

| 6. | 15 L              | SCI - I <sup>2</sup> C Mode                      | 562 |

|    | 6.15.1            | Overview                                         | 562 |

|    | 6.15.2            | Features                                         | 562 |

|    | 6.15.3            | Block Diagram                                    | 563 |

|    | 6.15.4            | Basic Configuration                              | 563 |

|    | 6.15.5            | Functional Description                           | 563 |

|    | 6.15.6            | Register Map                                     | 582 |

|    | 6.15.7            | Register Description                             | 583 |

| 6. | 16 L              | ART Interface Controller (UART)                  | 601 |

|    | 6.16.1            | Overview                                         | 601 |

|    | 6.16.2            | Features                                         | 601 |

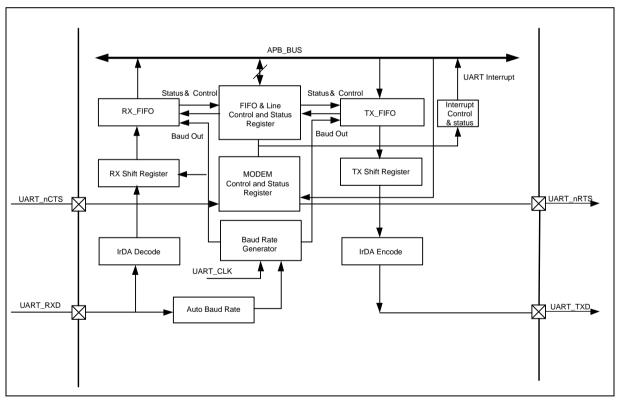

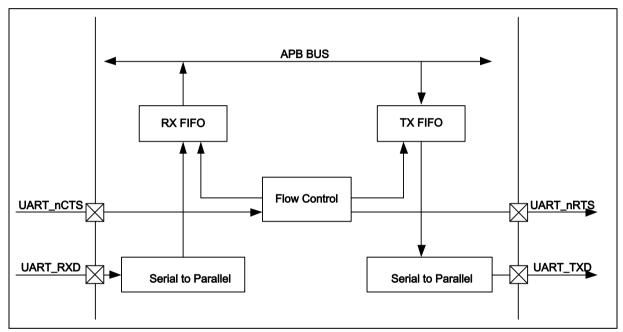

|    | 6.16.3            | Block Diagram                                    | 602 |

|    | 6.16.4            | Basic Configuration                              | 604 |

|    | 6.16.5            | Functional Description                           | 604 |

|    | 6.16.6            | Register Map                                     | 631 |

|    | 6.16.7            | Register Description                             | 633 |

| 6. | 17 l <sup>2</sup> | C Serial Interface Controller (I <sup>2</sup> C) | 667 |

|    | 6.17.1            | Overview                                         | 667 |

|    | 6.17.2            | Features                                         | 667 |

|    | 6.17.3            | Basic Configuration                              | 667 |

|    | 6.17.4            | Block Diagram                                    | 668 |

|    | 6.17.5            | Functional Description                           | 668 |

|    | 6.17.6            | Register Map                                     | 687 |

|    | 6.17.7            | Register Description                             | 688 |

| 6. | 18 S              | erial Peripheral Interface (SPI)                 | 702 |

|    | 6.18.1            | Overview                                         | 702 |

|    | 6.18.2            | Features                                         | 702 |

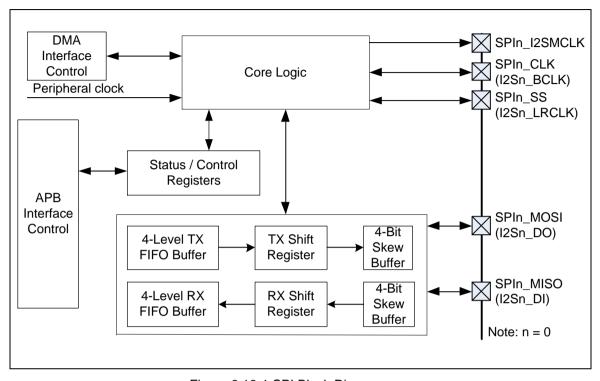

|    | 6.18.3            | Block Diagram                                    | 703 |

|    | 6.18.4            | Basic Configuration                              | 704 |

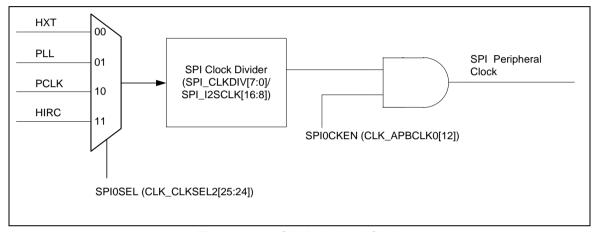

|    | 6.18.5            | Functional Description                           | 705 |

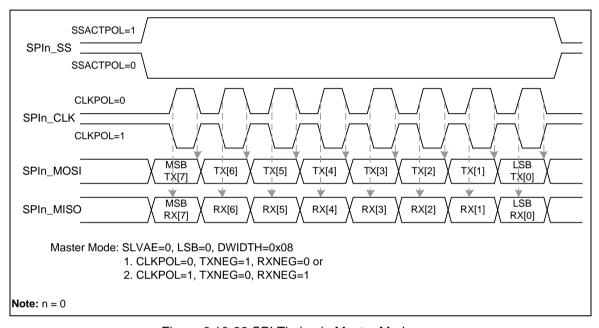

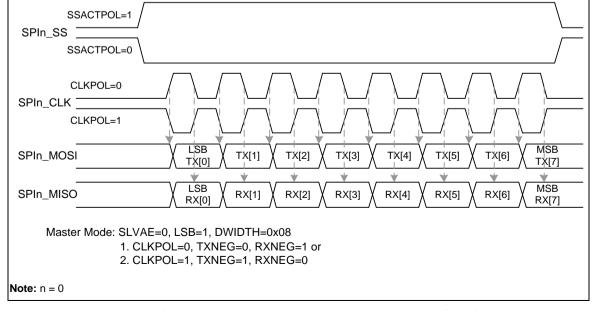

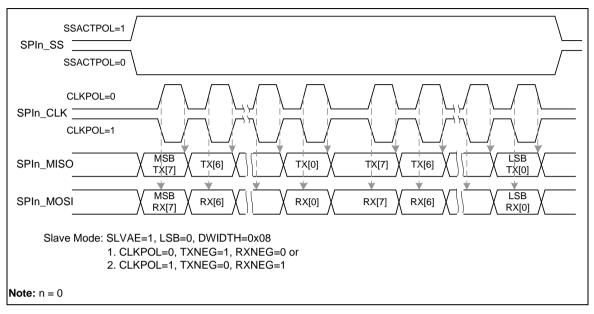

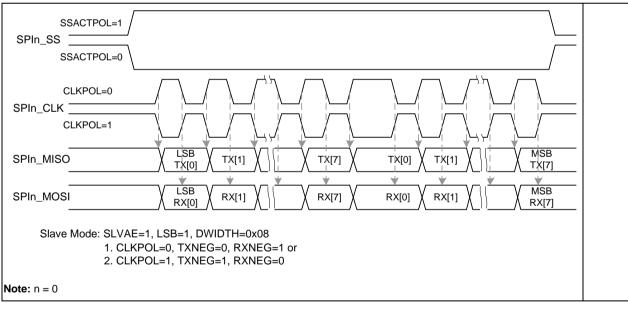

|    | 6.18.6            | Timing Diagram                                   | 719 |

|    |                   |                                                  |     |

| 9 | RE'    | VISION HISTORY                    | .803 |

|---|--------|-----------------------------------|------|

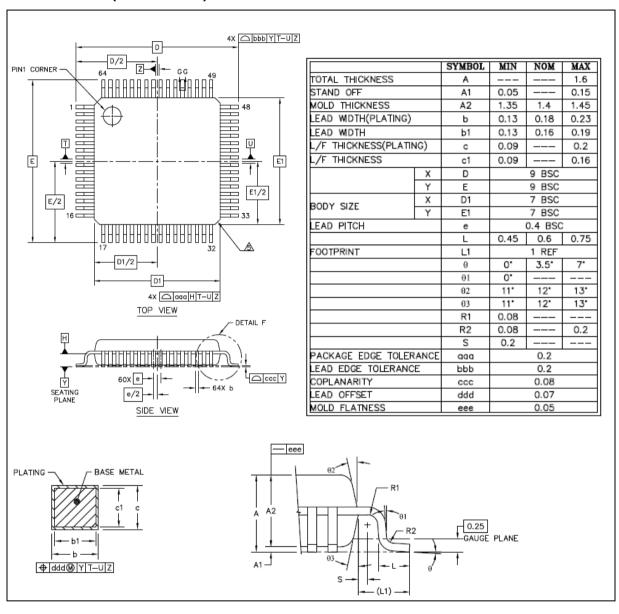

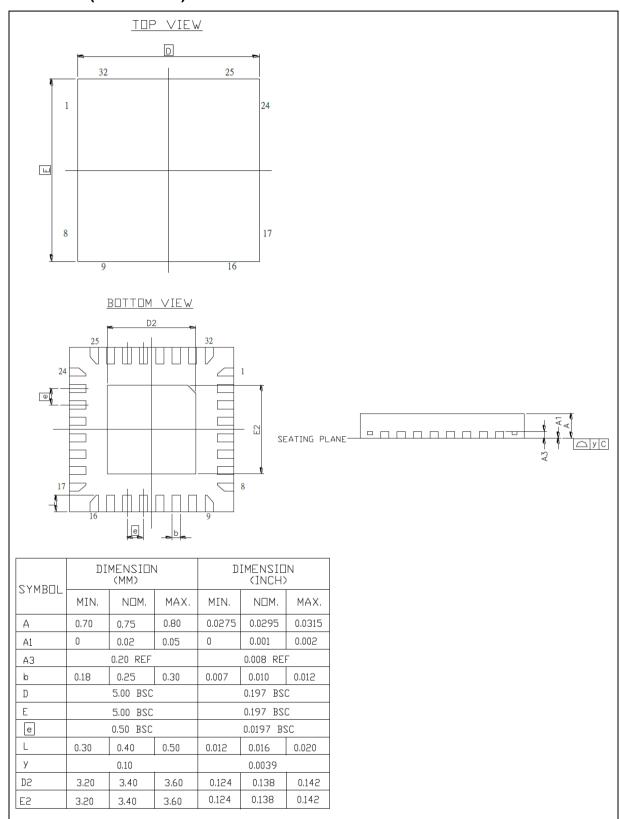

| - |        | QFN 33 (5x5x0.8 mm)               |      |

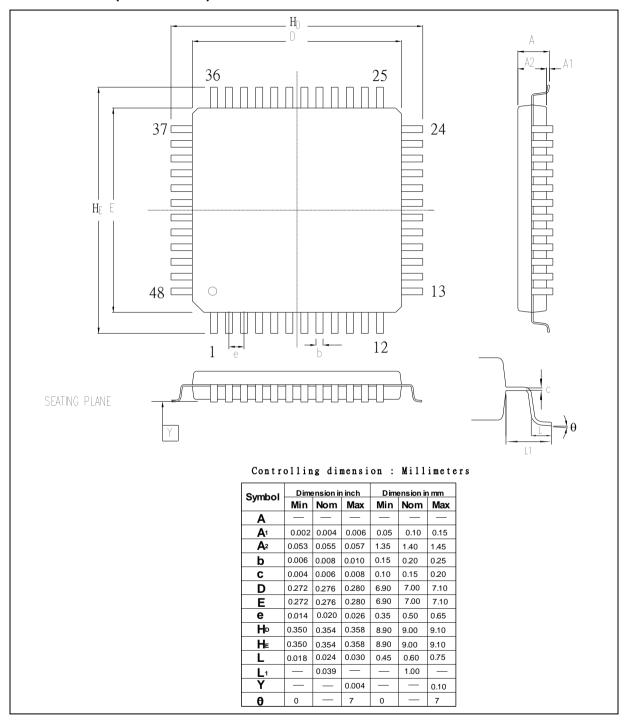

| 8 |        | LQFP 48L (7x7x1.4 mm)             |      |

| 8 |        | LQFP 64L (7x7x1.4 mm)             |      |

| 8 |        | CKAGE DIMENSIONS                  |      |

| 7 |        | ECTRICAL CHARACTERISTICS          |      |

|   | 6.20.7 | •                                 |      |

|   | 6.20.6 |                                   |      |

|   | 6.20.5 | ·                                 |      |

|   | 6.20.4 | 3                                 |      |

|   | 6.20.3 |                                   |      |

|   | 6.20.2 | Features                          | 773  |

|   | 6.20.1 | Overview                          | 773  |

| ( | 6.20   | Analog-to-Digital Converter (ADC) | 773  |

|   | 6.19.7 | Register Description              | 754  |

|   | 6.19.6 | Register Map                      | 752  |

|   | 6.19.5 | Functional Description            | 745  |

|   | 6.19.4 | -                                 |      |

|   | 6.19.3 |                                   |      |

|   | 6.19.2 |                                   |      |

| • | 6.19.1 | Overview                          |      |

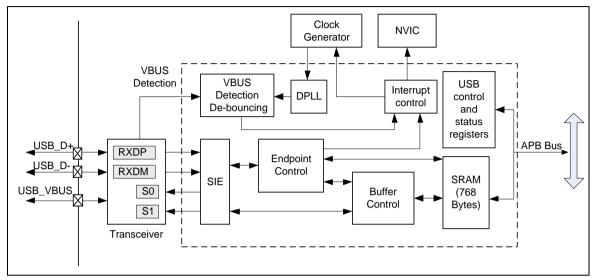

|   |        | USB Device Controller (USBD)      |      |

|   | 6.18.9 | ·                                 |      |

|   | 6.18.8 |                                   |      |

|   | 6.18.7 | Programming Examples              | 721  |

## List of Figures

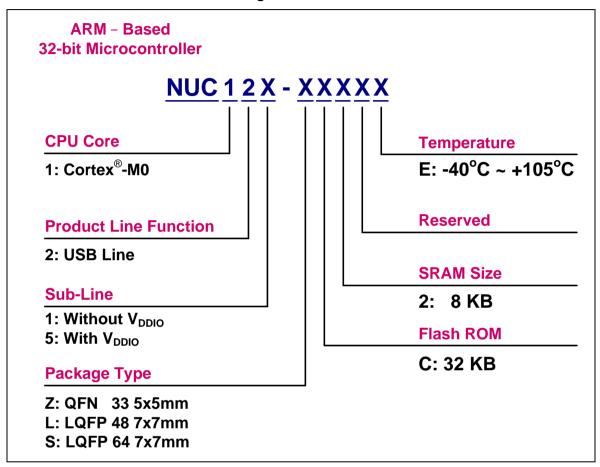

| Figure 4.1-1 NuMicro® NUC121/125 Selection Code                         | 27  |

|-------------------------------------------------------------------------|-----|

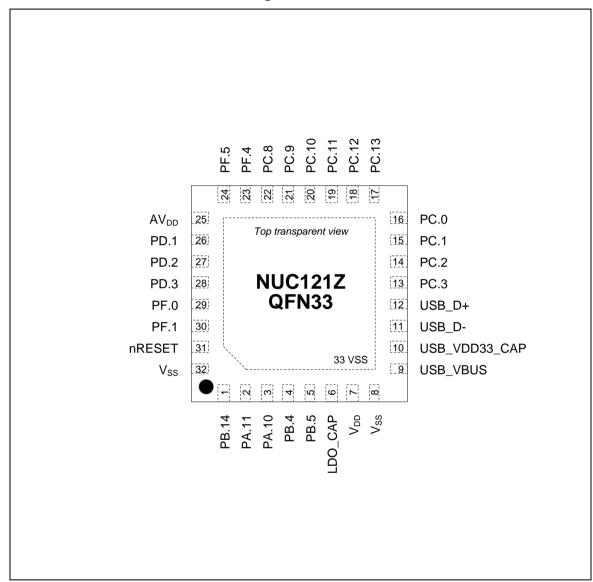

| Figure 4.2-1 NuMicro® NUC121 QFN 33-Pin Diagram                         | 29  |

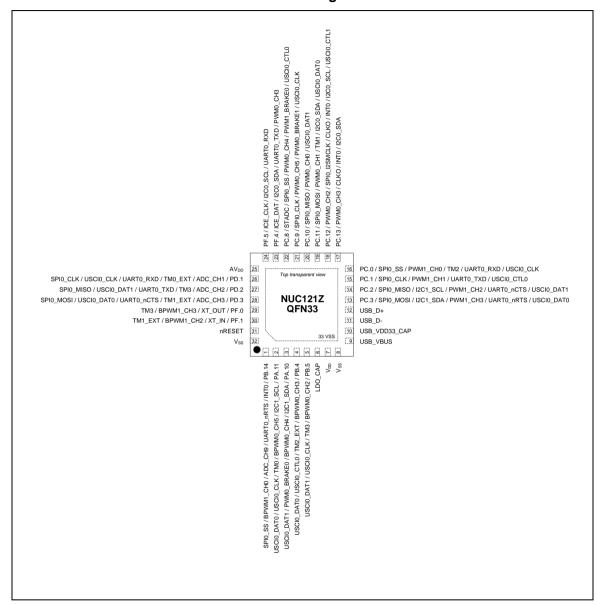

| Figure 4.2-2 NuMicro® NUC121 QFN 33-Pin Function Diagram                | 30  |

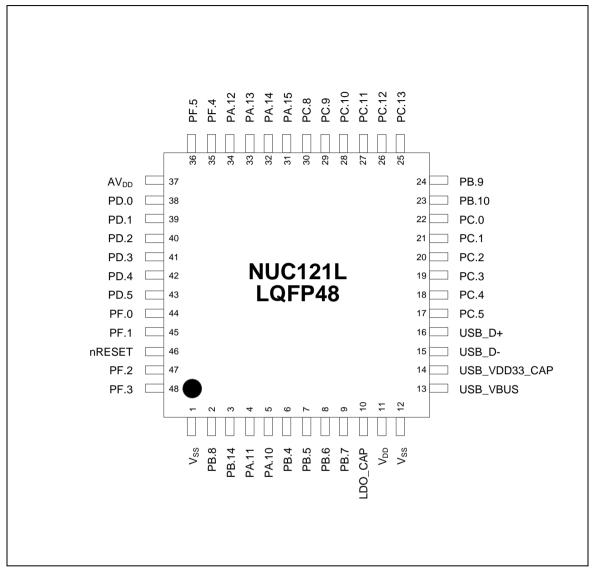

| Figure 4.2-3 NuMicro® NUC121 LQFP 48-Pin Diagram                        | 31  |

| Figure 4.2-4 NuMicro® NUC121 LQFP 48-Pin Function Diagram               | 32  |

| Figure 4.2-5 NuMicro® NUC121 LQFP 64-Pin Diagram                        | 33  |

| Figure 4.2-6 NuMicro® NUC121 LQFP 64-Pin Function Diagram               | 34  |

| Figure 4.2-7 NuMicro® NUC125 QFN 33-Pin Diagram                         | 35  |

| Figure 4.2-8 NuMicro® NUC125 QFN 33-Pin Function Diagram                | 36  |

| Figure 4.2-9 NuMicro® NUC125 LQFP 48-Pin Diagram                        | 37  |

| Figure 4.2-10 NuMicro® NUC125 LQFP 48-Pin Function Diagram              | 38  |

| Figure 4.2-11 NuMicro® NUC125 LQFP 64-Pin Diagram                       | 39  |

| Figure 4.2-12 NuMicro® NUC125 LQFP 64-Pin Function Diagram              | 40  |

| Figure 5.1-1 NuMicro <sup>®</sup> NUC121/125 Block Diagram              | 83  |

| Figure 6.1-1 Cortex <sup>®</sup> -M0 Block Diagram                      | 84  |

| Figure 6.2-1 System Reset Sources                                       | 87  |

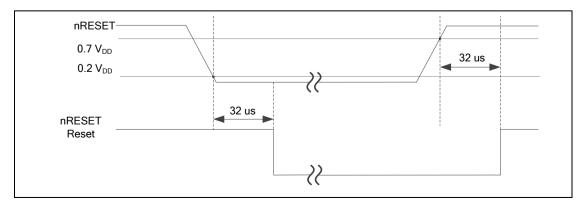

| Figure 6.2-2 nRESET Reset Waveform                                      | 89  |

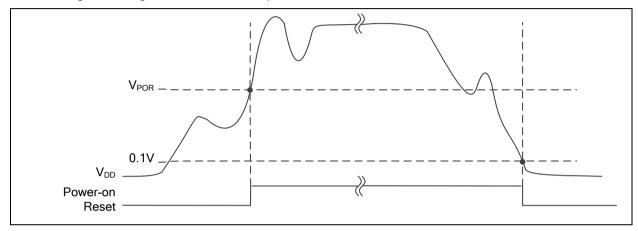

| Figure 6.2-3 Power-on Reset (POR) Waveform                              | 90  |

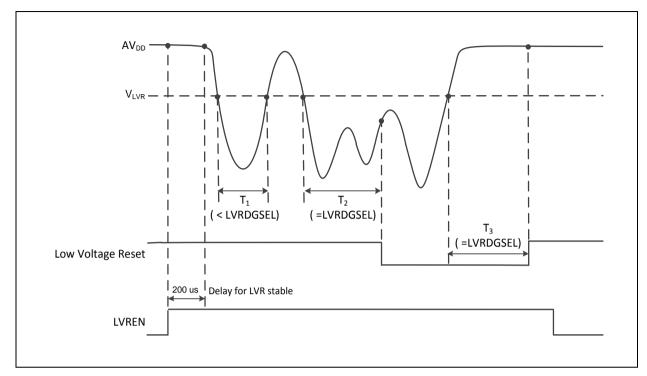

| Figure 6.2-4 Low Voltage Reset (LVR) Waveform                           | 91  |

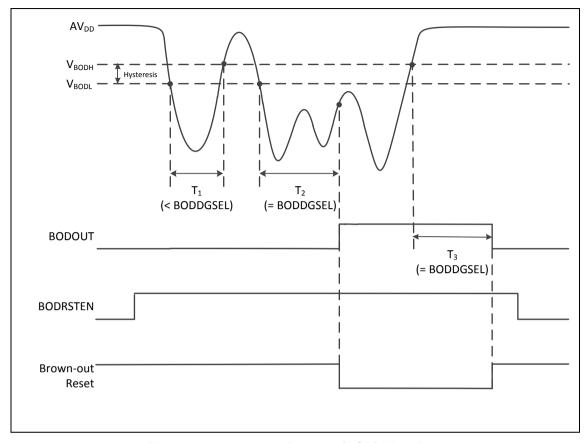

| Figure 6.2-5 Brown-out Detector (BOD) Waveform                          |     |

| Figure 6.2-6 Power Mode State Machine                                   | 93  |

| Figure 6.2-7 NuMicro <sup>®</sup> NUC121/125 Power Distribution Diagram |     |

| Figure 6.2-8 SRAM Block Diagram                                         |     |

| Figure 6.2-9 SRAM Memory Organization                                   | 99  |

| Figure 6.2-10 UART0_TXD Modulated with PWM Channel                      | 100 |

| Figure 6.2-11 USCI0_DAT0 Modulated with PWM Channel                     | 101 |

| Figure 6.3-1 Clock Generator Global View Diagram                        | 170 |

| Figure 6.3-2 Clock Generator Block Diagram                              | 172 |

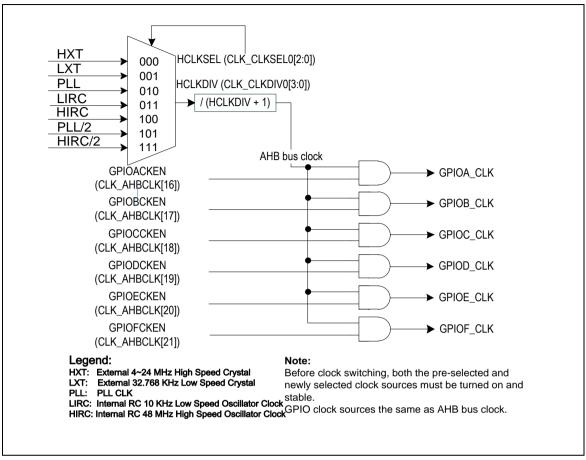

| Figure 6.3-3 System Clock Block Diagram                                 | 173 |

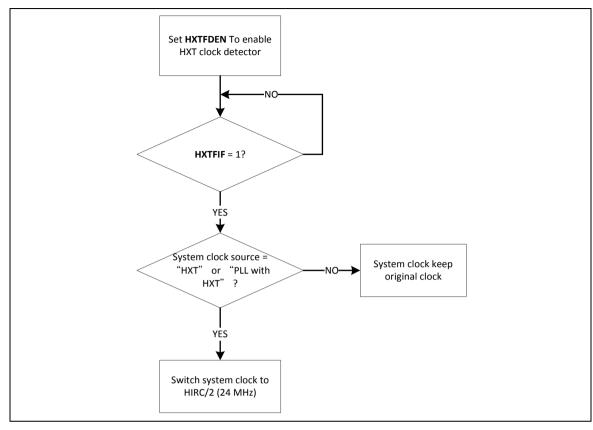

| Figure 6.3-4 HXT Stop Protect Procedure                                 | 174 |

| Figure 6.3-5 SysTick Clock Control Block Diagram                        | 175 |

| Figure 6.3-6 Clock Source of Clock Output                               | 176 |

| Figure 6.3-7 Clock Output Block Diagram                                 | 176 |

| Figure 6.4-1 Flash Memory Control Block Diagram                         | 203 |

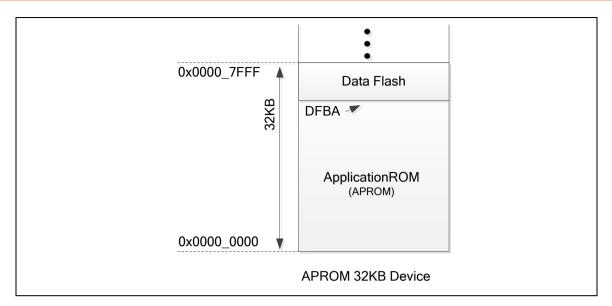

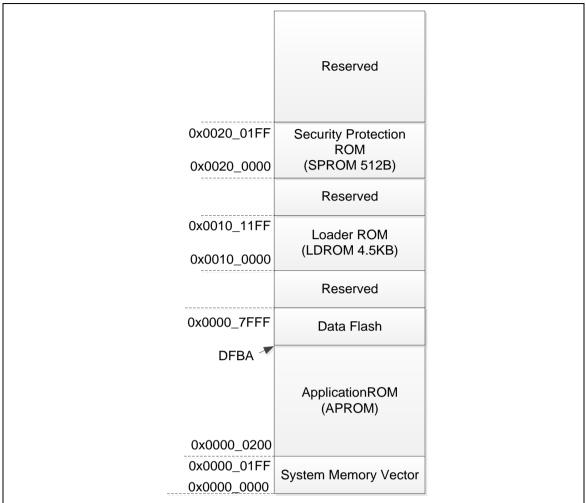

| Figure 6.4-2 Data Flash is Shared with APROM                            | 205 |

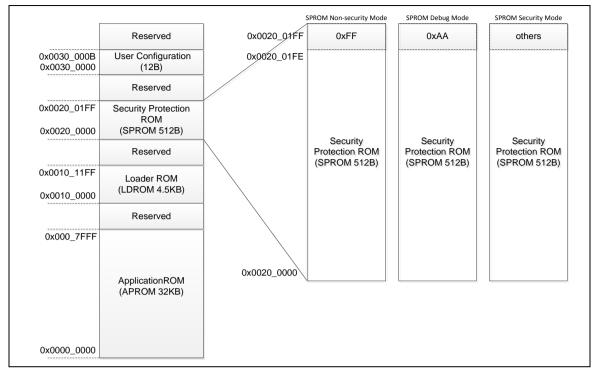

| Figure 6.4-3 SPROM Security Mode                                        | 211 |

|                                                                         |     |

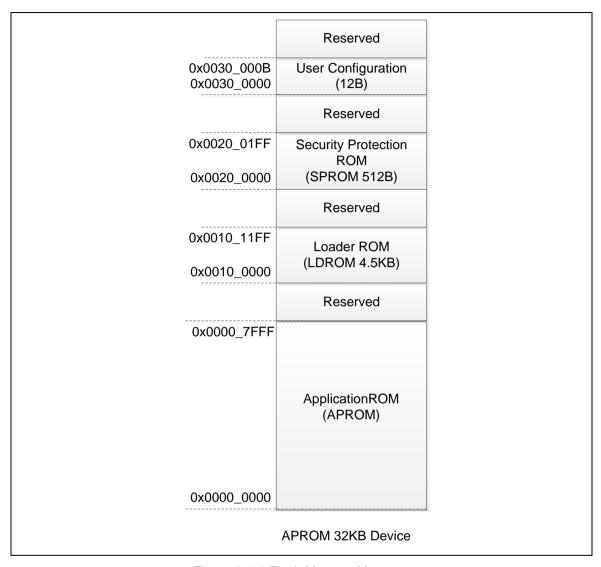

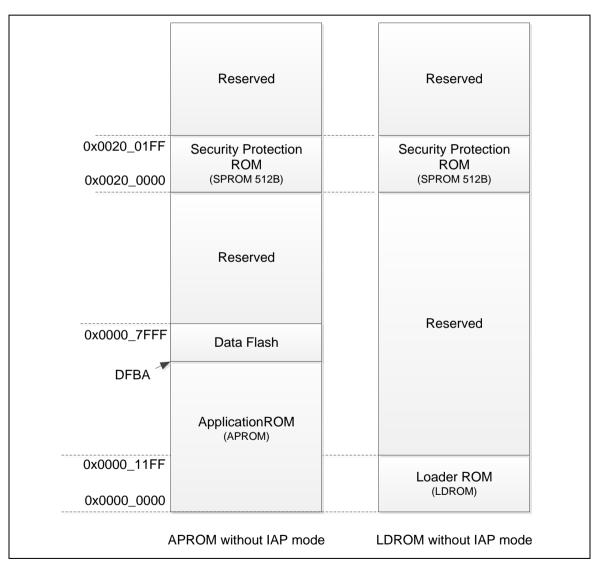

| Figure 6.4-4 Flash Memory Map                                                      | . 212 |

|------------------------------------------------------------------------------------|-------|

| Figure 6.4-5 System Memory Map with IAP Mode                                       | . 213 |

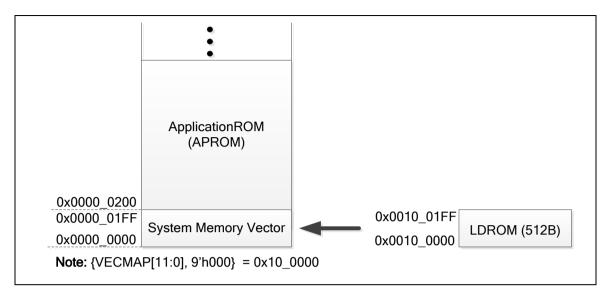

| Figure 6.4-6 LDROM with IAP Mode                                                   | . 214 |

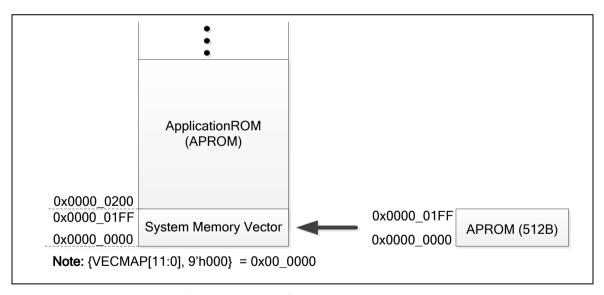

| Figure 6.4-7 APROM with IAP Mode                                                   | . 214 |

| Figure 6.4-8 System Memory Map without IAP Mode                                    | . 215 |

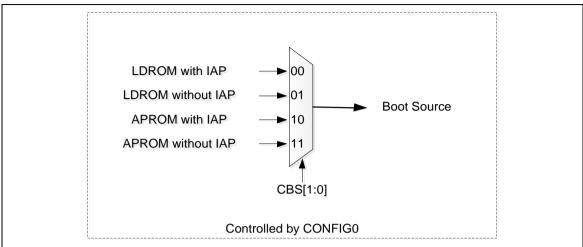

| Figure 6.4-9 Boot Source Selection                                                 | . 216 |

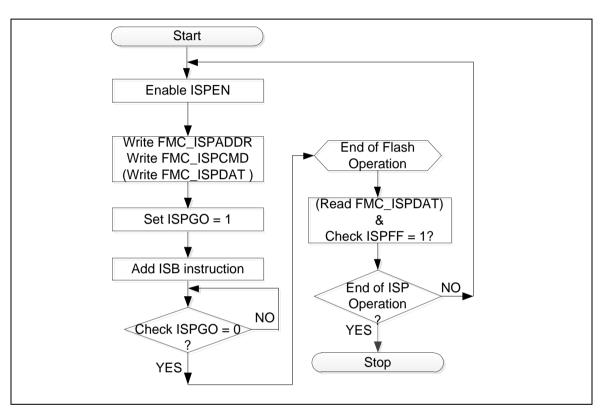

| Figure 6.4-6.4-10 ISP Procedure Example                                            | . 218 |

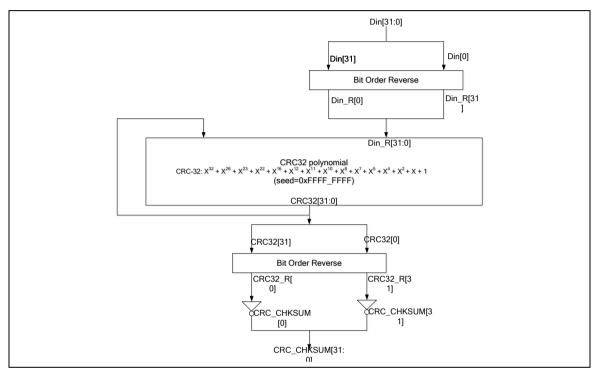

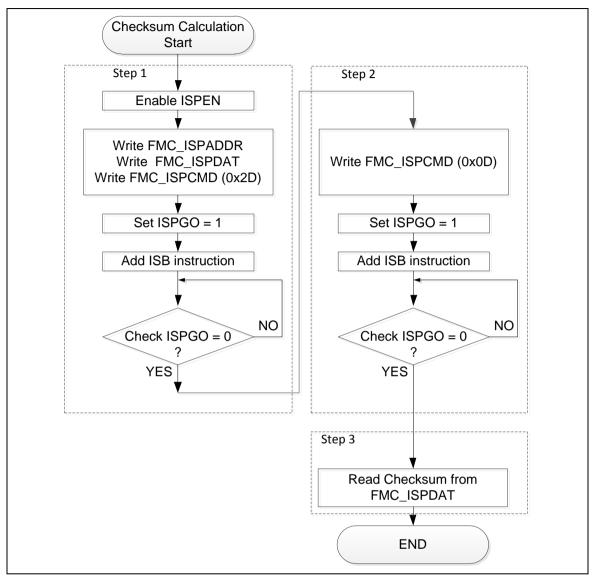

| Figure 6.4-6.4-11 CRC-32 Checksum Calculation                                      | . 219 |

| Figure 6.4-12 CRC-32 Checksum Calculation Flow                                     | . 220 |

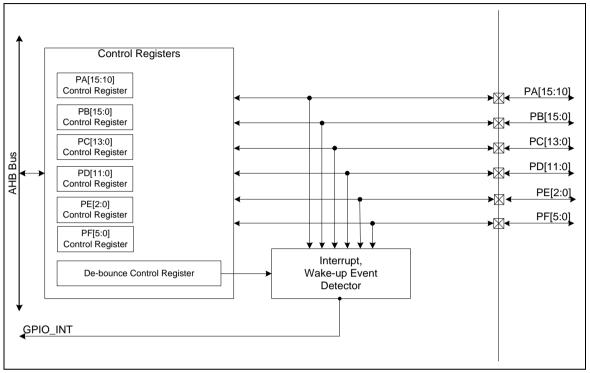

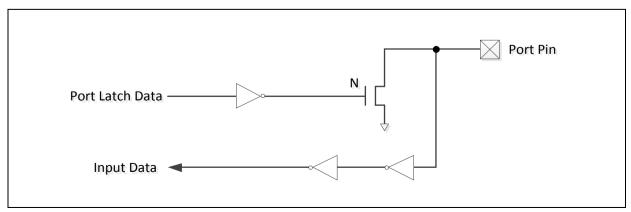

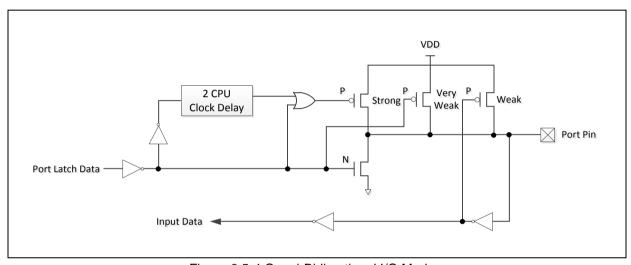

| Figure 6.5-1 GPIO Controller Block Diagram                                         | . 233 |

| Figure 6.5-2 GPIO Clock Control Diagram                                            | . 234 |

| Figure 6.6-1 PDMA Controller Block Diagram                                         | . 257 |

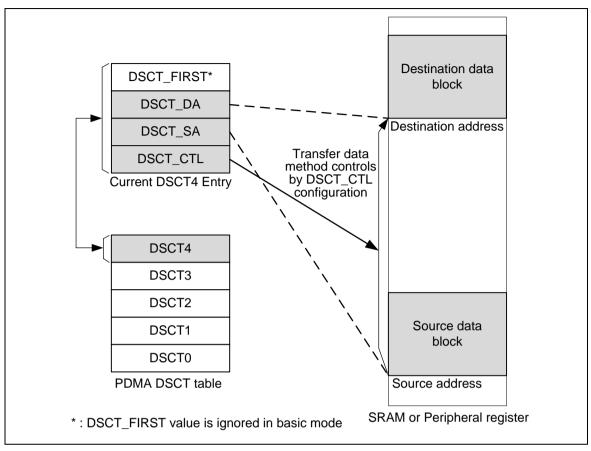

| Figure 6.6-2 Descriptor Table Entry Structure                                      | . 258 |

| Figure 6.6-3 Descriptor Table Operation in Basic Mode                              | . 260 |

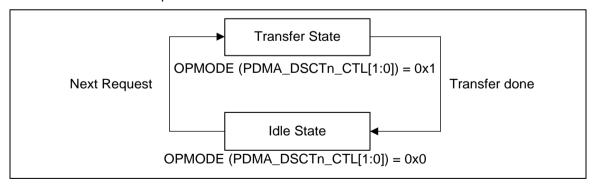

| Figure 6.6-4 Basic Mode Finite State Machine                                       | . 260 |

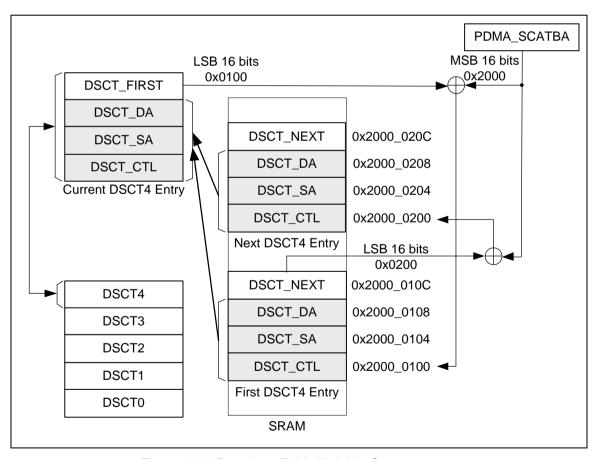

| Figure 6.6-5 Descriptor Table Link List Structure                                  | . 261 |

| Figure 6.6-6 Scatter-Gather Mode Finite State Machine                              | . 262 |

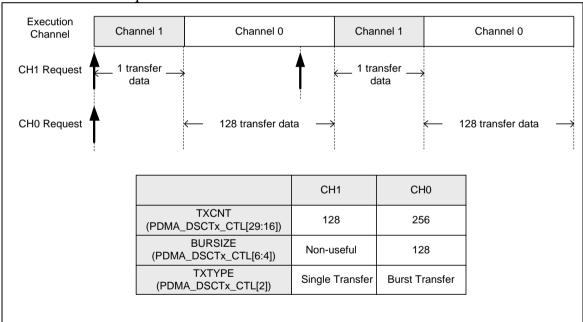

| Figure 6.6-7 Example of Single Transfer Type and Burst Transfer Type in Basic Mode | . 263 |

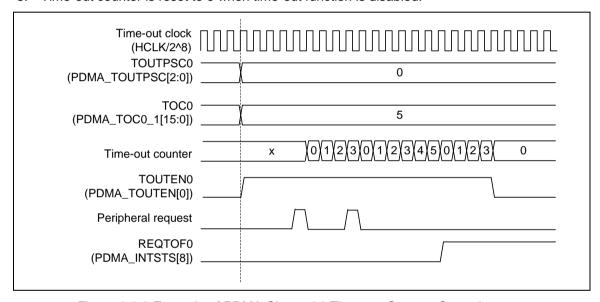

| Figure 6.6-8 Example of PDMA Channel 0 Time-out Counter Operation                  | . 264 |

| Figure 6.7-1 Timer Controller Block Diagram                                        | . 295 |

| Figure 6.7-2 Clock Source of Timer Controller                                      | . 296 |

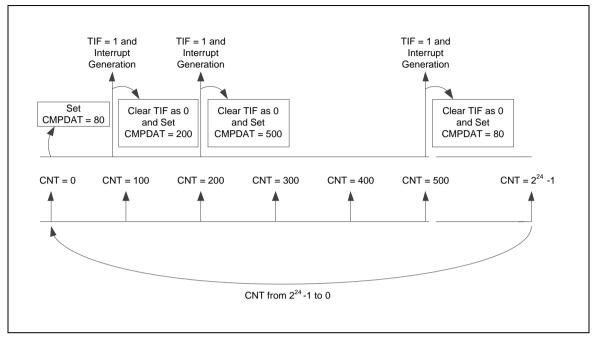

| Figure 6.7-3 Continuous Counting Mode                                              | . 298 |

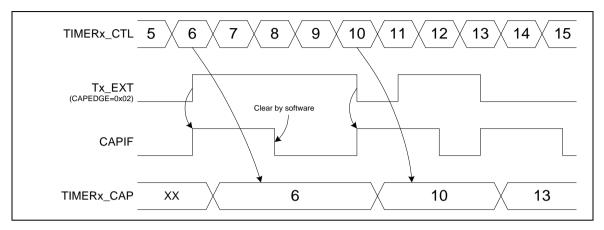

| Figure 6.7-4 External Capture Mode                                                 | . 299 |

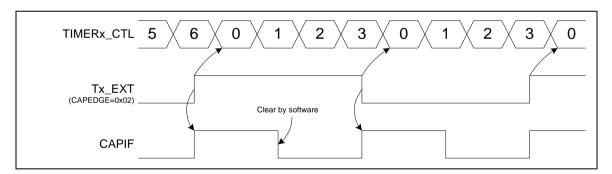

| Figure 6.7-5 External Reset Counter Mode                                           | . 299 |

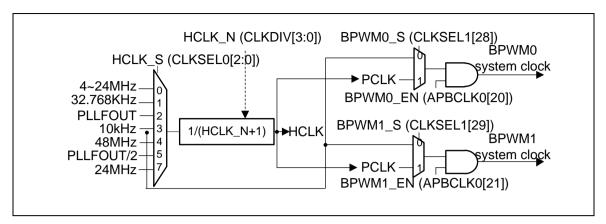

| Figure 6.8-1 BPWM Generator Overview Block Diagram                                 | . 316 |

| Figure 6.8-2 BPWM System Clock Source Control                                      | . 317 |

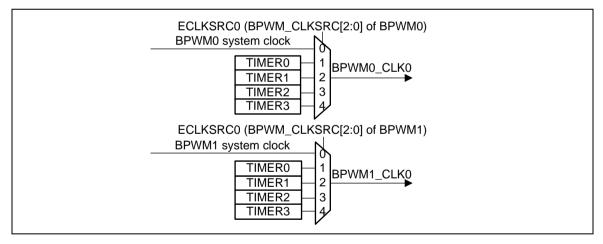

| Figure 6.8-3 BPWM Clock Source Control                                             | . 317 |

| Figure 6.8-4 BPWM Independent Mode Architecture Diagram                            | . 318 |

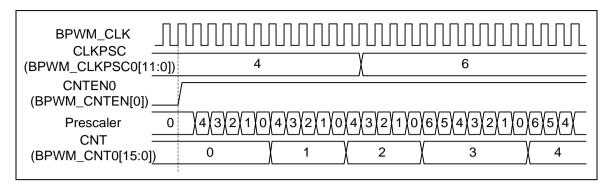

| Figure 6.8-5 BPWM_CH0 CLKPSC waveform                                              | . 319 |

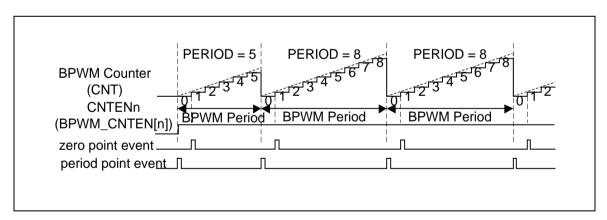

| Figure 6.8-6 BPWM Up Counter Type                                                  | . 319 |

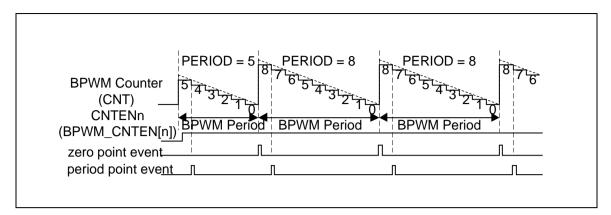

| Figure 6.8-7 BPWM Down Counter Type                                                | . 320 |

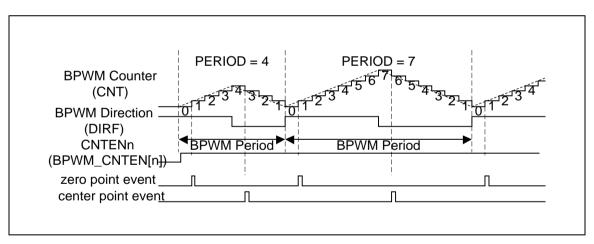

| Figure 6.8-8 BPWM Up-Down Counter Type                                             | . 320 |

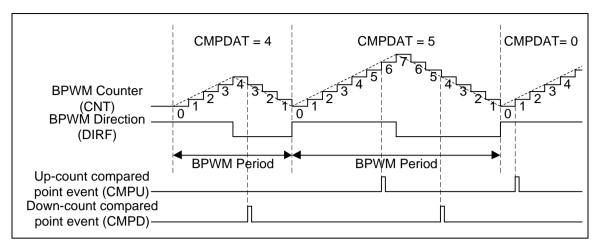

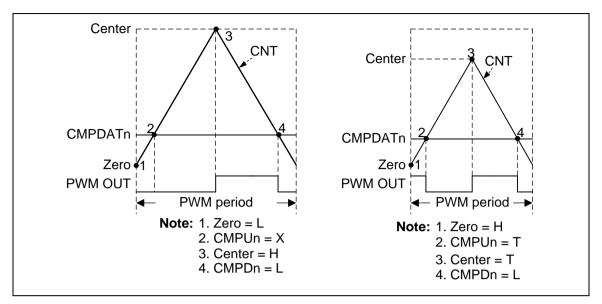

| Figure 6.8-9 BPWM CMPDAT Events in Up-Down Counter Type                            | . 321 |

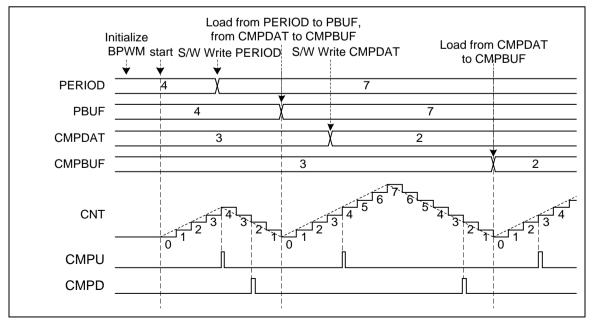

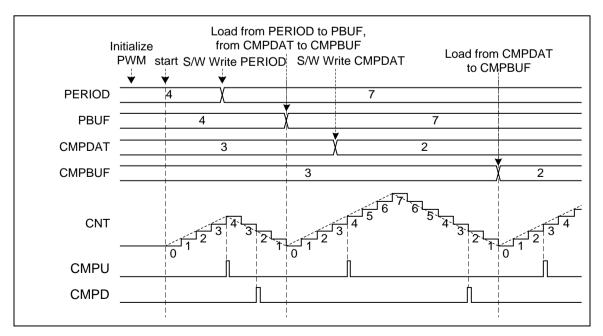

| Figure 6.8-10 BPWM Double Buffering Illustration                                   | . 321 |

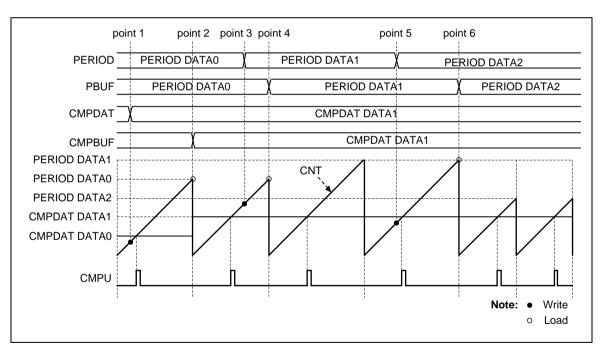

| Figure 6.8-11 Period Loading Mode with Up-Counter Type                             | . 322 |

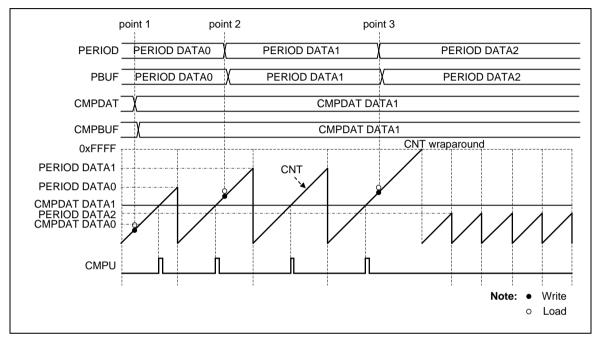

| Figure 6.8-12 Immediately Loading Mode with Up-Counter Type                        | . 323 |

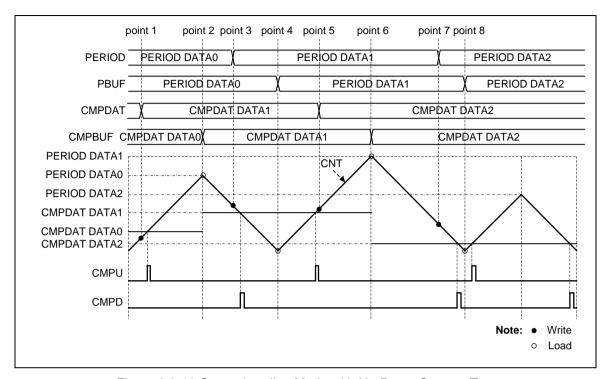

| Figure 6.8-13 Center Loading Mode with Up-Down-Counter Type                        | . 324 |

| Figure 6.8-14 BPWM Pulse Generation                                     | . 325 |

|-------------------------------------------------------------------------|-------|

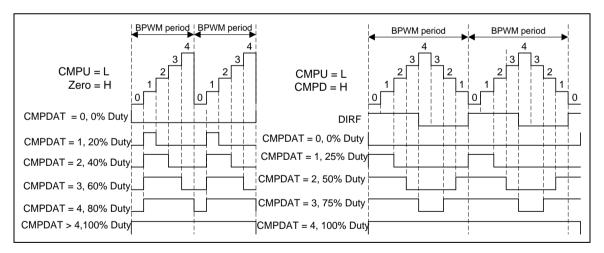

| Figure 6.8-15 BPWM 0% to 100% Pulse Generation                          | . 325 |

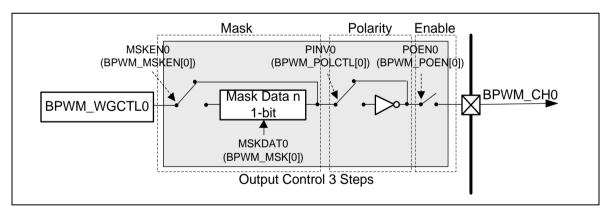

| Figure 6.8-16 BPWM_CH0 Output Control 3 Steps                           | . 326 |

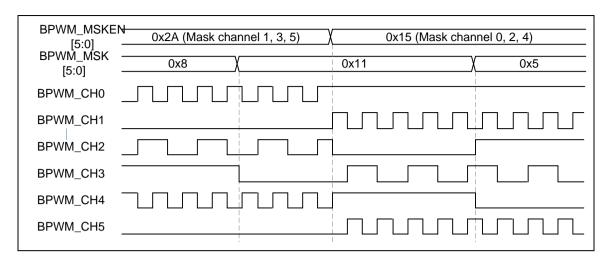

| Figure 6.8-17 Illustration of Mask Control Waveform                     | . 327 |

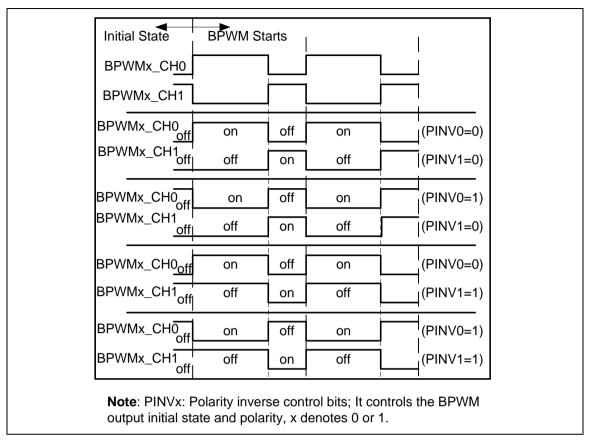

| Figure 6.8-18 Initial State and Polarity Control                        | . 328 |

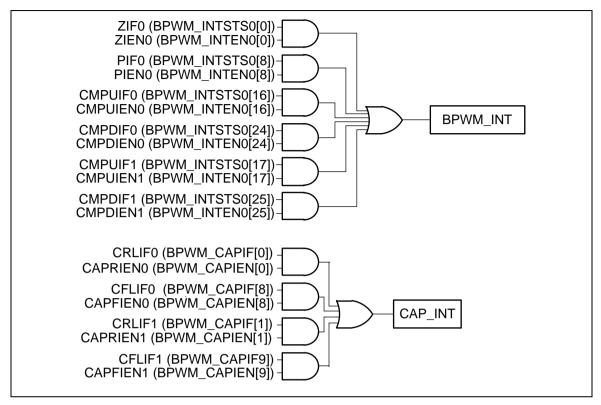

| Figure 6.8-19 BPWM_CH0 and BPWM_CH1 Pair Interrupt Architecture Diagram | . 329 |

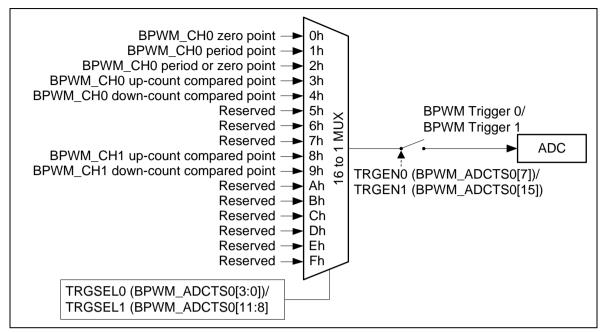

| Figure 6.8-20 BPWM_CH0 and BPWM_CH1 Pair Trigger ADC Block Diagram      | . 330 |

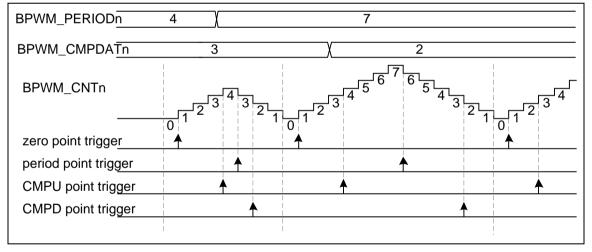

| Figure 6.8-21 BPWM Trigger ADC in Up-Down Counter Type Timing Waveform  | . 330 |

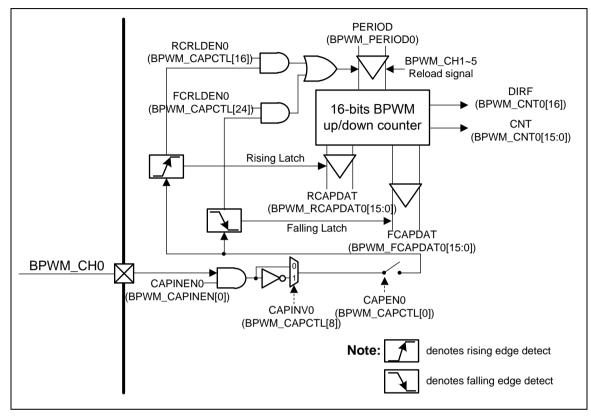

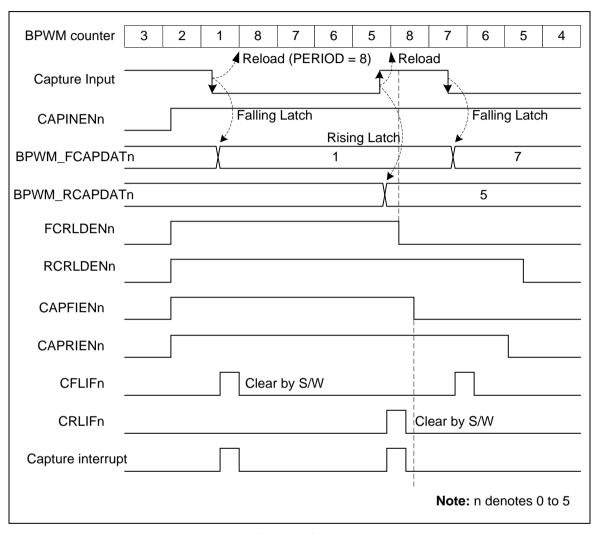

| Figure 6.8-22 BPWM_CH0 Capture Block Diagram                            | . 331 |

| Figure 6.8-23 Capture Operation Waveform                                | . 332 |

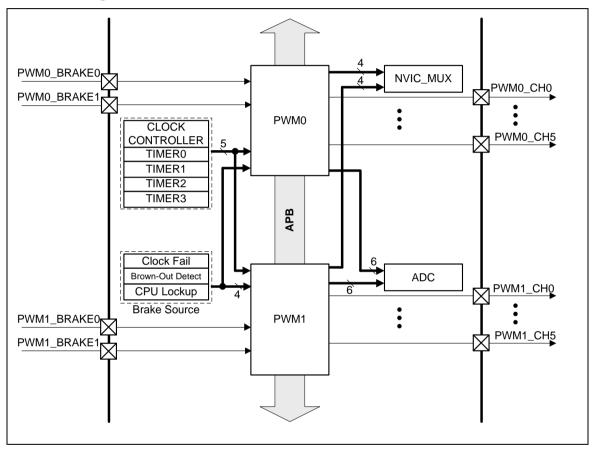

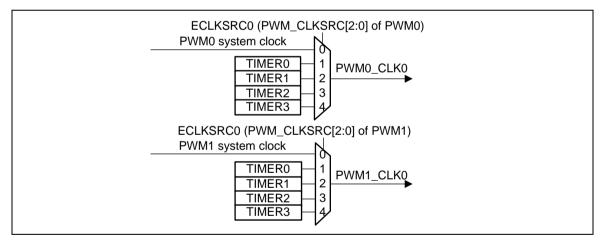

| Figure 6.9-1 PWM Generator Overview Block Diagram                       | . 371 |

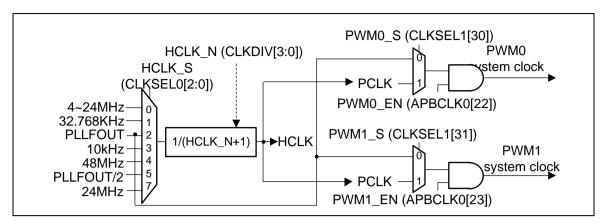

| Figure 6.9-2 PWM System Clock Source Control                            | . 372 |

| Figure 6.9-3 PWM Clock Source Control                                   | . 372 |

| Figure 6.9-4 PWM Independent Mode Architecture Diagram                  | . 373 |

| Figure 6.9-5 PWM Complementary Mode Architecture Diagram                | . 374 |

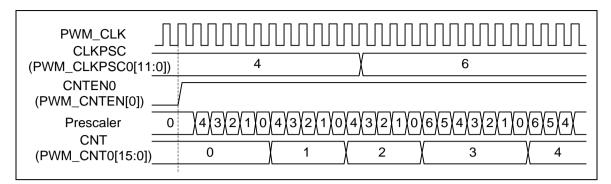

| Figure 6.9-6 PWM_CH0 CLKPSC waveform                                    | . 375 |

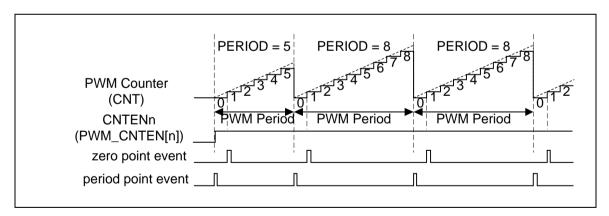

| Figure 6.9-7 PWM Up Counter Type                                        | . 375 |

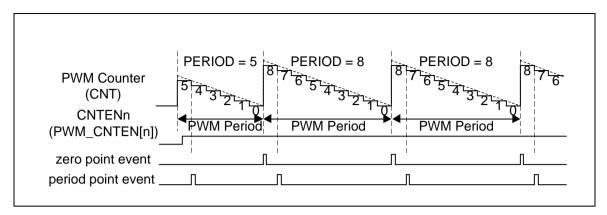

| Figure 6.9-8 PWM Down Counter Type                                      | . 376 |

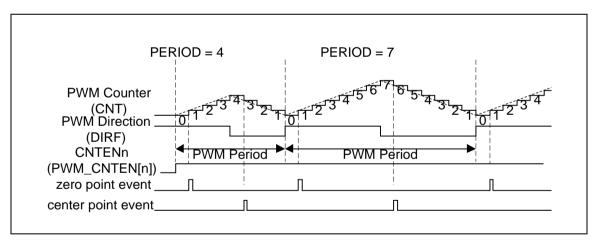

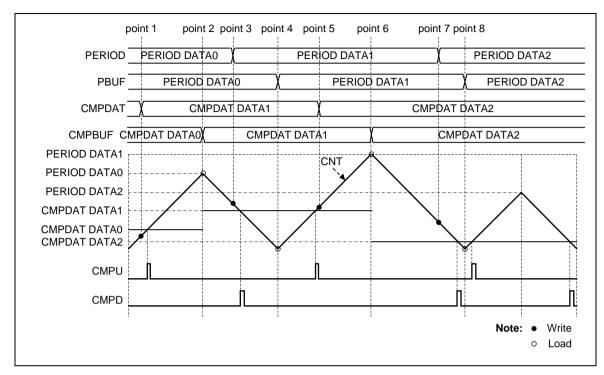

| Figure 6.9-9 PWM Up-Down Counter Type                                   | . 376 |

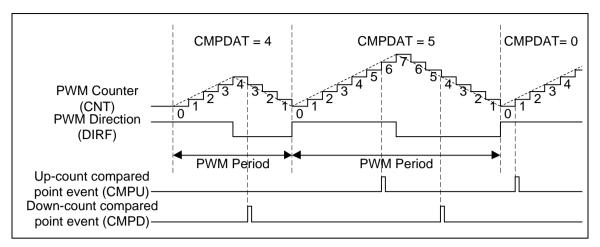

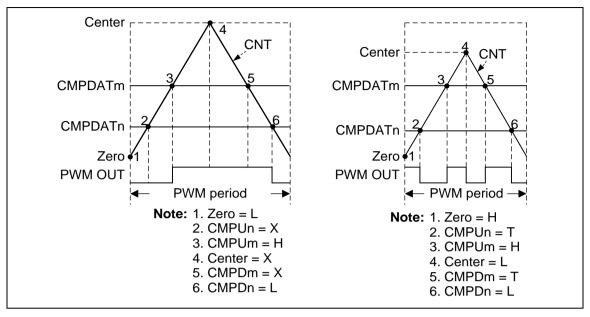

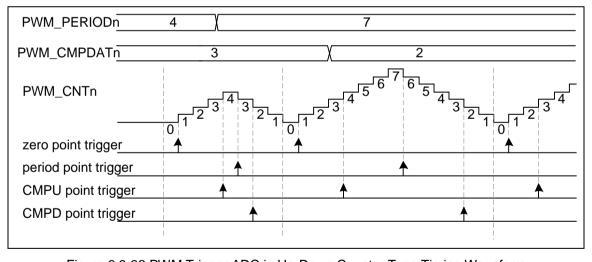

| Figure 6.9-10 PWM CMPDAT Events in Up-Down Counter Type                 | . 377 |

| Figure 6.9-11 PWM Double Buffering Illustration                         | . 377 |

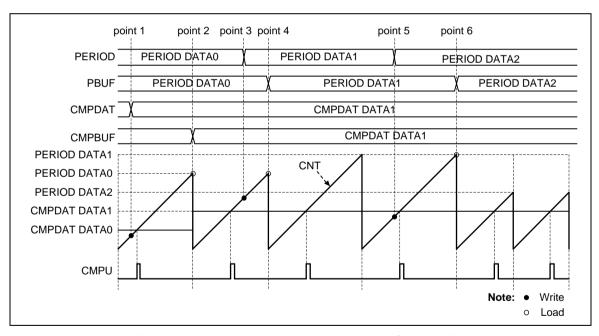

| Figure 6.9-12 Period Loading Mode with Up-Counter Type                  | . 378 |

| Figure 6.9-13 Immediately Loading Mode with Up-Counter Type             | . 379 |

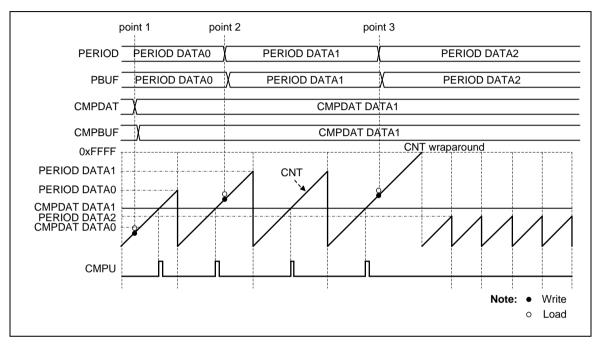

| Figure 6.9-14 Center Loading Mode with Up-Down-Counter Type             | . 380 |

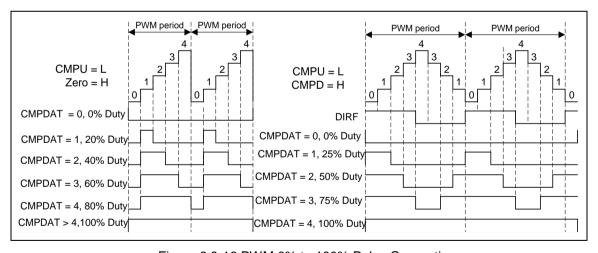

| Figure 6.9-15 PWM Pulse Generation                                      | . 381 |

| Figure 6.9-16 PWM 0% to 100% Pulse Generation                           | . 381 |

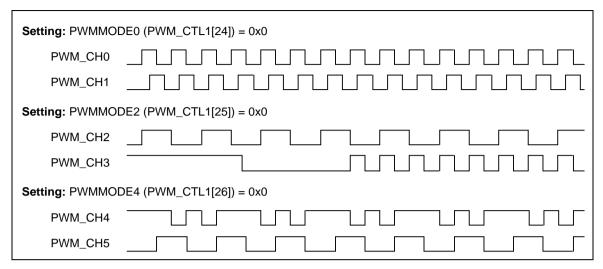

| Figure 6.9-17 PWM Independent Mode Waveform                             | . 383 |

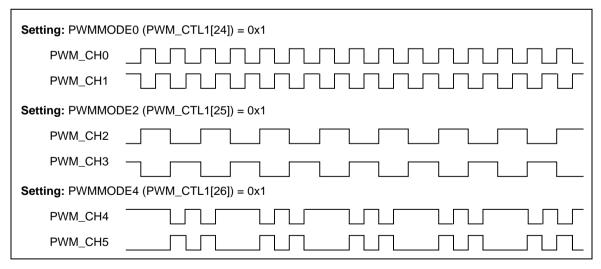

| Figure 6.9-18 PWM Complementary Mode Waveform                           | . 383 |

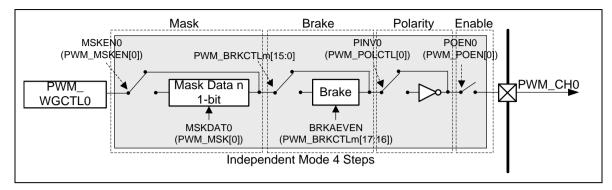

| Figure 6.9-19 PWM_CH0 Output Control in Independent Mode                | . 384 |

| Figure 6.9-20 PWM_CH0 and PWM_CH1 Output Control in Complementary Mode  | . 384 |

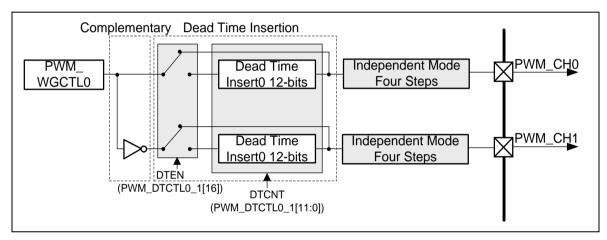

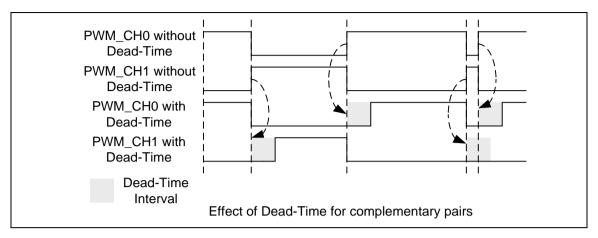

| Figure 6.9-21 Dead-Time Insertion                                       | . 385 |

| Figure 6.9-22 Illustration of Mask Control Waveform                     | . 385 |

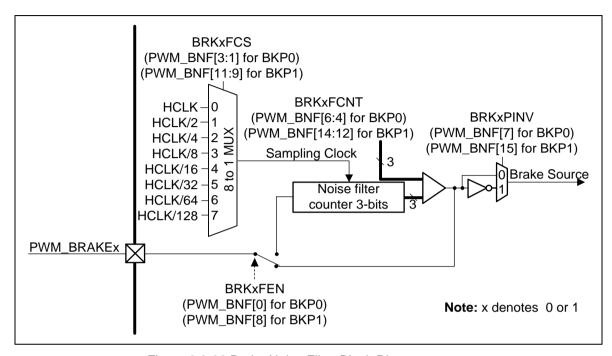

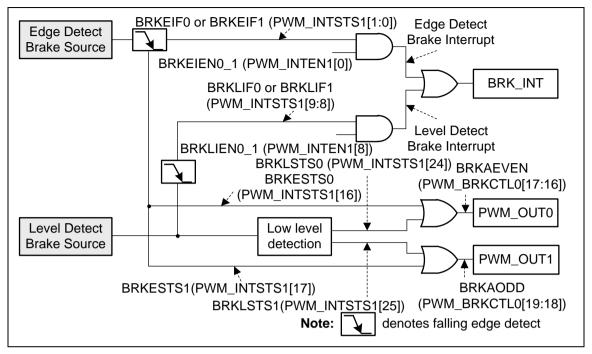

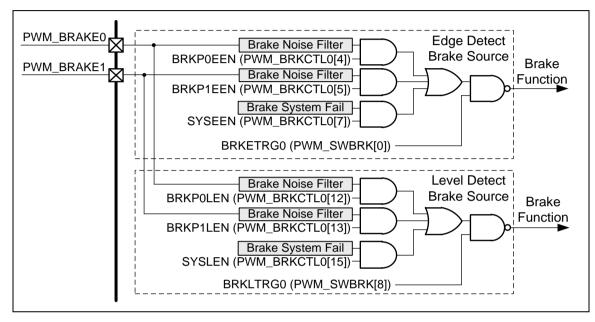

| Figure 6.9-23 Brake Noise Filter Block Diagram                          | . 386 |

| Figure 6.9-24 Brake Block Diagram for PWM_CH0 and PWM_CH1 Pair          | . 387 |

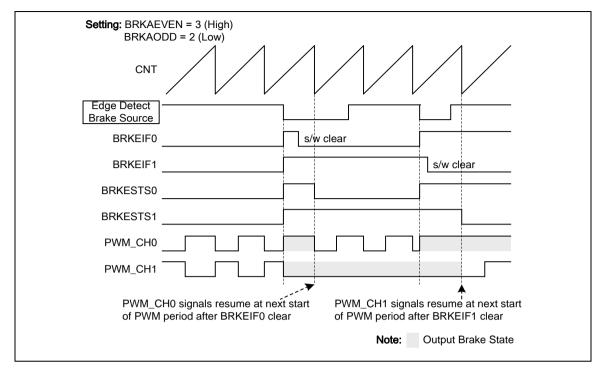

| Figure 6.9-25 Edge Detector Waveform for PWM_CH0 and PWM_CH1 Pair       | . 388 |

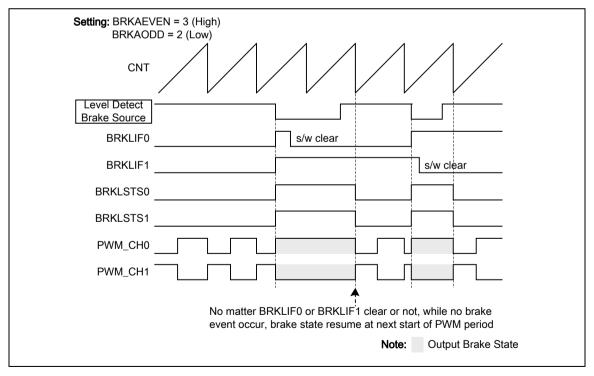

| Figure 6.9-26 Level Detector Waveform for PWM_CH0 and PWM_CH1 Pair      | . 388 |

| Figure 6.9-27 Brake Source Block Diagram for PWM_CH0 and PWM_CH1 Pair   | . 389 |

|                                                                         |       |

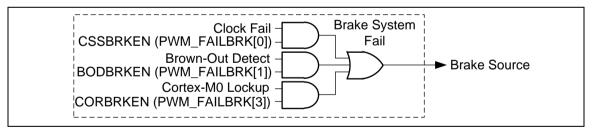

| Figure 6.9-28 Brake System Fail Block Diagram                                         | 389 |

|---------------------------------------------------------------------------------------|-----|

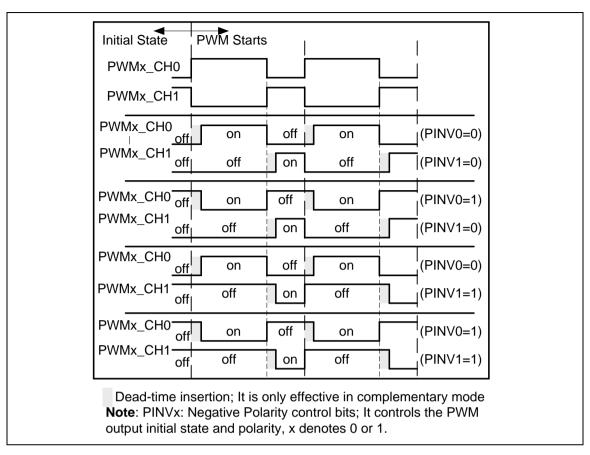

| Figure 6.9-29 Initial State and Polarity Control with Rising Edge Dead-Time Insertion | 390 |

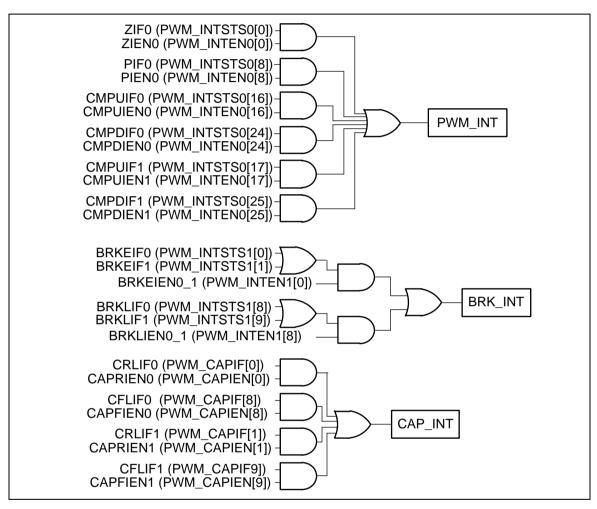

| Figure 6.9-30 PWM_CH0 and PWM_CH1 Pair Interrupt Architecture Diagram                 | 391 |

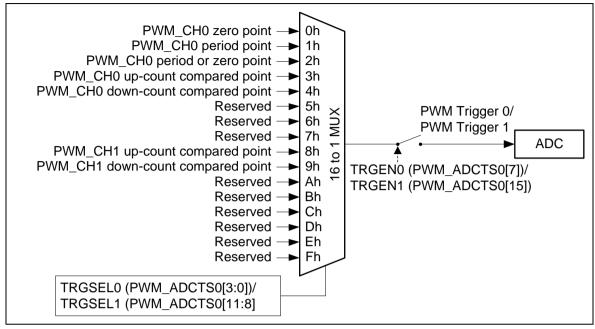

| Figure 6.9-31 PWM_CH0 and PWM_CH1 Pair Trigger ADC Block Diagram                      | 392 |

| Figure 6.9-32 PWM Trigger ADC in Up-Down Counter Type Timing Waveform                 | 392 |

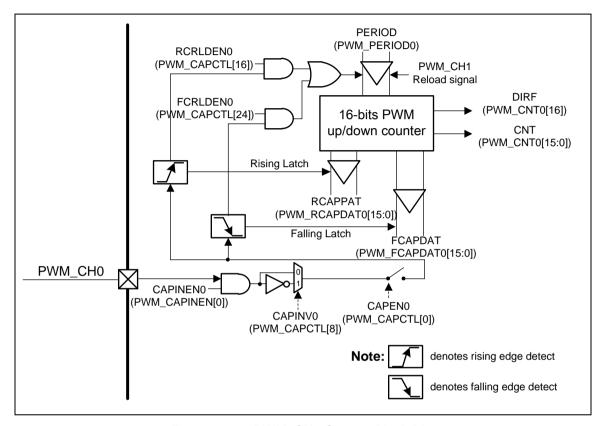

| Figure 6.9-33 PWM_CH0 Capture Block Diagram                                           | 393 |

| Figure 6.9-34 Capture Operation Waveform                                              | 394 |

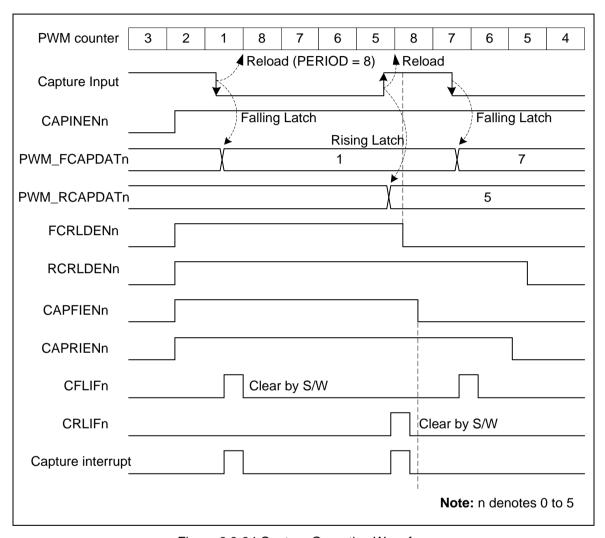

| Figure 6.9-35 Capture PDMA Operation Waveform of Channel 0                            | 395 |

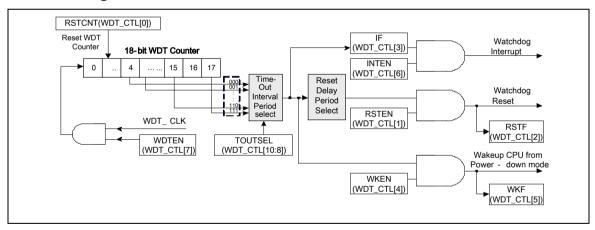

| Figure 6.10-1 Watchdog Timer Block Diagram                                            | 453 |

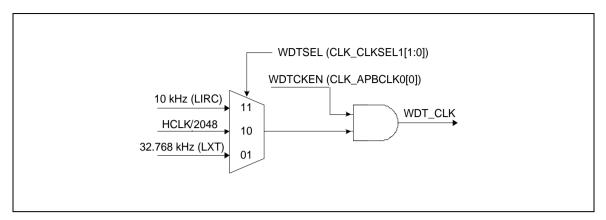

| Figure 6.10-2 Watchdog Timer Clock Control                                            | 454 |

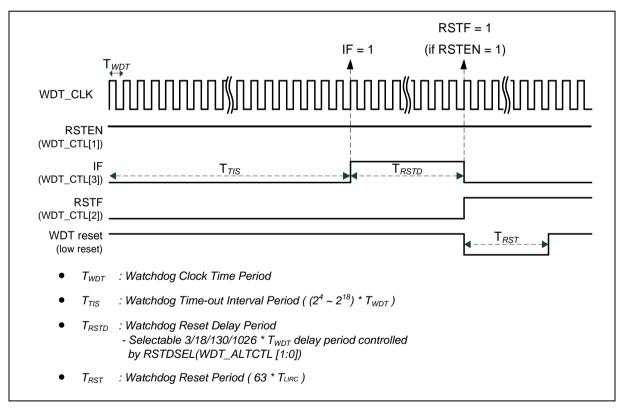

| Figure 6.10-3 Watchdog Timer Time-out Interval and Reset Period Timing                | 455 |

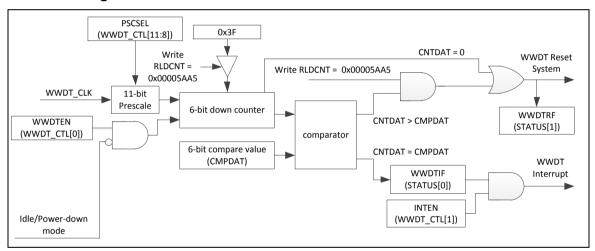

| Figure 6.11-1 WWDT Block Diagram                                                      | 463 |

| Figure 6.11-2 WWDT Clock Control                                                      | 464 |

| Figure 6.11-3 WWDT Compare Match Interrupt when CMPDAT is 0x3E                        | 466 |

| Figure 6.11-4 WWDT Reset and Reload Behavior                                          | 466 |

| Figure 6.12-1 USCI Block Diagram                                                      | 475 |

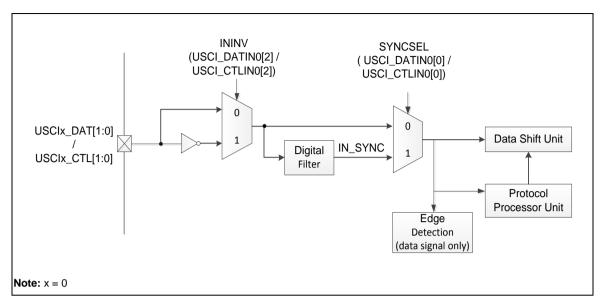

| Figure 6.12-2 Input Conditioning for USCIx_DAT[1:0] and USCIx_CTL[1:0]                | 477 |

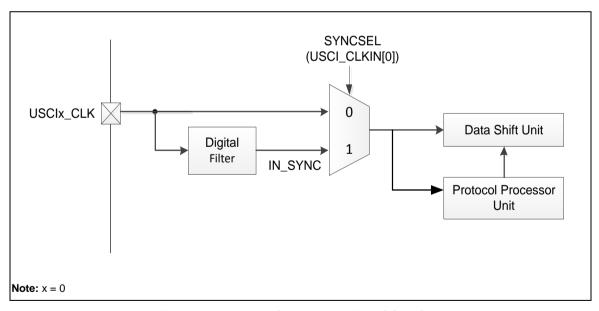

| Figure 6.12-3 Input Conditioning for USCIx_CLK                                        | 477 |

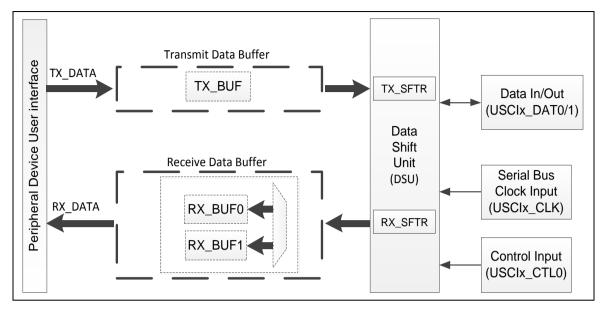

| Figure 6.12-4 Block Diagram of Data Buffering                                         | 479 |

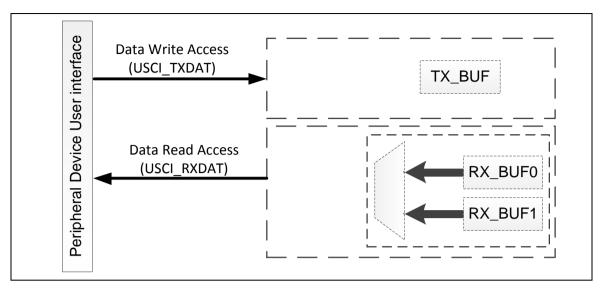

| Figure 6.12-5 Data Access Structure                                                   | 480 |

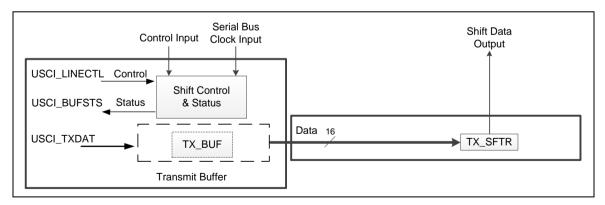

| Figure 6.12-6 Transmit Data Path                                                      | 480 |

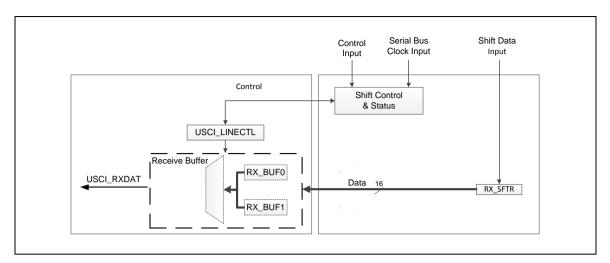

| Figure 6.12-7 Receive Data Path                                                       | 482 |

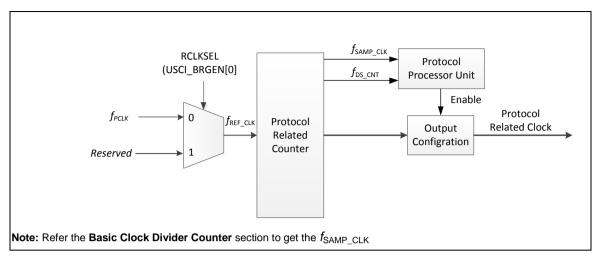

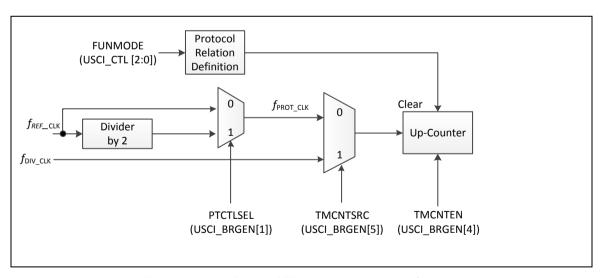

| Figure 6.12-8 Protocol-Relative Clock Generator                                       | 483 |

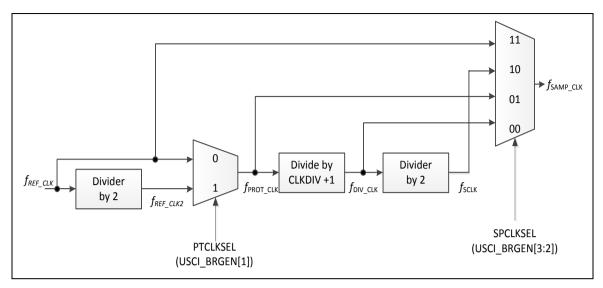

| Figure 6.12-9 Basic Clock Divider Counter                                             | 484 |

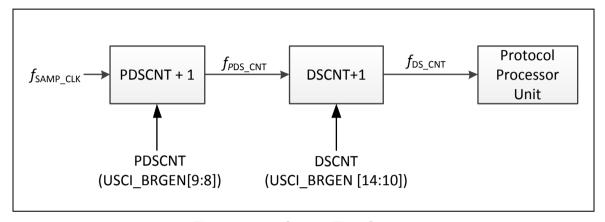

| Figure 6.12-10 Block of Timing Measurement Counter                                    | 484 |

| Figure 6.12-11 Sample Time Counter                                                    | 485 |

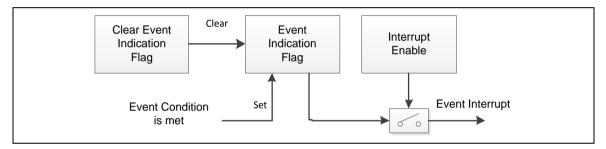

| Figure 6.12-12 Event and Interrupt Structure                                          | 486 |

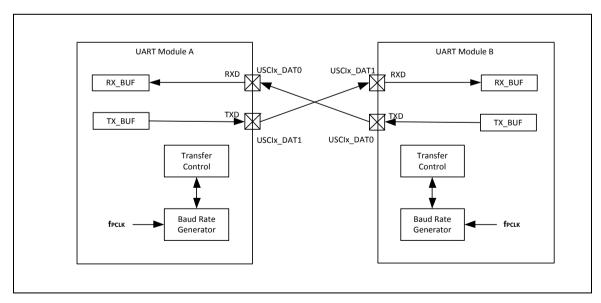

| Figure 6.13-1 Block Diagram                                                           | 489 |

| Figure 6.13-2 UART Signal Connection for Full-Duplex Communication                    | 489 |

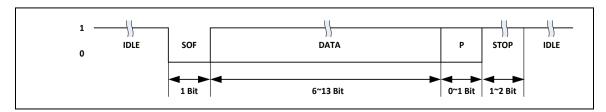

| Figure 6.13-3 UART Standard Frame Format                                              | 491 |

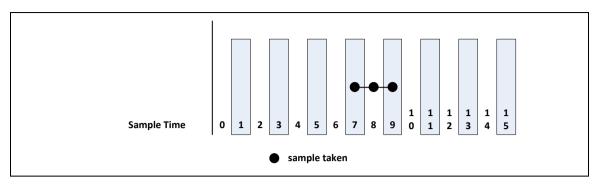

| Figure 6.13-4 UART Bit Timing (data sample time)                                      | 493 |

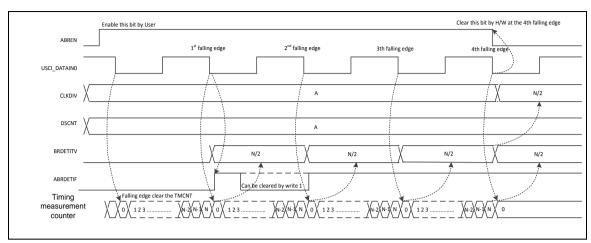

| Figure 6.13-5 UART Auto Baud Rate Control                                             | 495 |

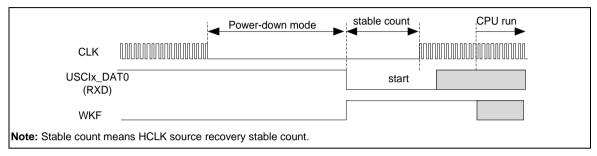

| Figure 6.13-6 Incoming Data Wake-Up                                                   | 496 |

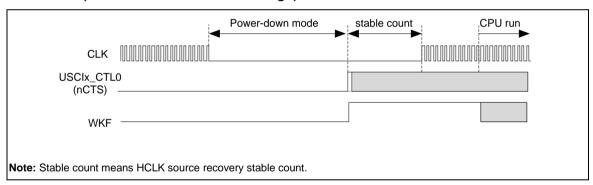

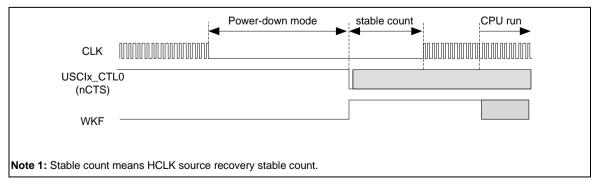

| Figure 6.13-7 nCTS Wake-Up Case 1                                                     | 496 |

| Figure 6.13-8 nCTS Wake-Up Case 2                                                     | 496 |

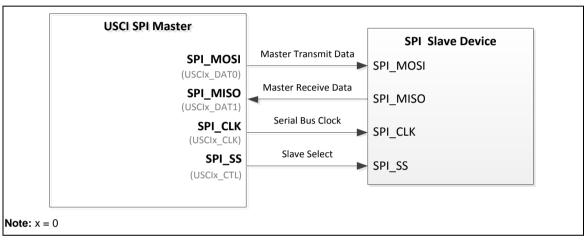

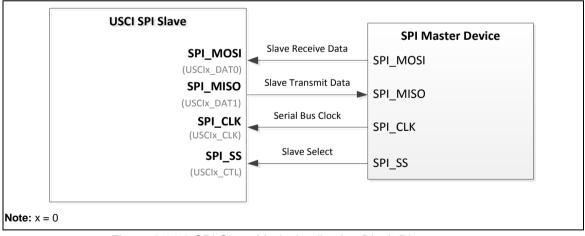

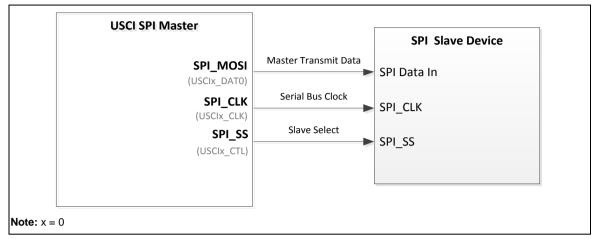

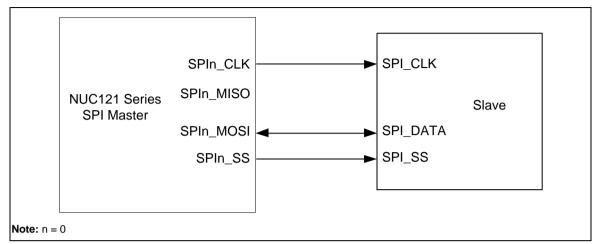

| Figure 6.14-1 SPI Master Mode Application Block Diagram                               | 522 |

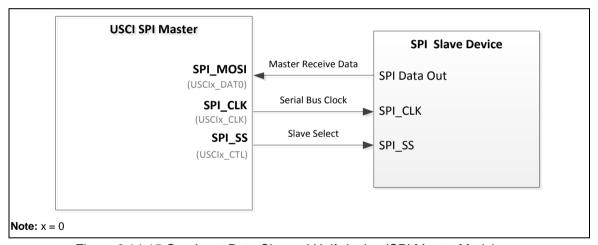

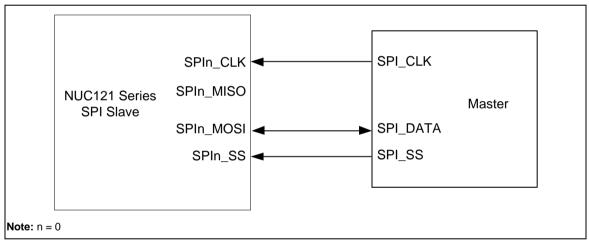

| Figure 6.14-2 SPI Slave Mode Application Block Diagram                                | 522 |

| Figure 6.14-3 Block Diagram                                                             | 523 |

|-----------------------------------------------------------------------------------------|-----|

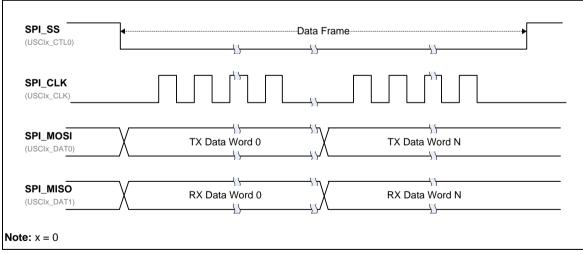

| Figure 6.14-4 4-Wire Full-Duplex SPI Communication Signals (Master Mode)                | 524 |

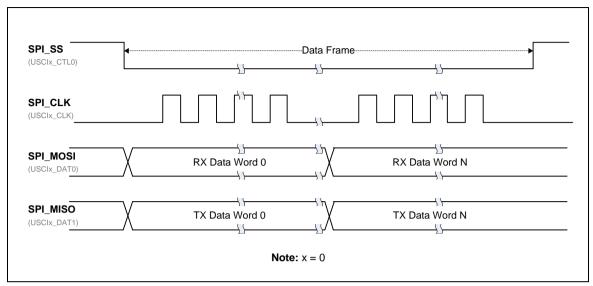

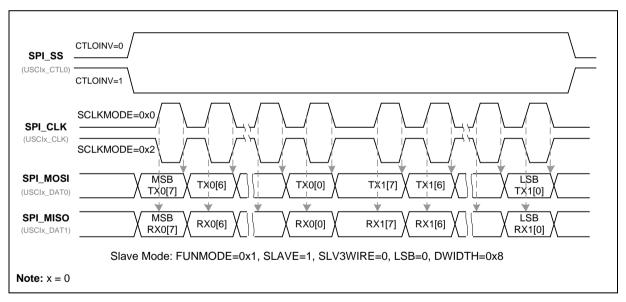

| Figure 6.14-54-Wire Full-Duplex SPI Communication Signals (Slave Mode)                  | 525 |

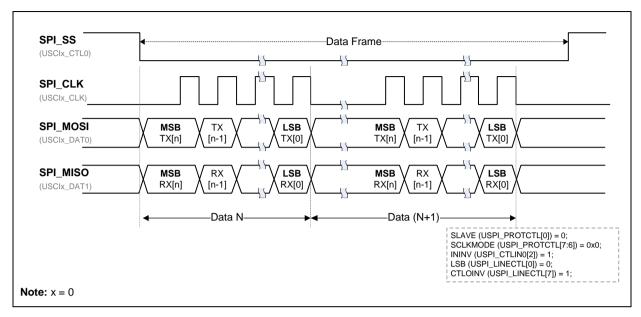

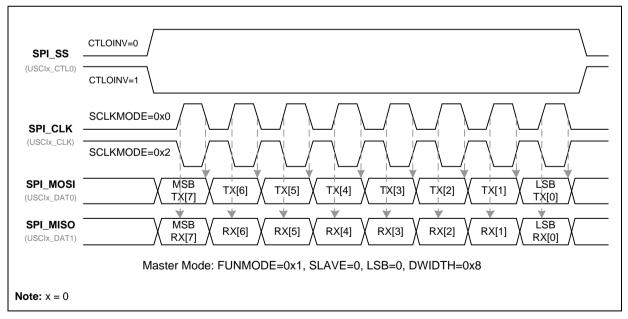

| Figure 6.14-6 SPI Communication with Different SPI Clock Configuration (SCLKMODE = 0x0) | 526 |

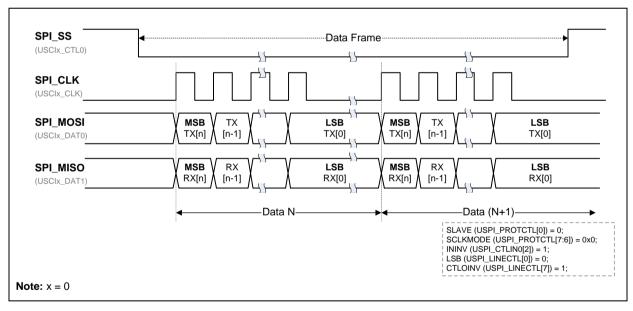

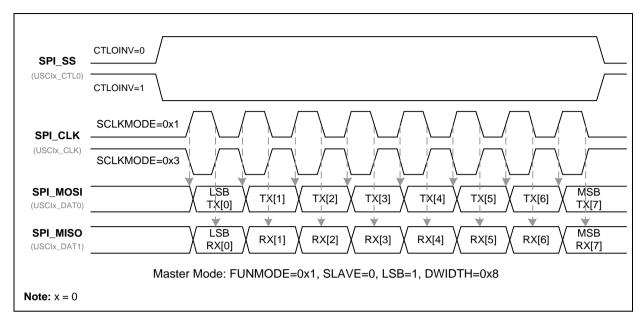

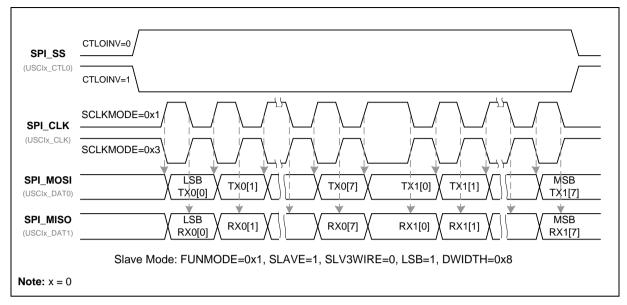

| Figure 6.14-7 SPI Communication with Different SPI Clock Configuration (SCLKMODE = 0x1) | 526 |

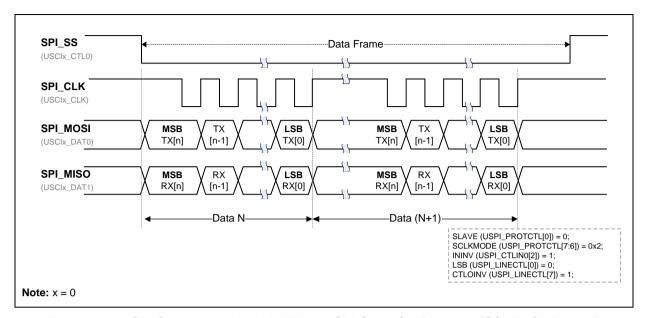

| Figure 6.14-8 SPI Communication with Different SPI Clock Configuration (SCLKMODE = 0x2) | 527 |

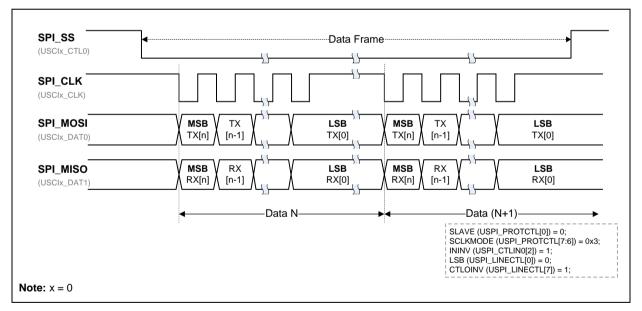

| Figure 6.14-9 SPI Communication with Different SPI Clock Configuration (SCLKMODE = 0x3) | 527 |

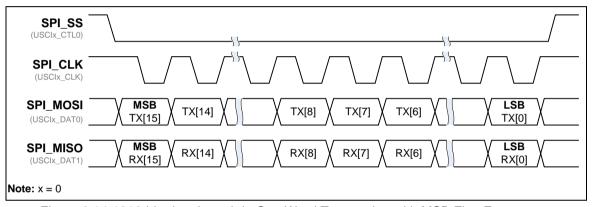

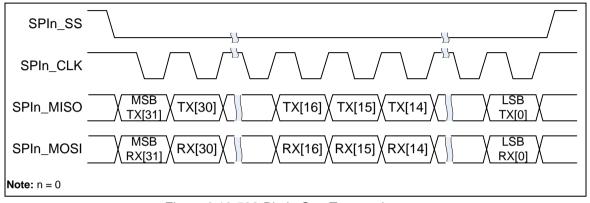

| Figure 6.14-1016-bit data Length in One Word Transaction with MSB First Format          | 528 |

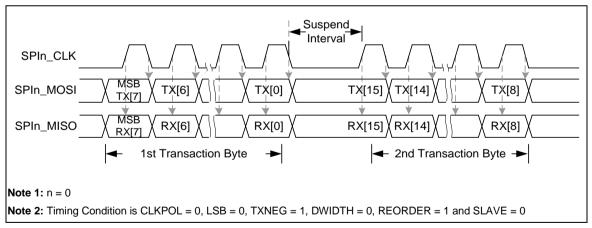

| Figure 6.14-11 Word Suspend Interval between Two Transaction Words                      | 528 |

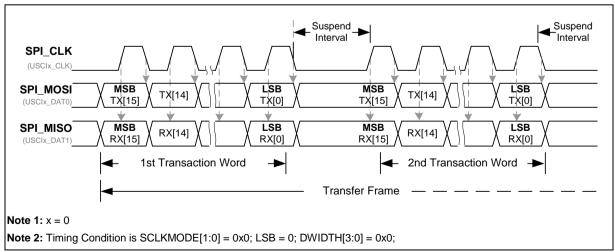

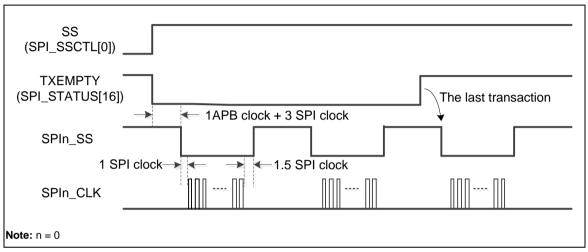

| Figure 6.14-12 Auto Slave Select (SUSPITV $\geq 0x3$ )                                  | 529 |

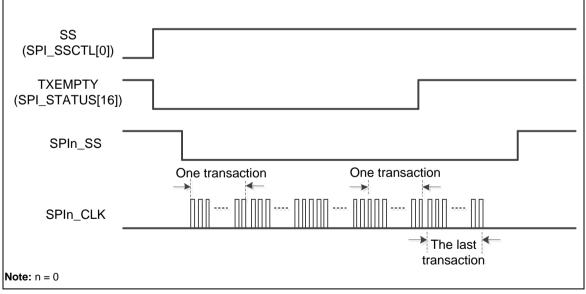

| Figure 6.14-13 Auto Slave Select (SUSPITV < 0x3)                                        | 530 |

| Figure 6.14-14 One Output Data Channel Half-duplex (SPI Master Mode)                    | 531 |

| Figure 6.14-15 One Input Data Channel Half-duplex (SPI Master Mode)                     | 531 |

| Figure 6.14-16 SPI Timing in Master Mode                                                | 533 |

| Figure 6.14-17 SPI Timing in Master Mode (Alternate Phase of Serial Bus Clock)          | 534 |

| Figure 6.14-18 SPI Timing in Slave Mode                                                 | 534 |

| Figure 6.14-19 SPI Timing in Slave Mode (Alternate Phase of Serial Bus Clock)           | 535 |

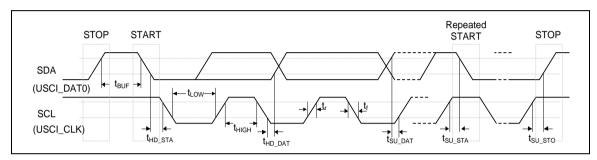

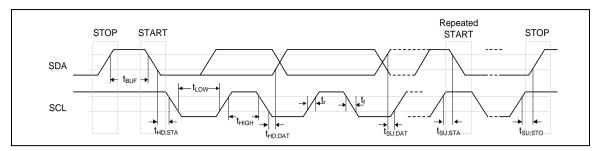

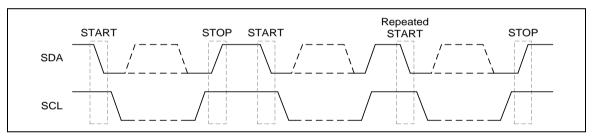

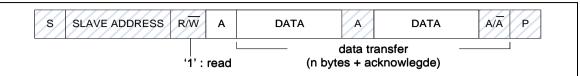

| Figure 6.15-1 I <sup>2</sup> C Bus Timing                                               | 562 |

| Figure 6.15-2 Block Diagram                                                             | 563 |

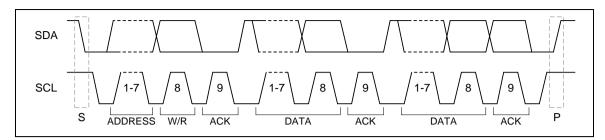

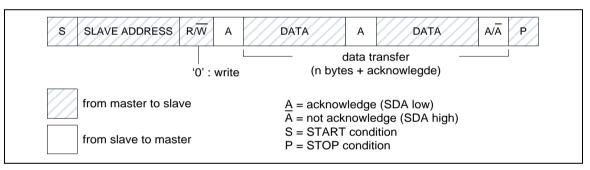

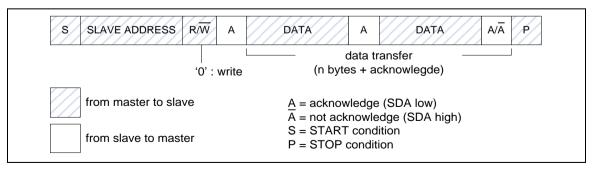

| Figure 6.15-3 I <sup>2</sup> C Protocol                                                 | 564 |

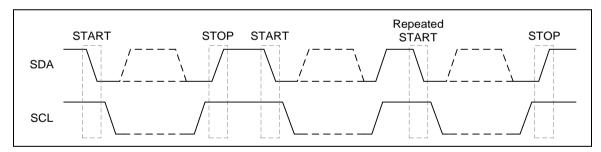

| Figure 6.15-4 START and STOP Conditions                                                 | 564 |

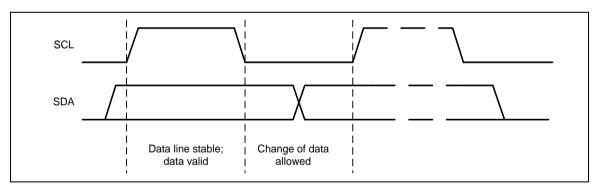

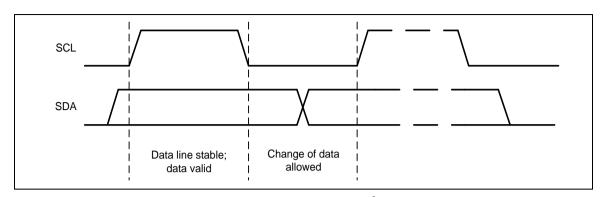

| Figure 6.15-5 Bit Transfer on the I <sup>2</sup> C Bus                                  | 565 |

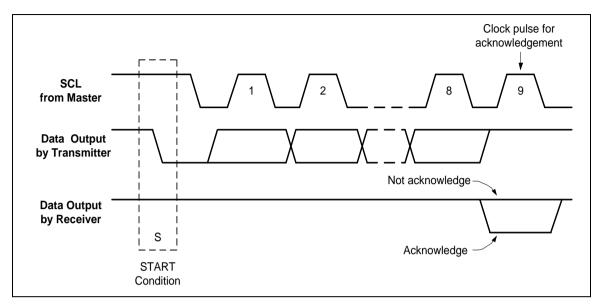

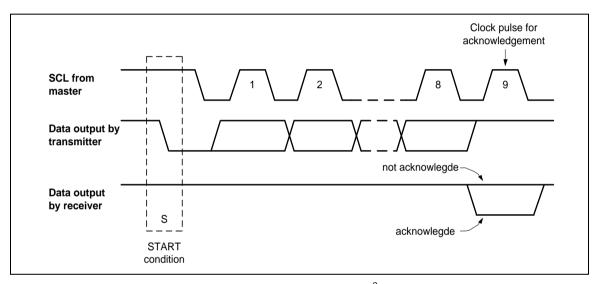

| Figure 6.15-6 Acknowledge on the I <sup>2</sup> C Bus                                   | 566 |

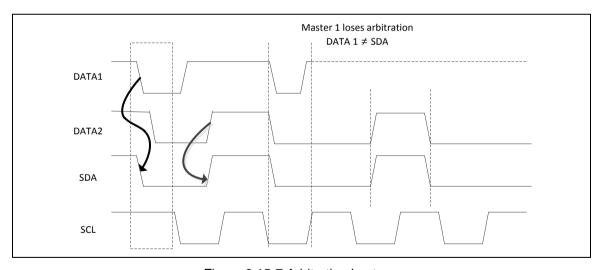

| Figure 6.15-7 Arbitration Lost                                                          | 567 |

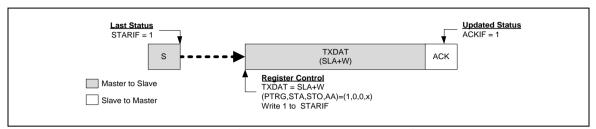

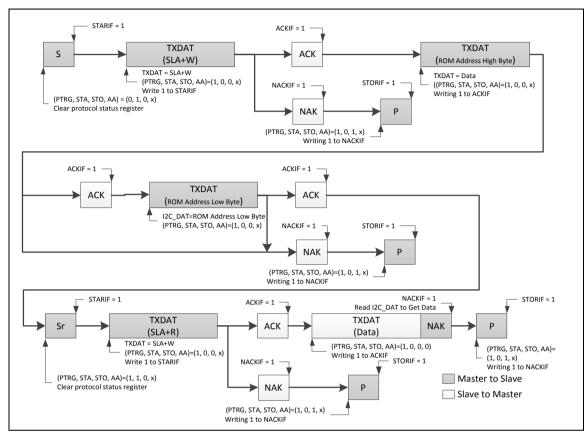

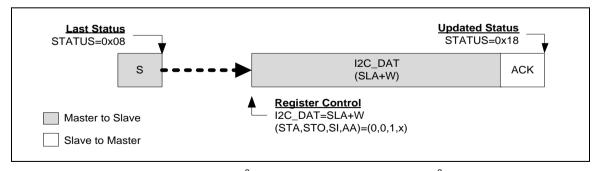

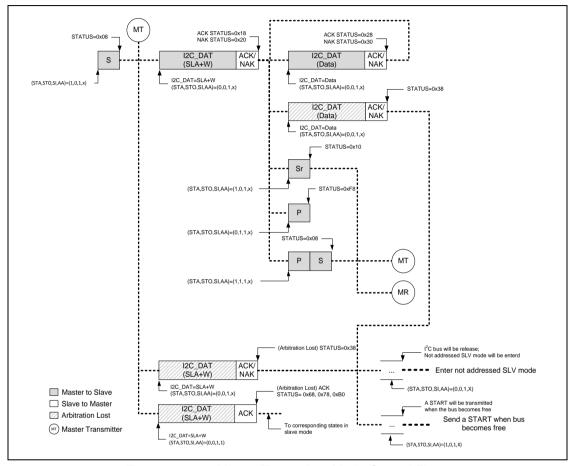

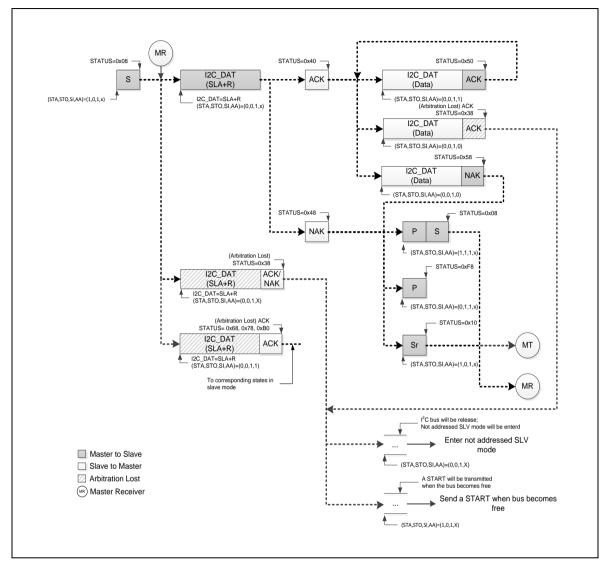

| Figure 6.15-8 Control I <sup>2</sup> C Bus according to Current I <sup>2</sup> C Status | 570 |

| Figure 6.15-9 Master Transmits Data to Slave with a 7-bit Address                       | 570 |

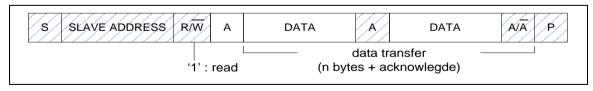

| Figure 6.15-10 Master Reads Data from Slave with a 7-bit Address                        | 570 |

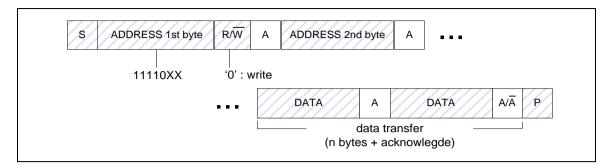

| Figure 6.15-11 Master Transmits Data to Slave by 10-bit Address                         | 571 |

| Figure 6.15-12 Master Reads Data from Slave by 10-bit Address                           | 571 |

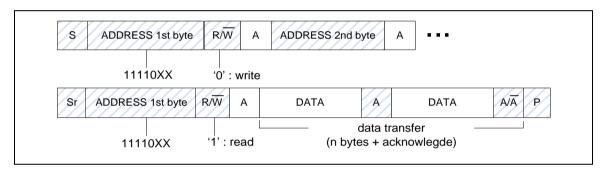

| Figure 6.15-13 Master Transmitter Mode Control Flow with 7-bit Address                  | 572 |

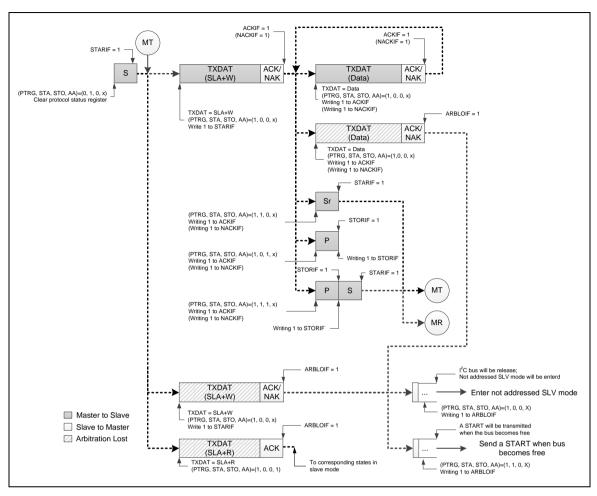

| Figure 6.15-14 Master Receiver Mode Control Flow with 7-bit Address                     | 573 |

| Figure 6.15-15 Save Mode Control Flow with 7-bit Address                                | 575 |

| Figure 6.15-16 GC Mode with 7-bit Address                                               | 576 |

| Figure 6.15-17 Setup Time Wrong Adjustment                                              | 578 |

| Figure 6.15-18 Hold Time Wrong Adjustment                                               | 579 |

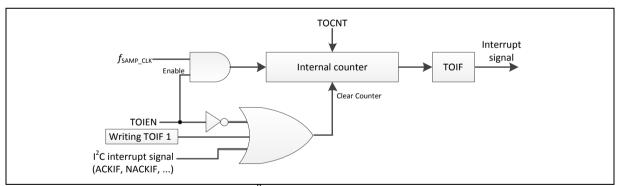

| Figure 6.15-19 I <sup>2</sup> C Time-out Count Block Diagram                            | 579 |

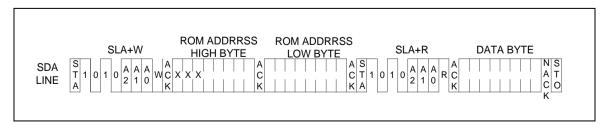

| Figure 6.15-20 EEPROM Random Read                                                       | 580 |

|                                                                                         |     |

| Figure 6.15-21 Protocol of EEPROM Random Read                                               | 581 |

|---------------------------------------------------------------------------------------------|-----|

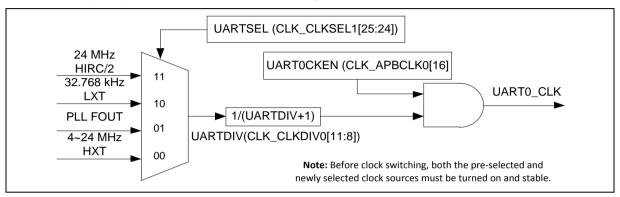

| Figure 6.16-1 UART Clock Control Diagram                                                    | 602 |

| Figure 6.16-2 UART Block Diagram                                                            | 602 |

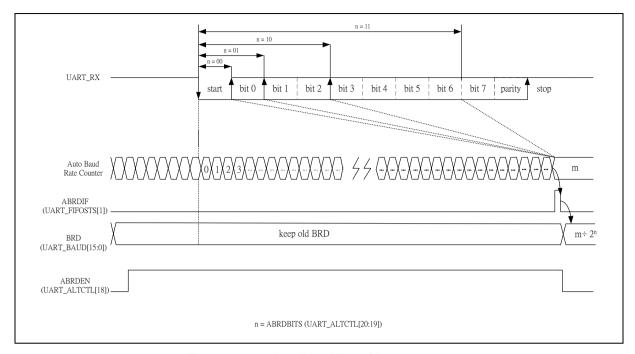

| Figure 6.16-3 Auto-Baud Rate Measurement                                                    | 608 |

| Figure 6.16-4 Transmit Delay Time Operation                                                 | 608 |

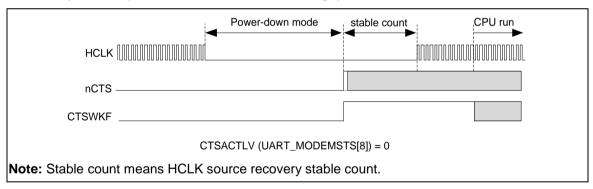

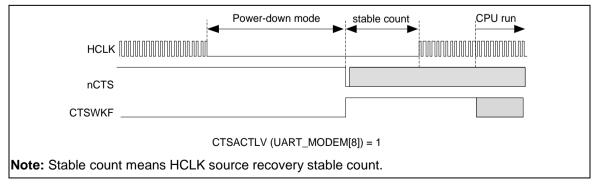

| Figure 6.16-5 UART nCTS Wake-up Case1                                                       | 609 |

| Figure 6.16-6 UART nCTS Wake-up Case2                                                       | 609 |

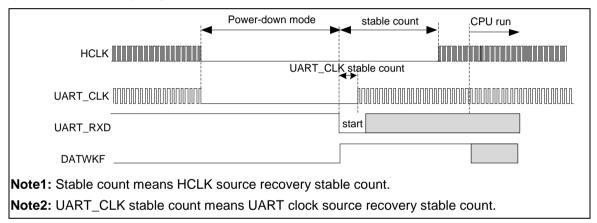

| Figure 6.16-7 UART Data Wake-up                                                             | 610 |

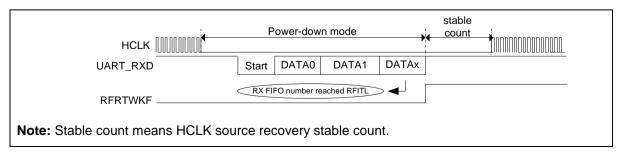

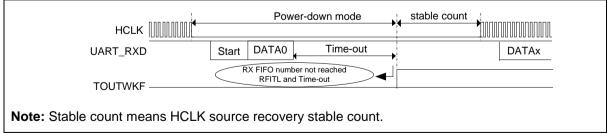

| Figure 6.16-8 UART Received Data FIFO reached threshold wake-up                             | 610 |

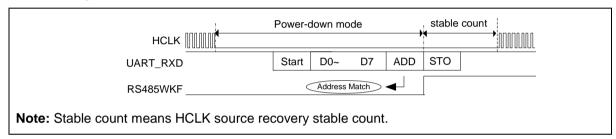

| Figure 6.16-9 UART RS-485 AAD Mode Address Match Wake-up                                    | 611 |

| Figure 6.16-10 UART Received Data FIFO threshold time-out wake-up                           | 611 |

| Figure 6.16-11 Auto-Flow Control Block Diagram                                              | 615 |

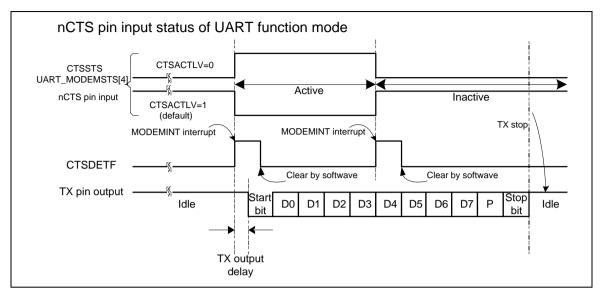

| Figure 6.16-12 UART nCTS Auto-Flow Control Enabled                                          | 616 |

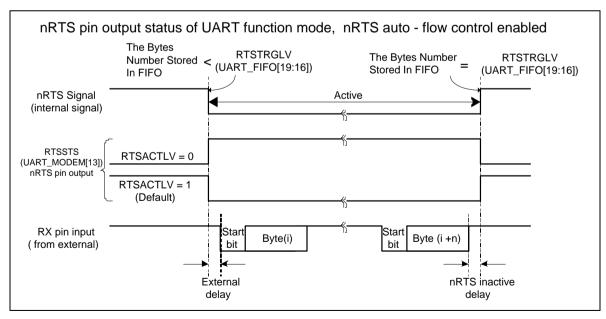

| Figure 6.16-13 UART nRTS Auto-Flow Control Enabled                                          | 616 |

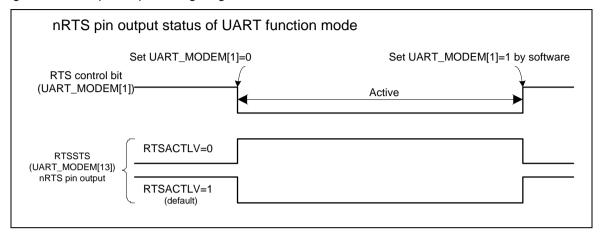

| Figure 6.16-14 UART nRTS Auto-Flow with Software Control                                    | 617 |

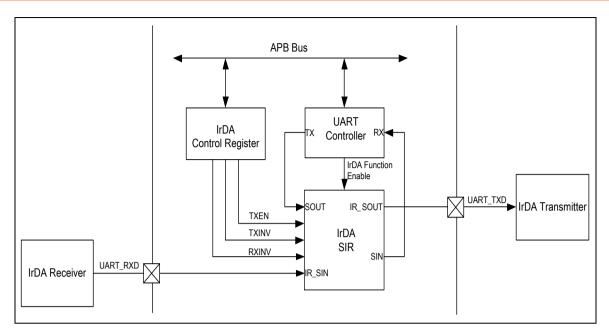

| Figure 6.16-15 IrDA Control Block Diagram                                                   | 618 |

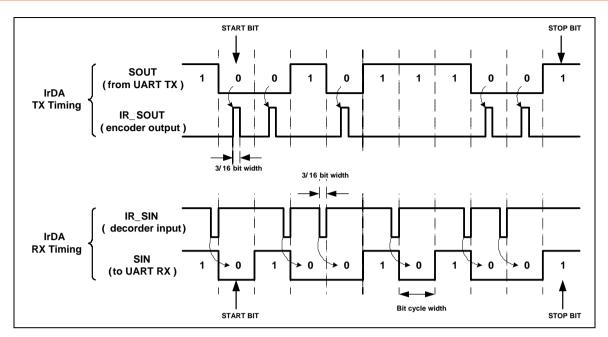

| Figure 6.16-16 IrDA TX/RX Timing Diagram                                                    | 619 |

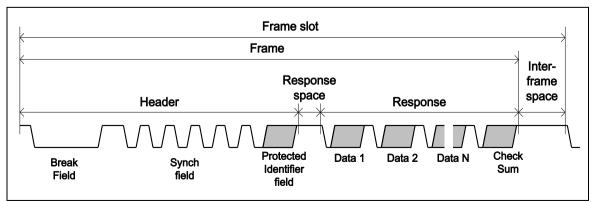

| Figure 6.16-17 Structure of LIN Frame                                                       | 619 |

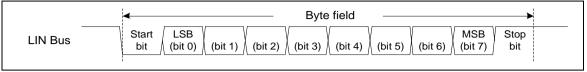

| Figure 6.16-18 Structure of LIN Byte                                                        | 620 |

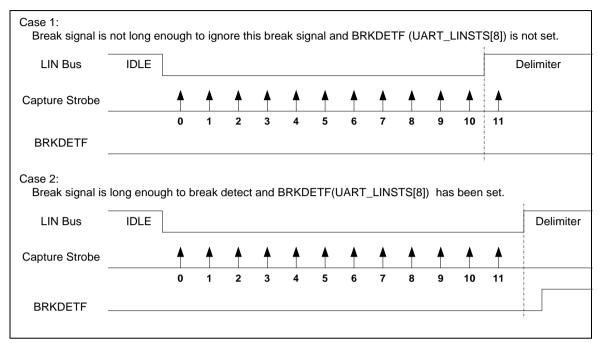

| Figure 6.16-19 Break Detection in LIN Mode                                                  | 622 |

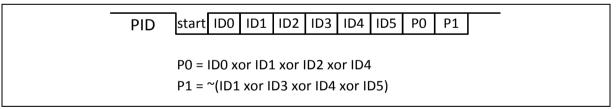

| Figure 6.16-20 LIN Frame ID and Parity Format                                               | 622 |

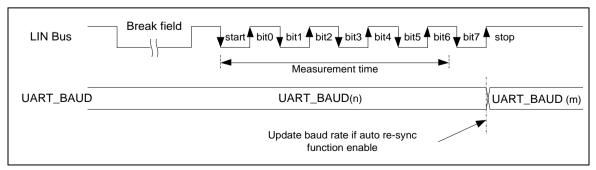

| Figure 6.16-21 LIN Sync Field Measurement                                                   | 624 |

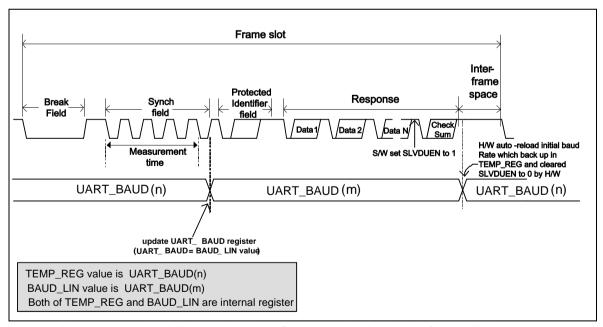

| Figure 6.16-22 UART_BAUD Update Sequence in AR Mode if SLVDUEN is 1                         | 625 |

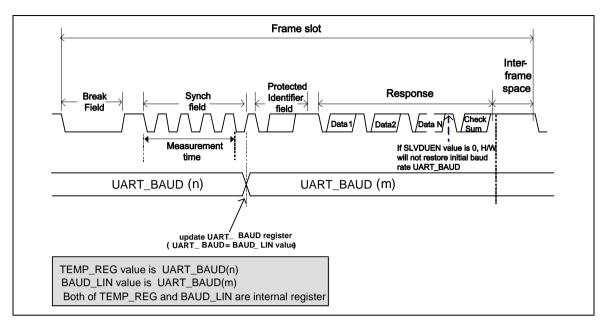

| Figure 6.16-23 UART_BAUD Update Sequence in AR Mode if SLVDUEN is 0                         | 626 |

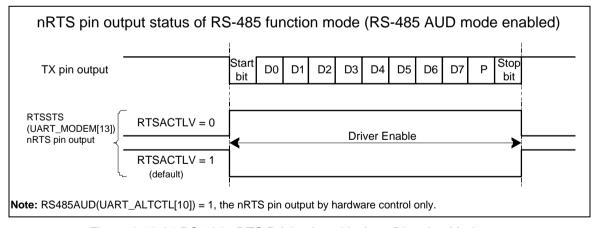

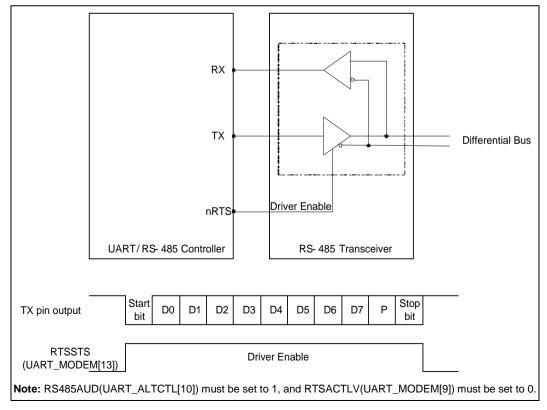

| Figure 6.16-24 RS-485 nRTS Driving Level in Auto Direction Mode                             | 628 |

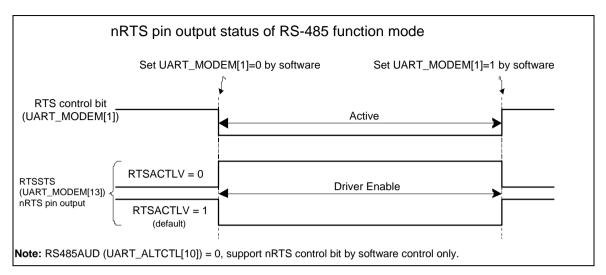

| Figure 6.16-25 RS-485 nRTS Driving Level with Software Control                              | 629 |

| Figure 6.16-26 Structure of RS-485 Frame                                                    | 630 |

| Figure 6.17-1 I <sup>2</sup> C Controller Block Diagram                                     | 668 |

| Figure 6.17-2 I <sup>2</sup> C Bus Timing                                                   | 669 |

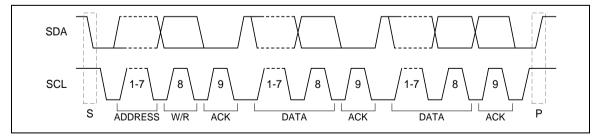

| Figure 6.17-3 I <sup>2</sup> C Protocol                                                     | 669 |

| Figure 6.17-4 START and STOP Conditions                                                     | 670 |

| Figure 6.17-5 Bit Transfer on the I <sup>2</sup> C Bus                                      | 671 |

| Figure 6.17-6 Acknowledge on the I <sup>2</sup> C Bus                                       | 671 |

| Figure 6.17-7 Master Transmits Data to Slave by 7-bit                                       | 671 |

| Figure 6.17-8 Master Reads Data from Slave by 7-bit                                         | 672 |

| Figure 6.17-9 Control I <sup>2</sup> C Bus according to the current I <sup>2</sup> C Status | 672 |

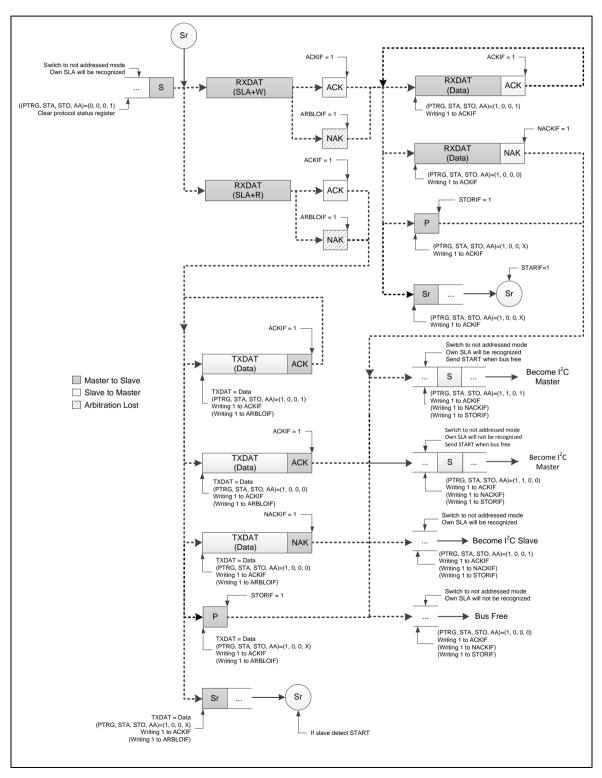

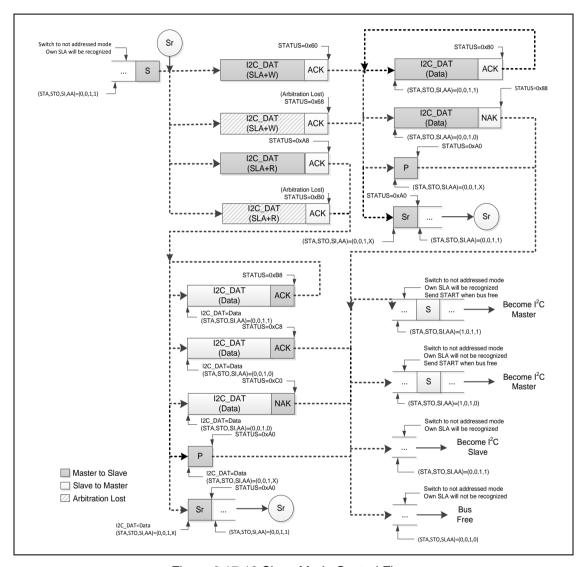

| Figure 6.17-10 Master Transmitter Mode Control Flow                                         | 673 |

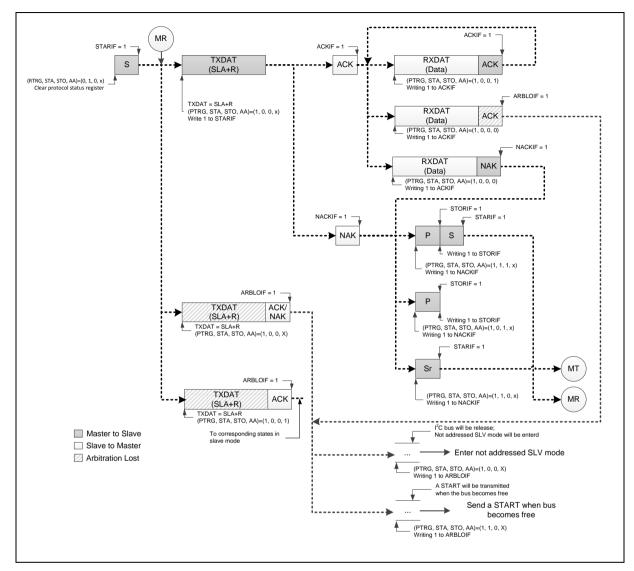

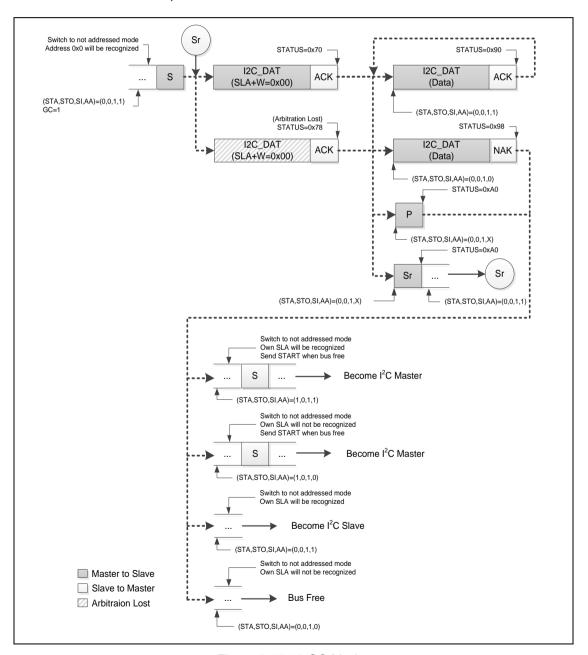

| Figure 6.17-12 Slave Mode Control Flow                                | 675 |

|-----------------------------------------------------------------------|-----|

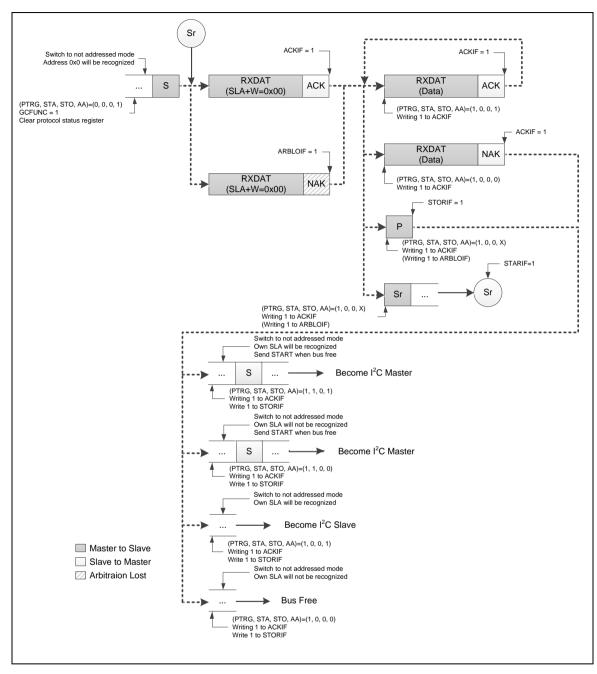

| Figure 6.17-13 GC Mode                                                | 676 |

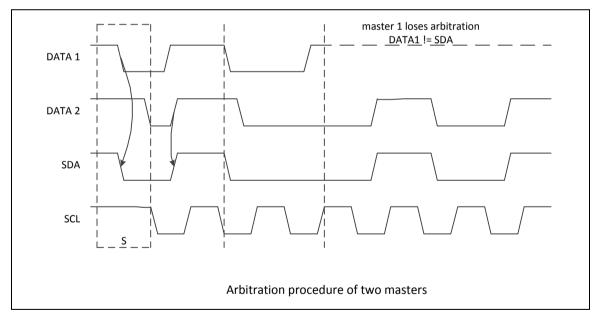

| Figure 6.17-14 Arbitration Lost                                       | 677 |

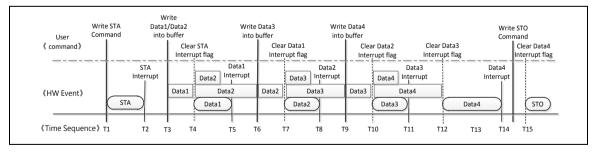

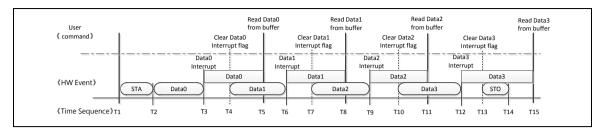

| Figure 6.17-15 Timing of Two-level Buffer Transmit in Master Write    | 678 |

| Figure 6.17-16 Timing of Two-level Buffer Transmit in Slave Read      | 679 |

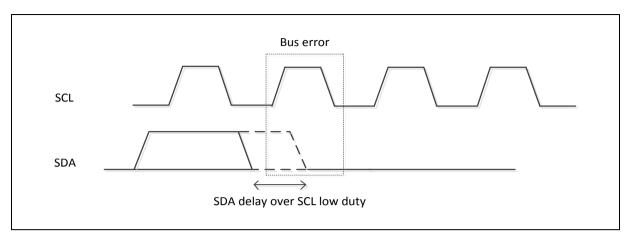

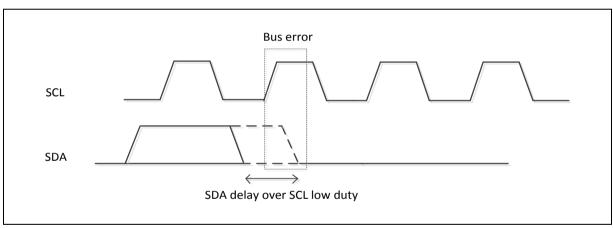

| Figure 6.17-17 Setup Time Wrong Adjustment                            | 680 |

| Figure 6.17-18 Hold Time Wrong Adjustment                             | 680 |

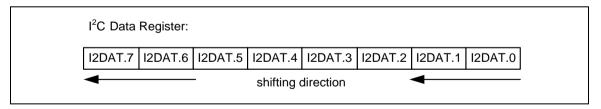

| Figure 6.17-19 I <sup>2</sup> C Data Shifting Direction               | 681 |

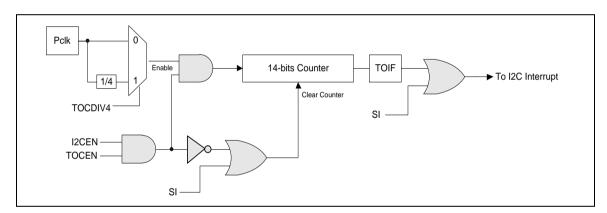

| Figure 6.17-20 I <sup>2</sup> C Time-out Count Block Diagram          | 683 |

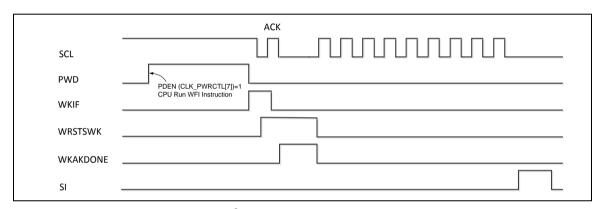

| Figure 6.17-21 I <sup>2</sup> C Wake-Up Related Signals Waveform      | 684 |

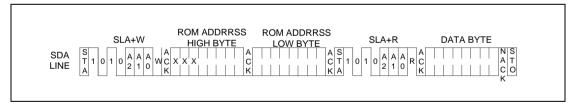

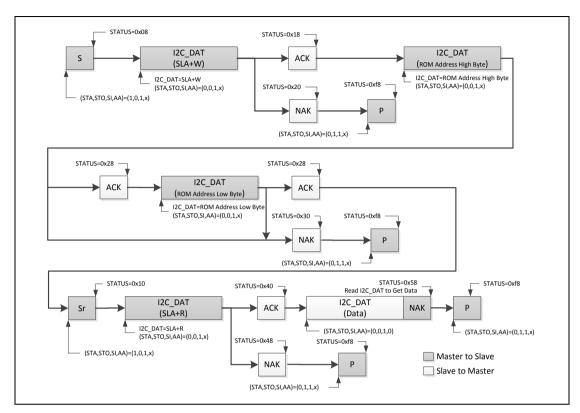

| Figure 6.17-22 EEPROM Random Read                                     | 685 |

| Figure 6.17-23 Protocol of EEPROM Random Read                         | 686 |

| Figure 6.18-1 SPI Block Diagram                                       | 703 |

| Figure 6.18-2 SPI Peripheral Clock                                    | 705 |

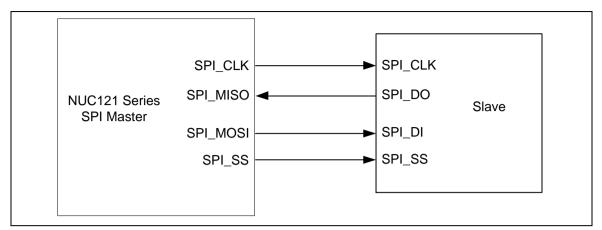

| Figure 6.18-3 SPI Full-Duplex Master Mode Application Block Diagram   | 706 |

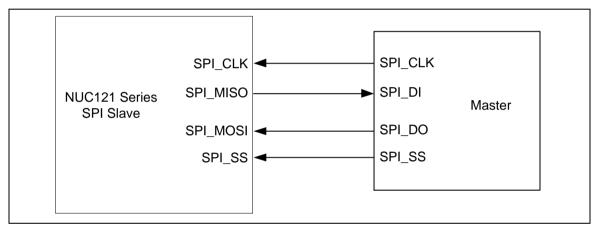

| Figure 6.18-4 SPI Full-Duplex Slave Mode Application Block Diagram    | 706 |

| Figure 6.18-532-Bit in One Transaction                                | 707 |

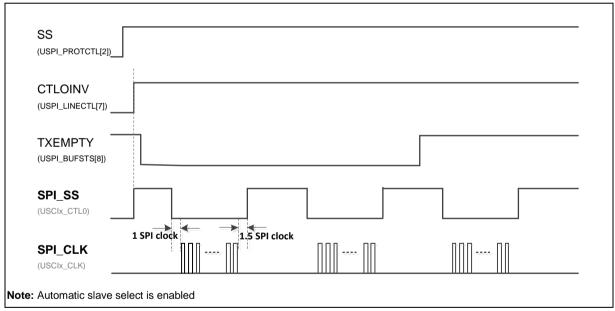

| Figure 6.18-6 Automatic Slave Selection (SSACTPOL = 0, SUSPITV > 0x2) | 708 |

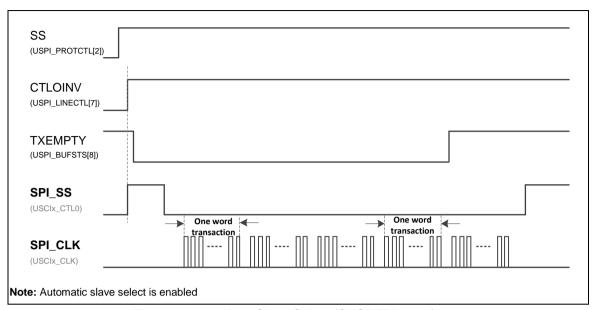

| Figure 6.18-7 Automatic Selection (SSACTPOL = 0, SUSPITV < 0x3)       | 708 |

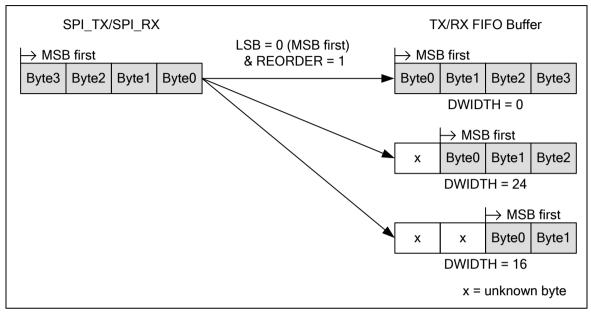

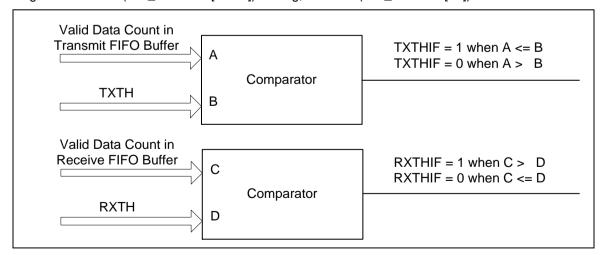

| Figure 6.18-8 Byte Reorder Function                                   | 709 |

| Figure 6.18-9 Timing Waveform for Byte Suspend                        | 709 |

| Figure 6.18-10 SPI Half-Duplex Master Mode Application Block Diagram  | 710 |

| Figure 6.18-11 SPI Half-Duplex Slave Mode Application Block Diagram   | 710 |

| Figure 6.18-12 FIFO Threshold Comparator                              | 711 |

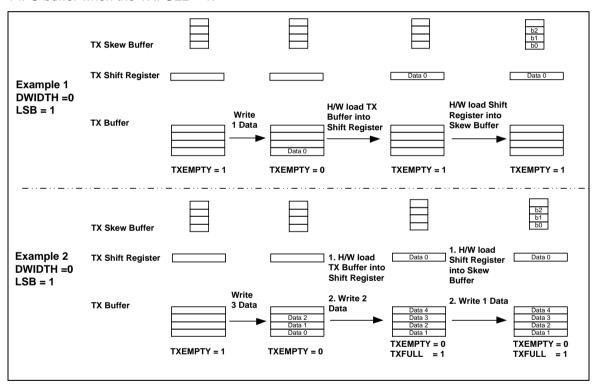

| Figure 6.18-13 Transmit FIFO Buffer Example                           | 712 |

| Figure 6.18-14 Receive FIFO Buffer Example                            | 713 |

| Figure 6.18-15 TX Underflow Event and Slave Under Run Event           | 714 |

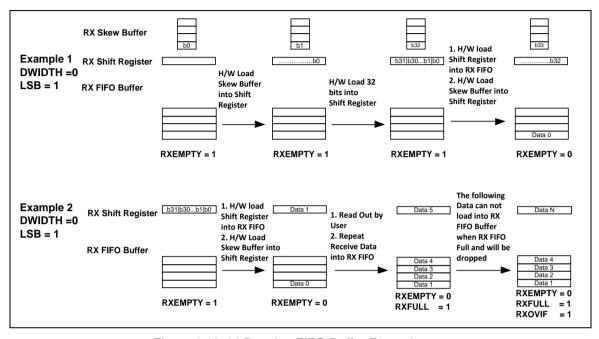

| Figure 6.18-16 Slave Mode Bit Count Error                             | 714 |

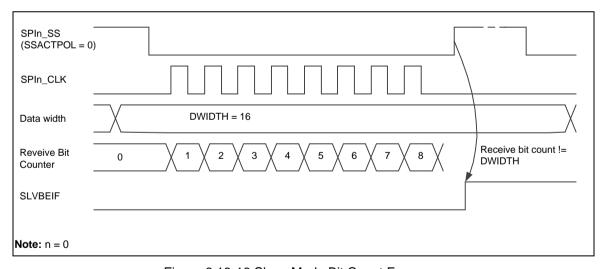

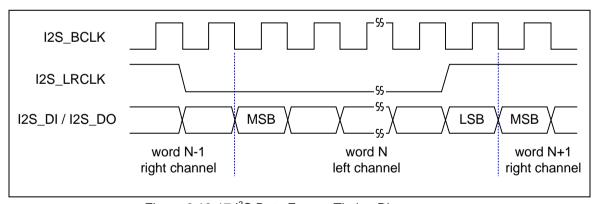

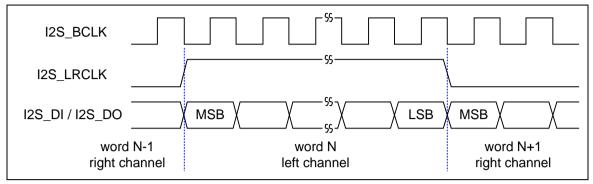

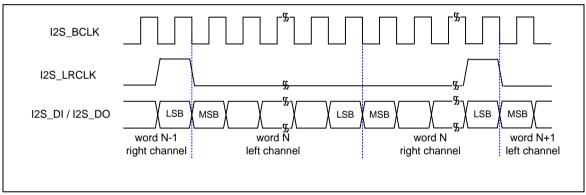

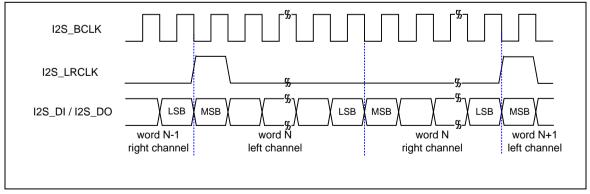

| Figure 6.18-17 I <sup>2</sup> S Data Format Timing Diagram            | 716 |

| Figure 6.18-18 MSB Justified Data Format Timing Diagram               | 717 |

| Figure 6.18-19 PCM Mode A Timing Diagram                              | 717 |

| Figure 6.18-20 PCM Mode B Timing Diagram                              | 717 |

| Figure 6.18-21 FIFO Contents for Various I <sup>2</sup> S Modes       | 718 |

| Figure 6.18-22 SPI Timing in Master Mode                              | 719 |

| Figure 6.18-23 SPI Timing in Master Mode (Alternate Phase of SPI_CLK) | 719 |

| Figure 6.18-24 SPI Timing in Slave Mode                               | 720 |

|                                                                       |     |

| Figure 6.18-25 SPI Timing in Slave Mode (Alternate Phase of SPI_CLK)       | 720 |

|----------------------------------------------------------------------------|-----|

| Figure 6.19-1 USB Block Diagram                                            | 745 |

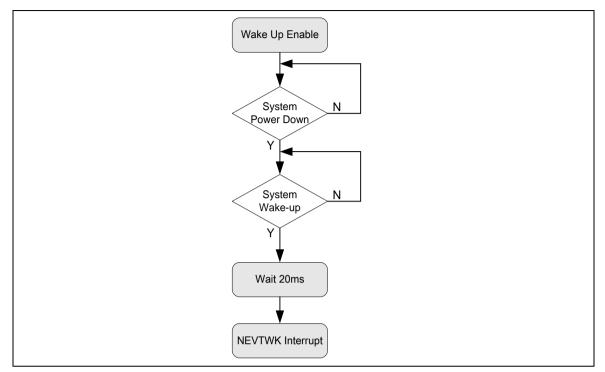

| Figure 6.19-2 NEVWK Interrupt Operation Flow                               | 747 |

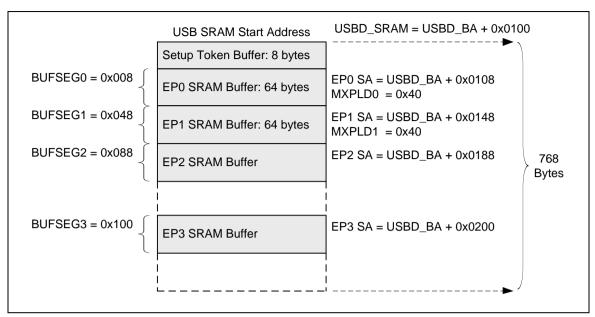

| Figure 6.19-3 Endpoint SRAM Structure                                      | 748 |

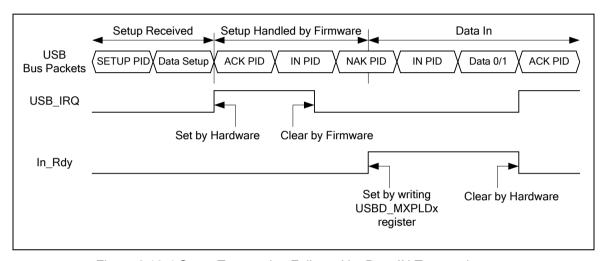

| Figure 6.19-4 Setup Transaction Followed by Data IN Transaction            | 749 |

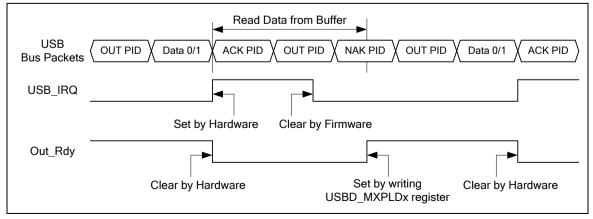

| Figure 6.19-5 Data Out Transfer                                            | 749 |

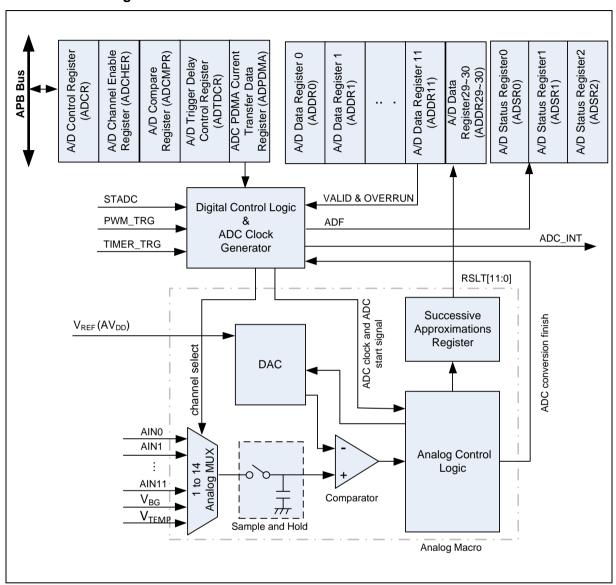

| Figure 6.20-1 ADC Controller Block Diagram                                 | 774 |

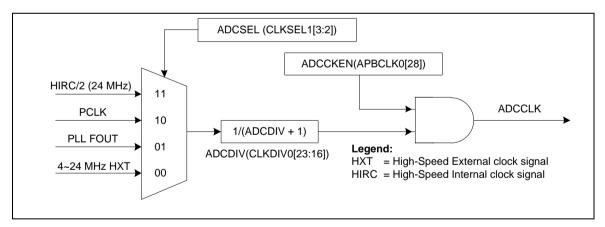

| Figure 6.20-2 ADC Peripheral Clock Control                                 | 775 |

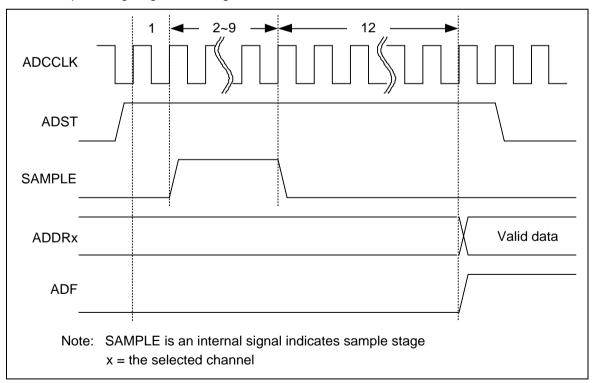

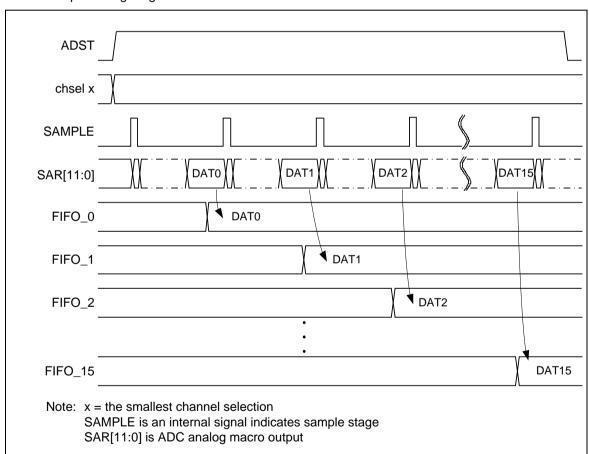

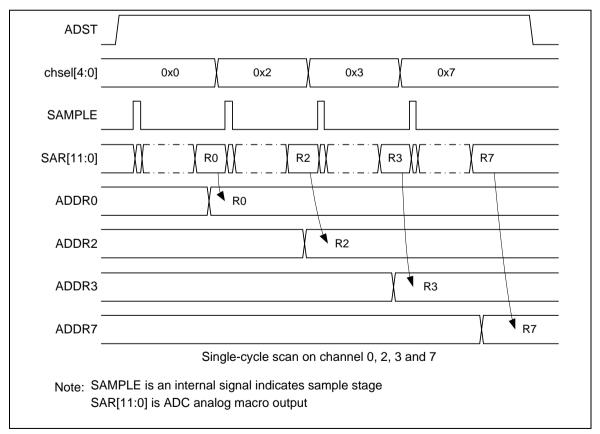

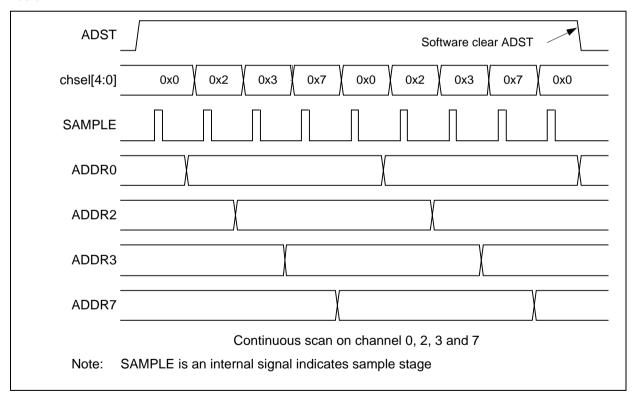

| Figure 6.20-3 Single Mode Conversion Timing Diagram                        | 776 |

| Figure 6.20-4 Burst Mode Conversion Timing Diagram                         | 777 |

| Figure 6.20-5 Single-Cycle Scan Mode on Enabled Channels Timing Diagram    | 778 |

| Figure 6.20-6 Continuous Scan Mode on Enabled Channels Timing Diagram      | 779 |

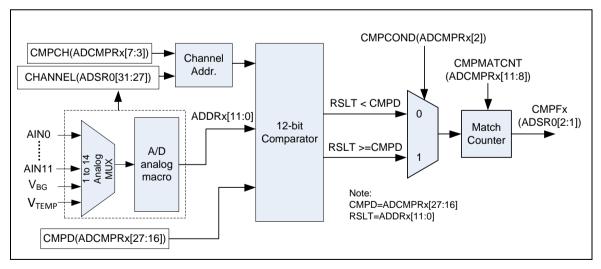

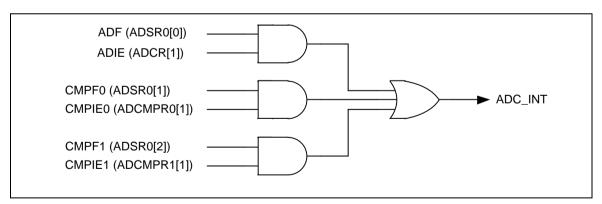

| Figure 6.20-7 A/D Conversion Result Monitor Logic Diagram                  | 781 |

| Figure 6.20-8 A/D Controller Interrupt                                     | 782 |

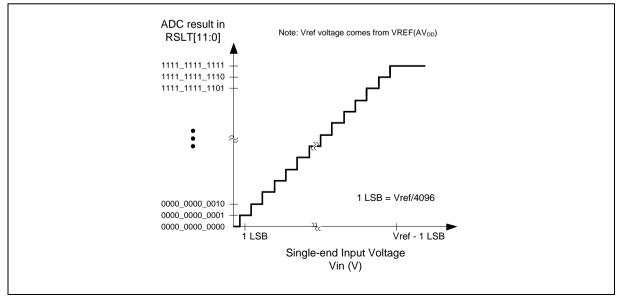

| Figure 6.20-9 Conversion Result Mapping Diagram of ADC Single-end Input    | 785 |

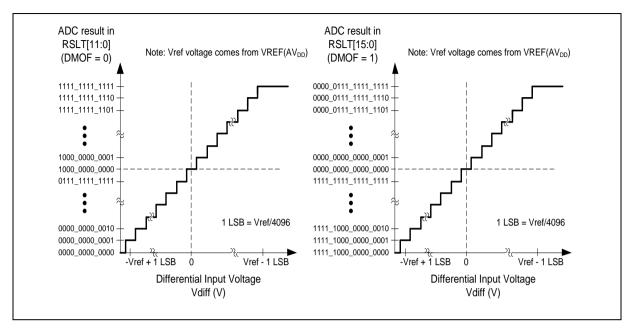

| Figure 6.20-10 Conversion Result Mapping Diagram of ADC Differential Input | 786 |

| List of Tables                                                       |     |

|----------------------------------------------------------------------|-----|

| Table 1.1-1 Key Features Support Table                               | 18  |

| Table 3.1-1 List of Abbreviations                                    | 26  |

| Table 4.1-1 NuMicro® NUC121 USB Series Selection Guide               | 28  |

| Table 4.1-2 NuMicro® NUC125 USB Series Selection Guide               | 28  |

| Table 4.3-1 NUC121 USB Series QFN33 Pin Description                  | 45  |

| Table 4.3-2 NUC121 USB Series LQFP48 Pin Description                 | 50  |

| Table 4.3-3 NUC121 USB Series LQFP64 Pin Description                 | 58  |

| Table 4.3-4 NUC121 USB Series QFN33 Pin Description                  | 62  |

| Table 4.3-5 NUC125 USB Series LQFP48 Pin Description                 | 68  |

| Table 4.3-6 NUC125 USB Series LQFP64 Pin Description                 | 76  |

| Table 4.3-7 NUC121 GPIO Multi-function Table                         | 82  |

| Table 6.2-1 Reset Value of Registers                                 | 89  |

| Table 6.2-2 Power Mode Difference Table                              | 93  |

| Table 6.2-3 Clocks in Power Modes                                    | 94  |

| Table 6.2-4 Condition of Entering Power-down Mode Again              | 95  |

| Table 6.2-5 Address Space Assignments for On-Chip Controllers        | 97  |

| Table 6.2-6 Part Number and PDID Mapping Table                       | 103 |

| Table 6.2-7 Exception Model                                          | 138 |

| Table 6.2-8 Interrupt Number Table                                   | 139 |

| Table 6.2-9 Interrupt Source Identity Detail Description             | 158 |

| Table 6.3-1 Clock Stable Count Value Table                           | 171 |

| Table 6.3-2 Power-down Mode Control Table                            | 180 |

| Table 6.3-3 PLL Output Clock Frequency Setting Description           | 194 |

| Table 6.6-1 Channel Priority Table                                   | 259 |

| Table 6.8-1 BPWM System Clock Source Control Registers Setting Table | 317 |

| Table 6.8-2 BPWM Pulse Generation Event Priority for Up-Counter      | 325 |

| Table 6.8-3 BPWM Pulse Generation Event Priority for Down-Counter    | 326 |

| Table 6.8-4 BPWM Pulse Generation Event Priority for Up-Down-Counter | 326 |

| Table 6.9-1 PWM System Clock Source Control Registers Setting Table  | 372 |

| Table 6.9-2 PWM Pulse Generation Event Priority for Up-Counter       | 382 |

| Table 6.9-3 PWM Pulse Generation Event Priority for Down-Counter     | 382 |

| Table 6.9-4 PWM Pulse Generation Event Priority for Up-Down-Counter  | 382 |

| Table 6.10-1 Watchdog Timer Time-out Interval Period Selection       | 455 |

| Table 6.11-1 WWDT Prescaler Value Selection                          |     |

| Table 6.11-2 CMPDAT Setting Limitation                               | 467 |

| Table 6.12-1 Input Signals for Different Protocols                   | 476 |

| Table 6.12-2 Output Signals for Different Protocols                    | 478 |

|------------------------------------------------------------------------|-----|

| Table 6.12-3 Data Transfer Events and Interrupt Handling               | 486 |

| Table 6.12-4 Protocol-specific Events and Interrupt Handling           | 487 |

| Table 6.13-1 Input Signals for UART Protocols                          | 490 |

| Table 6.13-2 Output Signals for Different Protocols                    | 490 |

| Table 6.13-3 Baud rate Relationship                                    | 494 |

| Table 6.14-1 SPI Communication Signals                                 | 524 |

| Table 6.14-2 Serial Bus Clock Configuration                            | 525 |

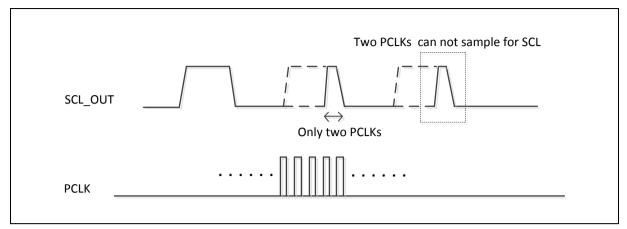

| Table 6.15-1 Relationship between I <sup>2</sup> C Baud Rate and PCLK  | 578 |

| Table 6.16-1 UART Interrupt                                            | 604 |

| Table 6.16-2 UART Interface Controller Pin                             | 604 |

| Table 6.16-3 UART controller Baud Rate Equation Table                  | 605 |

| Table 6.16-4 UART controller Baud Rate Parameter Setting Example Table | 605 |

| Table 6.16-5 UART controller Baud Rate Register Setting Example Table  | 606 |

| Table 6.16-6 Baud Rate Compensation Example Table 1                    | 606 |

| Table 6.16-7 Baud Rate Compensation Example Table 2                    | 607 |

| Table 6.16-8 UART controller Interrupt Source and Flag List            | 613 |

| Table 6.16-9 UART Line Control of Word and Stop Length Setting         | 614 |

| Table 6.16-10 UART Line Control of Parity Bit Setting                  | 615 |

| Table 6.16-11 LIN Header Selection in Master Mode                      | 620 |

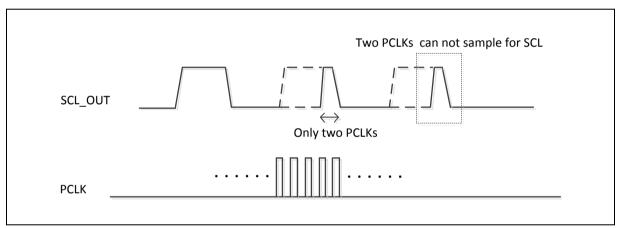

| Table 6.17-1 Relationship between I <sup>2</sup> C Baud Rate and PCLK  | 679 |

| Table 6.17-2 I <sup>2</sup> C Status Code Description                  | 682 |

| Table 6.18-1 SPI/I <sup>2</sup> S Interface Controller Pin             | 704 |

| Table 6.20-1 Differential Input Pairs                                  | 780 |

nuvoton

#### 1 GENERAL DESCRIPTION

The NuMicro® NUC121/125 series is a 32-bit Cortex®-M0 microcontroller with USB 2.0 Full-speed device, a 12-bit ADC and 4 sets of 6-channel BPWM. The NUC121/125 series provides the high 50 MHz operating speed, 8 Kbytes SRAM, 8 USB endpoints and 24 channels of BPWM, which make it powerful in USB communication and data processing. The NUC121/125 series is ideal for industrial control, consumer electronics, and communication system applications such as printers, touch panel, gaming keyboard, gaming joystick, USB audio, PC peripherals, and alarm systems.

The NUC121/125 series runs up to 50 MHz and supports 32-bit multiplier, structure NVIC (Nested Vector Interrupt Control), dual-channel APB and PDMA (Peripheral Direct Memory Access) with CRC function. Besides, the NUC121/125 series is equipped with 32 Kbytes Flash memory, 8 Kbytes SRAM, and 4 Kbytes loader ROM for the ISP. It operates at a wide voltage range of 2.5V  $\sim5.5V$  and temperature range of  $-40^{\circ}\text{C}$   $\sim+105^{\circ}\text{C}$ . It is also equipped with plenty of peripheral devices, such as 8-channel 12-bit ADC, USCI, UART, SPI, I²C, I²S, USB 2.0 FS device, and offers low-voltage reset and Brown-out detection, PWM (Pulse-width Modulation), capture and compare features, four sets of 32-bit timers, Watchdog Timer, and internal RC oscillator. All these peripherals have been incorporated into the NUC121/125 series to reduce component count, board space and system cost.

Additionally, the NUC121/125 series is equipped with ISP (In-System Programming), IAP (In-Application-Programming) and ICP (In-Circuit Programming) functions, which allows the user to update the program under software control through the on-chip connectivity interface, such as SWD, UART and USB. Also all series support SPROM. Moreover, the NUC125 support Voltage Adjustable Interface with individual I/O (1.8V-5.5V) for saving additional cost on adjusting the interface voltage difference of peripheral components.

### 1.1 Key Features Support Table

\* USCI can be set to UART, I2C or SPI

| Product Line | USBD | USCI | UART | I <sup>2</sup> C | SPI/ I <sup>2</sup> S | Timer | BPWM | ADC |

|--------------|------|------|------|------------------|-----------------------|-------|------|-----|

| NUC121       | 1    | 1    | 1    | 2                | 1                     | 4     | 24   | 12  |

| NUC125       | 1    | 1    | 1    | 2                | 1                     | 4     | 23   | 11  |

Table 1.1-1 Key Features Support Table

The NuMicro® NUC121/125 series is suitable for a wide range of applications such as:

- USB Keyboard / Mouse

- Gaming Joystick

- Industrial Automation

- Home Automation

- VR peripheral application

- USB audio

- Alarm system

#### 2 FEATURES

#### 2.1 NuMicro® NUC121/125 Features

#### Core

- ARM® Cortex®-M0 core running up to 50 MHz

- One 24-bit system timer

- Supports Low Power Sleep mode

- Single-cycle 32-bit hardware multiplier

- Supports programmable 4 level priorities of Nested Vectored Interrupt Controller (NVIC)

- Supports programmable mask-able interrupts

- Supports Serial Wire Debug(SWD) with 2 watch-points/4 breakpoints

- Built-in LDO for wide operating voltage ranged from 2.5V to 5.5V

#### Flash Memory

- Supports 32 KB application ROM (APROM)

- Supports 4.5 KB Flash for loader (LDROM)

- Supports 512 bytes Security Protection Rom (SPROM)

- Supports 12 bytes User Configuration block to control system initiation

- Supports Data Flash with configurable memory size

- Supports 512 bytes page erase for all embedded flash

- Supports In-System-Programming (ISP), In-Application-Programming (IAP) update embedded flash memory

- Supports CRC-32 checksum calculation function

- Supports flash all one verification function

- Hardware external read protection of whole flash memory by Security Lock Bit

- Supports 2-wired ICP update through SWD/ICE interface

#### SRAM Memory

- 8 KB embedded SRAM

- Supports byte-, half-word- and word-access

- Supports PDMA mode

#### PDMA (Peripheral DMA)

- Supports 5 independent configurable channels for automatic data transfer between memories and peripherals

- Supports single and burst transfer type

- Supports Normal and Scatter-Gather Transfer modes

- Supports two types of priorities modes: Fixed-priority and Round-robin modes

- Supports byte-, half-word- and word-access

- Supports incrementing mode for the source and destination address for each channel

- Supports time-out function for channel 0 and channel 1

- Supports software and SPI/I2S, UART, USCI, USB, ADC, PWM and TIMER request

#### Clock Control

- Built-in 48 MHz internal high speed RC oscillator (HIRC) for USB device operation (Frequency variation < 2% at -40 $^{\circ}$ C ~ +105 $^{\circ}$ C)

- ◆ Dynamically calibrating the HIRC OSC to 48 MHz ±0.25% from -40°C to 105°C by external 32.768K crystal oscillator (LXT) or internal USB synchronous mode

- Built-in 10 kHz internal low speed RC oscillator for Watchdog Timer and Wake-up operation

- Supports one interface to connect external crystal oscillator for high speed or low speed application

- Built-in 4~24 MHz external high speed crystal oscillator (HXT) for precise timing operation

- Built-in 32.768 kHz external low speed crystal oscillator (LXT) for low-power system operation

- Supports one PLL up to 100 MHz for high performance system operation, sourced from HIRC and HXT

- Supports clock on-the-fly switch

- Supports clock failure detection for high/low speed external crystal oscillator

- Supports auto clock switch once clock failure detected

- Supports exception (NMI) generated once a clock failure detected

- Supports divided clock output

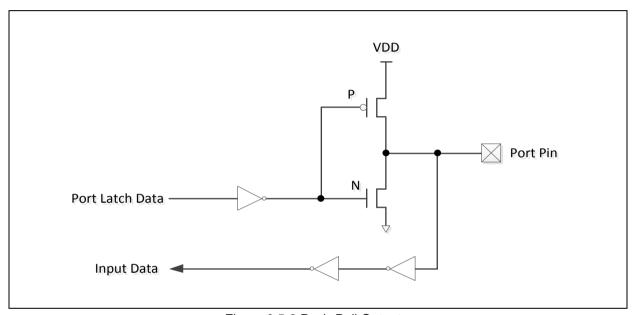

#### GPIO

- Four I/O modes

- TTL/Schmitt trigger input selectable

- I/O pin configured as interrupt source with edge/level trigger setting

- Supports high driver and high sink current I/O (up to 20 mA at 5V)

- Supports software selectable slew rate control

- Supports up to 52/38/22 GPIOs for LQFP64/48 and QFN33 respectively

#### Timer

- Supports 4 sets of 32-bit timers with 24-bit up-timer and one 8-bit pre-scale counter

- Independent clock source for each timer

- Provides one-shot, periodic, toggle and continuous counting operation modes

- Supports event counting function to count the event from external pin

- Supports input capture function to capture or reset counter value

- Supports chip wake-up from Idle/Power-down mode if a timer interrupt signal is generated

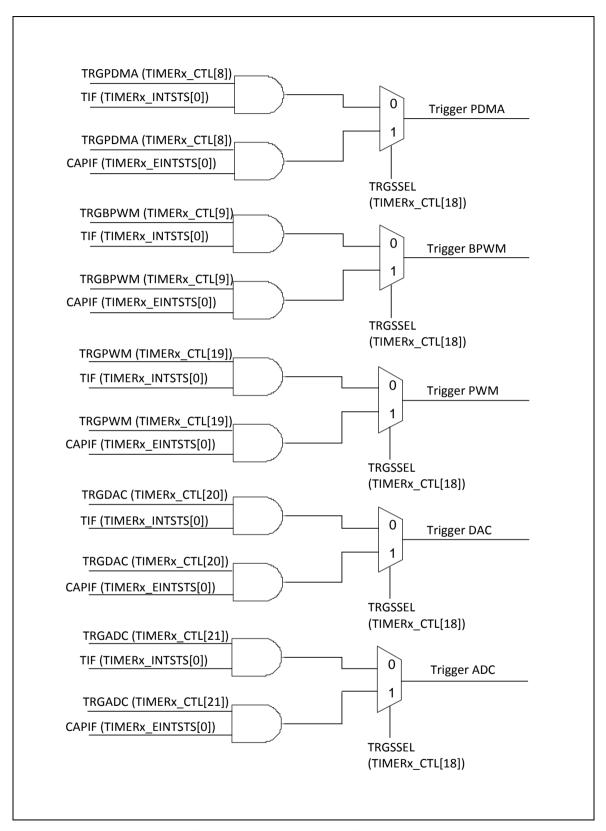

- Support Timer0 ~ Timer3 time-out interrupt signal or capture interrupt signal to trigger BPWM, PWM, ADC and PDMA function

- Supports Inter-Timer trigger mode

#### Watchdog Timer

- Supports multiple clock sources from LIRC (default selection), HCLK/2048 and LXT

- Supports 8 selections of time-out period (1.6ms ~ 26.0sec for LIRC)

- Supports wake up from Power-down or Idle mode

- Supports Interrupt or reset selectable on watchdog time-out

#### Window Watchdog Timer

- Supports multiple clock sources from HCLK/2048 (default selection) and LIRC

- Supports Window set by 6-bit counter with 11-bit prescale

- Supports Interrupt

#### BPWM/Capture

- Supports maximum clock frequency up to 100MHz

- Supports up to two BPWM modules, each module provides one 16-bit counter and 6 output channels

- Supports independent mode for BPWM output/Capture input channel

- Supports 12-bit pre-scalar from 1 to 4096

- Supports 16-bit resolution BPWM counter

- ◆ Up, down and up/down counter operation type

- Supports mask function and tri-state enable for each BPWM pin

- Supports interrupt on the following events:

- ◆ BPWM counter match zero, period value or compared value

- Supports trigger ADC on the following events:

- ◆ BPWM counter match zero, period value or compared value

- Supports capture mode with 16-bit resolution for each BPWM pin

- Supports rising edges, falling edges or both edges capture condition

- Supports input rising edges, falling edges or both edges capture interrupt

- Supports rising edges, falling edges or both edges capture with counter reload option

#### PWM/Capture

- Supports maximum clock frequency up to 100MHz

- Supports up to two PWM modules, each module provides three 16-bit counter and 6 output channels

- Supports independent mode for PWM output/Capture input channel

- Supports complementary mode for 3 complementary paired PWM output channel

- ◆ Dead-time insertion with 12-bit resolution

- ◆ Two compared values during one period

- Supports 12-bit pre-scalar from 1 to 4096

- Supports 16-bit resolution PWM counter

- ◆ Up, down and up/down counter operation type

- Supports mask function and tri-state enable for each PWM pin

- Supports brake function

- Brake source from pin and system safety events (clock failed, Brown-out detection and CPU lockup)

- Noise filter for brake source from pin

- ◆ Edge detect brake source to control brake state until brake interrupt cleared

- ◆ Level detect brake source to auto recover function after brake condition removed

- Supports interrupt on the following events:

- ◆ PWM counter match zero, period value or compared value

- Brake condition happened

- Supports trigger ADC on the following events:

- ◆ PWM counter match zero, period value or compared value

- Supports capture mode with 16-bit resolution for each PWM pin

- Supports rising edges, falling edges or both edges capture condition

- Supports input rising edges, falling edges or both edges capture interrupt

- Supports rising edges, falling edges or both edges capture with counter reload option

- Supports PDMA for capture mode

#### USCI

- UART Mode

- Supports one transmit buffer and two receive buffer for data payload

- ♦ Supports hardware auto flow control function

- Supports programmable baud-rate generator

- ◆ Support 9-Bit Data Transfer (Support 9-Bit RS-485)

- ◆ Baud rate detection possible by built-in capture event of baud rate generator

- ◆ Supports Wake-up function (Data and nCTS Wakeup Only)

- Supports PDMA transfer

- SPI Mode

- Supports Master or Slave mode operation (the maximum frequency -- Master =  $f_{PCLK} / 2$ , Slave =  $f_{PCLK} / 5$ )

- Supports one transmit buffer and two receive buffers for data payload

- ◆ Configurable bit length of a transfer word from 4 to 16-bit

- ♦ Supports MSB first or LSB first transfer sequence

- Supports Word Suspend function

- Supports 3-wire, no slave select signal, bi-direction interface

- ◆ Supports wake-up function by slave select signal in Slave mode

- Supports one data channel half-duplex transfer

- Supports PDMA transfer

- I<sup>2</sup>C Mode

- Full master and slave device capability

- Supports of 7-bit addressing, as well as 10-bit addressing

- Communication in standard mode (100 kBit/s) or in fast mode (up to 400 kBit/s)

- Supports multi-master bus

- ◆ Supports one transmit buffer and two receive buffer for data payload

- Supports 10-bit bus time-out capability

- Supports bus monitor mode.

- ◆ Supports Power down wake-up by data toggle or address match

- Supports setup/hold time programmable

- Supports multiple address recognition (two slave address with mask option)

#### UART

- Supports one set of UART

- Supports maximum clock frequency up to 10 Mbps

- Full-duplex asynchronous communications

- Separates receive and transmit 16/16 bytes entry FIFO for data payloads

- Supports hardware auto-flow control (RX, TX, CTS and RTS)

- Programmable receiver buffer trigger level

- Supports programmable baud rate generator for each channel individually

- Supports 8-bit receiver buffer time-out detection function

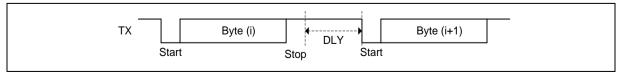

- Programmable transmitting data delay time between the last stop and the next start bit by setting DLY (UART\_TOUT [15:8])

- Supports Auto-Baud Rate measurement and baud rate compensation function

- Supports break error, frame error, parity error and receive/transmit buffer overflow detection function

- Fully programmable serial-interface characteristics

- ◆ Programmable number of data bit, 5-, 6-, 7-, 8- bit character

- Programmable parity bit, even, odd, no parity or stick parity bit generation and detection

- ◆ Programmable stop bit, 1, 1.5, or 2 stop bit generation

- Supports IrDA SIR function mode

- ♦ Supports for 3/16 bit duration for normal mode

- Supports LIN function mode

- ◆ Supports LIN master/slave mode

- ◆ Supports programmable break generation function for transmitter

- Supports break detection function for receiver

- Supports RS-485 mode

- ♦ Supports RS-485 9-bit mode

- Supports hardware or software enables to program nRTS pin to control RS-485 transmission direction

- Supports nCTS, incoming data, Received Data FIFO reached threshold and RS-485

Address Match (AAD mode) wake-up function

- Supports PDMA transfer

#### SPI / I<sup>2</sup>S

- SPI

- Supports one set of SPI controller

- Supports Master or Slave mode operation

- ◆ Configurable bit length of a transfer word from 8 to 32-bit

- ◆ Provides separate 4-/8-level depth transmit and receive FIFO buffers

- Supports MSB first or LSB first transfer sequence

- Supports Byte Reorder function

- Supports PDMA transfer

- I<sup>2</sup>S

- Supports Master or Slave mode operation

- Capable of handling 8-, 16-, 24- and 32-bit word sizes in I<sup>2</sup>S mode

- ◆ Provides separate 4-level depth transmit and receive FIFO buffers in I<sup>2</sup>S mode

- ♦ Supports monaural and stereo audio data in I<sup>2</sup>S mode

- Supports PCM mode A, PCM mode B, I<sup>2</sup>S and MSB justified data format in I<sup>2</sup>S mode

- Supports PDMA transfer

#### $\bullet$ $I^2C$

- Supports up to two sets of I<sup>2</sup>C devices

- Supports speed up to 1Mbps

- Supports Master/Slave mode

- Supports bidirectional data transfer between masters and slaves

- Supports multi-master bus bus (no central master)

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer

- Supports 14-bit time-out counter requesting the I<sup>2</sup>C interrupt if the I<sup>2</sup>C bus hangs up and timer-out counter overflows

- Programmable clocks allow versatile rate control

- Supports multiple address recognition, four slave address with mask option

- Supports two-level buffer function

- Supports setup/hold time programmable

- Supports wake-up function

#### USB 2.0 FS Device Controller

- Compliant with USB 2.0 Full-Speed specification

- Provides 1 interrupt vector with 4 different interrupt events (NEVWK, VBUSDET, USB and BUS)

- Supports Control/Bulk/Interrupt/Isochronous transfer type

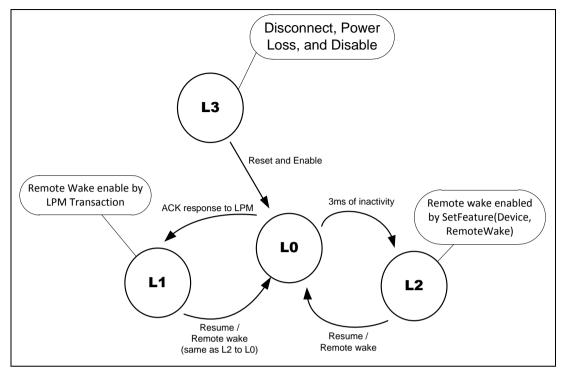

- Supports suspend function when no bus activity existing for 3 ms

- Supports 8 endpoints for configurable Control/Bulk/Interrupt/Isochronous transfer types and maximum 768 bytes buffer size

- Provides remote wake-up capability

- Supports USB 2.0 Link Power Management (LPM)

- Supports Crystal-less function

- Supports PDMA transfer

#### ADC

- Supports 12-bit SAR ADC

- 12-bit resolution and 10-bit accuracy is guaranteed

- Analog input voltage range: 0~ AV<sub>DD</sub>

- Up to 12 single-end analog input channels or 6 differential analog input channels

- Maximum ADC peripheral clock frequency is 16 MHz

- Conversion rate up to 800K SPS at 5V

- Configurable ADC internal sampling time

- Supports single, burst, single-cycle scan, and continuous scan modes on enabled channels

- Supports individual conversion result register with valid and overrun indicators for each channel

- Supports digital comparator to monitor conversion result and user can select whether to generate an interrupt when conversion result matches the compare register setting

- An A/D conversion can be triggered by:

- Software enable

- ◆ External pin (STADC)

- ◆ Timer 0~3 overflow pulse trigger

- PWM triggers with optional start delay period

- Supports 2 internal channels for

- ◆ Band-gap VBG input

- ◆ Temperature sensor input

- Supports PDMA transfer

- Supports 96-bit Unique ID (UID)

- Supports 128-bit Unique Customer ID (UCID)

- One built-in temperature sensor with 1<sup>o</sup>C resolution

- Brown-out detector

- With 4 levels: 4.3 V/ 3.7V/ 2.7V/ 2.2V

- Supports Brown-out Interrupt and Reset option

- Low Voltage Reset

- Threshold voltage levels: 2.0 V

- Operating Temperature: -40°C ~105°C

- Packages

- All Green package (RoHS)

- LQFP 64-pin (7mm x 7mm)

- LQFP 48-pin (7mm x 7mm)

- QFN 33-pin (5mm x 5 mm)

## 3 ABBREVIATIONS

## 3.1 Abbreviations

| Acronym | Description                                     |

|---------|-------------------------------------------------|

| ACMP    | Analog Comparator Controller                    |

| ADC     | Analog-to-Digital Converter                     |

| AES     | Advanced Encryption Standard                    |

| APB     | Advanced Peripheral Bus                         |

| AHB     | Advanced High-Performance Bus                   |

| BOD     | Brown-out Detection                             |

| DAP     | Debug Access Port                               |

| DES     | Data Encryption Standard                        |

| EBI     | External Bus Interface                          |

| EPWM    | Enhanced Pulse Width Modulation                 |

| FIFO    | First In, First Out                             |

| FMC     | Flash Memory Controller                         |

| FPU     | Floating-point Unit                             |

| GPIO    | General-Purpose Input/Output                    |

| HCLK    | The Clock of Advanced High-Performance Bus      |

| HIRC    | 48 MHz Internal High Speed RC Oscillator        |

| HXT     | 4~24 MHz External High Speed Crystal Oscillator |

| IAP     | In Application Programming                      |

| ICP     | In Circuit Programming                          |

| ISP     | In System Programming                           |

| LDO     | Low Dropout Regulator                           |

| LIN     | Local Interconnect Network                      |

| LIRC    | 10 kHz internal low speed RC oscillator (LIRC)  |

| MPU     | Memory Protection Unit                          |

| NVIC    | Nested Vectored Interrupt Controller            |

| PCLK    | The Clock of Advanced Peripheral Bus            |

| PDMA    | Peripheral Direct Memory Access                 |

| PLL     | Phase-Locked Loop                               |

| PWM     | Pulse Width Modulation                          |

| QEI     | Quadrature Encoder Interface                    |

| SD      | Secure Digital                                  |

| SPI     | Serial Peripheral Interface                     |

| SPS  | Samples per Second                          |

|------|---------------------------------------------|

| TDES | Triple Data Encryption Standard             |

| TMR  | Timer Controller                            |

| UART | Universal Asynchronous Receiver/Transmitter |

| UCID | Unique Customer ID                          |

| USB  | Universal Serial Bus                        |

| WDT  | Watchdog Timer                              |

| WWDT | Window Watchdog Timer                       |

Table 3.1-1 List of Abbreviations

#### 4 PARTS INFORMATION LIST AND PIN CONFIGURATION

#### 4.1 NuMicro® NUC121/125 Selection Guide

## 4.1.1 NuMicro® NUC121/125 Naming Rule

Figure 4.1-1 NuMicro® NUC121/125 Selection Code

## 4.1.2 NuMicro® NUC121 USB Series Selection Guide

\* USCI can be set to UART, I2C or SPI

|             |            |           | Σ                      |     |           |       | C    | onnectiv | ity |      |     |              |      |             | _              |         |

|-------------|------------|-----------|------------------------|-----|-----------|-------|------|----------|-----|------|-----|--------------|------|-------------|----------------|---------|

| Part Number | Flash (KB) | SRAM (KB) | ISP Loader ROM<br>(KB) | 0/1 | Timer/PWM | *IDSN | UART | SPI/I²S  | l²C | aasn | WMd | ADC (12-Bit) | PDMA | ICP/ISP/IAP | 1.8V Power Pin | Package |

| NUC121ZC2AE | 32         | 8         | 4.5                    | 22  | 4         | 1     | 1    | 1        | 2   | 1    | 17  | 4-ch         | 5-ch | <b>V</b>    | -              | QFN 33  |

| NUC121LC2AE | 32         | 8         | 4.5                    | 38  | 4         | 1     | 1    | 1        | 2   | 1    | 24  | 10-ch        | 5-ch | <b>√</b>    | -              | LQFP 48 |

| NUC121SC2AE | 32         | 8         | 4.5                    | 52  | 4         | 1     | 1    | 1        | 2   | 1    | 24  | 12-ch        | 5-ch | √           | -              | LQFP 64 |

Table 4.1-1 NuMicro® NUC121 USB Series Selection Guide

## 4.1.3 NuMicro® NUC125 USB Series Selection Guide

\* USCI can be set to UART, I2C or SPI

|             |            |           | 5                      |     |           |        | Connectivity |         |     |      |     |              |      |             | _              |         |

|-------------|------------|-----------|------------------------|-----|-----------|--------|--------------|---------|-----|------|-----|--------------|------|-------------|----------------|---------|

| Part Number | Flash (KB) | SRAM (KB) | ISP Loader ROM<br>(KB) | 0/1 | Timer/PWM | ∗ISCI* | UART         | SPI/I²S | l²C | USBD | PWM | ADC (12-Bit) | PDMA | ICP/ISP/IAP | 1.8V Power Pin | Package |

| NUC125ZC2AE | 32         | 8         | 4.5                    | 22  | 4         | 1      | 1            | 1       | 2   | 1    | 17  | 4-ch         | 5-ch | <b>V</b>    | √              | QFN 33  |

| NUC125LC2AE | 32         | 8         | 4.5                    | 37  | 4         | 1      | 1            | 1       | 2   | 1    | 23  | 9-ch         | 5-ch | <b>√</b>    | <b>√</b>       | LQFP 48 |

| NUC125SC2AE | 32         | 8         | 4.5                    | 51  | 4         | 1      | 1            | 1       | 2   | 1    | 23  | 11-ch        | 5-ch | <b>V</b>    | √              | LQFP 64 |

Table 4.1-2 NuMicro® NUC125 USB Series Selection Guide

## 4.2 Pin Configuration

## 4.2.1 NuMicro® NUC121 QFN 33-Pin Diagram

Figure 4.2-1 NuMicro® NUC121 QFN 33-Pin Diagram

#### NuMicro® NUC121 QFN 33-Pin Function Diagram 4.2.2

Figure 4.2-2 NuMicro® NUC121 QFN 33-Pin Function Diagram

#### NuMicro® NUC121 LQFP 48-Pin Diagram 4.2.3

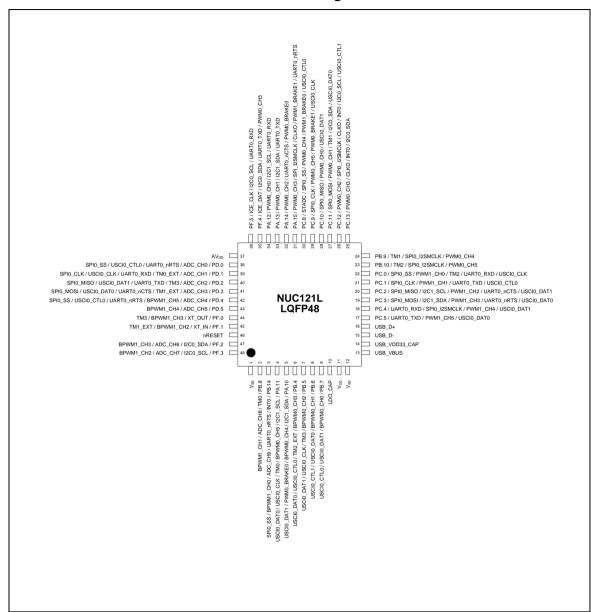

Figure 4.2-3 NuMicro® NUC121 LQFP 48-Pin Diagram

#### NuMicro® NUC121 LQFP 48-Pin Function Diagram 4.2.4

Figure 4.2-4 NuMicro® NUC121 LQFP 48-Pin Function Diagram

#### NuMicro® NUC121 LQFP 64-Pin Diagram 4.2.5

Figure 4.2-5 NuMicro® NUC121 LQFP 64-Pin Diagram

## 4.2.6 NuMicro® NUC121 LQFP 64-Pin Function Diagram

Figure 4.2-6 NuMicro® NUC121 LQFP 64-Pin Function Diagram

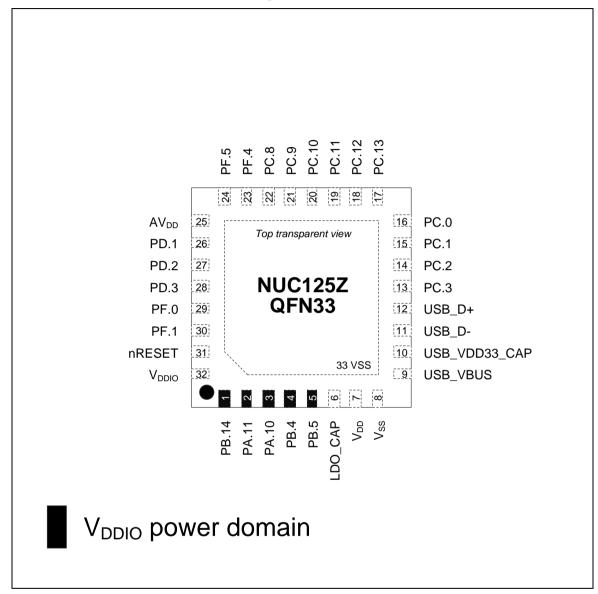

#### NuMicro® NUC125 QFN 33-Pin Diagram 4.2.7

Figure 4.2-7 NuMicro® NUC125 QFN 33-Pin Diagram

#### NuMicro® NUC125 QFN 33-Pin Function Diagram 4.2.8

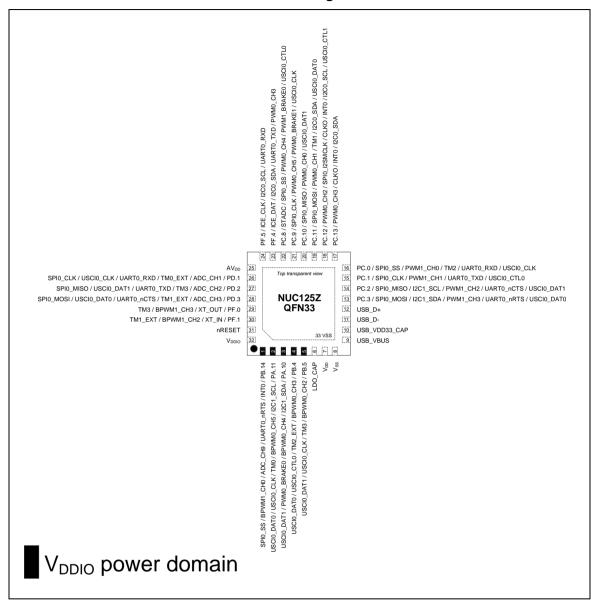

Figure 4.2-8 NuMicro® NUC125 QFN 33-Pin Function Diagram

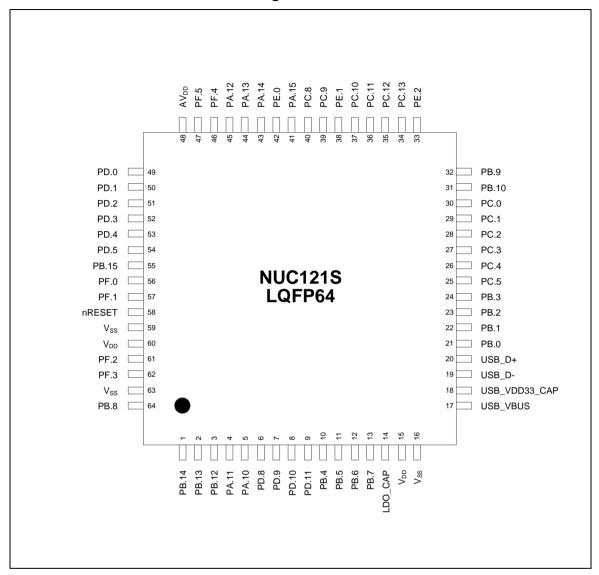

#### NuMicro® NUC125 LQFP 48-Pin Diagram 4.2.9

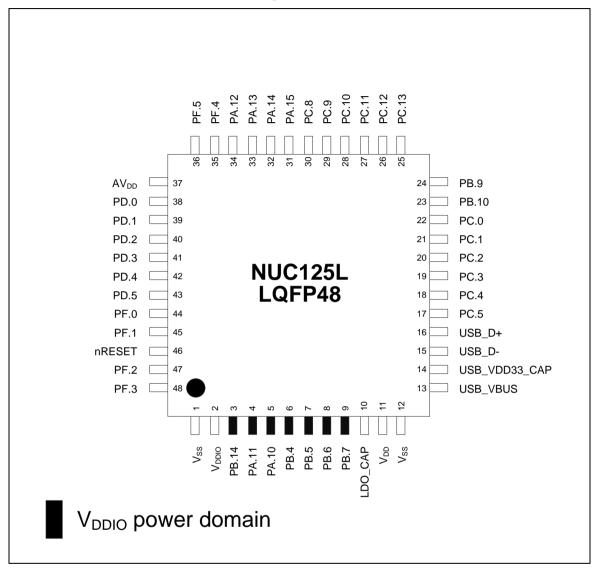

Figure 4.2-9 NuMicro® NUC125 LQFP 48-Pin Diagram

# 4.2.10 NuMicro® NUC125 LQFP 48-Pin Function Diagram

Figure 4.2-10 NuMicro® NUC125 LQFP 48-Pin Function Diagram

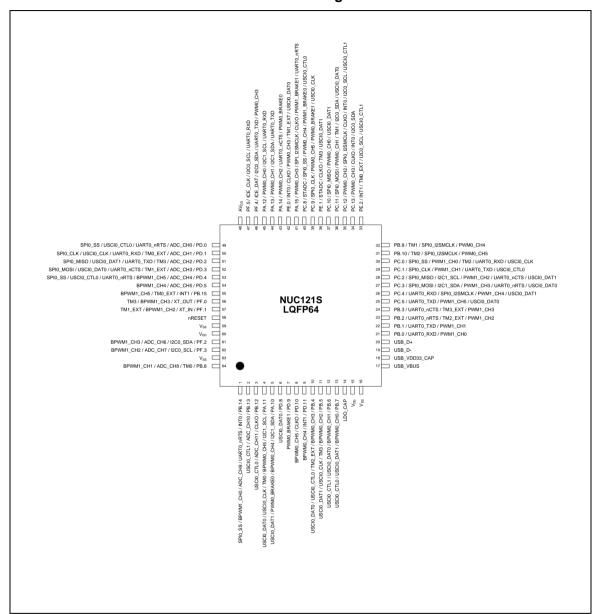

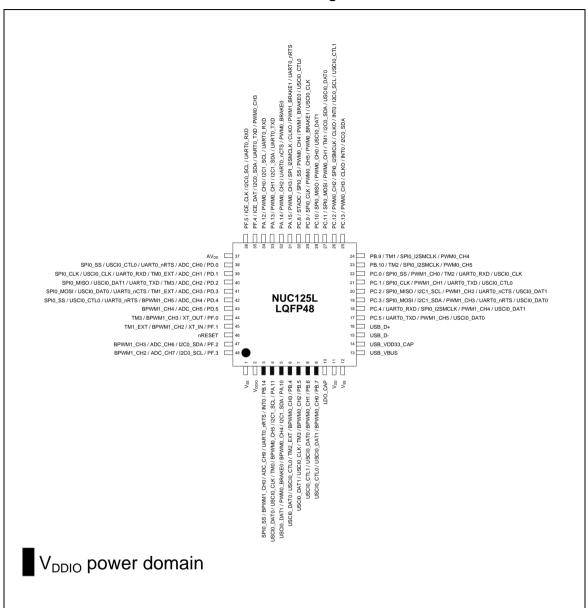

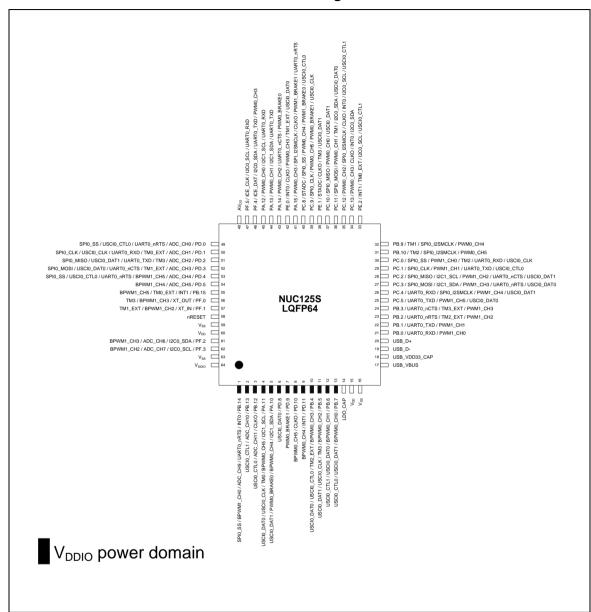

### NuMicro® NUC125 LQFP 64-Pin Diagram

nuvoton

Figure 4.2-11 NuMicro® NUC125 LQFP 64-Pin Diagram

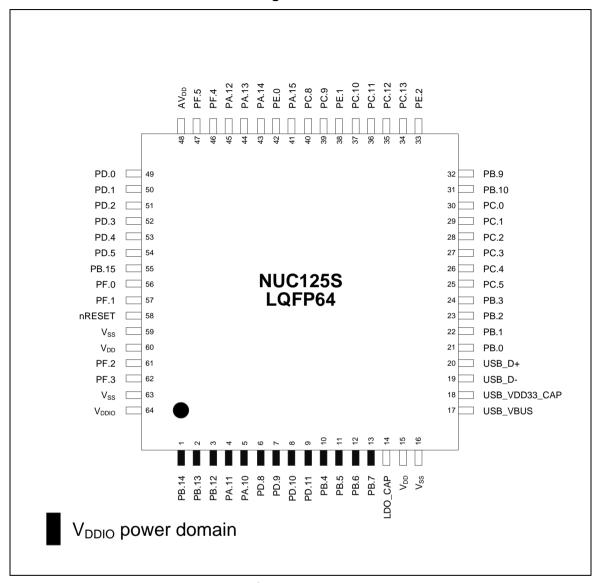

# 4.2.12 NuMicro® NUC125 LQFP 64-Pin Function Diagram

Figure 4.2-12 NuMicro® NUC125 LQFP 64-Pin Function Diagram

### 4.3 Pin Description

#### 4.3.1 NUC121 USB Series QFN33 Pin Description

MFP\* = Multi-function pin. (Refer to section SYS\_GPx\_MFPL and SYS\_GPx\_MFPH)

PA.10 MFP5 means SYS\_GPA\_MFPH[11:8]=0x5.

PC.0 MFP0 means SYS\_GPC\_MFPL[3:0]=0x0.

| Pin No. | Pin Name    | Туре | MFP* | Description                                |

|---------|-------------|------|------|--------------------------------------------|

|         | PB.14       | I/O  | MFP0 | General purpose digital I/O pin.           |

|         | INT0        | I    | MFP1 | External interrupt0 input pin.             |

| 4       | UART0_nRTS  | 0    | MFP2 | Request to Send output pin for UART0.      |

| 1       | ADC_CH9     | Α    | MFP3 | ADC channel 9 analog input.                |

|         | BPWM1_CH0   | I/O  | MFP4 | BPWM1 channel 0 output/capture input.      |

|         | SPI0_SS     | I/O  | MFP7 | SPI0 slave select pin.                     |

|         | PA.11       | I/O  | MFP0 | General purpose digital I/O pin.           |

|         | I2C1_SCL    | I/O  | MFP1 | I <sup>2</sup> C1 clock pin.               |

| 2       | BPWM0_CH5   | I/O  | MFP4 | BPWM0 channel 5 output/capture input.      |

| 2       | ТМО         | I/O  | MFP5 | Timer0event counter input / toggle output  |

|         | USCI0_CLK   | I/O  | MFP6 | USCI0 clock pin.                           |

|         | USCI0_DAT0  | I/O  | MFP7 | USCI0 DAT0 pin.                            |

|         | PA.10       | I/O  | MFP0 | General purpose digital I/O pin.           |

|         | I2C1_SDA    | I/O  | MFP1 | I <sup>2</sup> C1 data input/output pin.   |

| 3       | BPWM0_CH4   | I/O  | MFP4 | BPWM0 channel 4 output/capture input.      |

|         | PWM0_BRAKE0 | I    | MFP5 | Brake input pin 0 of PWM0.                 |

|         | USCI0_DAT1  | I/O  | MFP6 | USCI0 DAT1 pin.                            |

|         | PB.4        | I/O  | MFP0 | General purpose digital I/O pin.           |

|         | BPWM0_CH3   | I/O  | MFP4 | BPWM0 channel 3 output/capture input.      |

| 4       | TM2_EXT     | I    | MFP5 | Timer2 external counter input              |

|         | USCI0_CTL0  | I/O  | MFP6 | USCIO CTLO pin.                            |

|         | USCI0_DAT0  | I/O  | MFP7 | USCI0 DAT0 pin.                            |

|         | PB.5        | I/O  | MFP0 | General purpose digital I/O pin.           |

|         | BPWM0_CH2   | I/O  | MFP4 | BPWM0 channel 2 output/capture input.      |

| 5       | ТМЗ         | I/O  | MFP5 | Timer3 event counter input / toggle output |

|         | USCI0_CLK   | I/O  | MFP6 | USCI0 clock pin.                           |

|         | USCI0_DAT1  | I/O  | MFP7 | USCI0 DAT1 pin.                            |

| 6       | LDO_CAP     | Α    | MFP0 | LDO output pin.                            |

| Pin No. | Pin Name        | Туре | MFP* | Description                                                                      |

|---------|-----------------|------|------|----------------------------------------------------------------------------------|

| 7       | $V_{DD}$        | А    | MFP0 | Power supply for I/O ports and LDO source for internal PLL and digital function. |

| 8       | V <sub>SS</sub> | Α    | MFP0 | Ground pin for digital circuit.                                                  |

| 9       | USB_VBUS        | Α    | MFP0 | Power supply from USB host or HUB.                                               |

| 10      | USB_VDD33_CAP   | Α    | MFP0 | Internal power regulator output 3.3V decoupling pin.                             |

| 11      | USB_D-          | I    | MFP0 | USB differential signal D                                                        |

| 12      | USB_D+          | I    | MFP0 | USB differential signal D+.                                                      |

|         | PC.3            | I/O  | MFP0 | General purpose digital I/O pin.                                                 |

|         | SPI0_MOSI       | I/O  | MFP1 | SPI0 MOSI (Master Out, Slave In) pin.                                            |