# 10-Bit High Speed Multiplying D/A Converter (Universal Digital Logic Interface)

DAC<sub>10</sub>

**FEATURES**

Fast Settling: 85 ns

Low Full-Scale Drift: 10 ppm/°C

Nonlinearity to 0.05% Max Over Temperature Range Complementary Current Outputs: 0 mA to 4 mA Wide Range Multiplying Capability: 1 MHz Bandwidth Wide Power Supply Range: +5, -7.5 Min to  $\pm 18$  V Max Direct Interface to TTL, CMOS, ECL, PMOS, NMOS

Availability in Die Form

#### **GENERAL DESCRIPTION**

The DAC10 series of 10-bit monolithic multiplying digital-toanalog converters provide high speed performance and full-scale accuracy.

Advanced circuit design achieves 85 ns settling times with very low "glitch" energy and low power consumption. Direct interface to all popular logic families with full noise immunity is provided by the high swing, adjustable threshold logic inputs.

All DAC10 series models guarantee full 10-bit monotonicity, and nonlinearities as tight as +0.05% over the entire operating temperature range are available. Device performance is essentially unchanged over the  $\pm 18$  V power supply range, with 85 mW power consumption attainable at lower supplies.

A highly stable, unique trim method is used, which selectively shorts Zener diodes, to provide 1/2 LSB full-scale accuracy without the need for laser trimming.

Single-chip reliability, coupled with low cost and outstanding flexibility, make the DAC10 device an ideal building block for A/D converters, Data Acquisition systems, CRT displays, programmable test equipment and other applications where low power consumption, input/output versatility and long-term stability are required.

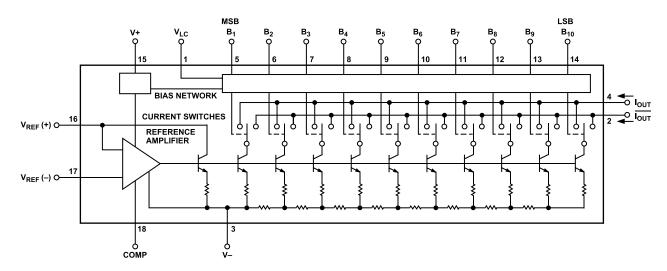

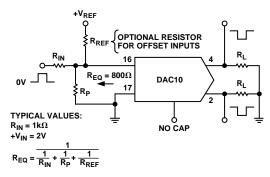

#### SIMPLIFIED SCHEMATIC

### DAC10-SPECIFICATIONS

##

| Parameter                    | Symbol                                       | Conditions                                                                                                       | I<br>Min | DAC10F<br>Typ            | Max                 | Min I | AC10G<br>Typ             | Max                 | Units                |

|------------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------|--------------------------|---------------------|-------|--------------------------|---------------------|----------------------|

| MONOTONICITY                 |                                              |                                                                                                                  | 10       |                          |                     | 10    |                          |                     | Bits                 |

| NONLINEARITY                 | NL                                           |                                                                                                                  |          | 0.3                      | 0.5                 |       | 0.6                      | 1                   | LSB                  |

| DIFFERENTIAL<br>NONLINEARITY | DNL                                          |                                                                                                                  |          | 0.3                      | 1                   |       | 0.7                      |                     | LSB                  |

| SETTLING TIME                | t <sub>S</sub>                               | All Bits Switched ON or OFF<br>Settle to 0.05% of FS (See Note)                                                  |          | 85                       | 135                 |       | 85                       | 150                 | ns                   |

| OUTPUT CAPACITANCE           | Co                                           |                                                                                                                  |          | 18                       |                     |       | 18                       |                     | pF                   |

| PROPAGATION DELAY            | t <sub>PLH</sub><br>t <sub>PHL</sub>         | All Bits Switched $R_L = 5 \text{ k}\Omega$<br>$R_L = 0 \text{ k}\Omega$                                         |          | 50<br>50                 |                     |       | 50<br>50                 |                     | ns<br>ns             |

| OUTPUT VOLTAGE<br>COMPLIANCE | V <sub>oc</sub>                              | Full-Scale Current Change<br><1 LSB                                                                              |          | -5.5<br>+10              |                     |       | -5.5<br>+10              |                     | V<br>V               |

| GAIN TEMPCO                  | $TCI_{FS}$                                   | (See Note)                                                                                                       |          | ±10                      | ±25                 |       | ±10                      | ±50                 | ppm/°C               |

| FULL-SCALE SYMMETRY          | I <sub>FSS</sub>                             | $I_{FR}$ – $\overline{I_{FR}}$                                                                                   |          | 0.1                      | 4                   |       | 0.1                      | 4                   | μΑ                   |

| ZERO-SCALE CURRENT           | I <sub>ZS</sub>                              |                                                                                                                  |          | 0.01                     | 0.5                 |       | 0.01                     | 0.5                 | μΑ                   |

| FULL-SCALE CURRENT           | $I_{FR}$                                     | (See Note)                                                                                                       | 3.960    | 3.996                    | 4.032               | 3.920 | 3.996                    | 4.072               | mA                   |

| REFERENCE INPUT<br>SLEW RATE | DI/dt                                        |                                                                                                                  |          | 6                        |                     |       | 6                        |                     | mA/μs                |

| REFERENCE BIAS<br>CURRENT    | $I_{\mathrm{B}}$                             |                                                                                                                  |          | -1                       | -3                  |       | -1                       | -3                  | μА                   |

| POWER SUPPLY<br>SENSITIVITY  | PPS/ <sub>FS</sub> +<br>PPS/ <sub>FS</sub> - | $4.5 \text{ V} \le \text{V} + \le -18 \text{ V}$<br>$-18 \text{ V} \le \text{V} - \le -10 \text{ V}$             |          | 0.001<br>0.0012          | 0.01<br>0.01        |       | 0.001<br>0.0012          | 0.01<br>0.01        |                      |

| POWER SUPPLY CURRENT         | I+<br>I-<br>I+<br>I-                         | $V_S = \pm 15 \text{ V}; I_{REF} = 2 \text{ mA}$<br>$V_S = +5 \text{ V}; -7.5 \text{ V}; I_{REF} = 1 \text{ mA}$ |          | 2.3<br>-9<br>1.8<br>-5.9 | 4<br>-15<br>4<br>-9 |       | 2.3<br>-9<br>1.8<br>-5.9 | 4<br>-15<br>4<br>-9 | mA<br>mA<br>mA<br>mA |

| POWER DISSIPATION            | $P_{\mathrm{D}}$ $P_{\mathrm{D}}$            | $V_S = \pm 15 \text{ V}; I_{REF} = 2 \text{ mA}$<br>$V_S = +5 \text{ V}; -7.5 \text{ V}; I_{REF} = 1 \text{ mA}$ |          | 231<br>85                | 285<br>88           |       | 231<br>85                | 285<br>88           | mW<br>mW             |

| LOGIC INPUT LEVELS           | $egin{array}{c} V_{IL} \ V_{IH} \end{array}$ | $V_{LC} = 0$ $V_{LC} = 0$                                                                                        | 2        |                          | 0.8                 | 2     |                          | 0.8                 | V<br>V               |

| LOGIC INPUT CURRENTS         | I <sub>IL</sub><br>I <sub>IH</sub>           | $V_{LC} = 0; V_{IN} = 0.8 \text{ V}$<br>$V_{IN} = 2.0 \text{ V}$                                                 | -10      | -5<br>0.001              | 10                  | -10   | -5<br>0.001              | 10                  | μA<br>μA             |

## **ELECTRICAL CHARACTERISTICS** (@ $V_S = \pm 15$ V; $I_{REF} = 2$ mA; $T_A = +25$ °C, unless otherwise noted. Output characteristics apply to both $I_{OUT}$ and $\overline{I_{OUT}}$ .)

| _                            |                  |                                                                      | _     | AC10F  |       | _     | AC10G  |       |       |

|------------------------------|------------------|----------------------------------------------------------------------|-------|--------|-------|-------|--------|-------|-------|

| Parameter                    | Symbol           | Conditions                                                           | Min   | Тур    | Max   | Min   | Тур    | Max   | Units |

| MONOTONICITY                 |                  |                                                                      | 10    |        |       | 10    |        |       | Bits  |

| NONLINEARITY                 | NL               |                                                                      |       | 0.3    | 0.5   |       | 0.6    | 1     | LSB   |

| DIFFERENTIAL<br>NONLINEARITY | DNL              |                                                                      |       | 0.3    | 1     |       | 0.7    |       | LSB   |

| OUTPUT VOLTAGE<br>COMPLIANCE | V <sub>oc</sub>  | Full-Scale Current Change, <1 LSB                                    | -5    | -6/+18 | +10   | -5    | -6/+15 | +10   | v     |

| FULL-SCALE CURRENT           | $I_{FS}$         | $V_{REF} = 10.000 \text{ V},$<br>$R14 = R15 = 5.000 \text{ k}\Omega$ | 3.978 | 3.996  | 4.014 | 3.956 | 3.996  | 4.036 | mA    |

| FULL-SCALE SYMMETRY          | I <sub>FSS</sub> | $I_{FR}$ – $\overline{I_{FR}}$                                       |       | 0.1    | 4     |       | 0.1    | 0.4   | μΑ    |

| ZERO-SCALE CURRENT           | I <sub>ZS</sub>  |                                                                      |       | 0.01   | 0.5   |       | 0.01   | 0.5   | μА    |

NOTE: Guaranteed by design.

-2- REV. D

### **WAFER TEST LIMITS** (@ $V_S = \pm 15$ V, $I_{REF} = 2$ mA, $T_A = +25$ °C, unless otherwise noted. Output characteristics refer to both $I_{OUT}$ and $I_{OUT}$ ).

| Parameter                 | Symbol          | Conditions                              | DAC10N<br>Limit | Units          |

|---------------------------|-----------------|-----------------------------------------|-----------------|----------------|

| RESOLUTION                |                 |                                         | 10              | Bits min       |

| MONOTONICITY              |                 |                                         | 10              | Bits min       |

| NONLINEARITY              | NL              |                                         | ±0.5            | LSB max        |

| OUTPUT VOLTAGE COMPLIANCE | V <sub>OC</sub> | True 1 LSB                              | +10<br>-5       | V max<br>V min |

| OUTPUT CURRENT RANGE      |                 | I <sub>FS</sub> ±3.996 mA               | ±18             | μA max         |

| ZERO-SCALE CURRENT        | $I_{ZS}$        | All Bits OFF                            | 0.5             | μA max         |

| LOGIC INPUT "1"           | V <sub>IH</sub> | I <sub>IN</sub> = 100 nA                | 2               | V min          |

| LOGIC INPUT "0"           | V <sub>IL</sub> | $V_{LC}$ @ Ground $I_{IN} = -100 \mu A$ | 0.8             | V max          |

| POSITIVE SUPPLY CURRENT   | I+              | V+ = 15 V                               | 4               | mA max         |

| NEGATIVE SUPPLY CURRENT   | I–              | V+ = -15 V                              | -15             | mA max         |

NOTE: Electrical tests are performed at wafer probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after packaging is not guaranteed for standard produce dice.

### TYPICAL ELECTRICAL CHARACTERISTICS (@ $V_S = \pm 15$ V, $I_{REF} = 2$ mA, unless otherwise noted. Output characteristics refer to both $I_{OUT}$ and $\overline{I_{OUT}}$ ).

| Parameter                            | Symbol | Conditions                                            | DAC10F<br>Typ | Units     |

|--------------------------------------|--------|-------------------------------------------------------|---------------|-----------|

| SETTLING TIME                        | $t_S$  | To $\pm 1/2$ LSB When Output Is Switched from 0 to FS | 85            | ns        |

| GAIN TEMPERATURE<br>COEFFICIENT (TC) |        | V <sub>REF</sub> Tempco Excluded                      | ±10           | ppm FS/°C |

| OUTPUT CAPACITANCE                   |        |                                                       | 18            | pF        |

| OUTPUT RESISTANCE                    |        |                                                       | 10            | ΜΩ        |

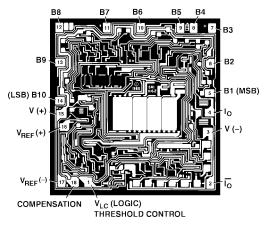

#### DICE CHARACTERISTICS

DIE SIZE 0.091  $\times$  0.087 inch, 7,917 sq. mils (2.311  $\times$  2.210 mm, 5.107 sq. mm)

REV. D -3-

### DAC10

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Operating Temperature                                                    |

|--------------------------------------------------------------------------|

| DAC10FX, GX, GS, GP                                                      |

| Junction Temperature $(T_J)$ 65°C to +150°C                              |

| Storage Temperature65°C to +150°C                                        |

| Lead Temperature (Soldering, 60 sec) +300°C                              |

| V+ Supply to V- Supply                                                   |

| Logic Inputs V- to V- plus 36 V                                          |

| $V_{LC}$ $V-$ to $V+$                                                    |

| Analog Current Outputs +18 V to -18 V                                    |

| Reference Inputs ( $V_{16}$ to $V_{17}$ ) $V-$ to $V+$                   |

| Reference Input Differential Voltage ( $V_{16}$ to $V_{17}$ ) $\pm 18~V$ |

| Reference Input Current (I <sub>16</sub> ) 2.5 mA                        |

| Package Type             | $\theta_{\mathrm{JA}}^{2}$ | $\theta_{ m JC}$ | Units |

|--------------------------|----------------------------|------------------|-------|

| 18-Lead Hermetic DIP (X) | 48                         | 15               | °C/W  |

| 18-Lead SOIC (S)         | 89                         | 28               | °C/W  |

| 18-Lead Plastic DIP (P)  | 74                         | 33               | °C/W  |

#### NOTES

#### **ORDERING GUIDE**

| Model   | INL<br>(LSB) | Temperature<br>Range | Package<br>Description | Package<br>Options |

|---------|--------------|----------------------|------------------------|--------------------|

| DAC10FX | 0.5          | 0°C to +70°C         | Cerdip                 | Q-18               |

| DAC10GX | 1            | 0°C to +70°C         | Cerdip                 | Q-18               |

| DAC10GS | 1            | 0°C to +70°C         | SOIC                   | R-18               |

| DAC10GP | 1            | 0°C to +70°C         | Plastic DIP            | N-18               |

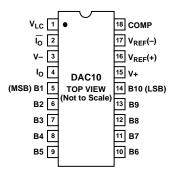

# PIN CONNECTIONS 18-Lead Hermetic DIP 18-Lead Plastic DIP 18-Lead SOIC

<sup>&</sup>lt;sup>1</sup>Absolute maximum ratings apply to both DICE and packaged parts, unless otherwise noted.

$<sup>^2\</sup>theta_{JA}$  is specified for worst case mounting conditions, i.e.,  $\theta_{JA}$  is specified for device in socket for Cerdip packages.

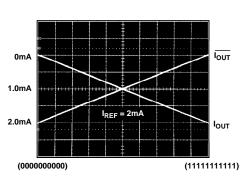

### **Typical Performance Characteristics—DAC10**

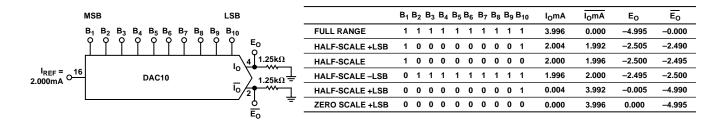

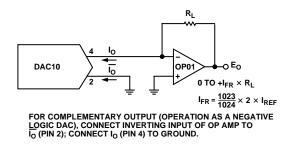

Figure 1. True and Complementary Output Operations

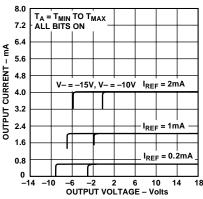

Figure 2. Output Current vs. Output Voltage (Output Voltage Compliance)

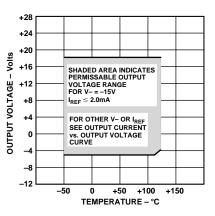

Figure 3. Output Voltage Compliance vs. Temperature

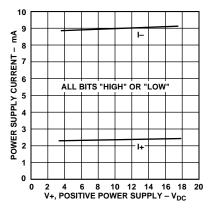

Figure 4. Power Supply Current vs. V+

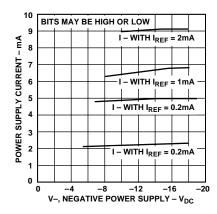

Figure 5. Power Supply Current vs. V-

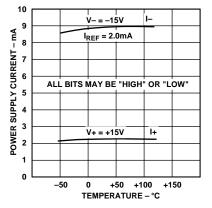

Figure 6. Power Supply Current vs. Temperature

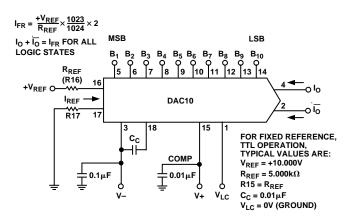

#### **BASIC CONNECTIONS**

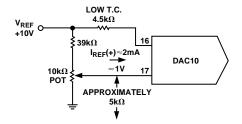

Figure 7. Basic Positive Reference Operation

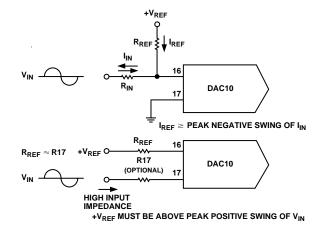

Figure 8. Accommodating Bipolar References

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection.

REV. D \_5\_

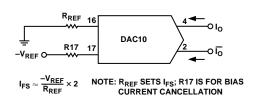

Figure 9. Basic Negative Reference Operation

Figure 10. Recommended Full-Scale Adjustment Circuit

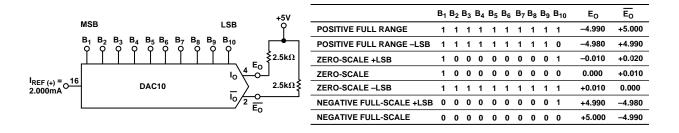

Figure 11. Basic Unipolar Negative Operation

Figure 12. Basic Bipolar Output Operation

Figure 13. Offset Binary Operation

-6- REV. D

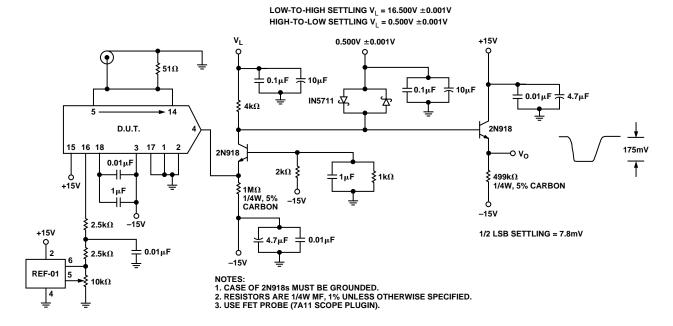

Figure 14. Settling Time Measurement

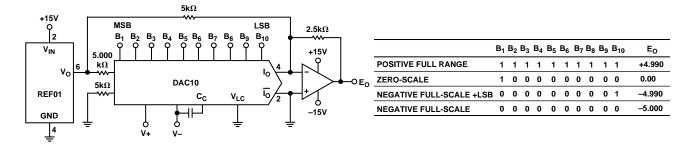

Figure 15. Positive Low Impedance Output Operation

FOR COMPLEMENTARY OUTPUT (OPERATION AS A NEGATIVE LOGIC DAC), CONNECT NOINVERTING INPUT OF OP AMP TO  $I_0$  PIN 2); CONNECT  $I_0$  (PIN 4) TO GROUND.

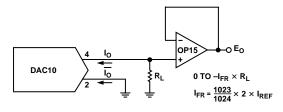

Figure 16. Negative Low Impedance Output Operation

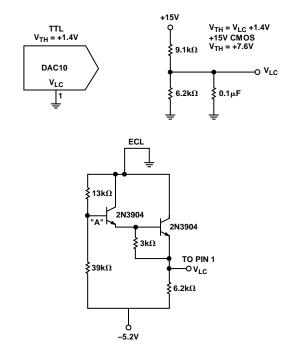

Figure 17. Interfacing with Various Logic Families

REV. D -7-

#### DAC10

#### **APPLICATIONS**

Figure 18. Pulsed Reference Operation

#### Reference Amplifier Setup

The DAC10 is a multiplying D/A converter in which the output current is the product of a digital number and the input reference current. The reference current may be fixed or may vary from nearly zero to 2 mA. The full-scale output current is a linear function of the reference current and is given by:

$$I_{FR} = \frac{1023}{1024} \times 2 \times I_{REF}$$

where  $I_{REF}$  equals current flowing into Pin 16.

In positive reference applications, an external positive reference voltage forces current through R16 into the  $V_{REF}$  (+) terminal (Pin 16) of the reference amplifier. Alternatively, a negative reference may be applied to  $V_{REF}$  (–) at Pin 17; reference current flows from ground through R16 into V(+) as in the positive reference case. This negative reference connection has the advantage of a very high impedance presented at Pin 17. R17 (nominally equal to R16) is used to cancel bias current errors; R17 may be eliminated with only a minor increase in error.

Bipolar references may be accommodated by offsetting  $V_{REF}$  or Pin 17. The negative common-mode range of the reference amplifier is given by:  $V_{CM^-} = V_-$  plus  $(I_{REF} \times 2 \text{ k}\Omega)$  plus 2 V. The positive common-mode range is V+ less 1.8 V.

When a dc reference is used, a reference bypass capacitor is recommended. A 5 V TTL logic supply is not recommended as a reference. If a regulated power supply is used as a reference, R16 should be split into two resistors with the junction bypassed to ground with a 0.1  $\mu F$  capacitor.

For most applications, the tight relationship between  $I_{REF}$  and  $I_{FS}$  will eliminate the need for trimming  $I_{REF}$ . If required, full-scale trimming may be accomplished by adjusting the value of R16, or by using a potentiometer for R16. An improved method of full-scale trimming that eliminates potentiometer TC effect is shown in the Recommended Full-Scale Adjustment circuit.

The reference amplifier must be compensated by using a capacitor from Pin 18 to V–. For fixed reference operation, a 0.01  $\mu F$  capacitor is recommended. For variable reference applications, see section entitled Reference Amplifier Compensation for Multiplying Applications.

#### **Multiplying Operation**

The DAC10 provides excellent multiplying performance with an extremely linear relationship between  $I_{FS}$  and  $I_{REF}$  over a range of 4 mA to 4  $\mu$ A. Monotonic operation is maintained over a typical range of  $I_{REF}$  from 100  $\mu$ A to 2 mA.

Reference Amplifier Compensation for Multiplying Applications AC reference applications will require the reference amplifier to be compensated using a capacitor from Pin 18 to V–. The value of this capacitor depends on the impedance presented to Pin 16 for R16 values of 1.0 k $\Omega$ , 2.5 k $\Omega$  and 5.0 k $\Omega$ , minimum values of  $C_C$  are 15 pF, 37 pF and 75 pF. Larger values of R16 require proportionately increased values of  $C_C$  for proper phase margin.

For fastest response to a pulse, low values of R16 enabling small  $C_{\rm C}$  values should be used. If Pin 16 is driven by a high impedance such as a transistor current source, none of the above values will suffice and the amplifier must be heavily compensated, which will decrease overall bandwidth and slew rate. For R16 = 1 k $\Omega$  and  $C_{\rm C}$  = 15 pF, the reference amplifier slews at 4 mA/ $\mu$ s enabling a transition from  $I_{\rm REF}$  = 0 to  $I_{\rm REF}$  = 2 mA in 500 ns.

Operation with pulse inputs to the reference amplifier may be accommodated by an alternate compensation scheme. This technique provides lowest full-scale transition times. An internal clamp allows quick recovery of the reference amplifier from a cutoff ( $I_{REF}=0$ ) condition. Full-scale transition (0 mA to 2 mA) occurs in 120 ns when the equivalent impedance at Pin 16 is 200  $\Omega$  and  $C_C=0$ . This yields a reference slew rate of 16 mA/  $\mu s$ , which is relatively independent of  $R_{IN}$  and  $V_{IN}$  values.

#### **LOGIC INPUTS**

The DAC10 design incorporates a unique logic input circuit that enables direct interface to all popular logic families and provides maximum noise immunity. This feature is made possible by the large input swing capability, 2 µA logic input current and completely adjustable logic threshold voltage. For  $V_{-} = -15 \text{ V}$ , the logic inputs may swing between -5 and +18 V. This enables direct interface with +15 V CMOS logic, even when the DAC10 is powered from a +5 V supply. Minimum input logic swing and minimum logic threshold voltage are given by: V- plus ( $l_{REF} \times$  $2 \text{ k}\Omega$ ) plus 3 V. The logic threshold may be adjusted over a wide range by placing an appropriate voltage at the logic threshold control Pin (Pin 1, V<sub>LC</sub>). The appropriate graph shows the relationship between V<sub>LC</sub> and V<sub>TH</sub> over the temperature range, with V<sub>TH</sub> nominally 1.4 V above V<sub>LC</sub>. For TTL interface, simply ground Pin 1. When interfacing ECL, an  $I_{REF} = 1$  mA is recommended. For interfacing other logic families, see Figure 17. For general setup of the logic control circuit, it should be noted that Pin 1 will sink 1.1 mA typical; external circuitry should be designed to accommodate this current.

Fastest settling times are obtained when Pin 1 sees a low impedance. If Pin 1 is connected to a 1 k $\Omega$  divider, for example, it should be bypassed to ground by a 0.01  $\mu F$  capacitor.

–8– REV. D

DAC<sub>10</sub>

#### ANALOG OUTPUT CURRENTS

Both true and complemented output sink currents are provided where  $I_O + \overline{I_O} = I_{FS}$ . Current appears at the "true" output when a "1" is applied to each logic input. As the binary count increases, the sink current at Pin 4 increases proportionally, in the fashion of a "positive logic" D/A converter. When a "0" is applied to any input bit, that current is turned off at Pin 4 and turned on at Pin 2. A decreasing logic count increases  $\overline{I_O}$  as in a negative or inverted logic D/A converter. Both outputs may be used simultaneously. If one of the outputs is not required, it must still be connected to ground or to a point capable of sourcing  $I_{FS}$ . DO NOT LEAVE AN UNUSED OUTPUT PIN OPEN.

Both outputs have an extremely wide voltage compliance enabling fast direct current-to-voltage conversion through a resistor tied to ground or other voltage source. Positive compliance is  $36\ V$  above V- and is independent of the positive supply. Negative compliance is  $+10\ V$  above V-.

The dual outputs enable double the usual peak-to-peak load swing when driving loads in quasi-differential fashion. This feature is especially useful in cable driving, CRT deflection and in other balanced applications such as driving center-tapped coils and transformers.

#### **POWER SUPPLIES**

The DAC10 operates over a wide range of power supply voltages from a total supply of 9 V to 36 V. When operating with V–supplies of –10 V or less,  $I_{REF} \leq 1$  mA is recommended. Low reference current operation decreases power consumption and increases negative compliance, reference amplifier negative common-mode range, negative logic input range and negative logic threshold range; consult the various figures for guidance. For example, operation at –9 V with  $I_{REF}$  = 2 mA is not recommended because negative output compliance would be reduced to near zero. Operation from lower supplies is possible, however at least 8 V total must be applied to ensure turn-on of the internal bias network.

Symmetrical supplies are not required, as the DAC10 is quite insensitive to variations in supply voltage. Battery operation is feasible as no ground connection is required; however, an artificial ground may be used to ensure that logic swings, etc., remain within acceptable limits.

#### TEMPERATURE PERFORMANCE

The nonlinearity and monotonicity specifications of the DAC10 are guaranteed to apply over the entire rated operating temperature range. Full-scale output current drift is tight, typically +10 ppm/°C, with zero-scale output current and drift essentially negligible compared to 1/2 LSB.

The temperature coefficient of the reference resistor, R14, should match and track that of the output resistor for minimum overall full-scale drift. Settling times of the DAC10 decrease approximately 10% at  $-55^{\circ}$ C; an increase of about 15% is typical at  $+125^{\circ}$ C.

#### **SETTLING TIME**

The DAC10 is capable of extremely fast settling times; typically 85 ns at  $I_{REF}$  = 2 mA. Judicious circuit design and careful board layout must be employed to obtain full performance potential during testing and application. The logic switch design enables propagation delays of only 35 ns for each of the 10 bits. Settling time to within 1/2 LSB of the LSB is therefore 35 ns, with each progressively larger bit taking successively longer. The MSB settles in 85 ns, thus determining the overall settling time of 130 ns. Settling to 8-bit accuracy requires about 60 ns to 78 ns. The output capacitance of the DAC10, including the package, is approximately 18 pF; therefore, the output RC time constant dominates settling time if  $R_{\rm L} > 500~\Omega$ .

Settling time and propagation delay are relatively insensitive to logic input amplitude and rise and fall times, due to the high gain of the logic switches. Settling time also remains essentially constant for  $I_{REF}$  values down to 1 mA, with gradual increases for lower  $I_{REF}$  values. The principal advantage of higher  $I_{REF}$  values lies in the ability to attain a given output level with lower load resistors, thus reducing the output RC time constant.

Measurement of settling time requires the ability to accurately resolve  $\pm 2~\mu A$ ; therefore, a 4 k\Omega load is needed to provide adequate drive for most oscilloscopes. The settling time fixture of schematic titled "Settling Time Measurement" uses a cascode design to permit driving a 4 k\Omega load with less than 5 pF of parasitic capacitance at the measurement node. At  $I_{REF}$  values of less than 1 mA, excessive RC damping of the output is difficult to prevent while maintaining adequate sensitivity. However, the major carry from 01111111111 to 1000000000 provides an accurate indicator of settling time. This code change does not require the normal 6.2 time constants to settle to within  $\pm 0.2\%$  of the final value, and thus settling times may be observed at lower values of  $I_{REF}$ .

DAC10 switching transients or "glitches" are very low and may be further reduced by small capacitive loads at the output with a minor sacrifice in settling time.

Fastest operation can be obtained by using short leads, minimizing output capacitance and load resistor values, and by adequate bypassing at the supply, reference and  $V_{LC}$  terminals. Supplies do not require large electrolytic bypass capacitors as the supply current drain is independent of input logic states; 0.1  $\mu F$  capacitors at the supply pins provide full transient protection.

REV. D –9–

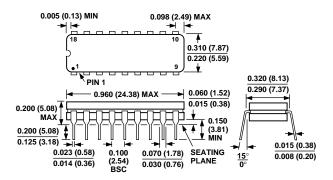

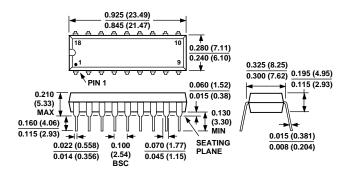

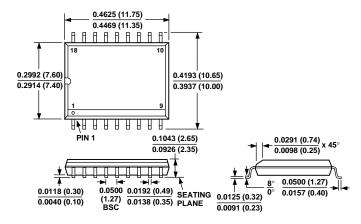

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

#### 18-Lead Cerdip (Q-18)

#### 18-Lead Plastic DIP (N-18)

#### 18-Lead Wide Body SOL (R-18)

-10-