Order

Now

**PGA300**

SLDS204B-OCTOBER 2014-REVISED JUNE 2020

# PGA300 Signal Conditioner and Transmitter for Pressure Sensors

# 1 Features

- Analog features:

- Analog front-end for resistive bridge sensors

- Accommodates sensor sensitivities from 1 mV/V to 135 mV/V

- On-chip temperature sensor

- Programmable gain

- 16-bit sigma-delta analog-to-digital converter for signal channel

- 16-bit sigma-delta analog-to-digital converter for temperature channel

- 14-bit output DAC

- Digital Features:

- <0.1% FSO accuracy across temperature

- System response time <220 µs

- Third-order temperature and nonlinearity compensation

- Diagnostic functions

- Integrated EEPROM for device operation, calibration data, and user data

- Peripheral features:

- One-wire interface enables communication through the power-supply pin

- 4-mA to 20-mA current-loop output

- Ratiometric and absolute voltage output

- Power supply:

- On-chip power management accepts wide power-supply voltage from 3.3 V to 30 V

- Integrated reverse voltage protection circuit

- Industrial temperature range: –40°C to +150°C

# 2 Applications

- Pressure transmitters

- Temperature transmitters

- Flow transmitters

- Level transmitters

# 3 Description

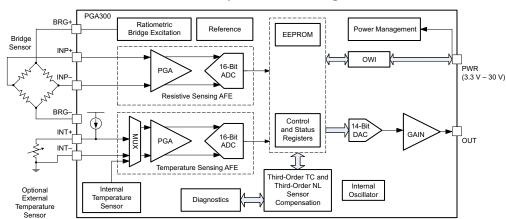

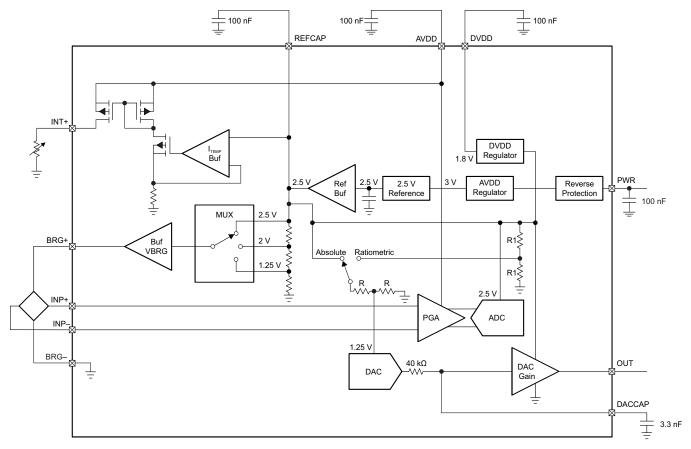

The PGA300 provides an interface for piezoresistive and strain-gauge pressure-sense elements. The device is a full system-on-chip (SoC) solution that incorporates a programmable analog front-end (AFE), ADC, and digital signal processing that enable direct connection to the sense element. Further, the PGA300 includes integrated voltage regulators and an oscillator, thus minimizing the number of external components. The device achieves high accuracy by employing third-order temperature and nonlinearity compensation. External communication is achieved by using a one-wire serial interface (OWI) through the power-supply pin in order to simplify the system calibration process. An Integrated DAC supports absolute-voltage, ratiometric-voltage, and 4-mA to 20-mA current-loop outputs.

## Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| PGA300      | VQFN (36) | 6.00 mm × 6.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

## **PGA300 Simplified Block Diagram**

Page

# **Table of Contents**

| 1 | Feat | tures 1                                                           |

|---|------|-------------------------------------------------------------------|

| 2 | Арр  | lications 1                                                       |

| 3 | Des  | cription 1                                                        |

| 4 | Rev  | ision History 2                                                   |

| 5 | Pin  | Configuration and Functions 4                                     |

| 6 | Spe  | cifications6                                                      |

|   | 6.1  | Absolute Maximum Ratings 6                                        |

|   | 6.2  | ESD Ratings 6                                                     |

|   | 6.3  | Recommended Operating Conditions 6                                |

|   | 6.4  | Thermal Information 6                                             |

|   | 6.5  | Electrical Characteristics: Reverse Voltage<br>Protection         |

|   | 6.6  | Electrical Characteristics: Regulators                            |

|   | 6.7  | Electrical Characteristics: Internal References7                  |

|   | 6.8  | Electrical Characteristics: Bridge Sensor Supply 7                |

|   | 6.9  | Electrical Characteristics: External Temperature<br>Sensor Supply |

|   | 6.10 | Electrical Characteristics: Internal Temperature<br>Sensor        |

|   | 6.11 | Electrical Characteristics: P Gain Stage (Chopper<br>Stabilized)  |

|   | 6.12 | Electrical Characteristics: P Analog-to-Digital<br>Converter      |

|   | 6.13 | B Electrical Characteristics: T Gain Stage (Chopper Stabilized)   |

|   | 6.14 | Electrical Characteristics: T Analog-to-Digital<br>Converter      |

|   | 6.15 | Electrical Characteristics: DAC Output 10                         |

|   | 6.16 | Electrical Characteristics: DAC Gain Stage 10                     |

|   | 6.17 | Electrical Characteristics: Diagnostics 11                        |

|   | 6.18 | Electrical Characteristics: One-Wire Interface 12                 |

|    | 6.19 | Electrical Characteristics: EEPROM (Non-Volatile Memory) | 12         |

|----|------|----------------------------------------------------------|------------|

|    | 6.20 | .,                                                       | 12         |

|    |      | Currents                                                 | 12         |

|    | 6.21 | Electrical Characteristics: Timing                       | 12         |

|    | 6.22 | Electrical Characteristics: Accuracy                     | 13         |

|    | 6.23 | Typical Characteristics                                  | 13         |

| 7  | Deta | iled Description 1                                       | 4          |

|    | 7.1  | Overview                                                 | 14         |

|    | 7.2  | Functional Block Diagram                                 | 15         |

|    | 7.3  | Feature Description 1                                    | 6          |

|    | 7.4  | Device Functional Modes                                  | 29         |

|    | 7.5  | Programming                                              | 31         |

|    | 7.6  | Register Maps                                            | 11         |

| 8  | App  | lication and Implementation6                             | 35         |

|    | 8.1  | Application Information                                  | 35         |

|    | 8.2  | Typical Applications                                     | 36         |

| 9  | Pow  | er Supply Recommendations                                | 1          |

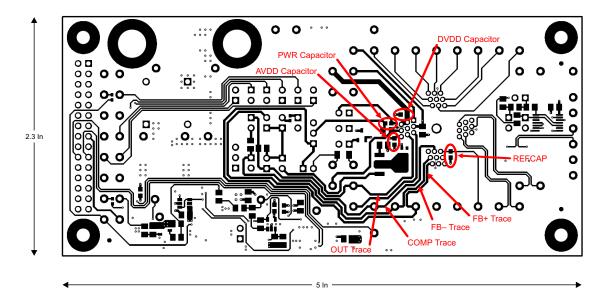

| 10 | Lay  | out7                                                     | 1          |

|    | 10.1 | Layout Guidelines                                        |            |

|    | 10.2 | Layout Example                                           | 71         |

| 11 | Dev  | ice and Documentation Support                            | <b>'</b> 3 |

|    | 11.1 | Documentation Support                                    |            |

|    | 11.2 | Receiving Notification of Documentation Updates          | 73         |

|    | 11.3 | Support Resources                                        | 73         |

|    | 11.4 | Trademarks                                               | 73         |

|    | 11.5 | Electrostatic Discharge Caution                          | 73         |

|    | 11.6 | Glossary                                                 | 73         |

| 12 |      | hanical, Packaging, and Orderable<br>rmation             | 73         |

# 4 Revision History

# Changes from Revision A (June 2016) to Revision B

| • | Changed document for flow, structure, correcting incorrect data, addition of missing data, and for clarification of device and how the device functions | 1    |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Changed Features section                                                                                                                                | 1    |

| • | Changed pin descriptions in Pin Functions table for clarity and functionality                                                                           | 5    |

| • | Changed Absolute Maximum Ratings table                                                                                                                  | 6    |

| • | Changed Recommended Operating Conditions table                                                                                                          | 6    |

| • | Changed Electrical Characteristics tables                                                                                                               | 7    |

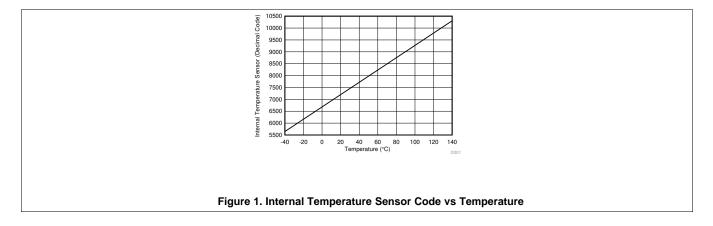

| • | Changed Internal Temperature Sensor Code vs Temperature figure and added Internal to caption                                                            | . 13 |

| • | Changed Overview section                                                                                                                                | . 14 |

| • | Changed Feature Description section                                                                                                                     |      |

| • | Changed Device Functional Modes section                                                                                                                 |      |

| • | Added Programming section                                                                                                                               | . 31 |

| • | Changed Register Maps section to new format, added missing registers and register bits, corrected register and register bit names                       | . 41 |

| • | Added Harness Open-Wire Diagnostics section                                                                                                             | . 65 |

| • | Added Typical Applications section                                                                                                                      |      |

| • | Changed Power Supply Recommendations section                                                                                                            | . 71 |

Page

# **Revision History (continued)**

| • | Changed Layout Guidelines section   |   |

|---|-------------------------------------|---|

| • | Added Related Documentation section | • |

|   |                                     |   |

# Changes from Original (October 2014) to Revision A

| Changed data sheet from PRODUCT PREVIEW to PRODUCTION DATA | ' |

|------------------------------------------------------------|---|

|------------------------------------------------------------|---|

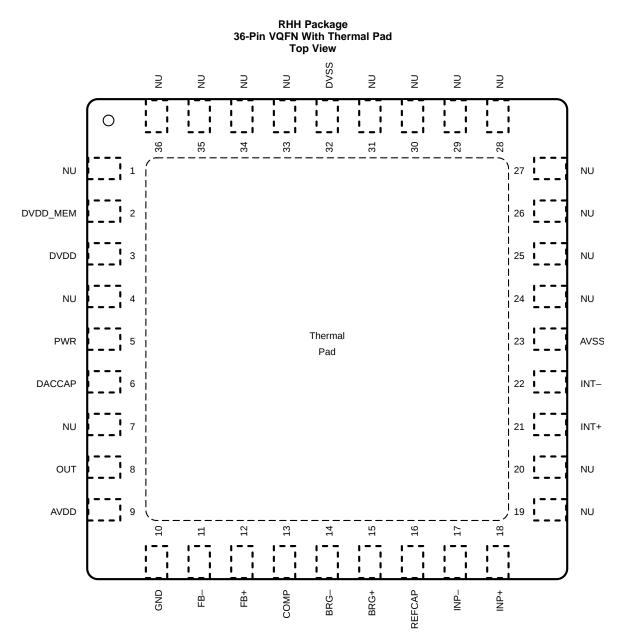

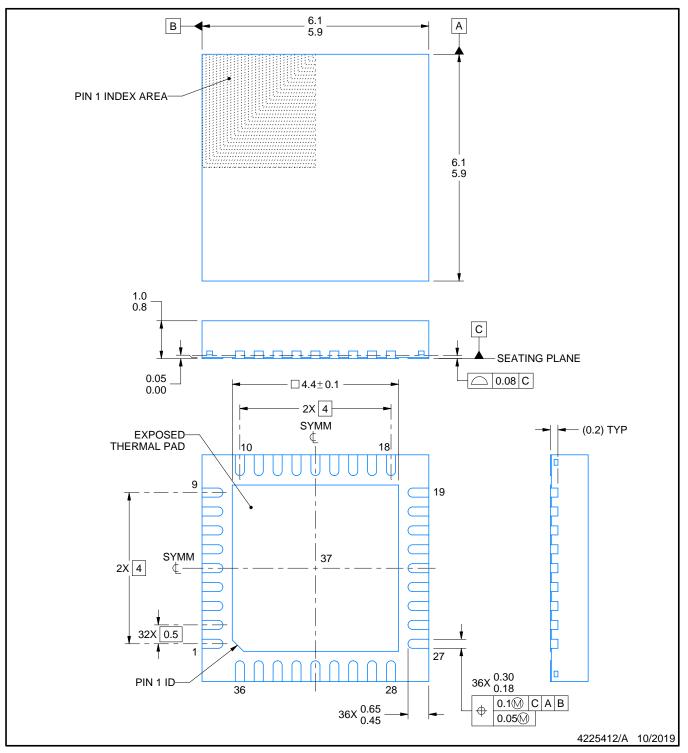

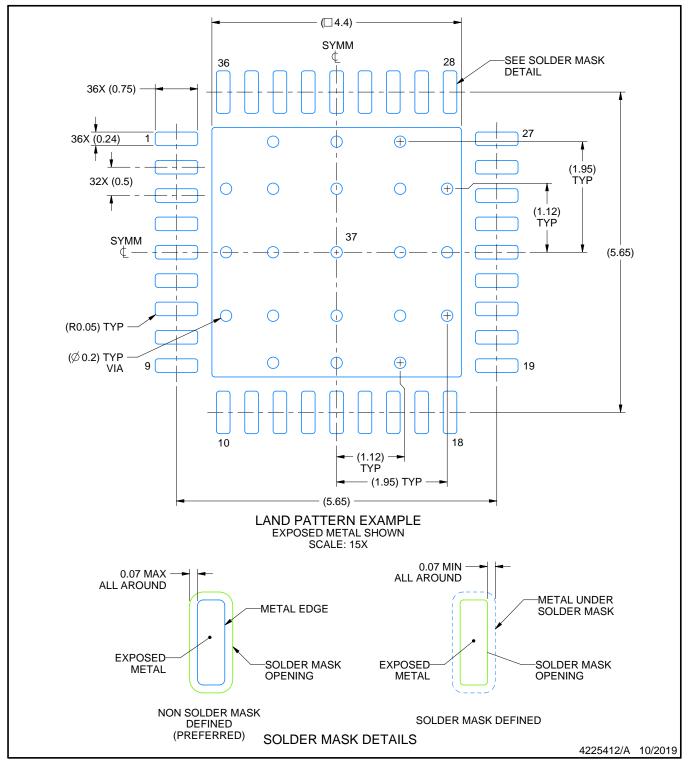

# 5 Pin Configuration and Functions

NU - Make no external connection

#### **Pin Functions**

| F           | PIN                                    | I/O | DESCRIPTION                                                               |

|-------------|----------------------------------------|-----|---------------------------------------------------------------------------|

| NAME        | NO.                                    | 1/0 | DESCRIPTION                                                               |

| AVDD        | 9                                      | 0   | AVDD regulator output. Connect a 100-nF capacitor to AVSS.                |

| AVSS        | 23                                     | _   | Analog ground <sup>(1)</sup>                                              |

| BRG+        | 15                                     | 0   | Bridge drive, positive                                                    |

| BRG-        | 14                                     | 0   | Bridge drive, negative                                                    |

| COMP        | 13                                     | Ι   | Output amplifier compensation                                             |

| DACCAP      | 6                                      | 0   | DAC capacitor                                                             |

| DVDD        | 3                                      | 0   | DVDD regulator output. Connect a 100-nF capacitor to DVSS.                |

| DVDD_MEM    | 2                                      | 0   | Power supply for EEPROM and OTP. Connect to DVDD.                         |

| DVSS        | 32                                     | _   | Digital ground <sup>(1)</sup>                                             |

| FB+         | 12                                     | Ι   | Feedback, positive                                                        |

| FB–         | 11                                     | Ι   | Feedback, negative                                                        |

| GND         | 10                                     | —   | Ground <sup>(1)</sup>                                                     |

| INP+        | 18                                     | Ι   | Resistive sensor positive input                                           |

| INP-        | 17                                     | I   | Resistive sensor negative input                                           |

| INT+        | 21                                     | Ι   | External temperature sensor positive input                                |

| INT–        | 22                                     | Ι   | External temperature sensor negative input                                |

| NU          | 1, 4, 7, 19, 20,<br>24 to 31, 33 to 36 | —   | Leave floating; solder to PCB but do not connect electrically to any net. |

| OUT         | 8                                      | 0   | DAC gain stage output                                                     |

| PWR         | 5                                      | I   | Input power supply. Connect a 100-nF capacitor to GND.                    |

| REFCAP      | 16                                     | 0   | Accurate reference capacitor. Connect a 100-nF capacitor to AVSS.         |

| Thermal pad | _                                      | _   | Connect to AVSS                                                           |

(1) Tie AVSS, DVSS and GND together.

# 6 Specifications

# 6.1 Absolute Maximum Ratings

see (1)

|                   |                                                                                         | MIN  | MAX                    | UNIT |

|-------------------|-----------------------------------------------------------------------------------------|------|------------------------|------|

| V <sub>PWR</sub>  | Supply voltage                                                                          | -28  | 33                     | V    |

|                   | Voltage at sensor input pins: INP+, INP-, INT+, INT-                                    | -0.3 | 2                      | V    |

|                   | Voltage at AVDD, AVSS, BRG+, BRG-, COMP, DACCAP, DVDD, DVDD_MEM, DVSS, FB-, REFCAP pins | -0.3 | 3.6                    | V    |

|                   | Voltage at FB+ pin                                                                      | -2   | V <sub>PWR</sub> + 0.3 | V    |

|                   | Voltage at OUT pin                                                                      | -0.3 | 33                     | V    |

| I <sub>PWR</sub>  | Supply current (OUT pin short to GND)                                                   |      | 25                     | mA   |

| T <sub>Jmax</sub> | Maximum junction temperature                                                            |      | 155                    | °C   |

| T <sub>stg</sub>  | Storage temperature                                                                     | -40  | 150                    | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                              |                                                                   |                                                                                | VALUE | UNIT |

|------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------|-------|------|

| V Electronetationalizationes | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2000                                                                          |       |      |

| V <sub>(ESD)</sub>           | Electrostatic discharge                                           | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating ambient temperature range (unless otherwise noted)

|                  |                               |                                         | MIN | NOM | MAX  | UNIT |

|------------------|-------------------------------|-----------------------------------------|-----|-----|------|------|

| V <sub>PWR</sub> | Power supply voltage          |                                         | 3.3 |     | 30   | V    |

|                  | Slew rate                     | $V_{PWR} = 0 V$ to 30 V                 |     |     | 0.5  | V/µs |

|                  | Capacitor value on PWR pin    |                                         | 10  | 100 |      | nF   |

|                  | Capacitor value on REFCAP pin | l i i i i i i i i i i i i i i i i i i i | 10  | 100 | 1000 | nF   |

| T <sub>A</sub>   | Operating ambient temperature |                                         | -40 |     | 150  | °C   |

|                  | EEPROM programming tempera    | ature                                   | -40 |     | 140  | °C   |

#### 6.4 Thermal Information

|                       |                                              | PGA300     |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RHH (VQFN) | UNIT |

|                       |                                              | 36 PINS    |      |

| $R_{	ext{	heta}JA}$   | Junction-to-ambient thermal resistance       | 30.6       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 16.4       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 5.4        | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.2        | °C/W |

| ΨJB                   | Junction-to-board characterization parameter | 5.4        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.7        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC package thermal metrics application report.

### 6.5 Electrical Characteristics: Reverse Voltage Protection

over operating ambient temperature range (unless otherwise noted)

| PARAMETER                                              | TEST CONDITIONS | MIN | ТҮР | MAX | UNIT |

|--------------------------------------------------------|-----------------|-----|-----|-----|------|

| Reverse voltage                                        |                 | -28 |     |     | V    |

| Voltage drop across reverse voltage protection element |                 |     | 20  |     | mV   |

## 6.6 Electrical Characteristics: Regulators

over operating ambient temperature range (unless otherwise noted)

| PARAMETER         |                          | TEST CONDITIONS            | MIN | ТҮР | MAX | UNIT |

|-------------------|--------------------------|----------------------------|-----|-----|-----|------|

| V <sub>AVDD</sub> | AVDD voltage             | C <sub>AVDD</sub> = 100 nF |     | 3   |     | V    |

| V <sub>DVDD</sub> | DVDD voltage – operating | C <sub>DVDD</sub> = 100 nF |     | 1.8 |     | V    |

# 6.7 Electrical Characteristics: Internal References

over operating ambient temperature range (unless otherwise noted)

| PARAMETER                      | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|--------------------------------|-----------------|-----|-----|-----|------|

| High-voltage reference voltage |                 |     | 1.2 |     | V    |

| Accurate reference voltage     |                 |     | 2.5 |     | V    |

## 6.8 Electrical Characteristics: Bridge Sensor Supply

over operating ambient temperature range (unless otherwise noted)

| PARAMETER                                |                              | TEST CONDITIONS                 | MIN | TYP  | MAX | UNIT |

|------------------------------------------|------------------------------|---------------------------------|-----|------|-----|------|

| V <sub>BRG+</sub> –<br>V <sub>BRG–</sub> |                              | VBRDG_CTRL[1:0] = 0b00, no load |     | 2.5  |     |      |

|                                          | Bridge supply voltage        | VBRDG_CTRL[1:0] = 0b01, no load |     | 2    |     | V    |

| *BRG-                                    |                              | VBRDG_CTRL[1:0] = 0b10, no load |     | 1.25 |     |      |

| I <sub>BRG</sub>                         | Current supply to the bridge |                                 |     |      | 1.5 | mA   |

| C <sub>BRG</sub>                         | Capacitive load              | $R_{BRG} = 20 \text{ k}\Omega$  |     |      | 2   | nF   |

## 6.9 Electrical Characteristics: External Temperature Sensor Supply

over operating ambient temperature range (unless otherwise noted)

|                   | PARAMETER                                     | TEST CONDITIONS         | MIN | ТҮР | MAX | UNIT |

|-------------------|-----------------------------------------------|-------------------------|-----|-----|-----|------|

| I <sub>TEMP</sub> |                                               | ITEMP_CTRL[2:0] = 0b000 |     | 25  |     |      |

|                   |                                               | ITEMP_CTRL[2:0] = 0b001 |     | 50  |     |      |

|                   | Current supply to external temperature sensor | ITEMP_CTRL[2:0] = 0b010 |     | 100 |     | μA   |

|                   |                                               | ITEMP_CTRL[2:0] = 0b011 |     | 500 |     |      |

|                   |                                               | ITEMP_CTRL[2:0] = 0b1xx |     | OFF |     |      |

| C <sub>TEMP</sub> | Capacitive load                               |                         |     |     | 100 | nF   |

|                   | Output impedance                              |                         |     | 15  |     | MΩ   |

#### 6.10 Electrical Characteristics: Internal Temperature Sensor

over operating ambient temperature range (unless otherwise noted)

| PARAMETER |                                    | TEST CONDITIONS                     | MIN | ТҮР  | MAX | UNIT         |

|-----------|------------------------------------|-------------------------------------|-----|------|-----|--------------|

|           | Temperature range                  |                                     | -40 |      | 150 | °C           |

|           | Zero-temperature T ADC output code | $T_A = 0^{\circ}C$ , T Gain = 5 V/V |     | 6680 |     | DEC          |

|           | Temperature coefficient            | T Gain = 5 V/V                      |     | 25.9 |     | Codes/°<br>C |

**ISTRUMENTS**

EXAS

# 6.11 Electrical Characteristics: P Gain Stage (Chopper Stabilized)

over operating ambient temperature range (unless otherwise noted)

| PARAMETER                                   | TEST CONDITIONS                         | MIN TYP MAX                                                            | UNIT  |

|---------------------------------------------|-----------------------------------------|------------------------------------------------------------------------|-------|

|                                             | P_GAIN[4:0] = 0b00000                   | 5                                                                      |       |

|                                             | P_GAIN[4:0] = 0b00001                   | 5.48                                                                   |       |

|                                             | P_GAIN[4:0] = 0b00010                   | 5.97                                                                   |       |

|                                             | P_GAIN[4:0] = 0b00011                   | 6.56                                                                   |       |

|                                             | P_GAIN[4:0] = 0b00100                   | 7.02                                                                   |       |

|                                             | P_GAIN[4:0] = 0b00101                   | 8                                                                      |       |

|                                             | P_GAIN[4:0] = 0b00110                   | 9.09                                                                   |       |

|                                             | P_GAIN[4:0] = 0b00111                   | 10                                                                     |       |

|                                             | P_GAIN[4:0] = 0b01000                   | 10.53                                                                  |       |

|                                             | P_GAIN[4:0] = 0b01001                   | 11.11                                                                  |       |

|                                             | P_GAIN[4:0] = 0b01010                   | 12.5                                                                   |       |

|                                             | P_GAIN[4:0] = 0b01011                   | 13.33                                                                  |       |

|                                             | P_GAIN[4:0] = 0b01100                   | 14.29                                                                  |       |

|                                             | P_GAIN[4:0] = 0b01101                   | 16                                                                     |       |

|                                             | P_GAIN[4:0] = 0b01110                   | 17.39                                                                  |       |

|                                             | P_GAIN[4:0] = 0b01111                   | 18.18                                                                  |       |

| Gain steps (5 bits)                         | P_GAIN[4:0] = 0b10000                   | 19.05                                                                  | V/V   |

|                                             | P_GAIN[4:0] = 0b10001                   | 20                                                                     |       |

|                                             | P_GAIN[4:0] = 0b10010                   | 22.22                                                                  |       |

|                                             | P_GAIN[4:0] = 0b10011                   | 25                                                                     |       |

|                                             | P_GAIN[4:0] = 0b10100                   | 30.77                                                                  |       |

|                                             | P_GAIN[4:0] = 0b10101                   | 36.36                                                                  |       |

|                                             | P_GAIN[4:0] = 0b10110                   | 40                                                                     |       |

|                                             | P_GAIN[4:0] = 0b10111                   | 44.44                                                                  |       |

|                                             | P_GAIN[4:0] = 0b11000                   | 50                                                                     |       |

|                                             | P_GAIN[4:0] = 0b11001                   | 57.14                                                                  |       |

|                                             | P_GAIN[4:0] = 0b11010                   | 66.67                                                                  |       |

|                                             | P_GAIN[4:0] = 0b11011                   | 80                                                                     |       |

|                                             | $P_GAIN[4:0] = 0b11100$                 | 100                                                                    |       |

|                                             | P_GAIN[4:0] = 0b11101                   | 133.33                                                                 |       |

|                                             | $P_GAIN[4:0] = 0b11110$                 | 200                                                                    |       |

|                                             | $P_GAIN[4:0] = 0b11111$                 | 400                                                                    |       |

| Gain-bandwidth product                      |                                         | 10                                                                     | MHz   |

| Input-referred noise density <sup>(1)</sup> | f = 0.1 Hz to 2 kHz, P Gain = 400 V/V   | 15                                                                     | nV/√F |

| Input offset voltage                        |                                         | 10                                                                     | μV    |

| Input bias current                          |                                         | 5                                                                      | nA    |

| Frequency response                          | P Gain = 400 V/V, <1 kHz                | ±0.1                                                                   | %V/\  |

| Common-mode voltage range                   |                                         | Depends on selected gain, bridge supply and sensor span <sup>(2)</sup> | V     |

| Common-mode rejection ratio                 | f <sub>CM</sub> = 50 Hz, P Gain = 5 V/V | 110                                                                    | dB    |

| Input impedance                             |                                         | 10                                                                     | MΩ    |

Total input-referred noise including P Gain noise, ADC reference noise, P ADC thermal noise, and P ADC quantization noise. (1) (2)

(a) The single-ended voltage of the positive and negative pins at the P Gain input must be between 0.3 V and 1.8 V

(b) The single-ended voltage of the positive and negative pins at the P Gain output must be between 0.1 V and 2 V

## 6.12 Electrical Characteristics: P Analog-to-Digital Converter

over operating ambient temperature range (unless otherwise noted)

|     | PARAMETER                        | TEST CONDITIONS               | MIN  | ТҮР    | MAX  | UNIT |

|-----|----------------------------------|-------------------------------|------|--------|------|------|

|     | Sigma-delta modulator frequency  |                               |      | 1      |      | MHz  |

|     | Differential input voltage range |                               | -2.5 |        | 2.5  | V    |

|     | Number of bits                   |                               |      | 16     |      | Bits |

| INL | Integral nonlinearity            |                               |      |        | ±0.5 | LSB  |

|     |                                  | Differential input = $-2.5$ V |      | 0x8000 |      |      |

|     | ADC two's complement code        | Differential input = 0 V      |      | 0x0000 |      |      |

|     |                                  | Differential input = 2.5 V    |      | 0x7FFF |      |      |

# 6.13 Electrical Characteristics: T Gain Stage (Chopper Stabilized)

over operating ambient temperature range (unless otherwise noted)

| PARAMETER                                   | TEST CONDITIONS                      | MIN TYP MAX                                                | UNIT   |

|---------------------------------------------|--------------------------------------|------------------------------------------------------------|--------|

|                                             | T_GAIN[1:0] = 0b00                   | 1.33                                                       |        |

|                                             | T_GAIN[1:0] = 0b01                   | 2                                                          |        |

| Gain steps (2 bits)                         | T_GAIN[1:0] = 0b10                   | 5                                                          | V/V    |

|                                             | T_GAIN[1:0] = 0b11                   | 20                                                         |        |

| Gain-bandwidth product                      |                                      | 350                                                        | kHz    |

| Input-referred noise density <sup>(1)</sup> | f = 0.1 Hz to 100 Hz, T Gain = 5 V/V | 110                                                        | nV/√Hz |

| Input offset voltage                        |                                      | 95                                                         | μV     |

| Input bias current                          |                                      | 5                                                          | nA     |

| Frequency response                          | T Gain = 20 V/V, <100 Hz             | 0.335                                                      | %V/V   |

| Common-mode voltage range                   |                                      | Depends on selected gain and current supply <sup>(2)</sup> | V      |

| Common-mode rejection ratio                 | f <sub>CM</sub> = 50 Hz              | 110                                                        | dB     |

| Input impedance                             |                                      | 1                                                          | MΩ     |

(1) Total input-referred noise including T Gain noise, ADC reference noise, T ADC thermal noise, and T ADC quantization noise.

(2) Common Mode at T Gain Input and Output: There are two constraints:

(a) The single-ended voltage of the positive and negative pins at the T Gain input must be between 5 mV and 1.8 V

(b) The single-ended voltage of the positive and negative pins at the T Gain output must be between 0.1 V and 2 V

# 6.14 Electrical Characteristics: T Analog-to-Digital Converter

over operating ambient temperature range (unless otherwise noted)

|     | PARAMETER                        | TEST CONDITIONS               | MIN  | TYP    | MAX  | UNIT |

|-----|----------------------------------|-------------------------------|------|--------|------|------|

|     | Sigma-delta modulator frequency  |                               |      | 1      |      | MHz  |

|     | Differential input voltage range |                               | -2.5 |        | 2.5  | V    |

|     | Number of bits                   |                               |      | 16     |      | Bits |

| INL | Integral nonlinearity            |                               |      |        | ±0.5 | LSB  |

|     |                                  | Differential input = $-2.5$ V |      | 0x8000 |      |      |

|     | ADC two's complement code        | Differential input = 0 V      |      | 0x0000 |      |      |

|     |                                  | Differential input = 2.5 V    |      | 0x7FFF |      |      |

# 6.15 Electrical Characteristics: DAC Output

over operating ambient temperature range (unless otherwise noted)

|           | · · · · · · · · · · · · · · · · · · · | ,                                   |     |                       |     |      |

|-----------|---------------------------------------|-------------------------------------|-----|-----------------------|-----|------|

| PARAMETER |                                       | TEST CONDITIONS                     | MIN | ТҮР                   | MAX | UNIT |

|           |                                       | DAC_RATIOMETRIC = 0b0 (ratiometric) |     | $0.25 \times V_{PWR}$ |     | V    |

|           | DAC reference voltage                 | DAC_RATIOMETRIC = 0b1               |     | 1.25                  |     | v    |

|           | DAC resolution                        |                                     |     | 14                    |     | Bits |

# 6.16 Electrical Characteristics: DAC Gain Stage

over operating ambient temperature range (unless otherwise noted)

| PARAMETER                              | TEST CONDITIONS                                 | MIN | ТҮР  | MAX  | UNIT  |

|----------------------------------------|-------------------------------------------------|-----|------|------|-------|

|                                        | DAC_GAIN[2:0] = 0b100                           |     | 2    |      |       |

|                                        | DAC_GAIN[2:0] = 0b010                           |     | 4    |      |       |

| Buffer gain (see Figure 6)             | DAC_GAIN[2:0] = 0b110                           |     | 6.67 |      | V/V   |

|                                        | DAC_GAIN[2:0] = 0b001                           |     | 10   |      |       |

| Current loop gain                      |                                                 |     | 1001 |      | mA/mA |

| Gain-bandwidth product                 |                                                 |     | 1    |      | MHz   |

| Zero-code voltage (gain = 4 V/V)       | DAC code = 0x0000, I <sub>DAC</sub> = 2.5 mA    |     |      | 20   | mV    |

| Full-scale code voltage (gain = 4 V/V) | DAC code is 0x1FFF, $I_{DAC} = -2.5 \text{ mA}$ | 4.8 |      |      | V     |

| Output current                         | DAC code = 0x1FFF, DAC code = 0x0000            |     |      | ±2.5 | mA    |

| Short-circuit source current           | DAC code = 0x1FFF                               |     | 27   |      | mA    |

| Short-circuit sink current             | DAC code = 0x0000                               |     | 27   |      | mA    |

|                                        | Without compensation                            |     |      | 100  | pF    |

| Maximum capacitance                    | With compensation                               |     |      | 100  | nF    |

# 6.17 Electrical Characteristics: Diagnostics

over operating ambient temperature range (unless otherwise noted)

|                    | PARAMETER                                                     | TEST                      | CONDITIONS        | MIN               | TYP  | MAX | UNIT               |

|--------------------|---------------------------------------------------------------|---------------------------|-------------------|-------------------|------|-----|--------------------|

| OSC_PWR<br>_OV     | Oscillator circuit supply overvoltage threshold               |                           |                   |                   | 3.3  |     | V                  |

| OSC_PWR<br>_UV     | Oscillator circuit supply undervoltage threshold              |                           |                   |                   | 2.7  |     | V                  |

| BRG_OV             | Resistive bridge sensor supply<br>overvoltage threshold       |                           |                   |                   | 10   |     | % V <sub>BRG</sub> |

| BRG_UV             | Resistive bridge sensor supply<br>undervoltage threshold      |                           |                   |                   | -10  |     | % V <sub>BRG</sub> |

| AVDD_OV            | AVDD overvoltage threshold                                    |                           |                   |                   | 3.3  |     | V                  |

| AVDD_UV            | AVDD undervoltage threshold                                   |                           |                   |                   | 2.7  |     | V                  |

| DVDD_OV            | DVDD overvoltage threshold                                    |                           |                   |                   | 2    |     | V                  |

| DVDD_UV            | DVDD undervoltage threshold                                   |                           |                   |                   | 1.53 |     | V                  |

| REF_OV             | Reference overvoltage threshold                               |                           |                   |                   | 2.75 |     | V                  |

| REF_UV             | Reference undervoltage threshold                              |                           |                   |                   | 2.25 |     | V                  |

|                    |                                                               | PD[1:0] = 0b00            |                   |                   | 4    |     |                    |

| P_DIAG_            | P Gain input diagnostics pulldown                             | PD[1:0] = 0b01            |                   |                   | 3    |     |                    |

| PD                 | resistor value                                                | PD[1:0] = 0b10            |                   |                   | 2    |     | MΩ                 |

|                    |                                                               | PD[1:0] = 0b11            |                   |                   | 1    |     |                    |

| T_DIAG_PU          | T Gain input diagnostics pullup resistor value                |                           |                   |                   | 1    |     | MΩ                 |

|                    | P Gain input overvoltage threshold <sup>(1)</sup>             |                           | THRS[2:0] = 0b000 |                   | 72.5 |     |                    |

|                    |                                                               | V <sub>BRG</sub> = 2.5 V  | THRS[2:0] = 0b001 |                   | 70   |     |                    |

|                    |                                                               | bitto                     | THRS[2:0] = 0b010 |                   | 65   |     |                    |

|                    |                                                               |                           | THRS[2:0] = 0b011 |                   | 90   |     |                    |

| INP_OV             |                                                               | V <sub>BRG</sub> = 2 V    | THRS[2:0] = 0b100 |                   | 87.5 |     | $\% V_{BRG}$       |

|                    |                                                               | bito                      | THRS[2:0] = 0b101 |                   | 82.5 |     |                    |

|                    |                                                               |                           |                   | THRS[2:0] = 0b110 |      | 100 |                    |

|                    |                                                               | V <sub>BRG</sub> = 1.25 V | THRS[2:0] = 0b111 |                   | 95   |     |                    |

|                    |                                                               |                           | THRS[2:0] = 0b000 |                   | 7.5  |     |                    |

|                    |                                                               | V <sub>BRG</sub> = 2.5 V  | THRS[2:0] = 0b001 |                   | 10.0 |     |                    |

|                    |                                                               | bito                      | THRS[2:0] = 0b010 |                   | 15.0 |     |                    |

|                    |                                                               |                           | THRS[2:0] = 0b011 |                   | 10.0 |     |                    |

| INP_UV             | P Gain input undervoltage threshold <sup>(1)</sup>            | V <sub>BRG</sub> = 2 V    | THRS[2:0] = 0b100 |                   | 12.5 |     | $\% V_{BRG}$       |

|                    |                                                               | bito                      | THRS[2:0] = 0b101 |                   | 17.5 |     |                    |

|                    |                                                               |                           | THRS[2:0] = 0b110 |                   | 17.5 |     |                    |

|                    |                                                               | V <sub>BRG</sub> = 1.25 V | THRS[2:0] = 0b111 |                   | 22.5 |     |                    |

| INT_OV             | T Gain input overvoltage threshold <sup>(2)</sup>             |                           |                   |                   | 2.1  |     | V                  |

| PGAIN_OV           | Output overvoltage (single-ended) threshold for P Gain        |                           |                   |                   | 2.25 |     | V                  |

| PGAIN_UV           | Output undervoltage (single-ended) threshold for P Gain       |                           |                   |                   | 0.15 |     | V                  |

| TGAIN_OV           | Output overvoltage (single-ended) threshold for T Gain        |                           |                   |                   | 2.25 |     | V                  |

| TGAIN_UV           | Output undervoltage (single-ended) threshold for T Gain       |                           |                   |                   | 0.15 |     | V                  |

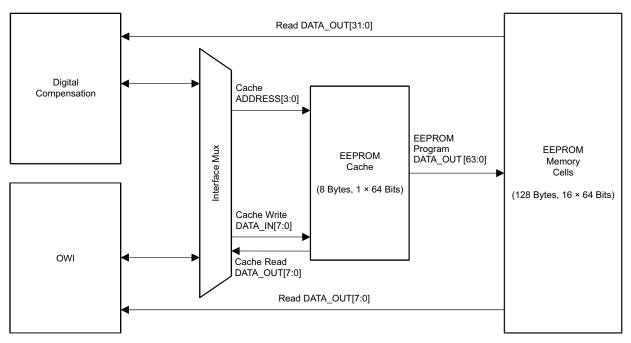

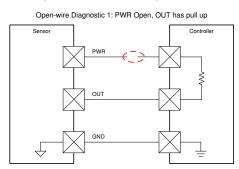

| HARNESS_<br>FAULT1 | Open-wire leakage current 1. Open<br>PWR with pullup on OUT   |                           |                   |                   | 2    |     | μA                 |

| HARNESS_<br>FAULT2 | Open-wire leakage current 2. Open<br>GND with pulldown on OUT |                           |                   |                   | 20   |     | μA                 |

INP+ and INP- each have individual threshold comparators.

INT+ and INT- each have individual threshold comparators.

# 6.18 Electrical Characteristics: One-Wire Interface

over operating ambient temperature range (unless otherwise noted)

|         | PARAMETER                              | TEST CONDITIONS | MIN  | TYP MAX | UNIT               |

|---------|----------------------------------------|-----------------|------|---------|--------------------|

|         | Communication baud rate <sup>(1)</sup> |                 | 600  | 9600    | Bits per<br>second |

| OWI_ENH | OWI activation high                    |                 | 5.95 |         | V                  |

| OWI_ENL | OWI activation low                     |                 |      | 5.75    | V                  |

| OWI_VIH | OWI transceiver Rx threshold for high  |                 | 4.8  | 5.1     | V                  |

| OWI_VIL | OWI transceiver Rx threshold for low   |                 | 3.9  | 4.2     | V                  |

| OWI_IOH | OWI transceiver Tx threshold for high  |                 | 500  | 1379    | μA                 |

| OWI_IOL | OWI transceiver Tx threshold for low   |                 | 2    | 5       | μA                 |

(1) OWI over power line does not work if there is an LDO between the supply to the sensor and the PWR pin, or if the OWI high and low voltages are greater than the regulated voltage.

# 6.19 Electrical Characteristics: EEPROM (Non-Volatile Memory)

over operating ambient temperature range (unless otherwise noted)

| PARAMETER          | TEST CONDITIONS | MIN | TYP | MAX  | UNIT   |

|--------------------|-----------------|-----|-----|------|--------|

| Size               |                 |     | 128 |      | Bytes  |

| Erase-write cycles |                 |     |     | 1000 | Cycles |

| Programming time   | Per 8-byte page |     |     | 8    | ms     |

| Data retention     |                 | 10  |     |      | Years  |

# 6.20 Electrical Characteristics: Power-Supply Currents

over operating ambient temperature range (unless otherwise noted)

|                  | PARAMETER            | TEST CONDITIONS                                                                             | MIN | TYP | MAX | UNIT |

|------------------|----------------------|---------------------------------------------------------------------------------------------|-----|-----|-----|------|

|                  |                      | Normal operation.<br>No load on BRG, no load on DAC.                                        |     | 2.5 |     |      |

| I <sub>PWR</sub> | Power-supply current | EEPROM programming.<br>While EEPROM is being programmed, no<br>load on BRG, no load on DAC. |     |     | 9   | mA   |

# 6.21 Electrical Characteristics: Timing

#### over operating ambient temperature range (unless otherwise noted)

|  | PARAMETER                                    | TEST CONDITIONS                                  | MIN | TYP  | MAX | UNIT |

|--|----------------------------------------------|--------------------------------------------------|-----|------|-----|------|

|  | Power-up time (including analog and digital) | V <sub>PWR</sub> ramp rate 0.5 V/µs              |     |      | 1   | ms   |

|  | Start-up time                                | No IIR filter <sup>(1)</sup>                     |     | 180  |     | μs   |

|  |                                              | IIR filter = 1000 Hz <sup><math>(2)</math></sup> |     | 1158 |     |      |

|  | Deserves time                                | No IIR filter <sup>(3)</sup>                     |     | 211  |     |      |

|  | Response time                                | IIR filter = 1000 Hz <sup><math>(4)</math></sup> |     | 1050 |     | μs   |

|  | Output rate                                  |                                                  |     | 128  |     | μs   |

|  |                                              |                                                  |     |      |     |      |

(1) Time from power up to reach 90% of valid output.

(2) Time from power up to reach valid output, including settling time.

(3) Time to reach 90% of valid output.

(4) Time to reach valid output, including settling time.

#### 6.22 Electrical Characteristics: Accuracy

over operating ambient temperature range (unless otherwise noted)

| PARAMETE                                                                | R                                                                                                 | TEST CONDITIONS                                                                                                                                                                          | MIN | TYP  | MAX | UNIT |

|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

|                                                                         |                                                                                                   | 3 pressure - 1 temperature calibration,<br>overall accuracy calculated using points<br>different from points used for calibration                                                        |     | 0.2  |     | %FSO |

| Absolute-voltage<br>overall accuracy (<br>sense element) <sup>(1)</sup> |                                                                                                   | 3 pressure - 3 temperature calibration, input<br>voltage not subject to temperature variation,<br>overall accuracy calculated using points<br>different from points used for calibration |     | 0.1  |     | %FSO |

|                                                                         |                                                                                                   | 4 pressure - 4 temperature calibration, input<br>voltage not subject to temperature variation,<br>overall accuracy calculated using points<br>different from points used for calibration |     | 0.08 |     | %FSO |

|                                                                         |                                                                                                   | 3 pressure - 1 temperature calibration,<br>overall accuracy calculated using points<br>different from points used for calibration                                                        |     | 0.5  |     | %FSO |

|                                                                         | Ratiometric-voltage output mode,<br>overall accuracy (PGA300, no sense<br>element) <sup>(1)</sup> | 3 pressure - 3 temperature calibration, input<br>voltage not subject to temperature variation,<br>overall accuracy calculated using points<br>different from points used for calibration |     | 0.25 |     | %FSO |

|                                                                         |                                                                                                   | 4 pressure - 4 temperature calibration, input<br>voltage not subject to temperature variation,<br>overall accuracy calculated using points<br>different from points used for calibration |     | 0.2  |     | %FSO |

|                                                                         |                                                                                                   | 3 pressure - 1 temperature calibration,<br>overall accuracy calculated using points<br>different from points used for calibration                                                        |     | 0.2  |     | %FSO |

| Current output mo<br>overall accuracy (<br>element) <sup>(1)</sup>      | ode,<br>(PGA300, no sense                                                                         | 3 pressure - 3 temperature calibration, input<br>voltage not subject to temperature variation,<br>overall accuracy calculated using points<br>different from points used for calibration |     | 0.1  |     | %FSO |

|                                                                         |                                                                                                   | 4 pressure - 4 temperature calibration, input<br>voltage not subject to temperature variation,<br>overall accuracy calculated using points<br>different from points used for calibration |     | 0.09 |     | %FSO |

(1) Sense element held at constant temperature while the PGA300 was calibrated at -25°C, 25°C, 85°C and 125°C. Accuracy was then measured at -40°C, 50°C and 150 °C.

# 6.23 Typical Characteristics

# 7 Detailed Description

## 7.1 Overview

The PGA300 can be used in a variety of applications. The most common ones are for pressure and temperature measurement. Depending on the application, the device itself can be configured in different modes. The following sections provide details regarding these configurations.

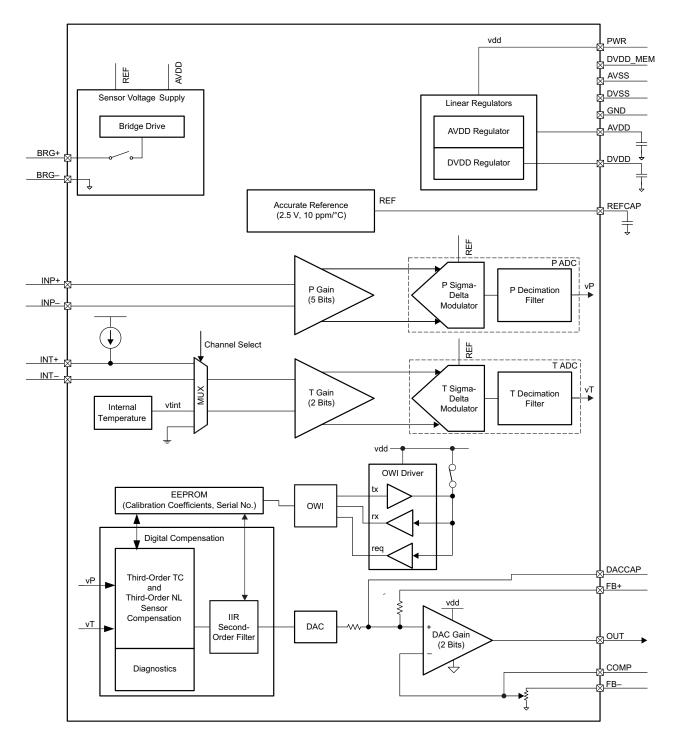

The PGA300 is a high-accuracy, low-drift, low-noise, low-power, and easily programmable signal-conditioner device for resistive bridge pressure and temperature sensing applications. The PGA300 implements a third-order temperature coefficient (TC) and nonlinearity (NL) compensation algorithm to linearize the analog output. The PGA300 accommodates various sensing element types, such as piezoresistive, ceramic film, and steel membrane. The device supports sensor element sensitivities ranging from 1 mV/V to 135 mV/V. The typical applications supported are pressure sensor transmitters, transducers, liquid-level meters, flow meters, strain gauges, weight scales, thermocouples, thermistors, 2-wire resistance thermometers (RTDs), and resistive field transmitters. The device can also be used in accelerometer and humidity sensor signal-conditioning applications.

The PGA300 provides bridge excitation voltages of 2.5 V, 2 V, and 1.25 V, all ratiometric to the ADC reference level. The PGA300 has a unique one-wire interface (OWI) that supports communication and configuration through the power-supply line during the calibration process. This feature minimizes the number of wires needed for an application.

The PGA300 contains two separated analog front-end (AFE) signal chains; one for resistive-bridge inputs and one for temperature-sensing inputs. Each AFE has its own gain amplifier and a 16-bit ADC operating at a 7.8-kHz output rate. The resistive-bridge input AFE consists of a programmable gain with 32 steps ranging from 5 V/V to 400 V/V. For the temperature-sensing AFE, the PGA300 provides a current source that can supply up to 500  $\mu$ A for optional external temperature sensing. This current source can also be used as a constant-current bridge excitation. The programmable gain in the temperature sensing AFE has four steps ranging from 1.33 V/V to 20 V/V. In addition, the PGA300 integrates an internal temperature sensor which can be configured as the input of the temperature-sensing AFE.

A 128-byte EEPROM is integrated in the PGA300 to store the calibration coefficients and the PGA300 configuration settings as needed. The PGA300 has a 14-bit DAC followed by a buffer gain stage of 2 V/V to 10 V/V. The device supports three industrial-standard outputs: ratiometric voltage, absolute voltage, and 4-mA to 20-mA current loop.

The diagnostic functions monitor the operating condition of the PGA300. The device can operate with a 3.3-V to 30-V power supply directly, without using an external LDO. The PGA300 has a wide ambient-temperature operating range from  $-40^{\circ}$ C to  $150^{\circ}$ C. The package form is 6-mm × 6-mm 36-pin VQFN. Within this small package size, the PGA300 integrates all the functions needed for resistive-bridge sensing applications to minimize PCB area and simplify the overall application design.

# 7.2 Functional Block Diagram

#### 7.3 Feature Description

This section describes individual functional blocks of the PGA300.

#### 7.3.1 Reverse-Voltage Protection Circuit

The PGA300 includes a reverse-voltage protection circuit. This circuit protects the device from reverse-battery conditions on the external power supply.

#### 7.3.2 Linear Regulators

The PGA300 has two main linear regulators: an AVDD regulator and a DVDD regulator. The AVDD regulator provides the 3-V voltage source for internal analog circuitry, whereas the DVDD regulator provides the 1.8-V regulated voltage for the digital circuitry. Connect 100-nF bypass capacitors between AVDD and AVSS and between DVDD and DVSS of the device.

#### 7.3.3 Internal References

The PGA300 has two internal references. These references are described in the following subsections.

#### 7.3.3.1 High-Voltage Reference

The high-voltage reference is an inaccurate reference used for the diagnostic thresholds.

#### 7.3.3.2 Accurate Reference

The accurate reference is used to generate the reference voltage for the P ADC, T ADC and DAC. Place a 100nF capacitor between the REFCAP pin and AVSS to limit the bandwidth of reference noise.

#### NOTE

The accurate reference is valid 50 µs after the digital core starts running at power up.

#### 7.3.4 Bridge Sensor Supply for Resistive Bridges (BRG+ to BRG-)

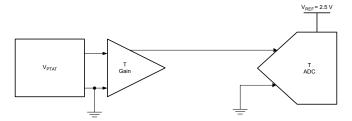

The bridge sensor voltage-supply block of the PGA300 provides power to the resistive-bridge sensor. The bridge sensor supply in the PGA300 is configurable to a nominal output voltage of 2.5-V, 2-V, or 1.25-V using the VBRDG\_CTRL[1:0] bits in the BRDG\_CTRL register to accommodate bridge sense elements with different resistor values. The bridge sensor supply is ratiometric to the accurate reference, as illustrated in Figure 2.

#### Feature Description (continued)

Figure 2. Bridge Sensor Supply and P ADC Reference Are Ratiometric

#### 7.3.5 ITEMP Supply for External Temperature Sensors

The ITEMP block in the PGA300 supplies a programmable current to an external temperature sensor such as an RTD temperature probe or NTC or PTC thermistor. The temperature-sensor current source is ratiometric to the accurate reference.

The value of the current can be programmed using the ITEMP\_CTRL[2:0] bits in the TEMP\_CTRL register.

#### 7.3.6 Internal Temperature Sensor

The PGA300 includes an internal temperature sensor whose voltage output is digitized by the T ADC. This digitized value is used to implement temperature compensation algorithms in software. The voltage generated by the internal temperature sensor is proportional to the device junction temperature.

Figure 3 shows the internal temperature sensor AFE.

Figure 3. Temperature Sensor AFE

#### Feature Description (continued)

#### 7.3.7 Pressure Measurement Signal Chain

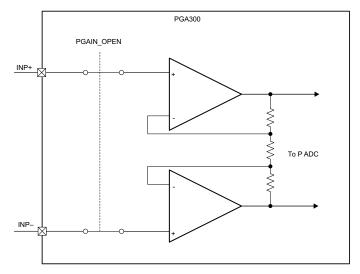

The pressure measurement signal chain of the PGA300 consists of a programmable gain, an instrumentation amplifier stage (P Gain), and a 16-bit, delta-sigma ADC (P ADC).

#### 7.3.7.1 P Gain Stage

The P Gain stage is designed with precision, low-drift, low-flicker-noise, chopper-stabilized amplifiers. P Gain is implemented as an instrumentation amplifier as shown in Figure 4. The gain of this stage is adjustable using the P\_GAIN[4:0] bits in the P\_GAIN\_SELECT register to accommodate sense elements with a wide range of signal spans.

Figure 4. P Gain Stage Diagram

The P Gain value should be set based on the maximum bridge output voltage. The maximum bridge voltage is the maximum sum of bridge offset and bridge span across the entire operating temperature range.

#### 7.3.7.2 P Analog-to-Digital Converter

The P analog-to-digital converter digitizes the voltage output of the P Gain amplifier. The digitized value is available in the PADC\_DATA\_MSB and PADC\_DATA\_LSB registers.

#### 7.3.7.2.1 P Sigma-Delta Modulator for P ADC

The sigma-delta modulator used in the P ADC is a 1-MHz, second-order, 3-bit quantizing sigma-delta modulator.

#### 7.3.7.2.2 P Decimation Filter for P ADC

The pressure signal path output conversion time is 128 µs, which equals an output rate of 7.8125 ksamples per second. The output of the decimation filter in the pressure signal path is a 16-bit *signed* value. Some example decimation output codes for given differential voltages at the input of the sigma-delta modulator are shown in Table 1.

| SIGMA-DELTA MODULATOR<br>DIFFERENTIAL INPUT VOLTAGE | 16-BIT NOISE-FREE<br>DECIMATOR OUTPUT |

|-----------------------------------------------------|---------------------------------------|

| -2.5 V                                              | -32 768 (0x8000)                      |

| -1.25 V                                             | -16 384 (0xC000)                      |

| 0 V                                                 | 0 (0x0000)                            |

| 1.25 V                                              | 16 383 (0x3FFF)                       |

| 2.5 V                                               | 32 767 (0x7FFF)                       |

#### Table 1. Input Voltage to Output Counts for the P ADC

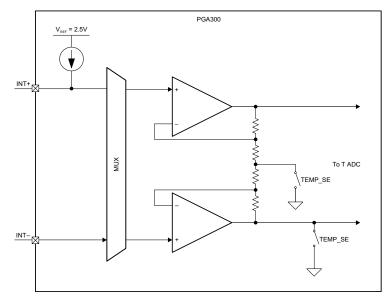

#### 7.3.8 Temperature Measurement Signal Chain

The temperature measurement signal chain of the PGA300 consists of a programmable gain amplifier stage (T Gain) and a 16-bit, delta-sigma ADC (T ADC).

#### 7.3.8.1 T Gain Stage

The device has the ability to perform temperature compensation via an internal or external temperature sensor. The user can select the source of the temperature measurement with the TEMP\_MUX\_CTRL[3:0] bits in the TEMP\_CTRL register. The device connects to an external temperature sensor via the INT+ and INT- pins.

The T Gain block is constructed with a low-flicker-noise, low-offset, chopper-stabilized amplifier. The gain is configured using the T\_GAIN[1:0] bits in the T\_GAIN\_SELECT register. Figure 5 shows the T Gain amplifier topology.

Figure 5. T Gain Stage Diagram

The T Gain amplifier can be configured for single-ended or differential operation using the TEMP\_SE bit in the TEMP\_SE register. When the T Gain amplifier is configured for single-ended operation, the differential voltage converted by the T ADC is with respect to ground. The T Gain amplifier must be set up for either single-ended or differential configuration, depending on the source of signal to the T Gain stage. Table 2 shows the configuration that the user must select for the different temperature sources.

| Table | 2. | Т | Gain | Configuration |

|-------|----|---|------|---------------|

|-------|----|---|------|---------------|

| TEMPERATURE SOURCE                                                                  | T GAIN CONFIGURATION |

|-------------------------------------------------------------------------------------|----------------------|

| Internal temperature sensor                                                         | Single-ended         |

| External temperature sensor with one terminal of the sensor connected to ground     | Single-ended         |

| External temperature sensor with neither terminal of the sensor connected to ground | Differential         |

The T Gain value must be set based on the temperature sense element used:

- For the internal temperature sensor, set T Gain = 5 V/V

- For an external temperature sensor such as a PTC thermistor, set T Gain = 20 V/V

(1)

#### 7.3.8.2 T Analog-to-Digital Converter

The T analog-to-digital converter digitizes the T Gain amplifier output. The digitized value is available in the TADC\_DATA\_MSB and TADC\_DATA\_LSB registers.

#### 7.3.8.2.1 T Sigma-Delta Modulator for T ADC

The sigma-delta modulator used in the T ADC is a 1-MHz, second-order, 3-bit quantizing sigma-delta modulator.

#### 7.3.8.2.2 T Decimation Filters for T ADC

The temperature signal path contains a decimation filter with an internal output rate of 128 µs.

The output of the decimation filter in the temperature signal path is a 16-bit *signed* value. Some example decimation output codes for given differential voltages at the input of the sigma-delta modulator are shown in Table 3.

| SIGMA-DELTA MODULATOR<br>DIFFERENTIAL INPUT VOLTAGE | 16-BIT NOISE-FREE<br>DECIMATOR OUTPUT |  |  |  |  |

|-----------------------------------------------------|---------------------------------------|--|--|--|--|

| –2.5 V                                              | -32 768 (0x8000)                      |  |  |  |  |

| -1.25 V                                             | -16 384 (0xC000)                      |  |  |  |  |

| 0 V                                                 | 0 (0x0000)                            |  |  |  |  |

| 1.25 V                                              | 16 383 (0x3FFF)                       |  |  |  |  |

| 2.5 V                                               | 32 767 (0x7FFF)                       |  |  |  |  |

# Table 3. Input Voltage to Output Codes Relationship for T ADC

The nominal relationship between the internal temperature sensor and the 16-bit T ADC code for T Gain = 5 V/V is shown in Equation 1.

T ADC Code = 25.9 Codes/°C × TEMP + 6680 Codes

where

• TEMP is temperature in °C

#### 7.3.9 DAC Output

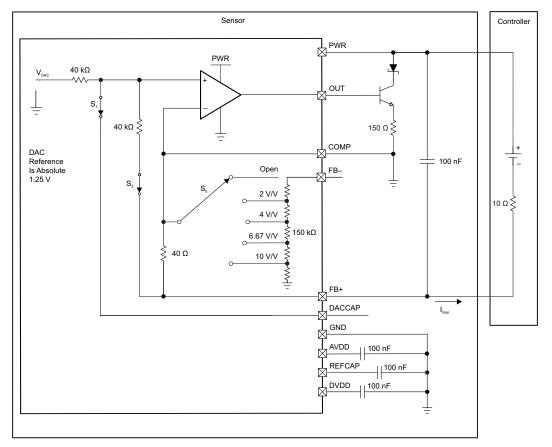

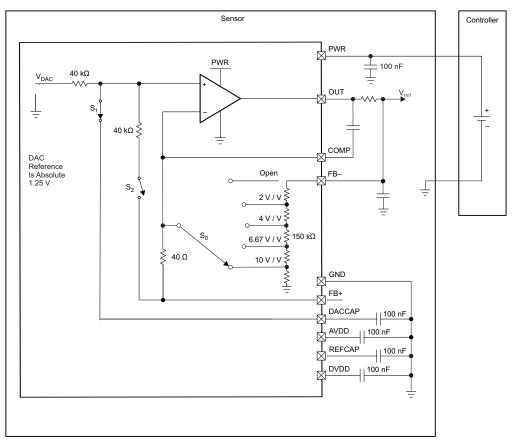

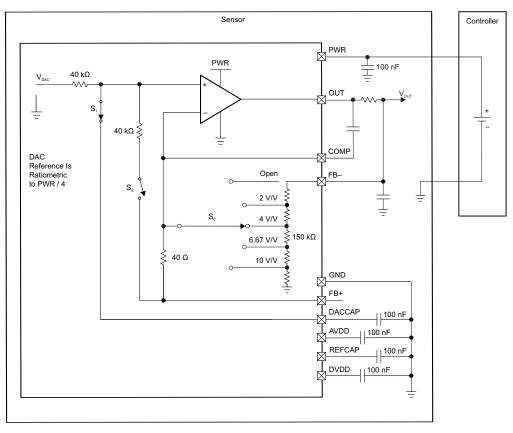

The device includes a 14-bit digital-to-analog converter that produces an absolute output voltage with respect to the accurate reference voltage or a ratiometric output voltage with respect to the PWR supply.

When the device undergoes a reset, the DAC registers are driven to the 0x0000 code.

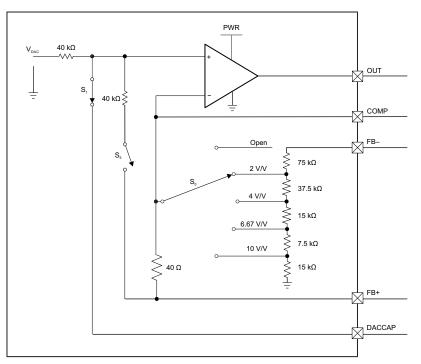

The PGA300 integrates a 40-k $\Omega$  filter resistor at the output of the DAC, as shown in Figure 6. Together with an external capacitor connected to the DACCAP pin, an RC low-pass filter can be implemented between the DAC output and the DAC gain amplifier. The external capacitor can be disconnected by opening switch S<sub>1</sub>. The DACCAP\_EN bit in the OP\_STAGE\_CTRL register controls the state of the S<sub>1</sub> switch.

#### 7.3.9.1 Ratiometric vs Absolute Output Mode

The DAC output can be configured to be either in ratiometric-to-PWR mode or independent-of-PWR (or absolute) mode using the DAC\_RATIOMETRIC bit in the DAC\_CONFIG register.

#### NOTE

In ratiometric mode, changes in the  $V_{PWR}$  voltage result in a proportional change in the DAC output voltage because the reference for the DAC is derived from  $V_{PWR}$ .

#### 7.3.10 DAC Gain Stage

The DAC gain amplifier is a configurable buffer stage following the DAC output. The DAC gain amplifier can be configured to operate in voltage amplification mode for voltage output or current amplification mode for 4-mA to 20-mA applications. In voltage output mode, the DAC gain is set to one of four possible gain settings using the DAC\_GAIN[2:0] bits in the OP\_STAGE\_CTRL register, as shown in Figure 6. In current output mode the gain of the DAC gain amplifier is fixed and cannot be changed.

The final stage of the DAC gain amplifier is connected to PWR and ground, thus providing the ability to drive the  $V_{OUT}$  voltage close to the  $V_{PWR}$  voltage.

The DAC gain amplifier also offers a COMP pin in order to allow implementing compensation when driving large capacitive loads. See the *PGA900 DAC Output Stability* application note and additional documentation in the *Related Documentation* section for details.

Figure 6. DAC Gain Stage Diagram

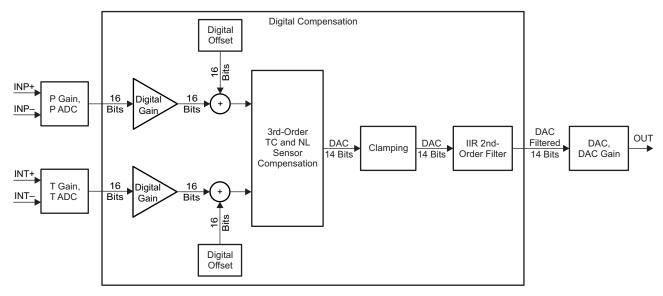

#### 7.3.11 Digital Compensation and Filter

The PGA300 implements digital gain and offset compensation as well as a third-order temperature (TC) and nonlinearity (NL) correction of the pressure and temperature inputs. The corrected output is filtered using a second-order IIR filter and then written to the DAC as shown in Figure 7.

Figure 7. Digital Compensation and Filter Block Diagram

#### 7.3.11.1 Digital Gain and Offset Compensation

The PGA300 implements digital gain and offset compensation for both pressure and temperature signal chains. Equation 2 and Equation 3 show the relationship between the outputs of the P ADC and T ADC, respectively and the gain and offset compensated pressure and temperature values:

| $P = a_P(P ADC + b_P)$ |  |

|------------------------|--|

|------------------------|--|

(2)

(3)

$T = a_T(T ADC + b_T)$

where

- a<sub>P</sub> and a<sub>T</sub> are the digital gain coefficients programmed in the PADC\_GAIN[15:0] and TADC\_GAIN[15:0] bits respectively

- $b_P$  and  $b_T$  are the digital offset coefficients programmed in the PADC\_OFFSET[15:0] and TADC\_OFFSET[15:0] bits respectively

- P is the gain and offset compensated pressure value

- T is the gain and offset compensated temperature value

- P ADC is the pressure digital output

- T ADC is the temperature digital output

For sensors with larger offset voltages or sensor bridges with low or high common-mode voltages, amplifying and offsetting the P ADC value in the digital domain can be useful. The digital gain and offset compensation allows the PGA300 to cancel the offset and amplify the signal further before being used by the temperature and nonlinearity compensation algorithm.

#### 7.3.11.2 Temperature and Nonlinearity Compensation

The PGA300 implements a third-order TC and NL compensation of the bridge offset, bridge span, and bridge nonlinearity. Equation 4 shows the digital temperature and nonlinearity compensation algorithm implemented in the PGA300:

$\begin{aligned} \mathsf{DAC} = (\mathsf{h}_0 + \mathsf{h}_1\mathsf{T} + \mathsf{h}_2\mathsf{T}^2 + \mathsf{h}_3\mathsf{T}^3) + (\mathsf{g}_0 + \mathsf{g}_1\mathsf{T} + \mathsf{g}_2\mathsf{T}^2 + \mathsf{g}_3\mathsf{T}^3) \times \mathsf{P} + (\mathsf{n}_0 + \mathsf{n}_1\mathsf{T} + \mathsf{n}_2\mathsf{T}^2 + \mathsf{n}_3\mathsf{T}^3) \times \mathsf{P}^2 + (\mathsf{m}_0 + \mathsf{m}_1\mathsf{T} + \mathsf{m}_2\mathsf{T}^2 + \mathsf{m}_3\mathsf{T}^3) \times \mathsf{P}^3 \end{aligned}$

where

- DAC = Digitally compensated value at the input of the DAC

- h<sub>x</sub>, g<sub>x</sub>, n<sub>x</sub> and m<sub>x</sub> are the TC and NL compensation coefficients programmed in EEPROM

- P is the offset and gain compensated pressure value

- T is the offset and gain compensated temperature value

(4)

(5)

Equation 4 has 16 coefficients, and therefore requires at least 16 different measurement points to compute a unique set of 16 coefficients.

The 16 different P ADC and T ADC measurements can be made, for example, at four temperatures and at four different pressures:

- The P Gain and T Gain values must be set to a fixed value for all measurements.

- At each measurement point, the P ADC value and the T ADC value must be recorded in order to compute the 16 coefficients.

- Measuring P ADC and T ADC at different temperatures and pressures may sometimes be expensive. In this

case, there are three approaches:

- Use a model of the bridge to estimate the P ADC and T ADC measurements instead of actually measuring them.

- Use batch modeling, in which a family of sense elements is characterized across temperature, and the TC coefficients of the compensation equation are determined prior to calibration. On a production line, measurements are made at a limited number of temperature and pressure set points, and coefficients are adjusted accordingly. Discuss details with TI application engineers on the E2E community.

- Reduce the number of coefficients by reducing the order of TC compensation. Discuss the procedure to

use fewer coefficients with TI application engineers on the E2E community.

#### 7.3.11.2.1 Operating Without TC and NL Compensation

The equation for P ADC-to-DAC conversion when operating without TC and NL compensation is shown in Equation 5.

$DAC = OFFSET_{PA2D} + GAIN_{PA2D} \times P ADC$

To use the PGA without TC and NL compensation set the  $h_x$ ,  $g_x$ ,  $n_x$  and  $m_x$  coefficients in EEPROM to the following values:

- $h_0 = OFFSET_{PA2D} / 4$

- $h_1$  to  $h_3 = 0x0000$

- $g_0 = GAIN_{PA2D} \times 2^{14}$

- $g_1$  to  $g_3 = 0x0000$

- $n_0$  to  $n_3 = 0x0000$

- $m_0$  to  $m_3 = 0x0000$

Consider an example of scaling the positive half of the 16-bit P ADC to a 14-bit DAC value. In this case,  $OFFSET_{PA2D} = 0$  and  $GAIN_{PA2D} = 0.5$ . Therefore,  $h_0 = 0$ , and  $g_0 = 2^{13}$ .

#### 7.3.11.2.2 Temperature Compensation Using the Internal Temperature Sensor

Temperature compensation can be performed using the internal temperature sensor with T Gain = 5 V/V. Typical internal temperature sensor ADC values at the different temperatures are shown in Table 4.

| Table 4. T ADC Value for the Internal Temperature           Sensor |        |  |  |  |

|--------------------------------------------------------------------|--------|--|--|--|

| TEMPERATURE T ADC VALUE (Typ)                                      |        |  |  |  |

| -40°C                                                              | 0x160C |  |  |  |

0x1A18

|                           | 150°C                    | 0x2945                       |

|---------------------------|--------------------------|------------------------------|

| For T ADC output codes at | intermediate temperature | s, use linear interpolation. |

0°C

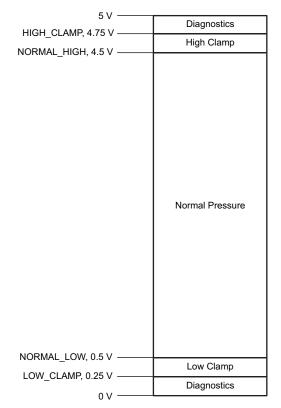

#### 7.3.11.3 Clamping

The output of the digital compensation is clamped. The low and high clamp values are programmable using the LOW\_CLAMP[15:0] and HIGH\_CLAMP[15:0] bits in the EEPROM. In addition, a normal operating output can be configured using the NORMAL\_LOW[15:0] and NORMAL\_HIGH[15:0] bits in the EEPROM. Any output value from the digital compensation that exceeds the NORMAL\_HIGH threshold gets driven to the HIGH\_CLAMP value. Similarly, any output value below the NORMAL\_LOW threshold gets driven to the LOW\_CLAMP value. Figure 8 shows an example of the clamping feature for 0-V to 5-V voltage output mode. The output of the compensation can be configured in a similar way when the 4-mA to 20-mA current output mode is used. In such case, however, the LOW\_CLAMP[15:0] value must be larger than the maximum supply current needed for normal operation of the device.

#### 7.3.11.4 Digital IIR Filter

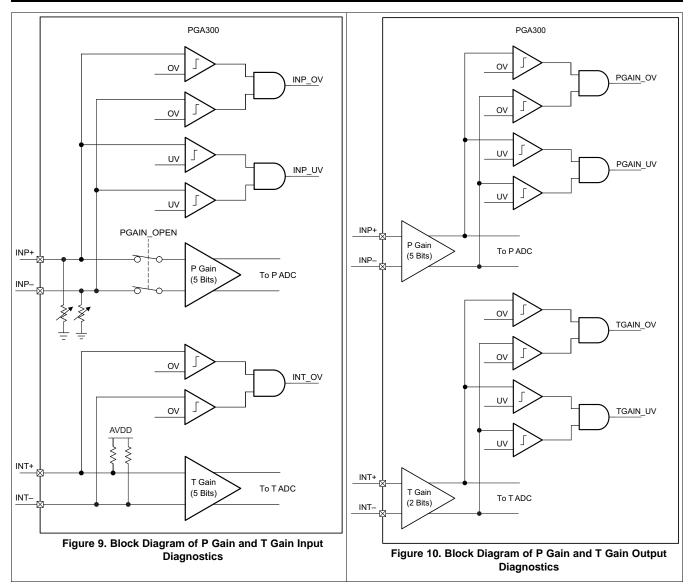

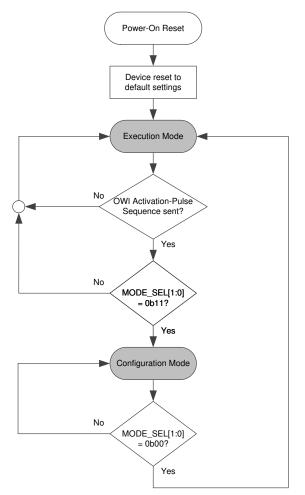

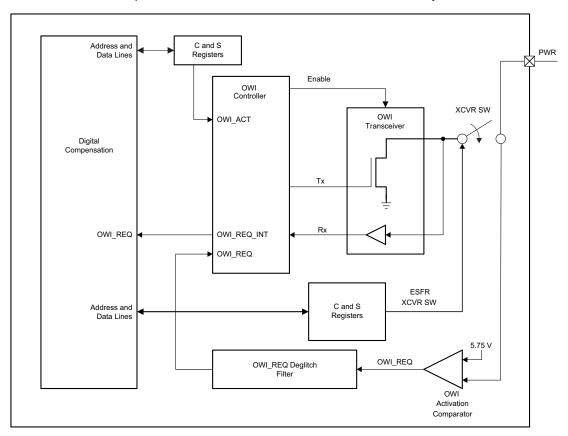

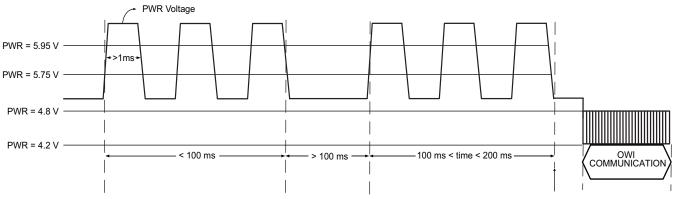

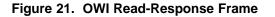

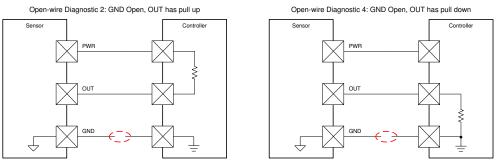

The IIR filter is implemented as follows: