## DCR021205, DCR022405

SBVS028C - DECEMBER 2000 - REVISED NOVEMBER 2016

# DCR02 Miniature, 2-W Isolated Regulated DC-DC Converters

#### **Features**

- 1000-Vrms Isolation

- **UL1950** Recognized

- 55-W/in<sup>3</sup> (3.3-W/cm<sup>3</sup>) Power Density

- 10-Pin PDIP and SOP Packages

- Device-to-Device Synchronization

- Thermal Protection

- 400-kHz Switching

- 125 FITS at 55°C

- **Short-Circuit Protection**

- 12-V and 24-V Input

- 5-V Output

# **Applications**

- Point-of-Use Power Conversion

- Digital Interface Power

- Ground Loop Elimination

- Power-Supply Noise Reduction

# 3 Description

The DCR02 family is a series of high-efficiency, inputisolated, output-regulated DC/DC converters. In addition to 2-W nominal, galvanically-isolated output power capability, this range of converters offers very low output noise and high accuracy.

The DCR02 family is implemented in standard molded device packaging, providing standard JEDEC outlines suitable for high-volume assembly.

The DCR02 family is manufactured using the same technology as standard device packages, thereby achieving very high reliability.

WARNING: This product has operational isolation and is intended for signal isolation only. It must not be used as a part of a safety isolation circuit requiring reinforced isolation. See definitions in *Isolation*.

#### Device Information<sup>(1)</sup>

| PART<br>NUMBER | PACKAGE   | BODY SIZE (NOM)    |

|----------------|-----------|--------------------|

| DCD02vavav     | PDIP (10) | 22.86 mm × 6.61 mm |

| DCR02xxxx      | SOP (10)  | 22.86 mm × 6.61 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

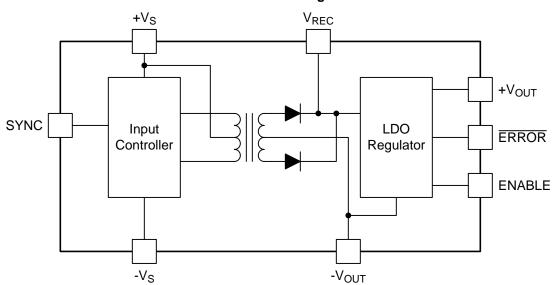

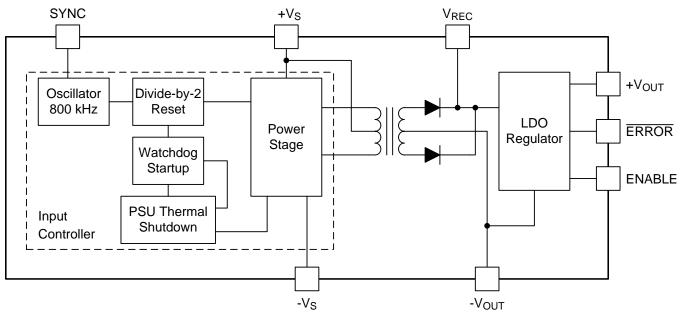

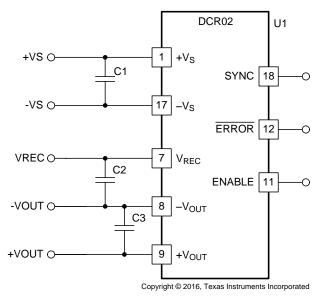

#### **DCR02 Block Diagram**

Copyright © 2016, Texas Instruments Incorporated

#### **Table of Contents**

| 1 | Features 1                           | 8  | Application and Implementation                      |            |

|---|--------------------------------------|----|-----------------------------------------------------|------------|

| 2 | Applications 1                       |    | 8.1 Application Information                         |            |

| 3 | Description 1                        |    | 8.2 Typical Application                             | 13         |

| 4 | Revision History2                    | 9  | Power Supply Recommendations                        | 1          |

| 5 | Pin Configuration and Functions 3    | 10 | Layout                                              | 18         |

| 6 | Specifications4                      |    | 10.1 Layout Guidelines                              | 1          |

| • | 6.1 Absolute Maximum Ratings         |    | 10.2 Layout Examples                                | 1          |

|   | 6.2 ESD Ratings                      |    | 10.3 Thermal Consideration                          | 16         |

|   | 6.3 Recommended Operating Conditions | 11 | Device and Documentation Support                    | 17         |

|   | 6.4 Thermal Information              |    | 11.1 Documentation Support                          | 17         |

|   | 6.5 Electrical Characteristics5      |    | 11.2 Related Links                                  | 17         |

|   | 6.6 Typical Characteristics6         |    | 11.3 Receiving Notification of Documentation Update | es 1       |

| 7 | Detailed Description 7               |    | 11.4 Community Resources                            | <b>1</b> 7 |

|   | 7.1 Overview                         |    | 11.5 Trademarks                                     | 17         |

|   | 7.2 Functional Block Diagram 7       |    | 11.6 Electrostatic Discharge Caution                | 17         |

|   | 7.3 Feature Description              |    | 11.7 Glossary                                       | 17         |

|   | 7.4 Device Functional Modes9         | 12 | Mechanical, Packaging, and Orderable Information    | 1          |

# 4 Revision History

#### Changes from Revision B (December 2007) to Revision C

Page

Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section.

Deleted Ordering Information table and Supplemental Ordering Information image; see Package Option Addendum at the end of the data sheet.

Changed DCR02 PinOut image in Pin Configuration and Functions

Changed Pin 1 From: V<sub>S</sub> To: +V<sub>S</sub>.

Changed Pin 8 From: 0V<sub>OUT</sub> To: -V<sub>OUT</sub>.

Changed Pin 9 From: V<sub>O</sub> To: +V<sub>OUT</sub>.

Changed Pin 17 From: 0V<sub>IN</sub> To: -V<sub>S</sub>.

3

Changed Pin 17 From: 0V<sub>IN</sub> To: -V<sub>S</sub>.

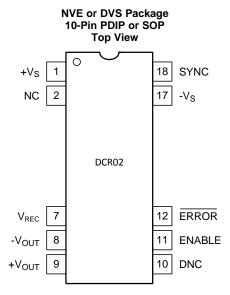

# 5 Pin Configuration and Functions

#### **Pin Functions**

|     | PIN I/O <sup>(1)</sup> |        | DESCRIPTION           |  |  |  |

|-----|------------------------|--------|-----------------------|--|--|--|

| NO. | NAME                   | 1/0(*) | DESCRIPTION           |  |  |  |

| 1   | +V <sub>S</sub>        | I      | Voltage input         |  |  |  |

| 2   | NC                     | _      | No connection         |  |  |  |

| 7   | V <sub>REC</sub>       | 0      | Rectified output      |  |  |  |

| 8   | -V <sub>OUT</sub>      | 0      | Output ground         |  |  |  |

| 9   | +V <sub>OUT</sub>      | 0      | Voltage output        |  |  |  |

| 10  | DNC                    | _      | Do not connect        |  |  |  |

| 11  | ENABLE                 | I      | Output voltage enable |  |  |  |

| 12  | ERROR                  | 0      | Error flag active low |  |  |  |

| 17  | -V <sub>S</sub>        | I      | Input ground          |  |  |  |

| 18  | SYNC                   | I      | Synchronization input |  |  |  |

(1) I = input and O = output

# 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                       |                                                          | MIN | MAX | UNIT |

|---------------------------------------|----------------------------------------------------------|-----|-----|------|

| Input voltage                         | DCR021205                                                |     | 15  | V    |

|                                       | DCR022405                                                |     | 29  | V    |

| Reflow solder temperature             | SOP package (surface temperature of device body or pins) |     | 260 | °C   |

| Storage temperature, T <sub>stg</sub> |                                                          | -60 | 125 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                              |               |                                                                                 | VALUE | UNIT |

|------------------------------|---------------|---------------------------------------------------------------------------------|-------|------|

| V                            | Electrostatic | Electrostatic Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> |       | V    |

| V <sub>(ESD)</sub> discharge | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup>  | ±250  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                       |           | MIN  | NOM | MAX  | UNIT |

|-----------------------|-----------|------|-----|------|------|

| Input voltogo         | DCR021205 | 10.8 | 12  | 13.2 | V    |

| Input voltage         | DCR022405 | 21.6 | 24  | 26.4 | V    |

| Operating temperature | ·         | -40  |     | 70   | ů    |

## 6.4 Thermal Information

|                      |                                              | DC         |           |      |

|----------------------|----------------------------------------------|------------|-----------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | NVE (PDIP) | DVS (SOP) | UNIT |

|                      |                                              | 10 PINS    | 10 PINS   |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 60         | 60        | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 26         | 26        | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 24         | 24        | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 7          | 7         | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 24         | 24        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Submit Documentation Feedback

Copyright © 2000–2016, Texas Instruments Incorporated

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.5 Electrical Characteristics

At  $T_A = +25$ °C,  $V_S =$  nominal,  $I_{OUT} = 10$  mA,  $C_{OUT} = 0.1$ - $\mu F$  ceramic, and  $C_{IN} = 2.2$ - $\mu F$  ceramic, unless otherwise noted. (1)

| PARAMETER                                                         | TEST COND                                  | ITIONS                          | MIN      | TYP      | MAX       | UNIT      |  |  |  |

|-------------------------------------------------------------------|--------------------------------------------|---------------------------------|----------|----------|-----------|-----------|--|--|--|

| OUTPUT                                                            |                                            |                                 |          |          |           |           |  |  |  |

| Nominal output voltage (+V <sub>OUT</sub> )                       |                                            |                                 |          | 5        |           | V         |  |  |  |

| Setpoint accuracy                                                 |                                            |                                 |          | 0.5%     | 2%        |           |  |  |  |

| Maximum output current                                            |                                            |                                 |          |          | 400       | mA        |  |  |  |

| Output short-circuit protected                                    | Duration                                   |                                 |          | Infinite |           |           |  |  |  |

| Line regulation                                                   |                                            |                                 |          | 1        |           | mV/V      |  |  |  |

| Over line and load                                                | 10-mA to 400-mA load, over +V              | / <sub>S</sub> range            |          | 1%       | 2.5%      |           |  |  |  |

| Temperature variation                                             | -40°C to 70°C                              |                                 |          | 1%       |           |           |  |  |  |

|                                                                   | DCR0212 ripple, 20-MHz band                | width, 50% load (1)             |          | 18       |           |           |  |  |  |

| Diagle and actes                                                  | DCR0212 noise, 100-MHz ban                 | dwidth, 50% load <sup>(1)</sup> |          | 20       |           | >/        |  |  |  |

| Ripple and noise                                                  | DCR0224 ripple, 20-MHz band                | width, 50% load <sup>(1)</sup>  |          | 18       |           | $mV_{PP}$ |  |  |  |

|                                                                   | DCR0224 noise, 100-MHz ban                 | dwidth, 50% load <sup>(1)</sup> |          | 25       |           |           |  |  |  |

| INPUT                                                             |                                            |                                 |          |          |           |           |  |  |  |

|                                                                   | DCR022405                                  |                                 |          | 12       |           |           |  |  |  |

| Nominal voltage (+V <sub>S</sub> )                                | DCR021205                                  |                                 |          | 24       |           | V         |  |  |  |

| Voltage range                                                     |                                            |                                 | -10%     |          | 10%       |           |  |  |  |

|                                                                   |                                            | $I_O = 0 \text{ mA}$            |          | 15       |           |           |  |  |  |

|                                                                   | DCR021205                                  | I <sub>O</sub> = 10 mA          |          | 23       |           |           |  |  |  |

|                                                                   |                                            | I <sub>O</sub> = 400 mA         |          | 250      |           |           |  |  |  |

| Supply current                                                    |                                            | $I_O = 0 \text{ mA}$            |          | 15       |           | mA        |  |  |  |

|                                                                   | DCR022405                                  | I <sub>O</sub> = 10 mA          |          | 17       |           | 7         |  |  |  |

|                                                                   |                                            | I <sub>O</sub> = 400 mA         |          | 129      |           |           |  |  |  |

| Reflected ripple current                                          | 20-MHz bandwidth, 100% load                | (1)                             |          | 8        |           | $mA_{PP}$ |  |  |  |

| ISOLATION                                                         |                                            |                                 |          |          |           |           |  |  |  |

|                                                                   |                                            | Voltage                         | 1        |          |           | kVrms     |  |  |  |

|                                                                   | 1-s flash test                             | dV/dt                           |          |          | 500       | V/s       |  |  |  |

| Voltage                                                           |                                            | Leakage current                 |          |          | 30        | nA        |  |  |  |

|                                                                   | Continuous working voltage                 | DC                              |          |          | 60        | VDC       |  |  |  |

|                                                                   | across isolation barrier                   | AC                              |          |          | 42.5      | VAC       |  |  |  |

| Barrier capacitance                                               |                                            | 1                               |          | 25       |           | pF        |  |  |  |

| OUTPUT ENABLE CONTROL                                             |                                            |                                 | <u>'</u> |          |           |           |  |  |  |

| Logic high input voltage                                          |                                            |                                 | 2        |          | $V_{REC}$ | V         |  |  |  |

| Logic high input current                                          | 2 < V <sub>ENABLE</sub> < V <sub>REG</sub> |                                 |          | 100      |           | nA        |  |  |  |

| Logic low input voltage                                           |                                            |                                 | -0.2     |          | 0.5       | V         |  |  |  |

| Logic low input current                                           | 0 < V <sub>ENABLE</sub> < 0.5              |                                 |          | 100      |           | nA        |  |  |  |

| ERROR FLAG                                                        |                                            |                                 | <u> </u> |          |           |           |  |  |  |

| Logic high open collector leakage                                 | V <sub>ERROR</sub> = 5 V                   |                                 |          |          | 10        | μA        |  |  |  |

| Logic low output voltage                                          | Sinking 2 mA                               |                                 |          |          | 0.4       | V         |  |  |  |

| THERMAL SHUTDOWN                                                  |                                            |                                 |          |          |           |           |  |  |  |

|                                                                   | Temp activated                             |                                 |          | 150      |           |           |  |  |  |

| Junction temperature                                              | Temp deactivated                           |                                 | 130      |          | °C        |           |  |  |  |

| SYNCHRONIZATION PIN                                               |                                            |                                 | +        |          | ļ.        |           |  |  |  |

|                                                                   |                                            |                                 | 720      | 800      | 880       | kHz       |  |  |  |

| Internal oscillator frequency                                     |                                            |                                 | 720      | 000      | 000       | 11112     |  |  |  |

| Internal oscillator frequency  External synchronization frequency |                                            |                                 | 720      | 000      | 880       | kHz       |  |  |  |

<sup>(1)</sup> Ceramic capacitors,  $C_{IN}$  = 2.2  $\mu F,$   $C_{FILTER}$  = 1  $\mu F,$  and  $C_{OUT}$  = 0.1  $\mu F.$

## **Electrical Characteristics (continued)**

At  $T_A$  = +25°C,  $V_S$  = nominal,  $I_{OUT}$  = 10 mA,  $C_{OUT}$  = 0.1- $\mu$ F ceramic, and  $C_{IN}$  = 2.2- $\mu$ F ceramic, unless otherwise noted. (1)

| PARAMETER                           | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-------------------------------------|-----------------|-----|-----|-----|------|

| External synchronization signal low |                 | 0   |     | 0.4 | V    |

| External capacitance on SYNC pin    |                 |     |     | 3   | pF   |

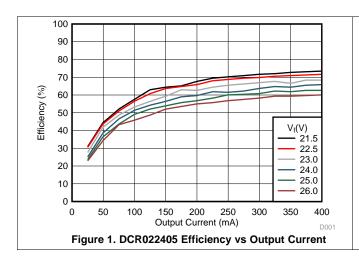

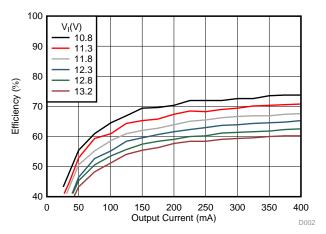

# 6.6 Typical Characteristics

Figure 2. DCR021205 Efficiency vs Output Current

Submit Documentation Feedback

Copyright © 2000–2016, Texas Instruments Incorporated

# 7 Detailed Description

#### 7.1 Overview

The DCR02 series of power modules offer isolation from a regulated power supply operating from 12 V or 24 V inputs. The DCR02s provide a regulated 5-V output voltage at a nominal output power of 2 W. The DCR02 devices include a low dropout linear regulator internal to the device to achieve a well-regulated output voltage. The DCR02 devices are specified for operational isolation only. The circuit design uses an advanced BiCMOS and DMOS process.

## 7.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

#### 7.3 Feature Description

#### 7.3.1 Isolation

Underwriters Laboratories (UL)<sup>™</sup> defines several classes of isolation that are used in modern power supplies.

Safety extra low voltage (SELV) is defined by UL (UL1950 E199929) as a secondary circuit which is so designated and protected that under normal and single fault conditions the voltage between any two accessible parts, or between an accessible part and the equipment earthing terminal for operational isolation does not exceed steady state 42.4 V<sub>RMS</sub> or 60 V<sub>DC</sub> peak.

#### 7.3.1.1 Operation or Functional Isolation

The type of isolation used in the DCR02 products is referred to as operational or functional isolation. Insulated wire used in the construction of the transformer acts as the primary isolation barrier. A high-potential (hipot), onesecond duration test (dielectric voltage, withstand test) is a production test used to verify that the isolation barrier is functioning. Products with operational isolation must never be used as an element in a safety-isolation system.

#### 7.3.1.2 Basic or Enhanced Isolation

Basic or enhanced isolation is defined by specified creepage and clearance limits between the primary and secondary circuits of the power supply. Basic isolation is the use of an isolation barrier in addition to the insulated wire in the construction of the transformer. Input and output circuits must also be physically separated by specified distances.

Copyright © 2000-2016, Texas Instruments Incorporated

## **Feature Description (continued)**

#### NOTE

The DCR02 products do not provide basic or enhanced isolation.

#### 7.3.1.3 Working Voltage

For a device with operational isolation, the continuous working voltage that can be applied across the device in normal operation must be less than 42.4  $V_{RMS}$  or 60  $V_{DC}$  (SELV limits).

#### **WARNING**

Do not use the device as an element of a safety isolation system if SELV is exceeded.

If the device is expected to function correctly with more than 42.4  $V_{RMS}$  or 60  $V_{DC}$  applied continuously across the isolation barrier, then the circuitry on both sides of the barrier must be regarded as operating at an unsafe voltage, and further isolation or insulation systems must form a barrier between these circuits and any user-accessible circuitry according to safety standard requirements.

## 7.3.1.4 Isolation Voltage Rating

The terms *Hipot test, flash-tested, withstand voltage, proof voltage, dielectric withstand voltage,* and *isolation test voltage* all relate to the same thing; a test voltage applied for a specified time across a component designed to provide electrical isolation to verify the integrity of that isolation. TI's DCR02 series of DC-DC converters are all 100% production tested at 1 kV<sub>AC</sub> for one second.

#### 7.3.1.5 Repeated High-Voltage Isolation Testing

Repeated high-voltage isolation testing of a barrier component can degrade the isolation capability, depending on materials, construction, and environment. The DCR02 series of DC–DC converters have toroidal, enameled, wire isolation transformers with no additional insulation between the primary and secondary windings. While a device can be expected to withstand several times the stated test voltage, the isolation capability depends on the wire insulation. Any material, including this enamel (typically polyurethane), is susceptible to eventual chemical degradation when subject to very-high applied voltages. Therefore, strictly limit the number of high-voltage tests and repeated high-voltage isolation testing. However, if it is absolutely required, reduce the voltage by 20% from specified test voltage with a duration limit of one second per test.

#### 7.3.2 Power Stage

The DCR02 series of devices use a push-pull, center-tapped topology. The DCR02 devices switch at 400 kHz (divide-by-2 from an 800-kHz oscillator). The internal transformer's output is full wave rectified and filtered by the external  $1-\mu F$  ceramic capacitor connected to the  $V_{REC}$  pin. An internal low-dropout regulator provides a well-regulated output voltage over the operating range of the device.

## 7.3.3 Oscillator and Watchdog

The onboard, 800-kHz oscillator generates the switching frequency through a divide-by-2 circuit. The oscillator can be synchronized to other DCR02 device circuits or an external source, and is used to minimize system noise.

A watchdog circuit monitors the operation of the oscillator circuit. The oscillator can be disabled by pulling the SYNC pin low. When the SYNC pin goes low, the output pins transition into tri-state mode, which occurs within  $2 \mu s$ .

## 7.3.4 ERROR Flag

The DCR02 has an  $\overline{\text{ERROR}}$  pin which provides a *power good* flag, as long as the internal regulator is in regulation. If the  $\overline{\text{ERROR}}$  output is required, place a 10-k $\Omega$  resistor between the  $\overline{\text{ERROR}}$  pin and the output voltage.

## Feature Description (continued)

#### 7.3.5 Synchronization

When more than one DC-DC converter is switching in an application, beat frequencies and other electrical interference can be generated. This interference occurs because of the small variations in switching frequencies between the DC-DC converters.

The DCR02 series of devices overcome this interference by allowing devices to be synchronized to one another. Synchronize up to eight devices by connecting the SYNC pins of each device, taking care to minimize the capacitance of tracking. Stray capacitance (greater than 3 pF) reduces the switching frequency, or can sometimes stop the oscillator circuit. The maximum recommended voltage applied to the SYNC pin is 3 V.

For an application that uses more than eight synchronized devices use an external device to drive the SYNC pins. *External Synchronization of the DCP01/02 Series of DC/DC Converters* (SBAA035) describes this configuration.

#### NOTE

During the start-up period, all synchronized devices draw maximum current from the input simultaneously. A ceramic capacitor must be connected close to each device's input pin. A 2.2-µF ceramic capacitor is required.

#### 7.3.6 Construction

The basic construction of the DCR02 series of devices is the same as standard integrated circuits. The molded package contains no substrate. The DCR02 series of devices are constructed using an IC, low dropout linear regulator, rectifier diodes, and a wound magnetic toroid on a leadframe. Because the package contains no solder, the devices do not require any special printed-circuit board (PCB) assembly processing. This architecture results in an isolated DC–DC converter with inherently high reliability.

## 7.3.7 Decoupling – Ripple Reduction

Due to the very low forward resistance of the DMOS switching transistors, high current demands are placed upon the input supply for a short time. By using a high quality, low Equivalent Series Resistance (ESR) ceramic input capacitor of 2.2-µF, placed close to the IC supply input pins, the effects on the power supply can be minimized.

The high switching frequency of 400 kHz allows relatively small values of capacitors to be used for filtering the rectified output voltage. A good-quality, low-ESR, 1-µF ceramic capacitor placed close to the VREC pin and output ground is required and reduces the ripple. The output at VREC is full wave rectified and produces a ripple of 800 kHz.

TI recommends that a  $0.1-\mu F$ , low-ESR ceramic capacitor is connected close to the output pin and ground to reduce noise on the output. The capacitor values listed are minimum values. If lower ripple is required, the filter capacitor must be increased in value to  $2.2 \ \mu F$ .

As with all switching power supplies, the best performance is obtained with low ESR ceramic capacitors connected close to the device pins. If low-ESR ceramic capacitors are not used, the ESR generates a voltage drop when the capacitor is supplying the load power. Often a larger capacitor is chosen for this purpose, when a low ESR, smaller capacitor would perform as well.

## NOTE

TI does not recommend that the DCR02 be fitted using an IC socket, as this degrades performance.

## 7.4 Device Functional Modes

## 7.4.1 Device Disable and Enable

Each of the DCR02 series devices can be disabled or enabled by driving the SYNC pin using an open-drain CMOS gate. If the SYNC pin is pulled low, the DCR02 becomes disabled. The disable time depends upon the external loading. The internal disable function is implemented in 2  $\mu$ s. Removal of the pulldown causes the DCR02 to be enabled.

Copyright © 2000–2016, Texas Instruments Incorporated

## **Device Functional Modes (continued)**

Capacitive loading on the SYNC pin must be minimized ( $\leq$  3 pF) to prevent a reduction in the oscillator frequency. *External Synchronization of the DCP01/02 Series of DC/DC Converters* (SBAA035) describes disable and enable control circuitry. This document contains information on how to null the effects of additional capacitance on the SYNC pin. The oscillator's frequency can be measured at  $V_{REC}$ , as this is the fundamental frequency of the ripple component.

# 7.4.2 Regulated Output Disable and Enable

The regulated output of the DCR02 can be disabled by pulling the ENABLE pin LOW. Disabling the output voltage this way still produces a voltage on the  $V_{REC}$  pin. When using the ENABLE control, TI recommends placing a 10-k $\Omega$  resistor between the  $V_{REC}$  and ENABLE pins. The ENABLE pin only controls the internal linear regulator.

If disabling the regulated output is not required, pull the ENABLE pin HIGH by shorting it directly to the  $V_{REC}$  pin. This enables the regulated output voltage, thus allowing the output to be controlled from the isolated side.

Submit Documentation Feedback

Copyright © 2000–2016, Texas Instruments Incorporated

# 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 8.1 Application Information

The DCR02 devices offer up to 2 W of isolated, 5-V regulated output power from a 12-V or 24-V input supply. Applications requiring up to 1-kVrms of operational isolation benefits from the small size and ease-of-use of the DCR02 family of devices.

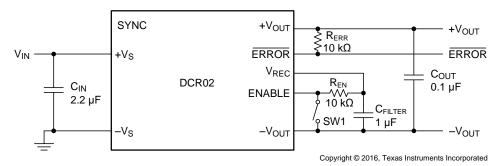

#### 8.1.1 DCR02 Single Voltage Output

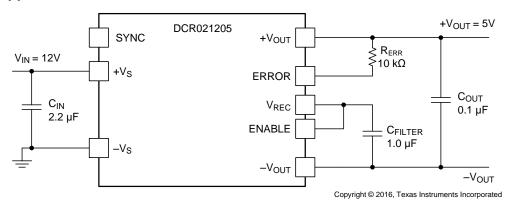

The DCR02 can be used to provide a single voltage output by connecting the circuit as shown in Figure 3. The ERROR output signal is pulled up to the value of  $V_{OUT}$  for the particular DCR02 being used. The value of  $R_{ERR}$  depends on the loading on the ERROR line; however, the total load on the ERROR line must not exceed the value given in *Electrical Characteristics*.

The output can be permanently enabled by connecting the ENABLE pin to the  $V_{REC}$  pin. The DCR02 can be enabled remotely by connecting the ENABLE pin to  $V_{REC}$  through a pull-up resistor ( $R_{EN}$ ); the value of this resistor is not critical for the DCR02, because only a small current flows. Switch SW1 can be used to pull the ENABLE pin low, thus disabling the output. The switching devices can be a bipolar transistor, FET, or a mechanical device; the main load that it senses is  $R_{EN}$ .

Low-ESR, ceramic capacitors are required for  $C_{\text{IN}}$ ,  $C_{\text{OUT}}$ , and  $C_{\text{FILTER}}$ .

Figure 3. DCR02 Single Output Voltage

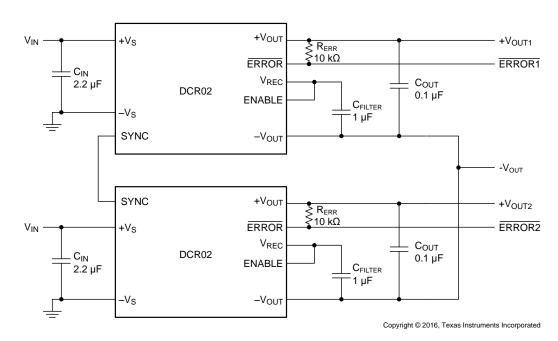

#### 8.1.2 Generating Two Positive Output Voltages

Two DCR02s can be used to create two +5V output voltages, as shown in Figure 4. The two DCR02s are connected in self-synchronization, thus locking the oscillators of both devices to a single frequency. The  $\overline{\text{ERROR}}$  and  $\overline{\text{ENABLE}}$  facilities can be used in a similar configuration for a single DCR02. The filter capacitors connected to the  $V_{\text{REC}}$  pins ( $C_{\text{FILTER}}$ ) must be kept separate from each other and connected in close proximity to the respective DCR02. If similar output voltages are being used, TI does not recommend that a single filter capacitor (with an increased capacitance) be used with both  $V_{\text{REC}}$  pins connected together, because this could result in the overloading of one of the devices.

## **Application Information (continued)**

Low-ESR, ceramic capacitors are required for  $C_{\text{IN}}$ ,  $C_{\text{OUT}}$ , and  $C_{\text{FILTER}}$ .

Figure 4. Generating Two Positive Voltages from Self-Synchronized DCR02s

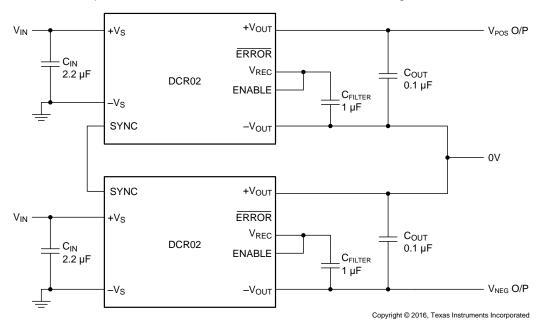

#### 8.1.3 Generation of Dual Polarity Voltages from Two Self-Synchronized DCR02s

Two DCR02s can be configured to produce a dual polarity supply (that is, ±5 V); the circuit must be connected as shown in Figure 5.

It must be observed that both DCR02s are positive voltage regulators; therefore the  $\overline{\text{ERROR}}$ , ENABLE, and  $V_{\text{REC}}$  pins are relative to their respective devices, 0 V, and must not be connected together.

Low-ESR, ceramic capacitors are required for  $C_{\text{IN}}$ ,  $C_{\text{OUT}}$ , and  $C_{\text{FILTER}}$ .

Figure 5. Dual Polarity Voltage Generation from Two Self-Synchronized DCR02s

#### 8.2 Typical Application

Low-ESR, ceramic capacitors are required for  $C_{\text{IN}},\,C_{\text{OUT}},$  and  $C_{\text{FILTER}}.$

Figure 6. DCR02 Typical Schematic

#### 8.2.1 Design Requirements

For this design example, use the parameters listed in Table 1 and follow the design procedure.

Table 1. Design Example Parameters

| DESIGN PARAMETER                 | VALUE              |

|----------------------------------|--------------------|

| Input voltage, V <sub>IN</sub>   | 12 V typical       |

| Output voltage, V <sub>OUT</sub> | 5 V regulated      |

| Output current rating            | 400 mA             |

| Isolation                        | 1000-V operational |

#### 8.2.2 Detailed Design Procedure

#### 8.2.2.1 Input Capacitor

For this design, a 2.2-µF, ceramic capacitor is required for the input decoupling capacitor.

#### 8.2.2.2 Output Capacitor

For this design, a 0.1-µF, ceramic capacitor is required for between +V<sub>OUT</sub> and -V<sub>OUT</sub>.

## 8.2.2.3 Filter Capacitor

A high-quality, low-ESR, 1-µF, ceramic capacitor placed close to the VREC pin and output ground is required to reduce output voltage ripple.

#### 8.2.2.4 ERROR Flag

Place a 10-k $\Omega$  resistor between the  $\overline{\sf ERROR}$  pin and the output voltage to provide a *power good* signal when the internal regulator is in regulation.

Copyright © 2000–2016, Texas Instruments Incorporated

## 8.2.3 Application Curves

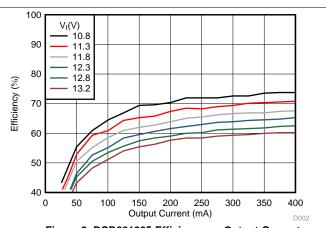

Figure 7. DCR021205 Efficiency vs Output Current

# 9 Power Supply Recommendations

The DCR02 is a switching power supply, and as such can place high peak current demands on the input supply. To avoid the supply falling momentarily during the fast switching pulses, ground and power planes must be used to connect the power to the input of DCR02. If this connection is not possible, then the supplies must be connected in a star formation with the traces made as wide as possible.

# 10 Layout

## 10.1 Layout Guidelines

Carefully consider the layout of the PCB in order for the best results to be obtained.

Input and output power and ground planes provide a low-impedance path for the input and output power. For the output, the positive and negative voltage outputs conduct through wide traces to minimize losses.

A good-quality, low-ESR, ceramic capacitor placed as close as practical across the input reduces reflected ripple and ensure a smooth start-up.

A good-quality, low-ESR, ceramic capacitor placed as close as practical across the rectifier output terminal and output ground gives the best ripple and noise performance.

The location of the decoupling capacitors in close proximity to their respective pins ensures low losses due to the effects of stray inductance, thus improving the ripple performance. This location is of particular importance to the input decoupling capacitor, because this capacitor supplies the transient current associated with the fast switching waveforms of the power drive circuits.

If the SYNC pin is being used, the tracking between device SYNC pins must be short to avoid stray capacitance. Never connect a capacitor to the SYNC pin. If the SYNC pin is not being used it is advisable to place a guard ring (connected to input ground) around this pin to avoid any noise pickup. Ensure that no other trace is in close proximity to this trace SYNC trace to decrease the stray capacitance on this pin. The stray capacitance affects the performance of the oscillator.

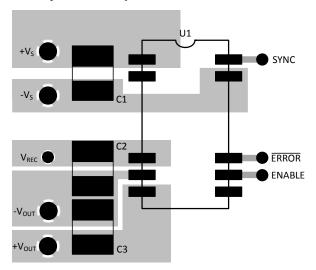

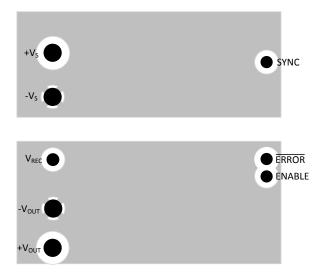

Figure 8 and Figure 9 show a typical layout for the SOP package DCR02 device. The layout shows proper placement of capacitors and power planes. Figure 10 shows a schematic for a single DCR02, SOP package device.

## 10.2 Layout Examples

Figure 8. PCB Layout Example, Component-Side View

Figure 9. PCB Layout Example, Non-Component-Side View

## **Layout Examples (continued)**

Figure 10. DCR02 PCB Schematic, U Package

#### 10.3 Thermal Consideration

Due to the high power density of this device, it is advisable to provide a ground plane on the output. The output regulator is mounted on a copper leadframe, and a ground plane serves as an efficient heatsink.

# 11 Device and Documentation Support

## 11.1 Documentation Support

#### 11.1.1 Related Documentation

For related documentation see the following:

External Synchronization of the DCP01/02 Series of DC/DC Converters (SBAA035)

#### 11.2 Related Links

The table below lists quick access links. Categories include technical documents, support and community resources, tools and software, and quick access to sample or buy.

Table 2. Related Links

| PARTS     | PRODUCT FOLDER | SAMPLE & BUY | TECHNICAL DOCUMENTS | TOOLS &<br>SOFTWARE | SUPPORT & COMMUNITY |

|-----------|----------------|--------------|---------------------|---------------------|---------------------|

| DCR021205 | Click here     | Click here   | Click here          | Click here          | Click here          |

| DCR022405 | Click here     | Click here   | Click here          | Click here          | Click here          |

## 11.3 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

#### 11.4 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community TI's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

## 11.5 Trademarks

E2E is a trademark of Texas Instruments.

Underwriters Laboratories (UL) is a trademark of UL LLC.

All other trademarks are the property of their respective owners.

#### 11.6 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# 11.7 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

# 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Copyright © 2000–2016, Texas Instruments Incorporated

6-Feb-2020

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan          | Lead/Ball Finish (6) | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|-------------------|----------------------|---------------------|--------------|-------------------------|---------|

| DCR021205P       | ACTIVE | PDIP         | NVE                | 10   | 20             | Pb-Free<br>(RoHS) | NIPDAU               | N / A for Pkg Type  | -40 to 70    | DCR021205P              | Samples |

| DCR021205P-U     | ACTIVE | SOP          | DVS                | 10   | 20             | Pb-Free<br>(RoHS) | NIPDAU               | Level-3-260C-168 HR | -40 to 70    | DCR021205P-U            | Samples |

| DCR022405P       | ACTIVE | PDIP         | NVE                | 10   | 20             | Pb-Free<br>(RoHS) | NIPDAU               | N / A for Pkg Type  | -40 to 70    | DCR022405P              | Samples |

| DCR022405P-U     | ACTIVE | SOP          | DVS                | 10   | 20             | Pb-Free<br>(RoHS) | NIPDAU               | Level-3-260C-168 HR | -40 to 70    | DCR022405P-U            | Samples |

| DCR022405P-U/700 | ACTIVE | SOP          | DVS                | 10   | 700            | Pb-Free<br>(RoHS) | NIPDAU               | Level-3-260C-168 HR | 0 to 0       | DCR022405P-U            | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: Til defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

# **PACKAGE OPTION ADDENDUM**

6-Feb-2020

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 8-Dec-2017

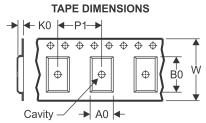

# TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

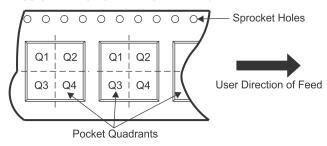

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device           | Package<br>Type | Package<br>Drawing |    | SPQ | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------------|-----------------|--------------------|----|-----|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| DCR022405P-U/700 | SOP             | DVS                | 10 | 700 | 330.0                    | 44.4                     | 10.85      | 23.5       | 5.25       | 16.0       | 44.0      | Q1               |

**PACKAGE MATERIALS INFORMATION**

www.ti.com 8-Dec-2017

#### \*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ | Length (mm) | Width (mm) | Height (mm) |

|------------------|--------------|-----------------|------|-----|-------------|------------|-------------|

| DCR022405P-U/700 | SOP          | DVS             | 10   | 700 | 346.0       | 346.0      | 61.0        |

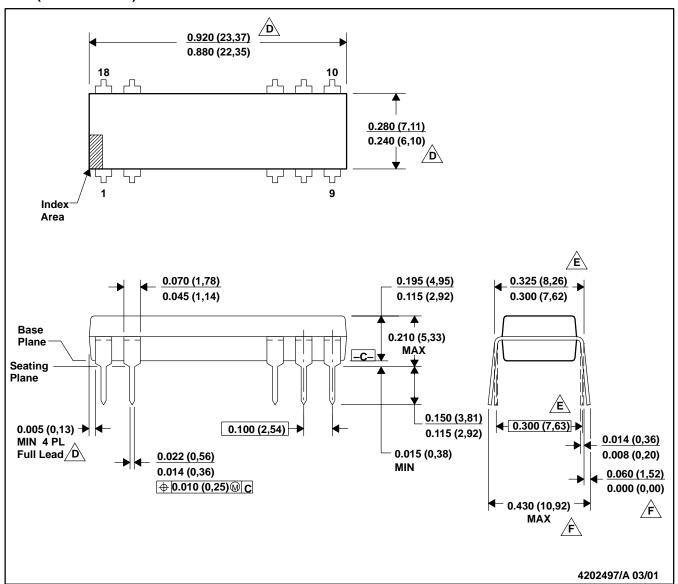

#### **NVE (R-PDIP-T10/18)**

## PLASTIC DUAL-IN-LINE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-001-AC with the exception of lead count.

- Dimensions do not include mold flash or protrusions.

Mold flash or protrusions shall not exceed 0.010 (0,25).

- Mold flash or protrusions shall not exceed 0.010 (0,25).

Dimensions measured with the leads constrained to be perpendicular to Datum C.

- Dimensions are measured at the lead tips with the leads unconstrained.

- G. A visual index feature must be located within the cross-hatched area.

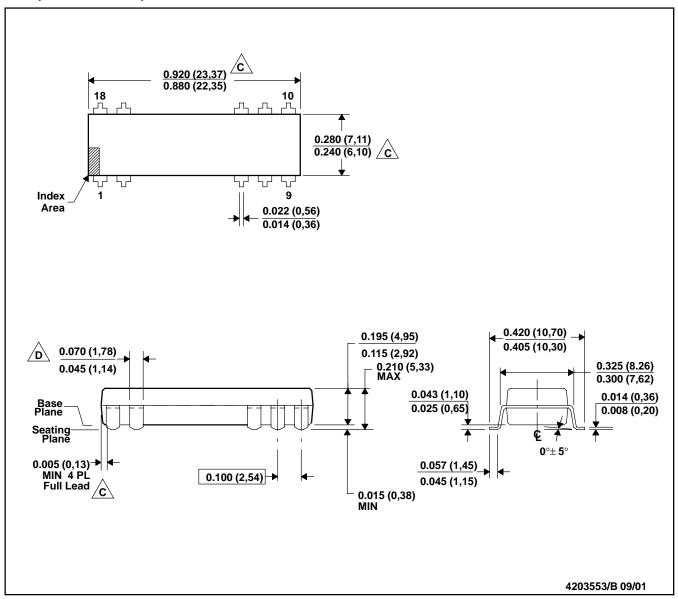

#### **DVS (R-PDSO-G10/18)**

#### PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

Dimensions do not include mold flash or protrusions.

Mold flash or protrusions shall not exceed 0.010 (0,25).

Maximum dimension does not include dambar protrusions. Dambar protrusions shall not exceed 0.010 (0,25)

- E. Distance between leads including dambar protrusions to be 0.005 (0,13) minimum.

- F. A visual index feature must be located within the cross–hatched area.

- G. For automatic insertion, any raised irregularity on the top surface (step, mesa, etc.) shall be symmetrical about the lateral and longitudinal package centerlines.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

Tl's products are provided subject to Tl's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such Tl products. Tl's provision of these resources does not expand or otherwise alter Tl's applicable warranties or warranty disclaimers for Tl products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated