# **KSZ9031MNX Silicon Errata & Data Sheet Clarification**

This document describes known silicon errata for the Microchip KSZ9031MNX device, which include the following variants:

- KSZ9031MNXCA

- KSZ9031MNXCC

- KSZ9031MNXIA

- KSZ9031MNXIC

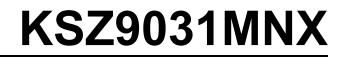

The silicon errata discussed in this document are for silicon revisions as listed in Table 1. The silicon revision can be determined by the device's top marking as indicated in Figure 1. A summary of KSZ9031MNX silicon errata is provided in Table 2.

#### TABLE 1: AFFECTED SILICON REVISIONS

| Part Numbers                                              | Silicon Revision |

|-----------------------------------------------------------|------------------|

| KSZ9031MNXCA, KSZ9031MNXCC,<br>KSZ9031MNXIA, KSZ9031MNXIC | A, A2, A4        |

**Note:** All future orders will be transitioning to silicon revision A4. Contact your local sales representative for additional information.

#### FIGURE 1: TOP MARKING DATE CODE INDICATION

**Note:** The purpose of Figure 1 is to detail the top markings of an example part and highlight the location of the silicon revision code. Other top marking values may differ (lot codes, location of manufacture, etc.).

#### TABLE 2: SILICON ISSUE SUMMARY

| ltem<br>Number | Silicon Issue Summary                                                                    | Affected Silicon<br>Revisions |

|----------------|------------------------------------------------------------------------------------------|-------------------------------|

| 1.             | Device fails to link after Asymmetric Pause capability is set                            | A, A2, A4                     |

| 2.             | Duty cycle variation for optional 125MHz reference output clock                          | A, A2, A4                     |

| 3.             | LED toggle is not visible for Tri-color Dual-LED Mode                                    | A, A2, A4                     |

| 4.             | Auto-Negotiation link-up failure / long link-up time due to default FLP interval setting | A, A2, A4                     |

| 5.             | Link failure after repeated unplugging/plugging of cable in forced 100BASE-TX mode       | A, A2, A4                     |

| 6.             | 6. 1000BASE-T Transmitter Jitter fails to meet IEEE compliance specification             |                               |

| 7.             | 1000BASE-T Transmitter Distortion fails to meet IEEE compliance specification            | A, A2, A4                     |

| 8.             | Transmitter common mode voltage drift at cold temperature                                | A, A2                         |

#### Silicon Errata Issues

#### Module 1: Device fails to link after Asymmetric Pause capability is set

#### DESCRIPTION

Whenever the device's Asymmetric Pause capability (Register 4h, Bit [11]) is set to 1, link-up may fail after a link-up to link-down transition (e.g., a cable disconnect).

#### END USER IMPLICATIONS

The device may fail to establish link when the Asymmetric Pause capability bit is set to 1.

#### Work around

Do not enable (set to 1) the Asymmetric Pause capability bit. If enabling this bit is required, a second link-up attempt (e.g., disconnect and reconnect cable) is required to establish link.

#### PLAN

This erratum will not be corrected in a future revision.

#### Module 2: Duty cycle variation for optional 125MHz reference output clock

#### DESCRIPTION

When the device links in the 1000BASE-T slave mode only, the optional 125MHz reference output clock (CLK125\_NDO, Pin 55) has wide duty cycle variation.

#### END USER IMPLICATIONS

The optional CLK125\_NDO clock does not meet the RGMII 45/55 percent (min/max) duty cycle requirement and therefore cannot be used directly by the MAC side for clocking applications that have setup/hold time requirements on rising and falling clock edges (e.g., to clock out RGMII transmit data from MAC to PHY (KSZ9031MNX device)).

#### Work around

Use an alternative external clock source for the MAC.

If an alternative clock source is not available, the CLK125\_NDO clock can be used with limitations. One solution requires the MAC side clock input to include an on-chip PLL that locks on the rising or falling edge of the CLK125\_NDO clock. Another solution requires the device to always operate in master mode (Register 9h, Bits [12:11] = '11') whenever there is 1000BASE-T link-up, which is workable only in those applications where the link partner is known and can always be configured to slave mode for 1000BASE-T.

#### PLAN

#### Module 3: LED toggle is not visible for Tri-color Dual-LED Mode

#### DESCRIPTION

In Tri-color Dual-LED mode, the LED[2:1] pin outputs toggle high pulses for transmit/receive activity indication. The high pulse width incorrectly tracks the activity data rate. At low data rate (e.g., one frame per second), the LED pin drives high (OFF) with a narrow high pulse width of about 640ns.

#### END USER IMPLICATIONS

Typically, the LED toggle rate should be <10Hz (100ms clock period or 50ms high pulse width) to be visible to the human eye. A 640ns pulse is not visible.

#### Work around

Use the Single-LED mode instead.

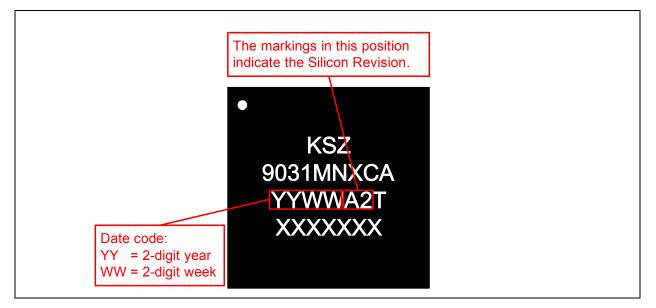

If Tri-color Dual-LED mode must be used, use a pulse stretching circuit to detect high narrow pulse widths down to 500ns and stretch them to the visible width (e.g., >50ms). The following Electronic Design web link article has a sample pulse stretching circuit:

http://electronicdesign.com/lighting/configurable-logic-chip-stretches-pulses-brighten-led-flash

Use the Input high / Output high configuration, as shown in Figure 2 from the Electronic Design link. The output high stretch time is set by the time constant (R1 \* C1).

# FIGURE 2: LED CONFIGURATION

#### PLAN

#### Module 4: Auto-Negotiation link-up failure / long link-up time due to default FLP interval setting

#### DESCRIPTION

The device's Auto-Negotiation FLP (Fast Link Pulse) burst-to-burst timing defaults to 8ms. IEEE Standard specifies this timing to be 16ms +/-8ms. Some link partners, such as Intel G-PHY controllers, were observed in bench tests to have tighter timing requirements that need to detect the FLP interval timing centered at 16ms.

#### END USER IMPLICATIONS

With the default 8ms FLP interval setting, intermittent link failure and long link-up time can occur with some link partners.

#### Work around

After device power-up/reset, change the FLP interval to 16ms using the following programming sequence to set MMD - Device Address 0h, Register 4h = 0x0006 and MMD - Device Address 0h, Register 3h = 0x1A80:

- a) Write Register Dh = 0x0000 //Set up register address for MMD Device Address 0h

- b) Write Register Eh = 0x0004 //Select Register 4h of MMD Device Address 0h

- c) Write Register Dh = 0x4000 //Select register data for MMD Device Address 0h, Register 4h

- d) Write Register Eh = 0x0006 //Write value 0x0006 to MMD Device Address 0h, Register 4h

- e) Write Register Dh = 0x0000 //Set up register address for MMD Device Address 0h

- f) Write Register Eh = 0x0003 //Select Register 3h of MMD Device Address 0h

- g) Write Register Dh = 0x4000 //Select register data for MMD Device Address 0h, Register 3h

- h) Write Register Eh = 0x1A80 //Write value 0x1A80 to MMD Device Address 0h, Register 3h

Then restart Auto-Negotiation for the 16ms FLP interval setting to take effect.

#### PLAN

This erratum will not be corrected in a future revision.

#### Module 5: Link failure after repeated unplugging/plugging of cable in forced 100BASE-TX mode

#### DESCRIPTION

With Auto-Negotiation disabled and the speed set to forced 100BASE-TX mode, the device can sometimes run into a failed link-up state where the device is in the link-down state and its link partner is in the link-up state. This link failure occurs if the device receive circuit does not get properly reset when the link status changes from link-up to link-down (e.g. cable is unplug), causing the next link-up attempt to fail when the cable is reconnected.

#### END USER IMPLICATIONS

When the device is set to forced 100BASE-TX mode, intermittent link failure can occur after repeated unplugging/ plugging of the cable.

#### Work around

Force a restart of the link-up process by causing the link partner to drop link and thereby cease its 100BASE-TX signal transmission to the device. When the 100BASE-TX receive signal is no longer detected, the device automatically generates a reset to its receive circuit to exit the link failure state and restart the link-up process.

#### PLAN

#### Module 6: 1000BASE-T Transmitter Jitter fails to meet IEEE compliance specification

#### DESCRIPTION

The device's 1000BASE-T Transmitter Jitter, Master Filtered (No TX\_TCLK Access) is in the 500-600ps range, versus the <300ps indicated in the IEEE specification.

#### END USER IMPLICATIONS

The device consumes an additional 200-300ps of the system's total jitter budget.

Link partners in properly designed systems that follow good Gigabit PHY design practices will not experience link drop and packet errors/losses that are attributed directly to the transmit jitter of the device. In lab testing and field testing, the device has shown to have neither link drop nor packet error/loss in continuous overnight runs (>12 hours) with 1000Mbps full-duplex traffic at 100% utilization. Table 3 provides a sampling of the overnight test results.

#### TABLE 3: SAMPLE OVERNIGHT TEST RESULTS

| Link Partners             | Continuous Overnight Run (>12 hours)      |                         |  |

|---------------------------|-------------------------------------------|-------------------------|--|

| Link Partners             | Short Cable (2 feet)                      | Long cable (100 meters) |  |

| KSZ9031 <=> KSZ9031       | No packet error/loss                      | No packet error/loss    |  |

| KSZ9031 <=> KSZ9021       | No packet error/loss                      | No packet error/loss    |  |

| KSZ9031 <=> LAN7800       | No packet error/loss                      | No packet error/loss    |  |

| KSZ9031 <=> LAN8810       | No packet error/loss No packet error/loss |                         |  |

| KSZ9031 <=> Netgear GS105 | No packet error/loss                      | No packet error/loss    |  |

Link partners in poorly designed systems will also typically exhibit poor receiver jitter tolerance. Here, link drops and packet errors/losses may be attributed to the receiver jitter tolerances of the link partners, not necessarily the transmit jitter of the device.

#### Work around

None.

PLAN

#### Module 7: 1000BASE-T Transmitter Distortion fails to meet IEEE compliance specification

#### DESCRIPTION

The device's 1000BASE-T Transmitter Distortion is in the 8-20mV range, versus the <10mV indicated in the IEEE specification.

#### END USER IMPLICATIONS

It is unlikely this specification failure will impact system performance. The following link to the Gigabit Transmit Distortion Testing document on the IEEE802.org website also questions the validity of this measurement:

http://www.ieee802.org/3/axay/public/may\_07/sefidvash\_1\_0507.pdf

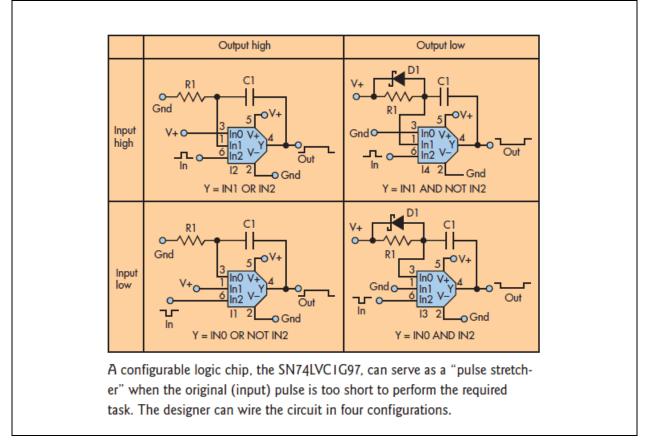

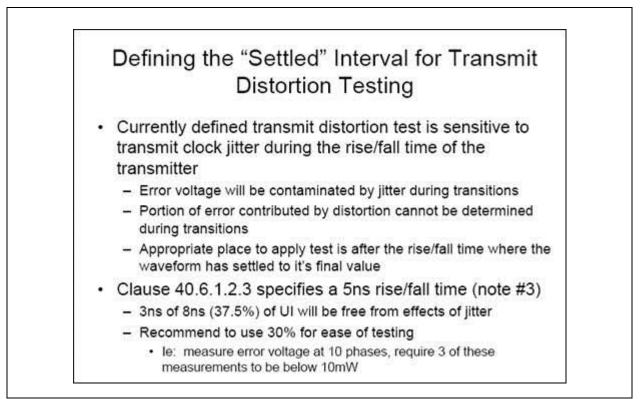

IEEE testing calls for <10mV peak transmitter distortion for at least 60% of the UI within the eye opening. However, this measurement might not be valid, as the transmit distortion test is sensitive to transmit jitter. Refer to the explanation below, taken from the aforementioned IEEE document.

The Gigabit Transmit Distortion Testing document indicates:

• On page 6, a contradiction between Transmit Jitter and Transmit Distortion requirements:

#### FIGURE 3: IEEE DOCUMENT PAGE 6

• On page 7:

- The transmit distortion test is sensitive to transmit clock jitter during the rise/fall time.

- It is recommended to change the requirement to use at least 30%, instead of at least 60%, of the UI within the eye opening for the <10mV peak transmitter distortion.

Extensive testing has been performed to ensure the device can inter-operate with different Gigabit PHY link partners. The following is a partial list of some of the Gigabit PHY link partners that have tested against the device and have passed interoperability testing.

| Link Partner                   |  |  |

|--------------------------------|--|--|

| 3Comm Corp. SuperStack 3 4050  |  |  |

| 3Comm Corp. SuperStack II 4900 |  |  |

| Agere Systems ET1310-EVB NIC   |  |  |

| Atheros AR8314 Switch          |  |  |

| Atheros AR8316 Switch          |  |  |

| Avaya 9640G IP Phone           |  |  |

| Broadcom BCM53115              |  |  |

| Broadcom BCM56218              |  |  |

| Broadcom BCM5650               |  |  |

| Coyote Point Systems E550si    |  |  |

| Coyote Point Systems E650gx    |  |  |

| Dell Power Connect 6224        |  |  |

| Extreme Networks Summit 1i     |  |  |

| HP ProCurve J9020A             |  |  |

#### TABLE 4: TESTED GIGABIT PHY LINK PARTNERS (CONTINUED)

| Link Partner                    |  |

|---------------------------------|--|

| Intel NetStructure 480T         |  |

| Polycom SoundPoint IP 670 Phone |  |

| Realtek RTL8368S+RTL8214        |  |

| Realtek RTL8369+RTL8212         |  |

| Realtek 8111C NIC               |  |

#### Work around

None.

#### PLAN

This erratum will not be corrected in a future revision.

#### Module 8: Transmitter common mode voltage drift at cold temperature

#### DESCRIPTION

Below 0<sup>o</sup>C, the voltage controlled output of the transmitter can become unstable and lead to distorted signaling. The voltage instability is common on both the TX+ and TX- lines, so the AC data is not affected unless the voltage drifts to the AVDDH level. If the common mode voltage drifts too close to AVDDH, the higher voltages will begin to clip, which can prevent successful Ethernet communication.

#### END USER IMPLICATIONS

There are two possible ways this issue may be seen:

- The device may exhibit communication issues (i.e., dropped link)

- · The device may not link or communicate

#### Work around

- Operate above 0°C

- · Contact your local sales representative for additional information

#### PLAN

This erratum has been corrected in silicon revision A4. All future orders will be transitioning to A4 devices. Contact your local sales representative for additional information.

### APPENDIX A: DOCUMENT REVISION HISTORY

| Revision Level & Date  | Section/Figure/Entry | Correction                                                                                                                                        |

|------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| DS80000691D (05-25-17) | Module 8.            | Updated module to indicate the erratum has been corrected in silicon revision A4.                                                                 |

|                        | Intro                | Added note: "All future orders will be transitioning to silicon revision A4. Contact your local sales representative for additional information." |

|                        | Table 2              | Added "Affected Silicon Revisions" column for clarity.                                                                                            |

|                        | All                  | Minor grammatical corrections.                                                                                                                    |

| DS80000691C (01-13-17) | Module 8.            | Added new erratum:                                                                                                                                |

|                        |                      | Transmitter common mode voltage drift at cold temperature                                                                                         |

| DS80000691B (07-26-16) | Module 6., Module 7. | Added new errata:                                                                                                                                 |

|                        |                      | 1000BASE-T Transmitter Jitter fails to meet<br>IEEE compliance specification                                                                      |

|                        |                      | 1000BASE-T Transmitter Distortion fails to meet IEEE compliance specification                                                                     |

| DS80000691A (03-16-16) | All                  | Initial release                                                                                                                                   |

# KSZ9031MNX

### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

### CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

#### Technical support is available through the web site at: http://microchip.com/support

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, AVR, AVR logo, AVR Freaks, BeaconThings, BitCloud, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KEELoQ, KEELoQ logo, Kleer, LANCheck, LINK MD, maXStylus, maXTouch, MediaLB, megaAVR, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, Prochip Designer, QTouch, RightTouch, SAM-BA, SpyNIC, SST, SST Logo, SuperFlash, tinyAVR, UNI/O, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, EtherSynch, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and Quiet-Wire are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, CryptoAuthentication, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, Mindi, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, QMatrix, RightTouch logo, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2017, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 9781522417538

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

China - Hong Kong SAR Tel: 852-2943-5100

Fax: 852-2401-3431 China - Nanjing Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-3326-8000 Fax: 86-21-3326-8021

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7830 Taiwan - Taipei

Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

Finland - Espoo Tel: 358-9-4520-820

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

France - Saint Cloud Tel: 33-1-30-60-70-00

**Germany - Garching** Tel: 49-8931-9700 **Germany - Haan** Tel: 49-2129-3766400

Germany - Heilbronn Tel: 49-7131-67-3636

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Germany - Rosenheim** Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Padova Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7289-7561

Poland - Warsaw Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Gothenberg Tel: 46-31-704-60-40

**Sweden - Stockholm** Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820