🖉 Order

Now

**CDCM7005**

Reference

Desian

SCAS793G -JUNE 2005-REVISED AUGUST 2017

# CDCM7005 3.3-V High Performance Clock Synchronizer and Jitter Cleaner

Technical

Documents

#### Features 1

- High Performance LVPECL and LVCMOS PLL Clock Synchronizer

- Two Reference Clock Inputs (Primary and Secondary Clock) for Redundancy Support With Manual or Automatic Selection

- Accepts LVCMOS Input Frequencies up to 200 • MHz

- VCXO IN Clock is Synchronized to One of the • Two Reference Clocks

- VCXO IN Frequencies Up to 2.2 GHz (LVPECL)

- Outputs Can Be a Combination of LVPECL and • LVCMOS (Up to Five Differential LVPECL Outputs or up to 10 LVCMOS Outputs)

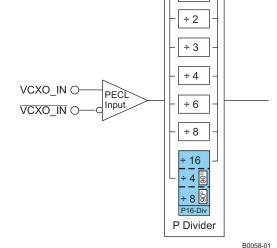

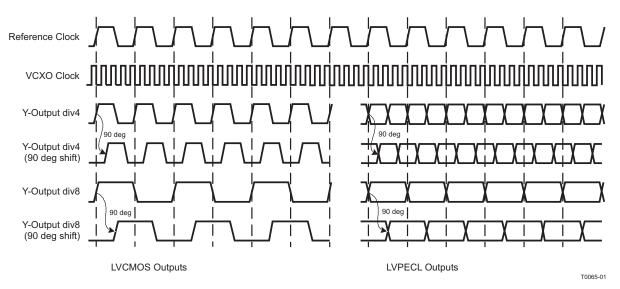

- Output Frequency is Selectable by x1, /2, /3, /4, /6, /8, /16 on Each Output Individually

- Efficient Jitter Cleaning From Low PLL Loop ٠ Bandwidth

- Low Phase Noise PLL Core

- Programmable Phase Offset (PRI\_REF and SEC\_REF to Outputs)

- Wide Charge Pump Current Range From 200 µA to 3 mA

- Dedicated Charge Pump Supply (VCC\_CP) for Wide Tuning Voltage Range VCOs

- Presets Charge Pump to VCC\_CP/2 for Fast ٠ Center-Frequency Setting of VC(X)O

- Analog and Digital PLL Lock Indication

- Provides VBB Bias Voltage Output for Single-• Ended Input Signals (VCXO\_IN)

- Frequency Hold-Over Mode Improves Fail-Safe ٠ Operation

- Power-up Control Forces LVPECL Outputs to 3-State at  $V_{CC}$  < 1.5 V

- SPI Controllable Device Setting

- 3.3-V Power Supply

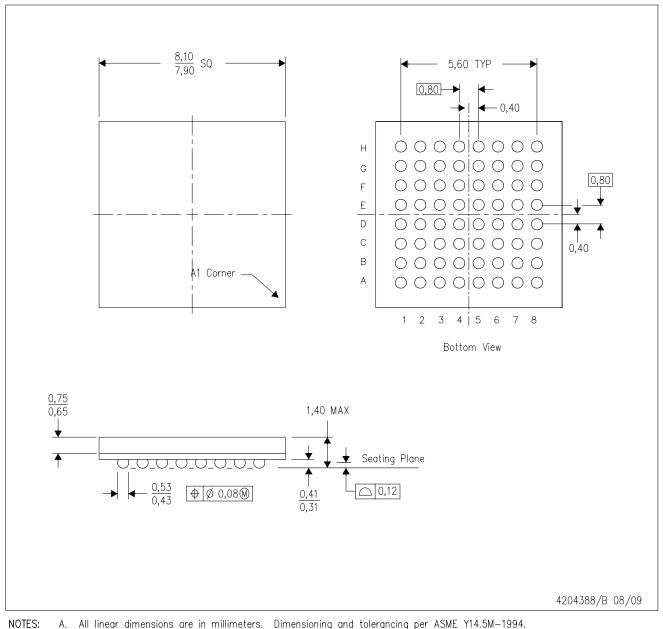

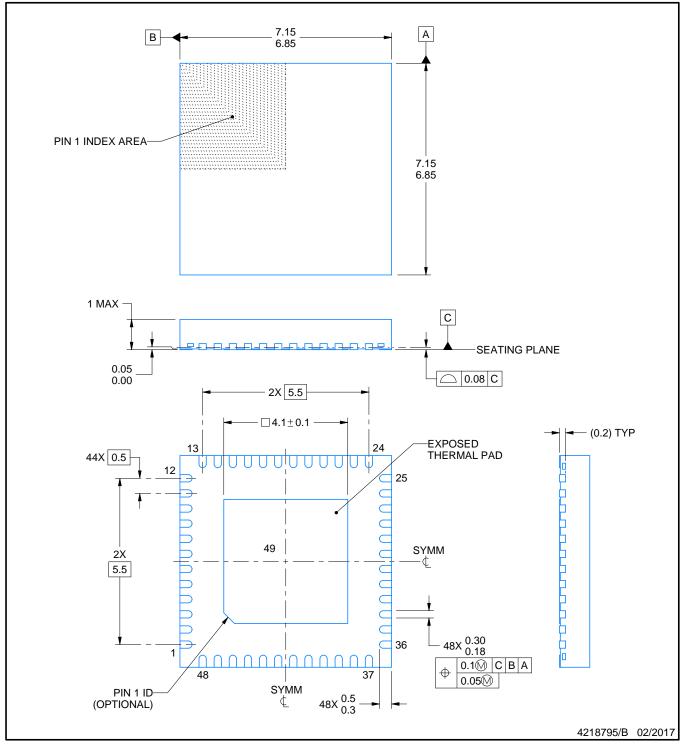

- Packaged in 64-Pin BGA (0.8 mm Pitch ZVA) or 48-Pin QFN (RGZ)

- Industrial Temperature Range -40°C to 85°C

#### Applications 2

- Wireless Infrastructure

- SONET

- Data Communication

- **Test Equipment**

# 3 Description

Tools &

Software

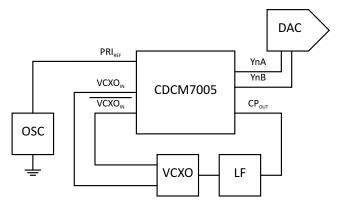

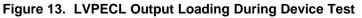

The CDCM7005 is a high-performance, low phase noise and low skew clock synchronizer that synchronizes a VCXO (voltage controlled crystal oscillator) or VCO (voltage controlled oscillator) frequency to one of the two reference clocks. The programmable pre-divider M and the feedbackdividers N and P give a high flexibility to the frequency ratio of the reference clock to VC(X)O

Support &

Community

2.2

VC(X)O\_IN clock operates up to 2.2 GHz. Through the selection of external VC(X)O and loop filter components, the PLL loop bandwidth and damping factor can be adjust to meet different system requirements.

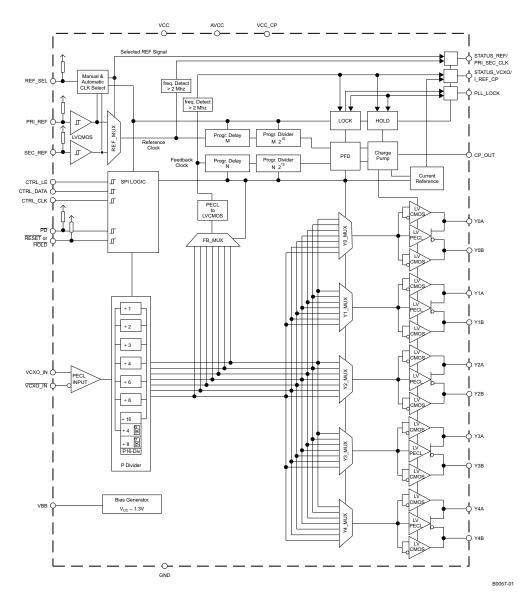

The CDCM7005 can lock to one of two reference clock inputs (PRI\_REF and SEC\_REF), supports frequency hold-over mode and fast-frequency-locking for fail-safe and increased system redundancy. The outputs of the CDCM7005 are user definable and can be any combination of up to five LVPECL outputs or 10 LVCMOS outputs. The built in up to synchronization latches ensure that all outputs are synchronized for low output skew.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |  |

|-------------|-----------|-------------------|--|

| CDCM7005    | VQFN (48) | 7.00 mm × 7.00 mm |  |

| CDCIVITUUD  | BGA (64)  | 8.00 mm × 8.00 mm |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

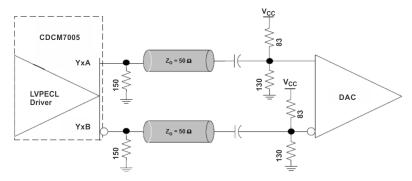

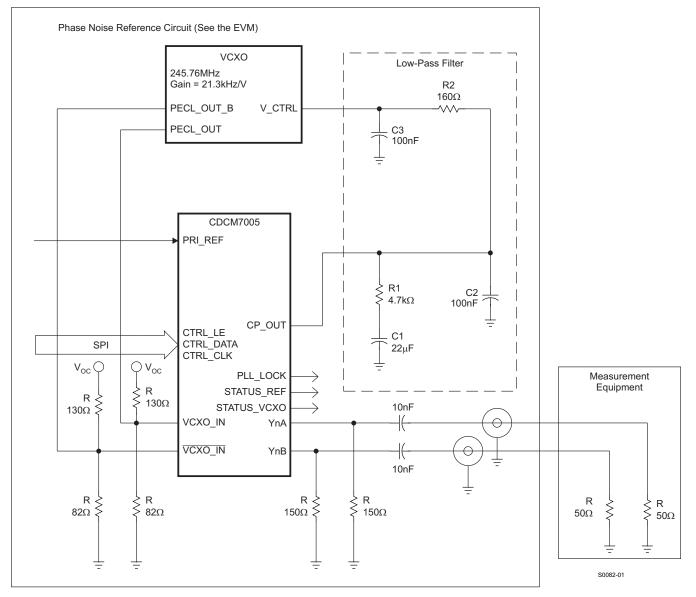

# **Typical Application Schematic**

# Table of Contents

| 1 | Feat | tures 1                            |

|---|------|------------------------------------|

| 2 | Арр  | lications 1                        |

| 3 | Des  | cription 1                         |

| 4 | Rev  | ision History 2                    |

| 5 | Des  | cription (continued) 4             |

| 6 | Pin  | Configuration and Functions 4      |

| 7 | Spe  | cifications7                       |

|   | 7.1  | Absolute Maximum Ratings 7         |

|   | 7.2  | ESD Ratings7                       |

|   | 7.3  | Recommended Operating Conditions 7 |

|   | 7.4  | Thermal Information 8              |

|   | 7.5  | Electrical Characteristics         |

|   | 7.6  | Timing Requirements 10             |

|   | 7.7  | Typical Characteristics 11         |

| 8 | Para | ameter Measurement Information 12  |

| 9 | Deta | ailed Description 15               |

|   | 9.1  | Overview 15                        |

|   | 9.2  | Functional Block Diagram 16        |

|    | 9.3   | Feature Description                             | 16 |

|----|-------|-------------------------------------------------|----|

|    | 9.4   | Device Functional Modes                         | 24 |

|    | 9.5   | Programming                                     | 25 |

| 10 | Арр   | lication and Implementation                     | 34 |

|    | 10.1  | Application Information                         | 34 |

|    | 10.2  | Typical Application                             | 37 |

| 11 | Pow   | ver Supply Recommendations                      | 40 |

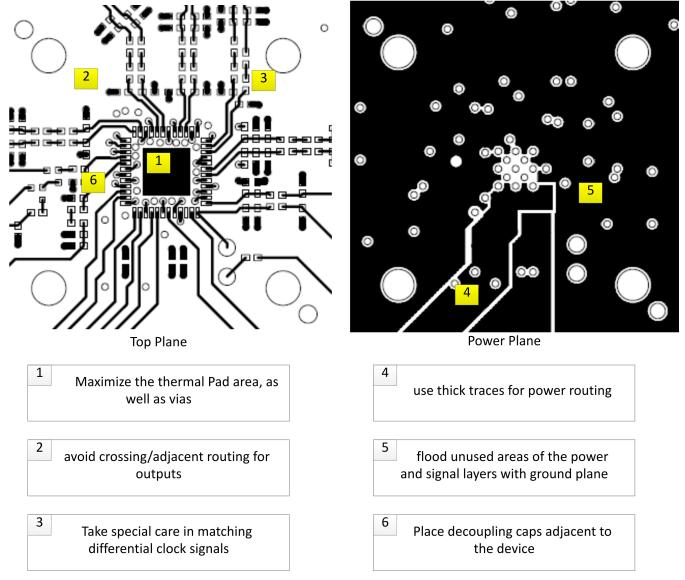

| 12 | Lay   | out                                             | 40 |

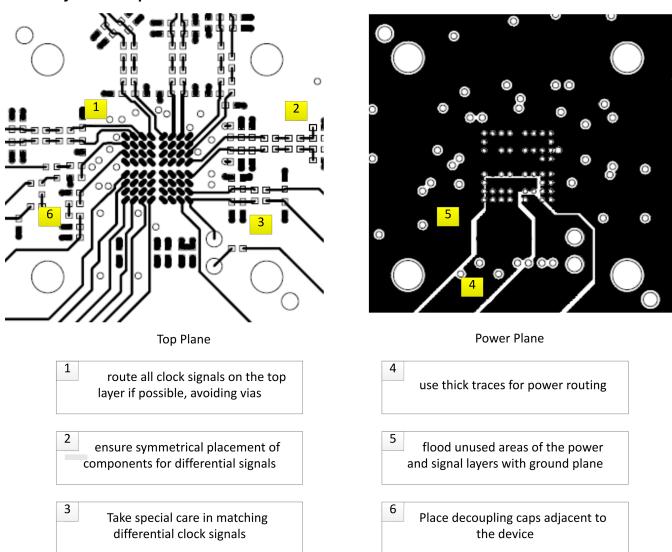

|    | 12.1  | Layout Guidelines                               | 40 |

|    | 12.2  | Layout Example                                  | 41 |

| 13 | Dev   | ice and Documentation Support                   | 43 |

|    | 13.1  | Receiving Notification of Documentation Updates | 43 |

|    | 13.2  | Community Resources                             | 43 |

|    | 13.3  | Trademarks                                      | 43 |

|    | 13.4  | Electrostatic Discharge Caution                 | 43 |

|    | 13.5  | Glossary                                        | 43 |

| 14 |       | hanical, Packaging, and Orderable               |    |

|    | Infor | mation                                          | 43 |

|    |       |                                                 |    |

# 4 Revision History

2

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| C | hanges from Revision F (July 2015) to Revision G                   | Page |

|---|--------------------------------------------------------------------|------|

| • | Removed duplicate row: PRI_SEC_CLK                                 | 5    |

| • | Changed text from: "STATUS_REF or" to: "STATUS_REF or PRI_SEC_CLK" | 6    |

#### Changes from Revision E (February 2013) to Revision F

Added Pin Configuration and Functions section, ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section

| C | hanges from Revision D (August 2009) to Revision E                                     | Page |

|---|----------------------------------------------------------------------------------------|------|

| • | Changed PLL_LOCK pin description, replaced cycle-slip text.                            | 5    |

| • | Changed the Frequency Hold-Over Mode section                                           | 22   |

| • | Changed text From: Cycle-Slip To: Frequency Offset in Figure 21                        | 23   |

| • | Changed Note 1 of table Word 3                                                         | 29   |

| • | Changed table Word 3, Cycle Slip (Bit 6) To: Frequency Offset                          | 29   |

| • | Changed table Lock-Detect Window (Word 3) - Clip slip To: Frequency offset, and Note 2 | 32   |

#### Changes from Revision C (December 2007) to Revision D

Submit Documentation Feedback

| • | Added text to the CTRL_CLK pin - Unused or floating inputs must be tied to proper logic level. A $20k\Omega$ or larger pull-up resistor to VCC is recommended.  | 4 |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| • | Added text to the CTRL_DATA pin - Unused or floating inputs must be tied to proper logic level. A $20k\Omega$ or larger pull-up resistor to VCC is recommended. | 4 |

| • | Added text to the CTRL_LE pin - Unused or floating inputs must be tied to proper logic level. A $20k\Omega$ or larger pull-up resistor to VCC is recommended.   | 4 |

| • | Added text to the $\overline{PD}$ pin - It is recommended to ramp up the $\overline{PD}$ with the same time as $V_{CC}$ and $AV_{CC}$ or later. The             |   |

# Texas Instruments

www.ti.com

Page

Page

Copyright © 2005–2017, Texas Instruments Incorporated

#### CDCM7005 SCAS793G – JUNE 2005 – REVISED AUGUST 2017

| ramp up rate of the $\overline{\text{PD}}$ should not be faster than the ramp up rate of V <sub>CC</sub> and AV <sub>CC</sub>                                                                                                                                                                                         | 5    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Changed VCC pin text From: 3.3-V supply. There is no internal connection between $V_{CC}$ and $AV_{CC}$ . It is recommended that $AV_{CC}$ use its own supply filter. To: 3.3-V supply. $V_{CC}$ and $AV_{CC}$ should always have the same supply voltage. It is recommended that $AV_{CC}$ use its own supply filter | 6    |

| Added text to the SPI CONTROL INTERFACE section - Unused or floating inputs must be tied to proper logic level.<br>A 20kΩ or larger pull–up resistor to VCC is recommended.                                                                                                                                           | . 25 |

| Added text to the SPI CONTROL INTERFACE section - It is recommended to program Word 0, Word 1, Word 2 and Word 3 right after power up and PD becomes HIGH.                                                                                                                                                            | . 25 |

| Changed From: RES To: GTME                                                                                                                                                                                                                                                                                            | . 29 |

| Changed From: RES To: PFDFC                                                                                                                                                                                                                                                                                           | . 29 |

|                                                                                                                                                                                                                                                                                                                       |      |

# Changes from Revision B (October 2005) to Revision C

| • | Changed N2, From: 1 To: 0 | 30 |

|---|---------------------------|----|

| • | Changed N3, From: 1 To: 0 | 30 |

| • | Changed N3, From: 1 To: 0 | 30 |

| • | Changed N2, From: 1 To: 0 | 30 |

## Changes from Revision A (June 2005) to Revision B

| Added minor updates. | 1 |

|----------------------|---|

|----------------------|---|

# Changes from Original (June 2005) to Revision A

| Changed da | sheet from Product Preview to Production data1 |

|------------|------------------------------------------------|

|------------|------------------------------------------------|

# Page

Page

# Page

CDCM7005 SCAS793G – JUNE 2005 – REVISED AUGUST 2017

# 5 Description (continued)

All device settings, like outputs signaling, divider value, and input selection are programmable by SPI (3-wire serial peripheral interface). SPI allows individually control of the device settings.

The device operates in 3.3-V environment and is characterized for operation from -40°C to 85°C.

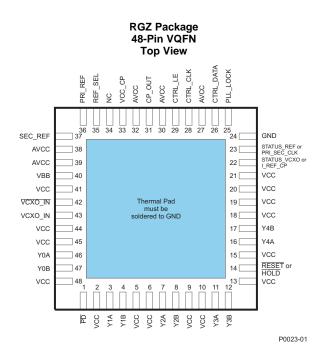

# 6 Pin Configuration and Functions

|   | Top View |         |        |        |         |          |               |                                      |

|---|----------|---------|--------|--------|---------|----------|---------------|--------------------------------------|

|   | 1        | 2       | 3      | 4      | 5       | 6        | 7             | 8                                    |

| A | PRI_REF  | REF_SEL | VCC_CP | CP_OUT | CTRL_LE | CTRL_CLK | CTRL_<br>DATA | PLL_LOCK                             |

| в | SEC_REF  | GND     | GND    | GND    | GND     | GND      | GND           | GND                                  |

| с | VBB      | GND     | AVCC   | AVCC   | AVCC    | AVCC     | AVCC          | STATUS_<br>REF or<br>PRI_SEC_<br>CLK |

| D | VCXO_IN  | GND     | GND    | GND    | GND     | GND      | VCC           | STATUS_<br>VCXO<br>or<br>I_REF_CP    |

| Е | VCXO_IN  | GND     | VCC    | VCC    | VCC     | VCC      | VCC           | vcc                                  |

| F | Y0A      | GND     | GND    | GND    | GND     | GND      | VCC           | Y4B                                  |

| G | Y0B      | VCC     | vcc    | vcc    | vcc     | vcc      | VCC           | Y4A                                  |

| н | PD       | Y1A     | Y1B    | Y2A    | Y2B     | Y3A      | Y3B           | RESET<br>or<br>HOLD                  |

**ZVA Package**

64-Pin BGA

P0022-01

#### Pin Functions

| PIN       |                                                                                                       | 1/0                          | DECODIDITION    |                                                                                                                                                                                                                            |  |

|-----------|-------------------------------------------------------------------------------------------------------|------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME      | BGA                                                                                                   | QFN                          | I/O             | DESCRIPTION                                                                                                                                                                                                                |  |

| AVCC      | C3, C4,<br>C5, C6,<br>C7                                                                              | 27, 30,<br>32, 38,<br>39     | Analog<br>Power | 3.3-V analog power supply. There is no internal connection between AV <sub>CC</sub> and V <sub>CC</sub> . It is recommended that AV <sub>CC</sub> use its own supply filter.                                               |  |

| CP_OUT    | A4                                                                                                    | 31                           | 0               | Charge pump output                                                                                                                                                                                                         |  |

| CTRL_CLK  | A6                                                                                                    | 28                           | I               | LVCMOS input, serial control clock input for SPI, with hysteresis. Unused or floating inputs must be tied to proper logic level. A 20kΩ or larger pull–up resistor to VCC is recommended.                                  |  |

| CTRL_DATA | A7                                                                                                    | 26                           | I               | LVCMOS input, serial control data input for SPI, with hysteresis. Unused or floating inputs must be tied to proper logic level. A $20k\Omega$ or larger pull-up resistor to VCC is recommended.                            |  |

| CTRL_LE   | A5                                                                                                    | 29                           | I               | LVCMOS input, control latch enable for serial programmable Interface (SPI), with hysteresis. Unused or floating inputs must be tied to proper logic level. A $20k\Omega$ or larger pull-up resistor to VCC is recommended. |  |

| GND       | B2, B3,<br>B4, B5,<br>B6, B7,<br>B8, C2,<br>D2, D3,<br>D4, D5,<br>D6, E2,<br>F2, F3,<br>F4, F5,<br>F6 | Thermal<br>pad and<br>pin 24 | Ground          | Ground                                                                                                                                                                                                                     |  |

# Pin Functions (continued)

|                | PIN |                                                                                                                                                                                                                                                                                                                                                               | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME           | BGA | QFN                                                                                                                                                                                                                                                                                                                                                           | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| HOLD           | H8  | is the default function. This pin is low active and can be activated<br>the corresponding bit in the SPI register. In case of RESET, the cl<br>is switched to 3-state and all counters (N, M, P) are reset to zero<br>settings are maintained in SPI registers). The LVPECL outputs are<br>high respectively and the LVCMOS outputs are all low or high if in |     | This LVCMOS input can be programmed (SPI) to act as HOLD or RESET. RESET is the default function. This pin is low active and can be activated external or via the corresponding bit in the SPI register. In case of RESET, the charge pump (CP) is switched to 3-state and all counters (N, M, P) are reset to zero (the initial divider settings are maintained in SPI registers). The LVPECL outputs are static low and high respectively and the LVCMOS outputs are all low or high if inverted. RESET is not edge triggered and should have a pulse duration of at least 5 ns.                                                                                                                                                      |

|                |     | 14                                                                                                                                                                                                                                                                                                                                                            |     | In case of HOLD, the CP is switched in to 3-state mode only. After HOLD is released and with the next valid reference clock cycle the charge pump is switched back in to normal operation (CP stays in 3-state as long as no reference clock is valid). During HOLD, the P divider and all outputs Yx are at normal operation. This mode allows an external control of the frequency hold-over mode.                                                                                                                                                                                                                                                                                                                                    |

|                |     |                                                                                                                                                                                                                                                                                                                                                               |     | The input has an internal 150-k $\Omega$ pullup resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                |     |                                                                                                                                                                                                                                                                                                                                                               |     | This LVCMOS output can be programmed (SPI) to provide either the STATUS_VCXO information or serve as current path for the charge pump (CP). STATUS_VCXO is the default setting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| I_REF_CP       | D8  | 22                                                                                                                                                                                                                                                                                                                                                            | 0   | In case of STATUS_VCXO, the LVCMOS output provides the status of the VCXO input (frequencies above 2 MHz are interpreted as valid clock; active high).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                |     |                                                                                                                                                                                                                                                                                                                                                               |     | In case of I_REF_CP, it provides the current path for the external reference resistor (12 k $\Omega$ ±1%) to support an accurate charge pump current, optional. Do not use any capacitor across this resistor to prevent noise coupling via this node. If the internal 12 k $\Omega$ is selected (default setting), this pin can be left open.                                                                                                                                                                                                                                                                                                                                                                                          |

| PD             | H1  | 1                                                                                                                                                                                                                                                                                                                                                             | I   | LVCMOS input, asynchronous power down ( $\overline{PD}$ ) signal. This pin is low active and can be activated external or by the corresponding bit in the SPI register (in case of logic high, the SPI setting is valid). Switches the device into power-down mode. Resets M- and N-Divider, 3-states charge pump, STATUS_REF, or PRI_SEC_CLK pin, STATUS_VCXO or I_REF_CP pin, PLL_LOCK pin, VBB pin and all Yx outputs. Sets the SPI register to default value; has internal 150-k $\Omega$ pullup resistor. It is recommended to ramp up the PD with the same time as V <sub>CC</sub> and AV <sub>CC</sub> or later. The ramp up rate of the PD should not be faster than the ramp up rate of V <sub>CC</sub> and AV <sub>CC</sub> . |

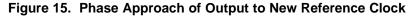

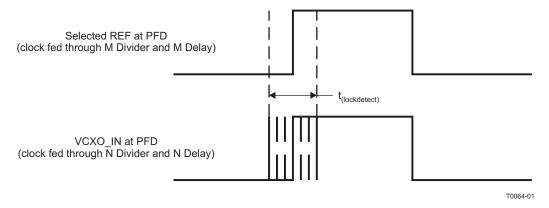

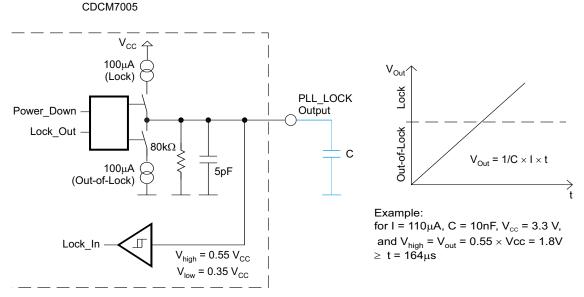

|                |     |                                                                                                                                                                                                                                                                                                                                                               |     | LVCMOS output for PLL_LOCK information. This pin is set high if the PLL is in lock (see feature description). This output can be programmed to be digital lock detect or analog lock detect (see feature description).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                |     | 05                                                                                                                                                                                                                                                                                                                                                            | 1/0 | The PLL is locked (set high), if the rising edge either of PRI_REF or SEC_REF clock and VCXO_IN clock at the phase frequency detector (PFD) are inside the lock detect window for a predetermined number of successive clock cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PLL_LOCK A8 25 |     | 25                                                                                                                                                                                                                                                                                                                                                            | I/O | The PLL is out-of-lock (set low), if the rising edge of either the PRI_REF or SEC_REF) clock and VCXO_IN clock at the PFD are outside the lock detect window or if a certain frequency offset between reference frequency and feedback frequency (VCXO) is detected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                |     |                                                                                                                                                                                                                                                                                                                                                               |     | Both, the lock detect window and the number of successive clock cycles are user definable (via SPI).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PRI_REF        | A1  | 36                                                                                                                                                                                                                                                                                                                                                            | I   | LVCMOS input for the primary reference clock, with an internal 150-k $\Omega$ pullup resistor and input hysteresis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| REF_SEL        | A2  | 35                                                                                                                                                                                                                                                                                                                                                            | 1   | LVCMOS reference clock selection input. In the manual mode the REF_SEL signal selects one of the two input clocks:<br>REF_SEL [1]: PRI_REF is selected;<br>REF_SEL [0]: SEC_REF is selected;<br>The input has an internal 150-k $\Omega$ pullup resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

CDCM7005 SCAS793G – JUNE 2005 – REVISED AUGUST 2017

www.ti.com

Texas Instruments

# Pin Functions (continued)

| PIN                                                 |                                                                                                                                                                                                                                                                                                      | I/O                                                                      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                | BGA                                                                                                                                                                                                                                                                                                  | QFN                                                                      | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                          |

| RESET                                               | is the default function. This pin is low active and can be<br>the corresponding bit in the SPI register. In case of RE<br>is switched to 3-state and all counters (N, M, P) are res<br>settings are maintained in SPI registers). The LVPECL<br>high respectively and the LVCMOS outputs are all low |                                                                          | This LVCMOS input can be programmed (SPI) to act as HOLD or RESET. RESET is the default function. This pin is low active and can be activated external or via the corresponding bit in the SPI register. In case of RESET, the charge pump (CP) is switched to 3-state and all counters (N, M, P) are reset to zero (the initial divider settings are maintained in SPI registers). The LVPECL outputs are static low and high respectively and the LVCMOS outputs are all low or high if inverted. RESET is not edge triggered and should have a pulse duration of at least 5 ns. |                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                     |                                                                                                                                                                                                                                                                                                      |                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | In case of HOLD, the CP is switched in to 3-state mode only. After HOLD is released and with the next valid reference clock cycle the charge pump is switched back in to normal operation (CP stays in 3-state as long as no reference clock is valid). During HOLD, the P divider and all outputs Yx are at normal operation. This mode allows an external control of the frequency hold-over mode. |

|                                                     |                                                                                                                                                                                                                                                                                                      |                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | The input has an internal 150-k $\Omega$ pullup resistor.                                                                                                                                                                                                                                                                                                                                            |

| SEC_REF                                             | B1                                                                                                                                                                                                                                                                                                   | 37                                                                       | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LVCMOS input for the secondary reference clock, with an internal 150-k $\Omega$ pullup resistor and input hysteresis.                                                                                                                                                                                                                                                                                |

|                                                     |                                                                                                                                                                                                                                                                                                      |                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | This output can be programmed (SPI) to provide either the STATUS_REF or PRI_SEC_CLK information. This pin is set high if one of the STATUS conditions is valid. STATUS_REF is the default setting.                                                                                                                                                                                                   |

| STATUS_REF or<br>PRI_SEC_CLK                        | C8                                                                                                                                                                                                                                                                                                   | 23                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | In case of STATUS_REF, the LVCMOS output provides the Status of the Reference Clock. If a reference clock with a frequency above 2 MHz is provided to PRI_REF or SEC_REF STATUS_REF will be set high.                                                                                                                                                                                                |

|                                                     |                                                                                                                                                                                                                                                                                                      |                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | In case of PRI_SEC_CLK, the LVCMOS output indicates whether the primary clock [high] or the secondary clock [low] is selected.                                                                                                                                                                                                                                                                       |

|                                                     |                                                                                                                                                                                                                                                                                                      |                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | This LVCMOS output can be programmed (SPI) to provide either the STATUS_VCXO information or serve as current path for the charge pump (CP). STATUS_VCXO is the default setting.                                                                                                                                                                                                                      |

| STATUS_VCXO                                         | D8                                                                                                                                                                                                                                                                                                   | 22                                                                       | Ο                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | In case of STATUS_VCXO, the LVCMOS output provides the status of the VCXO input (frequencies above 2 MHz are interpreted as valid clock; active high).                                                                                                                                                                                                                                               |

|                                                     |                                                                                                                                                                                                                                                                                                      |                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | In case of I_REF_CP, it provides the current path for the external reference resistor (12 k $\Omega \pm 1\%$ ) to support an accurate charge pump current, optional. Do not use any capacitor across this resistor to prevent noise coupling via this node. If the internal 12 k $\Omega$ is selected (default setting), this pin can be left open.                                                  |

| VBB                                                 | C1                                                                                                                                                                                                                                                                                                   | 40                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Bias voltage output to be used to bias unused complementary input $VCXO_{IN}$ for single ended signals. The output of VBB is $V_{CC} - 1.3$ V. The output current is limited to about 1.5 mA.                                                                                                                                                                                                        |

| VCC                                                 | D7, E3,<br>E4, E5,<br>E6, E7,<br>E8, F7,<br>G2, G3,<br>G4, G5,<br>G6, G7                                                                                                                                                                                                                             | 2, 5, 6,<br>9, 10,<br>13, 15,<br>18, 19,<br>20, 21,<br>41, 44,<br>45; 48 | Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3.3-V supply. $V_{CC}$ and $AV_{CC}$ should always have the same supply voltage. It is recommended that $AV_{CC}$ use its own supply filter.                                                                                                                                                                                                                                                         |

| VCC_CP                                              | A3                                                                                                                                                                                                                                                                                                   | 33                                                                       | Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | This is the charge pump power supply pin used to have the same supply as the external VCO. It can be set from 2.3 V to 3.6 V.                                                                                                                                                                                                                                                                        |

| VCXO_IN                                             | E1                                                                                                                                                                                                                                                                                                   | 43                                                                       | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | VCXO LVPECL input                                                                                                                                                                                                                                                                                                                                                                                    |

| VCXO_IN                                             | D1                                                                                                                                                                                                                                                                                                   | 42                                                                       | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Complementary VCXO LVPECL input                                                                                                                                                                                                                                                                                                                                                                      |

| Y0A:Y0B<br>Y1A:Y1B<br>Y2A:Y2B<br>Y3A:Y3B<br>Y4A:Y4B | F1, G1,<br>H2, H3,<br>H4, H5,<br>H6, H7,<br>G8, F8                                                                                                                                                                                                                                                   | 46, 47,<br>3, 4,<br>7, 8,<br>11,12,<br>16, 17                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | The outputs of the CDCM7005 are user definable and can be any combination of up to five LVPECL outputs or up to 10 LVCMOS outputs. The outputs are selectable via SPI (Word 1, Bit 2-6). The power-up setting is all outputs are LVPECL.                                                                                                                                                             |

# 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                               |                                                               | MIN  | MAX            | UNIT |

|-------------------------------|---------------------------------------------------------------|------|----------------|------|

| $V_{CC}, A_{VCC}, V_{CC\_CP}$ | Supply voltage <sup>(2)</sup>                                 | -0.5 | 4.6            | V    |

| VI                            | Input voltage <sup>(3)</sup>                                  | -0.5 | $V_{CC} + 0.5$ | V    |

| Vo                            | Output voltage <sup>(3)</sup>                                 | -0.5 | $V_{CC} + 0.5$ | V    |

| I <sub>OUT</sub>              | Output current for LVPECL/LVCMOS outputs $(0 < V_O < V_{CC})$ |      | ±50            | mA   |

| I <sub>IN</sub>               | Input current ( $V_I < 0$ , $V_I > V_{CC}$ )                  |      | ±20            | mA   |

| TJ                            | Maximum junction temperature                                  |      | 125            | °C   |

| T <sub>stg</sub>              | Storage temperature                                           | -65  | 150            | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All supply voltages have to be supplied at the same time.

(3) The input and output negative voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

# 7.2 ESD Ratings

|                    |                         |                                                                                       | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>                     | ±2500 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 $^{\left( 2\right) }$ | ±1500 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

|                      |                                                                | MIN                 | NOM | MAX                  | UNIT |

|----------------------|----------------------------------------------------------------|---------------------|-----|----------------------|------|

| $V_{CC}$ , $AV_{CC}$ | Supply voltage                                                 | 3                   | 3.3 | 3.6                  | V    |

| V <sub>CC_CP</sub>   | Supply voltage                                                 | 2.3                 |     | $V_{CC}$             | v    |

| V <sub>IL</sub>      | Low-level input voltage LVCMOS, see (1)                        |                     |     | $0.3 V_{CC}$         | V    |

| V <sub>IH</sub>      | High-level input voltage LVCMOS, see <sup>(1)</sup>            | 0.7 V <sub>CC</sub> |     |                      | V    |

| I <sub>OH</sub>      | High-level output current LVCMOS (includes all status pins)    |                     |     | -8                   | mA   |

| I <sub>OL</sub>      | Low-level output current LVCMOS (includes all status pins)     |                     |     | 8                    | mA   |

| VI                   | Input voltage range LVCMOS                                     | 0                   |     | 3.6                  | V    |

| V <sub>INPP</sub>    | Input amplitude LVPECL $(V_{VCXO_{IN}} - V_{VCXO_{IN}})^{(2)}$ | 0.5                 |     | 1.3                  | V    |

| V <sub>IC</sub>      | Common-mode input voltage LVPECL                               | 1                   |     | V <sub>CC</sub> -0.3 | V    |

| T <sub>A</sub>       | Operating free-air temperature                                 | -40                 |     | 85                   | °C   |

(1)  $V_{IL}$  and  $V_{IH}$  are required to maintain ac specifications; the actual device function tolerates a smaller input level of 1V, if an ac-coupling to  $V_{CC}/2$  is provided.

(2) V<sub>INPP</sub> minimum and maximum is required to maintain ac specifications; the actual device function tolerates at a minimum V<sub>INPP</sub> of 150 mV.

#### **CDCM7005**

SCAS793G - JUNE 2005 - REVISED AUGUST 2017

www.ti.com

## 7.4 Thermal Information

|                               |                                              |     |                                           |         | CDCM7005     |      |  |

|-------------------------------|----------------------------------------------|-----|-------------------------------------------|---------|--------------|------|--|

| THERMAL METRIC <sup>(1)</sup> |                                              | -   | RGZ ZVA<br>AIRFLOW AIRFLOW<br>(lfm) (m/s) |         | ZVA<br>(BGA) | UNIT |  |

|                               |                                              | ()  | (11/3)                                    | 48 PINS | 64 PINS      |      |  |

|                               |                                              | 0   | 0                                         | 29.9    | 53.9         |      |  |

| Р                             | Junction-to-ambient thermal resistance       | 150 | 1                                         | 24.7    | 49.8         | °C/W |  |

| $R_{	heta JA}$                |                                              | 250 | 2                                         | 23.2    | 48.5         | C/VV |  |

|                               |                                              | 500 | -                                         | 21.5    | _            |      |  |

| R <sub>0JC(top)</sub>         | Junction-to-case (top) thermal resistance    | t.  | •                                         | 22.4    | 28.3         | °C/W |  |

| $R_{\theta JB}$               | Junction-to-board thermal resistance         |     |                                           | 14.2    | 38.6         | °C/W |  |

|                               |                                              | 0   | 0                                         | 0.2     | 0.7          |      |  |

|                               |                                              | 150 | 1                                         | 0.2     | 0.7          |      |  |

| ΨЈТ                           | Junction-to-top characterization parameter   | 250 | 2                                         | 0.2     | 0.8          | °C/W |  |

|                               |                                              | 500 | -                                         | 0.3     | _            |      |  |

| Ψјв                           | Junction-to-board characterization parameter |     |                                           | -       | _            | °C/W |  |

| $R_{\theta JC(bot)}$          | Junction-to-case (bottom) thermal resistance |     |                                           |         |              | °C/W |  |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 7.5 Electrical Characteristics

over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER              |                                                                                 | TEST CONDITIONS                                                                                                                                                                                                                                           | MIN TYP <sup>(1)</sup> | MAX  | UNIT |

|------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|------|

| OVERALL                |                                                                                 |                                                                                                                                                                                                                                                           |                        |      |      |

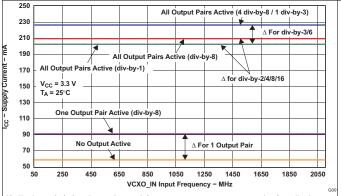

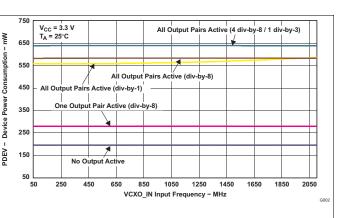

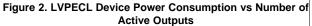

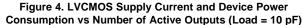

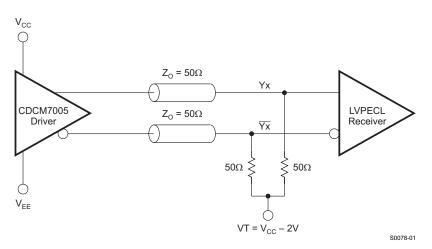

| I <sub>CC_LVPECL</sub> | Supply current (I <sub>CC</sub> over frequency see                              | $      f_{VCXO} = 245.76 \text{ MHz}, \\       f_{REF\_IN} = 30.72 \text{ MHz}, \\       PFD = 240 \text{ kHz}, \text{ I}_{CP} = 2 \text{ mA, all outputs are LVPECL} \\       and Div-by-8 (load, see Figure 13) $                                       | 210                    | 260  | mA   |

| I <sub>CC_LVCMOS</sub> | Figure 1 through Figure 4)                                                      | $      f_{VCXO} = 245.76 \text{ MHz}, \\       f_{REF\_IN} = 30.72 \text{ MHz}, \\       PFD = 240 \text{ kHz}, \text{ I}_{CP} = 2 \text{ mA}, \text{ All outputs are} \\       LVCMOS \text{ and Div-by-8 (load, 10 pF)} $                               | 120                    | 150  | mA   |

| I <sub>CCPD</sub>      | Power-down current                                                              | $ \begin{split} f_{\text{IN}} &= 0 \text{ MHz},  V_{\text{CC}} = 3.6 \text{ V},  \text{AV}_{\text{CC}} = 3.6 \text{ V}, \\ \text{V}_{\text{CC}\_\text{CP}} &= 3.6 \text{ V}, \\ \text{V}_{\text{I}} &= 0 \text{ V or } \text{V}_{\text{CC}} \end{split} $ | 100                    | 300  | μΑ   |

|                        | High-impedance state output current for Yx                                      | $V_{O} = 0 \text{ V or } V_{CC} - 0.8 \text{ V}$                                                                                                                                                                                                          |                        | ±40  | μA   |

| l <sub>oz</sub>        | outputs                                                                         | $V_{O} = 0 V \text{ or } V_{CC}$                                                                                                                                                                                                                          |                        | ±100 | μA   |

| V <sub>I_REF_CP</sub>  | Voltage on I_REF_CP (external current path<br>for accurate charge pump current) | 12 k $\Omega$ to GND at pin D8 (BGA), pin 22 (QFN)                                                                                                                                                                                                        | 1.21                   |      | V    |

| V <sub>BB</sub>        | Output reference voltage                                                        | $V_{CC} = 3 V - 3.6 V; I_{BB} = -0.2 mA$                                                                                                                                                                                                                  | V <sub>CC</sub> -1.3   |      | V    |

| Co                     | Output capacitance for Yx                                                       | $V_{CC}$ = 3.3 V, $V_O$ = 0 V or $V_{CC}$                                                                                                                                                                                                                 | 2                      |      | pF   |

| 0                      | Input capacitance at PRI_REF and SEC_REF                                        | $V_{I} = 0 V \text{ or } V_{CC}, V_{I} = 0 V \text{ or } V_{CC}$                                                                                                                                                                                          | 2.7                    |      | - 5  |

| CI                     | Input capacitance at CTRL_LE,<br>CTRL_CLOCK, CTRL_DATA                          | $V_{I} = 0 V \text{ or } V_{CC}$                                                                                                                                                                                                                          | 2                      |      | pF   |

| LVCMOS                 |                                                                                 | •                                                                                                                                                                                                                                                         |                        |      |      |

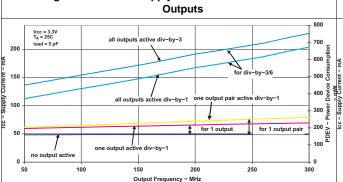

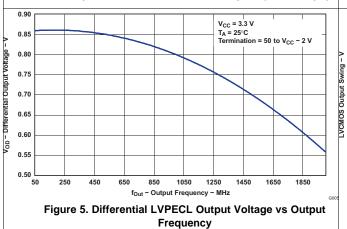

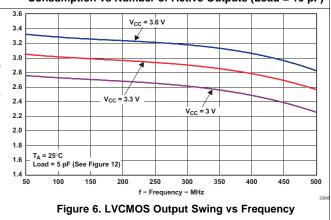

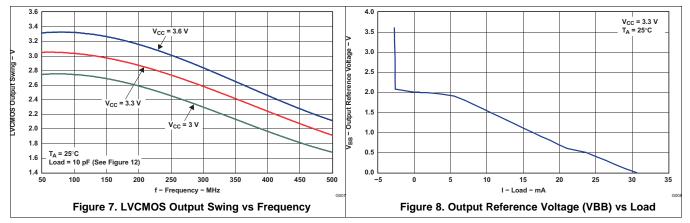

| f <sub>clk</sub>       | Output frequency, see <sup>(2)</sup> , <sup>(3)</sup> , Figure 6, and Figure 7  | Load = 5 pF to GND, 1 k $\Omega$ to V <sub>CC</sub> , 1 k $\Omega$ to GND                                                                                                                                                                                 |                        | 250  | MHz  |

| V <sub>IK</sub>        | LVCMOS input clamp voltage                                                      | $V_{CC} = 3 V, I_I = -18 mA$                                                                                                                                                                                                                              |                        | -1.2 | V    |

| I <sub>I</sub>         | LVCMOS input current for CTRL_LE,<br>CTRL_CLK, CTRL_DATA                        | $V_{I} = 0 V \text{ or } V_{CC}, V_{CC} = 3.6 V$                                                                                                                                                                                                          |                        | ±5   | μA   |

(1) All typical values are at  $V_{CC}$  = 3.3 V, temperature = 25°C.

(2) f<sub>clk</sub> can be up to 400 MHz in the typical operating mode (25°C / 3.3-V V<sub>CC</sub>). The total power consumption limit of 700 mW for the BGA package can be violated if several LVCMOS outputs switch at high frequency (see Figure 3 and Figure 4).

(3) Operating the LVCMOS or LVPECL output above the maximum frequency will not cause a malfunction to the device, but the output signal swing may no longer meet the output specification.

## **Electrical Characteristics (continued)**

over recommended operating free-air temperature range (unless otherwise noted)

|                                 | PARAMETER                                                                                        | TEST CONDITIONS                                                             | MIN                   | TYP <sup>(1)</sup> | MAX                       | UNIT |

|---------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------|--------------------|---------------------------|------|

| I <sub>IH</sub>                 | LVCMOS input current for PD, RESET,<br>HOLD, REF_SEL, PRI_REF, SEC_REF,<br>(see <sup>(4)</sup> ) | $V_{I} = V_{CC}, V_{CC} = 3.6 \text{ V}$                                    |                       |                    | 5                         | μA   |

| IIL                             | LVCMOS input current for PD, RESET,<br>HOLD, REF_SEL, PRI_REF, SEC_REF,<br>(see <sup>(4)</sup> ) | V <sub>I</sub> = 0 V, V <sub>CC</sub> = 3.6 V                               | -15                   |                    | -35                       | μA   |

|                                 |                                                                                                  | $V_{CC}$ = min to max,<br>$I_{OH}$ = -100 $\mu$ A                           | V <sub>CC</sub> -0.1  |                    |                           |      |

| V <sub>он</sub>                 | High-level output voltage for LVCMOS<br>outputs                                                  | $V_{CC} = 3 \text{ V}, I_{OH} = -6 \text{ mA}$                              | 2.4                   |                    |                           | V    |

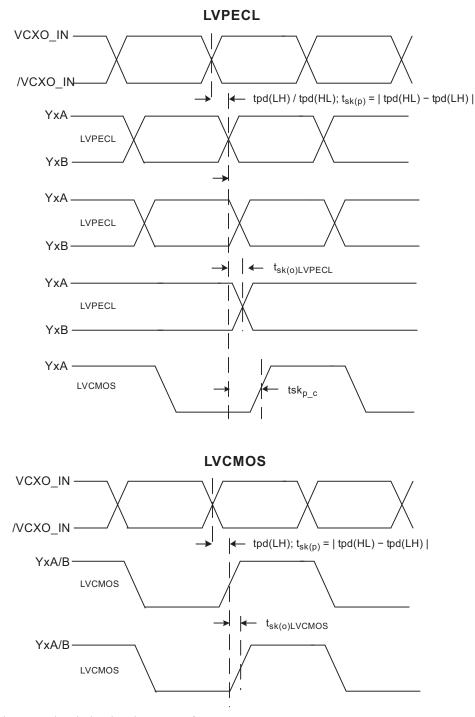

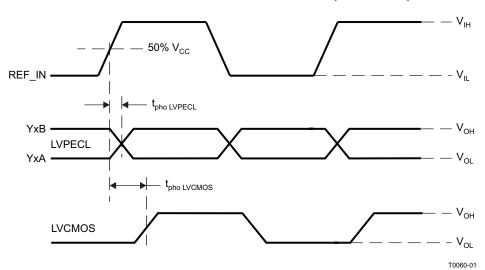

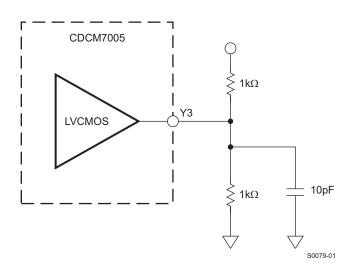

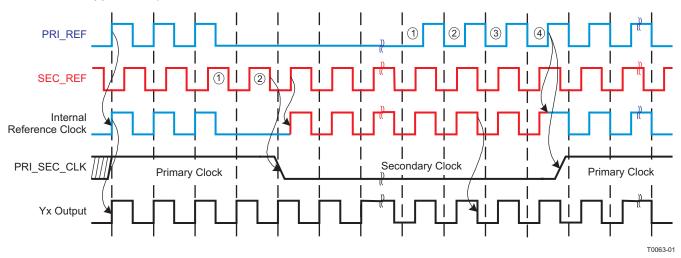

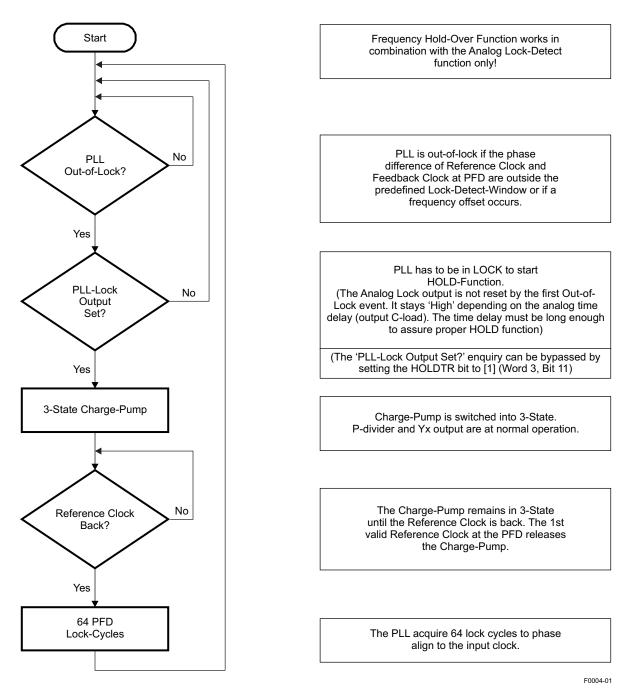

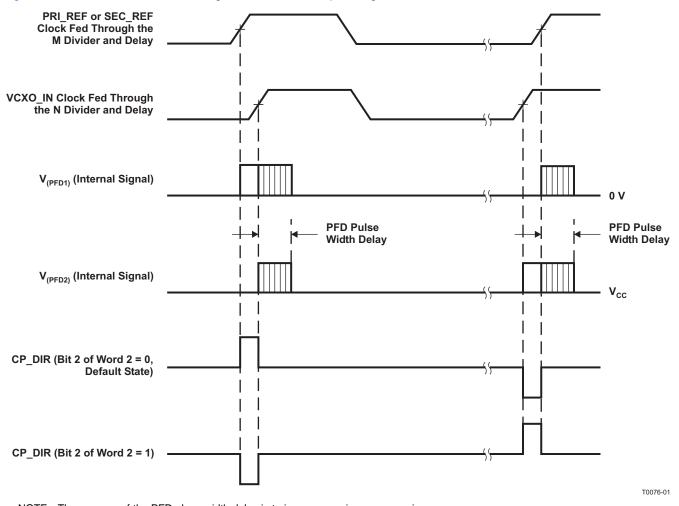

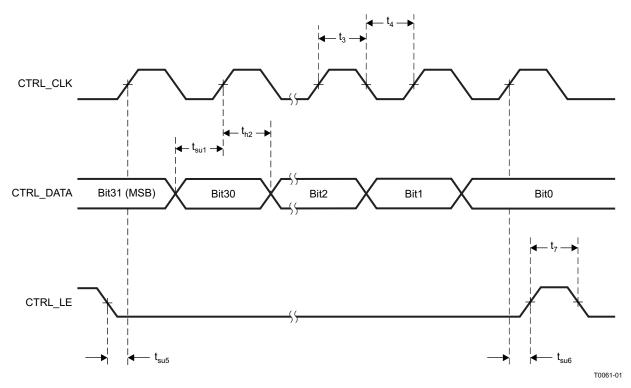

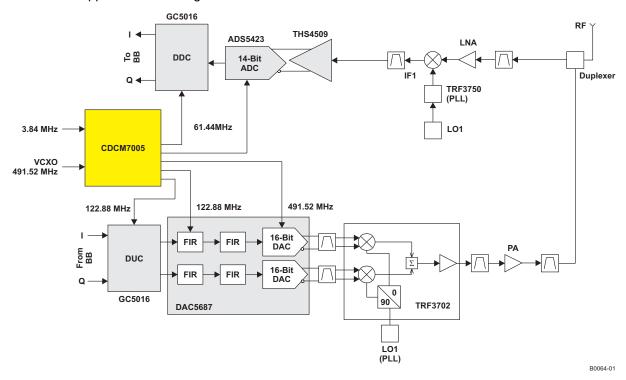

|                                 | ouputo                                                                                           | $V_{CC} = 3 \text{ V}, I_{OH} = -12 \text{ mA}$                             | 2.1                   |                    |                           |      |