# Ultra-Low Quiescent Current, Low Noise 3.5W Buck-Boost Regulator

## **General Description**

The MAX20343/MAX20344 is an ultra-low quiescent current, non-inverting buck-boost converter with 1A current capability at 3.5V intended for applications that require long run times while also demanding bursts of high current. The device employs a unique control algorithm which seamlessly transitions between buck, buck-boost, and boost modes, minimizing discontinuities and subharmonics in the output voltage ripple. The low 1.9V input voltage for startup allows users to power the device from a variety of sources, and the near-zero minimum operating voltage gives the user the ability to extract as much as possible from their energy source. The MAX20343/MAX20344 has also been designed to keep inductance and output capacitance requirements as low as possible for space-constrained applications.

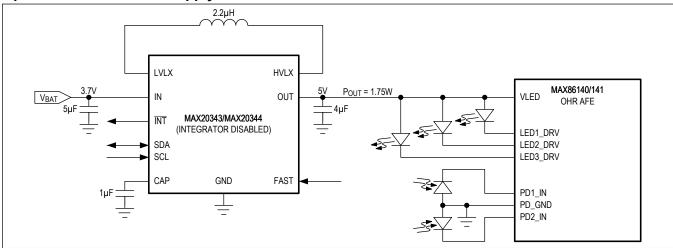

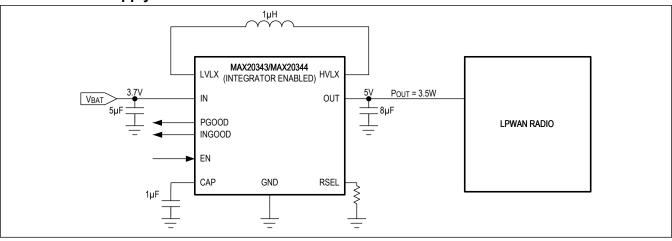

The MAX20343/MAX20344 is ideal for power in optical sensor applications as well as for powering radios in low power, wide area network (LPWAN) applications since in both cases noise must be minimal and efficiency must be high. For instance, the small light-load output voltage ripple allows a photoplethysmography (PPG) system to operate at low LED currents without interference. Additionally, seamless transitions between operating modes enables the use of dynamic voltage scaling (DVS) to minimize headroom on the LED and to save power in such systems. In applications where a low-power-density battery must be buffered by a super-capacitor to provide large LPWAN type bursts of current, the ultra-low operating voltage of the MAX20343/MAX20344 allows the user to extract as much energy as possible from the super capacitor. The low output inductance/capacitance requirement allows a small total solution size. For example in PPG systems, this provides the flexibility to place the MAX20343/ MAX20344 on a remote optical module if overcrowding on the main PCB is an issue.

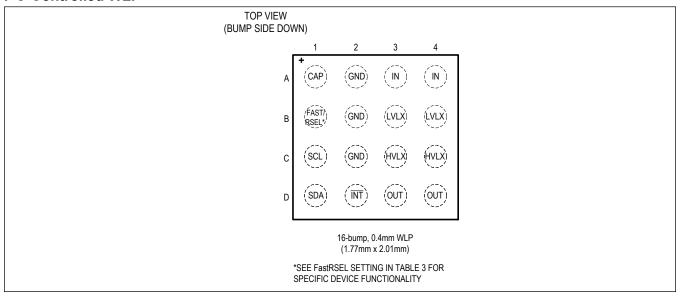

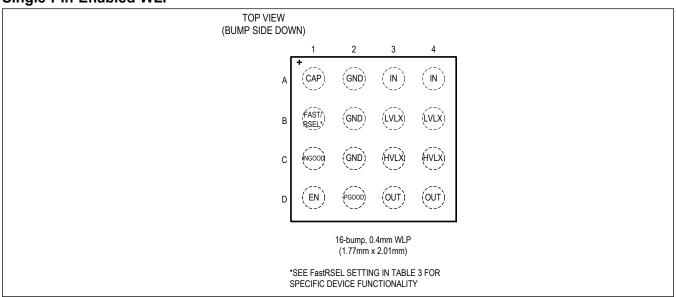

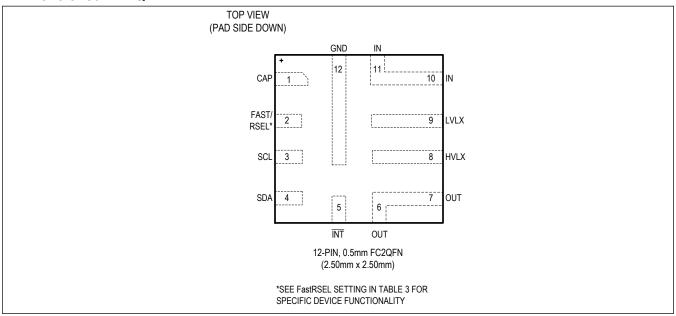

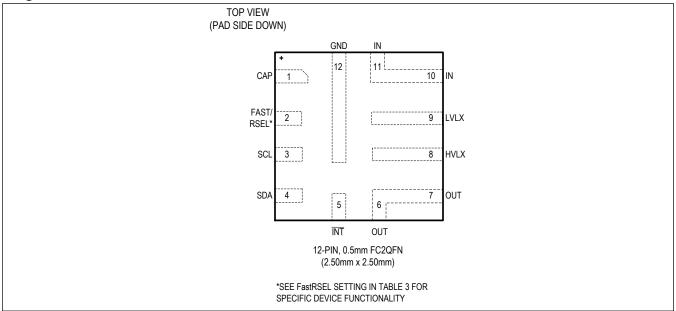

The MAX20343/MAX20344 is available with a highly configurable I $^2$ C serial interface or as a single-pin-enabled fixed-programming version. See <u>Table 3</u> for specific device settings. MAX20343 operates over the -40°C to +85°C temperature range, is available in a 16-bump, 1.77mm x 2.01mm, 0.4mm pitch WLP package and a 12-pin, 2.50mm x 2.50mm, 0.5mm pitch FC2QFN package. MAX20344 operates over the -40°C to +125°C temperature range, and is available in a 12-pin, 2.50mm x 2.50mm, 0.5mm pitch FC2QFN package.

## **Applications**

• Biometric Optical Sensing Including PPG

- LPWAN (LTE/NB-IoT, LTE/Cat-M1)

- InT

- Industrial Sensors

#### **Benefits and Features**

- Extend System Run Time

- Ultra-Low, 3.5µA (typ) Quiescent Current

- 250mW Ouptut Power with 500mV Input Voltage

- Dynamic Voltage Scaling (DVS)

- · Low, Continuous Noise Profile

- Eliminates Discontinuities Across Operating Voltage Range

- Eliminates Post-Filtering LDO in Noise Sensitive Applications

- Adaptable Load Transient Response

- Adjustable Peak Current for Optimal Performance in Each Application

- Fast Load Transient Response Minimizes Settling Time

- · Optional Feedback Integrator

- Enable for up to 3.5W Output Power Capabilities

- Disable for up to 1.75W Output Power and Faster Load Transient Settling Time

- FAST Pin Pretriggers Load Response and Offers Improved Load Transient

- Flexible Control Options

- I<sup>2</sup>C Interface with Status Interrupts

- EN and Status Pins, Single-Resistor V<sub>OUT</sub> Selection (RSEL)

- See Table 3 for specific device defaults.

- Extended Operating Temperature from -40°C to +85°C (MAX20343), -40°C to +125°C (MAX20344)

- Optimally Sized for Small Applications

- 16-bump, 1.77mm x 2.01mm, 0.4mm Pitch WLP

- 12-pin, 2.50mm x 2.50mm, 0.5mm Pitch Flip-Chip OFN

- Inductor/Capacitor Available in 0603/0402 Case Sizes

Ordering Information appears at end of datasheet.

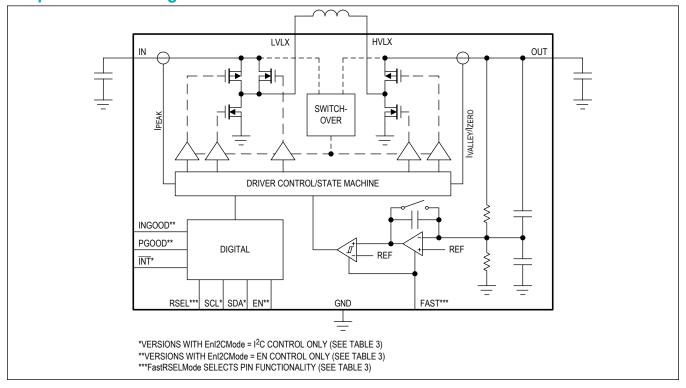

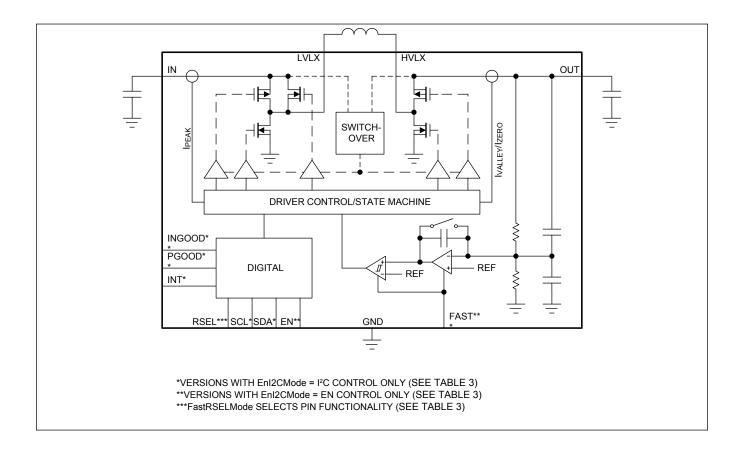

## **Simplified Block Diagram**

## **TABLE OF CONTENTS**

| General Description.       1         Applications.       1         Benefits and Features.       1         Simplified Block Diagram       2         Absolute Maximum Ratings.       7         Package Information       7         16-BUMP WLP.       7         12-Pin FC2QFN       7         Electrical Characteristics       8         Typical Operating Characteristics       81         Pin Configurations       16         I <sup>2</sup> C-Controlled WLP       16         Single-Pin-Enabled WLP       16         Single-Pin-Enabled WLP       16         I <sup>2</sup> C-Controlled FC2QFN       17         Single-Pin-Enabled FC2QFN       17         Single-Pin-Enabled FC2QFN       17         Pin Description       18         Functional Diagram       20         Functional Diagram       20         Detailed Description       21         Startup Voltage       21         Architectural Description       21         Switching Phases       21         Buck-Bost Mode       21         Buck-Only Mode       22         Inductor Peak and Valley Current Limits       22         Input Operating Power and Other Optim                                                       | Constal Description                            |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|----|

| Benefits and Features         1           Simplified Block Diagram         2           Absolute Maximum Ratings         7           Package Information         7           16-BUMP WLP         7           12-Pin FC2QFN         7           Electrical Characteristics         8           Typical Operating Characteristics         81           Pin Configurations         16           I <sup>2</sup> C-Controlled WLP         16           Single-Pin-Enabled WLP         16           Single-Pin-Enabled FC2QFN         17           Single-Pin-Enabled FC2QFN         17           Pin Description         18           Functional Diagram         20           Functional Diagram         20           Etailed Description         21           Startup Voltage         21           Architectural Description         21           Switching Phases         21           Buck-Boost Mode         22           Buck-Only Mode         22           Inductor Peak and Valley Current Limits         22           Inductor Peak and Valley Current Limits         22           Inductor Peak and Valley Current Limits         22           Inductor Peak and Valley Current Limits | ·                                              |    |

| Simplified Block Diagram       2         Absolute Maximum Ratings       7         Package Information       7         16-BUMP WLP       7         12-Pin FC2QFN       7         Electrical Characteristics       8         Typical Operating Characteristics       11         Pin Configurations       16         i?C-Controlled WLP       16         Single-Pin-Enabled WLP       16         i?C-Controlled FC2QFN       17         Single-Pin-Enabled FC2QFN       17         Pin Description       18         Functional Diagram       20         Detailed Description       21         Startup Voltage       21         Architectural Description       21         Switching Phases       21         Buck-Boost Mode       21         Buck-Only Mode       22         Inductor Peak and Valley Current Limits       22         Inductor Operating Voltage       23         Output Operating Voltage       23         Output Operating Power and Other Optimizations       24         Device Control       24         Incomplex Pin-Enable       25         Dynamic Voltage Sealing (DVS)       25                                                                                      | ••                                             |    |

| Absolute Maximum Ratings.       7         Package Information       7         16-BUMP WLP       7         12-Pin FC2QFN       7         Electrical Characteristics       8         Typical Operating Characteristics       11         Pin Configurations       16         I <sup>2</sup> C-Controlled WLP       16         Single-Pin-Enabled WLP       16         I <sup>2</sup> C-Controlled FC2QFN       17         Single-Pin-Enabled WLP       16         I <sup>2</sup> C-Controlled FC2QFN       17         Single-Pin-Enabled FC2QFN       17         Pin Description       18         Functional Diagram       20         Functional Diagram       20         Detailed Description       21         Startup Voltage.       21         Architectural Description       21         Switching Phases       21         Buck-Boost Mode       21         Buck-Only Mode       22         Inductor Peak and Valley Current Limits       22         Input Operating Voltage       23         Output Operating Power and Other Optimizations       24         Device Control       24         Incompanie Voltage Scaling (DVS)       25 <t< td=""><td></td><td></td></t<>                 |                                                |    |

| Package Information       7         16-BUMP WLP       7         12-Pin FC2QFN       7         Electrical Characteristics       8         Typical Operating Characteristics       11         Pin Configurations       16         I <sup>2</sup> C-Controlled WLP       16         Single-Pin-Enabled WLP       16         I <sup>2</sup> C-Controlled FC2QFN       17         Single-Pin-Enabled FC2QFN       17         Pin Description       18         Functional Diagram       20         Functional Diagram       20         Detailed Description       21         Startup Voltage       21         Architectural Description       21         Switching Phases       21         Buck-Boost Mode       21         Buck-Boost Mode       21         Buck-Only Mode       22         Inductor Peak and Valley Current Limits       22         Integrator Control Loop Disable       23         Input Operating Power and Other Optimizations       24         Device Control       24         Single-Pin-Enable       25         Dynamic Voltage Scaling (DVS)       25         RSEL Voltage Setting       25         Register Map                                                       | ·                                              |    |

| 16-BUMP WLP.       7         12-Pin FC2QFN       7         Electrical Characteristics       8         Typical Operating Characteristics       11         Pin Configurations       16         if <sup>2</sup> C-Controlled WLP       16         Single-Pin-Enabled WLP       16         if <sup>2</sup> C-Controlled FC2QFN       17         Single-Pin-Enabled FC2QFN       17         Pin Description       18         Functional Diagram       20         Functional Diagram       20         Detailed Description       21         Startup Voltage       21         Architectural Description       21         Switching Phases       21         Buck-Boost Mode       21         Buck-Boost Mode       22         Inductor Peak and Valley Current Limits       22         Input Operating Voltage       23         Output Operating Voltage       23         Output Operating Power and Other Optimizations       24         12C-Controlled       24         12C-Controlled       24         12C-Controlled       24         2FUDY Controlled       25         Dynamic Voltage Scaling (DVS)       25         RESEL Voltage Set                                                       | ·                                              |    |

| 12-Pin FC2QFN       7         Electrical Characteristics       8         Typical Operating Characteristics       11         Pin Configurations       16         I²C-Controlled WLP       16         Single-Pin-Enabled WLP       16         I²C-Controlled FC2QFN       17         Single-Pin-Enabled FC2QFN       17         Single-Pin-Enabled FC2QFN       17         Pin Description       18         Functional Diagram       20         Functional Diagram       20         Detailed Description       21         Startup Voltage       21         Architectural Description       21         Switching Phases       21         Buck-Boost Mode       22         Buck-Boost Mode       22         Buck-Only Mode       22         Inductor Peak and Valley Current Limits       22         Integrator Control Loop Disable       23         Input Operating Power and Other Optimizations       24         Device Control       24         1/2C-Controlled       24         Single-Pin-Enable       25         Dynamic Voltage Scaling (DVS)       25         RSEL Voltage Setting       25         Regi                                                                             | -                                              |    |

| Electrical Characteristics       8         Typical Operating Characteristics       11         Pin Configurations       16         I <sup>2</sup> C-Controlled WLP       16         Single-Pin-Enabled WLP       16         I <sup>2</sup> C-Controlled FC2QFN       17         Single-Pin-Enabled FC2QFN       17         Pin Description       18         Functional Diagram       20         Functional Diagram       20         Detailed Description       21         Startup Voltage       21         Architectural Description       21         Switching Phases       21         Buck-Boost Mode       21         Buck-Boost Mode       22         Inductor Peak and Valley Current Limits       22         Integrator Control Loop Disable       23         Input Operating Voltage       23         Output Operating Power and Other Optimizations       24         1 <sup>2</sup> C-Controlled       24         Single-Pin-Enable       25         Dynamic Voltage Scaling (DVS)       25         RESL Voltage Setting       25         Register Map       28         MMX2034/MAX20344       28         Applications Information       34 <td></td> <td></td>                     |                                                |    |

| Typical Operating Characteristics       11         Pin Configurations       16         I²C-Controlled WLP       16         Single-Pin-Enabled WLP       16         I²C-Controlled FC2QFN       17         Single-Pin-Enabled FC2QFN       17         Single-Pin-Enabled FC2QFN       17         Pin Description       18         Functional Diagram       20         Functional Diagram       20         Detailed Description       21         Startup Voltage       21         Architectural Description       21         Switching Phases       21         Buck-Boost Mode       21         Buck-Boost Mode       21         Buck-Only Mode       22         Inductor Peak and Valley Current Limits       22         Integrator Control Loop Disable       23         Input Operating Voltage       23         Output Operating Power and Other Optimizations       24         I²C-Controlled       24         Single-Pin-Enable       25         Dynamic Voltage Scaling (DVS)       25         RSEL Voltage Setting       25         Register Map       28         MAX20344MAX20344       28         Appl                                                                             |                                                |    |

| Pin Configurations       16         I²C-C-Controlled WLP       16         Single-Pin-Enabled WLP       16         I²C-Controlled FC2QFN       17         Single-Pin-Enabled FC2QFN       17         Pin Description       18         Functional Diagram       20         Functional Diagram       20         Edailed Description       21         Startup Voltage       21         Architectural Description       21         Switching Phases       21         Buck-Boost Mode       21         Buck-Only Mode       21         Inductor Peak and Valley Current Limits       22         Integrator Control Loop Disable       23         Input Operating Voltage       23         Output Operating Power and Other Optimizations       24         Device Control       24         I²C-Controlled       24         Single-Pin-Enable       25         Dynamic Voltage Scaling (DVS)       25         Register Map       28         MAX20343/MAX20344       28         Register Details       28         Applications Information       34                                                                                                                                                 |                                                |    |

| I²C-Controlled WLP       16         Single-Pin-Enabled WLP       16         I²C-Controlled FC2QFN       17         Single-Pin-Enabled FC2QFN       17         Pin Description       18         Functional Diagram       20         Functional Diagram       20         Functional Diagram       20         Startup Voltage       21         Architectural Description       21         Switching Phases       21         Buck-Boost Mode       21         Buck-Boost Mode       22         Inductor Peak and Valley Current Limits       22         Integrator Control Loop Disable       23         Input Operating Voltage       23         Output Operating Power and Other Optimizations       24         Device Control       24         I²C-Controlled       24         Single-Pin-Enable       25         Dynamic Voltage Scaling (DVS)       25         RSEL Voltage Setting       25         Register Map       28         MAX20343/MAX20344       28         Register Details       28         Applications Information       34                                                                                                                                                 |                                                |    |

| Single-Pin-Enabled WLP       16         I²C-Controlled FC2QFN       17         Single-Pin-Enabled FC2QFN       17         Pin Description       18         Functional Diagram       20         Functional Diagram       20         Detailed Description       21         Startup Voltage       21         Architectural Description       21         Switching Phases       21         Buck-Boost Mode       21         Buck-Only Mode       22         Inductor Peak and Valley Current Limits       22         Integrator Control Loop Disable       23         Input Operating Voltage       23         Output Operating Power and Other Optimizations       24         Device Control       24         I²C-Controlled       24         Single-Pin-Enable       25         Dynamic Voltage Scaling (DVS)       25         RSEL Voltage Setting       25         Register Map       28         MAX20343/MAX20344       28         Applications Information       34          Applications Information       34                                                                                                                                                                           |                                                |    |

| IPC-Controlled FC2QFN       17         Single-Pin-Enabled FC2QFN       17         Pin Description       18         Functional Diagram       20         Functional Diagram       20         Functional Diagram       20         Functional Diagram       20         Detailed Description       21         Startup Voltage       21         Architectural Description       21         Switching Phases       21         Buck-Boost Mode       21         Buck-Boost Mode       21         Buck-Only Mode       22         Inductor Peak and Valley Current Limits       22         Integrator Control Loop Disable       23         Input Operating Voltage       23         Output Operating Power and Other Optimizations       24         Device Control       24         I <sup>2</sup> C-Controlled       24         Single-Pin-Enable       25         Dynamic Voltage Scaling (DVS)       25         RSEL Voltage Setting       25         Register Map       28         MAX20343/MAX20344       28         Applications Information       34                                                                                                                                        |                                                |    |

| Single-Pin-Enabled FC2QFN       17         Pin Description       18         Functional Diagram       20         Functional Diagram       20         Detailed Description       21         Startup Voltage       21         Architectural Description       21         Switching Phases       21         Buck-Boost Mode       21         Buck-Only Mode       22         Inductor Peak and Valley Current Limits       22         Integrator Control Loop Disable       23         Input Operating Voltage       23         Output Operating Power and Other Optimizations       24         Device Control       24         I?C-Controlled       24         Single-Pin-Enable       25         Dynamic Voltage Scaling (DVS)       25         RSEL Voltage Setting       25         Register Map       28         MAX20343/MAX20344       28         Register Details       28         Applications Information       34                                                                                                                                                                                                                                                                   | ·                                              |    |

| Pin Description       18         Functional Diagram       20         Functional Diagram       20         Detailed Description       21         Startup Voltage       21         Architectural Description       21         Switching Phases       21         Buck-Boost Mode       21         Buck-Only Mode       22         Inductor Peak and Valley Current Limits       22         Integrator Control Loop Disable       23         Input Operating Voltage       23         Output Operating Power and Other Optimizations       24         Device Control       24         I <sup>2</sup> C-Controlled       24         Single-Pin-Enable       25         Dynamic Voltage Scaling (DVS)       25         RSEL Voltage Setting       25         Register Map       28         MAX20343/MAX20344       28         Register Details       28         Applications Information       34                                                                                                                                                                                                                                                                                                 | I <sup>2</sup> C-Controlled FC2QFN             | 17 |

| Functional Diagram       20         Functional Diagram       20         Detailed Description       21         Startup Voltage.       21         Architectural Description       21         Switching Phases       21         Buck-Boost Mode       21         Buck-Only Mode       22         Inductor Peak and Valley Current Limits       22         Integrator Control Loop Disable       23         Input Operating Voltage       23         Output Operating Power and Other Optimizations       24         Device Control       24         I <sup>2</sup> C-Controlled       24         Single-Pin-Enable       25         Dynamic Voltage Scaling (DVS)       25         RSEL Voltage Setting       25         Register Map       28         MAX20343/MAX20344       28         Register Details       28         Applications Information       34                                                                                                                                                                                                                                                                                                                                 | Single-Pin-Enabled FC2QFN                      | 17 |

| Functional Diagram       20         Detailed Description       21         Startup Voltage       21         Architectural Description       21         Switching Phases       21         Buck-Boost Mode       21         Buck-Only Mode       22         Inductor Peak and Valley Current Limits       22         Integrator Control Loop Disable       23         Input Operating Voltage       23         Output Operating Power and Other Optimizations       24         Device Control       24         I²C-Controlled       24         Single-Pin-Enable       25         Dynamic Voltage Scaling (DVS)       25         RSEL Voltage Setting       25         Register Map       28         MAX20343/MAX20344       28         Register Details       28         Applications Information       34                                                                                                                                                                                                                                                                                                                                                                                   | Pin Description                                | 18 |

| Detailed Description       21         Startup Voltage       21         Architectural Description       21         Switching Phases       21         Buck-Boost Mode       21         Buck-Only Mode       22         Inductor Peak and Valley Current Limits       22         Integrator Control Loop Disable       23         Input Operating Voltage       23         Output Operating Power and Other Optimizations       24         Device Control       24         Single-Pin-Enable       25         Dynamic Voltage Scaling (DVS)       25         RSEL Voltage Setting       25         Register Map       28         MAX20343/MAX20344       28         Register Details       28         Applications Information       34                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Functional Diagram                             | 20 |

| Startup Voltage       21         Architectural Description       21         Switching Phases       21         Buck-Boost Mode       21         Buck-Only Mode       22         Inductor Peak and Valley Current Limits       22         Integrator Control Loop Disable       23         Input Operating Voltage       23         Output Operating Power and Other Optimizations       24         Device Control       24         I <sup>2</sup> C-Controlled       24         Single-Pin-Enable       25         Dynamic Voltage Scaling (DVS)       25         RSEL Voltage Setting       25         Register Map       26         MAX20343/MAX20344       28         Register Details       28         Applications Information       34                                                                                                                                                                                                                                                                                                                                                                                                                                                | Functional Diagram                             | 20 |

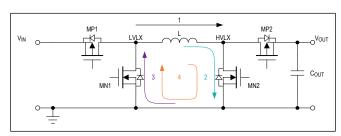

| Architectural Description       21         Switching Phases       21         Buck-Boost Mode       21         Buck-Only Mode       22         Inductor Peak and Valley Current Limits       22         Integrator Control Loop Disable       23         Input Operating Voltage       23         Output Operating Power and Other Optimizations       24         Device Control       24         I²C-Controlled       24         Single-Pin-Enable       25         Dynamic Voltage Scaling (DVS)       25         RSEL Voltage Setting       25         Register Map       28         MAX20343/MAX20344       28         Register Details       28         Applications Information       34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Detailed Description                           | 21 |

| Switching Phases       21         Buck-Boost Mode       21         Buck-Only Mode       22         Inductor Peak and Valley Current Limits       22         Integrator Control Loop Disable       23         Input Operating Voltage       23         Output Operating Power and Other Optimizations       24         Device Control       24         I <sup>2</sup> C-Controlled       24         Single-Pin-Enable       25         Dynamic Voltage Scaling (DVS)       25         RSEL Voltage Setting       25         Register Map       28         MAX20343/MAX20344       28         Register Details       28         Applications Information       34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Startup Voltage                                | 21 |

| Buck-Boost Mode       21         Buck-Only Mode       22         Inductor Peak and Valley Current Limits       22         Integrator Control Loop Disable       23         Input Operating Voltage       23         Output Operating Power and Other Optimizations       24         Device Control       24         I²C-Controlled       24         Single-Pin-Enable       25         Dynamic Voltage Scaling (DVS)       25         RSEL Voltage Setting       25         Register Map       28         MAX20343/MAX20344       28         Register Details       28         Applications Information       34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Architectural Description                      | 21 |

| Buck-Only Mode       22         Inductor Peak and Valley Current Limits       22         Integrator Control Loop Disable       23         Input Operating Voltage       23         Output Operating Power and Other Optimizations       24         Device Control       24         I <sup>2</sup> C-Controlled       24         Single-Pin-Enable       25         Dynamic Voltage Scaling (DVS)       25         RSEL Voltage Setting       25         Register Map       28         MAX20343/MAX20344       28         Register Details       28         Applications Information       34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Switching Phases                               | 21 |

| Inductor Peak and Valley Current Limits       22         Integrator Control Loop Disable       23         Input Operating Voltage       23         Output Operating Power and Other Optimizations       24         Device Control       24         I <sup>2</sup> C-Controlled       24         Single-Pin-Enable       25         Dynamic Voltage Scaling (DVS)       25         RSEL Voltage Setting       25         Register Map       28         MAX20343/MAX20344       28         Register Details       28         Applications Information       34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Buck-Boost Mode                                | 21 |

| Integrator Control Loop Disable       23         Input Operating Voltage       23         Output Operating Power and Other Optimizations       24         Device Control       24         I <sup>2</sup> C-Controlled       24         Single-Pin-Enable       25         Dynamic Voltage Scaling (DVS)       25         RSEL Voltage Setting       25         Register Map       28         MAX20343/MAX20344       28         Register Details       28         Applications Information       34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Buck-Only Mode                                 | 22 |

| Input Operating Voltage       23         Output Operating Power and Other Optimizations       24         Device Control       24         I²C-Controlled       24         Single-Pin-Enable       25         Dynamic Voltage Scaling (DVS)       25         RSEL Voltage Setting       25         Register Map       28         MAX20343/MAX20344       28         Register Details       28         Applications Information       34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Inductor Peak and Valley Current Limits        | 22 |

| Output Operating Power and Other Optimizations24Device Control24I²C-Controlled24Single-Pin-Enable25Dynamic Voltage Scaling (DVS)25RSEL Voltage Setting25Register Map28MAX20343/MAX2034428Register Details28Applications Information34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Integrator Control Loop Disable                | 23 |

| Device Control       24         I <sup>2</sup> C-Controlled       24         Single-Pin-Enable       25         Dynamic Voltage Scaling (DVS)       25         RSEL Voltage Setting       25         Register Map       28         MAX20343/MAX20344       28         Register Details       28         Applications Information       34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Input Operating Voltage                        | 23 |

| I <sup>2</sup> C-Controlled       24         Single-Pin-Enable       25         Dynamic Voltage Scaling (DVS)       25         RSEL Voltage Setting       25         Register Map       28         MAX20343/MAX20344       28         Register Details       28         Applications Information       34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Output Operating Power and Other Optimizations | 24 |

| Single-Pin-Enable       25         Dynamic Voltage Scaling (DVS)       25         RSEL Voltage Setting       25         Register Map       28         MAX20343/MAX20344       28         Register Details       28         Applications Information       34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Device Control                                 | 24 |

| Dynamic Voltage Scaling (DVS)       25         RSEL Voltage Setting       25         Register Map       28         MAX20343/MAX20344       28         Register Details       28         Applications Information       34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I <sup>2</sup> C-Controlled                    | 24 |

| Dynamic Voltage Scaling (DVS)       25         RSEL Voltage Setting       25         Register Map       28         MAX20343/MAX20344       28         Register Details       28         Applications Information       34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Single-Pin-Enable                              | 25 |

| RSEL Voltage Setting       25         Register Map       28         MAX20343/MAX20344       28         Register Details       28         Applications Information       34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •                                              |    |

| Register Map       28         MAX20343/MAX20344       28         Register Details       28         Applications Information       34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                |    |

| MAX20343/MAX20344       28         Register Details       28         Applications Information       34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                |    |

| Register Details    28      Applications Information    34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                |    |

| Applications Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | •                                              |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                |    |

# Ultra-Low Quiescent Current, Low Noise 3.5W Buck-Boost Regulator

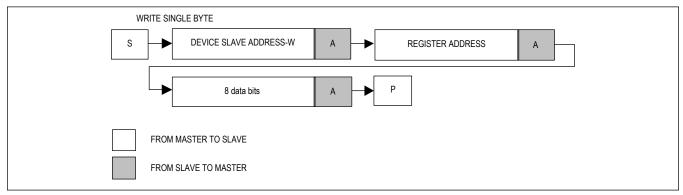

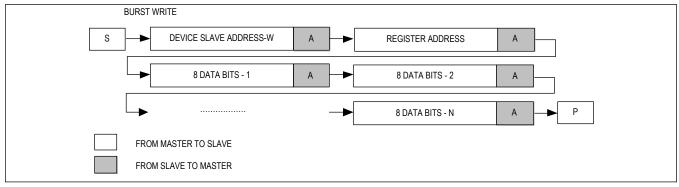

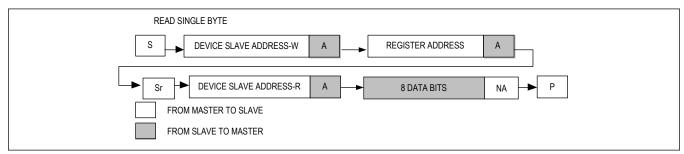

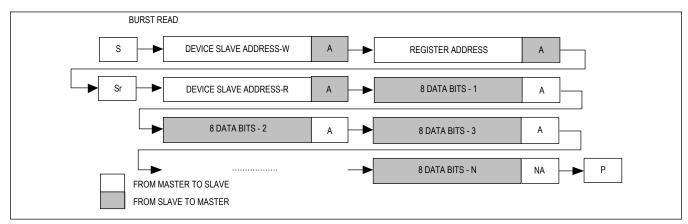

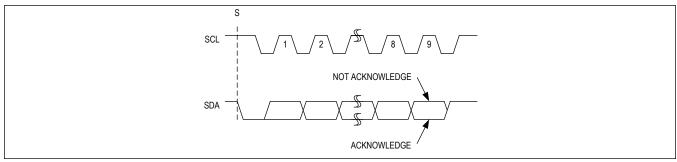

# TABLE OF CONTENTS (CONTINUED) Inductor Selection. 35 Soft-Start 35 I<sup>2</sup>C Interface. 35 Slave Address. 35 Start, Stop, and Repeated Start Conditions 35 Bit Transfer 36 Single-Byte Write. 36 Burst Write. 36 Single Byte Read. 37 Burst Read 37 Acknowledge Bits 38 Register Values 39 Typical Application Circuits 41 Optical Heart Rate LED Supply 41 LPWAN Radio Supply 41 Ordering Information 42

# Ultra-Low Quiescent Current, Low Noise 3.5W Buck-Boost Regulator

| EIGT OF TIGORES                                                       |    |

|-----------------------------------------------------------------------|----|

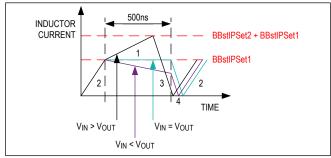

| Figure 1. The Buck-Boost Regulator and Switching Phases               | 21 |

| Figure 2. Buck-Boost Inductor Current in Buck-Boost Mode              | 21 |

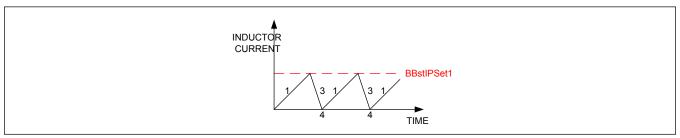

| Figure 3. Buck-Boost Inductor Current in Buck-Only Mode               | 22 |

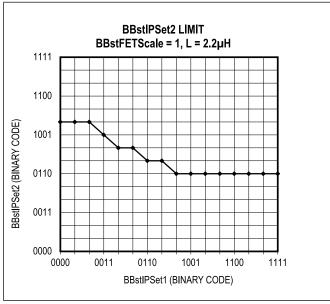

| Figure 4. Minimum BBstIPSet2 Limit for Given BBstIPSet1 Setting       | 23 |

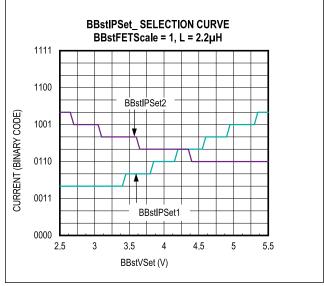

| Figure 5. Recommended BBstlPSet1 and BBstlPSet2 Settings              | 23 |

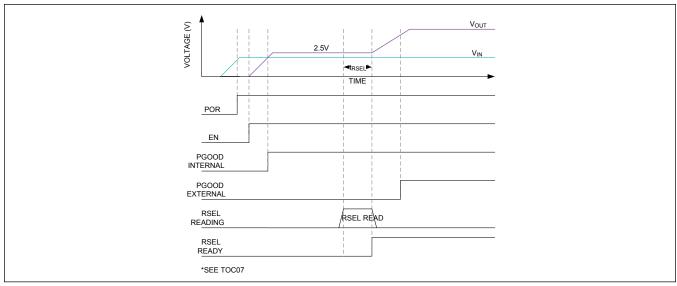

| Figure 6. MAX20343/MAX20344 RSEL Startup Sequence                     |    |

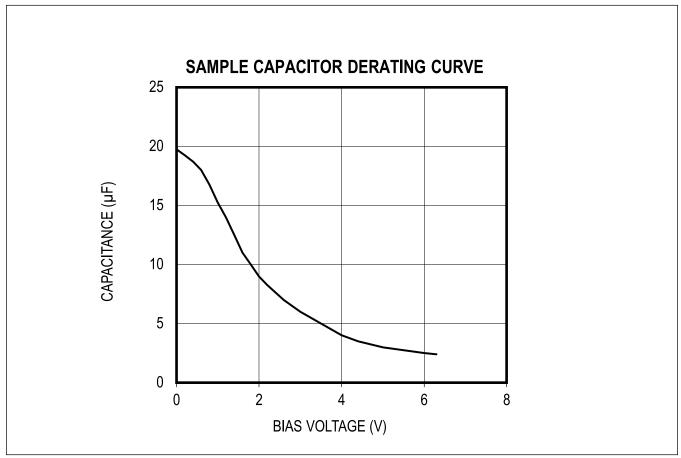

| Figure 7. Capacitor Derating for Input and Output Capacitance         | 34 |

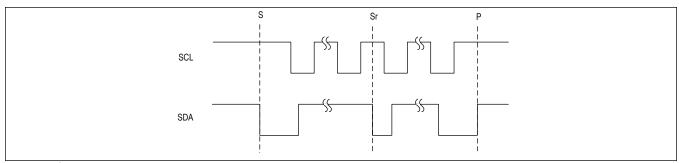

| Figure 8. I <sup>2</sup> C START, STOP, and REPEATED START Conditions |    |

LIST OF FIGURES

# Ultra-Low Quiescent Current, Low Noise 3.5W Buck-Boost Regulator

| LIST OF TABLES                               |    |

|----------------------------------------------|----|

| Table 1. RSEL SELECTION TABLE                | 26 |

| Table 2. Characteristics and Device Settings | 27 |

| Table 3. Register Bit Default Values         | 39 |

| Table 4. Register Default Values             | 40 |

# Ultra-Low Quiescent Current, Low Noise 3.5W Buck-Boost Regulator

## **Absolute Maximum Ratings**

| IN, OUT, SDA, SCL, EN, FAST, RSEL,                                  | FC2QFN) (derate 17.04mW/°C above +70°C) | 936.97mW        |

|---------------------------------------------------------------------|-----------------------------------------|-----------------|

| PGOOD, INGOOD, INT, CAP0.3V to +6.0V                                | Operating Temperature Range             |                 |

| LVLX0.3V to V <sub>IN</sub> + 0.3V                                  | MAX20343                                | 40°C to +85°C   |

| HVLX0.3 to min(V <sub>OUT</sub> + 0.3V, +6.0V)                      | MAX20344                                | -40°C to +125°C |

| Continuous Power Dissipation (Multilayer Board,                     | Junction Temperature                    | +150°C          |

| $T_A = +70^{\circ}C$ ) (4 x 4 Array 16-Ball, 1.77mm x 2.01mm, 0.4mm | Storage Temperature Range               | -40°C to +150°C |

| Pitch WLP) (derate 17.26mW/°C above +70°C)949.30mW                  | Soldering Temperature (reflow)          | +260°C          |

| Continuous Power Dissipation (Multilayer Board,                     |                                         |                 |

| $T_A = +70^{\circ}C$ ) (12-Pin, 2.50mm x 2.50mm, 0.5mm Pitch        |                                         |                 |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

#### 16-BUMP WLP

| Package Code                                           | W161C2+1                       |  |  |  |  |

|--------------------------------------------------------|--------------------------------|--|--|--|--|

| Outline Number                                         | <u>21-100328</u>               |  |  |  |  |

| Land Pattern Number                                    | Refer to Application Note 1891 |  |  |  |  |

| THERMAL RESISTANCE, SINGLE-LAYER BOARD                 |                                |  |  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                 |                                |  |  |  |  |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) |                                |  |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD                   |                                |  |  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | 57.93°C/W                      |  |  |  |  |

#### 12-Pin FC2QFN

| Package Code                                          | F122B2F+1        |  |  |  |  |

|-------------------------------------------------------|------------------|--|--|--|--|

| Outline Number                                        | <u>21-100331</u> |  |  |  |  |

| Land Pattern Number                                   | 90-100130        |  |  |  |  |

| THERMAL RESISTANCE, SINGLE-LAYER BOARD                |                  |  |  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                |                  |  |  |  |  |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) |                  |  |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD                  |                  |  |  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                | 58.70°C/W        |  |  |  |  |

| Junction-to-Case Thermal Resistance $(\theta_{JC})$   | 23.10°C/W        |  |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

## **Electrical Characteristics**

$(V_{IN} = +1.8V \text{ to } +5.5V, C_{IN} = 5\mu\text{F}, C_{OUT} = 8\mu\text{F}, T_{J} = -40^{\circ}\text{C to } +125^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } T_{A} = +25^{\circ}\text{C}, V_{IN} = +3.7V, L = 1\mu\text{H}, \text{ Limits are } 100\% \text{ tested at } T_{A} = +25^{\circ}\text{C}.) \text{ (Note 1)}$

| PARAMETER                                     | SYMBOL                                                          | COND                                                                                                                             | ITIONS                                                                                                     | MIN  | TYP  | MAX  | UNITS |                                |                            |     |  |

|-----------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------|------|------|-------|--------------------------------|----------------------------|-----|--|

| BUCK-BOOST                                    |                                                                 |                                                                                                                                  | ,                                                                                                          |      |      |      | •     |                                |                            |     |  |

| Input Voltage Range                           | V <sub>IN_START</sub>                                           | Input voltage require                                                                                                            | d for startup (Note 2)                                                                                     | 1.9  |      | 5.5  | V     |                                |                            |     |  |

|                                               | _                                                               |                                                                                                                                  | SwoFrcIN = 1, T <sub>A</sub> = +85°C (MAX20343)                                                            |      | 3.51 | 5    |       |                                |                            |     |  |

| Quiescent Supply<br>Current                   | ΙQ                                                              | No load, V <sub>OUT</sub> = 5V, V <sub>IN</sub> = 3.7V                                                                           | SwoFrcIN = 1, T <sub>A</sub> =<br>+125°C<br>(MAX20344)                                                     |      |      | 12.5 | μA    |                                |                            |     |  |

|                                               | IQ_FAST                                                         |                                                                                                                                  | FAST = 1                                                                                                   |      | 35   |      | μA    |                                |                            |     |  |

| Shutdown Supply<br>Current                    | I <sub>SHDN</sub>                                               | I <sup>2</sup> C controlled                                                                                                      |                                                                                                            |      | 0.3  |      | μA    |                                |                            |     |  |

|                                               |                                                                 | Integrator enabled,                                                                                                              | BBstFETScale = 0,<br>L = 1μH, C <sub>OUT</sub> =<br>8μF                                                    | 3.5  |      |      |       |                                |                            |     |  |

|                                               |                                                                 | V <sub>IN</sub> > 2.7V, V <sub>OUT</sub> ≥ 3.2V                                                                                  | BBstFETScale = 1,<br>L = 2.2µH, C <sub>OUT</sub> =<br>4µF                                                  | 1.75 |      |      |       |                                |                            |     |  |

| Maximum Output<br>Operative Power (Note<br>3) | Power (Note P <sub>MAX</sub> Integration of V <sub>IN</sub> > 3 |                                                                                                                                  | BBstFETScale = 0,<br>L = 1 $\mu$ H, C <sub>OUT</sub> =<br>8 $\mu$ F, T <sub>A</sub> = +85°C<br>(MAX20343)  | 3.2  |      |      | w     |                                |                            |     |  |

|                                               |                                                                 | Integrator disabled,<br>V <sub>IN</sub> > 3.2V (Note<br>4), V <sub>OUT</sub> ≥ 3.2V                                              | BBstFETScale = 0,<br>L = 1 $\mu$ H, C <sub>OUT</sub> =<br>8 $\mu$ F, T <sub>A</sub> = +125°C<br>(MAX20344) | 2.9  |      |      |       |                                |                            |     |  |

|                                               |                                                                 |                                                                                                                                  | BBstFETScale = 1,<br>L = 2.2 $\mu$ H, C <sub>OUT</sub> = 4 $\mu$ F, T <sub>A</sub> = +85°C<br>(MAX20343)   | 1.75 |      |      |       |                                |                            |     |  |

|                                               |                                                                 |                                                                                                                                  |                                                                                                            |      |      |      |       | $4\mu F, T_A = +125^{\circ} C$ | $L = 2.2 \mu H, C_{OUT} =$ | 1.6 |  |

|                                               |                                                                 |                                                                                                                                  |                                                                                                            | 2.5  |      | 5.5  |       |                                |                            |     |  |

| Output-Voltage Set<br>Range                   | V <sub>OUT</sub>                                                | 50mV step resolution                                                                                                             | V <sub>IN</sub> < 2.1V,<br>SwoFrcIN = 0 (see<br>the <u>Input Operating</u><br><u>Voltage</u> section)      | 3.2  |      | 5.5  | V     |                                |                            |     |  |

| Average Output-Voltage<br>Accuracy            | ACC_OUT                                                         | I <sub>OUT</sub> = 1mA, C <sub>OUT_EFF</sub> = 8μF                                                                               |                                                                                                            | -2.4 |      | +2.4 | %     |                                |                            |     |  |

| Line Regulation Error                         | V <sub>LINE_REG</sub>                                           |                                                                                                                                  |                                                                                                            |      |      | +1   | %/V   |                                |                            |     |  |

|                                               |                                                                 | Integrator enabled, \ 3.3V, BBstFETScale                                                                                         | / <sub>IN</sub> = 2.7V, V <sub>OUT</sub> =<br>= 0, P <sub>OUT</sub> = 3.5W                                 |      | -1   |      |       |                                |                            |     |  |

| Load Regulation Error V <sub>LOAD_RE</sub>    |                                                                 | Integrator disabled, $V_{IN}$ = 3.7V, $V_{OUT}$ = 5V, $P_{OUT}$ = 1.5W, BBstFETScale = 1, $C_{OUT}$ = 4 $\mu$ F, L = 2.2 $\mu$ H |                                                                                                            |      | -3.2 |      | %     |                                |                            |     |  |

## **Electrical Characteristics (continued)**

$(V_{IN}$  = +1.8V to +5.5V,  $C_{IN}$  = 5 $\mu$ F,  $C_{OUT}$  = 8 $\mu$ F,  $T_J$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C,  $V_{IN}$  = +3.7V, L = 1 $\mu$ H, Limits are 100% tested at  $T_A$  = +25°C.) (Note 1)

| PARAMETER                              | SYMBOL                  | COND                                                                                                           | ITIONS                                                                                       | MIN | TYP   | MAX | UNITS                        |

|----------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----|-------|-----|------------------------------|

| Line Transient<br>Response             | V <sub>LINE_TRAN</sub>  | $V_{OUT}$ = 3.4V, $V_{IN}$ from 3.4V to 2.9V, 1µs fall time, $I_{LOAD}$ = 750mA, BBstIntegEn = 1, SwoFrcIN = 0 |                                                                                              |     | 0     |     | mV                           |

| Load Transient<br>Response             | V <sub>LOAD_TRAN</sub>  | V <sub>OUT</sub> = 5V, V <sub>IN</sub> = 3.<br>700mA, BBstIntegEr                                              | 7V, I <sub>LOAD</sub> = 10μA to<br>n = 1                                                     |     | -150  |     | mV                           |

| Input Supply Current<br>During Startup | I <sub>IN_STUP</sub>    | V <sub>IN</sub> = 3.6V, V <sub>OUT</sub> =                                                                     | 5V, I <sub>LOAD</sub> = 0                                                                    |     | 1     |     | mA/<br>C <sub>OUT</sub> (μF) |

| Maximum Output Power                   | IPWR_MAX_ST             | BBstFETScale = 0                                                                                               |                                                                                              | 400 | 600   |     | mW                           |

| During Startup (Note 3)                | UP                      | BBstFETScale = 1                                                                                               |                                                                                              | 200 | 300   |     | 11177                        |

|                                        |                         | Time from V <sub>OUT</sub> =                                                                                   | I <sup>2</sup> C controlled                                                                  |     | 9.6   |     | _                            |

| Startup Time                           | <sup>t</sup> STARTUP    | 0V to final value                                                                                              | RSEL,<br>BBstRampEn = 0                                                                      |     | 32    |     | ms                           |

| PGOOD Threshold                        | V <sub>PGOOD</sub>      |                                                                                                                |                                                                                              |     | 84.7  |     | %V <sub>OUT</sub>            |

| PGOOD Threshold<br>Hysteresis          | V <sub>PGOOD_HYS</sub>  |                                                                                                                |                                                                                              |     | 2.25  |     | %V <sub>OUT</sub>            |

| Active Discharge<br>Current            | I <sub>ACTD</sub>       |                                                                                                                |                                                                                              |     | 20    |     | mA                           |

| Passive Discharge<br>Resistance        | R <sub>PSVD</sub>       |                                                                                                                |                                                                                              |     | 1.2   |     | kΩ                           |

| Input UVLO Rising                      |                         |                                                                                                                | Soft-start active,<br>SwoFrcIN = 1, or<br>V <sub>OUT</sub> set below<br>3.3V                 |     | 1.836 |     |                              |

| Threshold                              | VIN_UVLO_R              | V <sub>IN</sub> rising                                                                                         | V <sub>OUT</sub> set higher<br>than 3.3V,<br>SwoFrcIN = 0, soft-<br>start period<br>complete |     | 2.185 |     | V                            |

| Input IIV/I O Folling                  |                         |                                                                                                                | Soft-start active,<br>SwoFrcIN = 1, or<br>V <sub>OUT</sub> set below<br>3.3V                 |     | 1.782 |     |                              |

| Input UVLO Falling Threshold           |                         | V <sub>IN</sub> falling                                                                                        | V <sub>OUT</sub> set higher<br>than 3.3V,<br>SwoFrcIN = 0, soft-<br>start period<br>complete |     | 2.101 |     | V                            |

| Output UVLO Falling Threshold          | V <sub>OUT_UVLO_F</sub> | V <sub>OUT</sub> falling                                                                                       |                                                                                              |     | 1.873 |     | V                            |

| Output UVLO Rising Threshold           | V <sub>OUT_UVLO_R</sub> | V <sub>OUT</sub> rising                                                                                        |                                                                                              |     | 1.963 |     | V                            |

## **Electrical Characteristics (continued)**

$(V_{IN}$  = +1.8V to +5.5V,  $C_{IN}$  = 5 $\mu$ F,  $C_{OUT}$  = 8 $\mu$ F,  $T_J$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C,  $V_{IN}$  = +3.7V, L = 1 $\mu$ H, Limits are 100% tested at  $T_A$  = +25°C.) (Note 1)

| PARAMETER                                                                  | SYMBOL              | CONDITIONS             | MIN      | TYP MAX | UNITS |

|----------------------------------------------------------------------------|---------------------|------------------------|----------|---------|-------|

| DIGITAL                                                                    |                     |                        | <u>'</u> |         |       |

| SDA, EN, SCL, INT,<br>PGOOD, INGOOD<br>FAST, RSEL Input<br>Leakage Current | I <sub>LK_IO</sub>  | T <sub>J</sub> = +25°C | -1       | +1      | μА    |

| SDA, EN, SCL, FAST<br>Input Logic High                                     | V <sub>IO_IH</sub>  |                        | 1.4      |         | V     |

| SDA, EN, SCL, FAST<br>Input Logic Low                                      | $V_{IO\_IL}$        |                        |          | 0.4     | V     |

| SDA, INT, PGOOD,<br>INGOOD Output Logic<br>Low                             | V <sub>IO_OL</sub>  | I <sub>OL</sub> = 4mA  |          | 0.4     | V     |

| SCL Clock Frequency                                                        | f <sub>SCL</sub>    |                        |          | 680     | kHz   |

| Bus Free Time Between<br>STOP and START<br>Condition                       | t <sub>BUF</sub>    |                        | 0.75     |         | μs    |

| START Condition<br>(Repeated) Hold Time                                    | tHD_STA             | (Note 5)               | 0.35     |         | μs    |

| Low Period of SCL<br>Clock                                                 | $t_{LOW}$           |                        | 0.75     |         | μs    |

| High Period of SCL<br>Clock                                                | <sup>t</sup> HIGH   |                        | 0.35     |         | μs    |

| Setup Time for a<br>Repeated START<br>Condition                            | t <sub>SU_STA</sub> |                        | 0.35     |         | μs    |

| Data Hold Time                                                             | t <sub>HD_DAT</sub> | (Note 6)               | 0        | 0.53    | μs    |

| Data Setup Time                                                            | tsu_dat             |                        | 100      |         | ns    |

| Setup Time for STOP<br>Condition                                           | tsu_sto             |                        | 0.35     |         | μs    |

| Spike Pulse Widths<br>Suppressed by Input<br>Filter                        | t <sub>SP</sub>     |                        | 50       |         | ns    |

- Note 1: All devices are 100% production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range are guaranteed by design.

- Note 2: Output power across the input operating voltage range is limited by input current. Refer to TOC03 for details on how the power limit changes with  $V_{IN}$ .

- Note 3: The parameter is not production tested and values are generated through characterization only.

- **Note 4:** Operation down to 2.7V is supported with the integrator disabled, but stability is only guaranteed up to 1.75W output power. Beyond 1.75W, oscillations could occur unless output capacitance is increased.

- **Note 5:** f<sub>SCL</sub> must meet the minimum clock low time plus the rise/fall times.

- Note 6: The maximum t<sub>HD DAT</sub> has to be met only if the device does not stretch the low period (t<sub>LOW</sub>) of the SCL signal.

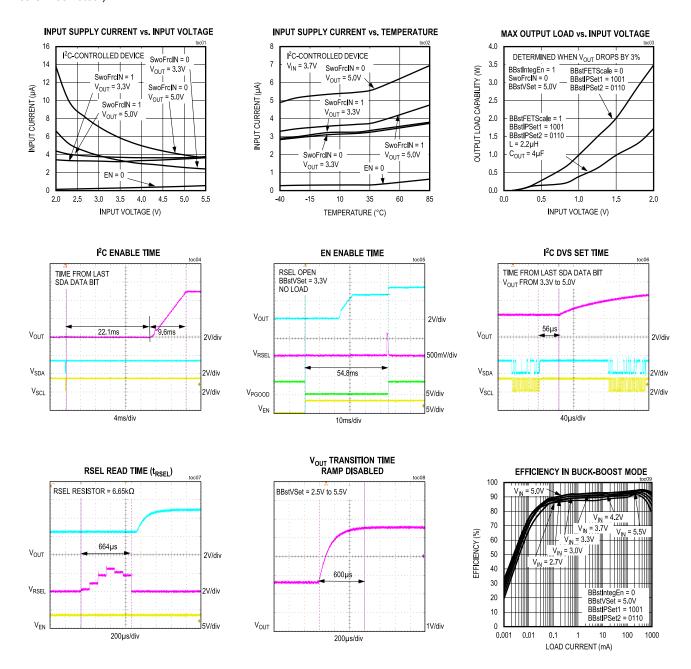

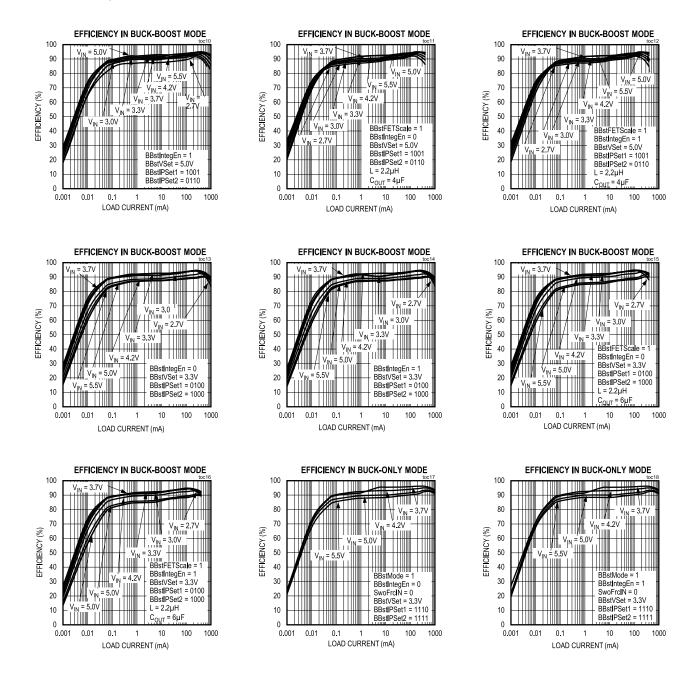

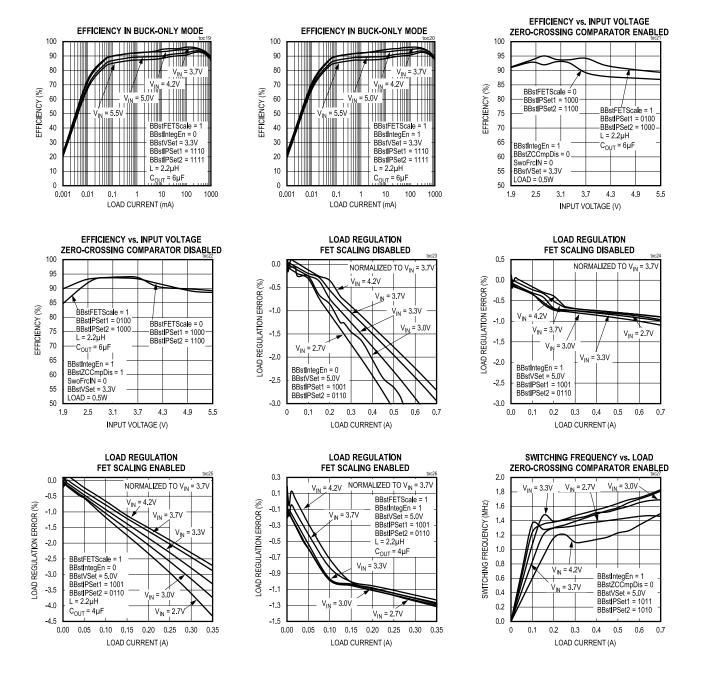

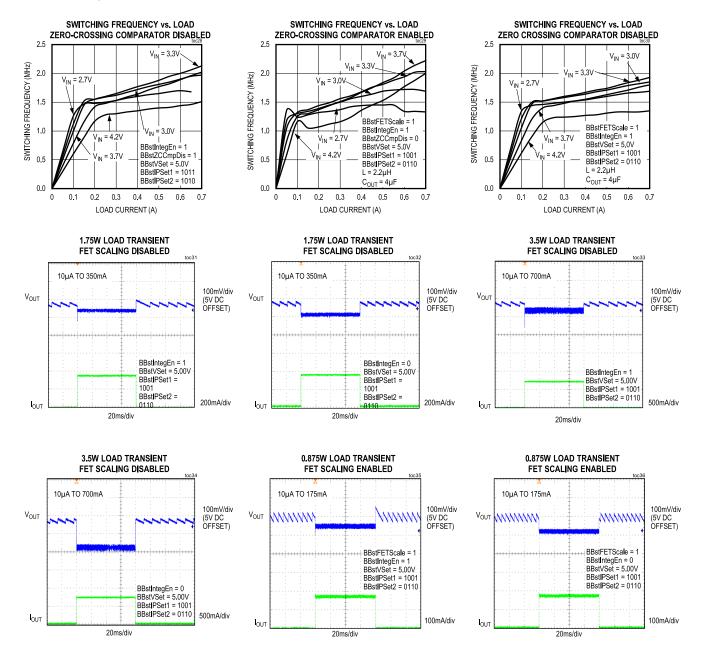

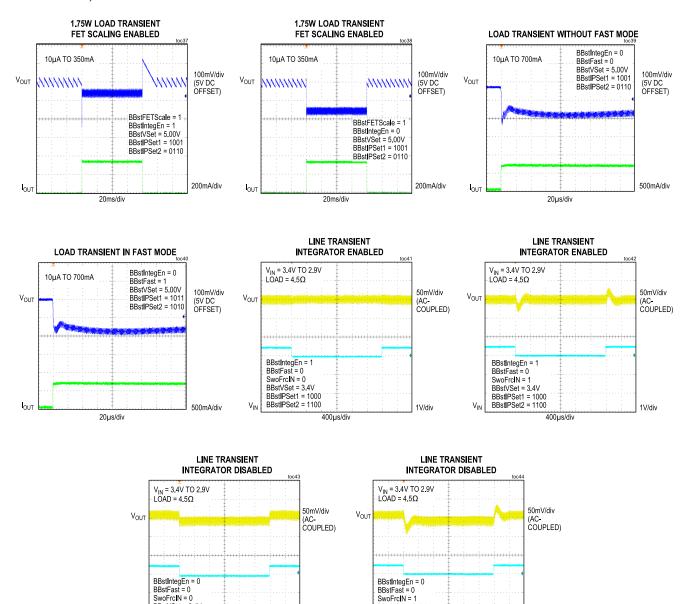

## **Typical Operating Characteristics**

$(V_{IN} = +3.7V, C_{IN} = GRM155R60J226ME11, refer to Figure 7 single capacitor derating, C_{OUT} = 2x GRM155R60J226ME11, L = 1<math>\mu$ H, BBstZCCmpDis = 0, BBstLowEMI = 0, BBstMode = 0, SwoFrcIN = 1, BBstIPAdptDis = 0, BBstFETScale = 0, T<sub>A</sub> = +25°C, unless otherwise noted.)

$(V_{IN}$  = +3.7V,  $C_{IN}$  = GRM155R60J226ME11, refer to Figure 7 single capacitor derating,  $C_{OUT}$  = 2x GRM155R60J226ME11, L = 1µH, BBstZCCmpDis = 0, BBstLowEMI = 0, BBstMode = 0, SwoFrcIN = 1, BBstIPAdptDis = 0, BBstFETScale = 0, T<sub>A</sub> = +25°C, unless otherwise noted.)