**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

## Audio Processor for Digital Hearing Aids and Hearables

# **EZAIRO 8300**

#### Introduction

Ezairo<sup>®</sup> 8300 includes six programmable or semi-programmable processing cores, providing a high degree of parallelism and flexibility:

- The CFX is an open-programmable dual-Harvard 24 bits digital signal processor (DSP) providing support for any type of audio signal processing

- The Arm<sup>®</sup> Cortex<sup>®</sup>-M3 processor is a 32-bit RISC processor providing support for general processing and interfacing to external components

- The HEAR configurable accelerator core is optimized for pre-programmed functions that are frequently needed in audio signal processing

- The Filter Engine allows time domain filtering and supports an ultra-low-delay audio path

- The LPDSP32 is an open-programmable dual-Harvard 32-bit DSP

- The Neural Network Accelerator that allows the Ezairo 8300 to perform neural network computations in a highly efficient and flexible way.

Ezairo 8300 includes 4 ADCs with signal detection mode and 2 direct digital output drivers, with high quality and ultra-low power performances. Ezairo 8300 also includes peripherals and interfaces needed to make it a complete hardware platform, when combined with non-volatile memory and wireless transceivers.

www.onsemi.com

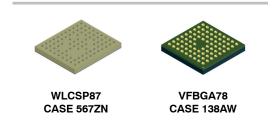

#### ORDERING INFORMATION

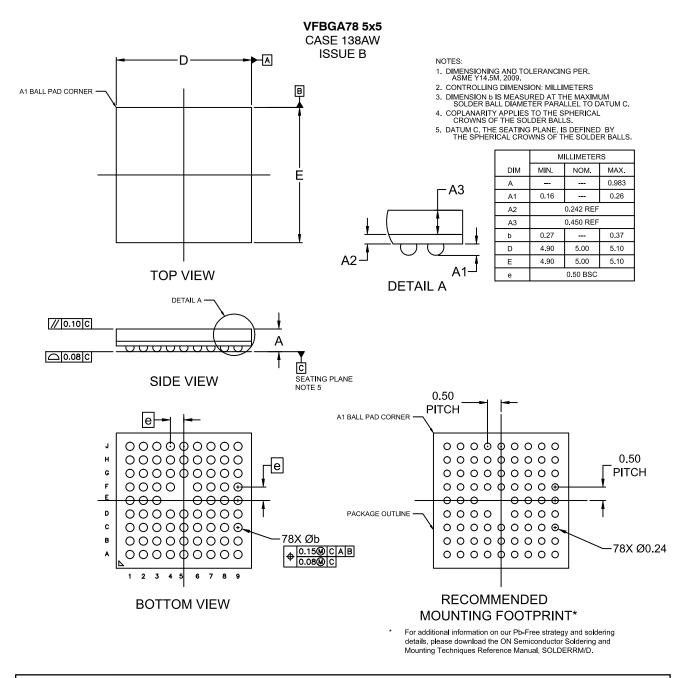

| Device                | Package               | Shipping    |

|-----------------------|-----------------------|-------------|

| E8300-<br>101WC78-ABG | Bare Die<br>(Pb-Free) | 5000 / Tape |

| E8300-<br>101B78-ABG  | VFBGA                 | and Reel    |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

#### **Key Features**

- High Performance: Best in class MIPS/mW.

- **Programmable Flexibility:** the open-programmable DSP-based system can be customized to the specific signal processing needs of manufacturers. Algorithms and features can be modified or completely new concepts implemented without having to modify the chip.

- Highly-integrated SoC: the six-core architecture includes a CFX DSP, an Arm Cortex-M3 Processor, a HEAR Configurable Accelerator, a programmable Filter Engine, a LPDSP 32 DSP and a Neural Network Accelerator. The system also includes an efficient input/output controller (IOC), system memories, input and output stages along with a full complement of peripherals and interfaces.

- **CFX DSP:** a highly cycle–efficient, programmable core that uses a 24–bit fixed–point, dual–MAC, dual–Harvard architecture. The CFX can be used as the master of the whole Ezairo 8300 SoC.

- Arm Cortex-M3 Processor: a complete subsystem that can be used as the master of the whole Ezairo 8300 SoC.

- HEAR Configurable Accelerator: a highly optimized signal processing engine designed to perform common signal processing operations and complex standard filterbanks.

- **Programmable Filter Engine:** a filtering system that allows applying a various range of pre- or post-processing filtering, such as IIR, FIR and biquad filters.

- LPDSP32: a highly cycle–efficient, programmable core that uses a 32–bit fixed–point, dual–MAC, dual–Harvard architecture.

- Neural Network Accelerator (NNA): a configurable hardware accelerator dedicated to support neural networks with high energy efficiency.

- Selectable System Clock Speeds: from 2.56 MHz up to 61.44 MHz, with clock throttling capabilities to optimize the computing performance versus power consumption ratio.

- Adaptive Voltage Scaling: automatically adjusts the digital supply voltage (VDDC) level using a critical path speed measurement block. This feature allows to optimize the SoC's power consumption in all situations.

- Ultra-low Delay path: the programmable Filter Engine supports an ultra-low-delay audio path of min 10.4 µs (analog input to analog output) for features such as active noise cancellation.

- Ultra-low Power Consumption: <0.7 mA @ 15.24 MHz system clock (CFX 97%, Arm Cortex-M3 processor 40%, HEAR 77%, FENG 9%, 2 ADC @ 20 kHz, 1 OD, 1 LSAD)

- **High fidelity audio system:** 108 dB system dynamic range, up to 64 KHz of sampling frequency

- **Output drivers:** capable of driving multiple types of speakers.

- Versatile Memory Architecture: a total of 1433 kB of memory, shared between the six programmable or semi–programmable cores.

- **Data Security:** sensitive program data can be encrypted for storage in external NVM to prevent unauthorized parties from gaining access to proprietary algorithm and intellectual property.

- **Multiple Audio Input Sources:** four analog input channels (AI0 to AI3) that can be used simultaneously for omni–directional and directional microphones, telecoils, bone conducting microphones, an input from a remote control interface, or a direct audio input.

- Signal Detection Mode: ultra-low-power detection system for signals on any analog inputs.

- High Throughput Communication Interface: fast I<sup>2</sup>C-based and SWJ-DP interfaces for quick download, debugging and general communication.

- **Highly Configurable Interfaces:** two PCM interfaces, three I<sup>2</sup>C interfaces, two I<sup>3</sup>C interfaces, two SPI interfaces, a UART interface, an eMMC interface with custom interface buffering, up to 36 GPIOs and 8 LSAD inputs.

- Asynchronous Sample Rate Converter (ASRC): provides a mean of synchronizing the audio sample rate between an external radio chip and the Ezairo 8300.

- **Two Audio Sink Clock Counters:** Can be used to measure the timing of the frame periods of an external radio relative to the internal audio sampling rate.

- Fitting Support: support for Microcard, HI–PRO 2, HI–PRO USB, QuickCom, and NOAHlink, including NOAHlink's audio streaming feature.

- Integrated Development Environment (IDE): a graphical user interface with the capabilities to edit, build and debug applications. It is the main programming interface for the Software Development Kit (SDK).

- Complete C-development tool chain for the CFX and the LPDSP32. Includes a C-compiler, an instruction set simulator, an assembler/disassembler, a linker and the IDE debugger integrated in the Ezairo 8300 SDK.

- **Sample Code:** The SDK includes several sample applications and libraries to demonstrate key features of Ezairo 8300. The libraries are typically provided in compiled form with source code also available.

- Pb-Free Device

#### Table 1. ABSOLUTE MAXIMUM RATINGS

| Parameter   | Min      | Тур | Мах      | Unit | Notes                              |  |  |

|-------------|----------|-----|----------|------|------------------------------------|--|--|

| VBAT        | -        | _   | 1.98     | V    | Power supply voltage               |  |  |

| VBATOD      | -        | _   | 1.98     | V    | Output driver power supply voltage |  |  |

| VDDO1/2/3/4 | -        | _   | 1.98     | V    | I/O supply voltage                 |  |  |

| VSSA        | 0        | -   | -        | V    | Analog ground                      |  |  |

| VSSOD       | 0        | -   | -        | V    | Output driver ground               |  |  |

| VSSC        | 0        | -   | -        | V    | Digital ground                     |  |  |

| VSSO        | 0        | -   | -        | V    | I/O ground                         |  |  |

| Vin         | VSSO-0.1 | -   | VDDO+0.3 | V    | Digital input pin voltage          |  |  |

|             | -0.1     | -   | 1.98     | V    | Digital input pin voltage          |  |  |

| Toperation  | 0        | 25  | 50       | °C   | Operational temperature            |  |  |

| Tfunctional | -40      | 25  | 85       | °C   | Extended op. temperature (Note 1)  |  |  |

| Tstorage    | -40      | -   | 125      | °C   | Storage temperature                |  |  |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. The IC is functional in the extended temperature range, however some parameters may not meet the specifications. E.g. bandgap voltage, oscillator frequency, ADC noise...

#### Table 2. OVERALL OPERATING CONDITIONS

| Parameter      | Min  | Тур              | Max   | Unit | Notes                                                                                      |

|----------------|------|------------------|-------|------|--------------------------------------------------------------------------------------------|

| VBAT           | 0.9  | 1.25             | 1.98  | V    | Supply voltage, measured at the VBAT pin (Note 2)                                          |

| VBATOD         | 0.9  | 1.25             | 1.98  | V    | Output driver supply voltage (Note 3)                                                      |

| VDDO1/2/3/4    | 0.9  | 1.25             | 1.98  | V    | I/O voltage (Note 4)                                                                       |

| System clock   | -    | 15.36            | 61.44 | MHz  | System clock frequency                                                                     |

| VDDC retention | 0.50 | 0.53<br>(Note 5) | -     | V    | Digital supply voltage, when memories are in retention mode                                |

| VDDC limit     | 0.50 | 0.51<br>(Note 5) | -     | V    | Digital supply voltage limit for adaptive voltage scaling                                  |

| VDDC active    | 0.76 | 0.78<br>(Note 5) | 0.88  | V    | Digital supply voltage in active mode; used as upper limit for<br>adaptive voltage scaling |

| VDDM retention | 0.50 | 0.58<br>(Note 5) | -     | V    | Memories supply voltage, when memories are in retention mode                               |

| VDDM standby   | 0.76 | 0.80<br>(Note 5) | -     | V    | Memory supply voltage in standby mode                                                      |

| VDDM active    | 0.76 | 0.78<br>(Note 5) | 0.88  | V    | Memory supply voltage in active mode (Note 6)                                              |

2. With VBAT below 1.0V, the performance will be degraded. E.g. reduced PSRR, line & load regulations.

3. At system boot, VBATOD is internally connected to VBAT for 5 ms. In case VBATOD is supplied at 1.8 V and VBAT is supplied at 1.25 V, a current of ~130 mA will flow from VBATOD to VBAT. This current does not represent a reliability risk for a typical usage of the chip of 10 boots per day over 10 years.

4. With VDDO below 1.0 V, the performance will be degraded, e.g. the drive strength will be reduced.

5. These values indicate the target trimming values.

6. The VDDM voltage should be higher or equal to the core voltage (VDDC).

#### Table 3. ELECTRICAL PERFORMANCE SPECIFICATIONS

Unless otherwise noted, the specifications mentioned in the table below are valid at  $25^{\circ}C$  at VBAT = 1.25 V. The system clock (SYS\_CLK) was set to 15.36 MHz. Parameters marked as screened are tested on each chip.

#### CURRENT CONSUMPTION

| Parameter                                         | Symbol               | Conditions                                                                                                                                                 | Min | Тур  | Max | Unit           | Screened |

|---------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|----------------|----------|

| Current<br>consumption                            | I <sub>VBAT</sub>    | CFX load 97%, Arm Cortex-M3 processor load<br>40%, HEAR load 77%, Filter Engine load 9%<br>2 ADC @ 20 kHz, 1 OD, 1 LSAD<br>SYS_CLK=15.36 MHz, CCO mult = 2 | _   | 0.7  | 0.9 | mA             | ~        |

| Standby Current                                   | I <sub>STDB</sub>    | Using ON Semiconductor's macro                                                                                                                             | -   | 90   | 120 | μΑ             | ~        |

| CFX power<br>consumption                          | I <sub>CFX</sub>     | Running 31-tap FIR, processing 4 output<br>points in parallel                                                                                              | -   | 13.7 | _   | μA/MHz         |          |

| Arm Cortex–M3<br>processor pow-<br>er consumption | I <sub>CM3</sub>     | Running 31-tap FIR, taking advantage of sym-<br>metrical coefficients                                                                                      | -   | 8.3  | -   | μ <b>Α/MHz</b> |          |

| HEAR power consumption                            | I <sub>HEAR</sub>    | Running 31-tap FIR, HEAR FIR_R function                                                                                                                    | -   | 18.7 | -   | μA/MHz         |          |

| Filter Engine<br>power con-<br>sumption           | I <sub>FENG</sub>    | Running 31-tap FIR                                                                                                                                         | -   | 12.0 | -   | μ <b>Α/MHz</b> |          |

| LPDSP32 pow-<br>er consumption                    | I <sub>LPDSP32</sub> | Running G.722 decoding                                                                                                                                     | -   | 10.0 | -   | μA/MHz         |          |

| NNA power consumption                             | I <sub>NNA1</sub>    | 256-input, 256-output layer, tanh activation<br>function, 8-bit inputs and outputs, 8-bit uncom-<br>pressed weights                                        | -   | 17.5 | -   | μ <b>Α/MHz</b> |          |

|                                                   | I <sub>NNA2</sub>    | 256-input, 256-output layer, tanh activation<br>function, 8-bit inputs and outputs, 4-bit loga-<br>rithmic encoded weights                                 | -   | 19.7 | -   | μ <b>Α/MHz</b> |          |

NOTE: SYS\_CLK = 15.36 MHz using adaptive voltage scaling.

NOTE: Currents are on VBAT at 1.25 V

#### VREG

| Parameter       | Symbol              | Conditions                                                      | Min  | Тур | Max  | Unit  | Screened |

|-----------------|---------------------|-----------------------------------------------------------------|------|-----|------|-------|----------|

| Output voltage  | VREG                | 50 μA < I <sub>LOAD</sub> < 200 μA, trimmed<br>bandgap (Note 7) | 0.89 | 0.9 | 0.91 | V     | ~        |

| Load current    | I <sub>LOAD</sub>   |                                                                 | -    | -   | 2    | mA    |          |

| Line regulation | LINE <sub>REG</sub> | I <sub>LOAD</sub> = 1 mA                                        | -    | -   | 5    | mV/V  |          |

| Load regulation | LOAD <sub>REG</sub> | 5 μA < I <sub>LOAD</sub> < 2 mA                                 | -    | 6   | 10   | mV/mA |          |

| PSRR @ 1 kHz    | PSRR                | I <sub>LOAD</sub> = 1 mA, VBAT > 1.05 V                         | 80   | -   | -    | dB    |          |

7. VBAT ≥ 1 V is required to have VREG at 0.9 V. Trimming steps: 5 mV. The typical (Typ) value shown for VREG is its target trimming value.

#### VDDA

| Parameter                                  | Symbol                | Conditions                                                               | Min  | Тур | Max  | Unit  | Screened |

|--------------------------------------------|-----------------------|--------------------------------------------------------------------------|------|-----|------|-------|----------|

| Output voltage                             | VDDA                  | Standby Mode (STBY), I <sub>LOAD</sub> <<br>100 μA, VBAT > 0.90 V        | 1.7  | 1.8 | 1.9  | V     | ~        |

|                                            |                       | Low–Power Mode (LPM), $I_{LOAD}$ = 100 $\mu A,$ VBAT > 0.92 V            | 1.7  | 1.8 | 1.9  | V     |          |

|                                            |                       | High-Power Mode (HPM), I <sub>LOAD</sub> <<br>4 mA, VBAT > 0.95 V        | 1.7  | 1.8 | 1.9  | V     | ~        |

| Typical output volt-<br>age trimming range | VDDA <sub>RANGE</sub> | LPM, Typical Process, 25°C,<br>VBAT = 1.25 V; Ι <sub>LOAD</sub> = 100 μA | 1.57 | -   | 1.98 | V     |          |

| Trimming steps                             | VDDA <sub>STEP</sub>  |                                                                          | _    | 6.5 | -    | mV    |          |

| Load current                               | I <sub>LOAD</sub>     | STBY                                                                     | -    | -   | 100  | μΑ    |          |

|                                            |                       | LPM                                                                      | -    | 100 | 500  | μΑ    |          |

|                                            |                       | НРМ                                                                      | -    | -   | 4    | mA    |          |

| Load regulation                            | LOAD <sub>REG</sub>   | LPM, VBAT = 1.20 V;<br>100 μA < I <sub>LOAD</sub> < 500 μA               | _    | 4   | 10   | mV/mA |          |

|                                            |                       | HPM, VBAT = 1.20 V;<br>1 mA < I <sub>LOAD</sub> < 2 mA                   | -    | 4   | 10   | mV/mA |          |

| Line regulation                            | LINE <sub>REG</sub>   | SDBY, 1.2 V < VBAT < 1.86 V;<br>Ι <sub>LOAD</sub> = 100 μΑ               | -    | 10  | 36   | mV/V  |          |

|                                            |                       | LPM, 1.2 V < VBAT < 1.86 V;<br>Ι <sub>LOAD</sub> = 100 μΑ                | _    | 4   | 10   | mV/V  |          |

|                                            |                       | HPM, 1.2 V < VBAT < 1.86 V;<br>I <sub>LOAD</sub> = 1 mA                  | _    | 4   | 10   | mV/V  |          |

| PSRR                                       | VDDA <sub>PSSR</sub>  | VBAT = 1.2 V; @ 1 kHz                                                    | 40   | -   | -    | dB    |          |

#### VDDIF

| Parameter                                  | Symbol                 | Conditions                                          | Min  | Тур | Max                              | Unit  | Screened |

|--------------------------------------------|------------------------|-----------------------------------------------------|------|-----|----------------------------------|-------|----------|

| Output voltage<br>(high-power mode)        | VDDIF                  | VBAT > 0.95 V; I <sub>LOAD</sub> < 5 mA<br>(Note 8) | 1.7  | 1.8 | (2xVBAT –<br>100 mV)<br>(Note 9) | V     |          |

|                                            |                        | VBAT > 1.05V; I <sub>LOAD</sub> < 15 mA             | 1.7  | 1.8 | (2xVBAT –<br>200 mV)<br>(Note 9) | V     | ~        |

| Typical output volt-<br>age trimming range | VDDIF <sub>RANGE</sub> |                                                     | 1.57 | _   | 1.98                             | V     |          |

| Trimming steps                             | VDDIF <sub>STEP</sub>  |                                                     | _    | 6.5 | -                                | mV    |          |

| Load current                               | I <sub>LOAD</sub>      | Low-power mode                                      | _    | -   | 1                                | mA    |          |

|                                            |                        | High–power mode                                     | _    | -   | 15                               | mA    |          |

| Load regulation                            | LOAD <sub>REG</sub>    | VBAT = 1.2 V; HPM, I <sub>LOAD</sub> = 5 mA         | -    | 5   | 10                               | mV/mA |          |

|                                            |                        | VBAT = 1.2 V; LPM; $I_{LOAD}$ = 500 $\mu$ A         | -    | 17  | 20                               | mV/mA |          |

| Line regulation                            | LINE <sub>REG</sub>    | VBAT > 1.2 V; $I_{LOAD} = 100 \ \mu A$              | -    | 4   | 20                               | mV/V  |          |

| PSRR                                       | VDDIF <sub>PSSR</sub>  | VBAT = 1.2 V; @ 1 kHz, I <sub>LOAD</sub> = 5 mA     | 30   | -   | -                                | dB    |          |

8. VBAT voltage on IC pin

9. VDDIF max can't exceed 1.98 V

NOTE: Low Power Mode (LPM): Switching frequency = 128 kHz / itrim = 0X00 High Power Mode (HPM): Switching frequency = 320 kHz / itrim = 0X10

#### VMIC

The output voltage on the VMIC pin can be chosen from 5 different sources:

- VMIC regulator powered by VBAT

- VMIC regulator powered by VDDA

- VREG

- VDDA

## • VDDIF

#### VMIC

| Parameter                                  | Symbol               | Conditions                                               | Min | Тур | Max | Unit  | Screened |

|--------------------------------------------|----------------------|----------------------------------------------------------|-----|-----|-----|-------|----------|

| Switch impedance                           | VMICIMP              | Measured with a 250 $\mu\text{A}$ load current           | 50  | 100 | 250 | Ω     |          |

| Typical output volt-<br>age trimming range | VMIC                 | Regulator powered by VBAT.<br>Maximum Output: VBAT-0.1 V | 0.8 | -   | 1.3 | V     | ~        |

|                                            |                      | Regulator powered by VDDA                                | 0.8 | -   | 1.3 | V     | ~        |

| Trimming steps                             | VMIC <sub>STEP</sub> |                                                          | -   | 25  | -   | mV    |          |

| Load current                               | I <sub>LOAD</sub>    |                                                          | -   | -   | 500 | uA    |          |

| Line regulation                            | LINE <sub>REG</sub>  |                                                          | -   | -   | 10  | mV/V  |          |

| Load regulation                            | LOAD <sub>REG</sub>  |                                                          | -   | 5   | 10  | mV/mA |          |

| Regulator VDDA<br>PSRR                     | VMIC <sub>PSSR</sub> | Regulated from VDDA                                      | 60  | -   | -   | dB    |          |

| Regulator VBAT<br>PSRR                     |                      | Regulated from VBAT, VBAT–VMIC > 0.1 V                   | 80  | -   | -   | dB    |          |

NOTE: The resistor between GND\_MIC and VSSA is 50 Ohm.

#### VDDOD

| Parameter                                  | Symbol                | Conditions                 | Min | Тур | Max | Unit  | Screened |

|--------------------------------------------|-----------------------|----------------------------|-----|-----|-----|-------|----------|

| Typical output volt-<br>age trimming range | VDDOD                 | Maximum Output: VBAT-0.2 V | 0.8 | -   | 1.4 | V     | ~        |

| Trimming steps                             | VDDOD <sub>STEP</sub> |                            | -   | 25  | -   | mV    |          |

| Load current                               | I <sub>LOAD</sub>     |                            | -   | _   | 25  | mA    |          |

| Line regulation                            | LINE <sub>REG</sub>   |                            | -   | -   | 10  | mV/V  |          |

| Load regulation                            | LOAD <sub>REG</sub>   |                            | -   | 1   | 10  | mV/mA |          |

| PSRR                                       | VMIC <sub>PSSR</sub>  |                            | 40  | _   | _   | dB    |          |

NOTE: We recommend to always enable the VDDOD regulator. It improves the PSRR when large transient currents are drawn elsewhere in the Ezairo 8300 based system and gives an audio output level that is independent of the battery voltage.

#### VDDM/VDDC

| Parameter                                  | Symbol                                           | Conditions                                                    | Min  | Тур | Max  | Unit  | Screened |

|--------------------------------------------|--------------------------------------------------|---------------------------------------------------------------|------|-----|------|-------|----------|

| Typical output volt-<br>age trimming range | VDDM <sub>RANGE</sub> ,<br>VDDC <sub>RANGE</sub> | (Note 10)                                                     | 0.45 | -   | 0.88 | V     | ~        |

| Trimming steps                             | VDDM <sub>STEP</sub> ,<br>VDDC <sub>STEP</sub>   |                                                               | -    | 2   | -    | mV    |          |

| Load regulation                            | LOAD <sub>REG</sub>                              |                                                               | -    | 7   | 10   | mV/mA |          |

| Line regulation                            | LINE <sub>REG</sub>                              |                                                               | -    | -   | 10   | mV/V  |          |

| Load current                               | I <sub>LOAD</sub>                                |                                                               | -    | _   | 5    | mA    |          |

| PSRR @ 1 kHz                               | VDDM <sub>PSRR</sub> ,<br>VDDC <sub>PSRR</sub>   | VBAT = 1.25 V, VDDC/M = 0.80 V,<br>I <sub>LOAD</sub> = 500 μA | 25   | -   | -    | dB    |          |

10. The voltage of VDDC and VDDM shall not go beyond the values specified in the operating conditions.

#### **REGULATORS TEMPERATURE STABILITY**

| Parameter             | Symbol | Conditions                       | Min  | Тур | Max | Unit | Screened |

|-----------------------|--------|----------------------------------|------|-----|-----|------|----------|

| Temperature Stability |        | Temperature range of -5 to 50°C. | -0.5 | -   | 0.5 | %    |          |

NOTE: Temperature stability for VREG, VDDA (LPM and HPM), VMIC, VDDOD, VDDC (using the band gap as reference) and VDDM (using the band gap as reference):

#### **REGULATORS TEMPERATURE STABILITY**

| Parameter             | Symbol | Conditions                       | Min | Тур | Max | Unit | Screened |

|-----------------------|--------|----------------------------------|-----|-----|-----|------|----------|

| Temperature Stability |        | Temperature range of −5 to 50°C. | -2  | 1   | 2   | %    |          |

NOTE: Temperature stability for VDDA (STBY), VDDC (using the PMU as reference) and VDDM (using the PMU as reference):

#### **POWER-ON-RESET**

| Description                                  | Symbol              | Conditions | Min  | Тур  | Max  | Unit | Screened |

|----------------------------------------------|---------------------|------------|------|------|------|------|----------|

| VBAT startup voltage: High threshold voltage | Vth <sub>High</sub> |            | 0.68 | 0.77 | 0.86 | V    | ~        |

| VBAT shutdown voltage: Low threshold voltage | Vth <sub>Low</sub>  |            | 0.63 | 0.72 | 0.81 | V    | >        |

NOTE: Typical time duration between application of VBAT and first NVM access: 77 ms

#### **INPUT STAGE**

| Parameter                                                                                                                                                  | Symbol              | Conditions                                                                                             | Min           | Тур | Max             | Unit  | Screened |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------|---------------|-----|-----------------|-------|----------|

| Nominal input referred<br>noise 16 kHz SF, RMS                                                                                                             | IN <sub>IRN</sub>   | A-weighted 100 Hz-8 kHz, 16 kHz<br>SF, nominal current setting                                         | -             | 2   | 4               | μVrms |          |

| Nominal input referred<br>noise 32 kHz SF, RMS                                                                                                             |                     | A-weighted 100 Hz-16 kHz, 32 kHz<br>SF, maximum current setting                                        | -             | 3   | 10<br>(Note 11) | μVrms | ~        |

| HiQ input referred noise<br>16 kHz SF, RMS                                                                                                                 |                     | A–weighted 100 Hz–8 kHz, 16 kHz<br>SF, maximum current setting                                         | -             | 1.5 | 3               | μVrms |          |

| HiQ input referred noise<br>48 kHz SF, RMS                                                                                                                 |                     | A-weighted 20 Hz-20 kHz, 48 kHz<br>SF, maximum current setting                                         | _             | 3   | 10<br>(Note 12) | μVrms | ~        |

| Nominal dynamic range                                                                                                                                      | IN <sub>DR</sub>    | A-weighted 100 Hz-8 kHz, nominal current setting                                                       | -             | 109 | -               | dB    |          |

| HiQ dynamic range                                                                                                                                          |                     | A-weighted 100 Hz-8 kHz, maxi-<br>mum current setting                                                  | , maxi- – 112 |     | -               | dB    |          |

| Input range                                                                                                                                                | IN <sub>RANGE</sub> | At VDDA 1.8 V                                                                                          | 0 –           |     | 1.6             | V     |          |

| Input impedance                                                                                                                                            | R <sub>IN</sub>     | Nominal and HiQ mode                                                                                   | 10            | -   | -               | MΩ    |          |

| Peak THDN                                                                                                                                                  | IN <sub>THDN</sub>  |                                                                                                        | -             | -85 | -70             | dB    | ~        |

| Channel gain mismatch                                                                                                                                      |                     | Calibrated (using digital gain factor,<br>1 kHz) or not calibrated.                                    | _             | -   | 0.1             | dB    |          |

| Channel delay mismatch                                                                                                                                     |                     | At 1 kHz ( approx. max 0.54 deg)                                                                       | -             | -   | 1.5             | μs    |          |

| Ultrasonic immunity, in-<br>put referred aliased level                                                                                                     |                     | A-weighted 100 Hz – 16 kHz aliased<br>level with a –40 dBV input signal<br>swept from 20 kHz to 50 kHz | 95            |     | -85             | dBV   |          |

| Signal detection mode<br>input referred noise                                                                                                              |                     | A-weighted 100 Hz-10 kHz, 1 MHz operation, current setting at 0x1 (4 $\mu\text{A})$                    | -             | 10  | 20              | μVrms |          |

| Microphone bias voltage MIC <sub>BIAS</sub> In order to maximize dynamic range of the input stage, the microphone bias should be set to the typical value. |                     | 0.2                                                                                                    | 0.75          | 1.0 | V               |       |          |

NOTE: Input Stage specifications are A-weighted, bandwidth 100 Hz-fs/2, sampling frequencies 16/32/48 kHz, with ADC\_CLK = 3.84 MHz. The CCO multiplier doesn't affect the specifications of the ADC as long as the ADC\_CLK is around 4 MHz.

NOTE: The specifications at 20 kHz are between the specifications at 16 and 32 kHz.

11. By characterization, the Max value is 5  $\mu\text{Vrms.}$

12. By characterization, the Max value is 5  $\mu$ Vrms.

#### OUTPUT STAGE

| Parameter              | Symbol             | Conditions                                                   | Min | Тур | Max              | Unit | Screened |

|------------------------|--------------------|--------------------------------------------------------------|-----|-----|------------------|------|----------|

| Output resistance      | R <sub>OD</sub>    | I <sub>LOAD</sub> = 1 mA. High and Low side combined.        | -   | 2   | _                | Ω    |          |

| Output Dynamic Range   | OD <sub>DR</sub>   | High impedance load (>1 k $\Omega$ ), XSDM0 mode             | 103 | 108 | -                | dB   |          |

|                        |                    | Low impedance speaker mode,<br>36R load, XSDM0 mode          | -   | 105 | _                | dB   |          |

|                        |                    | High impedance load (>1 k $\Omega$ ), OD_DELAY mode          | 95  | 100 | _                | dB   |          |

| Peak THD+N             | OD <sub>THDN</sub> | @ 1 kHz, high impedance load (>1 k $\Omega$ ), XSDM0 mode    | _   | -72 | -61<br>(Note 13) | dB   | ~        |

|                        |                    | @ 1 kHz, low impedance speaker mode, 36R load, XSDM0 mode    | -   | -61 | _                | dB   |          |

|                        |                    | @ 1 kHz, high impedance load (>1 k $\Omega$ ), OD_DELAY mode | -   | -81 | -75              | dB   |          |

| Output noise RMS       | OD <sub>ORN</sub>  | At 1.25 V VBATOD; scales linear-<br>ly with VBATOD           | _   | -   | 4.3              | μV   |          |

| Output Bandwidth       | OD <sub>BW</sub>   |                                                              | -   | -   | 24               | kHz  |          |

| Maximum output current | I <sub>OD</sub>    | This current can be drawn but with degraded audio quality.   | _   | -   | 25               | mA   |          |

| Power supply rejection | OD <sub>PSRR</sub> |                                                              | _   | -30 | -                | dB   |          |

| ratio (PSRR)           |                    | Using VDDOD regulator                                        | _   | -85 | -75              | dB   |          |

NOTE: Output stage specifications are A-weighted, bandwidth 100 Hz-fs/2, sampling frequencies 16/32/48 kHz, with SDM\_CLK = 15.36 MHz, SYS\_CLK = 15.36 MHz (CCO multiplier = 1), and with VDDOD = 1.0 V

NOTE: The performances of the OD are optimized when the SDM\_CLK operates on the CCO base frequency (the un-multiplied frequency).

13. By characterization, the Max value is -65 dB.

#### LSAD

| Parameter          | Symbol                | Conditions                                                   | Min | Тур | Мах | Unit | Screened |

|--------------------|-----------------------|--------------------------------------------------------------|-----|-----|-----|------|----------|

| ADC Resolution     | LSAD <sub>RES</sub>   | Depends on frequency setting                                 | 8   | 12  | 14  | Bits |          |

| Input signal level | LSAD <sub>RANGE</sub> |                                                              | 0   | -   | 1.8 | V    | ~        |

| Sampling rate      | LSAD <sub>SF</sub>    | For a sample clock of 128 kHz<br>(20 cycles per measurement) | _   | 6.4 | -   | kHz  |          |

| lsad_clk frequency | LSAD <sub>CLK</sub>   |                                                              | -   | 100 | 128 | kHz  |          |

| INL                | LSAD <sub>INL</sub>   |                                                              | -2  | -   | +2  | mV   |          |

| DNL                | LSAD <sub>DNL</sub>   |                                                              | -1  | -   | +1  | mV   |          |

| Input Impedance    | LSAD <sub>INI</sub>   |                                                              | 1   | -   | -   | MΩ   |          |

lOs

| Parameter                     | Symbol             | Conditions | Min       | Тур | Max       | Unit | Screened |

|-------------------------------|--------------------|------------|-----------|-----|-----------|------|----------|

| Voltage level of high input   | V <sub>IH</sub>    |            | -         | -   | 0.7x VDDO | V    | ~        |

| Voltage level of low input    | V <sub>IL</sub>    |            | 0.3x VDDO | -   | -         | V    | ~        |

| Voltage level of high output  | V <sub>OH</sub>    |            | 0.8x VDDO | -   | VDDO      | V    | ~        |

| Voltage level of low output   | V <sub>OL</sub>    |            | VSSO      |     | 0.2x VDDO | V    | ~        |

| Weak pull-up Impedance        | IMP <sub>WUP</sub> |            | 225       | 250 | 275       | kΩ   | ~        |

| Medium pull–up<br>Impedance   | IMP <sub>MUP</sub> |            | 45        | 50  | 60        | kΩ   | ~        |

| Medium pull–down<br>Impedance | IMP <sub>MDW</sub> |            | 45        | 50  | 60        | kΩ   | ~        |

#### lOs

| Parameter                             | Symbol                 | Conditions                                                                                                                                | Min                | Тур | Max  | Unit                                               | Screened |

|---------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|------|----------------------------------------------------|----------|

| Strong pull-up<br>Impedance           | IMP <sub>SUP</sub>     |                                                                                                                                           | 0.8                | 1   | 1.2  | kΩ                                                 | ~        |

| Pad Input Delay                       | IN <sub>DELAY</sub>    | VDDO=1.8V                                                                                                                                 | -                  | -   | 0.76 | ns                                                 |          |

|                                       |                        | VDDO=1.2V                                                                                                                                 | -                  | _   | 1.23 | ns                                                 |          |

| Pad Output Delay                      | OUT <sub>DELAY</sub>   | VDDO=1.8V<br>1x drive strength, 1 pF load<br>2x drive strength, 2 pF load<br>4x drive strength, 4 pF load<br>8x drive strength, 8 pF load | _                  | -   | 1.24 | ns                                                 |          |

|                                       |                        | VDDO=1.2V<br>1x drive strength, 1pF load<br>2x drive strength, 2 pF load<br>4x drive strength, 4 pF load<br>8x drive strength, 8 pF load  | _                  | _   | 1.74 | ns                                                 |          |

| Drive Strength                        | DRIVE                  | Configurable with 1x, 2x, 4x, 8x<br>Nominal drive strength: 1 mA                                                                          | 1                  | _   | 8    | Multiple<br>of the<br>nominal<br>drive<br>strength |          |

| Max Switching<br>Frequency            | IOFR <sub>Max</sub>    |                                                                                                                                           | Maximum<br>SYS_CLK | -   | -    |                                                    |          |

| Glitch filter : additional rise delay | DELAY <sub>RAISE</sub> |                                                                                                                                           | -                  | -   | 169  | ns                                                 |          |

| Glitch filter : additional fall delay | DELAY <sub>FALL</sub>  |                                                                                                                                           | -                  | -   | 245  | ns                                                 |          |

NOTE: DC Characteristics of the digital pad at VDDO 1.08/1.8/1.98V

NOTE: The glitch filter cuts glitches with duration shorter than 50 ns

#### CURRENT CONTROLLED OSCILLATOR (CCO)

| Parameter                               | Symbol                                             | Conditions                                                                   | Min  | Тур  | Max   | Unit | Screened |

|-----------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------|------|------|-------|------|----------|

| Recommended Working<br>Frequency        | SYS_CLK                                            | For recommended VDDC and VDDM                                                | 2.56 | -    | 61.44 | MHz  |          |

| Boot frequency                          | SYS_CLK                                            |                                                                              | 5    | 7.68 | 10    | MHz  | ~        |

| Oscillator frequency trimming precision |                                                    |                                                                              | -    | 0.10 | 0.20  | %    |          |

| Frequency stability in temperature      |                                                    | Temp: 0°C and 50°C. After cali-<br>bration at room temperature (25°C)        | -1.5 | -    | 1.5   | %    |          |

|                                         |                                                    | Temp: -40°C and 85°C. After cali-<br>bration at room temperature (25°C)      | -4   | -    | 4     | %    |          |

| Period jitter (rms)                     |                                                    | RMS, at 5.12 MHz, before multiplication                                      | -    | -    | 200   | ps   |          |

|                                         |                                                    | RMS, at 5.12 MHz, after<br>multiplied by 2 and divided by a<br>multiple of 2 | -    | -    | 200   | ps   |          |

|                                         |                                                    | RMS, at 5.12 MHz, after<br>multiplied by 4 and divided by a<br>multiple of 4 | -    | -    | 200   | ps   |          |

| Output duty cycle                       | Dutput duty cycle With multiplier setting 1x or 2x |                                                                              | 45   | -    | 55    | %    |          |

|                                         |                                                    | With multiplier setting 4x                                                   | 40   | -    | 60    | %    |          |

| Max frequency                           |                                                    | Un-multiplied                                                                | -    | 30   | -     | MHz  |          |

#### LOW DELAY PATH (using the low delay path of the Filter Engine)

| Parameter              | Symbol | Conditions                      | Min | Тур  | Max | Unit | Screened |

|------------------------|--------|---------------------------------|-----|------|-----|------|----------|

| Analog to analog delay |        | Fs=48kHz FENG delay: one sample | -   | 10.4 | -   | μs   |          |

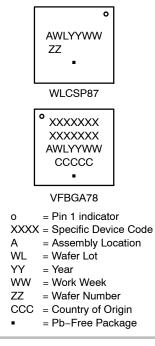

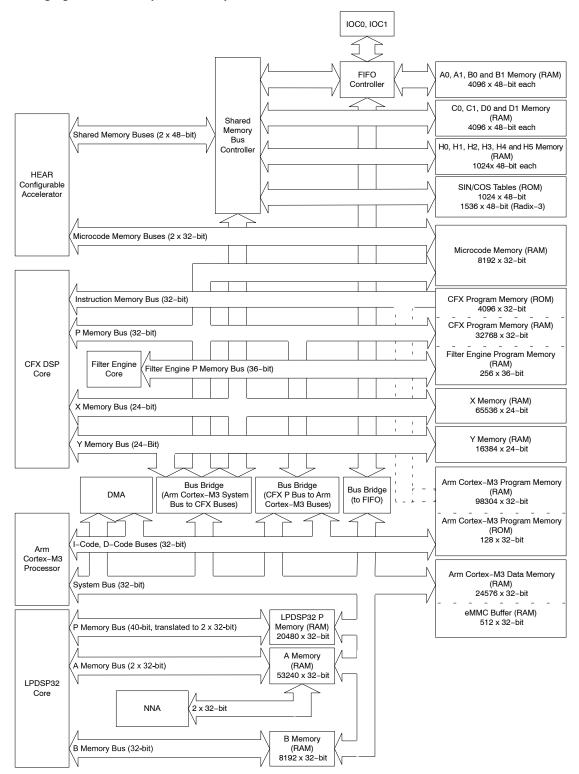

### **EZAIRO 8300 INTERNAL ARCHITECTURE**

The architecture of the Ezairo 8300 is shown on the following diagram:

Figure 1. Ezairo 8300 Architecture

## **ARCHITECTURE OVERVIEW**

The Ezairo 8300 system is an asymmetric 6-core architecture, mixed-signal system-on-chip designed specifically for the audio processing needs ultra-lower power portable devices. It centers around 6 processing cores: the CFX Digital Signal Processor (DSP), the Arm Cortex-M3 Processor, the LPDSP32 Digital Signal Processor (DSP), the HEAR Configurable Accelerator, the Filter Engine and the Neural Network Accelerator.

#### CFX DSP Core

The CFX DSP is a user-programmable general-purpose DSP core that uses a 24-bit fixed-point, dual-MAC, dual-Harvard architecture. It is able to perform two MACs, two memory operations and two pointer updates per cycle, making it well-suited to computationally intensive algorithms.

The CFX DSP is used for custom signal processing applications. The CFX DSP core can also be used as the master of the Ezairo 8300 SoC, by configuring the system and the other cores, by managing the Interrupts and by coordinating the flow of signal data progressing through the system.

The CFX features:

- Dual-MAC 24-bit load-store DSP core

- Four 56-bit accumulators

- Four 24-bit input registers

- Support for hardware loops nested up to four deep

- Combined XY memory space (48 bits wide)

- Dual address generator units

- A wide range of addressing modes:

- Direct

- Indirect with post-modification

- Modulo addressing

- Bit reverse

Software development on the CFX is done in C or assembly, and the development tools are available in the Ezairo 8300 SDK.

In cases where the Arm Cortex–M3 processor is used as the master of the system, the CFX is slave to the Arm Cortex–M3 processor. The inter–processor communication methods between the CFX processor and the rest of Ezairo 8300 are based on shared memories and interrupts.

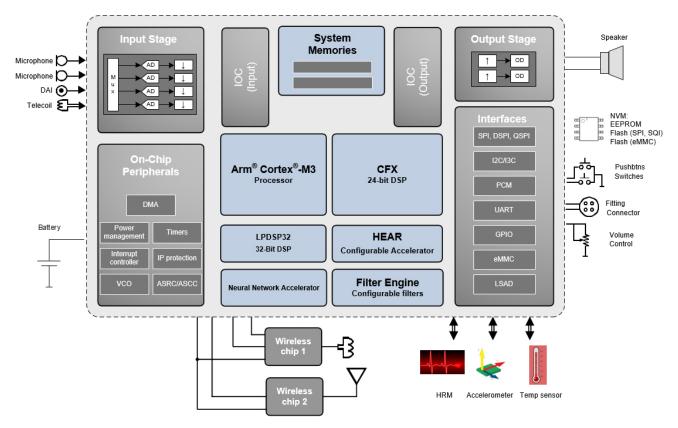

#### **CFX DSP Architecture**

The CFX employs a parallel instruction set for simultaneous control of multiple computation units. The DSP can execute up to four computation operations in parallel with two data transfers (including rounding and/or saturation as well as complex address updates), while simultaneously changing control flow.

The CFX architecture encompasses various memory types and sizes, peripherals, interrupt controllers, and interfaces.

Figure 2 illustrates the basic architecture of the CFX. The control lines shown exiting the PCU indicate that control signals go from the PCU to essentially all other parts of the CFX.

Figure 2. CFX DSP Core Architecture

#### Arm Cortex-M3 Processor

The Arm Cortex–M3 processor is a low–power processor that features low gate count, low interrupt latency, and low–cost debugging. It is intended for deeply embedded applications that require fast interrupt response features.

GNU tools provide build and link support for C programs that run on the Arm Cortex–M3 processor.

The Arm Cortex–M3 processor implements the ARMv7–M architecture. For power management, the processor can be placed into a sleep mode under firmware control in which the processor clock is disabled. The Nested Vectored Interrupt Controller (NVIC) continues to run to enable exiting sleep on an interrupt.

The Arm Cortex–M3 processor typically performs one or more of the following roles:

- The system master, configuring the system and the other cores, by managing the interrupts, and by coordinating the flow of signal data progressing through the system

- A coprocessor to the CFX DSP that provides additional microcontroller computation for interface drivers and protocols executing on those interfaces

- A controller for managing hardware acceleration peripherals such as the Reed–Solomon, G.722 blocks, the asynchronous sample rate converter (ASRC), the audio sink clock counters (ASCC), the neural network

accelerator (NNA), or the LPDSP32 DSP (which is expected to be used for codecs, a neural network, and similar use cases).

In cases where the CFX is used as the master of the system, the Arm Cortex–M3 processor is slave to the CFX. The inter–processor communication methods between the Arm Cortex–M3 processor and the rest of Ezairo 8300 are based on shared memories and interrupts.

#### HEAR Configurable Accelerator

The HEAR coprocessor is designed to perform both common signal processing operations and complex standard filterbanks such as the WOLA filterbank, reducing the load on the system programmable DSP cores.

The HEAR Configurable Accelerator is a highly optimized signal processing engine that is configured through the CFX or Arm Cortex–M3 processor. It offers high speed, high flexibility and high performance, while maintaining low power consumption. For added computing precision, the HEAR supports block floating point processing. Configuration of the HEAR is performed using the HEAR Configuration Tool (HCT). For further information on the usage of the HEAR, refer to the *HEAR Configurable Accelerator Reference Manual*.

The HEAR is optimized for advanced algorithms including but not limited to the following:

- Dynamic range compression

- Directional processing

- Feedback cancellation

- Noise reduction

To execute these and other algorithms efficiently, the HEAR excels at the following:

- Processing using a weighted overlap add (WOLA) filterbank

- Time domain filtering

- Subband filtering

- Attack/release filtering

- Vector addition/subtraction/multiplication

- Signal statistics (such as average, variance and correlation)

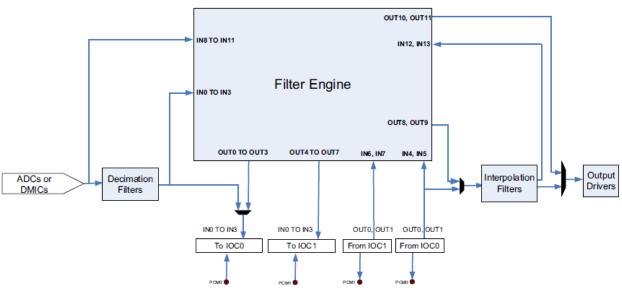

#### Filter Engine

The Filter Engine is a core that provides low-delay path and basic filtering capabilities for the Ezairo 8300 system.

The Filter Engine can implement filters (either FIR or IIR) with a total of up to 320 coefficients. FIR filters are implemented using a direct-form structure. IIR filters are implemented with a cascade of second-order sections (biquads), each implemented as a direct-form I filter.

The Filter Engine is programmable, but does not include direct debugging access. The CFX and the Arm Cortex–M3 Processor can monitor the Filter Engine state through control and configuration registers on the program memory bus.

Figure 3. Filter Engine: Audio Filtering and Multipliexing

#### LPDSP32 DSP

LPDSP32 is a C-programmable, 32-bit DSP developed by ON Semiconductor. LPDSP32 is a high efficiency, dual Harvard DSP that supports both single (32-bit) and double precision (64-bit) arithmetic.

LPDSP32's dual MAC unit, load store architecture is specifically optimized to support audio processing tasks such as audio codecs that might be required for wireless audio communication tasks, Artificial Intelligence (AI) functions, and other advanced developments requiring the additional processing power that this core provides. The advanced architecture also provides:

- Two 72-bit ALUs capable of doing single and double precision arithmetic and logical operations

- Two 32-bit integer/fractional multipliers

- Four 64-bit accumulators with 8-bit overflow (extension bits)

The LPDSP32 relies on the CFX DSP or the Arm Cortex-M3 processor to initialize its memories and

peripherals. Once initialized, the CFX DSP and/or the Arm Cortex–M3 processor control the LPDSP32 DSP's execution state.

Software development on the LPDSP32 is done in C.

#### **Neural Network Accelerator (NNA)**

The Neural Network Accelerator (NNA) is a hardware accelerator block that allows complex neural networks to run in an energy efficient manner. The accelerator can execute a single layer of a fully populated or sparsely populated neural network in a single task without any processor intervention. Layers with up to 1023 inputs and 1023 outputs are supported.

The NNA contains 16 multipliers, 16 accumulators, 16 input registers and 16 coefficient registers. It includes input and coefficient "fetchers" that, once configured, manage the data and coefficients memory access automatically. Support for coefficient compression/decompression and pruning is included and help minimize the amount of coefficient needed.

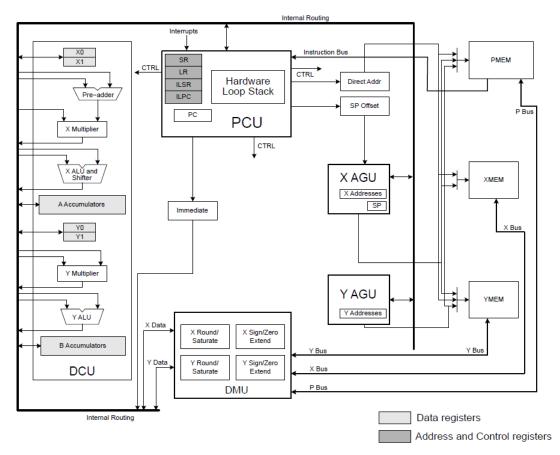

#### **Memory Structure**

The following figure shows the system memory structure. The individual blocks are described in the sections that follow.

Figure 4. System Memory Architecture

#### **FIFO Controller**

The Ezairo 8300 system's FIFO controller provides the ability to define up to 32 FIFO buffers. These FIFOs are

defined as up to eight FIFOs in each of the A0, A1, B0 and B1 memories.

These FIFOs may be used as:

- Input FIFOs as used by the IOC

- Output FIFOs as used by the IOC

- Intermediate FIFOs for transferring data between the CFX, HEAR and Arm Cortex–M3 processor

- Software FIFOs for the CFX DSP or Arm Cortex–M3 processor through the use of access registers

- Each individual FIFO is associated with a set of FIFO configuration registers that are mapped into X memory. Each FIFO can also be associated with one or more of

#### Table 4. CFX MEMORY INSTANCES

the eight FIFO interrupts that are available for the CFX DSP, eight FIFO events that are available for the HEAR, and eight FIFO interrupts that are available for the Arm Cortex–M3 core.

#### Ezairo 8300 Memory Structure

• The following tables list the memory structures attached to the CFX, the Arm Cortex-M3 Core, the HEAR, the LPDSP32, the FENG and the eMMC interface. They include the size and width of each memory structure.

| Memory Structure     | Memory Structure Data Width Memory I |              | Memory Size                     |

|----------------------|--------------------------------------|--------------|---------------------------------|

| Program memory (ROM) | 32                                   | -            | 4096                            |

| Program memory (RAM) | 32                                   | PRAM0, PRAM1 | 2 x 16384 (4 x 16384) (Note 14) |

| X memory (ROM)       | 24                                   | -            | 1280                            |

| X memory (RAM)       | 24                                   | -            | 4 x 16384                       |

| Y memory (RAM)       | 24                                   | YRAM0        | 8192                            |

|                      |                                      | YRAM1, YRAM2 | 2 x 4096                        |

14. The CFX program memory can be extended by assigning the Arm Cortex-M3 processor's program memory sections 0 and 1 to the CFX.

#### Table 5. Arm CORTEX-M3 CORE MEMORY STRUCTURES

| Memory Structure     | Data Width | Name                   | Memory Size                     |

|----------------------|------------|------------------------|---------------------------------|

| Program memory (ROM) | 32         | -                      | 128                             |

| Program memory (RAM) | 32         | CM3_PRAM0 to CM3_PRAM4 | 5 x 16384 (3 x 16384) (Note 15) |

|                      |            | CM3_PRAM5, CM3_PRAM6   | 2 x 8192                        |

| Data memory (RAM)    | 32         | CM3_DRAM0, CM3_DRAM1   | 2 x 8192                        |

|                      |            | CM3_DRAM2, CM3_DRAM3   | 2 x 4096                        |

15. Sections 0 and 1 of the Arm Cortex-M3 processor's program memory can be assigned to the CFX DSP.

#### Table 6. HEAR Memory Structures

| Memory Structure         | Data Width | Name                                          | Memory Size |

|--------------------------|------------|-----------------------------------------------|-------------|

| Microcode memory (RAM)   | 32         | HEAR_MICROCODE_PMEM0,<br>HEAR_MICROCODE_PMEM1 | 2 x 4096    |

| Data memory (RAM)        | 48         | H0, H1, H2, H3, H4, H5 memories               | 6 x 1024    |

| FiFo Memory (RAM)        | 48         | A0, A1, B0, B1 memories                       | 4 x 4096    |

| Coefficient Memory (RAM) | 48         | C0, C1, D0, D1 memories                       | 4 x 4096    |

| Data ROM                 | 48         | SIN/COS LUT                                   | 1024        |

|                          |            | SIN/COS Radix-3 LUT                           | 1536        |

#### Table 7. LPDSP32 CORE MEMORY STRUCTURES

| Memory Structure     | Data Width | Name                   | Memory Size |

|----------------------|------------|------------------------|-------------|

| Program memory (RAM) | 32         | DSP_PRAM0, DSP_PRAM1   | 2 x 2048    |

|                      |            | DSP_PRAM2 to DSP_PRAM5 | 4 x 4096    |

| A memory (RAM)       | 32         | DSP_ARAM0, DSP_ARAM1   | 2 x 8192    |

|                      |            | DSP_ARAM2, DSP_ARAM3   | 2 x 16384   |

|                      |            | DSP_ARAM4, DSP_ARAM5   | 2 x 2048    |

| B Memory (RAM)       | 32         | DSP_BRAM0, DSP_BRAM1   | 2 x 2048    |

|                      |            | DSP_BRAM2              | 2 x 2048    |

#### Table 8. OTHER MEMORY STRUCTURES

| Memory Structure            | Data Width | Memory Size |

|-----------------------------|------------|-------------|

| FENG Program memory (RAM)   | 36         | 256         |

| eMMC interface buffer (RAM) | 32         | 512         |

| Filter Engine State         | 24         | 320         |

| Filter Engine Temp          | 28         | 64          |

| Filter Engine Coefficients  | 28         | 320         |

#### Input/Output Controllers (IOC)

The IOCs are responsible for handling input/output audio data. Samples can be routed along a number of different paths using the multiplexing options available in the Ezairo 8300 system.

#### **Direct Memory Access (DMA) Controller**

The direct memory access controller (DMA) module allows background data transfers between components on the peripheral bus and memories without any processor intervention. This allows the processors to be used for other computational needs while enabling high speed sustained transfers to and from the peripherals/memories. The DMA has 8 independent configurable channels.

Each channel can be configured for one of four modes:

- Data transferred from peripheral-to-memory

- Data transferred from memory-to-peripheral

- Data transferred between peripherals

- Data transferred between memory locations

#### Interrupts

The Ezairo 8300 system contains an interrupt controller linked to the CFX DSP. This controller services all of the Ezairo 8300 interrupt sources, except the private peripheral interrupts and faults of the Arm Cortex–M3 processor.

The Arm Cortex–M3 processor can be used as the master of the Ezairo 8300 system. The Arm Cortex–M3 processor is closely tied to a nested vectored interrupt controller (NVIC), which is an integral part of the processor and provides the interrupt handling functionality. The NVIC services the private peripheral interrupts and faults of the Arm Cortex–M3 processor and all other Ezairo 8300 interrupt sources. The LPDSP32 is linked to an interrupt controller that services interrupts from the DMA, inter–processor communications, and the NNA.

#### Hear Function Chain Controller

The HEAR function chain controller responds to commands from the CFX or from the Arm Cortex–M3 processor, and events from the FIFO controller. It must be configured by the CFX or by the Arm Cortex–M3 processor to enable the triggering of particular function chains within a microcode configuration.

#### Timers

The Ezairo 8300 system provides five timers, including:

- The SysTick timer from the Arm Cortex-M3 processor

- Four general-purpose timers, each of them providing:

- A 24–bit counter

- A 3-bit prescale factor that increases by a factor of 2 at each step, scaling between a prescaler of 1 and 128.

- Three operating modes: single-shot/multiple-shot, free-run, and DIO interrupt capture

- A dedicated interrupt that can be used to signal timer expiration

- Dedicated configuration and status registers

#### Watchdog Timer

The watchdog timer is a programmable hardware timer that operates from the system clock and is used to ensure system sanity. It is always active and must be periodically acknowledged as a check that an application is still running.

Once the watchdog times out, it generates an interrupt. If left to time out a second consecutive time without acknowledgement, a system reset will occur.

#### Algorithm and Data Security

Algorithm software code and user data that requires permanent retention is stored off the Ezairo 8300 chip in separate non-volatile memory. To support this, the Ezairo 8300 chip can gluelessly interface to an external SPI, DSPI or QSPI EEPROM, Flash, or eMMC flash (referred here as external non-volatile memory or NVM).

To prevent unauthorized access to the sensitive intellectual property (IP) stored in the external non–volatile memory, a comprehensive system is in place to protect manufacturer's application code and data.

To protect the IP stored in the external non-volatile memory, the system supports decoding algorithm and data sections belonging to an application that have been encrypted using the Advanced Encryption Standard (AES) and stored in non-volatile memory. While system access restrictions are in place, the keys used in the decryption of these sections will be secured from external access by the regular access restrictions.

When the system is externally "unlocked" these keys will be cleared, preventing their use in decoding an application by unauthorized parties. After un-restricting access in this way the system may then be restored by re-programming the decryption keys.

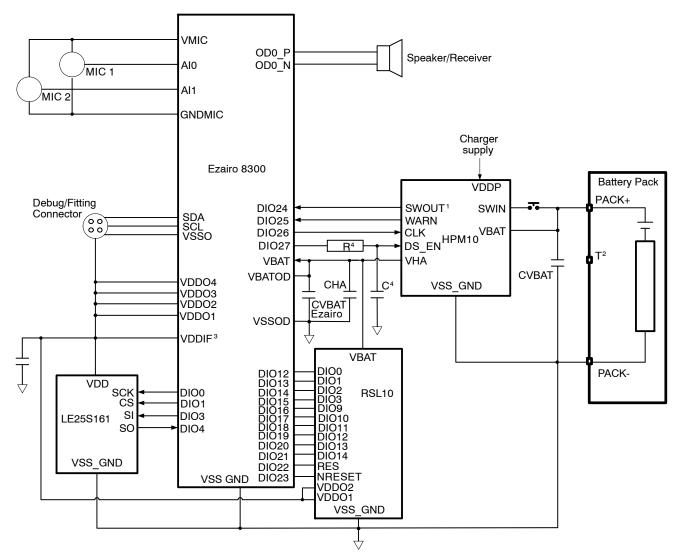

#### Input Stage

The input stage of an Ezairo 8300 provides four audio input channels that supply signal data to the rest of the Ezairo 8300 system. Each input channel includes:

- Input selection using an analog multiplexer to select between the input source from the available input sources and reference inputs

- Available line–out for the selected input signal

- An over-sampling analog-to-digital converter (ADC) which uses a programmable sampling frequency and provides a configurable sampling delay, useful in beam-forming applications.

- Selectable digital microphone inputs and bypass registers that can source data in place of the ADCs

- High-quality decimation filtering at all selectable sampling rates

- Selectable input muting

Each of the input channels from the Ezairo 8300 system can optionally source their input data from a digital microphone (DMIC input) instead of the channel's ADC.

#### **Output Stage**

The output stage of Ezairo 8300 provides two audio output channels that post-process signal data from the rest of the Ezairo 8300 system, and provide it to external receivers or speakers. The output channels include:

- High-quality interpolation filtering that automatically tracks the selected sample rate of the sigma-delta Modulator

- An ultra-low-power, high fidelity, over-sampled sigma-delta modulator with programmable sample rate

- A low-impedance direct digital output driver, driven by a pulse-density modulated signal, for zero-bias hearing aid or headset receivers

- Selectable digital microphone outputs that can sink data in parallel with either output channel

#### Digital Input/Output (DIO) Pads

The Ezairo 8300 system contains 36 digital input/output (DIO) pads that can be configured:

- To support the external interfaces, output clocks, and other I/Os

- As general-purpose I/Os (GPIO)

- Analog input/output function

The 36 DIOs are split into four power domains. The voltages for these 4 power domains are given by the VDDO1 pad (for DIO0 to DIO11), the VDDO2 pad (for DIO12 to DIO23), the VDDO3 pad (for DIO24 to DIO29) and the VDDO4 pad (for DIO30 to DIO35).

The NRESET, SDA and SCL pads are on the VDDO4 power domain.

## **EXTERNAL INTERFACEs**

#### General-Purpose Input/Output (GPIO)

Ezairo 8300 can configure any, or all, of the 36 DIO pads as software–controlled general–purpose DIO (GPIO) pads. The function of these GPIO pads is defined by the user application, which can use them for any general–purpose input or output. Each GPIO pad can be configured to generate interrupts to the CFX DSP and/or Arm Cortex-M3 processor.

#### **PCM Interface**

The Ezairo 8300 system includes two highlyconfigurable pulse code modulation (PCM) interfaces that can be used to stream signal, control and configuration data in and out of the device.

Each PCM interface connects to the processors through the Arm Cortex–M3 processor's peripheral bus. There are three possible ways PCM interfaces can handle transmission and reception buffers:

- By using the internally available data transmission and reception interrupts.

- By connecting to the DMA with two channels supporting transmit and receive operations.

- By connecting to the IOC with four FIFOs supporting transmit and receive operations. Each data channel for PCM transmit and receive buffers requires its own FIFO-as opposed to the case for using DMA, which allows one DMA channel to support both channel 0 and channel 1 for PCM.

Each PCM interface can be configured to generate interrupts to the CFX DSP and/or Arm Cortex–M3 processor.

#### SPI Interface

The Ezairo 8300 system includes two Serial Peripheral Interfaces (SPIs). Each SPI interface supports single and dual I/O modes, as well as the ability to add two additional I/O pins in a quad I/O mode.

The SPI interfaces allow the system to communicate with external components, including external analog front ends, external controllers, wireless transceivers, and non-volatile memories (NVMs).

The SPI interfaces support master/slave configuration as well as half/full duplex mode.

Each SPI interface can be configured to generate interrupts to the CFX DSP and/or Arm Cortex–M3 processor. Similarly, data transfers can be controlled by any of the host processors.

#### **UART Interface**

The general-purpose UART interface provides support for communicating with devices that use standard UART and RS-232 transmission protocols.

The UART Interface can be configured to generate interrupts to the CFX DSP and/or Arm Cortex–M3 processor. Similarly, data transfers can be controlled by any of the host processors.

#### Low-Speed A/D Converters (LSAD)

The purpose of the LSAD converters is to sample voltages that typically change slowly, such as the voltage associated with a potentiometer–based volume control.

The LSADs provide an analog to digital conversion of up to eight signals, from a combination of four internal signals

and four external signals. The LSAD provided 14 bits of resolution, at sampling rates up to 8 kHz.

The LSAD can be configured to generate interrupts to the CFX DSP and/or Arm Cortex–M3 processor. Similarly, data can be read by any of the host processors.

#### I<sup>2</sup>C Interface

The Ezairo 8300 includes 3 instances of  $I^2C$  interface, which are compatible with the Inter–IC Bus Specification from NXP Semiconductors.  $I^2C$  interfaces are typically used for communication with external sensors and storage devices, and as control signals for wireless radios.

The I<sup>2</sup>C Interface can be configured to generate interrupts to the CFX DSP and/or Arm Cortex–M3 processor. Similarly, data transfers can be controlled by any of the host processors. Maximum I<sup>2</sup>C SCL frequency is provided in the Ezairo 8300 Hardware Reference Manual.

#### I<sup>3</sup>C Interface

The Ezairo 8300 includes 2 instances of I<sup>3</sup>C interface which are compatible with the Improved Inter–IC Bus Specification from the MIPI Alliance. The I<sup>3</sup>C uses a two–wire interface including a bidirectional clock line (SCL) and a bidirectional data line (SDA). I<sup>3</sup>C is designed to enhance sensor system design architectures in mobile wireless products by providing a fast, low cost, low power, two–wire digital interface for sensors.

The I<sup>3</sup>C Interface can be configured to generate interrupts to the CFX DSP and/or Arm Cortex–M3 processor. Similarly, data transfers can be controlled by any of the host processors.

#### eMMC Interface

eMMC memory (Embedded MultiMedia Card memory) is a low-cost, high performance Flash memory that is designed for a wide range of applications in consumer electronics such as mobile phones, handheld computers, navigational systems, portable gaming and even industrial uses.

The eMMC interface of Ezairo 8300 implements the Host Controller portion of an eMMC link and can also be used to access SD cards.

The eMMC Interface can be configured to generate interrupts to the CFX DSP and/or Arm Cortex–M3 processor. Similarly, data transfers can be controlled by any of the host processors.

#### **Debug Ports**

#### I2C Debug Ports for the CFX and the Arm Cortex-M3

The I2C debug ports for the Ezairo 8300 system provide both the CFX DSP and Arm Cortex–M3 processor with a full debugging capacity.

The CFX DSP debug port coexists with the Arm Cortex–M3 processor debug port on the same I2C bus. One of the three general purpose I2C interface can be used on the

same bus. Each debug port will respond to debug commands on its I2C address.

#### SWJ-DP Debug Port for the Arm Cortex-M3

The Ezairo 8300 system contains a standard Core Sight SWJ-DP debug port for the Arm Cortex-M3 processor. This debug controller is used to provide access to all of the Arm Cortex-M3 processor registers, and to all of the Ezairo 8300 memories through the memory buses attached to the Arm Cortex-M3 processor. By default, the SWJ-DP is accessed using the JTAG connection that uses DIOs 30 to 33, to form a 4-wire JTAG interface. This debug port can be reconfigured for serial-wire mode using only DIOs 30 and 31.

The Arm Cortex-M3 processor's SWJ-DP debug port can be used as a bridge to the CFX I<sup>2</sup>C debug port through a memory-mapped register.

#### Standard JTAG debug port for the LPDSP32

The LPDSP32 is supported by a JTAG debug interface that can be assigned to a set of DIO pads.

#### **Other Peripherals**

#### **Clock-Generation Circuitry and Synchronization**

The main system clock is typically generated by a current–controlled oscillator (CCO) that can be configured for frequencies from 1.28 MHz to 61.44 MHz. Other needed clocks are derived from the main system clock.

An Asynchronous Sample Rate Converter (ASRC) and Audio Sink Clock Counters blocks to provide a means of synchronizing the audio sample rate between the radio link and the host device.

#### Power Supervisory Unit

The power supervisory unit monitors the battery supply voltage (VBAT) and the internal analog and digital supply voltages (VDDA, VDDC, VDDM), safely shutting down the system without user intervention when the supply voltages are below the thresholds required for valid system operation.

This unit is used to ensure that the system operates correctly and is not damaged by the power supply fluctuations that are encountered when a battery is inserted or removed from a hearing aid.

#### Power-on-Reset (POR)

The Ezairo 8300 device uses a power-on-reset (POR) sequence to ensure proper system behavior during startup, and to ensure proper system configuration after startup. At the start of the POR sequence, audio output is disabled and all configuration and control registers are asynchronously reset to their default values.

At the start of the POR sequence, the core registers for all five of the system's cores are cleared and the contents of all RAM is unspecified.

#### **EZAIRO 8300 PAD SPECIFICATIONS**

| Pad Name | Description                               | Power<br>Domain | Туре | Pull | Pad #, WLCSP | Pad #, BGA |

|----------|-------------------------------------------|-----------------|------|------|--------------|------------|

| VBAT     | Battery input voltage                     | VBAT            | Р    |      | C2, D2       | D6, C7, D7 |

| VDDA     | Analog power supply                       | VDDA            | Р    |      | B2           | B8         |

| VDDA_C0  | Analog charge pump cap terminal 0         |                 | Α    |      | C1           | B9         |

| VDDA_C1  | Analog charge pump cap terminal 1         |                 | Α    |      | B1           | A9         |

| VREG     | Regulated voltage output                  |                 | AO   |      | A1           | B7         |

| VMIC     | Microphone power supply                   |                 | AO   |      | B3           | B6         |

| VSSA     | Analog ground                             |                 | Р    |      | B4           | A8, C6     |

| GNDMIC   | Input Transducer ground                   |                 | AO   |      | B5           | B5         |

| Al0      | ADC analog input 0                        |                 | AI   |      | A2           | A7         |

| Al1      | ADC analog input 1                        |                 | AI   |      | A3           | A6         |

| Al2      | ADC analog input 2                        |                 | AI   |      | A4           | A5         |

| Al3      | ADC analog input 3                        |                 | AI   |      | A5           | A4         |

| VDDIF    | Interface power supply                    | VDDIF           | Р    |      | E2           | D8         |

| VDDIF_C0 | Interface power supply cap terminal 0     |                 | А    |      | D1           | D9         |

| VDDIF_C1 | Interface power supply cap terminal 1     |                 | А    |      | E1           | C9         |

| OD0_P    | Output Driver: Receiver Output 0 Positive | VBATOD          | AO   |      | F1           | E8         |