OBSOLETE PRODUCT

NO RECOMMENDED REPLACEMENT

contact our Technical Support Center at

1-888-INTERSIL or www.intersil.com/tsc

January 2004

FN2907.5

# 2.5MHz, Precision Operational Amplifier

The Intersil HA-5135 is a precision operational amplifier manufactured using a combination of key technological advancements to provide outstanding input characteristics.

A Super Beta input stage is combined with laser trimming, dielectric isolation and matching techniques to produce  $75\mu V$  (Maximum) input offset voltage and  $0.4\mu V/^{O}C$  input offset voltage average drift. Other features enhanced by this process include  $9nV/\sqrt{Hz}$  (Typ) Input Noise Voltage, 1nA Input Bias Current and 140dB Open Loop Gain.

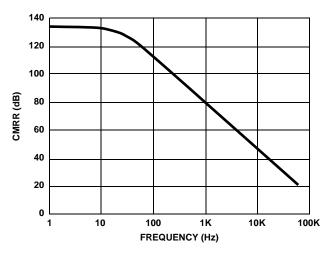

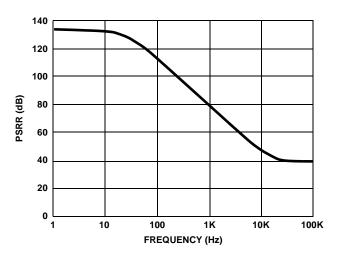

These features coupled with 120dB CMRR and PSRR make the HA-5135 an ideal device for precision DC instrumentation amplifiers. Excellent input characteristics in conjunction with 2.5MHz bandwidth and 0.8V/ $\mu$ s slew rate, make this amplifier extremely useful for precision integrator and biomedical amplifier designs. This amplifier is also well suited for precision data acquisition and for accurate threshold detector applications.

HA-5135 offers added features over the industry standard OP-07 in regards to bandwidth and slew rate specifications. For the military grade product, refer to the HA-5135/883 data sheet.

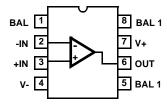

#### **Pinout**

#### HA-5135 (CERDIP) TOP VIEW

NOTE: Both BAL 1 pins are connected together internally.

#### Features

| • | Low Offset Voltage                         |

|---|--------------------------------------------|

| • | Low Offset Voltage Drift $0.4 \mu V/^{0}C$ |

| • | Low Noise                                  |

| • | Open Loop Gain                             |

| • | Unity Gain Bandwidth                       |

|   |                                            |

#### · All Bipolar Construction

## **Applications**

- High Gain Instrumentation

- · Precision Data Acquisition

- · Precision Integrators

- · Biomedical Amplifiers

- · Precision Threshold Detectors

#### Part Number Information

| PART NUMBER | TEMP.<br>RANGE (°C) | PACKAGE     | PKG.<br>NO. |

|-------------|---------------------|-------------|-------------|

| HA7-5135-5  | 0 to 75             | 8 Ld CERDIP | F8.3A       |

### **Absolute Maximum Ratings**

####

#### **Thermal Information**

| CERDIP Package                                | Thermal Resistance (Typical, Note 2)  | $\theta_{JA}$ (oC/W) | θ <sub>JC</sub> (oC/M)                 |

|-----------------------------------------------|---------------------------------------|----------------------|----------------------------------------|

| Maximum Storage Temperature Range65°C to 150° | CERDIP Package                        | 115                  | 28                                     |

|                                               |                                       |                      |                                        |

| Maximum Lead Temperature (Soldering 10s) 300° | Maximum Storage Temperature Range .   | 6                    | 5 <sup>0</sup> C to 150 <sup>0</sup> C |

|                                               | Maximum Lead Temperature (Soldering 1 | 0s)                  | 300°C                                  |

## **Operating Conditions**

| Temperature Ranges |             |

|--------------------|-------------|

| HA-5135-5          | 0°C to 75°C |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

- 1. Maximum power dissipation, including output load, must be designed to maintain the maximum junction temperature below 175°C.

- 2.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

### **Electrical Specifications** $V_{SUPPLY} = \pm 15V$

|                               |                                        | TEMP. | HA-5135-5 |      |      |                    |

|-------------------------------|----------------------------------------|-------|-----------|------|------|--------------------|

| PARAMETER                     | TEST CONDITIONS                        | (°C)  | MIN       | TYP  | MAX  | UNITS              |

| INPUT CHARACTERISTICS         | ·                                      |       |           | 1    |      |                    |

| Offset Voltage                |                                        | 25    | -         | 10   | 75   | μV                 |

|                               |                                        | Full  | -         | 50   | 130  | μV                 |

| Average Offset Voltage Drift  |                                        | Full  | -         | 0.4  | 1.3  | μV/ <sup>o</sup> C |

| Bias Current                  |                                        | 25    | -         | ±1   | ±4   | nA                 |

|                               |                                        | Full  | -         | -    | ±6   | nA                 |

| Bias Current Average Drift    |                                        | Full  | -         | 0.02 | 0.04 | nA/ <sup>o</sup> C |

| Offset Current                |                                        | 25    | -         | -    | 4    | nA                 |

|                               |                                        | Full  | -         | -    | 5.5  | nA                 |

| Offset Current Average Drift  |                                        | Full  | -         | 0.02 | 0.04 | nA/ <sup>o</sup> C |

| Common Mode Range             |                                        | Full  | ±12       | -    | -    | V                  |

| Differential Input Resistance |                                        | 25    | 20        | 30   | -    | ΜΩ                 |

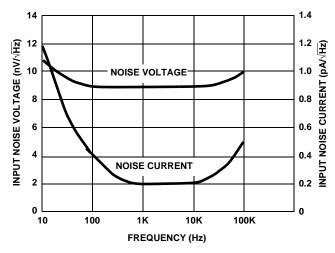

| Input Noise Voltage (Note 3)  | 0.1Hz to 10Hz                          | 25    | -         | -    | 0.6  | μV <sub>P-P</sub>  |

| Input Noise Voltage Density   | f = 10Hz                               | 25    | -         | 13.0 | 18.0 | nV/√Hz             |

| (Note 3)                      | f = 100Hz                              |       | -         | 10.0 | 13.0 | nV/√Hz             |

|                               | f = 1000Hz                             |       | -         | 9.0  | 11.0 | nV/√Hz             |

| Input Noise Current (Note 3)  | 0.1Hz to 10Hz                          | 25    | -         | 15   | 30   | pA <sub>P-P</sub>  |

| Input Noise Current Density   | f = 10Hz                               | 25    | -         | 0.4  | 0.8  | pA/√Hz             |

| (Note 3)                      | f = 100Hz                              |       | -         | 0.17 | 0.23 | pA/√Hz             |

|                               | f = 1000Hz                             |       | -         | 0.14 | 0.17 | pA/√Hz             |

| TRANSFER CHARACTERISTICS      | 1                                      |       |           |      |      |                    |

| Large Signal Voltage Gain     | $V_{OUT} = \pm 10V$ , $R_L = 2k\Omega$ | 25    | 120       | 140  | -    | dB                 |

|                               |                                        | Full  | 120       | -    | -    | dB                 |

| Common Mode Rejection Ratio   | V <sub>CM</sub> = ±10V                 | Full  | 106       | 120  | -    | dB                 |

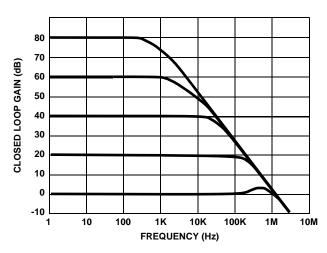

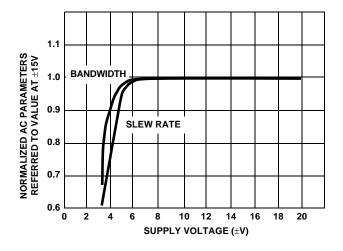

| Closed Loop Bandwidth         | A <sub>VCL</sub> = +1                  | 25    | 0.6       | 2.5  | -    | MHz                |

| OUTPUT CHARACTERISTICS        | '                                      |       | ı         |      | 1    | 1                  |

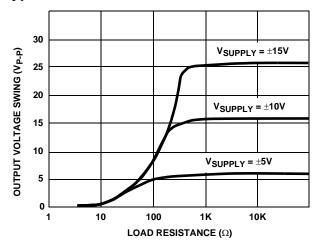

| Output Voltage Swing          | $R_L = 600\Omega$                      | 25    | ±10       | ±12  | -    | V                  |

|                               |                                        | Full  | ±10       | -    | -    | V                  |

# **Electrical Specifications** $V_{SUPPLY} = \pm 15V$ (Continued)

|                               | TF                          | TEMP. | HA-5135-5 |     |     |       |  |

|-------------------------------|-----------------------------|-------|-----------|-----|-----|-------|--|

| PARAMETER                     | TEST CONDITIONS             |       | MIN       | TYP | MAX | UNITS |  |

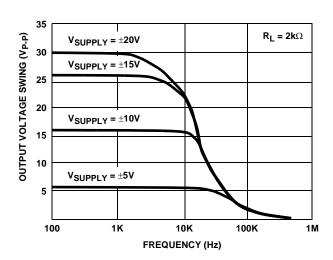

| Full Power Bandwidth (Note 4) | $R_L = 2k\Omega$            | 25    | 8         | 10  | -   | kHz   |  |

| Output Current                | V <sub>OUT</sub> = 10V      | 25    | ±15       | ±20 | -   | mA    |  |

| Output Resistance             | Note 5                      | 25    | -         | 45  | -   | Ω     |  |

| TRANSIENT RESPONSE (Note 6)   |                             |       |           |     |     |       |  |

| Rise Time                     |                             | 25    | -         | 340 | -   | ns    |  |

| Slew Rate                     |                             | 25    | 0.5       | 0.8 | -   | V/μs  |  |

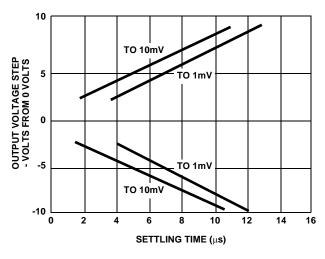

| Settling Time (Note 7)        |                             | 25    | -         | 11  | -   | μЅ    |  |

| POWER SUPPLY CHARACTERISTICS  |                             |       |           |     |     |       |  |

| Supply Current                |                             | Full  | -         | 1.0 | 1.7 | mA    |  |

| Power Supply Rejection Ratio  | $V_S = \pm 5V$ to $\pm 20V$ | Full  | 94        | 130 | -   | dB    |  |

#### NOTES:

- 3. Not tested. 90% of units meet or exceed these specifications.

- 4. Full power bandwidth guaranteed based on slew rate measurement using: FPBW =  $\frac{\text{Slew Rate}}{2\pi \text{ V}_{\text{PEAK}}}$

- 5. Output resistance measured under open loop conditions (f = 100Hz).

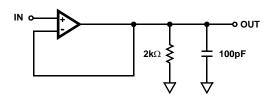

- 6. Refer to test circuits section of the data sheet.

- 7. Settling time is measured to 0.1% of final value for a 10V output step and  $A_V = -1$ .

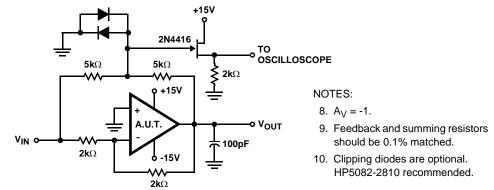

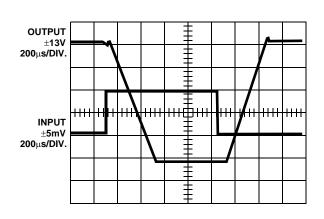

## Test Circuits and Waveforms

FIGURE 1. SLEW RATE AND TRANSIENT RESPONSE TEST CIRCUIT

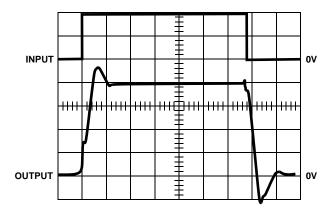

Vertical Scale: Input = 50mV/Div. Output = 100mV/Div. Horizontal Scale: 1µs/Div.

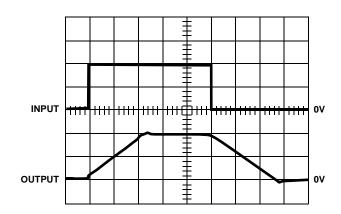

Vertical Scale: 5V/Div. Horizontal Scale: 5µs/Div.

**SMALL SIGNAL RESPONSE**

LARGE SIGNAL RESPONSE

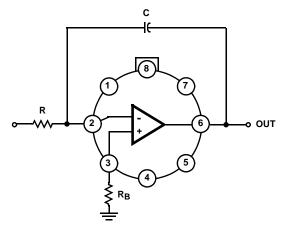

# Test Circuits and Waveforms (Continued)

FIGURE 2. SETTLING TIME CIRCUIT

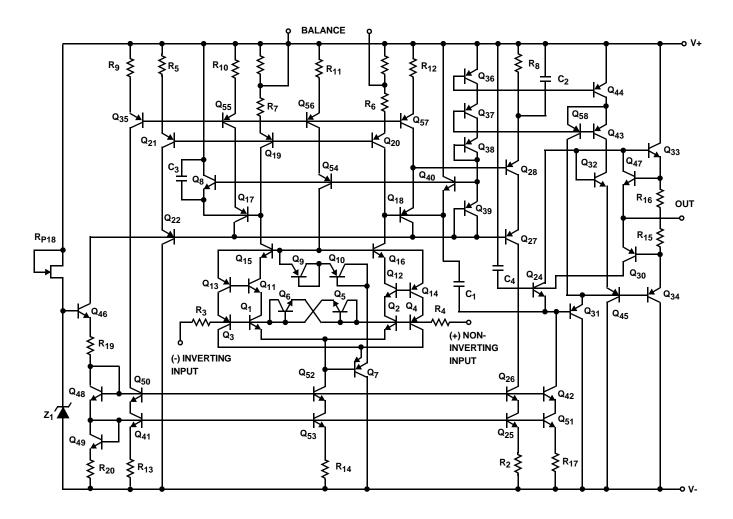

# Schematic Diagram

## Application Information

#### **Power Supply Decoupling**

Although not absolutely necessary, it is recommended that all power supply lines be decoupled with  $0.01\mu F$  ceramic capacitors to ground. Decoupling capacitors should be located as near to the amplifier terminals as possible.

#### Considerations For Prototyping:

The following list of recommendations are suggested for prototyping.

- Resolving low level signals requires minimizing leakage currents caused by external circuitry. Use of quality insulating materials, thorough cleaning of insulating surfaces and implementation of moisture barriers when required is suggested.

- Error voltages generated by thermocouples formed between dissimilar metals in the presence of temperature gradients should be minimized. Isolation of low level circuity from heat generating components is recommended.

- 3. Shielded cable input leads, guard rings and shield drivers are recommended for the most critical applications.

### Large Capacitive Loads

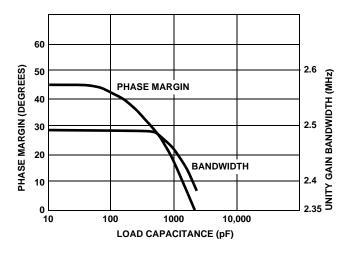

When driving large capacitive loads (>500pF), a small value resistor ( $\approx$ 50 $\Omega$ ) should be connected in series with the output and inside the feedback loop.

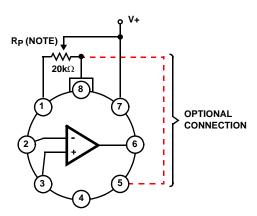

#### Offset Voltage Adjustment (See Figure 3)

A  $20k\Omega$  balance potentiometer is recommended if offset nulling is required. However, other potentiometer values such as  $10k\Omega$ ,  $50k\Omega$  and  $100k\Omega$  may be used. The minimum adjustment range for given values is  $\pm 2$ mV.  $V_{OS}$  TC of the amplifier is optimized at minimal  $V_{OS}$ . Tested Offset Adjustment is  $|V_{OS} + 1$ mV| minimum referred to output.

FIGURE 3. OFFSET NULLING CONNECTIONS

#### Saturation Recovery

Input and output saturation recovery time is negligible in most applications. However, care should be exercised to avoid exceeding the absolute maximum ratings of the device.

#### Differential Input Voltages

Inputs are shunted with back-to-back diodes for overvoltage protection. In applications where differential input voltages in excess of 1V are applied between the inputs, the use of limiting resistors at the inputs is recommended.

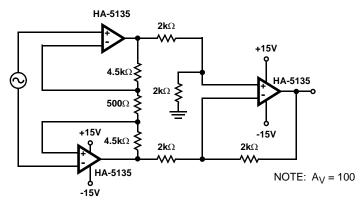

## Typical Applications

The excellent input and gain characteristics of HA-5135 are well suited for precision integrator applications. Accurate integration over seven decades of frequency using HA-5135, virtually nullifies the need for more expensive chopper-type amplifiers.

**FIGURE 4. PRECISION INTEGRATOR**

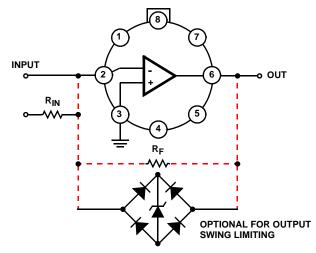

Low  $V_{\mbox{OS}}$  coupled with high open loop Gain, high CMRR and high PSRR make HA-5135 ideally suited for precision detector applications, such as the zero crossing detector shown in Figure 5.

FIGURE 5. ZERO CROSSING DETECTOR

FIGURE 6. PRECISION INSTRUMENTATION AMPLIFIER

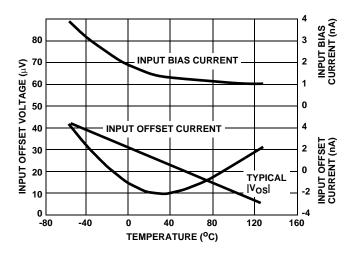

# **Typical Performance Curves**

FIGURE 7. INPUT OFFSET VOLTAGE, INPUT BIAS AND OFFSET CURRENT vs TEMPERATURE

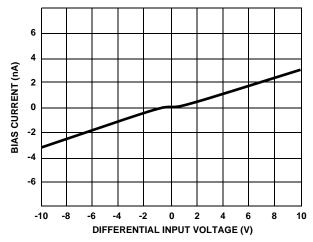

FIGURE 8. INPUT BIAS CURRENT vs DIFFERENTIAL INPUT VOLTAGE

## Typical Performance Curves (Continued)

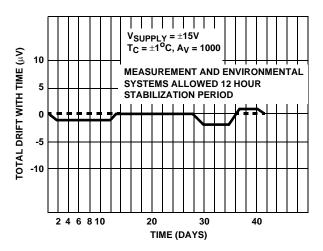

FIGURE 9. HA-5135 OFFSET VOLTAGE STABILITY vs TIME

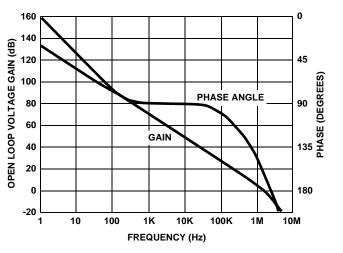

FIGURE 11. OPEN LOOP FREQUENCY RESPONSE

FIGURE 13. SMALL SIGNAL BANDWIDTH AND PHASE MARGIN vs LOAD CAPACITANCE

FIGURE 10. INPUT NOISE vs FREQUENCY

FIGURE 12. CLOSED LOOP FREQUENCY RESPONSE

FIGURE 14. OUTPUT VOLTAGE SWING vs FREQUENCY

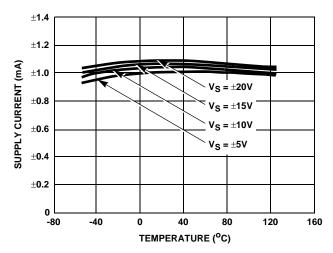

# Typical Performance Curves (Continued)

FIGURE 15. MAXIMUM OUTPUT VOLTAGE SWING vs LOAD RESISTANCE

FIGURE 17. CMRR vs FREQUENCY

FIGURE 19. SETTLING TIME FOR VARIOUS OUTPUT STEP VOLTAGES

FIGURE 16. NORMALIZED AC PARAMETERS vs SUPPLY VOLTAGE

FIGURE 18. PSRR vs FREQUENCY

FIGURE 20. POWER SUPPLY CURRENT vs TEMPERATURE

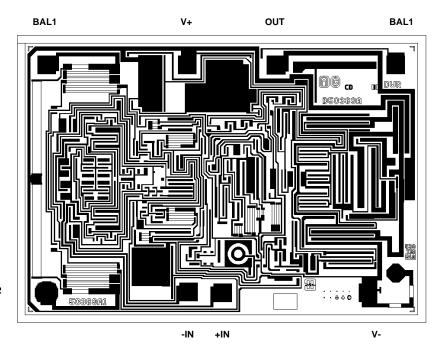

# Die Characteristics

#### **DIE DIMENSIONS:**

72 mils x 103 mils x 19 mils  $(1840\mu m \ x \ 2620\mu m \ x \ 483\mu m)$

#### **METALLIZATION:**

Type: Al, 1% Cu Thickness: 16kÅ ±2kÅ

### SUBSTRATE POTENTIAL (POWERED UP):

V-

# Metallization Mask Layout

#### **PASSIVATION:**

Type: Nitride (Si $_3$ N $_4$ ) over Silox (SiO $_2$ , 5% Phos.) Silox Thickness: 12kÅ  $\stackrel{+}{_{\sim}}$ 2kÅ

Nitride Thickness: 3.5kÅ ±1.5kÅ

#### TRANSISTOR COUNT:

71

#### PROCESS:

Bipolar Dielectric Isolation

HA-51350

BAL2

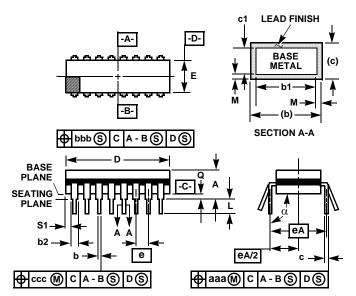

## Ceramic Dual-In-Line Frit Seal Packages (CERDIP)

#### NOTES:

- Index area: A notch or a pin one identification mark shall be located adjacent to pin one and shall be located within the shaded area shown. The manufacturer's identification shall not be used as a pin one identification mark.

- The maximum limits of lead dimensions b and c or M shall be measured at the centroid of the finished lead surfaces, when solder dip or tin plate lead finish is applied.

- Dimensions b1 and c1 apply to lead base metal only. Dimension M applies to lead plating and finish thickness.

- Corner leads (1, N, N/2, and N/2+1) may be configured with a partial lead paddle. For this configuration dimension b3 replaces dimension b2.

- 5. This dimension allows for off-center lid, meniscus, and glass overrun

- 6. Dimension Q shall be measured from the seating plane to the base plane.

- 7. Measure dimension S1 at all four corners.

- 8. N is the maximum number of terminal positions.

- 9. Dimensioning and tolerancing per ANSI Y14.5M 1982.

- 10. Controlling dimension: INCH

F8.3A MIL-STD-1835 GDIP1-T8 (D-4, CONFIGURATION A) 8 LEAD CERAMIC DUAL-IN-LINE FRIT SEAL PACKAGE

|        | INCHES MILLIMETERS |                  |          |                  |       |

|--------|--------------------|------------------|----------|------------------|-------|

| SYMBOL | MIN                | MAX              | MIN      | MAX              | NOTES |

| Α      | -                  | 0.200            | -        | 5.08             | -     |

| b      | 0.014              | 0.026            | 0.36     | 0.66             | 2     |

| b1     | 0.014              | 0.023            | 0.36     | 0.58             | 3     |

| b2     | 0.045              | 0.065            | 1.14     | 1.65             | -     |

| b3     | 0.023              | 0.045            | 0.58     | 1.14             | 4     |

| С      | 0.008              | 0.018            | 0.20     | 0.46             | 2     |

| c1     | 0.008              | 0.015            | 0.20     | 0.38             | 3     |

| D      | -                  | 0.405            | -        | 10.29            | 5     |

| Е      | 0.220              | 0.310            | 5.59     | 7.87             | 5     |

| е      | 0.100              | BSC              | 2.54     | -                |       |

| eA     | 0.300              | BSC              | 7.62     | -                |       |

| eA/2   | 0.150              | BSC              | 3.81 BSC |                  | -     |

| L      | 0.125              | 0.200            | 3.18     | 5.08             | -     |

| Q      | 0.015              | 0.060            | 0.38     | 1.52             | 6     |

| S1     | 0.005              | -                | 0.13     | -                | 7     |

| α      | 90°                | 105 <sup>0</sup> | 90°      | 105 <sup>0</sup> | -     |

| aaa    | -                  | 0.015            | - 0.38   |                  | -     |

| bbb    | -                  | 0.030            | - 0.76   |                  | -     |

| ccc    | -                  | 0.010            | - 0.25   |                  | -     |

| М      | -                  | 0.0015           | - 0.038  |                  | 2, 3  |

| N      | 8                  | 3                | 8        | 8                |       |

Rev. 0 4/94

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com