# RS8953B

© 1999, 2000, Conexant Systems, Inc. All Rights Reserved.

Information in this document is provided in connection with Conexant Systems, Inc. ("Conexant") products. These materials are provided by Conexant as a service to its customers and may be used for informational purposes only. Conexant assumes no responsibility for errors or omissions in these materials. Conexant may make changes to specifications and product descriptions at any time, without notice. Conexant makes no commitment to update the information and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to its specifications and product descriptions.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Conexant's Terms and Conditions of Sale for such products, Conexant assumes no liability whatsoever.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF CONEXANT PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. CONEXANT FURTHER DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. CONEXANT SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE OF THESE MATERIALS.

Conexant products are not intended for use in medical, lifesaving or life sustaining applications. Conexant customers using or selling Conexant products for use in such applications do so at their own risk and agree to fully indemnify Conexant for any damages resulting from such improper use or sale.

The following are trademarks of Conexant Systems, Inc.: Conexant<sup>™</sup>, the Conexant C symbol, and "What's Next in Communications Technologies" TM. Product names or services listed in this publication are for identification purposes only, and may be trademarks of third parties. Third-party brands and names are the property of their respective owners.

For additional disclaimer information, please consult Conexant's Legal Information posted at <a href="https://www.conexant.com">www.conexant.com</a>, which is incorporated by reference.

Reader Response: Conexant strives to produce quality documentation and welcomes your feedback. Please send comments and suggestions to tech.pubs@conexant.com. For technical questions, contact your local Conexant sales office or field applications engineer.

100418C Conexant

## **Table of Contents**

|     | List of Figuresxii |                                              |  |  |  |  |  |

|-----|--------------------|----------------------------------------------|--|--|--|--|--|

|     | List               | of Tables                                    |  |  |  |  |  |

| 1.0 | Intro              | oduction                                     |  |  |  |  |  |

|     | 1.1                | What's New in Channel Unit Version 6.x       |  |  |  |  |  |

|     |                    | 1.1.1 Bt8953A Revision C and RS8953B Support |  |  |  |  |  |

|     |                    | 1.1.2 RS8973 versus Bt8970 Line Card Support |  |  |  |  |  |

|     |                    | 1.1.3 EOC Protocol                           |  |  |  |  |  |

|     |                    | 1.1.4 Dynamic Loop Reversal and Master Loop  |  |  |  |  |  |

|     |                    | 1.1.5 Performance Monitoring                 |  |  |  |  |  |

|     |                    | 1.1.6 Channel Blocking                       |  |  |  |  |  |

|     |                    | 1.1.7 Bt8370 Support                         |  |  |  |  |  |

|     | 1.2                | Features and Functionality Not Supported     |  |  |  |  |  |

| 2.0 | EVM Specific       |                                              |  |  |  |  |  |

|     | 2.1                | HDSL EVM Hardware                            |  |  |  |  |  |

|     |                    | 2.1.1 DIP Switch                             |  |  |  |  |  |

|     |                    | 2.1.2 Channel Unit LEDs                      |  |  |  |  |  |

|     | 2.2                | General Purpose Timers                       |  |  |  |  |  |

|     |                    | 2.2.1 Continuous Mode                        |  |  |  |  |  |

|     |                    | 2.2.2 One Second Timer                       |  |  |  |  |  |

| 3.0 | Dire               | ectory Structure                             |  |  |  |  |  |

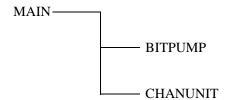

|     | 3.1                | MAIN (Application) Directory                 |  |  |  |  |  |

|     | 3.2                | BITPUMP Directory                            |  |  |  |  |  |

|     | 3.3                | CHANUNIT Directory                           |  |  |  |  |  |

|     | 3.4                | Header File Dependencies                     |  |  |  |  |  |

|     | 3.5                | TYPEDEFS.H                                   |  |  |  |  |  |

| <ul><li>4.1 Using the Keil uVision Project Manager</li></ul> |     |

|--------------------------------------------------------------|-----|

| 4.2 Using a Makefile                                         | 4-1 |

|                                                              |     |

| 4.3 Linker Flags                                             | 4-2 |

| 4.4 Compiler Flags                                           | 4-2 |

| 4.4.1 CHAN_UNIT                                              |     |

| 4.4.2 TWO_LOOPS                                              | 4-4 |

| 4.4.3 CU_EOC                                                 | 4-4 |

| 4.4.4 PERF_MONITOR                                           | 4-4 |

| 4.4.5 CU_2T1                                                 | 4-4 |

| 4.4.6 CU_2E1                                                 | 4-4 |

| 4.4.7 CU_3E1                                                 | 4-5 |

| 4.4.8 CU_1T1                                                 | 4-5 |

| 4.4.9 CU_1E1                                                 | 4-5 |

| 4.4.10 CU_CUSTOM                                             | 4-5 |

| 4.4.11 T1E1_FRAMER                                           | 4-5 |

| 4.4.12 CU_LED                                                | 4-5 |

| 4.4.13 BIT_REVERSE                                           | 4-6 |

| 4.4.14 ZIPSOCKET                                             | 4-6 |

| 5.0 Application Code                                         | 5-1 |

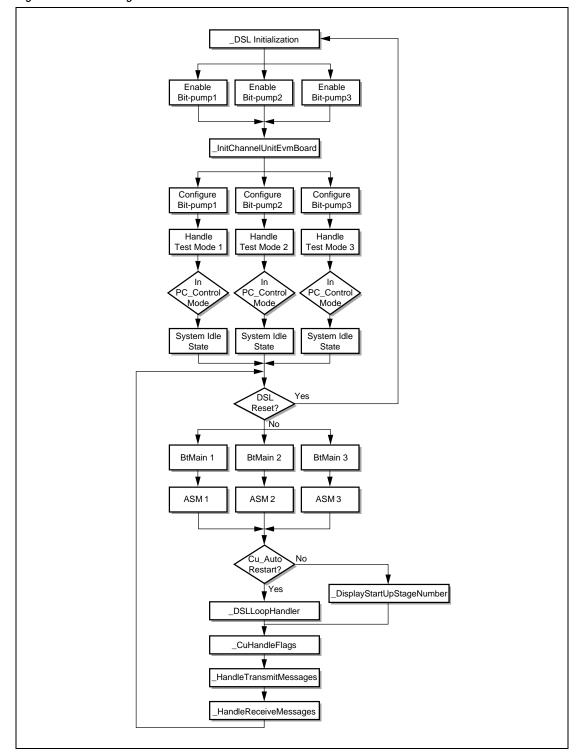

| 5.1 Software Flow                                            | 5-1 |

| 5.2 DSL Loop Manager                                         | 5-3 |

| 5.3 Software and Devices Initializations                     | 5-4 |

| 5.4 Activation State Manager                                 |     |

| 5.4.1 HTU-C Activation                                       |     |

| 5.4.1.1 Configuration State                                  |     |

| 5.4.1.2 Inactive State                                       |     |

| 5.4.1.3 Activating State                                     |     |

| 5.4.1.4 Activating State S1                                  |     |

| 5.4.1.5 Active Rx State                                      |     |

| 5.4.1.6 Active Tx State                                      |     |

| 5.4.1.7 GOTO Pair ID Validation State                        |     |

| 5.4.1.8 PID Validation State                                 |     |

| 5.4.1.9 GOTO Active Tx/Rx State                              |     |

| 5.4.1.10 Active Tx/Rx State                                  |     |

| 5.4.1.11 Pending Deactivated State                           |     |

| 5.4.1.12 Deactivated State                                   |     |

| 5.4.1.13 System Idle State                                   |     |

| Application and | Channel | Unit So | ftware | Develo | nor's | Guide |

|-----------------|---------|---------|--------|--------|-------|-------|

| Application and | Channel | Omiso   | nware  | Develo | pers  | Guiae |

|     |     | 5.4.2   | HTU-R Activation                                        | -16         |

|-----|-----|---------|---------------------------------------------------------|-------------|

|     |     |         | 5.4.2.1 Configuration State                             | .17         |

|     |     |         | 5.4.2.2 Inactive State                                  | .17         |

|     |     |         | 5.4.2.3 Activating State                                | .17         |

|     |     |         | 5.4.2.4 Activating State S1                             | -18         |

|     |     |         | 5.4.2.5 Active Rx State                                 |             |

|     |     |         | 5.4.2.6 Active Tx State                                 |             |

|     |     |         | 5.4.2.7 GOTO Pair ID Validation State                   |             |

|     |     |         | 5.4.2.8 PID Validation State                            |             |

|     |     |         | 5.4.2.9 GOTO Active Tx/Rx State                         |             |

|     |     |         | 5.4.2.10 Active Tx/Rx State5-                           |             |

|     |     |         | 5.4.2.11 Pending Deactivated State                      |             |

|     |     |         | 5-4.2.12 Deactivated State                              |             |

|     |     |         | 5.4.2.13 System Idle State                              | ·21         |

| 5.0 | Cha | nnel Ur | t Code                                                  | ó-1         |

|     | 6.1 |         | rations                                                 |             |

|     | 0.1 | 6.1.1   | CU_2T1                                                  |             |

|     |     | 6.1.2   | CU_2E1                                                  |             |

|     |     | 6.1.3   | CU_3E1                                                  |             |

|     |     | 6.1.4   | CU_1T1                                                  |             |

|     |     | 6.1.5   | CU_1E1                                                  |             |

|     |     | 6.1.6   | Modifying the Code for Custom Applications (_CU_CUSTOM) |             |

|     |     |         | 6.1.6.1 Rate_values[][]                                 |             |

|     |     |         | 6.1.6.2 CU_MAP.C                                        | 5-7         |

|     | 6.2 | Interru | Handler                                                 | <b>3-</b> 8 |

|     |     | 6.2.1   | Sync Status                                             |             |

|     |     | 6.2.2   | Error Status Reporting                                  |             |

|     |     | 6.2.3   | Tx/Rx FIFO Error Handling                               | <b>3-</b> 8 |

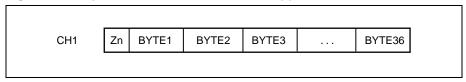

|     |     | 6.2.4   | DPLL Error Handling                                     | 5-9         |

|     |     | 6.2.5   | EOC Termination                                         | -10         |

|     |     | 6.2.6   | Pair ID Termination (E1 Mode)                           | -10         |

|     |     | 6.2.7   | Indicator Bit Termination                               | -10         |

|     |     | 6.2.8   | T1/E1 Framer Interrupt Handling—6 ms Polling 6-         | -10         |

|     | 6.3 | BER M   | er6-                                                    | -11         |

|     | 6.4 | Dynam   | : Master Loop                                           | -11         |

|     | 6.5 | Tip/Rir | Reversal                                                | -11         |

|     | 6.6 | Loop R  | versal6-                                                | -11         |

|     | 6.7 | EOC O   | eration                                                 | -12         |

|     |     | 6.7.1   | EOC Data Format                                         | -12         |

|     |     | 6.7.2   | EOC-Related Data6-                                      |             |

|     |     | 672     | Sunnorted FOC Commands 6.                               | 13          |

| Application | and | Channel | Unit | Software | Develo | nor's | Gui | de |

|-------------|-----|---------|------|----------|--------|-------|-----|----|

| Application | unu | Channel | Omi  | Software | Develo | per s | Gui | ие |

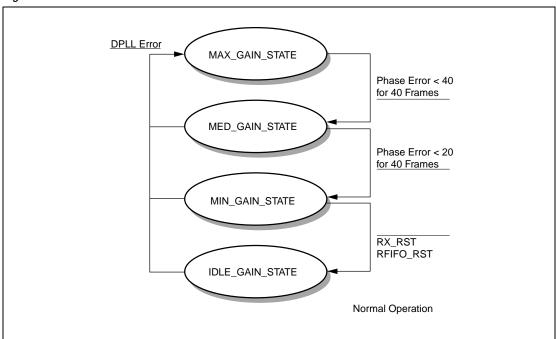

|     |       | 6.7.4   | EOC Hand    | dling on the HTU-R Side                                        |      |

|-----|-------|---------|-------------|----------------------------------------------------------------|------|

|     |       |         | 6.7.4.2     | EOC Task Handler Related to the EOC Slave                      |      |

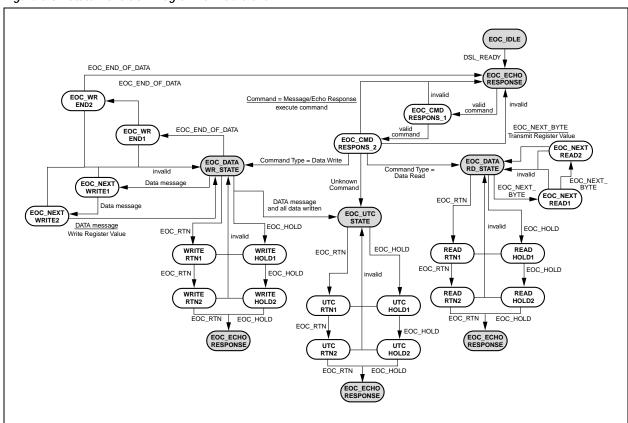

|     |       | 6.7.5   | EOC Hand    | dling on the HTU-C Side                                        |      |

|     |       |         | 6.7.5.1     | EOC Master                                                     |      |

|     |       |         | 6.7.5.2     | EOC Task Handler Related to the EOC Master                     | 6-20 |

|     | 6.8   | Perform | mance Mon   | itoring                                                        | 6-23 |

|     | 6.9   | Channe  | el Blocking |                                                                | 6-24 |

|     | 6.10  | T1/E1 F | ramer and   | LIU Support                                                    | 6-24 |

| 7.0 | Seria | al Com  | municatio   | on Interface                                                   | 7-1  |

|     | 7.1   | Commi   | unication P | rotocol                                                        | 7-1  |

|     | 7.2   | Messa   | ge Structur | e                                                              | 7-1  |

|     |       | 7.2.1   | Destination | on Field (Bits E3–E0)                                          | 7-2  |

|     |       | 7.2.2   | Opcode F    | Field (Bits 07–00)                                             | 7-2  |

|     |       | 7.2.3   | Paramete    | er Field (Bits P7–P0)                                          | 7-2  |

|     | 7.3   | Messa   | ge Transfer | Protocol                                                       | 7-3  |

|     | 7.4   | Checks  | um Functio  | on                                                             | 7-4  |

|     | 7.5   | Acknow  | vledge Mes  | ssage                                                          | 7-4  |

| 8.0 | API ( | Comma   | nd Set      |                                                                | 8-1  |

|     | 8.1   | Level 3 | API Comm    | nands                                                          | 8-1  |

|     |       | 8.1.1   |             | trol                                                           |      |

|     |       |         | 8.1.1.1     | Reset the DSL                                                  | 8-1  |

|     |       |         | 8.1.1.2     | Enable or Disable Activation State Manager                     | 8-2  |

|     |       | 8.1.2   | DSL Stati   | us                                                             | 8-2  |

|     |       |         | 8.1.2.1     | History of Link in Sync Status                                 | 8-2  |

|     |       |         | 8.1.2.2     | Overall DSL Status                                             | 8-3  |

|     |       |         | 8.1.2.3     | DSL Loop Status                                                | 8-5  |

|     |       |         | 8.1.2.4     | DSL ZipStartup Status                                          | 8-6  |

|     |       |         | 8.1.2.5     | DSL Version                                                    | 8-6  |

|     |       | 8.1.3   | Performa    | nce Monitoring                                                 | 8-6  |

|     |       |         | 8.1.3.1     | Enable or Disable Performance Monitoring Update                | 8-6  |

|     |       |         | 8.1.3.2     | Set Starting Address to Check Performance Record at Interval 1 |      |

|     |       |         | 8.1.3.3     | Set Starting Address to Check Performance Record at Interval 2 |      |

|     |       |         | 8.1.3.4     | Set Starting Address to Check Performance Record at Interval 3 |      |

|     |       |         | 8.1.3.5     | Performance Records at Different Intervals                     |      |

|     |       |         | 8.1.3.6     | Latest Performance Record at Different Intervals               | 8-9  |

| Application | and | Channel  | Unit So | ftware | Develo | ner's | Guide |

|-------------|-----|----------|---------|--------|--------|-------|-------|

| πρριιταιισι | unu | Chamilei | Omiso   | nware  | Develo | pers  | Juiue |

| 8.2 | Level 2 | API Comm  | ands                                                              | 8-11   |

|-----|---------|-----------|-------------------------------------------------------------------|--------|

|     | 8.2.1   | Channel B | Blocking                                                          | . 8-11 |

|     |         | 8.2.1.1   | Channel Blocking Time Slot Location                               | . 8-11 |

|     |         | 8.2.1.2   | Channel Blocking Time Slot Enable/Disable                         | . 8-11 |

|     |         | 8.2.1.3   | Channel Blocking Configuration                                    | . 8-11 |

|     |         | 8.2.1.4   | Set all Time Slots                                                | . 8-12 |

|     |         | 8.2.1.5   | Channel Blocking Time Slot Usage                                  | . 8-12 |

|     | 8.2.2   | Diagnosti | C                                                                 | . 8-13 |

|     |         | 8.2.2.1   | DSL Loopbacks                                                     | . 8-13 |

|     |         | 8.2.2.2   | DSL Test Modes                                                    | . 8-13 |

|     |         | 8.2.2.3   | Sending API Commands Through EOC Channel                          | . 8-14 |

|     | 8.2.3   | DSL Statu | IS                                                                | . 8-15 |

|     |         | 8.2.3.1   | Far End Signal Attenuation                                        | . 8-15 |

|     |         | 8.2.3.2   | Noise Margin                                                      | . 8-15 |

|     | 8.2.4   | ERLE Test | t                                                                 | . 8-16 |

|     |         | 8.2.4.1   | Background and ERLE Test Mode                                     | . 8-16 |

|     |         | 8.2.4.2   | ERLE Results                                                      | . 8-17 |

|     |         | 8.2.4.3   | AAGC Results                                                      | . 8-18 |

|     | 8.2.5   | DPLL Stat | tus Command                                                       | . 8-19 |

|     |         | 8.2.5.1   | Read the DPLL State                                               | . 8-19 |

|     | 8.2.6   | Channel L | Init Indicator Bit Commands                                       | . 8-19 |

|     |         | 8.2.6.1   | Write Indicator Low Byte                                          | . 8-19 |

|     |         | 8.2.6.2   | Write Indicator High Byte                                         | . 8-19 |

|     |         | 8.2.6.3   | Read Indicator Lo Byte                                            | . 8-20 |

|     |         | 8.2.6.4   | Read Indicator Hi Byte                                            | . 8-20 |

|     | 8.2.7   | Single Lo | op Commands                                                       | . 8-2  |

|     |         | 8.2.7.1   | Set Number of PCM Time Slots Used                                 | . 8-21 |

|     |         | 8.2.7.2   | Set Number of HDSL Payload Bytes                                  | . 8-21 |

|     |         | 8.2.7.3   | Set Number of Occupied HDSL Payload Bytes and PCM Time Slots Used | . 8-22 |

|     |         | 8.2.7.4   | Set F-bit Present                                                 | . 8-22 |

|     |         | 8.2.7.5   | Set Derived MClk Value                                            | . 8-22 |

|     |         | 8.2.7.6   | Configure Single Loop                                             | . 8-23 |

|     | 8.2.8   | EOC Com   | mands                                                             | . 8-23 |

|     |         | 8.2.8.1   | EOC Register Select                                               | . 8-24 |

|     |         | 8.2.8.2   | EOC Register Size                                                 | . 8-24 |

|     |         | 8.2.8.3   | EOC Byte Number Location                                          | . 8-25 |

|     |         | 8.2.8.4   | EOC Write Register Data                                           | . 8-25 |

|     |         | 8.2.8.5   | Start EOC Read/Write Operation                                    | . 8-26 |

|     |         | 8.2.8.6   | Set EOC Control Commands                                          | . 8-26 |

|     |         | 8.2.8.7   | Set EOC Address Destination                                       | . 8-27 |

|     |         | 8.2.8.8   | Insert CRC Errors                                                 | . 8-27 |

|     |         | 8.2.8.9   | EOC Query Received New Data                                       | . 8-27 |

|     |         | 8.2.8.10  | EOC Read Register                                                 | . 8-28 |

|     |         | 8 2 8 11  | Read FOC Status                                                   | 8-28   |

| 8.3   | <b>Applica</b> | ion Examples                                                                  | 0  |

|-------|----------------|-------------------------------------------------------------------------------|----|

|       | 8.3.1          | Read Example         8-3                                                      | 0  |

|       |                | 8.3.1.1 Step 1: Select HTU-C Register Name                                    | 0  |

|       |                | 8.3.1.2 Step 2: Select HTU-C Register Size                                    | 0  |

|       |                | 8.3.1.3 Step 3: Set Up HTU-R Register Name and Size                           | 0  |

|       |                | 8.3.1.4 Step 4: Load HTU-R Read Register D                                    | 1  |

|       |                | 8.3.1.5 Step 5: Set Command for HTU-C to Read HTU-R Register D 8-3            |    |

|       |                | 8.3.1.6 Step 6: Read New Data Flags                                           | 1  |

|       |                | 8.3.1.7 Step 7: Set Index to 0 for Read Register D                            | 1  |

|       |                | 8.3.1.8 Step 8: Read Register D                                               |    |

|       | 8.3.2          | Write Example                                                                 | 2  |

|       |                | 8.3.2.1 Step 1: Set Up HTU-C Register Number                                  | 2  |

|       |                | 8.3.2.2 Step 2: Set Up HTU-C Register Size                                    | 2  |

|       |                | 8.3.2.3 Step 3: Set Up HTU-R Register Number and Size 8-3                     |    |

|       |                | 8.3.2.4 Step 4: Load the HTU-C Write Register B                               |    |

|       |                | 8.3.2.5 Step 5: Set HTU-C Start Sending Command to Write HTU-R Register B 8-3 |    |

|       |                | 8.3.2.6 Step 6: Read the Received Data Status                                 | 13 |

|       |                | 8.3.2.7 Step 7: Set Byte Number Location                                      | 13 |

|       |                | 8.3.2.8 Step 8: Read the B Data Register                                      |    |

|       | 8.3.3          | HTU-C CRC Check Command Example                                               |    |

|       |                | 8.3.3.1 Step 1: HTU-C Receives Corrupted CRC from HTU-R8-3                    | 4  |

|       |                | 8.3.3.2 Step 2: Set the End Corrupted CRC Command 8-3                         | 4  |

|       | 8.3.4          | HTU-R CRC Check Command Example                                               | 4  |

|       |                | 8.3.4.1 Step 1: Notify the HTU-R of Corrupted CRC                             | 4  |

|       |                | 8.3.4.2 Step 2: Send Corrupted CRC                                            | 5  |

| 8.4   | Level 1        | API Commands 8-3                                                              | 16 |

| · · · | 8.4.1          | Bit Pump APIs                                                                 |    |

|       | 0.4.1          | 8.4.1.1 Input Signal Level                                                    |    |

|       |                | 8.4.1.2 Input DC Offset                                                       |    |

|       |                | 8.4.1.3 Bit Pump BER Meter                                                    |    |

|       |                | 8.4.1.4 Self-test                                                             |    |

|       |                |                                                                               |    |

| 8.5   |                | Unit API Commands. 8-3                                                        |    |

|       | 8.5.1          | Set the PCM Multiframe Length                                                 |    |

|       | 8.5.2          | Channel Unit Error Counters                                                   |    |

|       | 8.5.3          | Modify Receive Combination Table                                              |    |

|       | 8.5.4          | Modify Transmit Routing Table                                                 |    |

|       | 8.5.5          | Modify Transmit Payload Mapper (TMAPS)                                        |    |

|       | 8.5.6          | Modify Receive Payload Mapper (RMAPS)                                         |    |

|       | 8.5.7          | Modify Data Bank Patterns (DBANKs)                                            |    |

|       | 8.5.8          | Set Channel Unit Frame Format                                                 |    |

|       | 8.5.9          | Reset Transmit/Receive FIFOs                                                  |    |

|       | 8.5.10         | Set Transmit/Receive FIFO Water Levels                                        |    |

|       | 8.5.11         | Set Master Loop                                                               |    |

|       | 8.5.12         | Channel Unit SYNC Status                                                      |    |

|       | 8.5.13         | Channel Unit BER Meter                                                        | b  |

**Table of Contents**

| 9.0  | Stru                              | ctures                                          |  |  |  |  |  |  |  |

|------|-----------------------------------|-------------------------------------------------|--|--|--|--|--|--|--|

|      | 9.1                               | CU_WR                                           |  |  |  |  |  |  |  |

|      | 9.2                               | CU_RD 9-2                                       |  |  |  |  |  |  |  |

|      | 9.3                               | <b>CU_FLAGS</b> 9-3                             |  |  |  |  |  |  |  |

|      | 9.4                               | CU_REG_COPY                                     |  |  |  |  |  |  |  |

|      | 9.5                               | IRR                                             |  |  |  |  |  |  |  |

| 10.0 | Glob                              | al Variables10-1                                |  |  |  |  |  |  |  |

|      | 10.1                              | *cu_wr                                          |  |  |  |  |  |  |  |

|      | 10.2                              | *cu_rd                                          |  |  |  |  |  |  |  |

|      | 10.3                              | num_bit_pumps                                   |  |  |  |  |  |  |  |

|      | 10.4                              | <b>bp_position[]</b>                            |  |  |  |  |  |  |  |

|      | 10.5                              | rate_values[][]                                 |  |  |  |  |  |  |  |

|      | 10.6                              | rate_index                                      |  |  |  |  |  |  |  |

|      | 10.7                              | htu_values[][]                                  |  |  |  |  |  |  |  |

|      | 10.8                              | htu_index                                       |  |  |  |  |  |  |  |

|      | 10.9                              | route_table[64]                                 |  |  |  |  |  |  |  |

|      | 10.10                             | 10.10 combine_table[64]                         |  |  |  |  |  |  |  |

|      | 10.11                             | 10.11 tmap_table[9][_NO_0F_L00PS]               |  |  |  |  |  |  |  |

|      | 10.12 rmap_table[6][_NO_OF_LOOPS] |                                                 |  |  |  |  |  |  |  |

|      | 10.13 _CuFlags                    |                                                 |  |  |  |  |  |  |  |

|      | 10.14                             | cu_reg_copy                                     |  |  |  |  |  |  |  |

| 11.0 | Fund                              | tions                                           |  |  |  |  |  |  |  |

|      | 11.1                              | DSL Initialization Functions                    |  |  |  |  |  |  |  |

|      |                                   | 11.1.1 void _DSLInitialization(void)11-1        |  |  |  |  |  |  |  |

|      |                                   | 11.1.2 BP_U_8BIT_IsChannelUnitEvmPresent (void) |  |  |  |  |  |  |  |

|      |                                   | 11.1.3 BP_U_8BIT_InitChannelUnitEvmBoard (void) |  |  |  |  |  |  |  |

|      | 44.0                              | 11.1.3.1 BP_U_8BIT _CulnitFramer (void)         |  |  |  |  |  |  |  |

|      | 11.2                              | Channel Unit Initialization Functions. 11-3     |  |  |  |  |  |  |  |

|      |                                   | 11.2.1 BP_U_8BIT _CulnitChannelUnit (void)      |  |  |  |  |  |  |  |

|      |                                   | 11.2.2 Void _CulnitAddresses (Void)             |  |  |  |  |  |  |  |

|      |                                   | 11.2.4 void _CulnitHdslLoops                    |  |  |  |  |  |  |  |

| 11.3 | Channe   | I Unit Mapping Functions                               |

|------|----------|--------------------------------------------------------|

|      | 11.3.1   | void _CuDefaultRouteLoops(void)                        |

|      | 11.3.2   | void _CuDefaultCombineLoops(void)                      |

|      | 11.3.3   | void _CulnitMapper(void)                               |

|      | 11.3.4   | _CulnitRouteTable                                      |

|      | 11.3.5   | _CulnitCombineTable                                    |

|      | 11.3.6   | _CuWriteMapRouteCombine                                |

| 11.4 | void _A  | ctivationStateManager(BP_U_8BIT bp) 11-6               |

| 11.5 | void _Zi | ipStartValidationManager(BP_U_8BIT bp)                 |

| 11.6 | Channe   | I Unit ASM-Related Functions                           |

|      | 11.6.1   | void _CuForceOnes(BP_U_8BIT state, BP_U_8BIT loop)     |

|      | 11.6.2   | void _CuConfigureBeginStartup (BP_U_8BIT loop)         |

|      | 11.6.3   | void _CuConfigureTransmitS1(BP_U_8BIT loop)11-7        |

|      | 11.6.4   | void _CuHohEn(BP_U_8BIT state, BP_U_8BIT loop)         |

|      | 11.6.5   | void _CuConfigureStartupComplete (BP_U_8BIT loop)      |

|      | 11.6.6   | void _CuSetRtrInd(BP_U_8BIT state, BP_U_8BIT loop)11-8 |

|      | 11.6.7   | void _CuSetPid(BP_U_8BIT loop)11-8                     |

|      | 11.6.8   | void _CuSetPidToAllOnes(BP_U_8BIT loop)                |

| 11.7 | Channe   | I Unit Interrupt Handlers                              |

|      | 11.7.1   | void _CuInterruptHandler (void) interrupt 211-9        |

|      | 11.7.2   | void _CuTxInterrupt (BP_U_8BIT loop)11-9               |

|      | 11.7.3   | void _CuRxInterrupt (BP_U_8BIT loop)                   |

|      | 11.7.4   | void _CuDpllInterrupt (void)                           |

|      | 11.7.5   | void _CuFramerInterrupt (void)                         |

|      | 11.7.6   | void E1_Pairid_Validation(BP_U_8BIT loop)              |

| 11.8 | DSL Dyr  | namic Loop Managing Functions                          |

|      | 11.8.1   | void _DSLLoopHandler(void)                             |

|      | 11.8.2   | void _Set_2E1_PairID(BP_U_8BIT bp)                     |

|      | 11.8.3   | void _Set_2T1_SyncWord(BP_U_8BIT bp)                   |

|      | 11.8.4   | void _Set_3E1_PairID1(BP_U_8BIT bp)                    |

|      | 11.8.5   | void _Set_3E1_PairID2(BP_U_8BIT bp)                    |

|      | 11.8.6   | void _Reset_Pid_Validation(BP_U_8BIT bp)               |

| 11.9 | Channe   | Unit Dynamic Loop Managing Functions                   |

|      | 11.9.1   | void _CuSetMasterLoop(BP_U_8BIT loop)                  |

|      | 11.9.2   | void _CuReverseLoops(void)                             |

|      | 11.9.3   | void _Configure_Channel_Blocking(void)                 |

|      | 11.9.4   | void _CuCheckForLoopReversal(void)11-11                |

| Application as         | nd Channel | Unit So | ftware  | Develon | or's  | Guide |

|------------------------|------------|---------|---------|---------|-------|-------|

| $\Delta ppiicuiion ai$ | na Channei | Omiso   | nware 1 | Develop | e i s | Guiue |

| 11.10 API Fun                                                                                                           | ctions                                                                                                                                                                                                                                                                                                                                                                          | 11-12                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 11.10.1                                                                                                                 | _BtStatus(no, opcode, parameter, *indication)                                                                                                                                                                                                                                                                                                                                   | 11-13                                                                                  |

|                                                                                                                         | 11.10.1.1 _DSLStatus(no, opcode, parameter, *indication)                                                                                                                                                                                                                                                                                                                        |                                                                                        |

|                                                                                                                         | 11.10.1.2 _CuStatus(no, opcode, parameter, *indication)                                                                                                                                                                                                                                                                                                                         |                                                                                        |

|                                                                                                                         | 11.10.1.3 _FramerStatus(no, opcode, parameter, *indication)                                                                                                                                                                                                                                                                                                                     |                                                                                        |

|                                                                                                                         | 11.10.1.4 _BitpumpStatus(no, opcode, parameter, *indication)                                                                                                                                                                                                                                                                                                                    |                                                                                        |

| 11.10.2                                                                                                                 | _BtControl(no, opcode, parameter)                                                                                                                                                                                                                                                                                                                                               |                                                                                        |

|                                                                                                                         | 11.10.2.1 _DSLControl(no, opcode, parameter).                                                                                                                                                                                                                                                                                                                                   |                                                                                        |

|                                                                                                                         | 11.10.2.2 _CuControl(no, opcode, parameter)                                                                                                                                                                                                                                                                                                                                     |                                                                                        |

|                                                                                                                         | 11.10.2.3 _FramerControl(no, opcode, parameter)                                                                                                                                                                                                                                                                                                                                 |                                                                                        |

|                                                                                                                         | 11.10.2.4 _BitpumpControl(no, opcode, parameter)                                                                                                                                                                                                                                                                                                                                |                                                                                        |

|                                                                                                                         | Unit EOC Functions                                                                                                                                                                                                                                                                                                                                                              |                                                                                        |

| 11.11.1                                                                                                                 | EOC Protocol Handler                                                                                                                                                                                                                                                                                                                                                            |                                                                                        |

|                                                                                                                         | 11.11.1.1 void EocMaster(BP_U_8BIT loop)                                                                                                                                                                                                                                                                                                                                        |                                                                                        |

|                                                                                                                         | 11.11.1.2 void EocSlave(BP_U_8BIT loop)                                                                                                                                                                                                                                                                                                                                         |                                                                                        |

| 11.11.2                                                                                                                 | EOC Task Handler                                                                                                                                                                                                                                                                                                                                                                |                                                                                        |

|                                                                                                                         | 11.11.2.1 void EocTaskHandler_CO(BP_U_8BIT loop)                                                                                                                                                                                                                                                                                                                                |                                                                                        |

| 11 11 2                                                                                                                 | 11.11.2.2 void EocTaskHandler_RT(BP_U_8BIT loop)                                                                                                                                                                                                                                                                                                                                |                                                                                        |

| 11.11.3                                                                                                                 | 11.11.3.1 BP_U_8BIT EocGetData(BP_U_8BIT lByte, BP_U_8BIT hByte)                                                                                                                                                                                                                                                                                                                |                                                                                        |

|                                                                                                                         | 11.11.3.2 BP_U_16BIT EocSendWord(BP_U_8BIT command, BP_U_8BIT header)                                                                                                                                                                                                                                                                                                           |                                                                                        |

| 11 12 Ohanna                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                        |

|                                                                                                                         | Unit Utility Functions.                                                                                                                                                                                                                                                                                                                                                         |                                                                                        |

|                                                                                                                         | void _CuHandleFlags(void)                                                                                                                                                                                                                                                                                                                                                       |                                                                                        |

|                                                                                                                         | void _CuWriteMasterCmd5(void)                                                                                                                                                                                                                                                                                                                                                   |                                                                                        |

|                                                                                                                         | Void _CuclearCounters(bP_0_obit loop, bP_0_obit citit)                                                                                                                                                                                                                                                                                                                          | 11-10                                                                                  |

|                                                                                                                         | void CuRosotTvEIFO(void)                                                                                                                                                                                                                                                                                                                                                        | 11 16                                                                                  |

| 11 12 5                                                                                                                 | void _CuResetTxFIFO(void)                                                                                                                                                                                                                                                                                                                                                       |                                                                                        |

|                                                                                                                         | void _CuResetRxFIFO(void)                                                                                                                                                                                                                                                                                                                                                       | 11-17                                                                                  |

| 11.12.6                                                                                                                 | void _CuResetRxFIFO(void)                                                                                                                                                                                                                                                                                                                                                       | 11-17<br>11-17                                                                         |

| 11.12.6<br>11.12.7                                                                                                      | void _CuResetRxFIFO(void) void _CuResetReceiver(void) TX_RD *get_tx_rd_ptr(BP_U_8BIT loop)                                                                                                                                                                                                                                                                                      | 11-17<br>11-17<br>11-17                                                                |

| 11.12.6<br>11.12.7<br>11.12.8                                                                                           | void _CuResetRxFIFO(void)  void _CuResetReceiver(void)  TX_RD *get_tx_rd_ptr(BP_U_8BIT loop)  RX_RD *get_rx_rd_ptr(BP_U_8BIT loop)                                                                                                                                                                                                                                              | 11-17<br>11-17<br>11-17<br>11-17                                                       |

| 11.12.6<br>11.12.7<br>11.12.8<br>11.13 General                                                                          | void _CuResetRxFIFO(void) void _CuResetReceiver(void)  TX_RD *get_tx_rd_ptr(BP_U_8BIT loop)  RX_RD *get_rx_rd_ptr(BP_U_8BIT loop)  Purpose Timer Functions                                                                                                                                                                                                                      | 11-17<br>11-17<br>11-17<br>11-17<br>11-18                                              |

| 11.12.6<br>11.12.7<br>11.12.8<br><b>11.13 General</b><br>11.13.1                                                        | void _CuResetRxFIFO(void) void _CuResetReceiver(void)  TX_RD *get_tx_rd_ptr(BP_U_8BIT loop)  RX_RD *get_rx_rd_ptr(BP_U_8BIT loop)  Purpose Timer Functions void _InitGenPurposeTimer(void)                                                                                                                                                                                      | 11-17<br>11-17<br>11-17<br>11-17<br>11-18<br>11-18                                     |

| 11.12.6<br>11.12.7<br>11.12.8<br><b>11.13 General</b><br>11.13.1<br>11.13.2                                             | void _CuResetRxFIFO(void) void _CuResetReceiver(void) TX_RD *get_tx_rd_ptr(BP_U_8BIT loop) RX_RD *get_rx_rd_ptr(BP_U_8BIT loop)  Purpose Timer Functions void _InitGenPurposeTimer(void) void _LoadGenPurposeTimerInterval(void)                                                                                                                                                | 11-17<br>11-17<br>11-17<br>11-17<br>11-18<br>11-18                                     |

| 11.12.6<br>11.12.7<br>11.12.8<br><b>11.13 General</b><br>11.13.1<br>11.13.2<br>11.13.3                                  | void _CuResetRxFIFO(void) void _CuResetReceiver(void)  TX_RD *get_tx_rd_ptr(BP_U_8BIT loop)  RX_RD *get_rx_rd_ptr(BP_U_8BIT loop)  Purpose Timer Functions void _InitGenPurposeTimer(void)                                                                                                                                                                                      | 11-17<br>11-17<br>11-17<br>11-17<br>11-18<br>11-18<br>11-18                            |

| 11.12.6<br>11.12.7<br>11.12.8<br><b>11.13 General</b><br>11.13.1<br>11.13.2<br>11.13.3<br>11.13.4                       | void _CuResetRxFIFO(void) void _CuResetReceiver(void) TX_RD *get_tx_rd_ptr(BP_U_8BIT loop) RX_RD *get_rx_rd_ptr(BP_U_8BIT loop)  Purpose Timer Functions void _InitGenPurposeTimer(void) void _LoadGenPurposeTimerInterval(void) void _EnableGenPurposeTimer(bp, timer, value)                                                                                                  | 11-17<br>11-17<br>11-17<br>11-18<br>11-18<br>11-18<br>11-18<br>11-18                   |

| 11.12.6<br>11.12.7<br>11.12.8<br><b>11.13 General</b><br>11.13.1<br>11.13.2<br>11.13.3<br>11.13.4<br>11.13.5            | void _CuResetRxFIFO(void) void _CuResetReceiver(void)  TX_RD *get_tx_rd_ptr(BP_U_8BIT loop)  RX_RD *get_rx_rd_ptr(BP_U_8BIT loop)  Purpose Timer Functions void _InitGenPurposeTimer(void) void _LoadGenPurposeTimerInterval(void) void _EnableGenPurposeTimer(bp, timer, value) void _ContinuousGenPurposeTimer(bp, timer, state)                                              | 11-17<br>11-17<br>11-17<br>11-17<br>11-18<br>11-18<br>11-18<br>11-18<br>11-18          |

| 11.12.6<br>11.12.7<br>11.12.8<br><b>11.13 General</b><br>11.13.1<br>11.13.2<br>11.13.3<br>11.13.4<br>11.13.5<br>11.13.6 | void _CuResetRxFIFO(void) void _CuResetReceiver(void)  TX_RD *get_tx_rd_ptr(BP_U_8BIT loop)  RX_RD *get_rx_rd_ptr(BP_U_8BIT loop)  Purpose Timer Functions  void _InitGenPurposeTimer(void)  void _LoadGenPurposeTimerInterval(void)  void _EnableGenPurposeTimer(bp, timer, value)  void _ContinuousGenPurposeTimer(bp, timer, state)  void _DisableGenPurposeTimer(bp, timer) | 11-17<br>11-17<br>11-17<br>11-18<br>11-18<br>11-18<br>11-18<br>11-18<br>11-18<br>11-18 |

| 11.14 Performance Monitoring Functions         | 11-20 |

|------------------------------------------------|-------|

| 11.14.1 void InitPMRecord(BP_U_8BIT loop)      | 11-20 |

| 11.14.2 void UpdatePMRecord(BP_U_8BIT loop)    | 11-20 |

| 11.14.2.1 void UpdateInterval1(BP_U_8BIT loop) | 11-20 |

| 11.14.2.2 void UpdateInterval2(BP_U_8BIT loop) | 11-20 |

| 11.14.2.3 void UpdateInterval3(BP_U_8BIT loop) |       |

| 11.15 void _Configure_Channel_Blocking(void)   | 11-21 |

| 11.16 DSL Miscellaneous Functions              | 11-21 |

| 11.16.1 void _Cu_Led_Update(bp, state)         | 11-21 |

| 11.16.2 void Bp_Led_Update(bp, state)          |       |

| Appendix A: Acronyms and Abbreviations         | A-1   |

| Annendix R: References                         | R-1   |

## **List of Figures**

| Figure 1-1.  | Software Overview                                  | . 1-1 |

|--------------|----------------------------------------------------|-------|

| Figure 2-1.  | HDSL EVM Terminal Unit                             | . 2-1 |

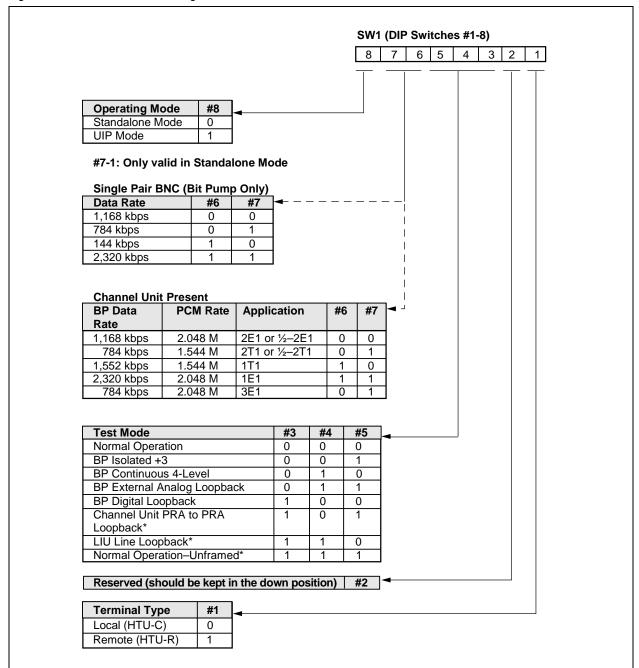

| Figure 2-2.  | DIP Switch Mode Configuration                      | . 2-2 |

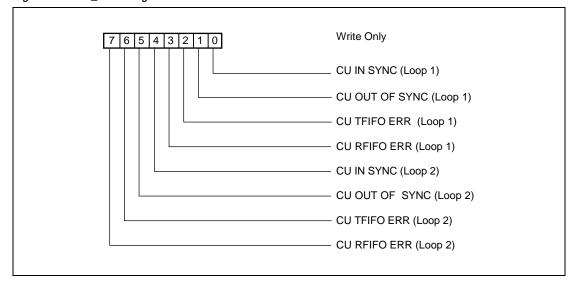

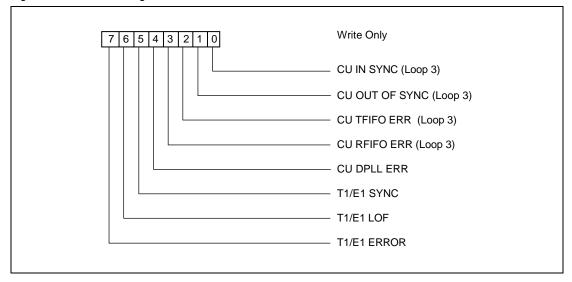

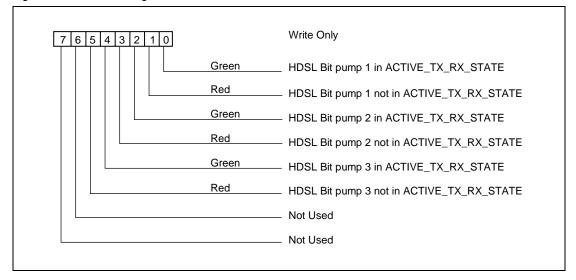

| Figure 2-3.  | CU_LED1 Register                                   | . 2-3 |

| Figure 2-4.  | CU_LED2 Register                                   | . 2-4 |

| Figure 2-5.  | CU_LED3 Register                                   | . 2-4 |

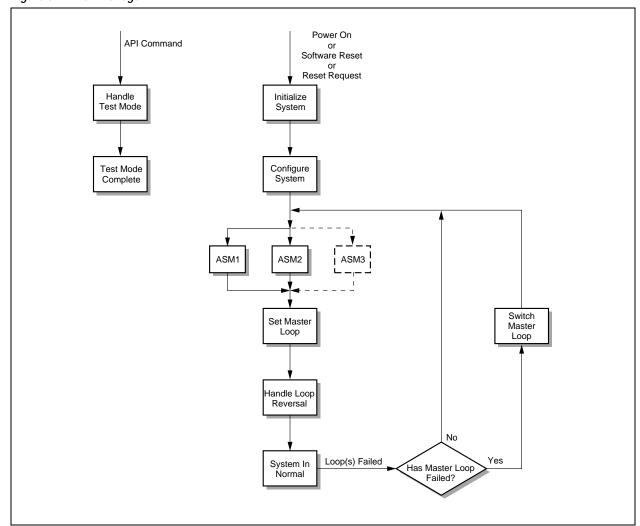

| Figure 5-1.  | Main Program Flow                                  | . 5-2 |

| Figure 5-2.  | DSL Manager                                        | . 5-3 |

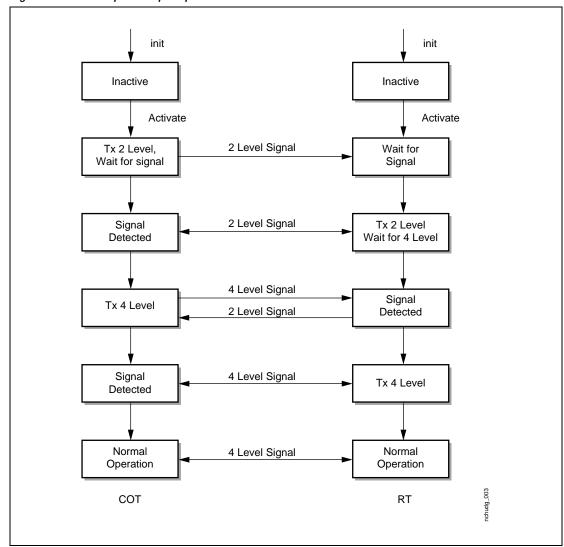

| Figure 5-3.  | Bit Pump Start-up Sequence                         | . 5-7 |

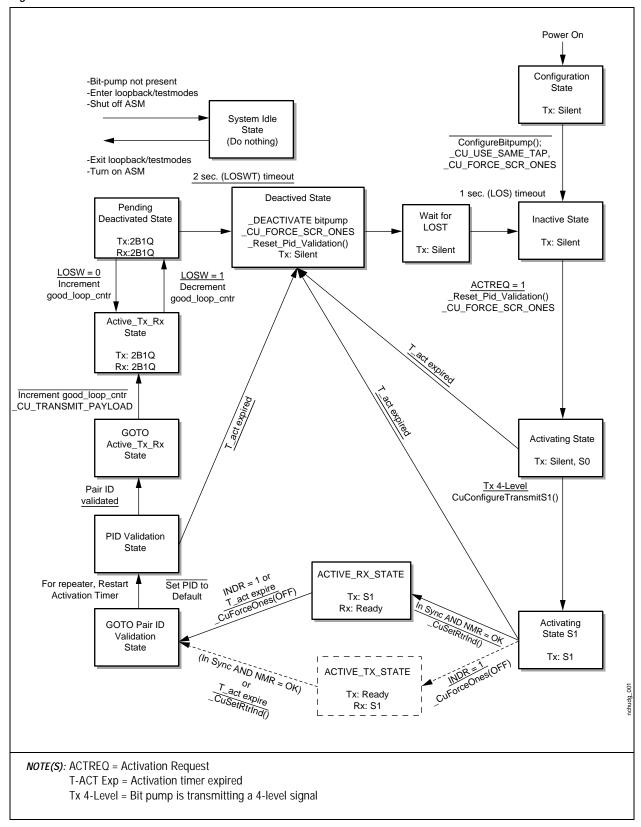

| Figure 5-4.  | Activation State Machine at HTU-C                  | 5-10  |

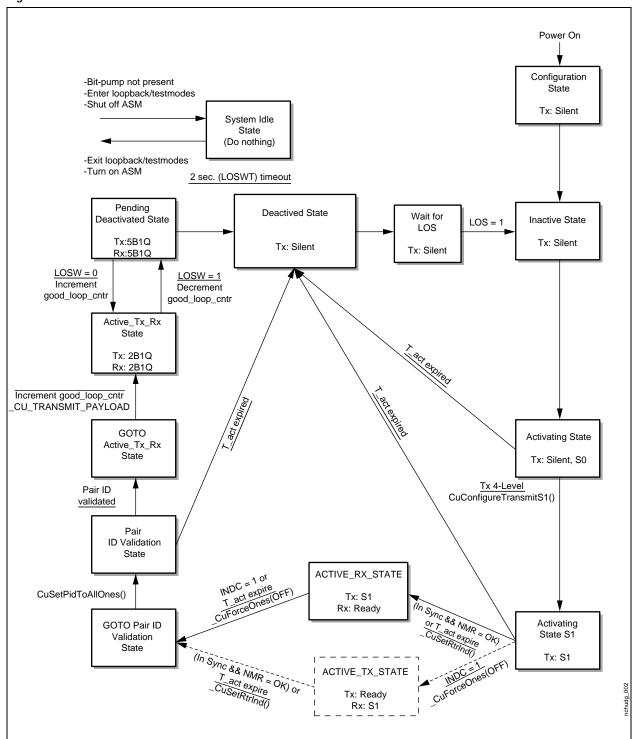

| Figure 5-5.  | Activation State Machine at HTU-R                  | 5-16  |

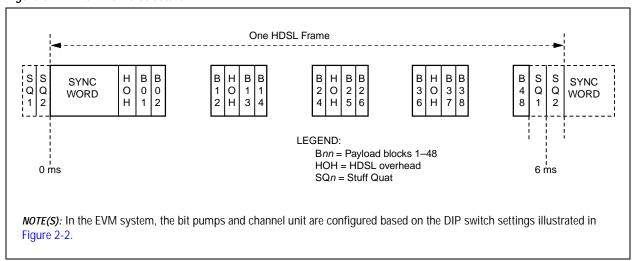

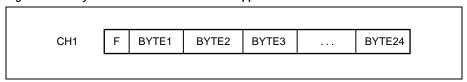

| Figure 6-1.  | HDSL Frame Structure                               | . 6-2 |

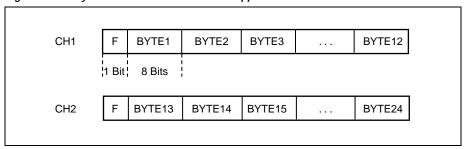

| Figure 6-2.  | Payload Block Structure for 2T1 Application        | . 6-3 |

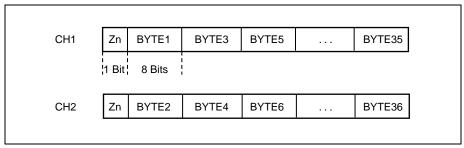

| Figure 6-3.  | Payload Block Structure for 2E1 Application        | . 6-4 |

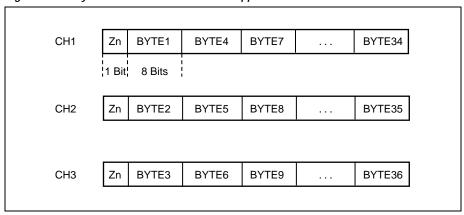

| Figure 6-4.  | Payload Block Structure for 3E1 Application        | . 6-5 |

| Figure 6-5.  | Payload Block Structure for 1T1 Application        | . 6-6 |

| Figure 6-6.  | Payload Block Structure for 1E1 Application        | . 6-7 |

| Figure 6-7.  | DPLL State Machine                                 | . 6-9 |

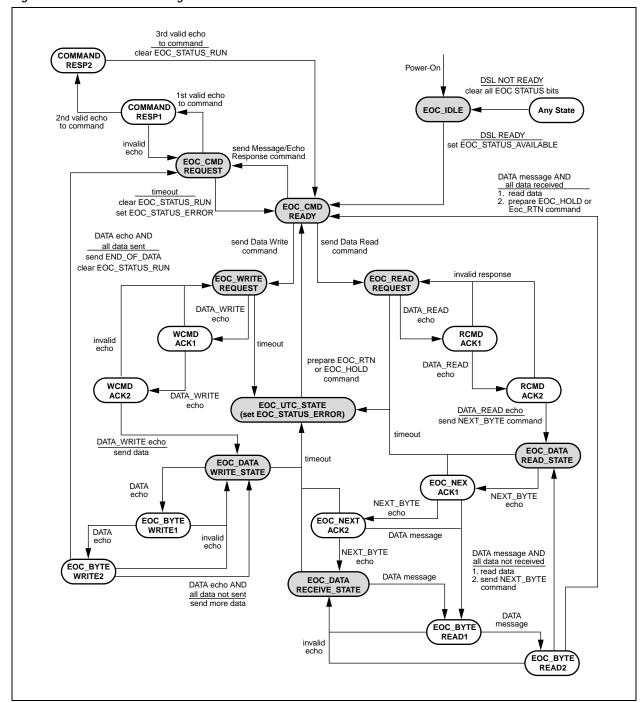

| Figure 6-8.  | State Transition Diagram for EOC Slave             | 6-14  |

| Figure 6-9.  | State Transition Diagram for the EOC Master        | 6-17  |

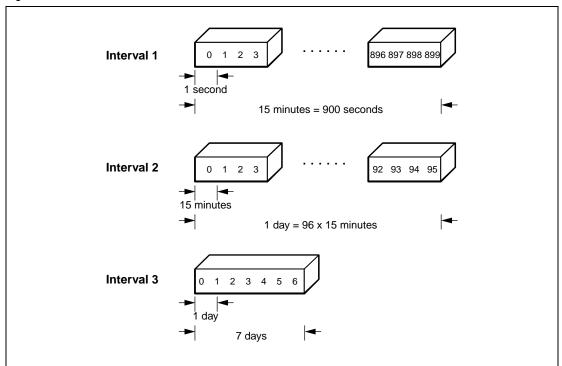

| Figure 6-10. | CRC and FEBE Error Records at Three Time Intervals | 6-23  |

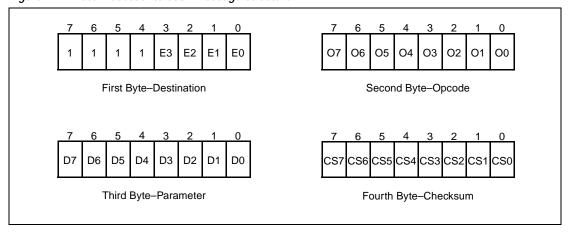

| Figure 7-1.  | Host Processor to 8032 Message Structure           | . 7-1 |

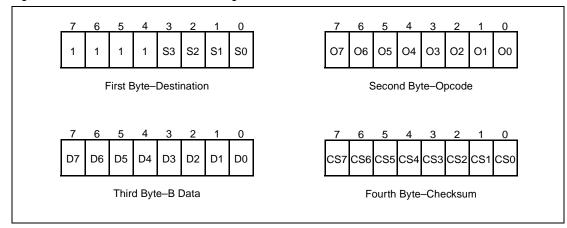

| Figure 7-2.  | 8032 to Host Processor Message Structure           | 7-3   |

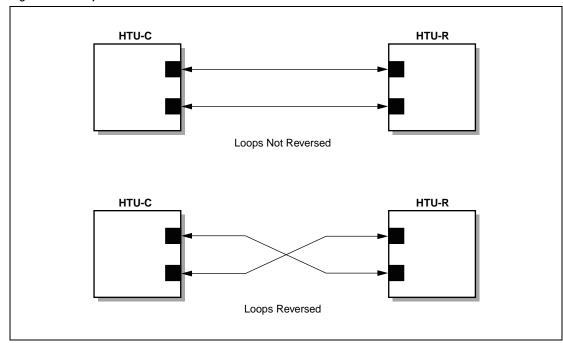

| Figure 8-1.  | Loop Reversal                                      | . 8-4 |

| Figure 11-1. | API Command Parsing Structure                      | 11-12 |

List of Figures RS8953B

## **List of Tables**

| Table 2-1.  | CU_LEDn Memory Map                                  |

|-------------|-----------------------------------------------------|

| Table 2-2.  | General Purpose Status Bit Definitions              |

| Table 3-1.  | Source Files Under the Main Directory               |

| Table 3-2.  | Source Files Under BITPUMP Directory                |

| Table 3-3.  | Source Files Under CHANUNIT Subdirectory            |

| Table 3-4.  | Header File Dependencies                            |

| Table 3-5.  | Data Type Definitions                               |

| Table 4-1.  | HEX Files                                           |

| Table 4-2.  | Compiler Directives                                 |

| Table 5-1.  | Software Initialization Functions                   |

| Table 5-2.  | Bit Pump Initialization Commands                    |

| Table 5-3.  | Channel Unit Initialization Commands5-5             |

| Table 5-4.  | Cross Reference of DSL Functions vs. ASM States 5-8 |

| Table 6-1.  | HDSL Frame Structure and Overhead Bit Allocation    |

| Table 6-2.  | 2T1 Framing                                         |

| Table 6-3.  | 2E1 Framing                                         |

| Table 6-4.  | 3E1 Framing                                         |

| Table 6-5.  | 1T1 Framing                                         |

| Table 6-6.  | 1E1 Framing                                         |

| Table 6-7.  | HDSL EOC Frame Structure                            |

| Table 6-8.  | EOC Command Processing in EOC_CMD_RESPONS_2         |

| Table 6-9.  | Buffer Values for EOC Registers (RT side)           |

| Table 6-10. | Tasks of the HTU-C-EOC Task Handler                 |

| Table 6-11. | Status Flags within the EOC Master                  |

| Table 6-12. | Buffer Values for EOC Registers (HTU-C side)        |

| Table 7-1.  | Destination Field Specification                     |

| Table 7-2.  | Acknowledge Message                                 |

| Table 8-1.  | Opcode: 0x01 (_DSL_RESET)                           |

| Table 8-2.  | Opcode: 0x02 (_DSL_ASM_ENABLE)                      |

| Table 8-3.  | Opcode: 0x85 (_DSL_AVAILABLE_SECONDS)               |

| Table 8-4.  | Opcode: 0x82 (_DSL_STATUS)8-3                       |

| Table 8-5.  | Status Register 0                                   |

| Table 8-6.  | Status Register 18-4                                |

| Table 8-7.  | Opcode: 0x83 (_DSL_LOOP_STATUS)                     |

| Table 8-8.  | Opcode: 0x83 (_DSL_LOOP_STATUS)                     |

| Table 8-9.  | Opcode: 0x81 (_DSL_VERSION)                         |

| Table 8-10. | Opcode: 0x10 (_SET_PERFMONITOR_STATE)               |

| Table 8-11. | Opcode: 0x11 (_INTERVAL1_ADDR_LO)                   |

| Table 8-12. | Opcode: 0x12 (_INTERVAL1_ADDR_HI)8-7                |

|             |                                                     |

| Table 8-13. | Opcode: 0x13 (_INTERVAL2_ADDR)                 |      |

|-------------|------------------------------------------------|------|

| Table 8-14. | Opcode: 0x14 (_INTERVAL3_ADDR)                 |      |

| Table 8-15. | Opcode: 0x90 (_CRC_ERR_AT_INTERVAL1)           | 8-8  |

| Table 8-16. | Opcode: 0x91 (_CRC_ERR_AT_INTERVAL2)           | 8-8  |

| Table 8-17. | Opcode: 0x92 (_CRC_ERR_AT_INTERVAL3)           | 8-8  |

| Table 8-18. | Opcode: 0x93 (_FEBE_ERR_AT_INTERVAL1)          |      |

| Table 8-19. | Opcode: 0x94 (_FEBE_ERR_AT_INTERVAL2)          | 8-8  |

| Table 8-20. | Opcode: 0x95 (_FEBE_ERR_AT_INTERVAL3)          | 8-8  |

| Table 8-21. | Opcode: 0x96 (_LAST_CRC_ERR_INTERVAL1)         | 8-9  |

| Table 8-22. | Opcode: 0x97 (_LAST_CRC_ERR_INTERVAL2)         |      |

| Table 8-23. | Opcode: 0x98 (_LAST_CRC_ERR_INTERVAL3)         | 8-9  |

| Table 8-24. | Opcode: 0x99 (_LAST_FEBE_ERR_INTERVAL1)        | 8-9  |

| Table 8-25. | Opcode: 0x9A (_LAST_FEBE_ERR_INTERVAL2)        | 8-10 |

| Table 8-26. | Opcode: 0x9B (_LAST_FEBE_ERR_INTERVAL3)        | 8-10 |

| Table 8-27. | Opcode: 0x30 (_CB_TIMESLOT_LOCATION)           |      |

| Table 8-28. | Opcode: 0x31 (_CB_TIMESLOT_STATE)              |      |

| Table 8-29. | Opcode: 0x32 (_CONFIGURE_CHANNEL_BLOCKING)     | 8-11 |

| Table 8-30. | Opcode: 0x33 (_SET_ALL_TIMESLOTS)              |      |

| Table 8-31. | Opcode: 0xA3 (_CB_TIMESLOT_USAGE)              | 8-12 |

| Table 8-32. | Opcode: 0x20 (_DSL_LOOPBACK)                   | 8-13 |

| Table 8-33. |                                                |      |

| Table 8-34. | Opcode: 0x21 (_DSL_TESTMODE)                   | 8-13 |

| Table 8-35. | Opcode: 0x22 (_API_DEST)                       |      |

| Table 8-36. | Opcode: 0x23 (_API_OPCODE)                     |      |

| Table 8-37. | Opcode: 0x24 (_API_DATA)                       | 8-14 |

| Table 8-38. | Opcode: 0x25 (_API_SEND)                       | 8-15 |

| Table 8-39. | Opcode: 0xA2 (_API_RESULT)                     |      |

| Table 8-40. | Opcode: 0xB0 (_DSL_FELM)                       | 8-15 |

| Table 8-41. | Opcode: 0xB1 (_DSL_NMR)                        |      |

| Table 8-42. | Opcode 0x18 (_ERLE_TEST_MODE)                  | 8-16 |

| Table 8-43. | _ERLE_TEST_MODE Parameter                      | 8-16 |

| Table 8-44. | Opcode 0x85 (_STARTUP_STATUS)                  | 8-16 |

| Table 8-45. | _STARTUP_STATUS Return Value                   | 8-17 |

| Table 8-46. | Meaningful Values Returned for Different Tests | 8-17 |

| Table 8-47. | Opcode 0x93 (ERLE_RESULTS)                     | 8-17 |

| Table 8-48. | Opcode 0x94 (_AAGC_RESULTS)                    | 8-18 |

| Table 8-49. | Opcode: 0x90 (_CU_READ_DPLL)                   | 8-19 |

| Table 8-50. | Opcode: 0x35 (_CU_WRITE_IND_LO)                | 8-19 |

| Table 8-51. | Opcode: 0x36 (_CU_WRITE_IND_HI)                | 8-19 |

| Table 8-52. | Opcode: 0x91 (_CU_READ_IND_LO)                 | 8-20 |

| Table 8-53. | Low Byte Return Status Bit Definitions         | 8-20 |

| Table 8-54. | Opcode: 0x92 (_CU_READ_IND_HI)                 | 8-20 |

| Table 8-55. | High Byte Return Status Bit Definitions        | 8-20 |

| Table 8-56. | Opcode: 0x40 (_SP_TOTAL_PCM_TSLOT)             | 8-21 |

| Table 8-57. | Opcode: 0x41 (_SP_TOTAL_HDSL_TSLOT)            | 8-21 |

| Table 8-58. | Opcode: 0x42 (_SP_USED_TSLOT)                  | 8-22 |

| $\Delta r$ | nlicat | ion   | and | Channel | Ilnit | Sa | ftware | D     | ovol | nor | <b>'</b> c | Guida |

|------------|--------|-------|-----|---------|-------|----|--------|-------|------|-----|------------|-------|

| $A\mu$     | рисаі  | wii i | ana | Cnannei | Omn   | 30 | uware  | $\nu$ | eveu | per | S          | Guiae |

| Table 8-59.  | Opcode: 0x43 (_SP_FBIT_PRESENT)              |

|--------------|----------------------------------------------|

| Table 8-60.  | Opcode: 0x44 (_SP_DERIVED_MCLK)              |

| Table 8-61.  | Opcode: 0x45 (_SP_CONFIGURE)8-23             |

| Table 8-62.  | Opcode: 0x35 (_EOC_REG_SELECT)               |

| Table 8-63.  | Opcode: 0x36 (_ EOC_REG_SIZE)8-24            |

| Table 8-64.  | Opcode: 0x37 (_EOC_BYTE_NUM_LOC)8-25         |

| Table 8-65.  | Opcode: 0x38 (_EOC_WRITE_REG_DATA)           |

| Table 8-66.  | Opcode 0x39 (_EOC_SEND_RD_WR)8-26            |

| Table 8-67.  | Opcode: 0x3A (_EOC_SET_CONTROL)              |

| Table 8-68.  | Opcode 0x3B (_EOC_ADD_DEST)8-27              |

| Table 8-69.  | Opcode: 0x3C (_INSERT_CRC6)                  |

| Table 8-70.  | Opcode: 0x86 (_EOC_RCVD_NEWDATA_STATUS) 8-27 |

| Table 8-71.  | Opcode: 0x87 (_EOC_READ_REG_DATA)            |

| Table 8-72.  | Opcode: 0x88 (_EOC_STATUS)8-28               |

| Table 8-73.  | Opcode: 0x80 (_SLM)8-36                      |

| Table 8-74.  | Opcode: 0x81 (_DC_METER)                     |

| Table 8-75.  | Opcode: 0x15 (_BER_METER_START)              |

| Table 8-76.  | Opcode: 0x16 (_BER_METER_STOP)               |

| Table 8-77.  | Opcode: 0x92 (_BER_METER_STATUS)             |

| Table 8-78.  | Opcode: 0x8C (_SELF_TEST)                    |

| Table 8-79.  | Opcode: 0x24 (_CU_SET_MFRAME)8-38            |

| Table 8-80.  | Opcode: 0x86 (_CU_ERROR_COUNTERS_LO)         |

| Table 8-81.  | Opcode: 0x87 (_CU_ERROR_COUNTERS_HI)         |

| Table 8-82.  | Opcode: 0x0A (_CU_CLEAR_ERROR_COUNTERS)      |

| Table 8-83.  | Opcode: 0x13 (_CU_COMBINE_ADDR)8-39          |

| Table 8-84.  | Opcode: 0x11 (_CU_COMBINE_VALUE)             |

| Table 8-85.  | Opcode: 0x12 (_CU_COMBINE_WRITE)             |

| Table 8-86.  | Opcode: 0x8B (_CU_READ_COMBINE)8-40          |

| Table 8-87.  | Opcode: 0x16 (_CU_ROUTE_ADDR)8-40            |

| Table 8-88.  | Opcode: 0x14 (_CU_ROUTE_VALUE)               |

| Table 8-89.  | Opcode: 0x15 (_CU_ROUTE_WRITE)               |

| Table 8-90.  | Opcode: 0x8C (_CU_READ_ROUTE)8-40            |

| Table 8-91.  | Opcode: 0x1B (_CU_TMAP1_VALUE)               |

| Table 8-92.  | Opcode: 0x1C (_CU_TMAP2_VALUE)               |

| Table 8-93.  | Opcode: 0x1D (_CU_TMAP3_VALUE)8-41           |

| Table 8-94.  | Opcode: 0x1E (_CU_TMAP4_VALUE)               |

| Table 8-95.  | Opcode: 0x1F (_CU_TMAP5_VALUE)               |

| Table 8-96.  | Opcode: 0x20 (_CU_WRITE_TMAP)                |

| Table 8-97.  | Opcode: 0x8D (_CU_READ_TMAP)                 |

| Table 8-98.  | Opcode: 0x21 (_CU_RMAP1_VALUE)8-42           |

| Table 8-99.  | Opcode: 0x22 (_CU_RMAP2_VALUE)8-42           |

| Table 8-100. | Opcode: 0x23 (_CU_RMAP3_VALUE)8-42           |

| Table 8-101. | Opcode: 0x24 (_CU_WRITE_RMAP)8-42            |

| Table 8-102. | Opcode: 0x8E (_CU_READ_RMAP)                 |

| Table 8-103. | Opcode: 0x17 (_CU_DBANK_1)                   |

| Table 8-104. | Opcode: 0x18 ( CU_DBANK_2)8-43               |

| Table 8-105. | Opcode: 0x19 (_CU_DBANK_3)                           |

|--------------|------------------------------------------------------|

| Table 8-106. | Opcode: 0x09 (_CU_FRAME_FORMAT)                      |

| Table 8-107. | Opcode: 0x0B (_CU_RESET_TX_FIF0)                     |

| Table 8-108. | Opcode: 0x04 (_CU_RESET_RX_FIF0)                     |

| Table 8-109. | Opcode: 0x0E (_CU_TFIFO_WL)                          |

| Table 8-110. | Opcode: 0x0F (_CU_RFIFO_WL_LO)                       |

| Table 8-111. | Opcode: 0x10 (_CU_RFIFO_WL_HI)                       |

| Table 8-112. | Opcode: 0x27 (_CU_SET_MASTER_LOOP)                   |

| Table 8-113. | Opcode: 0x27 (_CU_SET_MASTER_LOOP)                   |

| Table 8-114. | Opcode: 0x25 (_CU_BER_START)                         |

| Table 8-115. | Opcode: 0x26 (_CU_BER_CONFIGURE)                     |

| Table 8-116. | BER Parameter                                        |

| Table 8-117. | Opcode: 0x8A (_CU_MEASURE_BER)                       |

| Table 8-118. | Opcode: 0x89 (_CU_BER_STATUS)                        |

| Table 10-1.  | Possible Location Values of the Line Interface Cards |

| Table 10-2.  | Channel Unit Configuration Index                     |

| Table 10-3.  | Channel Unit htu_index Values                        |

| Table 10-4.  | Route Table Entry Definition                         |

| Table 10-5.  | Combine Table Entry Definition                       |

| Table 10-6.  | Transmit Payload Map (TMAP_1)                        |

| Table 10-7.  | Transmit Payload Map (TMAP_2)                        |

| Table 10-8.  | Transmit Payload Map (TMAP_3)                        |

| Table 10-9.  | Transmit Payload Map (TMAP_4)                        |

| Table 10-10. | Transmit Payload Map (TMAP_5)                        |

| Table 10-11. | Transmit Payload Map (TMAP_6)                        |

| Table 10-12. | Transmit Payload Map (TMAP_7)                        |

| Table 10-13. | Transmit Payload Map (TMAP_8)                        |

| Table 10-14. | Transmit Payload Map (TMAP_9)                        |

| Table 10-15. | Receive Payload Map (RMAP_1)10-12                    |

| Table 10-16. | Receive Payload Map (RMAP_2)10-12                    |

| Table 10-17. | Receive Payload Map (RMAP_3)10-12                    |

| Table 10-18. | Receive Payload Map (RMAP_4)                         |

| Table 10-19. | Receive Payload Map (RMAP_5)                         |

| Table 10-20. | Receive Payload Map (RMAP_6)10-13                    |

| Table 11-1.  | Initial PID Values (E1 Mode)                         |

| Table 11-2.  | API Functions                                        |

## 1.0 Introduction

This document describes the application and channel unit code distributed with the Conexant Evaluation Module Systems (EVMs). The application and channel unit code and bit pump code provide a complete DSL application. Refer to the *ZipWire Software User Guide* (100417C) for details of the bit pump code.

In Versions 5.3 and earlier, the channel unit code was primarily regarded as sample code for the evaluation boards. The code was written so the customer would be able to use it; however, it was incomplete and required extensive efforts by the end user.

Version 6.x is a more thorough software package. The main focus of the channel unit code is for the standard 1T1, 2T1, 1E1, 2E1, and 3E1 HDSL transport applications.

The channel unit is an extremely flexible device that can fit many applications. Even with all of the improvements, for many applications, the customer must modify the code.

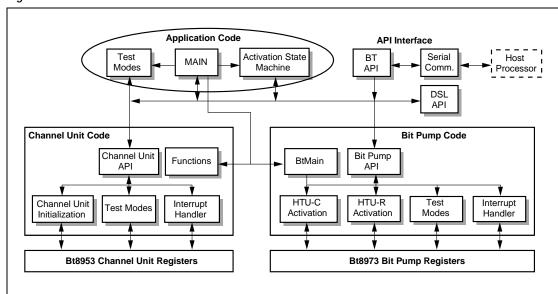

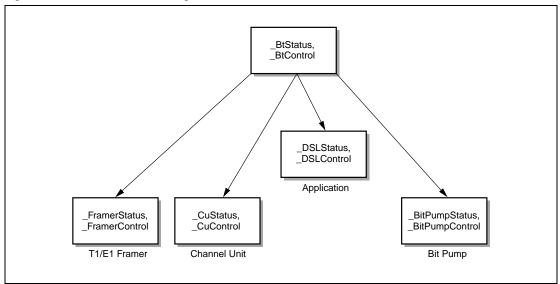

Figure 1-1 illustrates the software overview and interface to the HDSL chip sets. The bit pump code manages the transceiver functionality and the channel unit code is responsible for the framing functionality. The application code lays on top of the bit pump code and channel unit code and calls them to activate and maintain the system. The serial interface provides customer control of the system through a host computer.

Figure 1-1. Software Overview

#### 1.1 What's New in Channel Unit Version 6.x

The following features are added to the channel unit code version 6.x. See Chapter 6.0 for a detailed description of each feature.

#### 1.1.1 Bt8953A Revision C and RS8953B Support

Channel unit code version 6.x supports the newest channel unit devices: Bt8953A Rev. C and RS8953B.

#### 1.1.2 RS8973 versus Bt8970 Line Card Support

The channel unit PLL and stuffing values are based on the RS8973 XOUT values. The Bt8970 device will not work with any channel unit device (including the Conexant EVMs) because the Bt8970 XOUT frequency is different than the RS8973 XOUT frequency.

Customers who have both a Bt8970 and channel unit device must define the MCLK\_1024 directive.

#### 1.1.3 EOC Protocol

Previous versions of channel unit code did not support the ANSI/ETSI Embedded Operation Channel (EOC) protocol. In channel unit code version 6.x, the EOC protocol has been added and can be enabled by the CU\_EOC compiler flag defined in TYPEDEFS.H.

#### 1.1.4 Dynamic Loop Reversal and Master Loop

In channel unit code version 6.x, the master loop and the loop connections between the HTU-C and HTU-R are no longer fixed and can change dynamically.

#### 1.1.5 Performance Monitoring

In channel unit code version 6.x, Performance monitoring has been added to keep a history of CRC and FEBE errors at different time intervals. Performance monitoring can be enabled with the PERF\_MONITOR compiler flag defined in TYPEDEFS.H.

#### 1.1.6 Channel Blocking

Standard 2T1/2E1 channel blocking is implemented in channel unit code version 6.x.

RS8953B 1.0 Introduction

Application and Channel Unit Software Developer's Guide

1.2 Features and Functionality Not Supported

#### 1.1.7 Bt8370 Support

The Bt8370 T1/E1 framer/LIU support is added to the channel unit code version 6.x. The framer code configures the Bt8370 for either T1 or E1 mode. Bt8370 support can be enabled with the BT8370\_FRAMER compiler flag defined in TYPEDEFS.H.

### 1.2 Features and Functionality Not Supported

The following features or functionality are not by channel unit code version 6.x:

Bt8953A Evaluation Boards: Support for the Bt8510, Bt8360, and Bt8069 are compiler options

in version 6.x, which minimizes waste on ROM space. To revert to the Bt8510/Bt8360/Bt8069 framers, the compiler options must be enabled in the "TYPEDEFS.H" file. When using the Bt8510 or Bt8360 channel unit EVMs, the Bt8069 option should be enabled.

Loop Relativity: The term "loop relativity" is used to describe the EVM

motherboard slot where each line card is connected. Currently, if 1E1 or 1T1 is simulated, the line card must be in slot one. If the line card is in slot two or three, some application and channel unit

code features do not function properly.

Multiple Channel Unit Devices: The current release does not support multiple channel unit devices.

Contact Conexant for assistance.

1.0 Introduction RS8953B

1.2 Features and Functionality Not Supported

## 2.0 EVM Specific

This section describes any interaction of the software that is specific to the HDSL EVMs. Customers may need to modify the EVM-specific code for their platform.

#### 2.1 HDSL EVM Hardware

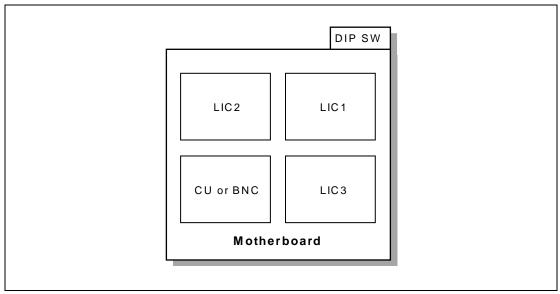

The modular HDSL EVM hardware is designed to accommodate the standard 1T1, 2T1, 1E1, 2E1, and 3E1 configurations. As illustrated in Figure 2-1, the HDSL EVM terminal unit consists of the following:

- Motherboard

- 1, 2, or 3 Line Interface Cards (LIC)