UCC28630, UCC28631 UCC28632, UCC28633, UCC28634

ZHCSC62D -MARCH 2014-REVISED DECEMBER 2017

# UCC2863x 高功率反激式控制器 具有初级侧稳压和峰值功率模式

## 1 特性

- 高功率初级侧 CV/CC 稳压

- 连续传导模式 (CCM) 和断续传导模式 (DCM) 运行

- 内置 700V 启动电流源

- 有源 X 电容器放电(UCC28630 和 UCC28633)

- 可调节恒定电流 (CC) 模式限制 (UCC28630 除外)

- 高栅极驱动电流, 1A 源电流和 2A 灌电流

- 针对系统待机功率小于 30mW 的低功率模式

- 业界一流的轻负载 (10%) 效率 >85%

- PSR 设计不包含光耦合器 可达到 CM 隔离和浪涌的高要求

- 用于开环反馈故障条件下独立间接输出过压的 VDD OVP

- 针对瞬态过载的峰值功率模式

- 外部 NTC 的关断引脚接口

- 保护:过压、过流、过热、过载计时器 (UCC28630)、交流线路 UV、欠压和引脚保护

- 频率抖动以轻松符合 EMI 标准(UCC28632 除外)

- 使用 UCC2863x 并借助 WEBENCH® Power Designer 创建定制设计方案

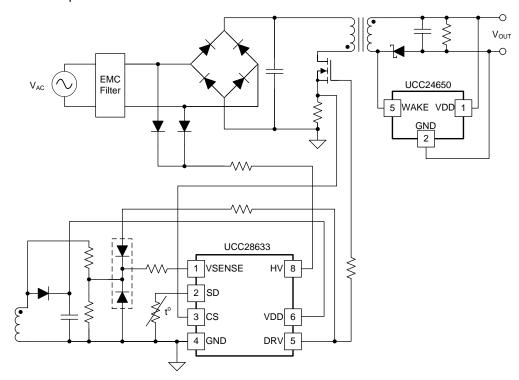

## 2 应用

- 针对笔记本电脑、游戏机和打印机的交流-直流适配器

- 针对工业、打印机、大型家电和 LCD 显示器的开放式结构开关模式电源 (SMPS)

- 针对 10W 至 65W 标称功率的高能效交流-直流电源,(具有高达 200% 的瞬态峰值功率)

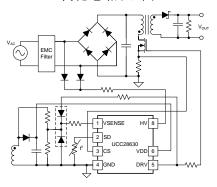

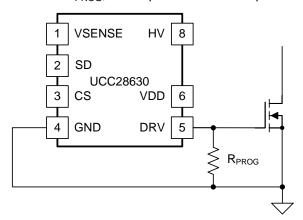

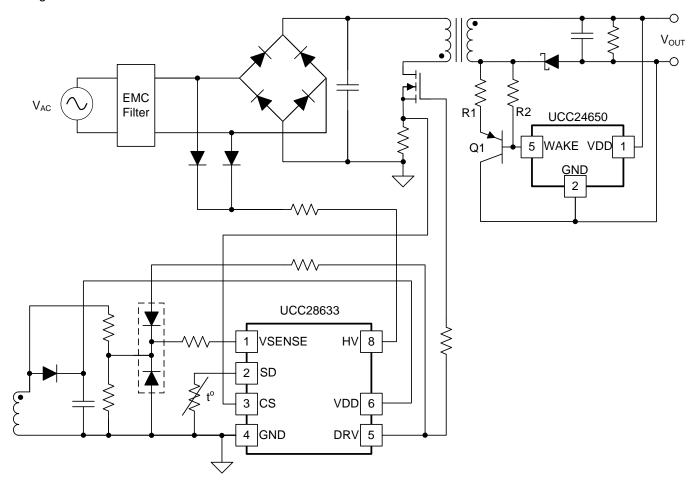

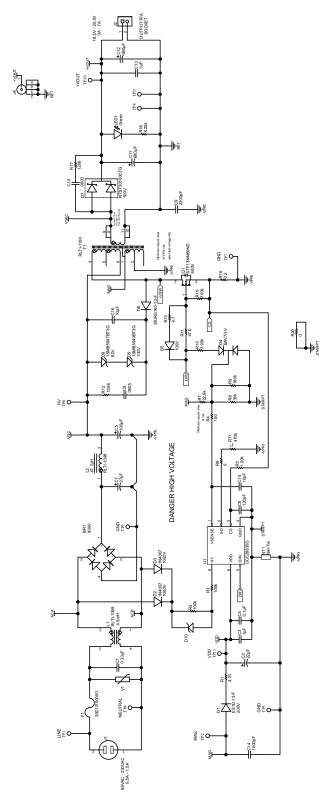

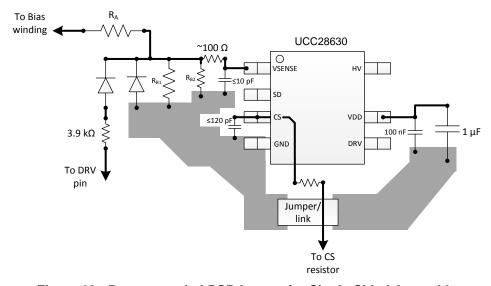

#### 简化电路原理图

## 3 说明

UCC2863x 适用于高功率初级侧稳压反激式变换器。 此器件能够以 CCM 和 DCM 模式运行,适用于 具有 宽功率范围 的应用。峰值功率模式使得瞬态峰值功率 能够达到标称额定值的 200%,峰值电流只增加 25%,最大限度地增加了变压器利用率。

变压器偏置绕组被用来感测输出电压以实现稳压,并用于低损耗输入电压感测。采用了先进的取样技术,可支持 CCM 运行,并在 100W 及以上功率范围内实现无光耦合器设计的出色输出电压稳压性能。

高压电流源可实现快速和高效启动。部署了先进的轻负载模式,可减少控制器和系统在无负载和轻负载状态下的功率消耗。这些模式支持潜在的系统设计,以满足30mW 无负载功耗对高达 30W 标称功率和 60W 峰值功率电源设计的需要。

按照设计,此器件易于使用并整合了多种特性,可实现多种设计。设计包含大量的保护特性以简化系统设计。

请参阅表格1《器件比较表》以了解各器件间的具体差异。

器件信息

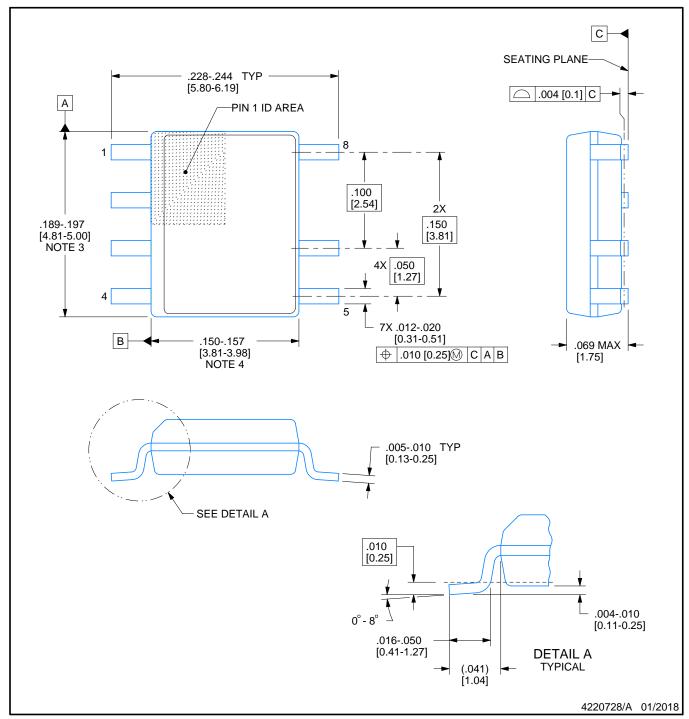

| 器件型号     | 封装       | 封装尺寸            |

|----------|----------|-----------------|

| UCC28630 |          |                 |

| UCC28631 |          |                 |

| UCC28632 | SOIC (7) | 4.90mm x 3.90mm |

| UCC28633 |          |                 |

| UCC28634 |          |                 |

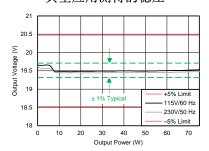

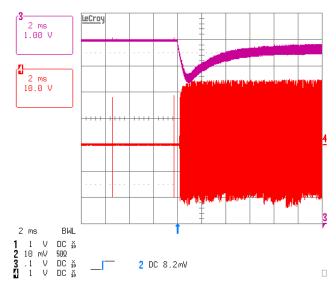

## 典型应用测得的稳压

# 目录

| 1 | 特性1                                  |    | 8.4 Device Functional Modes     | 52              |

|---|--------------------------------------|----|---------------------------------|-----------------|

| 2 | 应用 1                                 | 9  | Applications and Implementation | 53              |

| 3 | 说明 1                                 |    | 9.1 Application Information     | 53              |

| 4 | 修订历史记录                               |    | 9.2 Typical Application         | 53              |

| 5 | Device Comparison Table5             |    | 9.3 Dos and Don'ts              | <mark>73</mark> |

| 6 | Pin Configuration and Functions 5    | 10 | Power Supply Recommendations    | <mark>73</mark> |

| 7 | Specifications6                      | 11 | Layout                          | 74              |

| • | 7.1 Absolute Maximum Ratings 6       |    | 11.1 Layout Guidelines          | 74              |

|   | 7.2 ESD Ratings                      |    | 11.2 Layout Example             | <mark>75</mark> |

|   | 7.3 Recommended Operating Conditions | 12 | 器件和文档支持                         | <mark>76</mark> |

|   | 7.4 Thermal Information              |    | 12.1 商标                         | <mark>76</mark> |

|   | 7.5 Electrical Characteristics       |    | 12.2 静电放电警告                     | <mark>76</mark> |

|   | 7.6 Typical Characteristics          |    | 12.3 Glossary                   | <mark>76</mark> |

| 8 | Detailed Description                 |    | 12.4 器件支持                       | <mark>76</mark> |

| U | 8.1 Overview                         |    | 12.5 文档支持                       | <mark>76</mark> |

|   | 8.2 Functional Block Diagram         | 13 | 机械、封装和可订购信息                     | <mark>77</mark> |

|   | 8.3 Feature Description              |    |                                 |                 |

# 4 修订历史记录

| Changes from Revision C (March 2015) to Revision D                                | Page                      |

|-----------------------------------------------------------------------------------|---------------------------|

| • 已添加 UCC28634 初始发行版。                                                             | 1                         |

| 已删除 删除了文本"适用于 65W 标称功率设计"                                                         | 1                         |

| 已添加 添加了文本"PSR 设计不包含光耦合器 - 可达到 CM 隔离和浪涌的高要求"                                       | 1                         |

| 已添加 添加了文本"用于开环反馈故障条件下独立间接输出过压的 VDD OVP"                                           | 1                         |

| 已添加 Webench 链接。                                                                   | 1                         |

| 已添加 添加了文本"请参阅《器件比较表》以了解各器件间的具体差异"                                                 | 1                         |

| 已添加 向器件信息表中添加了 UCC28634。                                                          | 1                         |

| Added UCC28634 to the Device Comparison Table                                     | 5                         |

| Added UCC28634 to Thermal Information                                             | 7                         |

| Added UCC28634 to Electrical Characteristics                                      | 8                         |

| Added UCC28634 to Electrical Characteristics                                      | 8                         |

| Changed picture to represent added UCC28634                                       | 10                        |

| Added UCC28634                                                                    |                           |

| Added UCC28634                                                                    |                           |

| Added UCC28634                                                                    | 16                        |

| Changed to correct picture link                                                   |                           |

| Changed to fix equation typo                                                      | 21                        |

| Added UCC28634                                                                    | 41                        |

| Changed to correct typo                                                           | 41                        |

| Changed to correct typo, changed from 4.7 to 47                                   | 41                        |

| Added paragraph to clarify the fault protection.                                  | 41                        |

| Added UCC28634                                                                    | 42                        |

| Added text "For UCC28634, all pin-faults are non-latching."                       | 43                        |

| Added UCC28634 to the table                                                       | 52                        |

| Changed equation to fix typo                                                      | 67                        |

|                                                                                   |                           |

| Changes from Revision B (March 2014) to Revision C                                | Page                      |

| Changed "No" to "Yes" in Device Comparison Table for Part# UCC28633D, "ACTIVE->   | CAPACITOR DISCHARGE"      |

| column                                                                            | 5                         |

| Changed "Handling Ratings" table to "ESD Ratings" table. Moved Storage Temperatur | e and Lead Temperature to |

| Abs Max Ratings table.                                                            | 6                         |

| Revised Figure 40                                                                 | 47                        |

| 01                                                                                | P                         |

| Changes from Revision A (January 2014) to Revision B                              | Page                      |

| 已添加 向数据表中添加了 UCC28631、UCC28632 和 UCC28633 器件。                                     | 1                         |

| 已添加 添加了 UCC28630 和 UCC28633 的有源 X 电容器放电功能参考。                                      | 1                         |

| 已添加 添加了可调节恒定电流 (CC) 模式限制项目符号。                                                     | 1                         |

| 己添加 添加了 UCC28630(仅限)的过载计时器参考。                                                     | 1                         |

| 已添加 添加了频率抖动以轻松符合 EMI 标准(UCC28632 除外)。                                             | 1                         |

| 已添加 向器件信息部分中添加了 UCC28631D、UCC28632D 和 UCC28633D。                                  | 1                         |

| Added Device Comparison Table                                                     | 5                         |

| Added UCC28632 Frequency dither range exception.                                  | 8                         |

| Added UCC28632 Dither repetition period exception.                                | 8                         |

| ·                                                                                 |                           |

## UCC28630, UCC28631 UCC28632, UCC28633, UCC28634

ZHCSC62D -MARCH 2014-REVISED DECEMBER 2017

|  |  |  | cr |

|--|--|--|----|

|  |  |  |    |

| •  | Added UCC28633 Wake-up level (rising) exception.                                                                      | 8     |

|----|-----------------------------------------------------------------------------------------------------------------------|-------|

| •  | Added UCC28633 SD V <sub>WAKE(rise)</sub> vs. Temperature exception                                                   |       |

| •  | Added text to the, "The controller operates in either DCM and CCM" paragraph                                          |       |

| •  | Changed the "Supply the device bias power during latched fault mode" bullet                                           |       |

| •  | Added UCC28630 and UCC28633 only exception to the "AC sense input for X-capacitor discharge detect" bullet            |       |

| •  | Changed HV Pin Connection diagram.                                                                                    |       |

| •  | Added sentence, "In the UCC28631 and the UCC28632, the HV pin can connect to either the AC or DC side of the bridge." |       |

| •  | Added VIN(avg) definition.                                                                                            | 16    |

| •  | Added (UCC28630 and UCC28633 only) to the Active X-Capacitor Discharge section                                        | 19    |

| •  | Added UCC28633 to the Improved Performance with UCC28630 section.                                                     | 20    |

| •  | Added UCC28631, UCC28632 and the UCC28633 I <sub>OUT(lim)</sub> adjustment note.                                      | 37    |

| •  | Added UCC28630 only note to the Primary-Side Overload Timer section.                                                  | 38    |

| •  | Added UCC28630 only note added to the Overload Timer Adjustment section.                                              | 40    |

| •  | Added CC-Mode I <sub>OUT(lim)</sub> Adjustment section.                                                               | 41    |

| •  | Added UCC28631, UCC28632 and the UCC28633 to the Fault Sources and Associated Responses table                         | 42    |

| •  | Added The fault response (latching or auto recovery) depends on the device variant, per Table 4                       | 44    |

| •  | Added The fault response (latching or recovery) depends on the device variant, per Table 4.                           | 44    |

| •  | Added UCC28633 exception to the External SD Pin Wake Input section.                                                   |       |

| •  | Added External Wake Input at VSENSE Pin (UCC28633 Only) section                                                       |       |

| •  | Added UCC28632 exception to the Frequency Dither For EMI section                                                      | 51    |

| •  | Added External Wake Pulse Calculation at VSENSE Pin (UCC28633 Only) section                                           |       |

| Cł | hanges from Original (January 2014) to Revision A                                                                     | Page  |

| •  | 已更改 将销售状态从产品预览改为量产数据。                                                                                                 | <br>1 |

# 5 Device Comparison Table

**Table 1. Device Comparison Table**

|              | FEATURES                           |                   |                        |                     |                            |  |

|--------------|------------------------------------|-------------------|------------------------|---------------------|----------------------------|--|

| ORDER NUMBER | ACTIVE-X<br>CAPACITOR<br>DISCHARGE | OVERLOAD<br>TIMER | ADJUSTABLE<br>CC LIMIT | FREQUENCY<br>DITHER | SECONDARY-<br>SIDE WAKE UP |  |

| UCC28630D    | Yes                                | Yes               | No                     | Yes                 | SD Pin                     |  |

| UCC28631D    | No                                 | No                | Yes                    | Yes                 | SD Pin                     |  |

| UCC28632D    | No                                 | No                | Yes                    | No                  | SD Pin                     |  |

| UCC28633D    | Yes                                | No                | Yes                    | Yes                 | VSENSE Pin                 |  |

| UCC28634D    | No                                 | No                | Yes                    | Yes                 | SD Pin                     |  |

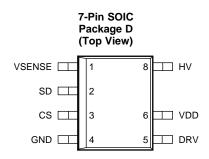

# 6 Pin Configuration and Functions

## **PIN Functions**

|        | T IN T GITOGOTO |     |                                                                                                                                                                                                                                 |  |  |  |  |

|--------|-----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PIN    |                 |     | DESCRIPTION                                                                                                                                                                                                                     |  |  |  |  |

| NAME   | NO.             | I/O | DESCRIPTION                                                                                                                                                                                                                     |  |  |  |  |

| CS     | 3               | I   | Current sense input                                                                                                                                                                                                             |  |  |  |  |

| DRV    | 5               | 0   | Output drive pin for the external flyback MOSFET                                                                                                                                                                                |  |  |  |  |

| GND    | 4               | G   | Ground reference connection for all signals                                                                                                                                                                                     |  |  |  |  |

| HV     | 8               | Р   | High-voltage connection to the internal high-voltage start-up current source                                                                                                                                                    |  |  |  |  |

| SD     | 2               | I   | Latching fault shutdown input pin. May be connected to an external temperature sensor                                                                                                                                           |  |  |  |  |

| VDD    | 6               | Р   | Bias supply input pin to the device. Decoupled with a 1-µF ceramic bypass capacitor, connect directly across pins 6-4. Connect an additional hold-up capacitor charged from the transformer auxiliary bias winding to this pin. |  |  |  |  |

| VSENSE | 1               | I   | Sense pin for the flyback transformer bias and sense winding for output feedback regulation, output OVP, and input voltage sense/UV protection                                                                                  |  |  |  |  |

## 7 Specifications

## 7.1 Absolute Maximum Ratings<sup>(1)</sup>

over operating junction temperature range (unless otherwise noted)

|                             |                                | MIN  | MAX | UNIT |

|-----------------------------|--------------------------------|------|-----|------|

| Start-up pin voltage        | HV                             |      | 700 |      |

| Bias supply voltage         | VDD                            |      | 20  |      |

| Current sense input voltage | cs                             | -0.3 | 1.5 | V    |

| All other inner nine        | VSENSE                         | -0.3 | VDD |      |

| All other input pins        | SD                             | -0.3 | VDD |      |

| Operating junction tem      | perature range, T <sub>J</sub> | -40  | 125 |      |

| Storage temperature, 7      | r<br>stg                       | -65  | 125 | °C   |

| Lead temperature            |                                |      | 260 |      |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. All voltages are with respect to GND. These ratings apply over the junction operating temperature ranges unless otherwise noted.

## 7.2 ESD Ratings

|             |                                        |                                                                                | VALUE | UNIT |

|-------------|----------------------------------------|--------------------------------------------------------------------------------|-------|------|

|             |                                        | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (2)                         | ±2000 |      |

| $V_{(ESD)}$ | Electrostatic discharge <sup>(1)</sup> | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(3)</sup> | ±500  | V    |

<sup>(1)</sup> Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges into the device.

#### 7.3 Recommended Operating Conditions

over operating junction temperature range (unless otherwise noted)

|                                                                         | MIN | NOM | MAX | UNIT |

|-------------------------------------------------------------------------|-----|-----|-----|------|

| CS input                                                                | 0   |     | 1.0 | V    |

| All other inputs (except HV, CS)                                        | 0   |     | VDD | V    |

| SD pin external capacitance                                             | 0   |     | 1   | nF   |

| R <sub>HV</sub> , external resistor on HV pin, see Figure 15            | 180 | 200 | 220 | kO   |

| R <sub>P</sub> , external pull-up resistor on VSENSE pin, see Figure 21 | 3.8 | 3.9 | 4.0 | kΩ   |

<sup>(2)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions. Pins listed as ±2000 V may actually have higher performance.

<sup>(3)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions. Pins listed as ±500 V may actually have higher performance.

## 7.4 Thermal Information

|                   |                                              | UCC28630 | UCC28631 |      |

|-------------------|----------------------------------------------|----------|----------|------|

|                   | THERMAL METRIC <sup>(1)</sup>                | D        | D        | UNIT |

|                   |                                              | 7 PINS   | 7 PINS   |      |

| $\theta_{JA}$     | Junction-to-ambient thermal resistance       | 128.5    | 128.5    |      |

| $\theta_{JCtop}$  | Junction-to-case (top) thermal resistance    | 57.3     | 57.3     |      |

| $\theta_{\sf JB}$ | Junction-to-board thermal resistance         | 83.4     | 83.4     | °C/W |

| ΨЈТ               | Junction-to-top characterization parameter   | 12.3     | 12.3     |      |

| ΨЈВ               | Junction-to-board characterization parameter | 82.1     | 82.1     |      |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

|                  |                                              | UCC28632 | UCC28633 | UCC28634 |      |

|------------------|----------------------------------------------|----------|----------|----------|------|

|                  | THERMAL METRIC <sup>(1)</sup>                | D        | D        | D        | UNIT |

|                  |                                              | 7 PINS   | 7 PINS   | 7 PINS   |      |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance       | 128.5    | 128.5    | 128.5    |      |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance    | 57.3     | 57.3     | 57.3     |      |

| $\theta_{JB}$    | Junction-to-board thermal resistance         | 83.4     | 83.4     | 83.4     | °C/W |

| ΨЈТ              | Junction-to-top characterization parameter   | 12.3     | 12.3     | 12.3     |      |

| ΨЈВ              | Junction-to-board characterization parameter | 82.1     | 82.1     | 82.1     |      |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

#### 7.5 Electrical Characteristics

over operating junction temperature range (unless otherwise noted) and VDD = 12 V

|                         | PARAMETER                                                  | TEST CONDITIONS                                                                               | MIN   | TYP    | MAX      | UNIT |

|-------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------|--------|----------|------|

| START-UP                | CURRENT SOURCE                                             |                                                                                               |       |        | <u> </u> |      |

| I <sub>VDD0</sub>       | VDD pin short-circuit charging current                     | VDD = 0.2 V, V <sub>HV</sub> = 100 V                                                          | 0.6   | 0.9    | 1.2      | mA   |

| $I_{VDD1}$              | VDD pin final charging current                             | VDD = 11.9 V, V <sub>HV</sub> = 100 V                                                         | 1.1   | 4.0    | 7.6      | mA   |

| I <sub>LEAK</sub>       | HV current source leakage current                          | VDD = 18 V, $V_{HV}$ = 100 V HV, current source off, $T_A$ = 25°C                             |       | 0.1    | 0.5      | μΑ   |

| SUPPLY V                | OLTAGE MONITORING                                          |                                                                                               |       |        |          |      |

| V <sub>DD(start)</sub>  | VDD start-up voltage                                       | VDD increasing                                                                                | 13.00 | 14.75  | 16.50    | V    |

| V <sub>DD(stop)</sub>   | VDD minimum operating voltage after start-up               | VDD decreasing after start-up                                                                 | 7.3   | 8.0    | 8.5      | V    |

| V <sub>DD(hyst)</sub>   | VDD start – VDD stop level                                 |                                                                                               |       | 6.5    |          | V    |

| V <sub>DD(reset)</sub>  | VDD reset restart level                                    |                                                                                               | 3.5   | 5.0    | 6.5      | V    |

| $V_{DD(ovp)}$           | VDD over-voltage protection level                          | VDD increasing after start-up,<br>UCC28630, UCC28631, UCC28632,<br>UCC28633                   | 16.5  | 17.5   | 18.3     | V    |

|                         |                                                            | VDD increasing after start-up, UCC28634 only                                                  | 14.0  | 14.85  | 15.55    | V    |

| I <sub>DD(run)</sub>    | Supply current during normal operation                     | V <sub>SENSE</sub> = 0.45 V, CS = 0 V See <sup>(1)</sup><br>C <sub>LOAD</sub> = 700 pF on DRV | 6.0   | 9.0    | 13.0     | mA   |

| I <sub>DD(sleep)</sub>  | Supply current during sleep mode, between switching pulses | $V_{SENSE}$ = 8.0 V, $V_{CS}$ = 1.0 V, light-load mode at 200 Hz, $T_A$ = 25°C                |       | 90     | 110      | μΑ   |

| OSCILLAT                | OR                                                         |                                                                                               |       |        |          |      |

| f <sub>SW(max)</sub>    | Maximum switching frequency                                | V <sub>SENSE</sub> = 0.45 V, V <sub>CS</sub> = 0 V                                            | 110   | 120    | 130      | kHz  |

| f <sub>SW(min)</sub>    | Minimum switching frequency                                | $V_{SENSE}$ = 8.0 V, $V_{CS}$ = 1.0 V, light-load mode                                        | 0.18  | 0.20   | 0.22     | kHz  |

| D <sub>MAX</sub>        | Maximum Duty Cycle                                         | V <sub>SENSE</sub> = 0.45 V, V <sub>CS</sub> = 0 V                                            |       | 70%    |          |      |

| t <sub>ON(min)</sub>    | Minimum On time                                            | V <sub>SENSE</sub> = 8.0 V, V <sub>CS</sub> = 1.0 V, light-load mode                          | 550   | 600    | 650      | ns   |

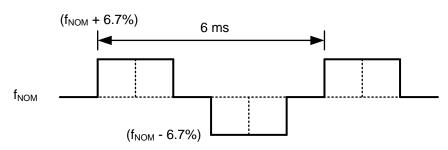

| f <sub>SW(dith)</sub>   | Frequency dither range                                     | Except UCC28632                                                                               |       | ± 6.7% |          |      |

| t <sub>DITH</sub>       | Dither repetition period                                   | Except UCC28632                                                                               |       | 6.0    |          | ms   |

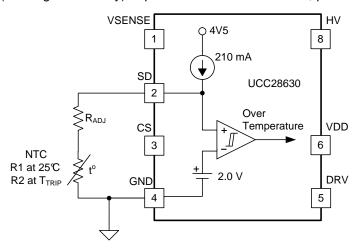

| SHUTDOW                 | N (SD) PIN (EXTERNAL FAULT INPU                            | JT) <sup>(2)</sup>                                                                            |       |        |          |      |

| I <sub>PULLUP</sub>     | Internal pull-up current source                            | See (2), (3), (4)                                                                             | 185   | 210    | 235      | μΑ   |

| $V_{TRIP(rise)}$        | Fault ok level (rising)                                    | See <sup>(2)</sup> , <sup>(3)</sup> , <sup>(4)</sup> , UCC28630, UCC28631, UCC28632,UCC28633  | 3.2   | 3.5    | 3.8      | V    |

|                         |                                                            | See <sup>(2)</sup> , <sup>(3)</sup> , <sup>(4)</sup> , UCC28634 only                          | 2.2   | 2.5    | 2.8      | V    |

| V <sub>TRIP(fall)</sub> | Fault trip level (falling)                                 | See <sup>(2)</sup> , <sup>(3)</sup> , <sup>(4)</sup>                                          | 1.7   | 2.00   | 2.3      | V    |

| V <sub>TRIP(hyst)</sub> |                                                            | See (2), (3), (4)                                                                             |       | 1.5    |          | V    |

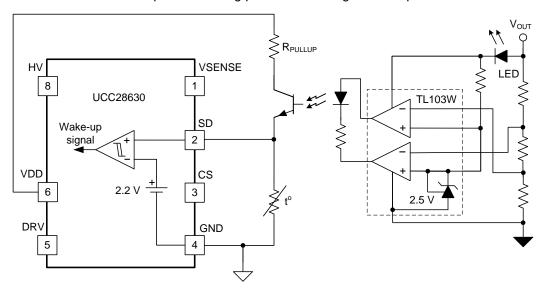

| $V_{\text{WAKE(rise)}}$ | Wake-up level (rising)                                     | See <sup>(2)</sup> , <sup>(3)</sup> , <sup>(4)</sup> Except UCC28633                          | 1.8   | 2.2    | 2.6      | V    |

| t <sub>WAKE</sub>       | Wake delay time                                            | Delay to first DRV pulse                                                                      |       | 10     |          | μs   |

$C_{LOAD}$  = 700 pF included on DRV pin.

The SD pin functions as an NTC input pin (with internal pull-up) during normal operation. The internal pull-up is clamped to 4 V. At startup, the external temperature sensor (NTC) must be cool enough that the SD pin pulls up above the V<sub>TRIP(rise)</sub> start level. After start-up, if

this pin is pulled below  $V_{TRIP(fall)}$  level, this activates external over-temperature shut-down. During low power modes (when  $F_{SW} < F_{SMP(max)}$ ), the internal SD pin pull-up is disabled, and the pin functions as a transient wake-up input. In this case, if the pin is raised above  $V_{WAKE(rise)}$  level, the device wakes from low power sleep mode (rather than waiting for the scheduled timer-based wake). This is useful for applications that require a response to load transients from zero or near-zero load, where a wake-up signal can be appropriately coupled to the SD pin from the secondary-side.

A decoupling capacitor on the SD pin should not be required; if used, it must not exceed 1 nF.

# **Electrical Characteristics (continued)**

over operating junction temperature range (unless otherwise noted) and VDD = 12 V

|                             | PARAMETER                                     | TEST CONDITIONS                                                   | MIN   | TYP   | MAX   | UNIT  |  |  |  |  |

|-----------------------------|-----------------------------------------------|-------------------------------------------------------------------|-------|-------|-------|-------|--|--|--|--|

| VSENSE Pin (MAGNETIC SENSE) |                                               |                                                                   |       |       |       |       |  |  |  |  |

| V <sub>OUT(ref)</sub>       | Internal output voltage sense reference level | Required positive voltage at VSENSE pin during off-time (at 25°C) | 7.425 | 7.500 | 7.575 | V     |  |  |  |  |

| t <sub>OUT(smp)</sub>       | Vsense sample delay for $V_{\text{OUT}}$      | Measured w.r.t. DRV falling edge                                  |       | 1.7   |       | μs    |  |  |  |  |

| V <sub>OUT(ovp)</sub>       | Internal output voltage sense OVP level       | Measured w.r.t. regulation level, tracking                        |       | 120%  |       |       |  |  |  |  |

| CURRENT                     | SENSE (CS) Pin                                |                                                                   |       |       |       |       |  |  |  |  |

| V <sub>CS(max)</sub>        | Peak CS pin voltage level                     | At maximum modulator demand                                       |       | 800   |       | mV    |  |  |  |  |

| V <sub>CS(min)</sub>        | Peak CS pin voltage level                     | At minimum modulator demand                                       |       | 172   |       | mV    |  |  |  |  |

| V <sub>SLOPE</sub>          | Slope compensation ramp                       |                                                                   |       | 30    |       | mV/μs |  |  |  |  |

| OVER TEM                    | PERATURE PROTECTION                           |                                                                   |       |       |       |       |  |  |  |  |

| TEMP <sub>TRIP</sub>        | Thermal protection shutdown temperature       | Default internal setting, latch-off protection                    |       |       | 125   | °C    |  |  |  |  |

| TEMP <sub>HYST</sub>        | Thermal protection hysteresis                 |                                                                   |       | 10    |       | °C    |  |  |  |  |

| GATE DRIV                   | /E OUTPUT (DRV)                               |                                                                   |       |       |       |       |  |  |  |  |

| R <sub>OH</sub>             | High level source resistance                  | I <sub>OH</sub> = 100 mA                                          |       | 22    | 35    | Ω     |  |  |  |  |

| R <sub>OL</sub>             | Low level sink resistance                     | I <sub>OL</sub> = -100 mA                                         |       | 1.2   | 2.5   | Ω     |  |  |  |  |

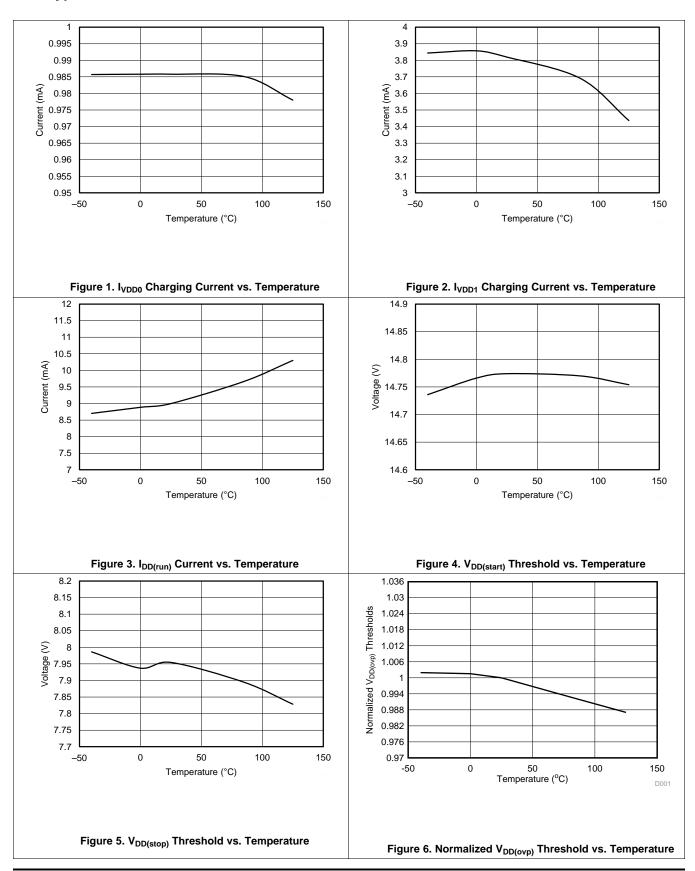

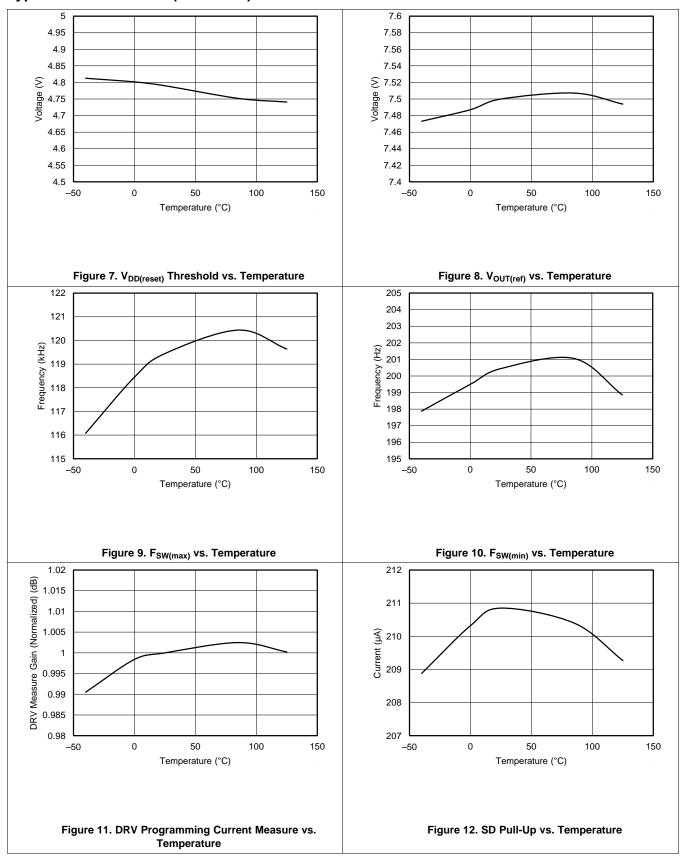

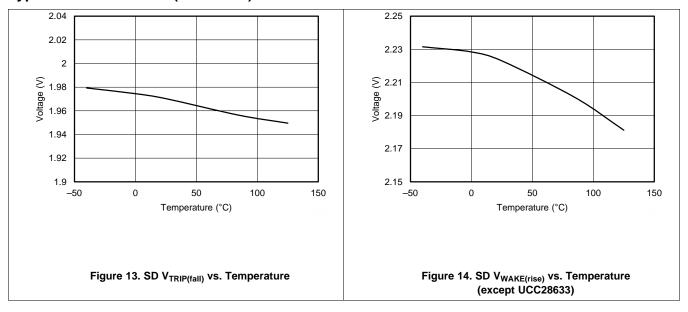

## 7.6 Typical Characteristics

## **Typical Characteristics (continued)**

# **Typical Characteristics (continued)**

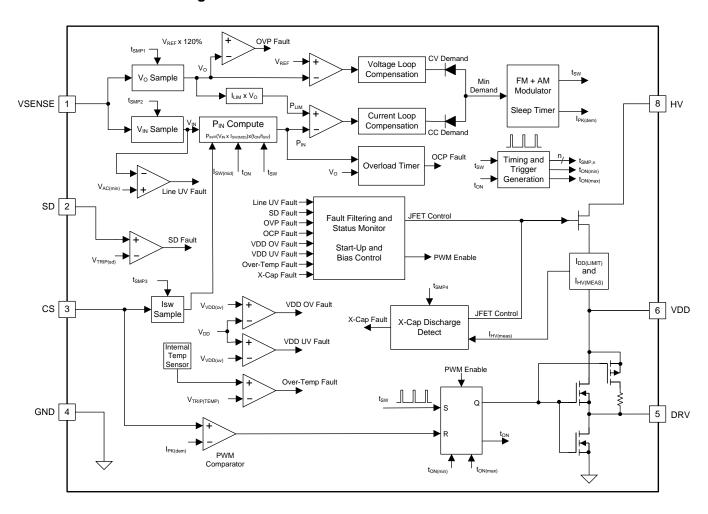

## 8 Detailed Description

#### 8.1 Overview

The UCC28630, UCC28631, UCC28633, UCC28633 and UCC28634 family of devices are highly-integrated, primary-side-regulated (PSR) flyback controllers. The device supports magnetically-sensed output voltage regulation via the transformer bias winding. This feature eliminates the need for a secondary-side reference, error amplifier and opto-isolator. The device employs an advanced internal control algorithm that offers accurate static output voltage regulation against line and load. The fixed-point, magnetic-sampling scheme allows operation in both continuous conduction mode (CCM) and discontinuous conduction mode (DCM). Additionally, the device achieves accurate constant-current (CC) control of the output current limit using only primary-side, current sensing. Uniquely, this CC function operates seamlessly as the operating mode changes between DCM and CCM operation.

The controller includes an internal, high-voltage (HV) start-up current-source, and employs low-power sleep modes and switching frequency reduction, to improve light-load efficiency and standby power. The device typically achieves standby power levels between 0.05% and 0.1% of peak output power.

The controller operates in either DCM and CCM, using a mix of peak current-mode PWM (AM) and switching-frequency modulation (FM) schemes. The control approach improves performance (efficiency, size and cost) and can reduce transformer size and cost by allowing operation in CCM with FM during peak overload conditions. Extensive protection features are incorporated, including output overvoltage protection (OVP), bias rail overvoltage and undervoltage (OV/UV), active X-capacitor discharge, line undervoltage and brownout protection, overcurrent overload timer, open- and short-circuit pin protections, peak current adjustment with line and frequency dither for system EMI reduction. The various devices in the UCC2863x family offer a different mix of features to suit a wide range of applications and requirements.

## 8.2 Functional Block Diagram

#### 8.3 Feature Description

The application designer requires some key device internal parameters in order to calculate the required power stage components and values for a given design specification. Table 7 summarizes the key parameters.

#### 8.3.1 High-Voltage Current Source Start-Up Operation

The controller includes a switched, high-voltage, current source on the HV pin to allow fast start-up, and eliminates the static power dissipation in a conventional resistive start-up approach. This feature reduces standby power consumption.

The HV pin has three major functions:

- · Supply the device start-up current

- Supply the device bias power during latched fault mode

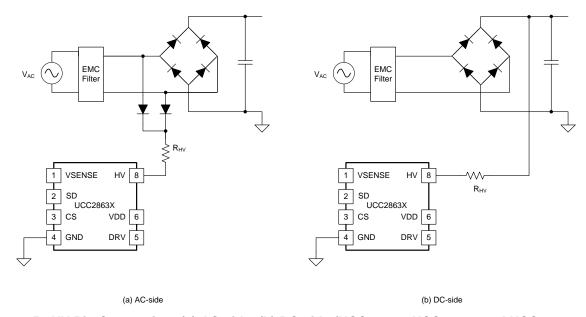

- AC sense input for X-capacitor discharge detect (UCC28630 and UCC28633 only)

The UCC28630 and UCC28633 input supply to the HV start-up pin must be connected to the AC side of the bridge rectifier as shown in Figure 15, in order to support X-capacitor discharge. More details are given in Active X-Capacitor Discharge (UCC28630 and UCC28633 only), below. Connection to the AC side of the bridge also allows faster detection of AC mains removal under latched fault conditions, allowing prompt reset of latched faults for fast restart.

Figure 15. HV Pin Connection: (a) AC-side, (b) DC-side (UCC28631, UCC28632 and UCC28634 only)

In the UCC28631, UCC28632 and UCC28634, the HV pin can connect to either the AC or DC side of the bridge. The addition of the 200-k $\Omega$  external HV resistance (required for X-capacitor discharge sensing) limits the available charging current for the external bias supply input capacitor. However, for typical values of between 22  $\mu$ F and 33  $\mu$ F of input capacitance, start-up bias times of less than 1.5 s are achievable at 90 V<sub>AC</sub>. Start-up time can be estimated using Equation 1.

$$t_{START} = R_{HV} \times C_{VDD} \times ln \left( \frac{V_{IN(avg)}}{V_{IN(avg)} - V_{DD(start\ max)}} \right)$$

where

$$V_{IN(avg)} = V_{RMS} \times \frac{2 \times \sqrt{2}}{\pi}$$

for AC connection and  $V_{IN(avg)} = V_{RMS} \times \sqrt{2}$  for DC connection (1)

For 90  $V_{AC}$ , if  $C_{VDD}$  = 22  $\mu F$  and worst case  $V_{DD(start\_max)}$  = 16.5 V, then  $t_{START}$  is 1.002 s.

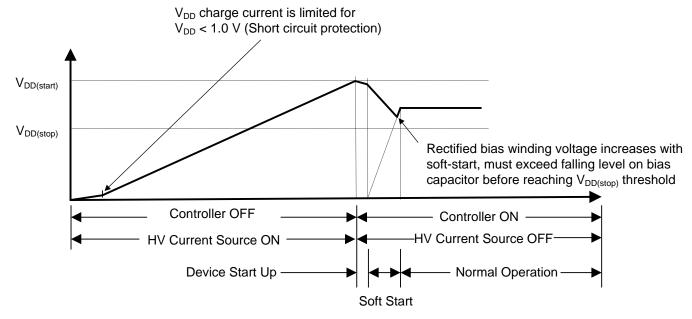

Figure 16 illustrates the start-up behavior of the controller. The HV current source has built-in short-circuit protection that limits the initial charge current out of the bias voltage pin until the bias voltage reaches  $V_{DD(sc)}$ . This limits the power dissipated in the HV current source in the event of a short circuit on the VDD pin. Thereafter, the HV current source switches to full available current. The controller remains in a low-power, start-up mode until the bias voltage reaches  $V_{DD(start)}$ , after which the HV current source is turned off and the controller initiates a start-up sequence.

The bias voltage decays during the start-up sequence at a rate dependent on the size of the energy storage capacitor connected to the VDD pin. The VDD storage capacitor must be sized appropriately to ensure adequate energy storage to supply both the controller bias power and MOSFET drive power during start-up, until the VDD rail can be supplied through the transformer bias winding. If the bias voltage falls below  $V_{DD(stop)}$  (due to bias winding fault or an inadequate VDD storage capacitance), the controller stops switching, and transitions into low-power mode for a time delay of  $t_{RESET(long)}$ , or until the bias voltage falls to the  $V_{DD(reset)}$  level, whichever is shorter. See VDD Capacitor Selection for required VDD capacitor sizing. Once the time delay elapses, the bias voltage rapidly discharges to the  $V_{DD(reset)}$  level, followed by turn-on of the internal HV current source, and a normal restart attempt follows.

Figure 16. Normal Start-Up Sequence, (assuming  $V_{AC} > UV$  start threshold)

#### 8.3.2 AC Input UVLO / Brownout Protection

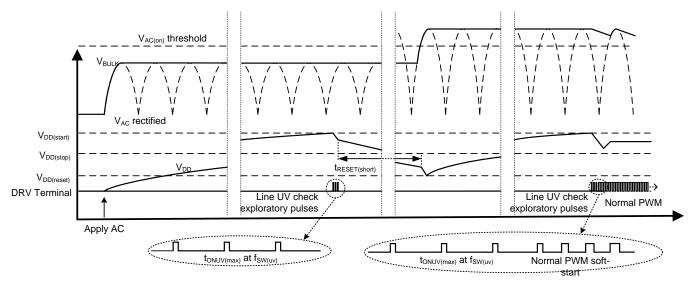

At start-up, once the VDD pin has reached the  $V_{DD(start)}$  level, the internal start-up current source is turned off. The controller tests the voltage across the bulk capacitor to determine if the level is high enough to allow the power stage to start, if it has exceeded the rising  $AC_{ON}$  level. Because there is no load across the bulk capacitor at this stage, the bulk voltage can be used as a proxy for the peak of the AC line. In order to measure the bulk voltage in a low-loss fashion, the controller generates a sequence of three exploratory switching pulses at a frequency of  $f_{SW(uv)}$ , at minimum peak-current demand level  $V_{CS(min)}$  to avoid audible noise, and to deliver minimum energy to the output of the power stage.

Based on the magnetic sampling information determined via the bias winding during these switching pulses, if the output voltage is greater than the output overvoltage threshold, the pulsing stops immediately, and the controller transitions into latched-fault mode. If, however, there is no overvoltage condition detected at the output, the pulse-set completes. If the sensed line voltage is above the line  $AC_{ON}$  start threshold, then the controller starts up normally, and begins to generate the PWM drive pulses that charge and regulate the output voltage. Alternatively, if the sensed bulk level is below the  $AC_{ON}$  threshold, then the controller enters low power mode for the reset period ( $t_{RESET(short)}$ ). It then depletes the VDD rail to the  $V_{DD(reset)}$  level. At this point, the start-up sequence repeats, and the device generates another set of exploratory switching pulses. This sequence repeats indefinitely until the AC input is increased to a sufficient level that the bulk voltage exceeds the  $AC_{ON}$  level.

Figure 17. AC Input UVLO Detection and Start Up

Once started, the controller regularly monitors the bulk capacitor voltage. Because the ripple on the bulk capacitor depends on the load level, the device determines the maximum bulk level every 11 ms (approprite for minimum AC frequency of 47 Hz), so the AC peak can be determined. The controller provides input undervoltage protection based on the sensed AC peak level. Once the peak drops below the  $AC_{OFF}$  level for the delay period ( $t_{UV(delay)}$ ), the PWM switching halts, and the controller enters low-power mode for the reset period ( $t_{RESET(short)}$ ). The device then discharges the bias voltage to the  $V_{DD(reset)}$  level, followed by a restart sequence. The controller cycles through the  $AC_{ON}$ , monitoring (detailed above) indefinitely until the AC input again rises above the  $AC_{ON}$  level.

#### 8.3.3 Active X-Capacitor Discharge (UCC28630 and UCC28633 only)

Safety standards such as EN60950 require that any X-capacitors in EMC filters on the AC side of the bridge rectifier quickly discharge to a safe level when AC is disconnected. This discharge requirement ensures that any high-voltage level present at the pins of the AC plug does not present an electric shock hazard. The standards require that the voltage across the X-capacitor decay with a maximum time constant of 1 second. Typically, this requirement is achieved by including a resistive discharge element in parallel with the X-capacitor. However, this resistance causes a continuous power dissipation that impacts the standby power performance. The power dissipation in the discharge resistors depends on the X-capacitor value. Assuming that the discharge resistor meets the 1-second time-constant requirement, (in other words, the R-C product is 1 second) the dissipation is described in Equation 2.

$$P_{X} = V_{AC}^{2} \times C_{X} \tag{2}$$

Thus at 230 V<sub>AC</sub>, the discharge resistor causes 5.3-mW dissipation for every 100 nF of X-capacitance – for a typical 470-nF X-capacitor value, that causes 25 mW to be lost in the discharge resistors.

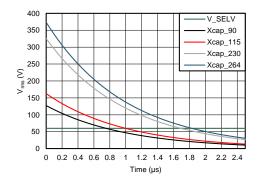

The safety standard does not mandate that the X-capacitor is fully discharged to zero within one second. It simply requires the discharge rate to exhibit a 1-s time constant. Figure 18 shows the discharge characteristic (for a 1-s discharge time constant) versus time, for disconnection at the peak of 90  $V_{AC}$ , 115  $V_{AC}$ , 230  $V_{AC}$  and 264  $V_{AC}$ . For AC inputs above 115  $V_{AC}$ , with 1-s discharge time constant, the voltage does not drop below the Safety-Extra-Low-Voltage (SELV) 60-V level until 1 s or longer. In fact, at 264  $V_{AC}$ , 1.83 seconds elapse before reaching 60 V.

Figure 18. X-Capacitor Discharge with 1-s Time Constant, for Various Voltages

#### 8.3.3.1 Improved Performance with UCC28630 and UCC28633

In order to reduce standby power and eliminate the standing loss associated with the conventional discharge resistors, the UCC28630 and the UCC28633 devices incorporate active X-capacitor discharge circuitry. This circuit periodically monitors the voltage across the X-capacitor to detect any possible DC-condition (which would indicate that AC mains disconnection has occurred), and then discharges the voltage across the X-capacitor using the internal HV current source. The X-capacitor discharge function discharges the X-capacitor to the SELV 60-V level in 1 s (as long as the design considerations discussed in this section are followed).

The device internally monitors the current into the HV pin to determine if the voltage across the X-capacitor in the EMI filter has a sufficient AC ripple component. If insufficient AC content is detected, then a DC condition is internally flagged. This causes the controller to enter low-power mode for the reset period (t<sub>RESET(short)</sub>), followed by bias voltage discharge to the reset level (V<sub>DD(reset)</sub>), and then the start-up HV current source turns on again to effectively discharge the X-capacitor by transferring charge to the VDD reservoir capacitor.

Because the device monitors the HV pin to detect a DC condition on the X-capacitor, the system cannot operate with DC input to the HV pin. Instead, the HV pin must be connected to an AC source only. The device interprets any DC input on the HV pin as DC across the X-capacitor, indicating an AC-disconnect event. This causes a repeating cycle of start-up and shutdown. The device requires an external 200-k $\Omega$  of resistance on the HV pin, to limit the current to a level below the saturation point of the internal HV current source. This limit produces a HV input current that is approximately proportional to AC line, so that the AC content can be sensed.

The size of the X-capacitor that can be discharged depends on the VDD energy storage capacitor. Assuming the worst case, a maximum X-capacitor disconnect voltage could be at the peak of 264  $V_{RMS}$ , and assuming that it should be discharged down to 60-V SELV level, the minimum allowed VDD capacitor can be sized based on the worst case  $V_{DD(reset)}$  and  $V_{DD(start)}$  levels as described in Equation 3.

worst case

$$V_{DD(reset)}$$

and  $V_{DD(start)}$  levels as described in Equation 3.

$$C_{VDD} \ge C_X \times \left(\frac{V_{AC(pk)} - V_{SELV}}{V_{DD(start\_min)} - V_{DD(reset\_max)}}\right) = C_X \times \left(\frac{373 - 60}{13.0 - 6.5}\right) = C_X \times (48.15)$$

For example, for a 330-nF X-capacitor value, the required VDD capacitor is 15.9  $\mu$ F, so a 22- $\mu$ F capacitor suffices.

$$C_{VDD} \ge 330 \text{ nF} \times (48.15) = 15.9 \,\mu\text{F}$$

(4)

In order to reduce the power consumption from the high voltage AC line, the device pulses current into the HV pin at a low frequency with very low duty-cycle. The HV current source on-time  $(t_{ON(HV)})$ , repeats at intervals of  $t_{SMP(HV)}$ . Moreover, the pulsing occurs in bursts, with a time delay between bursts. The sampling occurs in bursts of 21, at intervals of  $t_{SMP(HV)}$ , with a wait time of  $t_{WAIT(HV)}$  between bursts. This reduces the effective average duty-cycle to a very low value (approximately 0.2%), and minimizes the overhead of X-capacitor sampling current and device bias consumption overhead to approximately 2 mW of extra standby consumption at high-line 230  $V_{AC}$ .

The device enables the X-capacitor monitor in latched fault mode, and in light-load regions where the power level is below  $P_{LL(\%)}$ , as a percentage of the nominal rated level. Above the  $P_{LL(\%)}$  level, the X-capacitor monitor is disabled. At this load level the bulk capacitor discharges at a rate that is sufficient to also discharge the X-capacitor, which appears in parallel with the bulk capacitor once the bulk voltage drops far enough to forward bias the bridge rectifier diodes. In this case ensure that the bulk capacitance value is not too large for the power level desired, which in-turn ensures that the bulk capacitor discharge rate is fast enough to discharge the X-capacitor to meet the 1-s discharge target. This can be calculated in Equation 5.

$$C_{BULK} \le \frac{2\left(\frac{P_{NOM} \times P_{LL\%}}{\eta}\right) \times t_{XCAP(dis)}}{\left(V_{AC(pk)}^2 - V_{SELV}^2\right)}$$

(5)

Assuming a worst case AC disconnect at the peak at 264  $V_{RMS}$  (373  $V_{PK}$ ), and a requirement to discharge to SELV level of 60 V in  $t_{XCAP(dis)}$  of 1 s, for a  $P_{NOM}$  of 65 W at 87% efficiency, this is calculated in Equation 6.

$$C_{\text{BULK}} \le \frac{2 \times \left[ \frac{(65 \times 0.125)}{0.87} \right] \times 1}{(373^2 - 60^2)} = 138 \,\mu\text{F}$$

(6)

Once the bulk capacitance value is chosen, also ensure that when the bulk capacitor has been discharged down to the line UV  $AC_{OFF}$  threshold, that it continues to discharge to an acceptable level during the line UV persistence delay time  $(t_{UV(delay)})$  as shown in Equation 7.

$$C_{\text{BULK}} \le \frac{2 \times \left(\frac{P_{\text{NOM}} \times P_{\text{LL}\%}}{\eta}\right) \times t_{\text{UV(delay)}}}{2 \times AC_{\text{OFF}}^2 - V_{\text{SELV}}^2}$$

(7)

Again, taking the example above:

$$C_{\text{BULK}} \le \frac{2 \times \left(\frac{(65 \times 0.125)}{0.87}\right) \times 0.04}{(2 \times 65^2 - 60^2)} = 154 \,\mu\text{F}$$

(8)

Once the first constraint is satisfied, the second one is also automatically met.

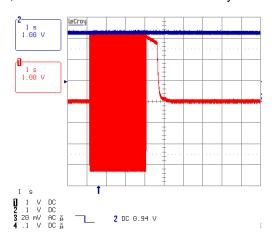

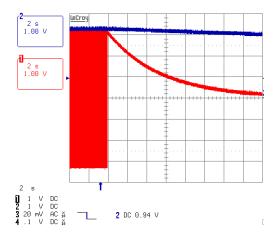

Figure 19. X-Capacitor Discharge Activation, at 230  $V_{AC}$ , No Load (red = X-capacitor, blue = bulk-capacitor, both 100 V/div)

Figure 20. X-Capacitor Decay Rate Without Active Discharge (time constant dominated by 20-M $\Omega$  probe impedance) (red = X-capacitor, blue = bulk-capacitor, both 100 V/div)

#### 8.3.4 Magnetic Input and Output Voltage Sensing

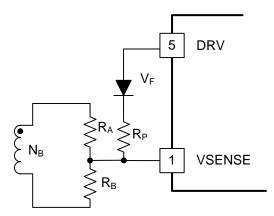

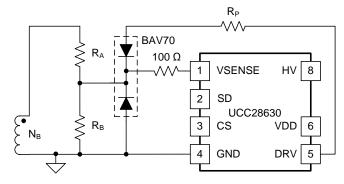

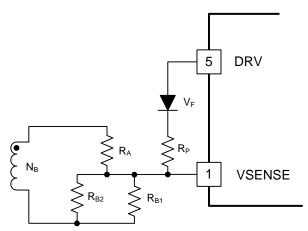

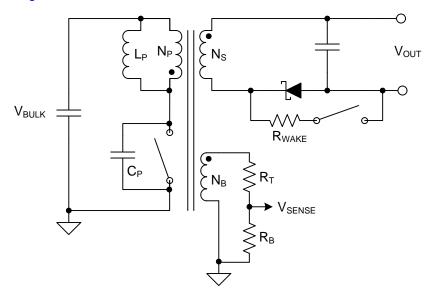

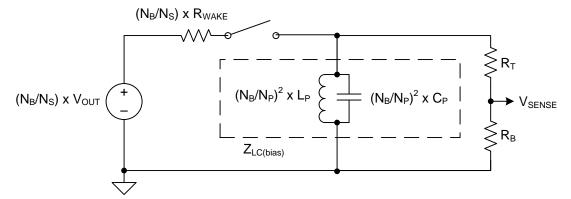

A sense winding on the transformer is used to measure the input voltage and output voltage of the power stage. This winding is typically the converter bias winding. The sense winding should be interfaced to the VSENSE pin as shown in Figure 21. This interface requires that the voltage across the winding be scaled with a resistor divider  $R_A / R_B$ , and then offset with a switched, pull-up resistor  $R_P$  (in series with a diode) connected to the gate drive pin DRV.

Figure 21. VSENSE Pin Interface Arrangement

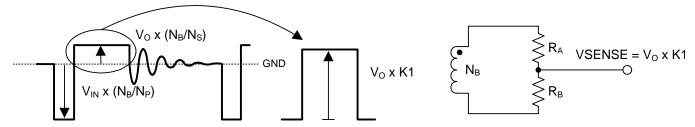

During the off-time portion of the switching cycle (also referred to as the flyback interval), the resistor divider ( $R_B / (R_A + R_B)$ ) scales the positive voltage swing at the VSENSE pin for output voltage regulation, as shown in Figure 22. During this interval, since the DRV output is low, the diode in series with  $R_P$  is reverse-biased, and so  $R_P$  is out-of-circuit.

Figure 22. V<sub>OUT</sub> Sense Using the Positive Swing on the Sense Winding

During the on-time portion of the switching cycle, when the DRV pin goes high (should swing very close to the value at the VDD pin), the switched pull-up  $R_P$  allows the negative swing on the winding to be level-shifted positive, and thus also be sensed at the VSENSE pin, as shown in Figure 23. In this way the bias winding may be used to sense both line input voltage and output voltage.

#### NOTE

The input voltage sensed by the transformer bias winding is actually the voltage across the bulk capacitor, not the AC input voltage, because the bulk capacitor voltage appears across the primary winding when the flyback switch turns on

Uses of the sensed bulk and output voltages:

- Input AC mains UVLO

- Input brownout

- · Line-dependent peak-current adjustment

- Accurate output-current regulation

- Output-voltage regulation

- Output over-voltage protection (OVP)

Figure 23. Line Input Sense by Offsetting the Negative Swing on the Sense Winding

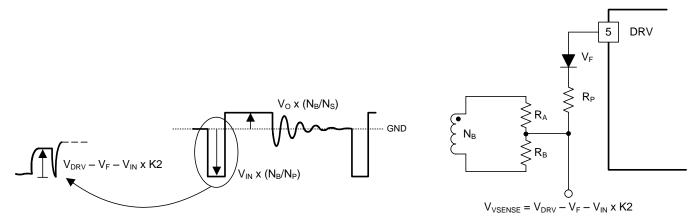

In order to protect the VSENSE pin from excessive negative current in the event of a manufacturing fault (such as an open circuit on R<sub>P</sub>), use a series limiting resistor and clamping diode on the VSENSE pin. Combine the clamping diode and DRV pull-up diode into a single-package common-cathode diode to reduce the component count of the system. This is illustrated in Figure 24.

Figure 24. VSENSE Pin Protection and Interface to Bias Winding

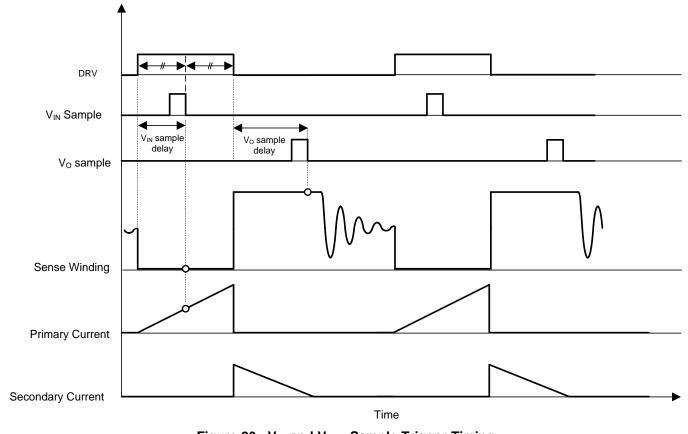

The device continually adjusts the input voltage sample delay, measuring the sample half-way through the ontime interval, to ensure the cleanest signal. The device uses same mid-point sample trigger when measuring the main MOSFET switch current (I<sub>SW</sub>). Sampling MOSFET switch current in the middle of the on-time automatically measures the average current during the on-time, I<sub>SW(on\_avg)</sub>, which is required for the current limit and overload timer block.

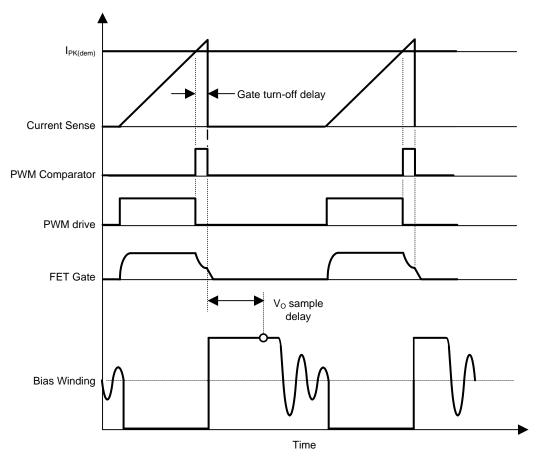

The output voltage sample point is always time relative to the turn-off instant. Internally, the device uses the CS pin to determine the cycle end, rather than the PWM falling edge on the DRV pin. The device bases this determination on the instant that the MOSFET switch current drops below the demanded peak current level ( $I_{PEAK}$ ) at the peak current mode comparator. Some delay always occurs from the falling edge on DRV to the point when the external power MOSFET turns off. This internal timing method ensures a more accurate measure of  $I_{SW(on\_avg)}$ , and also ensures that the output voltage sample point is not measured too early, before the leakage ringing has subsided. The effect of the gate turn-off delay and the adjustment of the output voltage sample point is illustrated in Figure 25.

Figure 25. V<sub>OUT</sub> Sample Adjust for External Gate Delay

The sampling of the input voltage and output voltage signals on the bias winding must be synchronized to the ontime and off-time flyback intervals respectively, because the signals occur during only those intervals in the switching cycle. Typical waveforms and timing are illustrated in Figure 26.

More conventional *knee-point* detection schemes, where the sample is measured at the end of the flyback interval when the secondary-side current has decayed to zero, inherently always operate in discontinuous conduction mode (DCM). However, the fixed sample-point scheme used on the UCC2863x has the advantages of being able to operate in regions of fixed frequency, and being able to operate in continuous conduction mode (CCM). Fixed sample-point schemes conventionally suffer poorer regulation than *knee-point* schemes, because there is always current flowing at the sample instant. This current produces a sensing error as a result of the voltage drop produced across the secondary-side resistance and leakage inductance. This parasitic voltage drop varies with output voltage, line and load, thus influencing the regulation. The UCC2863x devices uses a novel internal compensation scheme to adjust for this parasitic voltage drop, and can deliver excellent static line and load regulation, even when operating heavily in CCM.

Figure 26. V<sub>IN</sub> and V<sub>OUT</sub> Sample Trigger Timing

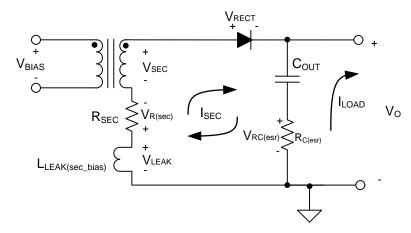

#### 8.3.5 Fixed-Point Magnetic Sense Sampling Error Sources

To support operation in CCM, and allow operation at fixed frequency over a large percentage of the load range, the UCC2863x uses fixed-point sampling rather than *knee-point* detection. When conventionally used, fixed-point sampling typically suffers from poorer regulation performance. This poor performance results from the voltage drops across the secondary-side parasitic resistance  $R_{\text{SEC}}$ , and the secondary-side leakage inductance from secondary-side to bias  $L_{\text{LK(sec\_bias)}}$ , as a consequence of the fact that current remains flowing on the secondary-side when the device measures the output voltage. As shown in Figure 27, the secondary-side pin voltage that gets reflected to the bias winding is detailed in Equation 9.

$$V_{SEC} = V_{OUT} + V_{RECT} + V_{R(sec)} - V_{L(leak)} + V_{RC(esr)}$$

(9)

Equation 9 can be expanded and rearranged into Equation 10.

$$V_{SEC} = V_{OUT} \times \left(1 - \frac{L_{LK(sec\ bias\ )}}{L_{SEC}}\right) + V_{RECT} + I_{SEC} \times \left(R_{SEC} + R_{C(esr)}\right) - \left(I_{LOAD} \times R_{C(esr)}\right)$$

(10)

Figure 27. Secondary-Side Pin Voltage Contributors with Secondary-Side Current Flow

Many elements contribute errors to the sensed secondary-side pin voltage, when measured across the bias winding:

- V<sub>L(leak)</sub>: Negative voltage drop across the sec-bias leakage inductance L<sub>LK(sec\_bias)</sub>; assuming constant regulated output voltage, this voltage drop is fixed constant offset, because V<sub>OUT</sub>/L<sub>SEC</sub> is constant as long as the output is in regulation.

- V<sub>RECT</sub>: Positive voltage drop across the output rectifier (assuming use of a conventional diode). This voltage

drop varies with load current and temperature. However, a constant nominal voltage drop can usually be

used, because the increasing forward voltage drop with increasing load current is largely cancelled by the

decrease in forward drop as a result of the temperature rise that results.

- **V**<sub>R(sec)</sub>: This is the drop across the secondary-side winding resistance. This value depends on loading, and varies in proportion to the primary peak current demand that is set by the modulator.

- V<sub>RC(esr)</sub>: This is the drop across the output capacitor equivalent series resistance (esr). This value depends on the difference between the secondary-side winding current and the DC load current being drawn.

Typically, the peak secondary-side winding current  $I_{SEC}$  is many times larger than the load current, and the secondary-side winding resistance is typically larger than the output capacitor esr. Thus, the last term in Equation 10 involving  $I_{LOAD}$  can typically be neglected.

The leakage inductance and secondary-side rectifier terms represent quasi-constant offset terms, so do not affect regulation to a significant extent. Thus, the quasi-constant offset terms can be accounted for in the calculation of the required scaling resistors to produce the desired setpoint voltage.

The remaining term that dominates the regulation error in Equation 10 is the drop across the secondary-side winding resistance and capacitor esr at the sample instant,  $\{I_{SEC} \ x(R_{SEC} + R_{C(esr)})\}$ . The controller internally adjusts the control loop reference in proportion to the primary peak current demand in order to null the  $I_{SEC}$  related error term in the sampled bias winding voltage. Since the peak secondary-side current  $I_{SEC(pk)}$  is the primary peak current  $I_{PRI(pk)}$  scaled by the transformer turns ratio, the internal control loop reference effectively varies in approximate proportion to  $I_{SEC}$ , resulting in dramatically improved regulation performance.

This improved regulation performance allows the use of primary-side regulation in a wider range of applications, and at unprecedented power levels, operating in both CCM and DCM.

#### 8.3.6 Magnetic Sense Resistor Network Calculations

Because the device uses the VSENSE pin to measure both  $V_{OUT}$  and  $V_{IN}$  of the power stage, it is important to calculate the resistor values correctly. The step-by-step design process is outlined in this section.

#### 8.3.6.1 Step 1

Depending on the power level, choice of transformer size, and required trade-offs between primary MOSFET and secondary-side rectifier ratings, the transformer turns  $N_P$ ,  $N_S$  and  $N_B$  will be chosen first. The controller can support a wide range of turns ratios.

Figure 28. Practical Magnetic Sense Setup with Extra Resistor R<sub>B2</sub> for Setpoint Fine Adjust

#### 8.3.6.2 Step 2

Once N<sub>P</sub>, and N<sub>B</sub> are known, the required value of R<sub>A</sub> in Figure 28 is calculated using Equation 11.

$$R_{A} = R_{P} \times \left(\frac{N_{B}}{N_{P}}\right) \times K_{LINE} \tag{11}$$

In this equation, the internal controller gain  $K_{LINE}$  is 49.25 (see Table 7 for key internal controller parameters), and the internal gains are designed for a fixed value for  $R_P$ , (i.e.  $R_P$  MUST be 3.9 k $\Omega$ ).

#### 8.3.6.3 Step 3

Once  $N_S$ , target  $V_{OUT}$ , output rectifier drop  $V_{RECT}$ , and the secondary-side-to-bias leakage inductance  $L_{LK(sec\_bias)}$  are known, the required value for  $R_B$  can be calculated. Referring to Equation 10,  $L_{LK(sec\_bias)}$  can be approximated as a percentage of the secondary-side-referred magnetizing inductance  $L_{SEC}$ . (See Magnetic Sense Resistor Network Selection for details).

$$R_{B} = \frac{R_{A}}{\left(\frac{\left(V_{OUT} \times \left(1 - \%L_{LK(sec\_bias)}\right) + V_{RECT}\right) \times \left(\frac{N_{B}}{N_{S}}\right)}{V_{OUT(ref)}} - 1\right)}$$

(12)

In this case,  $R_B$  may need to be empirically adjusted to achieve the required exact output set-point, especially if  $V_{RECT}$  varies or is not known precisely. For this reason, it is recommended that  $R_B$  should be implemented on the system PCB as two parallel resistors  $R_{B1}$  and  $R_{B2}$  as shown in Figure 28, to allow easier fine-tuning of set-point. For set-point tuning, only  $R_B$  should be adjusted.  $R_A$  should never be adjusted, because to do so would affect the line sense gain and introduce errors into the line voltage measurement.

## 8.3.6.4 Step 4

Verify that the equivalent Thevenin resistance  $R_{TH}$  of the  $R_A/R_B$  combination falls in the required range of 10 k $\Omega$  to 20 k $\Omega$ .

$$R_{TH} = \frac{R_A \times R_B}{R_A + R_B} \tag{13}$$

$$10 \text{ k}\Omega < R_{\text{TH}} < 20 \text{ k}\Omega \tag{14}$$

If the Thevenin resistance is outside of that range, then the original choice of turns ratio must be adjusted, and design steps repeated until a valid value for  $R_{TH}$  is determined. This is unlikely to occur in practice, unless an extreme turns ratio is chosen. If  $R_{TH}$  is outside this range, it triggers the VSENSE pin open or short pin-check at start-up.

#### 8.3.7 Magnetic Sensing: Power Stage Design Constraints

Because the controller employs fixed-point sampling for output voltage sensing, there are some transformer design constraints that must be observed. The minimum magnetizing volt-seconds during the on-time interval occurs at the minimum CS pin voltage,  $V_{CS(min)}$ , under light-load conditions. This minimum should be the case at all line voltages, because the controller compensates for line-dependent peak-current overshoot during turn-off delay. The choice of transformer turns ratio, transformer inductance ( $L_{PRI}$ ), and current sense resistance ( $R_{CS}$ ) must ensure that the corresponding reset volt-seconds during the flyback interval are sufficient that a valid output sample is available at the sample point,  $t_{OUT(smp)}$ . This constraint is summarized in Equation 15.

$$\frac{R_{CS}}{L_{PRI}} \leq \frac{V_{CS(min\,)}}{t_{OUT(smp\,)}} \times \frac{N_S}{N_P} \times \frac{1}{(V_{OUT} + V_{RECT})}$$

where

Additionally, the device requires a minimum on-time,  $t_{ON(min)}$ , to ensure enough time for the system input voltage  $(V_{IN})$  and switch current  $(I_{SW})$  to be measured. To meet the minimum on-time requirement at maximum line, and minimum load, the ratio of current sense resistance  $(R_{CS})$  to transformer inductance  $(L_{PRI})$  must meet the constraint shown in Equation 16.

$$\frac{R_{CS}}{L_{PRI}} \le \frac{1}{V_{IN(pk\_max)}} \times \frac{V_{CS(min)}}{t_{ON(min)}}$$

(16)

Equation 15 or Equation 16 sets the limit for the ratio of  $R_{CS}$  to  $L_{PRI}$ , but both need to be verified. See Typical Application for more details.

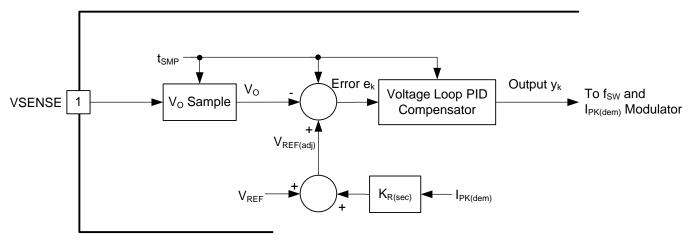

#### 8.3.8 Magnetic Sense Voltage Control Loop

Because the output voltage feedback is inherently a sampled signal obtained from the bias winding, the internal voltage control loop is most naturally implemented digitally. The internal control loop implements the equivalent of a PID loop in digital form. Because the output can be sampled only at certain intervals in each switching cycle, the sample rate is naturally tied to the switching frequency, and the sample rate increases with increasing frequency. However, the device clamps the sample rate at a normalized maximum rate,  $f_{\text{SMP(max)}}$ . But because the device must always synchronize to the next available switching cycle to obtain a new sample of the output voltage, the effective sample rate varies somewhat around this value.

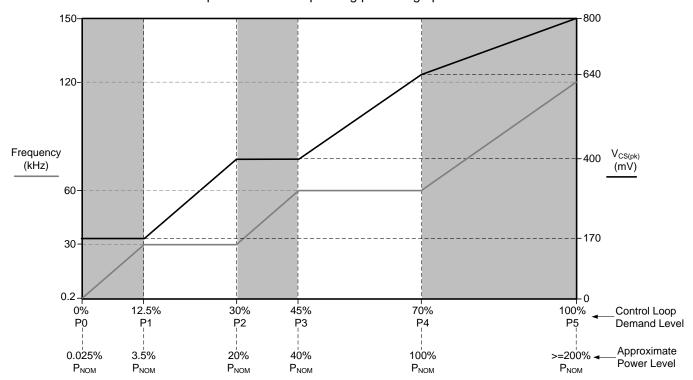

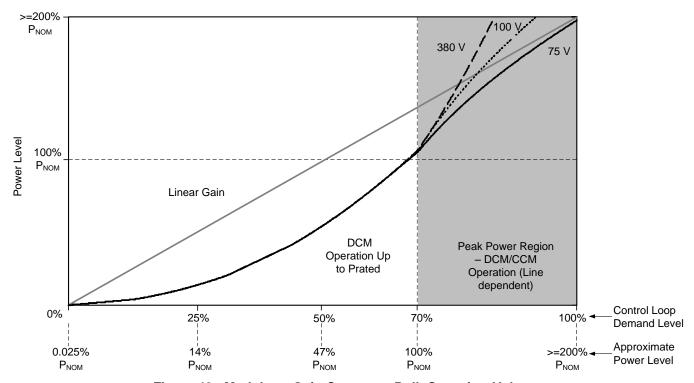

The digital control loop compensator block diagram is shown in Figure 29. A new sample of output voltage is supplied to the compensator at the normalized maximum clock rate  $(f_{SMP(max)})$ , or  $f_{SW}$ , whichever is lower. An updated output voltage demand signal,  $y_k$ , is produced at the same clock rate. This voltage loop demand represents the required operating point on the modulator curves to keep the output voltage in regulation. The modulator sets the appropriate switching frequency and peak current demand depending on the load power.

Figure 29. Digital Voltage Control Loop Simplified Block Diagram

The control loop PID gain factors are internally fixed values, optimized for flyback power stages in the range between 20 W and 130 W. The loop is designed to work with magnetizing inductance values in the range between 200  $\mu$ H and 1500  $\mu$ H. Assuming that the output capacitance value is chosen based on required ripple current rating, then loop stability is not a problem. Adding extra output capacitance does not degrade the loop performance and the resulting extra output hold-up improves transient response.

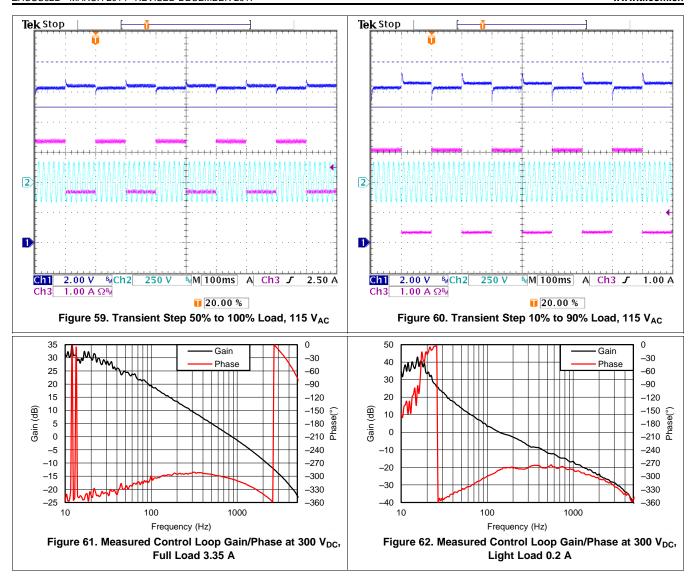

The Typical Application section includes gain-phase measurements taken using the 65-W UCC28630EVM-572 evaluation module.

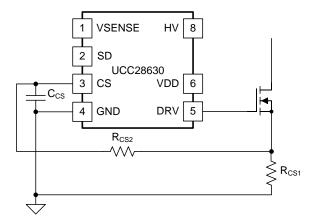

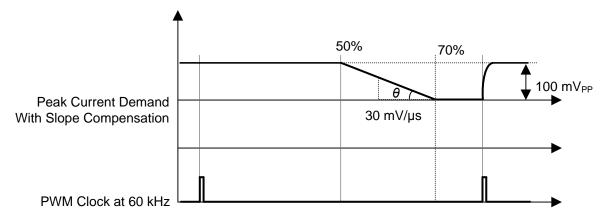

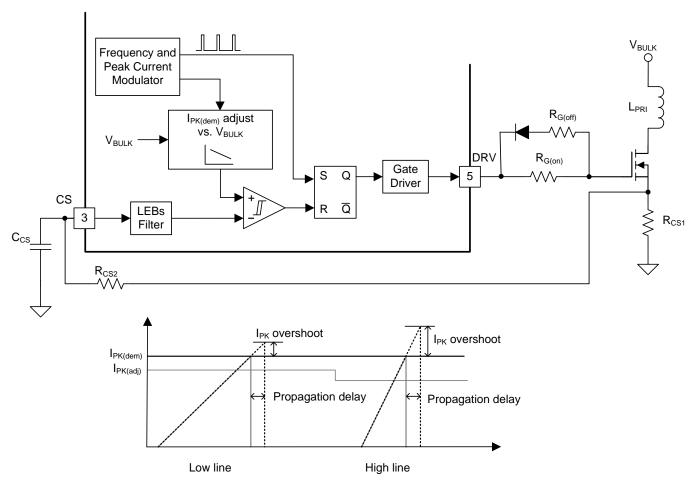

#### 8.3.9 Peak Current Mode Control

The controller operates in peak current mode. The primary-side switch (MOSFET) current is sensed by a shunt resistor (R<sub>CS1</sub>) connected in series with the source of the FET as shown in Figure 30. The voltage that is developed across the sense resistor is connected to the CS pin of the controller. The device uses the current sense signal at the CS pin to terminate the PWM pulse according to the peak current demand of the modulator. The device automatically applies slope compensation as soon as the duty cycle of the DRV pin pulse exceeds 50%. This compensation provides stable operation up to maximum DRV duty cycle. The device applies this slope compensation as a downslope on the demand signal at the PWM comparator, so is not measureable at the CS pin. The device synchronizes the slope compensation signal to the PWM and is active only between 50% and 70% duty cycle, as shown in Figure 31.

Normal operating range for the CS pin is between 0 mV and 800 mV. The R<sub>CS1</sub> resistor should be scaled such that the peak current at maximum peak load and minimum bulk capacitor voltage produces a signal of approximately 800 mV peak at the CS pin. This resistor value is calculated in conjunction with the calculation of the required primary magnetizing inductance, as outlined in Notebook Adapter, 19.5 V, 65 W, section.

Figure 30. Primary-Side Current Sensing

A nominal 100 ns of filtering that is internal to the CS pin helps filter the leading turn-on spike of current. Depending on PCB layout, an RC filter ( $R_{CS2}$  and  $C_{CS}$ ) may be required on the CS pin as shown in Figure 30 to filter noise and spikes. The capacitor  $C_{CS}$  should be positioned as close as possible to pins 3 and 4 and tracked directly to the pins. Series resistor  $R_{CS2}$  should also be located close to pin 3 to minimize noise pick-up.  $R_{CS2}$  value should not exceed 20 k $\Omega$ , because a larger value could be detected as a possible open circuit on the CS pin during the start-up pin-fault checks. The R-C filter time constant should not be excessive (timing between 100 ns and 200 ns is typical). Otherwise the filter reduces the measured peak current, and allows greater actual peak current to flow versus the modulator demand level. Such effects force the regulation loop to reduce the switching frequency to compensate, and at highest line, no load, this can lead to regulation difficulties if the control loop attempts to drop the frequency so far that it reaches the  $f_{MIN}$  limit.

Figure 31. Peak Current Demand with Slope Compensating Downslope

#### 8.3.10 I<sub>PEAK</sub> Adjust vs. Line

The controller applies a line-dependent reduction in the peak-current demand to correct for the current overshoot due to the PWM and gate drive propagation delay, with the aim of delivering a constant peak current versus line at a given power level. This maintains approximately constant switching frequency versus line for a given power level (until the operation enters into CCM), improves regulation, reduces audio noise, and allows lower standby power at high line. If not corrected, the current overshoot could become significant at high line, where the inductor current di/dt is higher. This overshoot would cause a pronounced increase in transferred power per switching cycle at high line, because power is proportional to  $I_{PK}^2$ . The effect of the delay on the peak-current overshoot is illustrated in Figure 32.

Figure 32. Peak-Current Demand Adjustment vs V<sub>BULK</sub> to Correct Prop Delay Overshoot

For different power stage designs, the combination of primary magnetizing inductance  $L_{PRI}$ , current sense resistance  $R_{CS}$  and external MOSFET gate turn-off delay  $t_{OFF(ext)}$ , must be verified against Equation 17, to ensure that the internal peak-current compensation gain range is satisfied. The  $K_{LINE(adj)}$  factor should be within the range indicated. If the external turn-off delay is too long, then the internal  $I_{PEAK}$  adjustment factor is too low, and the adjustment at high line is not able to achieve the required level of over-shoot compensation. As noted previously, this could result in regulation difficulties at no-load, and may cause poor line and load regulation, or require an increase in output pre-load power.

$$K_{LINE(adj\,)} = \left(\frac{R_{CS}}{L_{PRI}} \times \left(t_{PROP(gate\,)} + t_{OFF(ext\,)}\right)\right) > 120~\mu \text{ and} < 350\mu$$

where

• where t<sub>PROP(gate)</sub> is the internal controller gate-drive turn-off propagation delay, given in Table 7. (17)

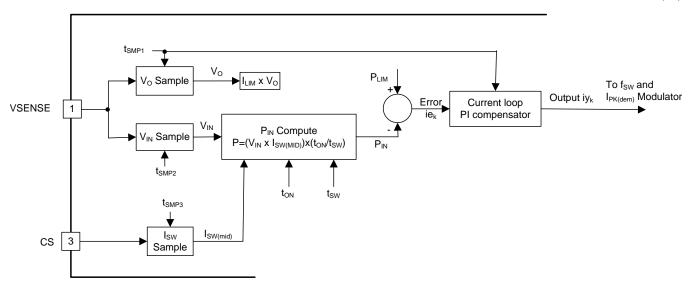

#### 8.3.11 Primary-Side Constant-Current Limit (CC Mode)

In addition to the peak-current mode PWM function, the device also uses sensed current at the CS pin to estimate the secondary-side load current. The device samples the CS pin voltage and measures it in the middle of the on-time, which is effectively the average switch current during the on time,  $I_{SW(avg\_on)}$ . This measurement scheme is the case during both DCM and CCM operational modes. The average switch current during the on time is scaled by the PWM duty cycle to give the  $I_{IN(avg)}$  of the power stage. The power stage input power,  $P_{IN}$ , can then be estimated as the product of  $(V_{IN} \times I_{IN(avg)})$ . The CC mode operation regulates  $P_{IN}$  to track  $(I_{OUT(lim)} \times V_{OUT})$ , if  $P_{IN}$  increases to reach  $P_{IN(lim)}$ , thereby achieving a regulated constant current as shown in Equation 18.

$$P_{IN} = V_{IN} \times I_{IN(avg)} = \frac{V_{OUT} \times I_{OUT(lim)}}{\eta} = P_{IN(lim)}$$

(18)

$$I_{OUT} = \frac{V_{IN} \times I_{IN(avg)} \times \eta}{V_{OUT}} = \frac{P_{IN(lim)} \times \eta}{V_{OUT}} = I_{OUT(lim)}$$

(19)

Figure 33. Digital Current Control Loop Simplified Block Diagram

Assuming that the power stage efficiency does not change significantly with operating point, by regulating the input power in inverse proportion to output voltage, this regulates output current. This achieves a *brick-wall* CC characteristic, where the output current is regulated as the input voltage changes and as the output voltage rolls off, regardless of power stage operating mode (CCM or DCM). The CC mode protection eliminates the characteristic load current *tail-out* that is typically seen with peak-current mode control as output voltage collapses and operation goes deeper into CCM mode.

#### NOTE

As the output voltage decreases in CC mode, the VDD level also decreases. If the overload is severe, the drop in output voltage causes VDD to drop below the  $V_{DD(stop)}$  UV level. This drop causes a shutdown for  $t_{RESET(long)}$ , as given in Table 7, followed by a restart attempt.

The constant-current mode output current limit level ( $I_{OUT(lim)}$ ) is a function of both the  $R_{CS1}$  resistor and the transformer turns ratio. The device uses an internal reference and gain for the CC loop,  $K_{CC1}$  and  $K_{CC2}$ , that set the CC  $I_{OUT(lim)}$  point as a function of the chosen turns ratio, output voltage and current sense resistance as shown in Equation 20.

$$I_{OUT(lim)} = \frac{1}{R_{CS1}} \times \frac{N_P}{N_S} \times \frac{K_{CC1}}{K_{CC2} + V_{OUT} \times \frac{N_P}{N_S}}$$

(20)

For the UCC28631, UCC28632 and the UCC28633 devices, the  $I_{OUT(lim)}$  can be adjusted to be a percentage of the maximum value calculated by equation Equation 20. see CC-Mode  $I_{OUT(lim)}$  Adjustment for more details.

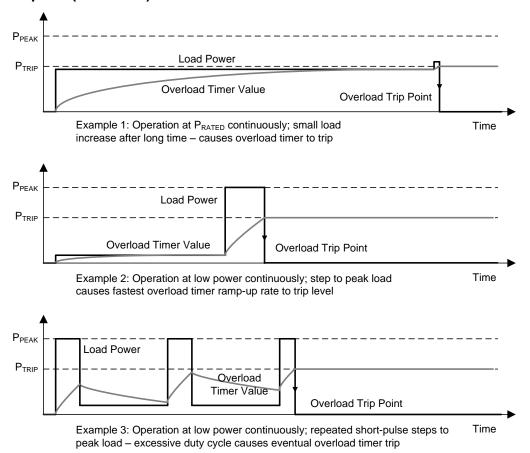

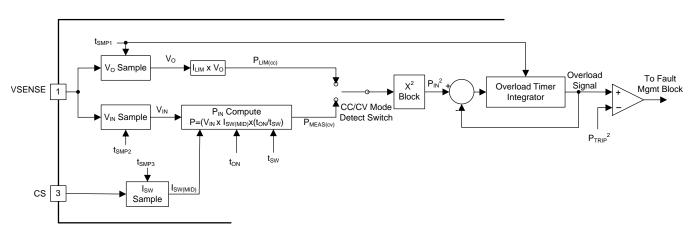

### 8.3.12 Primary-Side Overload Timer (UCC28630 only)

The internal overload timer in the UCC28630 uses the same output load current measurement that is used by the CC loop. This measurement tracks the power stage thermal stress, and protects the power stage against output overload. If the output is overloaded for too long such that the power stage would be over-stressed, then the PWM shuts down, and enters low-power mode for a time period of  $t_{RESET(long)}$ ; thereafter the device discharges VDD to the  $V_{DD(reset)}$  level and initiates a hiccup mode restart.

The overload timer operates by taking an estimate of output current, squaring it (assuming the power stage losses are dominated by resistive  $I^2$  losses) to produce (K x  $I^2_{OUT}$ ), where K is a scaling gain factor. The overload timer is constantly running at every load level, and accumulates at a rate dependent on the difference between (K x  $I^2_{OUT}$ ) and the previous level of the timer. If (K x  $I^2_{OUT}$ ) is greater than the previous timer level, the timer level continues to increase; if (K x  $I^2_{OUT}$ ) is less than the previous timer level, then the timer level decreases. At any steady load, the overload timer level eventually settles at a level proportional to  $I^2_{OUT}$ . Because the overload timer level adjusts at a rate dependent on the difference between (K  $xI^2_{OUT}$ ) and the previous level, the timer initially reacts faster to larger differences, but over time settles exponentially at a level proportional to (K x  $I^2_{OUT}$ ).

As shown in Figure 34, in both the first and second examples, the initial steady load allows the timer to integrate and settle at a level proportional to the load. The margin to the over-load trip level depends on the historical loading, lower prior average loading results in greater future over-load capability, and vice versa. The rate at which the timer reacts to different load steps is set by the chosen time constant (or response rate) per Table 2.

The overload timer can cope with pulsed loads and loads with a complex waveform. Because the rate of increase and decrease also depends on the load change from the previous load, it also times out faster for bigger overloads, or allows a smaller overload to run for much longer. The overload timer operates in both normal CV mode and overload CC mode, or a dynamic mix of both modes.

Figure 34. Overload Timer Example Waveforms Under Various Load Scenarios

Figure 35. Overload Timer Block Diagram

39

## 8.3.13 Overload Timer Adjustment (UCC28630 only)

The UCC28630 overload timer trip level and time constant are both selectable from a defined list of combinations. The user can select the overload timer trip level as a percentage of the rated continuous nominal power, P<sub>NOM</sub> (see Figure 41), and the timer response speed. The available choices are detailed in Table 2.

**Table 2. Overload Timer Adjustment**

| $R_{PROG}$ PROGRAMMING RESISTOR (k $\Omega$ ) (E96 series values) | TIMER CONTINUOUS OPERATION P <sub>TRIP</sub> /P <sub>NOM</sub> (%) | TIME CONSTANT AT 200% of P <sub>NOM</sub> OR IN CC MODE (ms) |

|-------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------|

| Open, or > 47                                                     | 160                                                                | 1000                                                         |

| 20.0                                                              | 160                                                                | 500                                                          |

| 12.7                                                              | 160                                                                | 150                                                          |

| 9.31                                                              | 135                                                                | 1000                                                         |

| 7.32                                                              | 135                                                                | 500                                                          |