## **Preconfigured DSP System** for Hearing Aids

### Description

The Paragon GA3224 hybrid is a programmable DSP system based on a two-channel compression circuit. It can be used as a platform for a wide range of hearing aid applications. Its extensive programmability and compact size make it ideal for sophisticated CIC applications. The reflowable thinSTAX<sup>®</sup> packaging enables easy use in BTE applications. This very versatile DSP hybrid is capable of multiple configurations and has a wide range of functions.

The Paragon GA3224 hybrid contains the GC5057 controller chip featuring Power On Reset (POR).

The Paragon GA3224 hybrid code programmed into the GC5057 controller chip is "8".

### Features

- Highly Configurable, Versatile DSP Platform

- High Quality, Two-channel AGC Signal Processing

- High Performance Data Converters Dual, Over–sampled A/Ds; Over–sampled D/A with Efficient Switched–mode Output Power Amp

- High-fidelity Audio Quality

- Drives Zero-bias 2-terminal Receivers

- Multiple Communication Rates up to 85.3 kb/s

- thinSTAX Packaging CIC Size

- Multi-memory

- Internal/External Volume Control

- Volume Control Taper determined by External VC

- Tri-state Memory Select Operation

- Audible Memory Change Indicator

- Also Available as E1 RoHS Compliant Hybrid

### thinSTAX Packaging

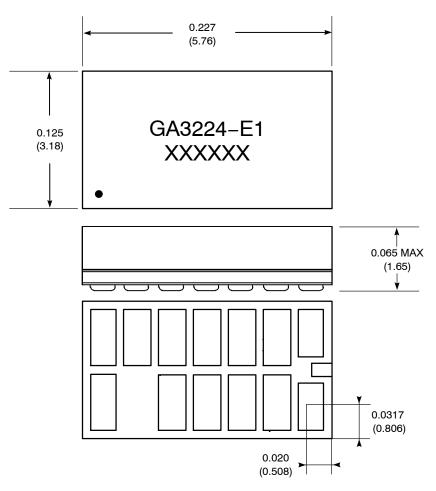

• Hybrid Typical Dimensions: 0.227 x 0.125 x 0.060 in (5.76 x 3.18 x 1.52 mm)

### **ON Semiconductor®**

http://onsemi.com

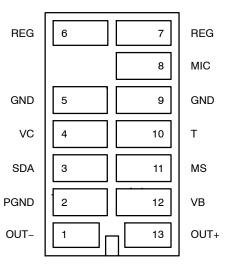

PAD CONNECTION

(Bottom View)

### MARKING DIAGRAM

### **ORDERING INFORMATION**

| Device      | Shipping <sup>†</sup>   |

|-------------|-------------------------|

| GA3224-E1   | 25 Units / Bubble Pack  |

| GA3224-E1-T | 500 Units / Tape & Reel |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

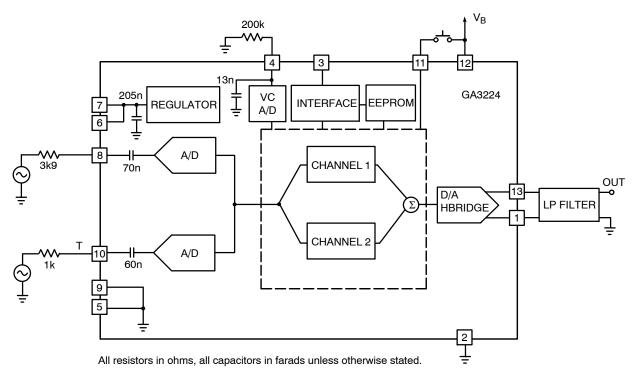

#### **BLOCK DIAGRAM** VC SDA MS VB 4 3 11 12 13n 205n GA3224 VC Ι INTERFACE EEPROM REGULATOR REG 7 A/D REG 6 MIC A/D 8 CHANNEL 1 70n OUT+ 13 D/A Σ HBRIDGE OUT-1 CHANNEL 2 T 10 A/D 60n GND 9 GND 5 2 PGND All resistors in ohms, all capacitors in farads unless otherwise stated.

### Figure 1. Paragon GA3224 Block Diagram

### Table 1. ABSOLUTE MAXIMUM RATINGS

| Parameter                          | Value      | Units |

|------------------------------------|------------|-------|

| Operating Temperature Range        | -10 to +40 | °C    |

| Storage Temperature Range          | -20 to +70 | °C    |

| Absolute Maximum Power Dissipation | 25         | mW    |

| Maximum Operating Supply Voltage   | 1.5        | VDC   |

| Absolute Maximum Supply Voltage    | 2          | VDC   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

WARNING: Electrostatic Sensitive Device - Do not open packages or handle except at a static-free workstation.

WARNING: Moisture Sensitive Device – Non–RoHS Compliant – Level 3 MSL; RoHS Compliant – Level 4 MSL. Do not open packages except under controlled conditions.

| Parameter                                       | Symbol              | Conditions                                                       | Min                  | Тур   | Max                  | Units  |

|-------------------------------------------------|---------------------|------------------------------------------------------------------|----------------------|-------|----------------------|--------|

| Hybrid Current                                  | I <sub>AMP</sub>    | See current consumption section                                  | -                    | 700   | -                    | μA     |

| Minimum Operating Supply Voltage                | V <sub>BOFF</sub>   | Ramp down                                                        | 0.94                 | 1.0   | 1.05                 | V      |

| Supply Voltage Turn On Threshold                | V <sub>BON</sub>    | Ramp up                                                          | 1.06                 | 1.10  | 1.16                 | V      |

| Supply Voltage Hysteresis                       | -                   |                                                                  |                      | 100   | 110                  | mV     |

| Supply Voltage during<br>Communication          | V <sub>BC</sub>     | During Communication                                             | 1.19                 | 1.35  | 1.5                  | V      |

| Hybrid Current during Communication             | Ι <sub>Ρ</sub>      | Programming (<5 ms)                                              |                      | 3.7   | -                    | mA     |

| EEPROM Burn Cycles                              | -                   | (Note 2)                                                         | 100 k                | _     | -                    | cycles |

| Low Frequency System Bandwidth                  | -                   | -                                                                | 100                  | 140   | 225                  | Hz     |

| High Frequency System Bandwidth                 | -                   | -                                                                | 15.2                 | 16    | 16.8                 | kHz    |

| Total Maximum System Gain                       | A <sub>V</sub>      | V <sub>IN</sub> = -95 dBV at 3 kHz;<br>squelch disabled (Note 1) | 81                   | 83    | 85                   | dB     |

| Converter Gain                                  | A <sub>CONV</sub>   | A/D + D/A gain                                                   | 27                   | 29    | 31                   | dB     |

| Total Harmonic Distortion                       | THD                 | $V_{IN} = -40 \text{ dBV}$                                       | -                    | 0.05  | 1                    | %      |

| THD at Maximum Input                            | THD <sub>M</sub>    | V <sub>IN</sub> = –15 dBV, HRX – ON                              | -                    | 1.5   | 3                    | %      |

| Clock Frequency                                 | $f_{clk}$           | -                                                                | 1.945                | 2.048 | 2.151                | MHz    |

| REGULATOR                                       |                     |                                                                  |                      |       |                      |        |

| Regulator Voltage                               | V <sub>REG</sub>    | -                                                                | 0.90                 | 0.95  | 1.00                 | V      |

| Regulator Supply Rejection                      | PSRR <sub>REG</sub> | -                                                                | -                    | 50    | -                    | dB     |

| INPUT                                           |                     |                                                                  |                      |       |                      |        |

| Input Referred Noise                            | IRN                 | Bandwidth 100 Hz – 8 kHz                                         | -                    | -108  | -106                 | dBV    |

| Input Impedance                                 | Z <sub>IN</sub>     | -                                                                | 11.2                 | 16    | 22                   | kΩ     |

| Anti-alias Filter Rejection<br>(input referred) | -                   | $f = f_{Clk} - 8 \text{ kHz},$<br>$V_{IN} = -40 \text{ dBV}$     | -                    | 80    | -                    | dB     |

| Maximum Input Level                             | -                   | -                                                                | -                    | -15   | -                    | dBV    |

| Input Dynamic Range                             | -                   | HRX – ON,<br>Bandwidth 100 Hz – 8 kHz                            | -                    | 93    | -                    | dB     |

| Audio Sample Rate                               | -                   | -                                                                | 30.4                 | 32    | 33.6                 | kHz    |

| A/D Dynamic Range                               | -                   | Bandwidth 100 Hz - 8 kHz                                         | -                    | 86    | -                    | dB     |

| OUTPUT                                          |                     |                                                                  |                      |       |                      |        |

| Maximum RMS Output Voltage                      | -                   | 0 dBFS $f = 1 \text{ kHz}$                                       | -3                   | -1    | 1                    | dBV    |

| D/A Dynamic Range                               | _                   | Bandwidth 100 Hz – 8 kHz                                         | 80                   | _     | -                    | dB     |

| Output Impedance                                | Z <sub>OUT</sub>    | (Note 2)                                                         | -                    | _     | 20                   | Ω      |

| VOLUME CONTROL                                  |                     |                                                                  | -                    |       | -                    | -      |

| Volume Control Resistance                       | R <sub>VC</sub>     | -                                                                | 160                  | 200   | 240                  | kΩ     |

| Volume Control Range                            | ΔΑ                  | _                                                                | 47.5                 | 48    | 48.5                 | dB     |

| MS INPUT                                        |                     |                                                                  |                      |       | ·                    |        |

| Low State                                       | Lo                  | _                                                                | 0                    | -     | V <sub>REG</sub> /3  | V      |

| Open State                                      | Z                   | _                                                                | V <sub>REG</sub> /3  | -     | 2V <sub>REG</sub> /3 | V      |

| High State                                      | Hi                  | _                                                                | 2V <sub>REG</sub> /3 | _     | VB                   | V      |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

1. Total System Gain consists of: Wideband System Gain + High and Low Independent Channel Gains + Converter Gain. Total System Gain is calibrated during Cal/Config process.

2. Sample tested.

### Table 2. ELECTRICAL CHARACTERISTICS (Conditions: V<sub>B</sub> = 1.3 V; Temperature = 25°C)

| Parameter                                             | Symbol            | Conditions | Min   | Тур   | Max   | Units |

|-------------------------------------------------------|-------------------|------------|-------|-------|-------|-------|

| SDA INPUT                                             | • • • • •         |            | •     |       | •     |       |

| Logic 0 Voltage                                       | _                 | (Note 2)   | 0     | -     | 0.3   | V     |

| Logic 1 Voltage                                       | _                 | (Note 2)   | 1     | -     | 1.3   | V     |

| SDA OUTPUT                                            |                   |            |       | -     |       | -     |

| Standby Pull Up Current                               | _                 | -          | 1.4   | 2     | 2.6   | μΑ    |

| Sync Pull Up Current                                  | _                 | -          | 450   | 500   | 550   | μΑ    |

| Logic 0 Current (Pull Down)                           | _                 | -          | 225   | 250   | 275   | μΑ    |

| Logic 1 Current (Pull Up)                             | -                 | -          | 225   | 250   | 275   | μA    |

| Synchronization Time<br>(Synchronization Pulse Width) | T <sub>SYNC</sub> | Baud = 0   | 237   | 250   | 263   | μs    |

|                                                       |                   | Baud = 1   | 118   | 125   | 132   |       |

|                                                       |                   | Baud = 2   | 59    | 62.5  | 66    |       |

|                                                       |                   | Baud = 3   | 29.76 | 31.25 | 32.81 |       |

|                                                       |                   | Baud = 4   | 14.88 | 15.63 | 16.41 |       |

|                                                       |                   | Baud = 5   | 7.44  | 7.81  | 8.20  | 1     |

|                                                       |                   | Baud = 6   | 3.72  | 3.91  | 4.10  | 1     |

|                                                       |                   | Baud = 7   | 1.86  | 1.95  | 2.05  | 1     |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

1. Total System Gain consists of: Wideband System Gain + High and Low Independent Channel Gains + Converter Gain.

Total System Gain is calibrated during Cal/Config process.

2. Sample tested.

### Support Software

Paragon GA3224 is fully supported ON Semiconductor's software tools available from ARKonline® website http://ark.onsemi.com/.

### **TYPICAL APPLICATIONS**

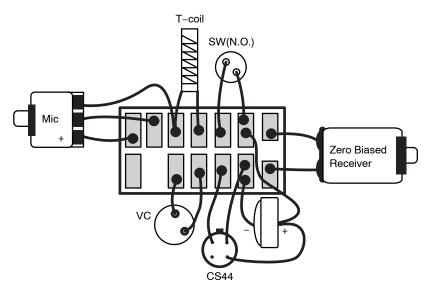

Figure 2. Test Circuit

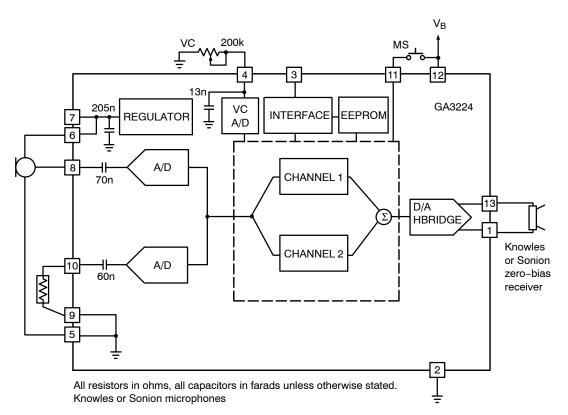

### **TYPICAL APPLICATIONS (Continued)**

Figure 3. Sample Application Circuit

Figure 4. Assembly Diagram

### Table 3. PAD POSITION AND DIMENSIONS

|         | Pad P  | osition | Pad Dimensions |            |  |

|---------|--------|---------|----------------|------------|--|

| Pad No. | x      | Y       | Xdim (mil)     | Ydim (mil) |  |

| 1       | 0      | 0       | 23.0           | 40.5       |  |

| 2       | -31.5  | 3       | 24.0           | 46.5       |  |

| 3       | -63.0  | 3       | 23.0           | 46.5       |  |

| 4       | -94.0  | 3       | 23.0           | 46.5       |  |

| 5       | -125.0 | 3       | 23.0           | 46.5       |  |

| 6       | -187.0 | 3       | 23.0           | 46.5       |  |

| 7       | -187.0 | 64.5    | 23.0           | 46.5       |  |

| 8       | -156.0 | 64.5    | 23.0           | 46.5       |  |

| 9       | -125.0 | 64.5    | 23.0           | 46.5       |  |

| 10      | -94.0  | 64.5    | 23.0           | 46.5       |  |

| 11      | -63.0  | 64.5    | 23.0           | 46.5       |  |

| 12      | -31.5  | 64.5    | 24.0           | 46.5       |  |

| 13      | 0      | 67.5    | 23.0           | 40.5       |  |

| Pad No. | x      | Y       | Xdim (mm)      | Ydim (mm)  |  |

| 1       | 0      | 0       | 0.584          | 1.029      |  |

| 2       | -0.800 | 0.076   | 0.610          | 1.181      |  |

| 3       | -1.600 | 0.076   | 0.584          | 1.181      |  |

| 4       | -2.388 | 0.076   | 0.584          | 1.181      |  |

| 5       | -3.175 | 0.076   | 0.584          | 1.181      |  |

| 6       | -4.750 | 0.076   | 0.584          | 1.181      |  |

| 7       | -4.750 | 1.638   | 0.584          | 1.181      |  |

| 8       | -3.962 | 1.638   | 0.584          | 1.181      |  |

| 9       | -3.175 | 1.638   | 0.584          | 1.181      |  |

| 10      | -2.388 | 1.638   | 0.584          | 1.181      |  |

| 11      | -1.600 | 1.638   | 0.584          | 1.181      |  |

| 12      | -0.800 | 1.638   | 0.610          | 1.181      |  |

| 13      | 0      | 1.715   | 0.584          | 1.029      |  |

#### PACKAGE DIMENSIONS

Dimension units are in inches.

Dimensions in parentheses are in millimeters, converted from inches and include minor rounding errors.

1.000 inches = 25.4 mm

Dimension tolerances:  $\pm 0.003$  ( $\pm 0.08$ ) unless otherwise stated.

= location of Pin 1

RoHS compliant hybrid, MSL#4

This Hybrid is designed for either point-to-point manual soldering or for reflow according to ON Semiconductor's reflow process.

thinSTAX and FRONTWAVE are registered trademarks of Semiconductor Components Industries, LLC. HRX is a trademark of Semiconductor Components Industries, LLC.

**ON Semiconductor** and **W** are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemic.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC products are not designed, intended, or authorized for use as components insystems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Depen: 421-22-200-2010

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5817–1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative