## 19-OUTPUT PCIE GEN3 AND QPI BUFFER

#### **Features**

- Nineteen 0.7 V current-mode, HCSL PCIe Gen3 outputs

- 100 MHz /133 MHz PLL operation, supports PCIe and QPI

- PLL bandwidth SW SMBUS programming overrides the latch value from HW pin

- 9 selectable SMBUS addresses

- Fixed internal feedback path

- 8 dedicated OE pins

- PLL or bypass mode

- Spread spectrum tolerable

- 50 ps output-to-output skew

- Fixed 0 ps input to output delay

- Low phase jitter (Intel QPI, PCIe Gen 1/2/3/4 common clock compliant)

- Gen 3 SRNS Compliant

- 100 ps input-to-output delay

- Extended Temperature: -40 to 85 °C

- Package: 72-pin QFN

Ordering Information: See page 32.

### **Applications**

- Server

- Storage

Data center

### **Description**

The Si53019-A02A is a 19-output, current mode HCSL differential clock buffer that meets all of the performance requirements of the Intel DB1900Z specification. The device is optimized for distributing reference clocks for Intel<sup>®</sup> QuickPath Interconnect (Intel QPI), PCIe Gen 1/Gen 2/Gen 3/Gen 4, SAS, SATA, and Intel Scalable Memory Interconnect (Intel SMI) applications. The VCO of the device is optimized to support 100 MHz and 133 MHz operation. Each differential output can be enabled through I<sup>2</sup>C for maximum flexibility and power savings.

The Si53019-A02A features a fixed internal feedback path. Measuring PCIe clock jitter is quick and easy with the Silicon Labs PCIe Clock Jitter Tool. Download it for free at <a href="https://www.silabs.com/pcie-learningcenter">www.silabs.com/pcie-learningcenter</a>.

Patents pending

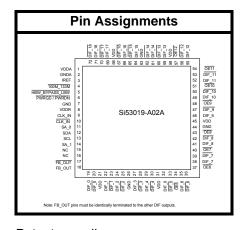

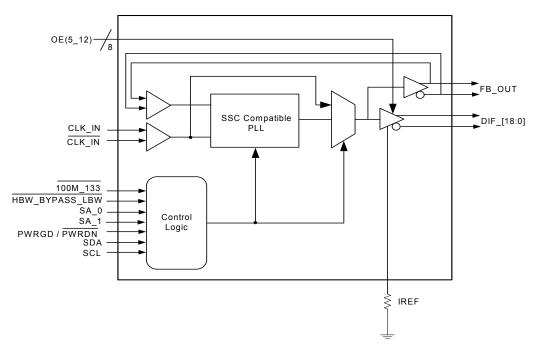

### **Functional Block Diagram**

Note:  ${\sf FB\_OUT}$  pins must be identically terminated to the other DIF outputs.

# TABLE OF CONTENTS

| <u>Section</u>                           | <u>Page</u> |

|------------------------------------------|-------------|

| 1. Electrical Specifications             |             |

| 2. Functional Description                |             |

| 2.1. CLK IN, CLK IN                      |             |

| 2.2. 100M_133M—Frequency Selection       |             |

| 2.3. SA_0, SA_1—Address Selection        |             |

| 2.4. CKPWRGD/PWRDN                       |             |

| 2.5. HBW BYPASS LBW                      |             |

| 2.6. Miscellaneous Requirements          |             |

| 3. Test and Measurement Setup            |             |

| 3.1. Input Edge                          |             |

| 3.2. Termination of Differential Outputs |             |

| 4. Control Registers                     |             |

| 4.1. Byte Read/Write                     |             |

| 4.2. Block Read/Write                    |             |

| 4.3. Control Registers                   |             |

| 5. Pin Descriptions: 72-Pin QFN          |             |

| 6. Power Filtering Example               |             |

| 6.1. Ferrite Bead Power Filtering        |             |

| 7. Ordering Guide                        |             |

| 8. Package Outline                       |             |

| 9. Land Pattern                          |             |

| Document Change List                     |             |

### 1. Electrical Specifications

Table 1. DC Operating Characteristics<sup>1</sup>

$V_{DD\ A} = 3.3\ V\ \pm 5\%,\ V_{DD} = 3.3\ V\ \pm 5\%$

| Parameter                              | Symbol              | Condition                 | Min     | Max                  | Unit |

|----------------------------------------|---------------------|---------------------------|---------|----------------------|------|

| 3.3 V Core Supply Voltage              | VDD/VDD_A           | 3.3 V ±5%                 | 3.135   | 3.465                | V    |

| 3.3 V Input High Voltage               | V <sub>IH</sub>     | $V_{\mathrm{DD}}$         | 2.0     | V <sub>DD</sub> +0.3 | V    |

| 3.3 V Input Low Voltage                | V <sub>IL</sub>     |                           | VSS-0.3 | 0.8                  | V    |

| Input Leakage Current <sup>2</sup>     | I <sub>IL</sub>     | 0 < VIN < V <sub>DD</sub> | -5      | +5                   | μΑ   |

| 3.3 V Input High Voltage <sup>3</sup>  | V <sub>IH_FS</sub>  | $V_{DD}$                  | 0.7     | V <sub>DD</sub> +0.3 | V    |

| 3.3 V Input Low Voltage <sup>3</sup>   | V <sub>IL_FS</sub>  |                           | VSS-0.3 | 0.35                 | V    |

| 3.3 V Input Low Voltage                | V <sub>IL_Tri</sub> |                           | 0       | 0.9                  | V    |

| 3.3 V Input Med Voltage                | V <sub>IM_Tri</sub> |                           | 1.3     | 1.8                  | V    |

| 3.3 V Input High Voltage               | V <sub>IH_Tri</sub> |                           | 2.4     | V <sub>DD</sub>      | V    |

| 3.3 V Output High Voltage <sup>4</sup> | V <sub>OH</sub>     | I <sub>OH</sub> = -1 mA   | 2.4     | _                    | V    |

| 3.3 V Output Low Voltage <sup>4</sup>  | V <sub>OL</sub>     | I <sub>OL</sub> = 1 mA    | _       | 0.4                  | V    |

| Input Capacitance <sup>5</sup>         | C <sub>IN</sub>     |                           | 2.5     | 4.5                  | pF   |

| Output Capacitance <sup>5</sup>        | C <sub>OUT</sub>    |                           | 2.5     | 4.5                  | pF   |

| Pin Inductance                         | L <sub>PIN</sub>    |                           | _       | 7                    | nH   |

| Ambient Temperature                    | T <sub>A</sub>      | No Airflow                | 0       | 70                   | °C   |

|                                        |                     |                           | II.     | 1                    |      |

#### Notes:

- 1. VDD\_IO applies to the low-power NMOS push-pull HCSL compatible outputs.

- 2. Input Leakage Current does not include inputs with pull-up or pull-down resistors. Inputs with resistors should state current requirements.

- 3. Internal voltage reference is to be used to guarantee  $V_{IH}$ FS and  $V_{IL}$ FS thresholds levels over full operating range.

- **4.** Signal edge is required to be monotonic when transitioning through this region.

- 5. Ccomp capacitance based on pad metalization and silicon device capacitance. Not including pin capacitance.

Table 2. DIF 0.7 V AC Timing Characteristics (Non-Spread Spectrum Mode)<sup>1</sup>

| Parameter                                           | Symbol                                           | CLK 1   | 100 MHz, 13 | 3 MHz    | Unit |

|-----------------------------------------------------|--------------------------------------------------|---------|-------------|----------|------|

|                                                     |                                                  | Min     | Тур         | Max      |      |

| Clock Stabilization Time <sup>2</sup>               | T <sub>STAB</sub>                                | _       | 1.5         | 1.8      | ms   |

| Long Term Accuracy <sup>3,4,5</sup>                 | L <sub>ACC</sub>                                 | _       |             | 100      | ppm  |

| Absolute Host CLK Period (100 MHz) <sup>3,4,6</sup> | T <sub>ABS</sub>                                 | 9.94900 |             | 10.05100 | ns   |

| Absolute Host CLK Period (133 MHz) <sup>3,4,6</sup> | T <sub>ABS</sub>                                 | 7.44925 |             | 7.55075  | ns   |

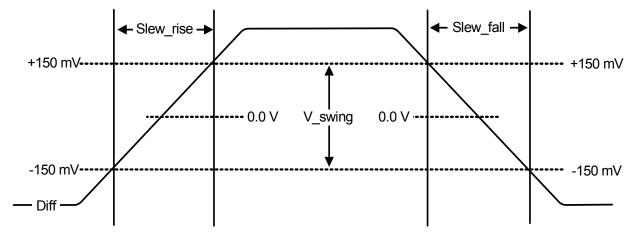

| Slew Rate <sup>3,4,7</sup>                          | Edge_rate                                        | 1.0     | 3.0         | 4.0      | V/ns |

| Slew Rate Matching <sup>3,8,10,11</sup>             | T <sub>RISE_MAT</sub> /<br>T <sub>FALL_MAT</sub> | _       | 7           | 20       | %    |

| Rise Time Variation <sup>3,8,9</sup>                | Δ Trise                                          | _       |             | 125      | ps   |

| Fall Time Variation <sup>3,8,9</sup>                | ∆ Tfall                                          | _       |             | 125      | ps   |

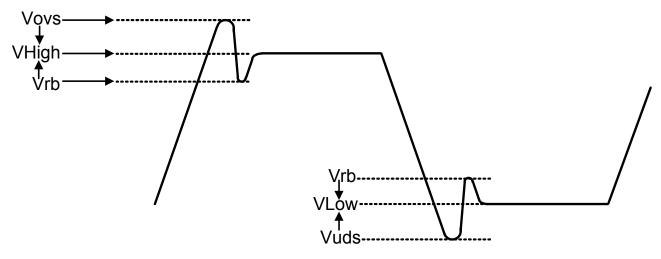

| Voltage High (typ 0.7 V) <sup>3,8,12</sup>          | V <sub>HIGH</sub>                                | 660     | 750         | 850      | mV   |

| Voltage Low (typ 0.7 V) <sup>3,8,13</sup>           | $V_{LOW}$                                        | -150    | 15          | 150      | mV   |

| Maximum Voltage <sup>8</sup>                        | V <sub>MAX</sub>                                 | _       | 850         | 1150     | mV   |

| Minimum Voltage                                     | V <sub>MIN</sub>                                 | -300    |             |          | mV   |

#### Notes

- 1. Unless otherwise noted, all specifications in this table apply to all processor frequencies.

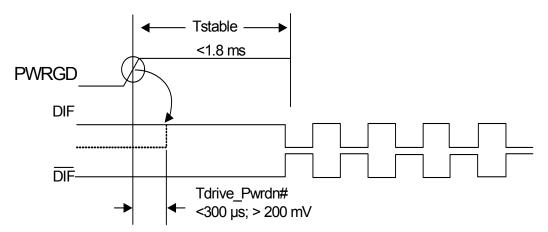

- 2. This is the time from the valid CLK\_IN input clocks and the assertion of the PWRGD signal level at 1.8–2.0 V to the time that stable clocks are output from the buffer chip (PLL locked).

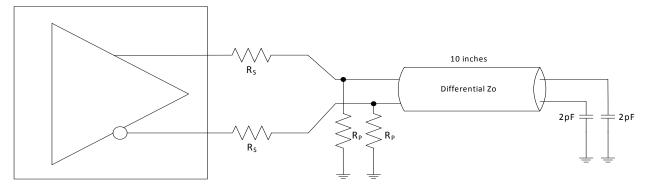

- 3. Test configuration is Rs = 33.2  $\Omega$ , Rp = 49.9, 2 pF for 100  $\Omega$  transmission line; Rs = 27  $\Omega$ , Rp = 42.2, 2 pF for 85  $\Omega$  transmission line.

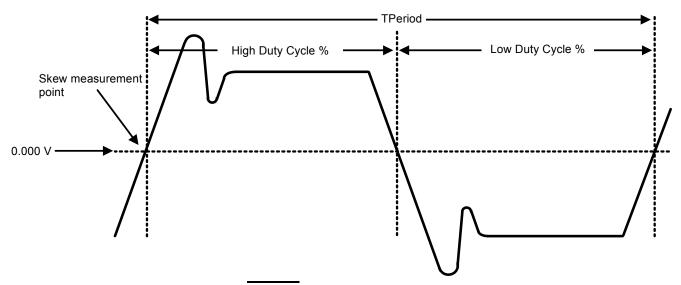

- 4. Measurement taken from differential waveform.

- **5.** Using frequency counter with the measurement interval equal or greater than 0.15 s, target frequencies are 99.750,00 Hz, 133,000,000 Hz.

- **6.** The average period over any 1  $\mu$ s period of time must be greater than the minimum and less than the maximum specified period.

- 7. Measure taken from differential waveform on a component test board. The edge (slew) rate is measured from –150 mV to +150 mV on the differential waveform. Scope is set to average because the scope sample clock is making most of the dynamic wiggles along the clock edge. Only valid for Rising clock and Falling CLOCK. Signal must be monotonic through the Vol to Voh region for Trise and Tfall.

- 8. Measurement taken from single-ended waveform.

- 9. Measured with oscilloscope, averaging off, using min max statistics. Variation is the delta between min and max.

- **10.** Measured with oscilloscope, <u>averaging</u> on. The difference between the rising edge rate (average) of clock verses the falling edge rate (average) of CLOCK.

- 11. Rise/Fall matching is derived using the following: 2\*(Trise Tfall) / (Trise + Tfall).

- 12. VHigh is defined as the statistical average High value as obtained by using the Oscilloscope VHigh Math function.

- 13. VLow is defined as the statistical average Low value as obtained by using the Oscilloscope VLow Math function.

- 14. Measured at crossing point where the instantaneous voltage value of the rising edge of CLK equals the falling edge of CLK.

- **15.** This measurement refers to the total variation from the lowest crossing point to the highest, regardless of which edge is crossing.

- 16. The crossing point must meet the absolute and relative crossing point specifications simultaneously.

- **17.** Vcross(rel) Min and Max are derived using the following, Vcross(rel) Min = 0.250 + 0.5 (Vhavg 0.700), Vcross(rel) Max = 0.550 0.5 (0.700 Vhavg), (see Figures 3-4 for further clarification).

- **18.** ΔVcross is defined as the total variation of all crossing voltages of Rising CLOCK and Falling CLOCK. This is the maximum allowed variance in Vcross for any particular system.

- 19. Overshoot is defined as the absolute value of the maximum voltage.

- 20. Undershoot is defined as the absolute value of the minimum voltage.

Table 2. DIF 0.7 V AC Timing Characteristics (Non-Spread Spectrum Mode)<sup>1</sup> (Continued)

| Parameter                                                  | Symbol             | CLK ' | 100 MHz, 13 | 3 MHz                   | Unit |

|------------------------------------------------------------|--------------------|-------|-------------|-------------------------|------|

|                                                            |                    | Min   | Тур         | Max                     |      |

| Absolute Crossing Point Voltages <sup>3,8,14,15,16</sup>   | Vox <sub>ABS</sub> | 250   | 450         | 550                     | mV   |

| Total Variation of Vcross Over All Edges <sup>3,8,18</sup> | Total ∆<br>Vox     | _     | 14          | 140                     | mV   |

| Vswing <sup>4</sup>                                        | Vswing             | 300   |             |                         | mV   |

| Duty Cycle <sup>3,4</sup>                                  | DC                 | 45    |             | 55                      | %    |

| Maximum Voltage (Overshoot) <sup>3,8,19</sup>              | V <sub>ovs</sub>   | _     |             | V <sub>High</sub> + 0.3 | V    |

| Maximum Voltage (Undershoot) <sup>3,8,20</sup>             | V <sub>uds</sub>   | _     |             | $V_{Low} - 0.3$         | V    |

| Ringback Voltage <sup>3,8</sup>                            | V <sub>rb</sub>    | 0.2   |             | N/A                     | V    |

#### Notes:

- 1. Unless otherwise noted, all specifications in this table apply to all processor frequencies.

- 2. This is the time from the valid CLK\_IN input clocks and the assertion of the PWRGD signal level at 1.8–2.0 V to the time that stable clocks are output from the buffer chip (PLL locked).

- 3. Test configuration is Rs = 33.2  $\Omega$ , Rp = 49.9, 2 pF for 100  $\Omega$  transmission line; Rs = 27  $\Omega$ , Rp = 42.2, 2 pF for 85  $\Omega$  transmission line.

- 4. Measurement taken from differential waveform.

- 5. Using frequency counter with the measurement interval equal or greater than 0.15 s, target frequencies are 99.750.00 Hz. 133.000.000 Hz.

- **6.** The average period over any 1  $\mu$ s period of time must be greater than the minimum and less than the maximum specified period.

- 7. Measure taken from differential waveform on a component test board. The edge (slew) rate is measured from -150 mV to +150 mV on the differential waveform. Scope is set to average because the scope sample clock is making most of the dynamic wiggles along the clock edge. Only valid for Rising clock and Falling CLOCK. Signal must be monotonic through the Vol to Voh region for Trise and Tfall.

- 8. Measurement taken from single-ended waveform.

- 9. Measured with oscilloscope, averaging off, using min max statistics. Variation is the delta between min and max.

- **10.** Measured with oscilloscope, <u>averaging</u> on. The difference between the rising edge rate (average) of clock verses the falling edge rate (average) of CLOCK.

- 11. Rise/Fall matching is derived using the following: 2\*(Trise Tfall) / (Trise + Tfall).

- 12. VHigh is defined as the statistical average High value as obtained by using the Oscilloscope VHigh Math function.

- 13. VLow is defined as the statistical average Low value as obtained by using the Oscilloscope VLow Math function.

- 14. Measured at crossing point where the instantaneous voltage value of the rising edge of CLK equals the falling edge of CLK.

- **15.** This measurement refers to the total variation from the lowest crossing point to the highest, regardless of which edge is crossing.

- **16.** The crossing point must meet the absolute and relative crossing point specifications simultaneously.

- **17.** Vcross(rel) Min and Max are derived using the following, Vcross(rel) Min = 0.250 + 0.5 (Vhavg 0.700), Vcross(rel) Max = 0.550 0.5 (0.700 Vhavg), (see Figures 3-4 for further clarification).

- **18.** ΔVcross is defined as the total variation of all crossing voltages of Rising CLOCK and Falling CLOCK. This is the maximum allowed variance in Vcross for any particular system.

- **19.** Overshoot is defined as the absolute value of the maximum voltage.

- 20. Undershoot is defined as the absolute value of the minimum voltage.

**Table 3. SMBus Characteristics**

| Parameter                                | Symbol              | Conditions                                                      | Min | Max                | Unit |

|------------------------------------------|---------------------|-----------------------------------------------------------------|-----|--------------------|------|

| SMBus Input Low Voltage <sup>1</sup>     | V <sub>ILSMB</sub>  |                                                                 |     | 0.8                | V    |

| SMBus Input High Voltage <sup>1</sup>    | V <sub>IHSMB</sub>  |                                                                 | 2.1 | $V_{\text{DDSMB}}$ | ٧    |

| SMBus Output Low Voltage <sup>1</sup>    | V <sub>OLSMB</sub>  | @ I <sub>PULLUP</sub>                                           |     | 0.4                | V    |

| Nominal Bus Voltage <sup>1</sup>         | V <sub>DDSMB</sub>  | @ V <sub>OL</sub>                                               | 2.7 | 5.5                | V    |

| SMBus Sink Current <sup>1</sup>          | I <sub>PULLUP</sub> | 3 V to 5 V ±10%                                                 | 4   |                    | mA   |

| SCLK/SDAT Rise Time <sup>1</sup>         | t <sub>RSMB</sub>   | (Max V <sub>IL</sub> – 0.15) to (Min V <sub>IH</sub> + 0.15)    |     | 1000               | ns   |

| SCLK/SDAT Fall Time <sup>1</sup>         | t <sub>FSMB</sub>   | (Min V <sub>IH</sub> + 0.15) to<br>(Max V <sub>IL</sub> – 0.15) |     | 300                | ns   |

| SMBus Operating Frequency <sup>1,2</sup> | f <sub>MINSMB</sub> | Minimum Operating Frequency                                     | 100 |                    | kHz  |

#### Notes:

- Guaranteed by design and characterization.

The differential input clock must be running for the SMBus to be active.

Table 4. Current Consumption  $T_A$  = 0–70 °C; supply voltage  $V_{DD}$  = 3.3 V ±5%

| Parameter          | Symbol               | Conditions                              | Min | Тур | Max | Unit |

|--------------------|----------------------|-----------------------------------------|-----|-----|-----|------|

| Operating Current  | $IDD_VDD$            | 100 MHz, CL = Full Load, Rs=33 $\Omega$ | _   | 310 | 350 | mA   |

| Power Down Current | IDD <sub>VDDPD</sub> | All differential pairs tri-stated       | _   | 6   | 15  | mA   |

## Si53019-A02A

### **Table 5. Clock Input Parameters**

$T_A = 0-70 \, ^{\circ}\text{C}$ ; supply voltage  $V_{DD} = 3.3 \, \text{V} \pm 5\%$

| Parameter                    | Symbol             | Conditions                                      | Min     | Тур    | Max  | Unit |

|------------------------------|--------------------|-------------------------------------------------|---------|--------|------|------|

| Input High Voltage           | V <sub>IHDIF</sub> | Differential Inputs (singled-ended measurement) | 600     | 800    | 1150 | mV   |

| Input Low Voltage            | V <sub>IHDIF</sub> | Differential Inputs (singled-ended measurement) | VSS-300 | 0      | 300  | mV   |

| Input Common Mode<br>Voltage | V <sub>com</sub>   | Common mode input voltage                       | 300     |        | 1000 | mV   |

| Input Amplitude              | V <sub>swing</sub> | Peak to Peak Value                              | 300     |        | 1450 | mV   |

| Input Slew Rate              | dv/dt              | Measured differentially                         | 0.4     |        | 8    | V/ns |

| Input Duty Cycle             |                    | Measurement from differential wave form         | 45      | 50     | 55   | %    |

| Input Jitter—Cycle to Cycle  | $J_{DFin}$         | Differential measurement                        |         |        | 125  | ps   |

| Input Frequency              | F <sub>ibyp</sub>  | V <sub>DD</sub> = 3.3 V, bypass mode            | 33      |        | 150  | MHz  |

|                              | F <sub>iPLL</sub>  | V <sub>DD</sub> = 3.3 V, 100 MHz PLL Mode       | 90      | 100    | 110  | MHz  |

|                              | FiPLL              | V <sub>DD</sub> = 3.3 V, 133.33 MHz PLL Mode    | 120     | 133.33 | 147  | MHz  |

| Input SS Modulation<br>Rate  | f <sub>MODIN</sub> | Triangle Wave modulation                        | 30      | 31.5   | 33   | kHz  |

### Table 6. Output Skew, PLL Bandwidth and Peaking

$T_A = 0-70$  °C; supply voltage  $V_{DD} = 3.3 \text{ V} \pm 5\%$

| Parameter          | Parameter                                                                                       | Min         | TYP | Max | Unit        |

|--------------------|-------------------------------------------------------------------------------------------------|-------------|-----|-----|-------------|

| CLK_IN, DIF[x:0]   | Input-to-Output Delay in PLL Mode<br>Nominal Value <sup>1,2,3,4</sup>                           | -100        | 10  | 100 | ps          |

| CLK_IN, DIF[x:0]   | Input-to-Output Delay in Bypass Mode<br>Nominal Value <sup>2,4,5</sup>                          | 2.5         | 3.3 | 4.5 | ns          |

| CLK_IN, DIF[x:0]   | Input-to-Output Delay Variation in PLL Mode<br>Over voltage and temperature <sup>2,4,5</sup>    | <b>–</b> 50 |     | 50  | ps          |

| CLK_IN, DIF[x:0]   | Input-to-Output Delay Variation in Bypass Mode<br>Over voltage and temperature <sup>2,4,5</sup> | -250        | _   | 250 | ps          |

| CLK_IN, DIF[x:0]   | Random differential spread spectrum tracking error between 2 DB1900Z devices in Hi BW Mode      |             | 15  | 75  | ps          |

| CLK_IN, DIF[x:0]   | Random differential tracking error between 2 DB1900Z devices in Hi BW Mode                      |             | 3   | 5   | ps<br>(rms) |

| DIF[18:0]          | Output-to-Output Skew across all Outputs (Common to Bypass and PLL Mode) <sup>1,2,3,4,5</sup>   | 0           | 20  | 50  | ps          |

| PLL Jitter Peaking | (HBW_BYPASS_LBW = 0) <sup>6</sup>                                                               | _           | 0.4 | 2.0 | dB          |

| PLL Jitter Peaking | (HBW_BYPASS_LBW = 1) <sup>6</sup>                                                               | _           | 0.1 | 2.5 | dB          |

| PLL Bandwidth      | $(\overline{\text{HBW\_BYPASS\_LBW}} = 0)^7$                                                    |             | 0.7 | 1.4 | MHz         |

| PLL Bandwidth      | (HBW_BYPASS_LBW = 1) <sup>7</sup>                                                               | _           | 2   | 4   | MHz         |

### Notes:

- 1. Measured into fixed 2 pF load cap. Input-to-output skew is measured at the first output edge following the corresponding input.

- 2. Measured from differential cross-point to differential cross-point.

- 3. This parameter is deterministic for a given device.

- **4.** Measured with scope averaging on to find mean value.

- **5.** All Bypass Mode Input-to-Output specs refer to the timing between an input edge and the specific output edge created by it.

- **6.** Measured as maximum pass band gain. At frequencies within the loop BW, highest point of magnification is called PLL jitter peaking.

- 7. Measured at 3 db down or half power point.

Table 7. Phase Jitter

| Parameter                | Condition                                                                                                 | Min | Тур  | Max  | Units       |

|--------------------------|-----------------------------------------------------------------------------------------------------------|-----|------|------|-------------|

| Phase Jitter<br>PLL Mode | PCIe Gen 1, Common Clock <sup>1,2,3</sup>                                                                 | _   | 30   | 86   | ps          |

|                          | PCle Gen2 Low Band, Common Clock<br>F < 1.5 MHz <sup>1,3,4,5</sup>                                        |     | 1.0  | 3.0  | ps<br>(RMS) |

|                          | PCIe Gen2 High Band, Common Clock<br>1.5 MHz < F < Nyquist <sup>1,3,4,5</sup>                             | _   | 2.6  | 3.1  | ps<br>(RMS) |

|                          | PCIe Gen 3, Common Clock<br>(PLL BW 2–4 MHz, CDR = 10 MHz) <sup>1,3,4,5</sup>                             | _   | 0.6  | 1.0  | ps<br>(RMS) |

|                          | Intel <sup>®</sup> QPI & Intel SMI<br>(4.8 Gbps or 6.4 Gb/s, 100 or 133 MHz, 12 UI) <sup>1,6,7</sup>      | _   | 0.25 | 0.5  | ps<br>(RMS) |

|                          | PCIe Gen 3 Separate Reference No Spread, SRNS (PLL BW of 2–4 or 2–5 MHz, CDR = 10 MHz) <sup>1,3,4,5</sup> | _   | 0.42 | 0.71 | ps<br>(RMS) |

|                          | PCIe Gen 4, Common Clock<br>(PLL BW of 2–4 or 2–5 MHz, CDR = 10 MHz) <sup>1,4,5,8</sup>                   | _   | 0.6  | 1.0  | ps<br>(RMS) |

|                          | Intel QPI & Intel SMI<br>(8 Gb/s, 100 MHz, 12 UI) <sup>1,6</sup>                                          | _   | 0.17 | 0.3  | ps<br>(RMS) |

|                          | Intel QPI & Intel SMI<br>(9.6 Gb/s, 100 MHz, 12 UI) <sup>1,6</sup>                                        | _   | 0.15 | 0.2  | ps<br>(RMS) |

#### **Notes**

- 1. Post processed evaluation through Intel supplied Matlab\* scripts. Defined for a BER of 1E-12. Measured values at a smaller sample size have to be extrapolated to this BER target.

- **2.**  $\zeta$  = 0.54 implies a jitter peaking of 3 dB.

- 3. PCIe\* Gen3 filter characteristics are subject to final ratification by PCISIG. Check the PCI-SIG for the latest specification.

- 4. Measured on 100 MHz PCIe output using the template file in the Intel-supplied Clock Jitter Tool V1.6.3.

- 5. Measured on 100 MHz output using the template file in the Intel-supplied Clock Jitter Tool V1.6.3.

- 6. Measured on 100 MHz, 133 MHz output using the template file in the Intel-supplied Clock Jitter Tool V1.6.3.

- **7.** These jitter numbers are defined for a BER of 1E-12. Measured numbers at a smaller sample size have to be extrapolated to this BER target.

- 8. Gen 4 specifications based on the PCI-Express Base Specification 4.0 rev. 0.5.

- 9. Download the Silicon Labs PCIe Clock Jitter Tool at www.silabs.com/pcie-learningcenter.

**Table 7. Phase Jitter (Continued)**

| Additive Phase Jitter | PCIe Gen 1 <sup>1,2,3</sup>                                                              | _ | 4    | _ | ps          |

|-----------------------|------------------------------------------------------------------------------------------|---|------|---|-------------|

| Bypass Mode           | PCIe Gen 2 Low Band<br>F < 1.5 MHz <sup>1,3,4,5</sup>                                    | _ | 0.08 | _ | ps<br>(RMS) |

|                       | PCIe Gen 2 High Band<br>1.5 MHz < F < Nyquist <sup>1,3,4,5</sup>                         | _ | 1.0  | _ | ps<br>(RMS) |

|                       | PCIe Gen 3<br>(PLL BW 2–4 MHz, CDR = 10 MHz) <sup>1,3,4,5</sup>                          | - | 0.27 | _ | ps<br>(RMS) |

|                       | PCIe Gen 4, Common Clock<br>(PLL BW of 2–4 or 2–5 MHz, CDR = 10 MHz) <sup>1,4,5,8</sup>  | _ | 0.27 | _ | ps<br>(RMS) |

|                       | Intel QPI & Intel® SMI<br>(4.8 Gbps or 6.4 Gb/s, 100 or 133 MHz, 12 UI) <sup>1,6,7</sup> | _ | 0.25 | _ | ps<br>(RMS) |

|                       | Intel QPI & Intel® SMI<br>(8 Gb/s, 100 MHz, 12 UI) <sup>1,6</sup>                        | _ | 0.08 | _ | ps<br>(RMS) |

|                       | Intel QPI & Intel® SMI<br>(9.6 Gb/s, 100 MHz, 12 UI) <sup>1,6</sup>                      | _ | 0.07 | _ | ps<br>(RMS) |

#### Notes:

- 1. Post processed evaluation through Intel supplied Matlab\* scripts. Defined for a BER of 1E-12. Measured values at a smaller sample size have to be extrapolated to this BER target.

- **2.**  $\zeta = 0.54$  implies a jitter peaking of 3 dB.

- **3.** PCIe\* Gen3 filter characteristics are subject to final ratification by PCISIG. Check the PCI-SIG for the latest specification.

- 4. Measured on 100 MHz PCIe output using the template file in the Intel-supplied Clock Jitter Tool V1.6.3.

- 5. Measured on 100 MHz output using the template file in the Intel-supplied Clock Jitter Tool V1.6.3.

- 6. Measured on 100 MHz, 133 MHz output using the template file in the Intel-supplied Clock Jitter Tool V1.6.3.

- **7.** These jitter numbers are defined for a BER of 1E-12. Measured numbers at a smaller sample size have to be extrapolated to this BER target.

- 8. Gen 4 specifications based on the PCI-Express Base Specification 4.0 rev. 0.5.

- **9.** Download the Silicon Labs PCIe Clock Jitter Tool at www.silabs.com/pcie-learningcenter.

Table 8. Clock Periods Differential Clock Outputs with SSC Disabled

| SSC OFF             |                              |                                  | Meas                            | urement Wi                 | ndow                            |                                  |                                 | Units |

|---------------------|------------------------------|----------------------------------|---------------------------------|----------------------------|---------------------------------|----------------------------------|---------------------------------|-------|

| Center<br>Freq, MHz | 1 Clock                      | 1 µs                             | 0.1 s                           | 0.1 s                      | 0.1 s                           | 1 µs                             | 1 Clock                         |       |

|                     | -C-C Jitter<br>AbsPer<br>Min | -SSC<br>Short<br>Term AVG<br>Min | -ppm<br>Long<br>Term AVG<br>Min | 0 ppm<br>Period<br>Nominal | +ppm<br>Long<br>Term AVG<br>Max | +SSC<br>Short<br>Term AVG<br>Max | +C-C<br>Jitter<br>AbsPer<br>Max |       |

| 100.00              | 9.94900                      |                                  | 9.99900                         | 10.00000                   | 10.00100                        |                                  | 10.05100                        | ns    |

| 133.33              | 7.44925                      |                                  | 7.49925                         | 7.50000                    | 7.50075                         |                                  | 7.55075                         | ns    |

### Table 9. Clock Periods Differential Clock Outputs with SSC Enabled

| SSC ON              |                              |                                       | Meas                            | urement Wi                 | ndow                            |                                  |                                 | Units |

|---------------------|------------------------------|---------------------------------------|---------------------------------|----------------------------|---------------------------------|----------------------------------|---------------------------------|-------|

| Center<br>Freq, MHz | 1 Clock                      | 1 Clock 1 μs 0.1 s 0.1 s 1 μs 1 Clock |                                 |                            |                                 |                                  |                                 |       |

| ·                   | -C-C Jitter<br>AbsPer<br>Min | -SSC<br>Short<br>Term AVG<br>Min      | –ppm<br>Long<br>Term AVG<br>Min | 0 ppm<br>Period<br>Nominal | +ppm<br>Long<br>Term AVG<br>Max | +SSC<br>Short<br>Term AVG<br>Max | +C-C<br>Jitter<br>AbsPer<br>Max |       |

| 99.75               | 9.94906                      | 9.99906                               | 10.02406                        | 10.02506                   | 10.02607                        | 10.05107                         | 10.10107                        | ns    |

| 133.00              | 7.44930                      | 7.49930                               | 7.51805                         | 7.51880                    | 7.51955                         | 7.53830                          | 7.58830                         | ns    |

### **Table 10. Absolute Maximum Ratings**

| Parameter                               | Symbol         | Min         | Max                   | Unit |

|-----------------------------------------|----------------|-------------|-----------------------|------|

| 3.3 V Core Supply Voltage <sup>1</sup>  | VDD/VDD_A      | _           | 4.6                   | V    |

| 3.3 V Input High Voltage <sup>1,2</sup> | VIH            | _           | V <sub>DD</sub> +0.5V | V    |

| 3.3 V Input Low Voltage <sup>1</sup>    | VIL            | -0.5        |                       | V    |

| Storage Temperature <sup>1</sup>        | t <sub>s</sub> | <b>–</b> 65 | 150                   | °C   |

| Input ESD protection <sup>3</sup>       | ESD            | 2000        | _                     | V    |

### Notes:

- Consult manufacturer regarding extended operation in excess of normal dc operating parameters.

Maximum VIH is not to exceed maximum V<sub>DD</sub>.

- 3. Human body model.

## 2. Functional Description

Note: FB\_OUT pins must be identically terminated to the other DIF outputs.

Figure 1. Si53019-A02A Functional Block Diagram

**Table 11. Functionality at Powerup (PLL Mode)**

| 100M_133M | CLK_IN (MHz) | DIF    |

|-----------|--------------|--------|

| 1         | 100          | CLK_IN |

| 0         | 133.33       | CLK_IN |

**Table 12. PLL Operating Mode Readback Table**

| HBW_BYPASS_LBW | Byte 0, Bit 7 | Byte 0, Bit 6 | Mode        |

|----------------|---------------|---------------|-------------|

| Low            | 0             | 0             | PLL Low BW  |

| Mid (Bypass)   | 0             | 1             | Bypass      |

| High           | 1             | 1             | PLL High BW |

**Table 13. Tri-Level Input Thresholds**

| Parameter | Voltage           |

|-----------|-------------------|

| Low       | < 0.8 V           |

| Mid       | 1.2 < Vin < 1.8 V |

| High      | Vin > 2.2 V       |

**Table 14. Power Connections**

| Pin Number      |          | Description  |

|-----------------|----------|--------------|

| V <sub>DD</sub> | GND      |              |

| 1               | 2        | Analog PLL   |

| 8               | 7        | Analog Input |

| 21,31,45,58,68  | 26,44,63 | DIF Outputs  |

**Table 15. SMBus Addressing**

| Pin    | SMBus  |         |  |

|--------|--------|---------|--|

| SMB_A1 | SMB_A0 | Address |  |

| 0      | 0      | D8      |  |

| 0      | М      | DA      |  |

| 0      | 1      | DE      |  |

| М      | 0      | C2      |  |

| М      | М      | C4      |  |

| М      | 1      | C6      |  |

| 1      | 0      | CA      |  |

| 1      | М      | CC      |  |

| 1      | 1      | CE      |  |

### 2.1. CLK IN, CLK IN

The differential input clock is expected to be sourced from a clock synthesizer or PCH.

### 2.2. 100M\_133M—Frequency Selection

The Si53019-A02A is optimized for lowest phase jitter performance at operating frequencies of 100 and 133 MHz. 100M\_133M is a hardware input pin, which programs the appropriate output frequency of the differential outputs. Note that the CLK\_IN frequency must be equal to the CLK\_OUT frequency; meaning Si53019-A02A is operated in 1:1 mode only. Frequency selection can be enabled by the 100M\_133M hardware pin. An external pull-up or pull-down resistor is attached to this pin to select the input/output frequency. The functionality is summarized in Table 16.

**Table 16. Frequency Program Table**

| 100M_133M | Optimized Frequency (DIF_IN = DIF_x) |

|-----------|--------------------------------------|

| 0         | 133.33 MHz                           |

| 1         | 100.00 MHz                           |

Note: All differential outputs transition from 100 to 133 MHz or from 133 to 100 MHz in a glitch free manner.

### 2.3. SA\_0, SA\_1—Address Selection

SA\_0 and SA\_1 are tri-level hardware pins, which program the appropriate address for the Si53019-A02A. The two tri-level input pins can configure the device to nine different addresses.

**Table 17. SMBUS Address Table**

| SA_1 | SA_0 | SMBUS Address |

|------|------|---------------|

| L    | L    | D8            |

| L    | М    | DA            |

| L    | Н    | DE            |

| М    | L    | C2            |

| М    | М    | C4            |

| М    | Н    | C6            |

| Н    | L    | CA            |

| Н    | М    | CC            |

| Н    | Н    | CE            |

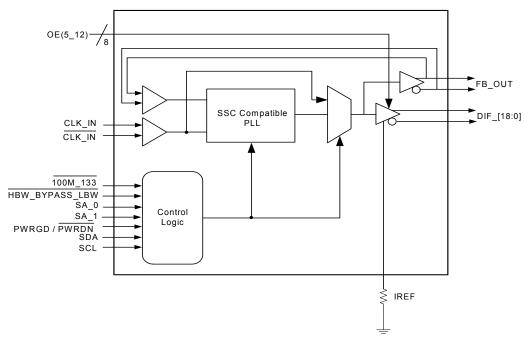

### 2.4. CKPWRGD/PWRDN

CKPWRGD is asserted high and deasserted low. Deassertion of PWRGD (pulling the signal low) is equivalent to indicating a power-down condition. CKPWRGD (assertion) is used by the Si53019-A02A to sample initial configurations, such as frequency select condition and SA selections. After CKPWRGD has been asserted high for the first time, the pin becomes a PWRDN (Power Down) pin that can be used to shut off all clocks cleanly and instruct the device to invoke power-saving mode. PWRDN is a completely asynchronous active low input. When entering power-saving mode, PWRDN should be asserted low prior to shutting off the input clock or power to ensure all clocks shut down in a glitch free manner. When PWRDN is asserted low, all clocks will be disabled prior to turning off the VCO. When PWRDN is deasserted high, all clocks will start and stop without any abnormal behavior and will meet all AC and DC parameters.

**Note:** The assertion and deassertion of PWRDN is absolutely asynchronous.

**Warning:** Disabling of the CLK\_IN input clock prior to assertion of PWRDN is an undefined mode and not recommended. Operation in this mode may result in glitches, excessive frequency shifting, etc.

Table 18. CKPWRGD/PWRDN Functionality

| CKPWRGD/<br>PWRDN | DIF_IN/<br>DINF_IN# | SMBus<br>EN bit | OE# Pin | DIF(5:12)<br>DIF(5:12)# | Other DIF/<br>DIF# | FBOUT_NC/<br>FBOUT_NC# | PLL State |

|-------------------|---------------------|-----------------|---------|-------------------------|--------------------|------------------------|-----------|

| 0                 | Х                   | Х               | Х       | Hi-Z <sup>*</sup>       | Hi-Z <sup>*</sup>  | Hi-Z <sup>*</sup>      | OFF       |

| 1                 | Running             | 0               | Х       | Hi-Z*                   | Hi-Z <sup>*</sup>  | Running                | ON        |

|                   |                     | 1               | 0       | Running                 | Running            | Running                | ON        |

|                   |                     | 1               | 1       | Hi-Z*                   | Running            | Running                | ON        |

\*Note: Due to external pull down resistors, Hi-Z results in Low/Low on the True/Complement outputs.

#### 2.4.1. PWRDN Assertion

When  $\overline{\text{PWRDN}}$  is sampled low by two consecutive rising edges of  $\overline{\text{DIF}}$ , all differential outputs must be held Tristate/Tri-state on the next  $\overline{\text{DIF}}$  high-to-low transition. The device will put all outputs in high impedance mode, and all outputs will be pulled low by the external terminating resistors.

Figure 2. PWRDN Assertion

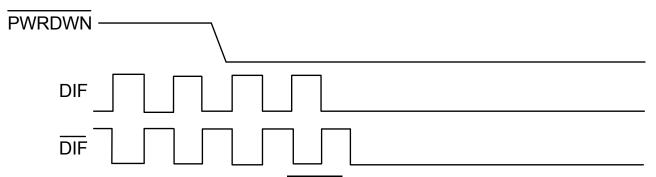

#### 2.4.2. CKPWRGD Assertion

The power-up latency is to be less than 1.8 ms. This is the time from a valid CLK\_IN input clock and the assertion of the PWRGD signal to the time that stable clocks are output from the device (PLL locked). All differential outputs stopped in a Tri-state/Tri-state condition resulting from power down must be driven high in less than 300 µs of PWRDN deassertion to a voltage greater than 200 mV.

Figure 3. PWRDG Assertion (Pwrdown—Deassertion)

### 2.5. HBW\_BYPASS\_LBW

The HBW\_BYPASS\_LBW pin is a tri-level function input pin (refer to Table 1 for VIL\_Tri, VIM\_Tri, and VIH\_Tri signal levels). It is used to select between PLL high-bandwidth, PLL bypass mode, or PLL low-bandwidth mode. In PLL bypass mode, the input clock is passed directly to the output stage, which may result in up to 50 ps of additive cycle-to-cycle jitter (50 ps + input jitter) on the differential outputs. In the case of PLL mode, the input clock is passed through a PLL to reduce high-frequency jitter. The PLL HBW, BYPASS, and PLL LBW modes may be selected by asserting the HBW\_BYPASS\_LBW input pin to the appropriate level described in Table 19.

| HBW_BYPASS_LBW Pin | Mode   | Byte 0, Bit 7 | Byte 0, Bit 6 |

|--------------------|--------|---------------|---------------|

| L                  | LBW    | 0             | 0             |

| M                  | BYPASS | 0             | 1             |

| Н                  | HBW    | 1             | 1             |

Table 19. PLL Bandwidth and Readback Table

The Si53019-A02A has the ability to override the latch value of the PLL operating mode from hardware strap Pin 5 via the use of Byte 0 and Bits 2 and 1. Byte 0 Bit 3 must be set to 1 to allow the user to change Bits 2 and 1, affecting the PLL. Bits 7 and 6 will always read back the original latched value. A warm reset of the system will have to be accomplished if the user changes these bits.

### 2.6. Miscellaneous Requirements

18

**Data Transfer Rate:** 100 kbps (standard mode) is the base functionality required. Fast mode (400 kbps) functionality is optional.

**Logic Levels:** SMBus logic levels are based on a percentage of  $V_{DD}$  for the controller and other devices on the bus. Assume all devices are based on a 3.3 V supply.

**Clock Stretching:** The clock buffer must not hold/stretch the SCL or SDA lines low for more than 10 ms. Clock stretching is discouraged and should only be used as a last resort. Stretching the clock/data lines for longer than this time puts the device in an error/time-out mode and may not be supported in all platforms. It is assumed that all data transfers can be completed as specified without the use of clock/data stretching.

General Call: It is assumed that the clock buffer will not have to respond to the "general call."

**Electrical Characteristics:** All electrical characteristics must meet the standard mode specifications found in Section 3 of the SMBus 2.0 specification.

**Pull-Up Resistors:** Any internal resistor pull-ups on the SDATA and SCLK inputs must be stated in the individual datasheet. The use of internal pull-ups on these pins of below 100 K is discouraged. Assume that the board designer will use a single external pull-up resistor for each line and that these values are in the 5–6 k $\Omega$  range. Assume one SMBus device per DIMM (serial presence detect), one SMBus controller, one clock buffer, one clock driver plus one/two more SMBus devices on the platform for capacitive loading purposes.

**Input Glitch Filters:** Only fast mode SMBus devices require input glitch filters to suppress bus noise. The clock buffer is specified as a standard mode device and is not required to support this feature. However, it is considered a good design practice to include the filters.

**PWRDN:** If a clock buffer is placed in PWRDN mode, the SDATA and SCLK inputs must be Tri-stated and the device must retain all programming information. I<sub>DD</sub> current due to the SMBus circuitry must be characterized and in the data sheet.

### 3. Test and Measurement Setup

### 3.1. Input Edge

Input edge rate is based on single-ended measurement. This is the minimum input edge rate at which the Si53019-A02A is guaranteed to meet all performance specifications.

| <b>Table</b> | 20. | Input | Edge | Rate |

|--------------|-----|-------|------|------|

|--------------|-----|-------|------|------|

| Frequency | Min  | Max | Unit |

|-----------|------|-----|------|

| 100 MHz   | 0.35 | N/A | V/ns |

| 133 MHz   | 0.35 | N/A | V/ns |

#### 3.1.1. Measurement Points for Differential

Figure 4. Measurement Points for Rise Time and Fall Time

Figure 5. Single-ended Measurement Points for  $V_{ovs}$ ,  $V_{uds}$ ,  $V_{rb}$

Figure 6. Differential (CLOCK-CLOCK) Measurement Points (Tperiod, Duty Cycle, Jitter)

### 3.2. Termination of Differential Outputs

All differential outputs are to be tested into a  $100\,\Omega$  or  $85\,\Omega$  differential impedance transmission line. Source terminated clocks have some inherent limitations as to the maximum trace length and frequencies that can be supported. For CPU outputs, a maximum trace length of 10" and a maximum of 200 MHz are assumed. For SRC clocks, a maximum trace length of 16" and maximum frequency of 100 MHz is assumed. For frequencies beyond 200 MHz, trace lengths must be restricted to avoid signal integrity problems.

| Clock                                 | IREF ( $\Omega$ ) | Board Trace Impedance | Rs             | Rp           | Unit |

|---------------------------------------|-------------------|-----------------------|----------------|--------------|------|

| DIFF Clocks—50 $\Omega$ configuration | 475               | 100                   | 33 <u>+</u> 5% | 50           | Ω    |

| DIFF Clocks—43 Ω configuration        | 412               | 85                    | 27 <u>+</u> 5% | 42.2 or 43.2 | Ω    |

**Table 21. Differential Output Termination**

#### 3.2.1. Termination of Differential Current Mode HCSL Outputs

Figure 7. 0.7 V Configuration Test Load Board Termination

### 4. Control Registers

### 4.1. Byte Read/Write

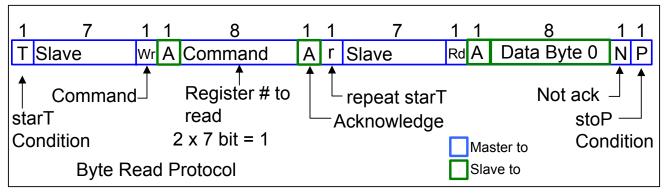

Reading or writing a register in an SMBus slave device in byte mode always involves specifying the register number.

#### 4.1.1. Byte Read

The standard byte read is shown in Figure 8. It is an extension of the byte write. The write start condition is repeated; then the slave device starts sending data, and the master acknowledges it until the last byte is sent. The master terminates the transfer with a NAK, then a stop condition. For byte operation, the  $2 \times 7$ th bit of the command byte must be set. For block operations, the  $2 \times 7$ th bit must be reset. If the bit is not set, the next byte must be the byte transfer count.

Figure 8. Byte Read Protocol

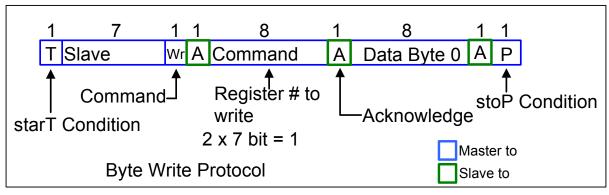

#### 4.1.2. Byte Write

Figure 9 illustrates a simple, typical byte write. For byte operation, the 2 x 7th bit of the command byte must be set. For block operations, the 2 x 7th bit must be reset. If the bit is not set, the next byte must be the byte transfer count. The count can be between 1 and 32. It is not allowed to be zero or to exceed 32.

Figure 9. Byte Write Protocol

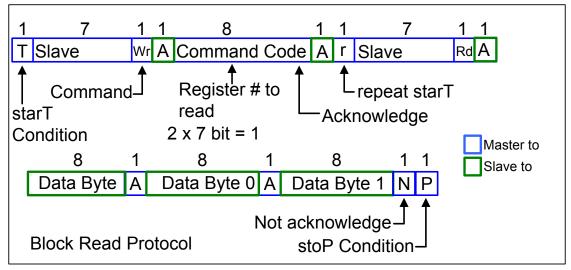

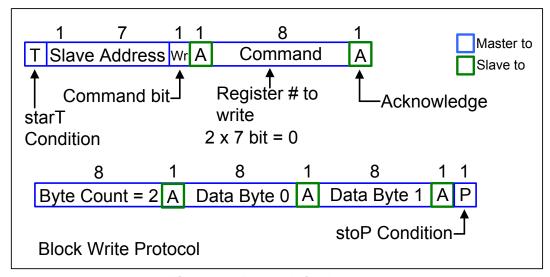

#### 4.2. Block Read/Write

#### 4.2.1. Block Read

After the slave address is sent with the R/W condition bit set, the command byte is sent with the MSB = 0. The slave acknowledges the register index in the command byte. The master sends a repeat start function. After the slave acknowledges this, the slave sends the number of bytes it wants to transfer (> 0 and < 33). The master acknowledges each byte except the last and sends a stop function.

Figure 10. Block Read Protocol

#### 4.2.2. Block Write

After the slave address is sent with the R/W condition bit not set, the command byte is sent with the MSB = 0. The lower seven bits indicate the register at which to start the transfer. If the command byte is 00h, the slave device will be compatible with existing block mode slave devices. The next byte of a write must be the count of bytes that the master will transfer to the slave device. The byte count must be greater than zero and less than 33. Following this byte are the data bytes to be transferred to the slave device. The slave device always acknowledges each byte received. The transfer is terminated after the slave sends the ACK and the master sends a stop function.

Figure 11. Block Write Protocol

### 4.3. Control Registers

Table 22. Byte 0: PLL Mode and Frequency Select Register

| Bit | Pin#       | Name                 | Control Function                       | 0                                       | 1      | Туре  | Default |

|-----|------------|----------------------|----------------------------------------|-----------------------------------------|--------|-------|---------|

| 0   | 4          | 100M_133M#           | Frequency Select Read-<br>back         | 133MHz                                  | 100MHz | R     | Latch   |

| 1   | 1 reserved |                      |                                        |                                         |        |       |         |

| 2   |            |                      | reserved                               |                                         |        |       |         |

| 3   | 67/66      | Output Enable DIF 16 | Output control, over-<br>rides OE# pin |                                         |        |       | 1       |

| 4   | 70/69      | Output Enable DIF 17 | Output control, over-<br>rides OE# pin |                                         |        |       | 1       |

| 5   | 72/71      | Output Enable DIF 18 | Output control, over-<br>rides OE# pin |                                         |        |       | 1       |

| 6   | 5          | PLL Mode 0           | PLL operating mode readback 0          | See PLL operating R mode readback table |        | Latch |         |

| 7   | 5          | PLL Mode1            | PLL operating mode readback 1          |                                         |        | R     | Latch   |

Table 23. Byte 1: Output Enable Control Register

| Bit | Pin#  | Description         | Control Functions                    | If Bit = 0 | If Bit = 1 | Туре | Default |

|-----|-------|---------------------|--------------------------------------|------------|------------|------|---------|

| 0   | 19/20 | Output Enable DIF 0 | Output control, overrides OE# pin    | Hi-Z       | Enabled    | RW   | 1       |

| 1   | 22/23 | Output Enable DIF 1 | Output control,<br>overrides OE# pin |            | RW         | 1    |         |

| 2   | 24/25 | Output Enable DIF 2 | Output control, overrides OE# pin    |            |            | RW   | 1       |

| 3   | 27/28 | Output Enable DIF 3 | Output control, overrides OE# pin    |            |            | RW   | 1       |

| 4   | 29/30 | Output Enable DIF 4 | Output control, overrides OE# pin    |            |            | RW   | 1       |

| 5   | 32/33 | Output Enable DIF 5 | Output control, overrides OE# pin    |            |            | RW   | 1       |

| 6   | 35/36 | Output Enable DIF 6 | Output control, overrides OE# pin    |            |            | RW   | 1       |

| 7   | 39/38 | Output Enable DIF 7 | Output control, overrides OE# pin    |            |            | RW   | 1       |

Table 24. Byte 2: Output Enable Control Register

| Bit | Pin#  | Description          | Control Function                  | If Bit = 0 | If Bit = 1 | Туре | Default |

|-----|-------|----------------------|-----------------------------------|------------|------------|------|---------|

| 0   | 42/41 | Output Enable DIF 8  | Output control, overrides OE# pin | Hi-Z       | Enabled    | RW   | 1       |

| 1   | 47/46 | Output Enable DIF 9  | Output control, overrides OE# pin |            |            | RW   | 1       |

| 2   | 50/49 | Output Enable DIF 10 | Output control, overrides OE# pin |            |            | RW   | 1       |

| 3   | 53/52 | Output Enable DIF 11 | Output control, overrides OE# pin |            |            | RW   | 1       |

| 4   | 56/55 | Output Enable DIF 12 | Output control, overrides OE# pin |            |            | RW   | 1       |

| 5   | 60/59 | Output Enable DIF 13 | Output control, overrides OE# pin |            |            | RW   | 1       |

| 6   | 62/61 | Output Enable DIF 14 | Output control, overrides OE# pin |            |            | RW   | 1       |

| 7   | 65/64 | Output Enable DIF 15 | Output control, overrides OE# pin |            |            | RW   | 1       |

Table 25. Byte 3: Output Enable Pin Status Readback Register

| Bit | Pin# | Description | Control Function           | If Bit = 0  | If Bit = 1      | Туре | Default      |

|-----|------|-------------|----------------------------|-------------|-----------------|------|--------------|

| 0   | 34   | OE_RB5      | Real time readback of OE5  | OE# pin Low | OE# pin<br>High | R    | Real<br>Time |

| 1   | 37   | OE_RB6      | Real time readback of OE6  |             |                 | R    | Real<br>Time |

| 2   | 40   | OE_RB7      | Real time readback of OE7  |             |                 | R    | Real<br>Time |

| 3   | 43   | OE_RB8      | Real time readback of OE8  |             |                 | R    | Real<br>Time |

| 4   | 48   | OE_RB9      | Real time readback of OE9  |             |                 | R    | Real<br>Time |

| 5   | 51   | OE_RB10     | Real time readback of OE10 |             |                 | R    | Real<br>Time |

| 6   | 54   | OE_RB11     | Real time readback of OE11 |             |                 | R    | Real<br>Time |

| 7   | 57   | OE_RB12     | Real time readback of OE12 |             |                 | R    | Real<br>Time |

SILICON LARS

Table 26. Byte 4: Reserved Control Register

| Bit | Pin# | Description | Control Function | If Bit = 0 | If Bit = 1 | Туре | Default |

|-----|------|-------------|------------------|------------|------------|------|---------|

| 0   |      |             | Reserved         |            |            |      |         |

| 1   |      |             | Reserved         |            |            |      | 0       |

| 2   |      |             | Reserved         |            |            |      | 0       |

| 3   |      |             | Reserved         |            |            |      | 0       |

| 4   |      |             | Reserved         |            |            |      | 0       |

| 5   |      |             | Reserved         |            |            |      | 0       |

| 6   |      | Reserved    |                  |            |            | 0    |         |

| 7   |      |             | Reserved         |            |            |      | 0       |

### Table 27. Byte 5: Vendor/Revision Identification Control Register

| Bit | Pin# | Description         | Control Function | If Bit = 0   | If Bit = 1 | Туре | Default |

|-----|------|---------------------|------------------|--------------|------------|------|---------|

| 0   | _    | Vendor ID Bit 0     | Vendor ID        |              | R          | 1    |         |

| 1   | _    | Vendor ID Bit 1     |                  |              |            | R    | 0       |

| 2   | _    | Vendor ID Bit 2     |                  |              |            | R    | 0       |

| 3   | _    | Vendor ID Bit 3     |                  |              |            | R    | 0       |

| 4   | _    | Revision Code Bit 0 | Revision ID      | -A01A = 0001 |            | R    | Х       |

| 5   | _    | Revision Code Bit 1 |                  | -A02A        | = 0010     | R    | Х       |

| 6   | _    | Revision Code Bit 2 |                  |              |            | R    | Х       |

| 7   | _    | Revision Code Bit 3 |                  |              |            | R    | Х       |

Table 28. Byte 6: Device ID Control Register

| Bit | Pin# | Description | Control Function | If Bit = 0 | If Bit = 1 | Туре | Default |

|-----|------|-------------|------------------|------------|------------|------|---------|

| 0   | _    | Device ID 0 |                  |            |            | R    | 1       |

| 1   | _    | Device ID 1 |                  |            |            | R    | 1       |

| 2   | _    | Device      | Device ID 2      |            |            | R    | 0       |

| 3   | _    | Device ID 3 |                  |            |            | R    | 1       |

| 4   | _    | Device      |                  |            | R          | 1    |         |

| 5   | _    | Device ID 5 |                  |            |            | R    | 0       |

| 6   | _    | Device ID 6 |                  |            |            | R    | 1       |

| 7   | _    | Device ID   | 7 (MSB)          |            |            | R    | 1       |

## Si53019-A02A

Table 29. Byte 7: Byte Count Register

| Bit | Pin #    | Description | Control Functions                            | If Bit = 0                                       | If Bit = 1   | Туре | Default |

|-----|----------|-------------|----------------------------------------------|--------------------------------------------------|--------------|------|---------|

| 0   | _        | BC0         | Writing to this register                     |                                                  | ue is 8 hex, | RW   | 0       |

| 1   | _        | BC1         | configures how many bytes will be read back. | so 9 bytes (0 to 8) will be read back by default |              | RW   | 0       |

| 2   | _        | BC2         |                                              |                                                  |              | RW   | 0       |

| 3   | _        | BC3         |                                              |                                                  |              | RW   | 1       |

| 4   | _        | BC4         |                                              |                                                  |              | RW   | 0       |

| 5   | Reserved |             |                                              |                                                  |              |      |         |

| 6   |          | Reserved    |                                              |                                                  |              |      |         |

| 7   |          |             | Reserved                                     |                                                  |              |      | 0       |

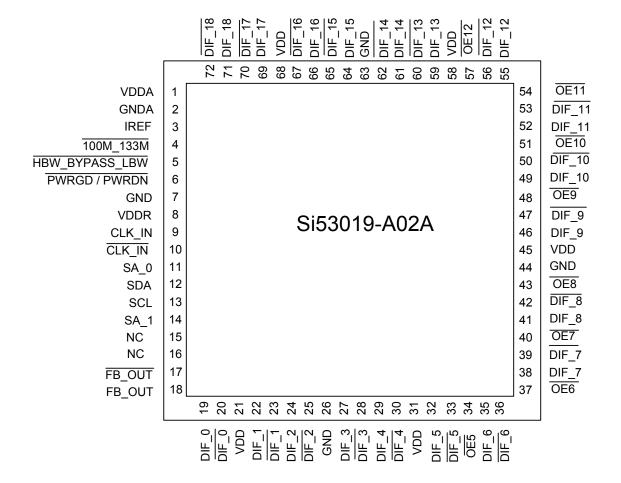

### 5. Pin Descriptions: 72-Pin QFN

Note: FB\_OUT pins must be identically terminated to the other DIF outputs.

Table 30. Si53019-A02A 72-Pin QFN Descriptions

| Pin # | Name           | Туре   | Description                                                                                                                                                                                                                                                 |

|-------|----------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | VDDA           | 3.3 V  | 3.3 V power supply for PLL.                                                                                                                                                                                                                                 |

| 2     | GNDA           | GND    | Ground for PLL.                                                                                                                                                                                                                                             |

| 3     | IREF           | OUT    | This pin establishes the reference for the differential current mode output pairs. It requires a fixed precision resistor to ground. 475 $\Omega$ is the standard value for 100 $\Omega$ differential impedance. Other impedances require different values. |

| 4     | 100M_133M      | I,SE   | 3.3 V tolerant inputs for input/output frequency selection. An external pull-up or pull-down resistor is attached to this pin to select the input/output frequency.  High = 100 MHz output  Low = 133 MHz output                                            |

| 5     | HBW_BYPASS_LBW | I, SE  | Tri-Level input for selecting the PLL bandwidth or bypass mode. High = High BW mode Med = Bypass mode Low = Low BW mode                                                                                                                                     |

| 6     | PWRGD/PWRDN    | I      | 3.3 V LVTTL input to power up or power down the device.                                                                                                                                                                                                     |

| 7     | GND            | GND    | Ground for outputs.                                                                                                                                                                                                                                         |

| 8     | VDDR           | VDD    | 3.3 V power supply for differential input receiver. This VDDR should be treated as an analog power rail and filtered appropriately.                                                                                                                         |

| 9     | CLK_IN         | I, DIF | 0.7 V Differential True clock input.                                                                                                                                                                                                                        |

| 10    | CLK_IN         | I, DIF | 0.7 V Differential Complementary clock input.                                                                                                                                                                                                               |

| 11    | SA_0           | I,PU   | 3.3 V LVTTL input selecting the address. Tri-level input.                                                                                                                                                                                                   |

| 12    | SDA            | I/O    | Open collector SMBus data.                                                                                                                                                                                                                                  |

| 13    | SCL            | I/O    | SMBus slave clock input.                                                                                                                                                                                                                                    |

| 14    | SA_1           | I,PU   | 3.3 V LVTTL input selecting the address. Tri-level input.                                                                                                                                                                                                   |

| 15    | NC             | _      | Do not connect this pin to anything.                                                                                                                                                                                                                        |

| 16    | NC             | _      | Do not connect this pin to anything.                                                                                                                                                                                                                        |

| 17    | FB_OUT         | I/O    | Complementary differential feedback output, providing the feedback signal to the PLL for synchronization to the input clock.                                                                                                                                |

| 18    | FB_OUT         | I/O    | True differential feedback output, providing the feedback signal to the PLL for synchronization to the input clock.                                                                                                                                         |

| 19    | DIF_0          | O, DIF | 0.7 V Differential TRUE clock output.                                                                                                                                                                                                                       |

| 20    | DIF_0          | O, DIF | 0.7 V Differential Complimentary clock output.                                                                                                                                                                                                              |

| 21    | VDD            | VDD    | Power supply for differential outputs.                                                                                                                                                                                                                      |

| 22    | DIF_1          | O, DIF | 0.7 V Differential TRUE clock output.                                                                                                                                                                                                                       |

| 23    | DIF_1          | O, DIF | 0.7 V Differential Complimentary clock output.                                                                                                                                                                                                              |

Table 30. Si53019-A02A 72-Pin QFN Descriptions

| Pin# | Name   | Туре      | Description                                                                      |

|------|--------|-----------|----------------------------------------------------------------------------------|

| 24   | DIF_2  | O, DIF    | 0.7 V Differential TRUE clock output.                                            |

| 25   | DIF_2  | O, DIF    | 0.7 V Differential Complimentary clock output.                                   |

| 26   | GND    | GND       | Ground for outputs.                                                              |

| 27   | DIF_3  | O, DIF    | 0.7 V Differential TRUE clock output.                                            |

| 28   | DIF_3  | O, DIF    | 0.7 V Differential Complimentary clock output.                                   |

| 29   | DIF_4  | O, DIF    | 0.7 V Differential TRUE clock output.                                            |

| 30   | DIF_4  | O, DIF    | 0.7 V Differential Complimentary clock output.                                   |

| 31   | VDD    | 3.3 V     | 3.3 V power supply                                                               |

| 32   | DIF_5  | O, DIF    | 0.7 V Differential TRUE clock output.                                            |

| 33   | DIF_5  | O, DIF    | 0.7 V Differential Complimentary clock output.                                   |

| 34   | OE5    | IN        | Active low input for enabling DIF pair 5 1 = disable outputs, 0 = enable outputs |

| 35   | DIF_6  | O, DIF    | 0.7 V Differential TRUE clock output.                                            |

| 36   | DIF_6  | O, DIF    | 0.7 V Differential Complimentary clock output.                                   |

| 37   | OE6    | IN        | Active low input for enabling DIF pair 6 1 = disable outputs, 0 = enable outputs |

| 38   | DIF_7  | O, DIF    | 0.7 V Differential TRUE clock output.                                            |

| 39   | DIF_7  | O, DIF    | 0.7 V Differential Complimentary clock output.                                   |

| 40   | OE7    | IN        | Active low input for enabling DIF pair 7 1 = disable outputs, 0 = enable outputs |

| 41   | DIF_8  | O, DIF    | 0.7 V Differential TRUE clock output.                                            |

| 42   | DIF_8  | O, DIF    | 0.7 V Differential Complimentary clock output.                                   |

| 43   | OE8    | IN        | Active low input for enabling DIF pair 8 1 = disable outputs, 0 = enable outputs |

| 44   | GND    | GND       | Ground for outputs.                                                              |

| 45   | VDD    | 3.3 V     | 3.3 V power supply                                                               |

| 46   | DIF_9  | O,<br>DIF | 0.7 V Differential TRUE clock output.                                            |

| 47   | DIF_9  | O,<br>DIF | 0.7 V Differential Complimentary clock output.                                   |

| 48   | OE9    | IN        | Active low input for enabling DIF pair 9 1 = disable outputs, 0 = enable outputs |

| 49   | DIF_10 | O, DIF    | 0.7 V Differential TRUE clock output.                                            |

## Si53019-A02A

Table 30. Si53019-A02A 72-Pin QFN Descriptions

| Pin# | Name   | Туре   | Description                                                                          |

|------|--------|--------|--------------------------------------------------------------------------------------|

| 50   | DIF_10 | O, DIF | 0.7 V Differential Complimentary clock output.                                       |

| 51   | OE10   | IN     | Active low input for enabling DIF pair 10<br>1 = disable outputs, 0 = enable outputs |

| 52   | DIF_11 | O, DIF | 0.7 V Differential TRUE clock output.                                                |

| 53   | DIF_11 | O, DIF | 0.7 V Differential Complimentary clock output.                                       |

| 54   | OE11   | IN     | Active low input for enabling DIF pair 11<br>1 = disable outputs, 0 = enable outputs |

| 55   | DIF_12 | O, DIF | 0.7 V Differential TRUE clock output.                                                |

| 56   | DIF_12 | O, DIF | 0.7 V Differential Complimentary clock output.                                       |

| 57   | OE12   | IN     | Active low input for enabling DIF pair 12<br>1 = disable outputs, 0 = enable outputs |

| 58   | VDD    | 3.3 V  | 3.3 V power supply                                                                   |

| 59   | DIF_13 | O, DIF | 0.7 V Differential TRUE clock output.                                                |

| 60   | DIF_13 | O, DIF | 0.7 V Differential Complimentary clock output.                                       |

| 61   | DIF_14 | O, DIF | 0.7 V Differential TRUE clock output.                                                |

| 62   | DIF_14 | O, DIF | 0.7 V Differential Complimentary clock output.                                       |

| 63   | GND    | GND    | Ground for outputs.                                                                  |

| 64   | DIF_15 | O, DIF | 0.7 V Differential TRUE clock output.                                                |

| 65   | DIF_15 | O, DIF | 0.7 V Differential Complimentary clock output.                                       |

| 66   | DIF_16 | O, DIF | 0.7 V Differential TRUE clock output.                                                |

| 67   | DIF_16 | O, DIF | 0.7 V Differential Complimentary clock output.                                       |

| 68   | VDD    | 3.3 V  | 3.3 V power supply                                                                   |

| 69   | DIF_17 | O, DIF | 0.7 V Differential TRUE clock output.                                                |

| 70   | DIF_17 | O, DIF | 0.7 V Differential Complimentary clock output.                                       |

| 71   | DIF_18 | O, DIF | 0.7 V Differential TRUE clock output.                                                |

| 72   | DIF_18 | O, DIF | 0.7 V Differential Complimentary clock output.                                       |

| 73   | GND    | GND    | Ground for outputs.                                                                  |

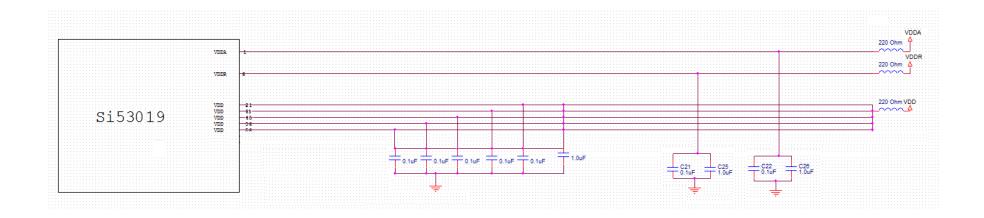

## 6. Power Filtering Example

### 6.1. Ferrite Bead Power Filtering

Recommended ferrite bead filtering equivalent to the following:

Figure 12. Schematic Example of the Si53019-A02A Power Filtering

## Si53019-A02A

## 7. Ordering Guide

| Part Number     | Package Type             | Temperature            |  |  |

|-----------------|--------------------------|------------------------|--|--|

| Lead-free       |                          |                        |  |  |

| Si53019-A02AGM  | 72-pin QFN               | Extended, –40 to 85 °C |  |  |

| Si53019-A02AGMR | 72-pin QFN—Tape and Reel | Extended, –40 to 85 °C |  |  |

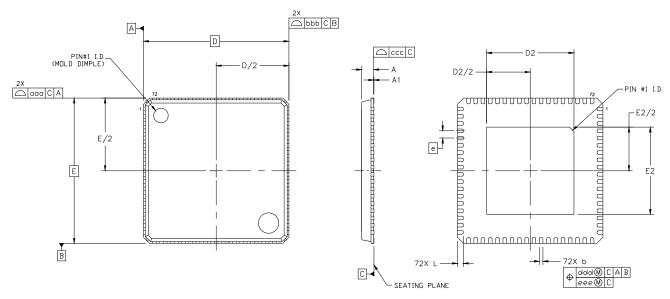

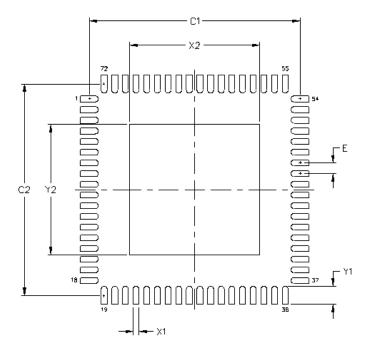

### 8. Package Outline

Figure 13 illustrates the package details for the Si53019-A02A. Table 31 lists the values for the dimensions shown in the illustration.

Figure 13. 72-Pin Quad Flat No Lead (QFN) Package

Table 31. Package Diagram Dimensions 1,2,3,4

| Dimension | Min        | Nom        | Max  | Dimension | Min  | Nom  | Max  |

|-----------|------------|------------|------|-----------|------|------|------|

| А         | 0.80       | 0.85       | 0.90 | E2        | 5.90 | 6.00 | 6.10 |

| A1        | 0.00       | 0.02       | 0.05 | L         | 0.30 | 0.40 | 0.50 |

| b         | 0.18       | 0.25       | 0.30 | aaa       | 0.10 |      |      |

| D         |            | 10.00 BSC. |      | bbb       | 0.10 |      |      |

| D2        | 5.90       | 6.00       | 6.10 | ccc       | 0.08 |      |      |

| е         | 0.50 BSC.  |            |      | ddd       | 0.10 |      |      |

| E         | 10.00 BSC. |            | eee  | 0.05      |      |      |      |

#### Notes:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC outline MO-220.

- **4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

### 9. Land Pattern

Figure 14 illustrates the package details for the Si53019-A02A. Table 32 lists the values for the dimensions shown in the illustration.

Figure 14. 72-Pin Quad Flat No Lead (QFN) Package

Table 32. Package Diagram Dimensions 1,2,3,4

| Dimension | mm   |

|-----------|------|

| C1        | 9.90 |

| C2        | 9.90 |

| E         | 0.50 |

| X1        | 0.30 |

| Y1        | 0.85 |

| X2        | 6.10 |

| Y2        | 6.10 |

#### Notes:

#### General

- 1. All dimensions shown are in millimeters (mm).

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

- **3.** All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05mm.

#### Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60?m minimum, all the way around the pad.

### Stencil Design

- 1. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125mm (5 mils).

- 3. The ratio of stencil aperture to land pad size should be 1:1 for all pads.

- **4.** A 3x3 array of 1.45mm square openings on a 2.00mm pitch should be used for the center ground pad.

#### **Card Assembly**

- **1.** A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## Si53019-A02A

### **DOCUMENT CHANGE LIST**

### **Revision 0.9 to Revision 1.0**

■ Corrected specs in Table 7, "Phase Jitter," on page 10.

### **Revision 1.0 to Revision 1.1**

- Updated Features on page 1.

- Updated Description on page 1.

- Updated specs in Table 7, "Phase Jitter," on page 10.

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific written consent of Silicon Laboratories. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**