Now

**TPS23881**

SLVSF02A -MARCH 2019-REVISED MAY 2019

# TPS23881 High-Power, 8-Channel, Power-Over-Ethernet PSE With 200-m $\Omega$ R<sub>SENSE</sub>

### **Features**

- IEEE 802.bt PSE solution for PoE applications

- Eight independent PSE channels

- Resistor selectable Autonomous operation

- Compatible with TI's FirmPSE system firmware

- SRAM Programmable memory

- Programmable power limiting accuracy ±2.5%

- 200-mΩ Current sense resistor

- Legacy PD capacitance measurement

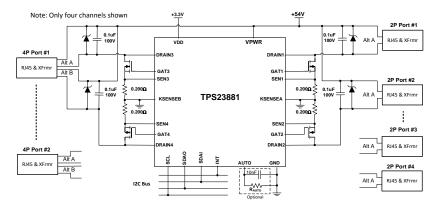

- Selectable 2-pair or 4-pair port power allocations

- 15.4 W, 30 W, 45 W, 60 W, 75 W or 90 W

- Single and dual signature PD compatibility

- Dedicated 14-bit integrating current ADC per port

- Noise immune MPS for DC disconnect

- 2% Current sensing accuracy

- 1- and 3-Bit fast port shutdown input

- Auto-class discovery and power measurement

- Inrush and operational foldback protection

- Port re-mapping

- Flexible processor controlled operating modes

- Auto, semi auto and manual / diagnostic

- Per Port voltage monitoring and telemetry

- -40°C to +125°C Temperature operation

- Ultra Low Alpha (ULA) packaging (TPS23881A)

# **Applications**

- Enterprise and SoHO switches and routers

- Connected ceiling LED lighting switches

- PoE Pass-through power modules

- Network Video Recorders (NVRs)

- Wireless backhaul and small cell networking

# 3 Description

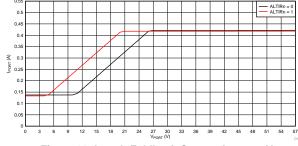

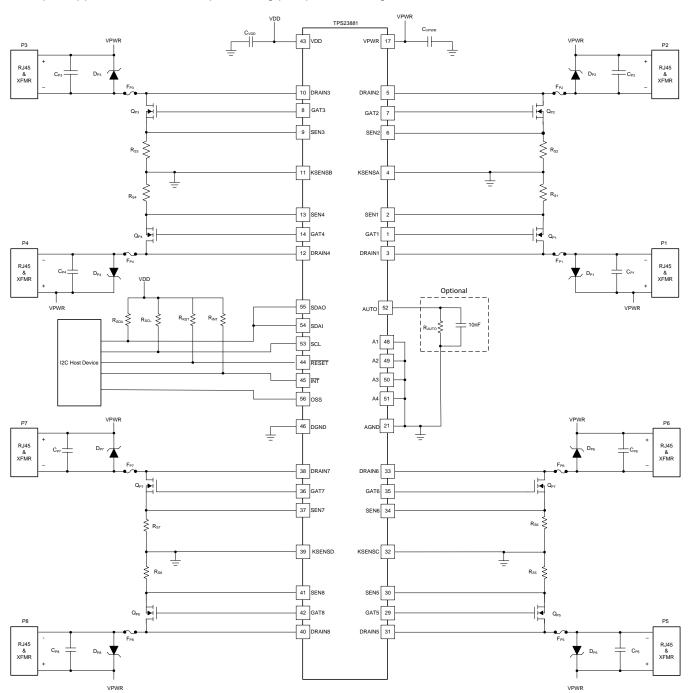

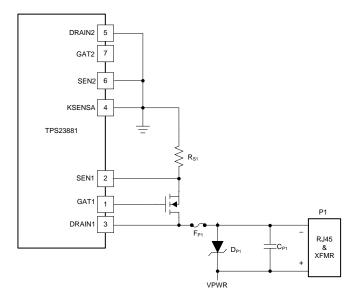

The TPS23881 is an 8-channel power sourcing equipment (PSE) controller engineered to insert power onto Ethernet cables in accordance with the IEEE 802.3bt standard. The eight individual power channels can be configured in any combination of 2-Pair (1-channel) or 4-Pair (2-channels) PoE Ports. The PSE controller can detect powered devices (PDs) that have a valid signature, determine the power requirements of the devices according to their classification, and apply power.

Support &

Community

The TPS23881 improves on the TPS23880 with reduced current sense resistors, more accurate power programable limiting, capacitance measurement, and the ability to operate from ROM (see Device Comparison Table). The TPS23881 is also compatible with TI's *FirmPSE* system firmware, which provides a fully configurable solution for controlling multiple TP\$23881 devices in systems offering up to 48-ports of 4-pair PoE power.

Programmable SRAM enables in-field firmware upgradability over I<sup>2</sup>C to ensure interoperability with the latest PoE enabled devices. Dedicated per port ADCs provide continuous port current monitoring and perform parallel ability to classification measurements for faster port turn on times. A ±2.5% accurate programmable port power limit provides the ability to expand the maximum power sourced from 90 W to upwards of 125 W. The 200 m $\Omega$  current sense resistor and external FET architecture allow designs to balance size, efficiency, thermal, and solution cost requirements.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| TPS23881    | VQFN (56) | 8.00 mm × 8.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

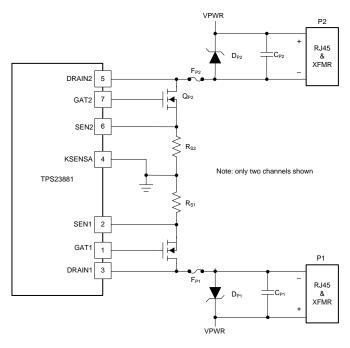

#### Simplified Schematic

# **Table of Contents**

| 1 | Features 1                           |    | 9.5 Programming                                  | 25  |

|---|--------------------------------------|----|--------------------------------------------------|-----|

| 2 | Applications 1                       |    | 9.6 Register Maps                                |     |

| 3 | Description 1                        | 10 | Application and Implementation                   | 104 |

| 4 | Revision History2                    |    | 10.1 Application Information                     | 104 |

| 5 | Device Comparison Table3             |    | 10.2 Typical Application                         | 106 |

| 6 | Pin Configuration and Functions      | 11 | Power Supply Recommendations                     | 111 |

| • | 6.1 Detailed Pin Description         |    | 11.1 VDD                                         | 111 |

| 7 | Specifications6                      |    | 11.2 VPWR                                        | 111 |

| • | 7.1 Absolute Maximum Ratings         | 12 | Layout                                           | 112 |

|   | <u> </u>                             |    | 12.1 Layout Guidelines                           |     |

|   | · · · · · · · · · · · · · · · ·      |    | 12.2 Layout Example                              |     |

|   | 7.3 Recommended Operating Conditions | 13 | Device and Documentation Support                 |     |

|   | 7.4 Thermal Information              |    | 13.1 Documentation Support                       |     |

|   | 7.5 Electrical Characteristics7      |    | 13.2 Receiving Notification of Documentation     |     |

| 8 | Parameter Measurement Information 13 |    | Updates                                          | 114 |

|   | 8.1 Timing Diagrams                  |    | 13.3 Community Resources                         |     |

| 9 | Detailed Description 17              |    | 13.4 Trademarks                                  |     |

|   | 9.1 Overview 17                      |    |                                                  |     |

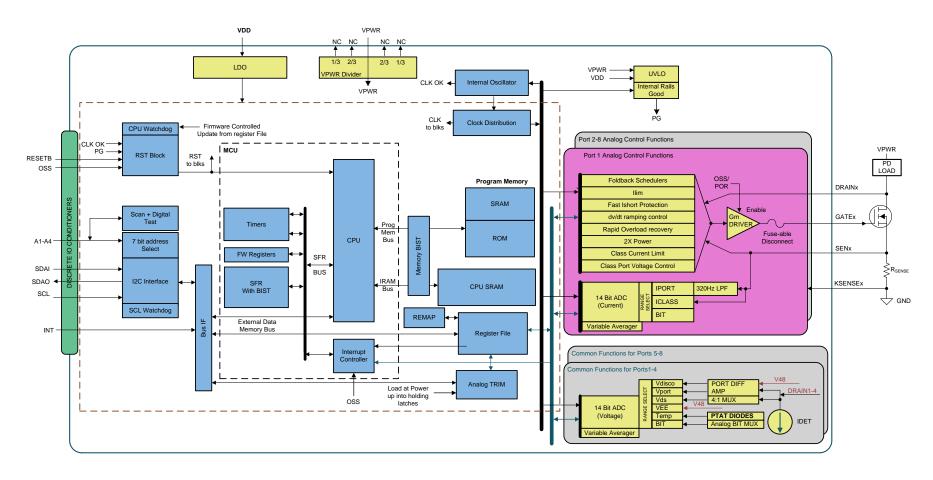

|   | 9.2 Functional Block Diagram         |    | 13.5 Electrostatic Discharge Caution             |     |

|   | 9.3 Feature Description21            |    | 13.6 Glossary                                    | 112 |

|   | 9.4 Device Functional Modes          | 14 | Mechanical, Packaging, and Orderable Information | 114 |

# 4 Revision History

| Cł | Changes from Original (March 2019) to Revision A Pag |   |  |  |

|----|------------------------------------------------------|---|--|--|

| •  | First public release of the APL data sheet           | 1 |  |  |

Submit Documentation Feedback

# 5 Device Comparison Table

Table 1 summarizes the primary differences between the TPS23880 and TPS23881 devices.

Table 1. TPS23880 vs TPS23881

| KEY FEATURES                                        | TPS23880                       | TPS23881                   |

|-----------------------------------------------------|--------------------------------|----------------------------|

| R <sub>SENSE</sub>                                  | 0.255 Ω                        | 0.200 Ω                    |

| Resistor selectable Autonomous operation            | No                             | Yes                        |

| 2-Pair / 4-Pair P <sub>CUT</sub> programable ranges | 0.5 W to 54 W / 0.5 W to 108 W | 2 W to 65 W / 4 W to 127 W |

| 90+ W 4-pair P <sub>CUT</sub> accuracy              | +/- 3.0 %                      | +/- 2.5 %                  |

| Channel capacitance measurement range               | N/A                            | 1 μF to 12 μF              |

| ULA Packaging                                       | No                             | Yes (TPS23881A)            |

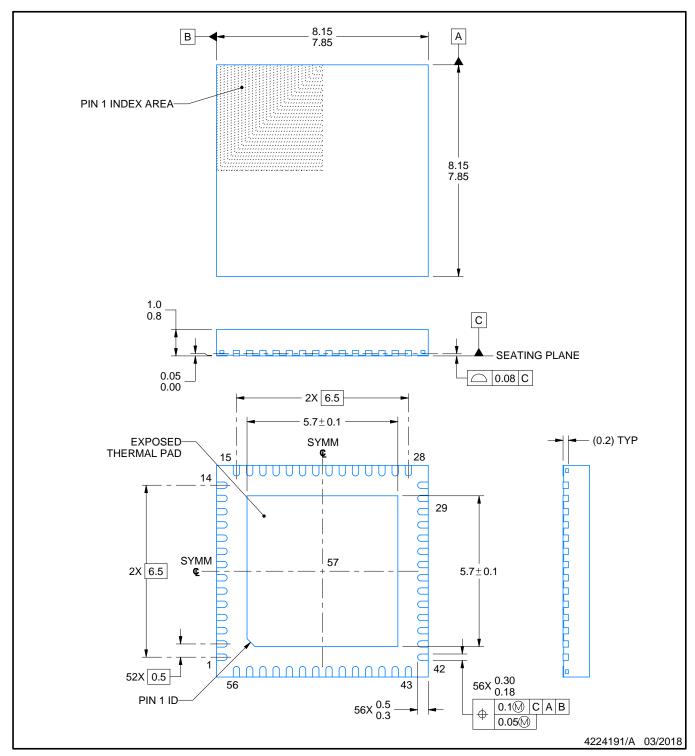

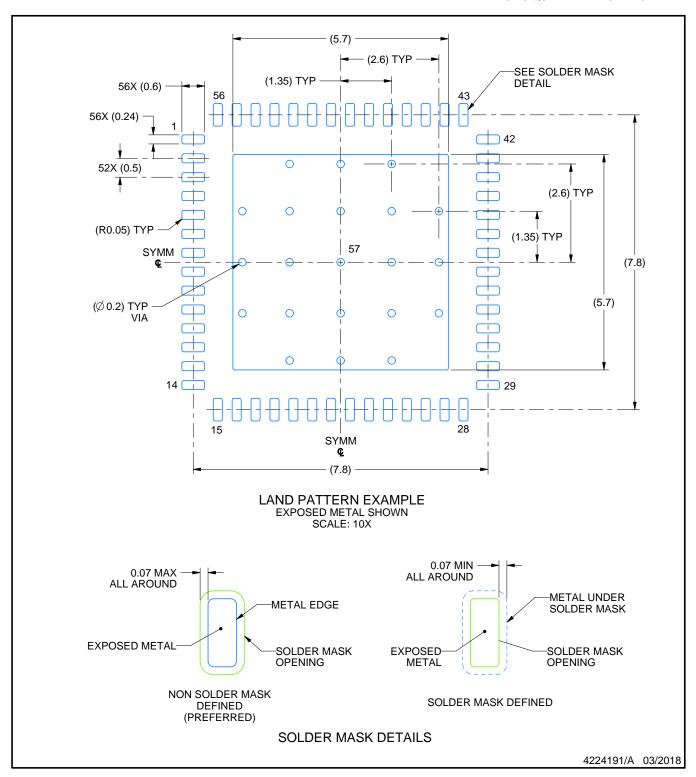

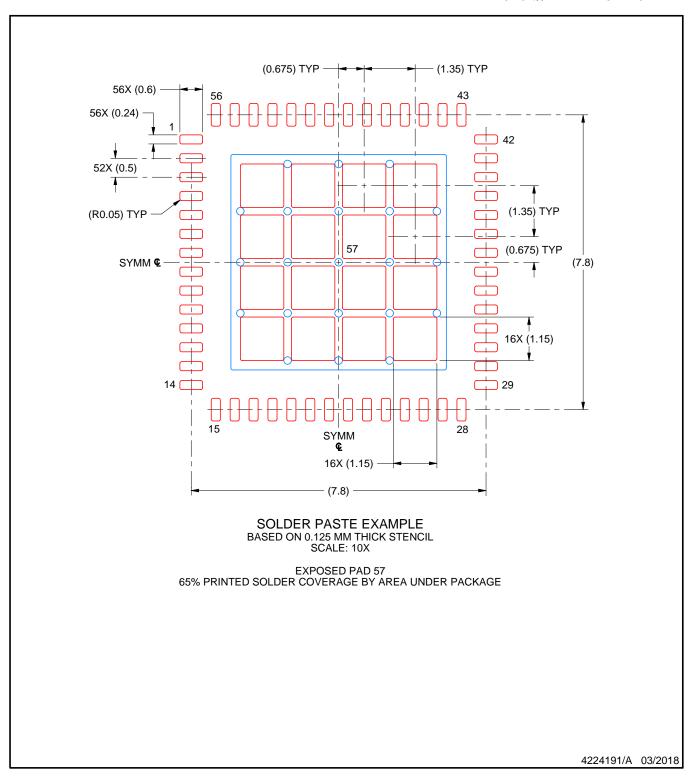

# 6 Pin Configuration and Functions

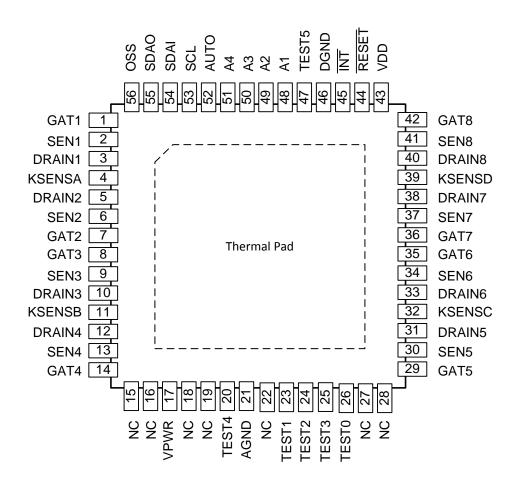

RTQ Package With Exposed Thermal Pad 56-Pin VQFN Top View

Copyright © 2019, Texas Instruments Incorporated

Submit Documentation Feedback

#### Pin Functions

| P           | IN                              | 1/0 | DESCRIPTION                                                                                                                              |

|-------------|---------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | NO.                             | 1/0 | DESCRIPTION                                                                                                                              |

| A1-4        | 48–51                           | I   | I <sup>2</sup> C A1-A4 address lines. These pins are internally pulled up to VDD.                                                        |

| AGND        | 21                              | _   | Analog ground. Connect to GND plane and exposed thermal pad.                                                                             |

| DGND        | 46                              | _   | Digital ground. Connect to GND plane and exposed thermal pad.                                                                            |

| DRAIN1-8    | 3, 5, 10, 12, 31,<br>33, 38, 40 | ı   | Channel 1-8 output voltage monitor.                                                                                                      |

| GAT1-8      | 1, 7, 8, 14, 29,<br>35, 36, 42  | 0   | Channel 1-8 gate drive output.                                                                                                           |

| ĪNT         | 45                              | 0   | Interrupt output. This pin asserts low when a bit in the interrupt register is asserted. This output is open-drain.                      |

| KSENSA/B    | 4, 11                           | - 1 | Kelvin point connection for SEN1-4                                                                                                       |

| KSENSC/D    | 32, 39                          | I   | Kelvin point connection for SEN5-8                                                                                                       |

| NC          | 15, 16, 18, 19                  | 0   | No connect pins. These pins are internally biased at 1/3 and 2/3 of VPWR in order to control the voltage gradient from VPWR. Leave open. |

|             | 22, 27, 28, 52                  | _   | No connect pin. Leave open.                                                                                                              |

| OSS         | 56                              | I   | Channel 1-8 fast shutdown. This pin is internally pulled down to DGND.                                                                   |

| RESET       | 44                              | I   | Reset input. When asserted low, the TPS23881 is reset. This pin is internally pulled up to VDD.                                          |

| SCL         | 53                              | - 1 | Serial clock input for I <sup>2</sup> C bus.                                                                                             |

| SDAI        | 54                              | - 1 | Serial data input for I <sup>2</sup> C bus. This pin can be connected to SDAO for non-isolated systems.                                  |

| SDAO        | 55                              | 0   | Serial data output for I <sup>2</sup> C bus. This pin can be connected to SDAI for non-isolated systems. This output is opendrain.       |

| AUTO        | 52                              | I/O | Autonomous mode enable and selection pin.                                                                                                |

| SEN1-8      | 2, 6, 9, 13, 30,<br>34, 37, 41  | ı   | Channel 1-8 current sense input.                                                                                                         |

| TEST0-5     | 20, 23, 24, 25,<br>26, 47       | I/O | Used internally for test purposes only. Leave open.                                                                                      |

| Thermal pad | _                               | _   | The DGND and AGND terminals must be connected to the exposed thermal pad for proper operation.                                           |

| VDD         | 43                              | _   | Digital supply. Bypass with 0.1 μF to DGND pin.                                                                                          |

| VPWR        | 17                              | _   | Analog 54-V positive supply. Bypass with 0.1 µF to AGND pin.                                                                             |

# 6.1 Detailed Pin Description

The following descriptions refer to the pinout and the functional block diagram.

**DRAIN1-DRAIN8:** Channels 1-8 output voltage monitor and detect sense. Used to measure the port output voltage, for port voltage monitoring, port power good detection and foldback action. Detection probe currents also flow into this pin.

The TPS23881 uses an innovative 4-point technique to provide reliable PD detection and avoids powering an invalid load. The discovery is performed by sinking two different current levels via the DRAINn pin, while the PD voltage is measured from VPWR to DRAINn. If prior to starting a new detection cycle the port voltage is >2.5 V, an internal 100-k $\Omega$  resistor is connected in parallel with the port and a 400-ms detect backoff period is applied to allow the port capacitor to be discharged before the detection cycle starts.

There is an internal resistor between each DRAINn pin and VPWR in any operating mode except during detection or while the port is ON. If the port n is not used, DRAINn can be left floating or tied to GND.

**GAT1-GAT8:** Channels 1-8 gate drive outputs are used for external N-channel MOSFET gate control. At port turn on, it is driven positive by a low current source to turn the MOSFET on. GATn is pulled low whenever any of the input supplies are low or if an overcurrent timeout has occurred. GATn is also pulled low if the port is turned off by use of manual shutdown inputs. Leave floating if unused.

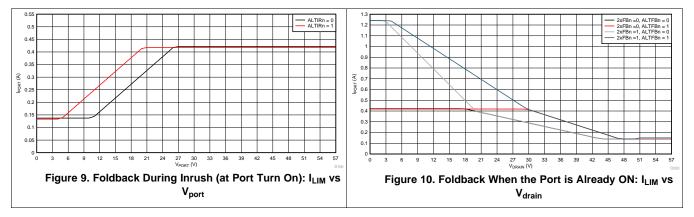

For improved design robustness, the current foldback functions limit the power dissipation of the MOSFET during low resistance load or short-circuit events and during the inrush period at port turn on. There is also fast overload protection comparator for major faults like a direct short that forces the MOSFET to turn off in less than a microsecond.

The circuit leakage paths between the GATn pin and any nearby DRAINn pin, GND or Kelvin point connection must be minimized (< 250 nA), to ensure correct MOSFET control.

Submit Documentation Feedback

Product Folder Links: TPS23881

### **Detailed Pin Description (continued)**

**INT**: This interrupt output pin asserts low when a bit in the interrupt register is asserted. This output is open-drain.

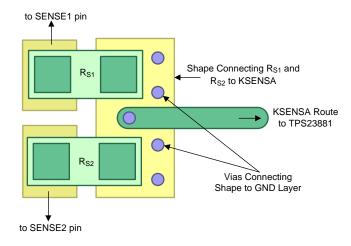

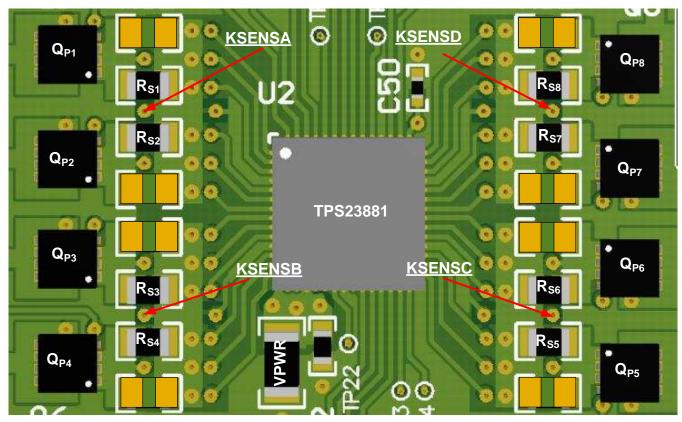

**KSENSA, KSENSB, KSENSC, KSENSD:** Kelvin point connection used to perform a differential voltage measurement across the associated current sense resistors.

Each KSENS is shared between two neighbor SEN pins as following: KSENSA with SEN1 and SEN2, KSENSB with SEN3 and SEN4, KSENSC with SEN5 and SEN6, KSENSD with SEN7 and SEN8. To optimize the measurement accuracy, ensure proper PCB layout practices are followed.

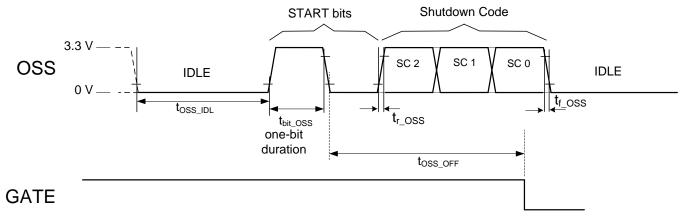

**OSS:** Fast shutdown, active high. This pin is internally pulled down to DGND, with an internal 1-µs to 5-µs deglitch filter.

The turn off procedure is similar to a port reset using Reset command (1Ah register). The 3-bit OSS function allows for a series of pulses on the OSS pin to turn off individual or multiple ports with up to 8 levels of priority.

**RESET:** Reset input, active low. When asserted, the TPS23881 resets, turning off all ports and forcing the registers to their power-up state. This pin is internally pulled up to VDD, with internal 1-µs to 5-µs deglitch filter. The designer can use an external RC network to delay the turn-on. There is also an internal power-on-reset which is independent of the RESET input.

**SCL:** Serial clock input for I<sup>2</sup>C bus.

**SDAI:** Serial data input for I<sup>2</sup>C bus. This pin can be connected to SDAO for non-isolated systems.

**SDAO:** Open-drain I<sup>2</sup>C bus output data line. Requires an external resistive pull-up. The TPS23881 uses separate SDAO and SDAI lines to allow optoisolated I<sup>2</sup>C interface. SDAO can be connected to SDAI for non-isolated systems.

**AUTO:** *Autonomous* mode selection pin: Floating this pin will disable autonomous operation. Tying this pin to GND through a resistor ( $R_{AUTO}$ ) will enable autonomous operation at selectable port power allocation levels. A 10 nF capacitor is required between the Auto pin and GND if  $R_{AUTO}$  is connected.

**A4-A1:** I<sup>2</sup>C bus address inputs. These pins are internally pulled up to VDD. See *PIN STATUS Register* for more details.

**SEN1-8:** Channel current sense input relative to KSENSn (see KSENSn description). A differential measurement is performed using KSENSA-D Kelvin point connection. Monitors the external MOSFET current by use of a  $0.200-\Omega$  current sense resistor connected to GND. Used by current foldback engine and also during classification. Can be used to perform load current monitoring via ADC conversion.

When the TPS23881 performs the classification measurements, the current flows through the external MOSFETs. This avoids heat concentration in the device and makes it possible for the TPS23881 to perform classification measurements on multiple ports at the same time. For the current limit with foldback function, there is an internal 2-µS analog filter on the SEN1-8 pins to provide glitch filtering. For measurements through an ADC, an anti-aliasing filter is present on the SEN1-8 pins. This includes the port-powered current monitoring, port policing, and DC disconnect.

If the port is not used, tie SENn to GND.

VDD: 3.3-V logic power supply input.

VPWR: High voltage power supply input. Nominally 54 V.

**AGND and DGND:** Ground references for internal analog and digital circuitry respectively. Not connected together internally. Both pins require a low resistance path to the system GND plane. If a robust GND plane is used to extract heat from the device's thermal pad, these pins may be connected together through the thermal pad connection on the pcb.

# 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

| <u> </u>         |                                                        | MIN  | MAX                        | UNIT            |

|------------------|--------------------------------------------------------|------|----------------------------|-----------------|

|                  | VPWR                                                   | -0.3 | 70                         | V               |

|                  | VDD                                                    | -0.3 | 4                          | V               |

|                  | OSS, RESET, A1, A2, A3, A4, SDAI, SDAO, SCL, INT, AUTO | -0.3 | 4                          | V               |

| \                | SEN1-8, KSENSA, KSENSB, KSENSC, KSENSD                 | -0.3 | 3                          | V               |

| Voltage          | GATE1-8                                                | -0.3 | 12                         | V               |

|                  | DRAIN1-8                                               | -0.3 | 70                         | V               |

|                  | TEST0-3, ATST_DCPL0, DTST_DCPL1                        | -0.3 | 4                          | V               |

|                  | AGND - DGND                                            | -0.3 | 70 V 4 V 4 V 3 V 12 V 70 V |                 |

| Sink Current     | INT, SDA                                               |      | 20                         | V V V V V MA °C |

| Lead Temperat    | ure 1/6mm from case for 10 seconds                     |      | 260                        | °C              |

| T <sub>stg</sub> | Storage temperature                                    | -65  | 150                        | °C              |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to thedevice. These are stress ratings only, which do not imply functional operation of the device atthese or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periodsmay affect device reliability.

# 7.2 ESD Ratings

|        |                         |                                                                               | VALUE | UNIT |

|--------|-------------------------|-------------------------------------------------------------------------------|-------|------|

| V      | Electrostatio discharge | Human body model (HBM), per<br>ANSI/ESDA/JEDEC JS-001, allpins <sup>(1)</sup> | ±2000 | V    |

| V(ESD) | Electrostatic discharge | Charged device model (CDM), per JEDEC specificationJESD22-C101, all pins (2)  | ± 500 | V    |

<sup>(1)</sup> JEDEC documentJEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                   |                                  | MIN | NOM | MAX | UNIT |

|-------------------|----------------------------------|-----|-----|-----|------|

| $V_{VDD}$         |                                  | 3   | 3.3 | 3.6 | V    |

| V <sub>VPWR</sub> |                                  | 44  | 54  | 57  | V    |

|                   | Voltage Slew rate on VPWR        |     |     | 1   | V/µs |

| f <sub>SCL</sub>  | I <sup>2</sup> C Clock Frequency |     |     | 400 | kHz  |

| $T_J$             | Junction temperature             | -40 |     | 125 | °C   |

### 7.4 Thermal Information

|                      |                                              | TPS23881           |      |

|----------------------|----------------------------------------------|--------------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RTQ Package (VQFN) | UNIT |

|                      |                                              | 56 PINS            |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 25.3               | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 9.7                | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 3.7                | °C/W |

| $\Psi_{JT}$          | Junction-to-top characterization parameter   | 0.2                | °C/W |

| $\Psi_{JB}$          | Junction-to-board characterization parameter | 3.7                | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 0.5                | °C/W |

For more information abouttraditional and new thermal metrics, see the Semiconductor and IC Package ThermalMetrics application report.

<sup>(2)</sup> JEDEC documentJEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 7.5 Electrical Characteristics

Conditions are  $-40 < T_J < 125$  °C unless otherwisenoted.  $V_{VDD} = 3.3 \text{ V}, V_{VPWR} = 54 \text{ V}, V_{DGND} = V_{AGND}, DGND, KSENSA, KSENSB, KSENSC and KSENSD connected to AGND, and all outputs are unloaded, 2xFBn =0. Positive currents are into pins. <math>R_S = 0.200 \Omega$ , to KSENSA (SEN1 orSEN2), to KSENSB (SEN3 or SEN4), to KSENSC (SEN5 or SEN6) or to KSENSD (SEN7 or SEN8). Typicalvalues are at 25 °C. All voltages are with respect to AGND unless otherwise noted. Operatingregisters loaded with default values unless otherwise noted.

| Operatingreg              | Islers loaded with default values diffess                    |                                                                      | F 7              | <b>T</b> / <b>C</b> |       |        |

|---------------------------|--------------------------------------------------------------|----------------------------------------------------------------------|------------------|---------------------|-------|--------|

|                           | PARAMETER                                                    | TEST CONDITIONS                                                      | MIN              | TYP                 | MAX   | UNIT   |

| INPUT SUPPI               |                                                              |                                                                      |                  |                     |       |        |

| I <sub>VPWR</sub>         | VPWR Current consumption                                     | VVPWR = 54 V                                                         |                  | 10                  | 12.5  | mA     |

| $V_{UVLOPW\_F}$           | VPWR UVLO falling threshold                                  | Check internal oscillator stops operating                            | 14.5             |                     | 17.5  | V      |

| V <sub>UVLOPW_R</sub>     | VPWR UVLO rising threshold                                   |                                                                      | 15.5             |                     | 18.5  | V      |

| V <sub>PUV_F</sub>        | VPWR Undervoltage falling threshold                          | VPUV threshold                                                       | 25               | 26.5                | 28    | V      |

| INPUT SUPPI               | LY VDD                                                       |                                                                      |                  |                     |       |        |

| $I_{VDD}$                 | VDD Current consumption                                      |                                                                      |                  | 6                   | 12    | mA     |

| $V_{UVDD\_F}$             | VDD UVLO falling threshold                                   | For channel deassertion                                              | 2.1              | 2.25                | 2.4   | V      |

| $V_{UVDD_R}$              | VDD UVLO rising threshold                                    |                                                                      | 2.45             | 2.6                 | 2.75  | V      |

| V <sub>UVDD_HYS</sub>     | Hysteresis VDD UVLO                                          |                                                                      |                  | 0.35                |       | V      |

| V <sub>UVW_F</sub>        | VDD UVLO warning threshold                                   | VDD falling                                                          | 2.6              | 2.8                 | 3     | V      |

| A/D CONVER                | TERS                                                         | ,                                                                    |                  |                     |       |        |

| T <sub>CONV_I</sub>       | Conversion time                                              | All ranges, each channel                                             | 0.64             | 0.8                 | 0.96  | ms     |

| T <sub>CONV_V</sub>       | Conversiontime                                               | All ranges, each channel                                             | 0.82             | 1.03                | 1.2   | ms     |

| T <sub>INT CUR</sub>      | Integration time, Current                                    | Each channel, channel ON current                                     | 82               | 102                 | 122   | ms     |

| T <sub>INT_DET</sub>      | Integration time, Detection                                  |                                                                      | 13.1             | 16.6                | 20    | ms     |

| T <sub>INT_channelV</sub> | Integration time, Channel Voltage                            | channel powered                                                      | 3.25             | 4.12                | 4.9   | ms     |

| T <sub>INT_inV</sub>      | Integration time, Input Voltage                              |                                                                      | 3.25             | 4.12                | 4.9   | ms     |

| - 1141_1117               | 1                                                            |                                                                      | 15175            | 15565               | 15955 | Counts |

|                           |                                                              | VVPWR = 57 V                                                         | 55.57            | 57                  | 58.43 | V      |

|                           | accuracy                                                     |                                                                      | 11713            | 12015               | 12316 | Counts |

|                           |                                                              |                                                                      | 42.89            | 44                  | 45.10 | V      |

|                           |                                                              |                                                                      | 15175            | 15565               | 15955 | Counts |

|                           | Downered Channel voltage conversion                          | VVPWR - VDRAINn = 57 V                                               | 55.57            | 57                  | 58.43 | V      |

|                           | Powered Channel voltage conversion scale factor and accuracy |                                                                      | 11713            | 12015               | 12316 | Counts |

|                           | ,                                                            | VVPWR - VDRAINn = 44 V                                               | 42.89            | 44                  | 45.10 | V      |

| δV/V <sub>Channel</sub>   | Voltage reading accuracy                                     |                                                                      | -2.5             |                     | 2.5   |        |

| 0 V V Channel             | Voltage reading accuracy                                     |                                                                      | 8431             | 8604                | 8776  | Counts |

|                           |                                                              | Channel current = 770 mA                                             | 754.5            | 770                 | 785.4 | mA     |

|                           | Powered Channel current conversion scale factor and accuracy |                                                                      | 66               | 84                  | 102   |        |

|                           | could racter area accuracy                                   | Channel Current = 7.5 mA                                             |                  |                     |       | Counts |

|                           |                                                              | Channel Current FO mA                                                | 5.966            | 7.5                 | 9.125 | mA     |

| δI/I <sub>Channel</sub>   | Current reading accuracy                                     | Channel Current = 50 mA                                              | -3               |                     | 3     | %      |

|                           |                                                              | Channel Current =770 mA                                              | <b>-2</b>        | 45074               | 2     | 0      |

|                           | Powered Channel current ful scale output                     | Channel currents = 1.5 A, 2xFBn = 1                                  | 14959            | 15671               |       | Counts |

|                           | ·                                                            | - " o . ' . "                                                        | 1.34             | 1.400               |       | Α      |

| σl                        | Current Reading Repeatability                                | Full Scale reading                                                   | <del>-</del> 7.5 |                     | 7.5   | mA     |

| δR/R <sub>Channel</sub>   | Resistance reading accuracy                                  | 15 kΩ ≤ R <sub>Channel</sub> ≤ 33 kΩ, C <sub>Channel</sub> ≤ 0.25 μF | -7               |                     | 7     | %      |

| I <sub>bias</sub>         | Sense Pin bias current                                       | Channel ON or during class                                           | -2.5             |                     | 0     | μΑ     |

Conditions are  $-40 < T_J < 125$  °C unless otherwisenoted.  $V_{VDD} = 3.3 \text{ V}, V_{VPWR} = 54 \text{ V}, V_{DGND} = V_{AGND}, DGND, KSENSA, KSENSB, KSENSC and KSENSD connected to AGND, and all outputs are unloaded, <math>2xFBn = 0$ . Positive currents are into pins.  $R_S = 0.200 \Omega$ , to KSENSA (SEN1 orSEN2), to KSENSB (SEN3 or SEN4), to KSENSC (SEN5 or SEN6) or to KSENSD (SEN7 or SEN8). Typicalvalues are at 25 °C. All voltages are with respect to AGND unless otherwise noted.

|                          | PARAMETER                                                                               | TEST CONDITIONS                                                                                        | MIN  | TYP  | MAX  | UNIT   |

|--------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------|------|------|--------|

| GATE 1-8                 |                                                                                         |                                                                                                        |      |      |      |        |

| V <sub>GOH</sub>         | Gate drive voltage                                                                      | V <sub>GATEn</sub> , I <sub>GATE</sub> = -1 μA                                                         | 10   |      | 12.5 | V      |

| I <sub>GO-</sub>         | Gate sinking current with Power-on<br>Reset, OSS detected or channel turnoff<br>command | V <sub>GATEn</sub> = 5 V                                                                               | 60   | 100  | 190  | mA     |

| I <sub>GO short-</sub>   | Gate sinking current with channel short-circuit                                         | $V_{GATEn} = 5 \text{ V},$<br>$V_{SENn} \ge V_{short} \text{ (or } V_{short2X} \text{ if 2X mode)}$    | 60   | 100  | 190  | mA     |

| I <sub>GO+</sub>         | Gate sourcing current                                                                   | V <sub>GATEn</sub> = 0 V, default selection                                                            | 39   | 50   | 63   | μΑ     |

| t <sub>D_off_OSS</sub>   | Gate turnoff time from 1-bit OSS input                                                  | From OSS to VGATEn < 1 V,<br>VSENn = 0 V, MbitPrty = 0                                                 | 1    |      | 5    | μs     |

| t <sub>OSS_OFF</sub>     | Gate turnoff time from 3-bit OSS input                                                  | From Start bit falling edge to VGATEn < 1 V, VSENn = 0 V, MbitPrty = 1                                 | 72   |      | 104  | μs     |

| t <sub>P_off_CMD</sub>   | Gate turnoff time from channel turnoff command                                          | From Channel off command (POFFn = 1) to V <sub>GATEn</sub> < 1 V, V <sub>SENn</sub> = 0 V              |      |      | 300  | μs     |

| t <sub>P_off_RST</sub>   | Gate turnoff time with /RESET                                                           | From /RESET low to $V_{GATEn} < 1 \text{ V}$ , $V_{SENn} = 0 \text{ V}$                                | 1    |      | 5    | μs     |

| DRAIN 1-8                |                                                                                         |                                                                                                        |      |      |      |        |

| $V_{PGT}$                | Power-Good threshold                                                                    | Measured at V <sub>DRAINn</sub>                                                                        | 1    | 2.13 | 3    | V      |

| $V_{SHT}$                | Shorted FET threshold                                                                   | Measured at V <sub>DRAINn</sub>                                                                        | 4    | 6    | 8    | V      |

| R <sub>DRAIN</sub>       | Resistance from DRAINn to VPWR                                                          | Any operating mode except during detection or while the Channel is ON, including in device RESET state | 80   | 100  | 190  | kΩ     |

| AUTOCLASS                |                                                                                         |                                                                                                        |      |      |      |        |

| t <sub>Class_ACS</sub>   | Start of Autoclass Detection                                                            | Measured from the start of Class                                                                       | 90   |      | 100  | ms     |

|                          |                                                                                         | Measured from the end of Inrush                                                                        | 1.4  |      | 1.6  | s      |

| t <sub>AUTO_PSE1</sub>   | Start of Autoclass Power Measurement                                                    | Measured from setting the MACx bit while channel is already powered                                    |      |      | 10   | ms     |

| t <sub>AUTO</sub>        | Duration of Autoclass Power<br>Measurement                                              |                                                                                                        | 1.7  | 1.8  | 1.9  | s      |

| t <sub>AUTO_window</sub> | Autoclass Power Measurement Sliding Window                                              |                                                                                                        | 0.15 |      | 0.3  | s      |

| D                        | Autoclass Channel Power conversion                                                      | VPWR = 52 V, VDRAINn = 0 V,<br>Channel current = 770 mA                                                | 76   | 80   | 84   | Counts |

| P <sub>AC</sub>          | scale factor and accuracy                                                               | VPWR = 50 V, VDRAINn = 0 V,<br>Channel current = 100 mA                                                | 9    | 10   | 11   |        |

Submit Documentation Feedback

Product Folder Links: TPS23881

Conditions are  $-40 < T_J < 125$  °C unless otherwisenoted.  $V_{VDD} = 3.3 \text{ V}, V_{VPWR} = 54 \text{ V}, V_{DGND} = V_{AGND}, DGND, KSENSA, KSENSB, KSENSC and KSENSD connected to AGND, and all outputs are unloaded, <math>2xFBn = 0$ . Positive currents are into pins.  $R_S = 0.200 \Omega$ , to KSENSA (SEN1 orSEN2), to KSENSB (SEN3 or SEN4), to KSENSC (SEN5 or SEN6) or to KSENSD (SEN7 or SEN8). Typicalvalues are at 25 °C. All voltages are with respect to AGND unless otherwise noted. Operating registers loaded with default values unless otherwise noted.

|                        | PARAMETER                                 | TEST CONDITIONS                                                      | MIN  | TYP  | MAX          | UNIT      |

|------------------------|-------------------------------------------|----------------------------------------------------------------------|------|------|--------------|-----------|

| DETECTION              | l                                         |                                                                      |      |      |              |           |

| 1                      | Detection current                         | First and 3rd detection points VVPWR - VDRAINn = 0 V                 | 145  | 160  | 190          |           |

| IDISC                  | Detection current                         | 2nd and 4th detection points VVPWR - VDRAINn = 0 V                   | 235  | 270  | 300          | μA        |

| $\Delta I_{DISC}$      | 2nd – 1st detection currents              | VVPWR - VDRAINn = 0 V                                                | 98   | 110  | 118          | μΑ        |

| V <sub>det_open</sub>  | Open circuit detection voltage            | Measured as VVPWR - VDRAINn                                          | 23.5 | 26   | 29           | V         |

| R <sub>REJ_LOW</sub>   | Rejected resistance low range             |                                                                      | 0.86 |      | 15           | $k\Omega$ |

| R <sub>REJ_HI</sub>    | Rejected resistance high range            |                                                                      | 33   |      | 100          | $k\Omega$ |

| R <sub>ACCEPT</sub>    | Accepted resistance range                 |                                                                      | 19   | 25   | 26.5         | kΩ        |

| R <sub>SHORT</sub>     | Shorted Channel threshold                 |                                                                      |      |      | 360          | Ω         |

| R <sub>OPEN</sub>      | Open Channel Threshold                    |                                                                      | 400  |      |              | kΩ        |

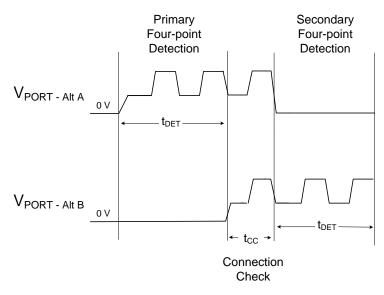

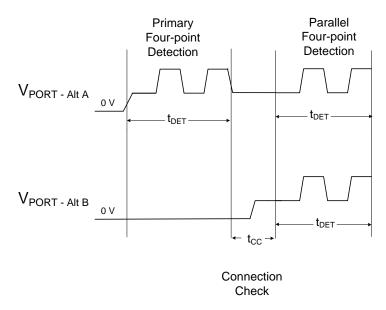

| t <sub>DET</sub>       | Detection Duration                        | Time to complete a detection, 4Pxx = 0                               | 275  | 350  | 425          | ms        |

| t <sub>CC</sub>        | Connection Check Duration                 | Time to complete connection check after a valid detection, 4Pxx = 1  |      | 150  | 400          | ms        |

|                        | Detect backoff pause between discovery    | VVPWR - VDRAINn > 2.5 V                                              | 300  | 400  | 500          | ms        |

| t <sub>DET_BOFF</sub>  | attempts                                  | VVPWR - VDRAINn < 2.5 V                                              | 20   |      | 100          | ms        |

| t <sub>DET_DLY</sub>   | Detection delay                           | From command or PD attachment to Channel detection complete 4Pxx = 0 |      |      | 590          | ms        |

|                        | Capactance Measurement                    | Cport = 10uF                                                         | 8.5  | 10   | 11.5         | uF        |

| CLASSIFICA             | ATION                                     |                                                                      |      |      |              |           |

| V <sub>CLASS</sub>     | Classification Voltage                    | VVPWR - VDRAINn, VSENn ≥ 0 mV<br>I <sub>channel</sub> ≥ 180 μA       | 15.5 | 18.5 | 20.5         | V         |

| I <sub>CLASS_Lim</sub> | Classification Current Limit              | VVPWR - VDRAINn = 0 V                                                | 65   | 75   | 90           | mA        |

|                        |                                           | Class 0-1                                                            | 5    |      | 8            | mA        |

|                        |                                           | Class 1-2                                                            | 13   |      | 16           | mA        |

| I <sub>CLASS_TH</sub>  | Classification Threshold Current          | Class 2-3                                                            | 21   |      | 25           | mA        |

|                        |                                           | Class 3-4                                                            | 31   |      | 35           | mA        |

|                        |                                           | Class 4-Class overcurrent                                            | 45   |      | 51           | mA        |

| t <sub>LCE</sub>       | Classification Duration (1st Finger)      | From detection complete                                              | 95   |      | 105          | ms        |

| t <sub>CLE2-5</sub>    | Classification Duration (2nd- 5th Finger) | From Mark complete                                                   | 6.5  |      | 12           | ms        |

| MARK                   |                                           |                                                                      |      |      | <del>!</del> |           |

| V <sub>MARK</sub>      | Mark Voltage                              | 4 mA ≥ IChannel ≥ 180 μA<br>VVPWR - VDRAINn                          | 7    |      | 10           | V         |

| I <sub>MARK_Lim</sub>  | Mark Sinking Current Limit                | VVPWR - VDRAINn = 0 V                                                | 60   | 75   | 90           | mA        |

| t <sub>ME</sub>        | Mark Duration                             |                                                                      | 6    |      | 12           | ms        |

Conditions are  $-40 < T_J < 125$  °C unless otherwisenoted.  $V_{VDD} = 3.3 \text{ V}, V_{VPWR} = 54 \text{ V}, V_{DGND} = V_{AGND}, DGND, KSENSA, KSENSB, KSENSC and KSENSD connected to AGND, and all outputs are unloaded, 2xFBn =0. Positive currents are into pins. <math>R_S = 0.200 \, \Omega$ , to KSENSA (SEN1 orSEN2), to KSENSB (SEN3 or SEN4), to KSENSC (SEN5 or SEN6) or to KSENSD (SEN7 or SEN8). Typicalvalues are at 25 °C. All voltages are with respect to AGND unless otherwise noted. Operatingregisters loaded with default values unless otherwise noted.

|                                     | PARAMETER                                      | TEST CONDITIONS        | MIN | TYP | MAX          | UNIT |

|-------------------------------------|------------------------------------------------|------------------------|-----|-----|--------------|------|

| DC DISCON                           | NECT                                           |                        | •   |     |              |      |

| V                                   | DC discours at threat ald                      | DCDTxx = 0             | 0.8 | 1.3 | 1.8          | mV   |

| $V_{IMIN}$                          | DC disconnect threshold                        | DCDTxx = 1             | 0.4 | 0.9 | 1.4          | mV   |

|                                     |                                                | TMPDO = 00             | 320 |     | 400          | ms   |

|                                     | PD Maintain Power signature dropout            | TMPDO = 01             | 75  |     | 100          | ms   |

| t <sub>MPDO</sub>                   | time limit                                     | TMPDO = 10             | 150 |     | 200          | ms   |

|                                     |                                                | TMPDO = 11             | 600 |     | 800          | ms   |

| t <sub>MPS</sub>                    | PD Maintain Power Signature time for validity  |                        |     | 2.5 | 3            | ms   |

| PORT POWE                           | R POLICING                                     |                        |     |     |              |      |

| δP <sub>CUT</sub> /P <sub>CUT</sub> | PCUT tolerance                                 | POL ≤ 15W              | 0   | 5   | 10           | %    |

| $\delta P_{CUT}/P_{CUT}$            | PCUT tolerance                                 | 15W < POL < 90W        | 0   | 3   | 6            | %    |

| $\delta P_{CUT}/P_{CUT}$            | PCUT tolerance                                 | POL ≥ 90W              | 0   | 2.5 | 5            | %    |

|                                     |                                                | TOVLD = 00             | 50  |     | 70           |      |

| <b>t</b>                            | PCUT time limit                                | TOVLD = 01             | 25  |     | 35           | ms   |

| tovld                               | FCOT time limit                                | TOVLD = 10             | 100 |     | 140          | 1115 |

|                                     |                                                | TOVLD = 11             | 200 |     | 280          |      |

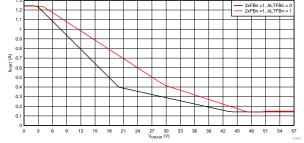

| PORT CURR                           | ENT INRUSH                                     |                        |     |     |              |      |

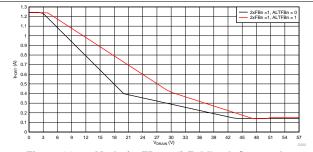

|                                     |                                                | VVPWR - VDRAINn = 1 V  | 19  | 30  | 41           |      |

|                                     |                                                | VVPWR - VDRAINn = 10 V | 19  | 30  | 41           |      |

|                                     | IInrush limit, ALTIRNn = 0                     | VVPWR - VDRAINn = 15 V | 33  | 44  | 55           |      |

|                                     |                                                | VVPWR - VDRAINn = 30 V | 80  |     | 90           |      |

| V                                   |                                                | VVPWR - VDRAINn = 55 V | 80  |     | 90           | mV   |

| $V_{Inrush}$                        |                                                | VVPWR - VDRAINn = 1 V  | 19  | 30  | 41           | IIIV |

|                                     |                                                | VVPWR - VDRAINn = 10 V | 36  | 47  | 58           |      |

|                                     | IInrush limit, ALTIRNn = 1                     | VVPWR - VDRAINn = 15 V | 53  | 64  | 75           |      |

|                                     |                                                | VVPWR - VDRAINn = 30 V |     | 90  | <del>.</del> |      |

|                                     |                                                | VVPWR - VDRAINn = 55 V | 80  |     | 90           |      |

|                                     |                                                | TSTART = 00            | 50  |     | 70           |      |

| t <sub>START</sub>                  | Maximum current limit duration in start-<br>up | TSTART = 01            | 25  |     | 35           | ms   |

|                                     | ~~                                             | TSTART = 10            | 100 |     | 140          |      |

Conditions are  $-40 < T_J < 125$  °C unless otherwisenoted.  $V_{VDD} = 3.3 \text{ V}, V_{VPWR} = 54 \text{ V}, V_{DGND} = V_{AGND}, DGND, KSENSA, KSENSB, KSENSC and KSENSD connected to AGND, and all outputs are unloaded, 2xFBn =0. Positive currents are into pins. <math>R_S = 0.200 \Omega$ , to KSENSA (SEN1 orSEN2), to KSENSB (SEN3 or SEN4), to KSENSC (SEN5 or SEN6) or to KSENSD (SEN7 or SEN8). Typicalvalues are at 25 °C. All voltages are with respect to AGND unless otherwise noted. Operating registers loaded with default values unless otherwise noted.

|                         | PARAMETER                                                                                                       | TEST CONDITIONS                                                                 | MIN | TYP | MAX | UNIT |  |  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----|-----|-----|------|--|--|

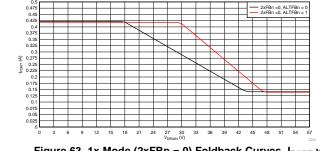

| PORT CURI               | RENT FOLDBACK                                                                                                   |                                                                                 |     |     |     |      |  |  |

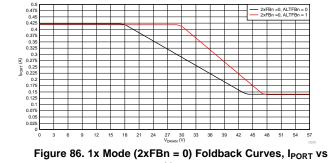

|                         |                                                                                                                 | VDRAINn = 1 V                                                                   | 80  |     | 90  |      |  |  |

|                         | HILLAND IN C. ED. C. LAUTED CO.                                                                                 | VDRAINn = 15 V                                                                  | 80  |     | 90  |      |  |  |

|                         | ILIM 1X limit, 2xFB = 0 and ALTFBn = 0                                                                          | VDRAINn = 30 V                                                                  | 51  | 58  | 65  |      |  |  |

|                         |                                                                                                                 | VDRAINn = 50 V                                                                  | 23  | 30  | 37  |      |  |  |

| $V_{LIM}$               |                                                                                                                 | VDRAINn = 1 V                                                                   | 80  |     | 90  | mV   |  |  |

|                         | HIMAY For South ALTER 4                                                                                         | VDRAINn = 25 V                                                                  | 80  |     | 90  |      |  |  |

|                         | ILIM 1X limit, 2xFB = 0 and ALTFBn = 1                                                                          | VDRAINn = 40 V                                                                  | 47  | 53  | 59  |      |  |  |

|                         |                                                                                                                 | VDRAINn = 50 V                                                                  | 23  | 30  | 37  |      |  |  |

| -                       |                                                                                                                 | VDRAINn = 1 V                                                                   | 245 | 250 | 262 |      |  |  |

|                         | HIMOVIEW OFFE                                                                                                   | VDRAINn = 10 V                                                                  | 156 | 172 | 188 |      |  |  |

|                         | ILIM 2X limit, 2xFB = 1 and ALTFBn = 0                                                                          | VDRAINn = 30 V                                                                  | 51  | 58  | 64  |      |  |  |

|                         |                                                                                                                 | VDRAINn = 50 V                                                                  | 23  | 30  | 37  | >/   |  |  |

| $V_{LIM2X}$             |                                                                                                                 | VDRAINn = 1 V                                                                   | 245 | 250 | 262 | mV   |  |  |

| ILIM                    | HIMOVIEW OFF                                                                                                    | VDRAINn = 20 V                                                                  | 143 | 151 | 159 |      |  |  |

|                         | ILIM 2X limit, 2xFB = 1 and ALTFBn = 1                                                                          | VDRAINn = 40 V                                                                  | 45  | 51  | 57  |      |  |  |

|                         |                                                                                                                 | VDRAINn = 50 V                                                                  | 23  | 30  | 37  |      |  |  |

|                         | ILIM time limit                                                                                                 | 2xFBn = 0                                                                       | 55  | 60  | 65  |      |  |  |

|                         |                                                                                                                 | TLIM = 00                                                                       | 55  | 60  | 65  |      |  |  |

| t <sub>LIM</sub>        | 0.50. 4                                                                                                         | TLIM = 01                                                                       | 15  | 16  | 17  | ms   |  |  |

|                         | 2xFBn = 1                                                                                                       | TLIM = 10                                                                       |     |     |     |      |  |  |

|                         |                                                                                                                 | TLIM = 11                                                                       | 6   | 6.5 | 7   |      |  |  |

| SHORT CIR               | CUIT DETECTION                                                                                                  |                                                                                 |     |     |     |      |  |  |

| V <sub>short</sub>      | I <sub>SHORT</sub> threshold in 1X mode and during inrush                                                       |                                                                                 | 200 |     | 240 | mV   |  |  |

| V <sub>short2X</sub>    | I <sub>SHORT</sub> threshold in 2X mode                                                                         |                                                                                 | 280 |     | 320 |      |  |  |

|                         | Outs to well the four OFNs in a                                                                                 | 2xFBn = 0, VDRAINn = 1 V<br>From VSENn pulsed to 0.425 V.                       |     |     | 0.9 |      |  |  |

| t <sub>D_off_</sub> SEN | Gate turnoff time from SENn input                                                                               | 2xFBn = 1, VDRAINn = 1 V<br>From VSENn pulsed to 0.62 V.                        |     |     | 0.9 | μs   |  |  |

| CURRENT F               | FAULT RECOVERY (BACKOFF) TIMING                                                                                 |                                                                                 |     |     |     |      |  |  |

| t <sub>ed</sub>         | Error delay timing. Delay before next attempt to power a channel following power removal due to error condition | P <sub>CUT</sub> , I <sub>LIM</sub> or I <sub>Inrush</sub> fault Semi-auto mode | 0.8 | 1   | 1.2 | s    |  |  |

| $\delta I_{fault}$      | Duty cycle of I <sub>channel</sub> with current fault                                                           |                                                                                 | 5.5 |     | 6.7 | %    |  |  |

|                         | SHUTDOWN                                                                                                        |                                                                                 |     |     |     |      |  |  |

|                         | Shutdown temperature                                                                                            | Temperature rising                                                              | 135 | 146 |     | °C   |  |  |

|                         | Hysteresis                                                                                                      |                                                                                 |     | 7   |     | °C   |  |  |

Conditions are  $-40 < T_J < 125$  °C unless otherwisenoted.  $V_{VDD} = 3.3 \text{ V}, V_{VPWR} = 54 \text{ V}, V_{DGND} = V_{AGND}, DGND, KSENSA, KSENSB, KSENSC and KSENSD connected to AGND, and all outputs are unloaded, <math>2xFBn = 0$ . Positive currents are into pins.  $R_S = 0.200 \Omega$ , to KSENSA (SEN1 orSEN2), to KSENSB (SEN3 or SEN4), to KSENSC (SEN5 or SEN6) or to KSENSD (SEN7 or SEN8). Typicalvalues are at 25 °C. All voltages are with respect to AGND unless otherwise noted.

| Operaungre            | gisters loaded with default values unless                              | otherwise noted.                                                              |      |     |     |      |

|-----------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------|------|-----|-----|------|

|                       | PARAMETER                                                              | TEST CONDITIONS                                                               | MIN  | TYP | MAX | UNIT |

| DIGITAL I/O           | (SCL, SDAI, A1-A4, /RESET, OSS unless of                               | otherwise stated)                                                             |      |     |     |      |

| V <sub>IH</sub>       | Digital input High                                                     |                                                                               | 2.1  |     |     | V    |

| V <sub>IL</sub>       | Digital input Low                                                      |                                                                               |      |     | 0.9 | V    |

| V <sub>IT_HYS</sub>   | Input voltage hysteresis                                               |                                                                               | 0.17 |     |     | V    |

|                       | Digital output Low                                                     | SDAO at 9mA                                                                   |      |     | 0.4 | V    |

| $V_{OL}$              | Digital output Low                                                     | /INT at 3mA                                                                   |      |     | 0.4 | V    |

| R <sub>pullup</sub>   | Pullup resistor to VDD                                                 | /RESET, A1-A4, TEST0                                                          | 30   | 50  | 80  | kΩ   |

| R <sub>pulldown</sub> | Pulldown resistor to DGND                                              | OSS, TEST1, TEST2                                                             | 30   | 50  | 80  | kΩ   |

| t <sub>FLT_INT</sub>  | Fault to /INT assertion                                                | Time to internally register an Interrupt fault, from Channel turn off         |      | 50  | 500 | μs   |

| T <sub>RESETmin</sub> | /RESET input minimum pulse width                                       |                                                                               |      |     | 5   | μs   |

| T <sub>bit_OSS</sub>  | 3-bit OSS bit period                                                   | MbitPrty = 1                                                                  | 24   | 25  | 26  | μs   |

| t <sub>OSS_IDL</sub>  | Idle time between consecutive shutdown code transmission in 3-bit mode | MbitPrty = 1                                                                  | 48   | 50  |     | μs   |

| t <sub>r_OSS</sub>    | Input rise time of OSS in 3-bit mode                                   | 0.8 V → 2.3 V, MbitPrty = 1                                                   | 1    |     | 300 | ns   |

| t <sub>f OSS</sub>    | Input fall time of OSS in 3-bit mode                                   | 2.3 V → 0.8 V, MbitPrty = 1                                                   | 1    |     | 300 | ns   |

| _                     | REQUIREMENTS                                                           | -                                                                             |      |     |     |      |

| t <sub>POR</sub>      | Device power-on reset delay                                            |                                                                               |      |     | 20  | ms   |

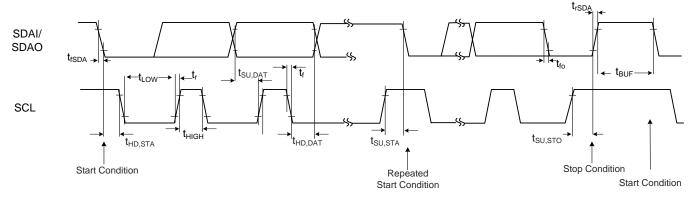

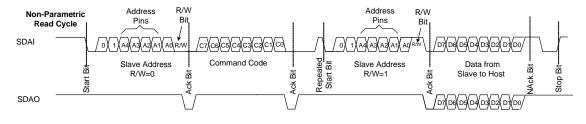

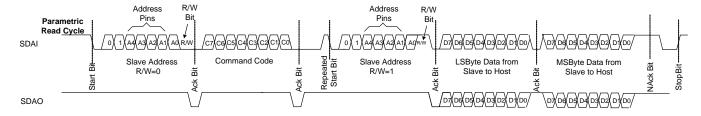

| f <sub>SCL</sub>      | SCL clock frequency                                                    |                                                                               | 10   |     | 400 | kHz  |

| $t_{LOW}$             | LOW period of the clock                                                |                                                                               | 0.5  |     |     | μs   |

| t <sub>HIGH</sub>     | HIGH period of the clock                                               |                                                                               | 0.26 |     |     | μs   |

| _                     |                                                                        | SDAO, 2.3 V $\rightarrow$ 0.8 V, Cb = 10 pF, 10 k $\Omega$ pull-up to 3.3 V   | 10   |     | 50  | ns   |

| t <sub>fo</sub>       | SDAO output fall time                                                  | SDAO, 2.3 V $\rightarrow$ 0.8 V, Cb = 400 pF, 1.3 k $\Omega$ pull-up to 3.3 V | 10   |     | 50  | ns   |

| C <sub>I2C</sub>      | SCL capacitance                                                        |                                                                               |      |     | 10  | рF   |

| C <sub>I2C_SDA</sub>  | SDAI, SDAO capacitance                                                 |                                                                               |      |     | 6   | pF   |

| t <sub>SU,DATW</sub>  | Data setup tme (Write operation)                                       |                                                                               | 50   |     |     | ns   |

| t <sub>HD,DATW</sub>  | Data hold time (Write operation)                                       |                                                                               | 0    |     |     | ns   |

| t <sub>HD,DATR</sub>  | Data hold time (Read operation)                                        |                                                                               | 150  |     | 400 | ns   |

| t <sub>fSDA</sub>     | Input fall times of SDAI                                               | 2.3 V → 0.8 V                                                                 | 20   |     | 120 | ns   |

| t <sub>rSDA</sub>     | Input rise times of SDAI                                               | 0.8 V → 2.3 V                                                                 | 20   |     | 120 | ns   |

| t <sub>r</sub>        | Input rise time of SCL                                                 | 0.8 V → 2.3 V                                                                 | 20   |     | 120 | ns   |

| t <sub>f</sub>        | Input fall time of SCL                                                 | 2.3 V → 0.8 V                                                                 | 20   |     | 120 | ns   |

| t <sub>BUF</sub>      | Bus free time between a STOP and START condition                       |                                                                               | 0.5  |     |     | μs   |

| t <sub>HD,STA</sub>   | Hold time After (Repeated) START condition                             |                                                                               | 0.26 |     |     | μs   |

| t <sub>SU,STA</sub>   | Repeated START condition setup time                                    |                                                                               | 0.26 |     |     | μs   |

| t <sub>SU,STO</sub>   | STOP condition setup time                                              |                                                                               | 0.26 |     |     | μs   |

| t <sub>DG</sub>       | Suppressed spike pulse width, SDAI and SCL                             |                                                                               | 50   |     |     | ns   |

| t <sub>WDT_I2C</sub>  | I2C Watchdog trip delay                                                |                                                                               | 1.1  | 2.2 | 3.3 | sec  |

Submit Documentation Feedback

# 8 Parameter Measurement Information

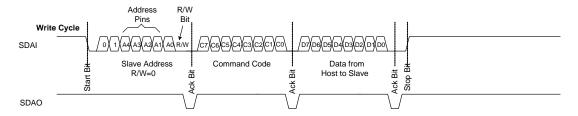

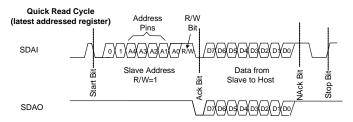

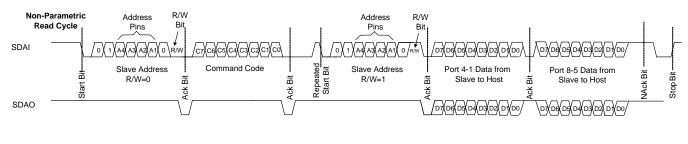

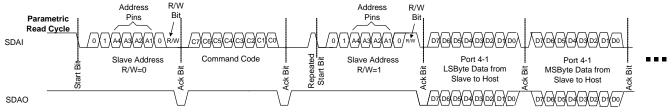

# 8.1 Timing Diagrams

Figure 1. I<sup>2</sup>C Timings

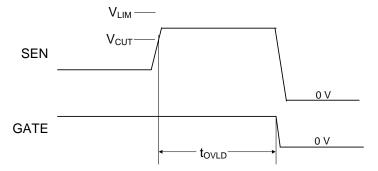

Figure 2. Overcurrent Fault Timing

Copyright © 2019, Texas Instruments Incorporated

Submit Documentation Feedback

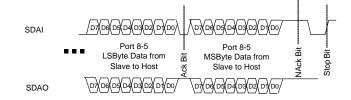

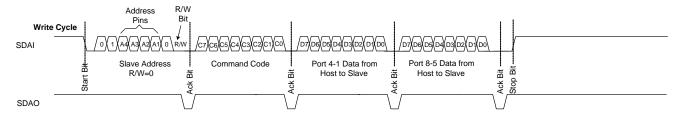

# **Timing Diagrams (continued)**

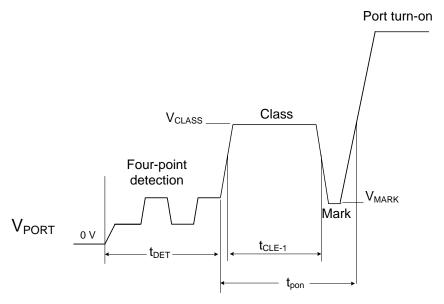

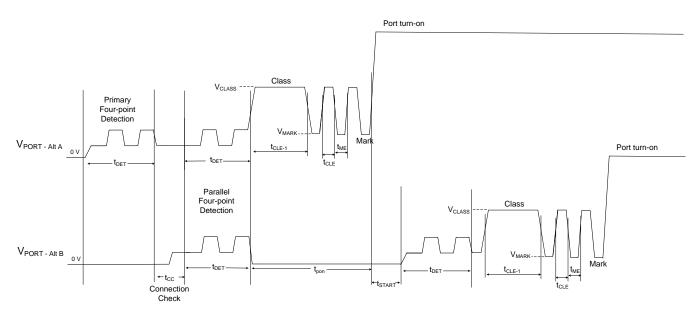

Figure 3. 2-Pair Detection, 1-Event Classification and Turn On

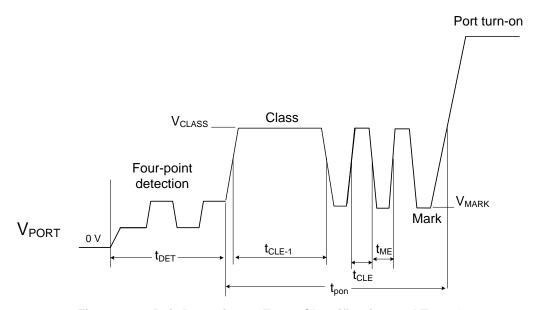

Figure 4. 2-Pair Detection, 3-Event Classification and Turn On

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

# **Timing Diagrams (continued)**

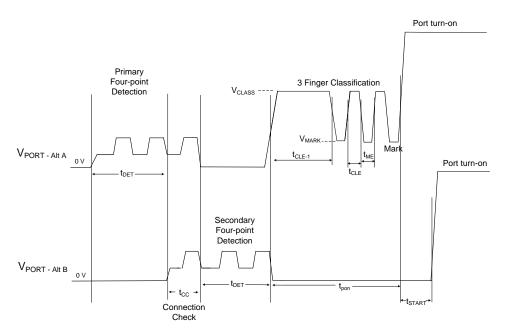

Figure 5. 4-Pair Single Signature Detection, 3-Event Classification and Turn On

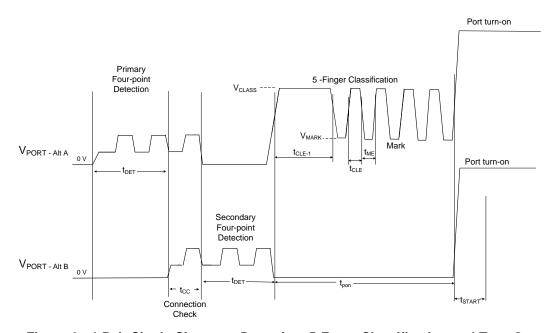

Figure 6. 4-Pair Single Signature Detection, 5-Event Classification and Turn On

# **Timing Diagrams (continued)**

Figure 7. 4-Pair Dual Signature Detection, 3-Event Classification and Turn On

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

# 9 Detailed Description

#### 9.1 Overview

The TPS23881 is an eight-channel PSE for power over Ethernet applications. Each of the eight channels provides detection, classification, protection, and shutdown in compliance with the IEEE 802.3bt (draft) standard.

Basic PoE features include the following:

- · Performs high-reliability 4-point load detection

- Performs classification including type-3/4 (three, four or five -fingers) of up to Class 8 loads

- Recognizes single signature and dual signature PDs

- Enables power with protective fold-back current limiting, and an adjustable P<sub>CUT</sub> threshold

- · Shuts down during faults such as overcurrent or outputs shorts

- · Performs a maintain power signature function to ensure power is removed if the load is disconnected

- Undervoltage lockout occurs if VPWR falls below V<sub>PUV F</sub> (typical 26.5 V).

Enhanced features include the following:

- Programable SRAM memory

- Dedicated 14-bit integrating current ADCs per port

- Port re-mapping capability

- 8- and 16-bit access mode selectable

- 1- and 3-bit port shutdown priority

### 9.1.1 Operating Modes

#### 9.1.1.1 Auto

The port performs detection and classification (if valid detection occurs) continuously. Registers are updated each time a detection or classification occurs. The port power is automatically turned on based on the Power Allocation settings in register 0x29 if a valid classification is measured.

#### 9.1.1.2 Autonomous

Unlike Auto mode, which still requires a host to initialize the TPS23881 operation through a a series of  $I^2C$  commands, there is no host or  $I^2C$  communication required when the TPS23881 in configured in Autonomous mode.

During power up, the resistance on the AUTO pin (R<sub>AUTO</sub>) is measured, and the device is pre-configured according to Table 16. The port automatically performs detection and classification (if valid detection occurs) continuously on all ports. Port power is automatically turned on based on Power Allocation settings in register 0x29 if a valid classification is measured.

### **NOTE**

A 10 nF capacitor is required in parallel with  $R_{AUTO}$  to ensure stability in the Autonomous mode selection.

#### 9.1.1.3 Semiauto

The port performs detection and classification (if valid detection occurs) continuously. Registers are updated each time a detection or classification occurs. The port power is not automatically turned on. A Power Enable command is required to turn on the port.

### **Overview (continued)**

### 9.1.1.4 Manual/Diagnostic

The use of this mode is intended for system diagnostic purposes only in the event that ports are not performing as expected in Semiauto or Auto modes.

The port performs the functions as configured in the registers. There is no automatic state change. Singular detection and classification measurements will be performed when commanded. Ports will be turned on immediately after a Power Enable command without any detection or classification measurements. Even though multiple classification events may be provided, the port voltage will reset immediately after the last finger, resetting the PD.

#### 9.1.1.5 Power Off

The port is powered off and does not perform a detection, classification, or power-on. In this mode, Status and Enable bits for the associated port are reset.

### 9.1.2 Channel versus Port Terminology

Throughout this document the use of the terms *port* and *channel* will be used regularly, but these terms are **not interchangeable**. Instead the term *port* will be used to refer to the PSE PI (Power Interface), which is most commonly associated with a RJ45 connector, whereas the term *channel* will be used to refer to the individual power path or paths associated with each *port*.

Previous PSE devices commonly equated the number of controlled outputs as *ports* as each output would be dedicated to providing power on either the ALT-A **or** Alt-B pair set of a RJ45 jack/Ethernet port. However, with the adoption of 4-Pair power delivery sending power down both the ALT-A **and** ALT-B pair sets, there is now a need to differentiate between 2-pair and 4-pair capable PoE *ports*. Even more so, with the requirement to provide individual current limiting per pair set, any 4-pair *port* will now use two *channels* per 4-pair *port* to ensure safe and reliable delivery of power down each pair set.

As the TPS23881is an 8-channel PSE controller. It can be configured to support up to eight 2-pair PoE ports or four 4-pair PoE ports, or any combination thereof where each 2-pair port accounts for one channel, and each 4-pair port accounts for 2 channels.

#### 9.1.3 Requested Class versus Assigned Class

The *requested* class is the classification the PSE measures during mutual identification prior to turnon, whereas the *assigned* class is the classification level the channel was powered on with based on the power allocation setting in register 0x29h. In most cases where the power allocation equals or exceeds the *requested* class, the *requested* and *assigned* classes will be the same. However, in the case of power demotion, these values will differ.

For example: If a Class 8 PD is connected to a 60 W (Class 6) limited PSE port, the *requested* class reports "Class 8", while the *assigned* class reports "Class 6".

The requested classification results are available in registers 0x0C-0F

The assigned classification results are available in registers 0x4C-4F

#### **NOTE**

There is no Assigned Class assigned for ports/channels powered out of Manual/Diagnostic mode.

### **Overview (continued)**

#### 9.1.4 Power Allocation and Power Demotion

The Power Allocation settings in register 0x29 sets the maximum power level a port will power on. Settings for each Class level from 2-pair 4 W (Class 1) up to 4-pair 90 W (Class 8) have been provided to maximize system design flexibility.

#### NOTE

The Power Allocation settings in register 0x29 do not set the power limit for a given port. The port and channel power limiting is configured with the 2P (registers 0x1E- x 21) and 4P (0x2A - x2B) policing registers

During a turn on attempt, if a PD presents a classification level greater than the power allocation setting for a port, the TPS23881 limits the number of classification fingers presented to the PD prior to turn on based on the power allocation settings in register 0x29. This behavior is called *Power Demotion* as it is the number of fingers presented to the PD that sets the maximum level of power the PD is allowed to draw before the PSE is allowed to disable it.

#### NOTE

Power Demotion on a port is limited to the Type boundaries as the only means of communication from the PSE to the PD is the number of classification fingers prior to turn on.

1 finger = 15.4 W, 3 fingers = 30 W, 4 fingers = 60 W, and 5 fingers = 90W

### **Table 2. Single Signature PD Power Demotion Table**

| Power Allocation |            | Assigned Class Value (based on the PD connected at the port) |            |            |            |            |  |  |  |  |  |  |

|------------------|------------|--------------------------------------------------------------|------------|------------|------------|------------|--|--|--|--|--|--|

| Register 0x29    | Class 3 PD | Class 4 PD                                                   | Class 5 PD | Class 6 PD | Class 7 PD | Class 8 PD |  |  |  |  |  |  |

| 15W              | Class 3    | Class 3                                                      | Class 3    | Class 3    | Class 3    | Class 3    |  |  |  |  |  |  |

| 30W              | Class 3    | Class 4                                                      | Class 4    | Class 4    | Class 4    | Class 4    |  |  |  |  |  |  |

| 45W              | Class 3    | Class 4                                                      | Class 5    | Class 4    | Class 5    | Class 5    |  |  |  |  |  |  |