# Integrated 10/100/1000 Gigabit Ethernet Transceiver

#### **Features**

- IEEE 802.3 compliant 1000BASE-T, 100BASE-TX, and 10BASE-T

- Support auto-negotiation

- Support timing programmable MII/ GMII/ RGMII (delay clock, and driving current etc.)

- Support 3 power saving modes

- Support software based Smart Cable Analyzer (SCA)

- Support auto MDI/MDIX (auto negotiation or force mode)

- Support auto polarity correction

- Supports programmable LED modes and LED driving current

- Supports speed down shift feature

- Built in synchronization FIFO to support jumbo frame size up to 10KB in giga mode (4KB in 10M/100M mode)

- Supports 2.1v and 1.2v built-in regulator control

- Provide a 125MHz free running clock

- Operating voltage 3.3v/ (2.5v option for RGMII)/ 1.8v/ 1.2v

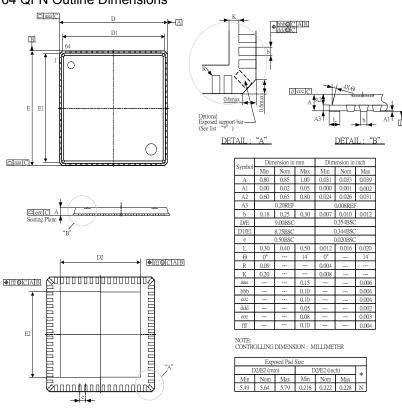

- 64-pin QFN lead-free package

- Supports Lead Free package (Please refer to the Order Information)

#### **General Description**

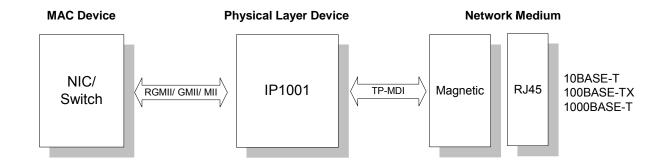

IP1001 is an integrated physical layer device for 1000BASE-T, 100BASE-TX, and 10BASE-T applications. IP1001 supports MII, GMII and RGMII for different types of 10/100/1000Mb Media Access Controller (MAC). It supports Auto MDI/MDIX function to simplify the network installation and reduce the system maintenance cost. IP1001 supports speed down shift feature for a poor link quality to guarantee data transmission. Cable analysis function "SCA" is supported by programming MII registers of IP1001 through MDC/MDIO.

IP1001 supports 2 types of power saving modes; i.e., power down mode defined in IEEE802.3, and APS (auto power saving).

1/48

# **Table of Contents**

| Fea | atures   |                                                         |    |

|-----|----------|---------------------------------------------------------|----|

| Gei | neral De | escription                                              | 1  |

| Tab | le of Co | ontents                                                 | 2  |

| Rev | vision H | listory                                                 | 3  |

| 1   | Pin dia  | agram                                                   | 4  |

| 2   | Pin de   | escription                                              | 5  |

| 3   | Functi   | ional Description                                       |    |

|     | 3.1      | Medium Dependent Interface (MDI) for Twisted Pair Cable | 16 |

|     | 3.2      | MAC Interface (RGMII/ GMII/ MII)                        |    |

|     | 3.3      | Serial Management Interface                             |    |

|     | 3.4      | LED                                                     |    |

|     | 3.5      | Auto MDI/MDIX Crossover                                 |    |

|     | 3.6      | Polarity Correction                                     |    |

|     | 3.7      | Auto-Negotiation                                        |    |

|     | 3.8      | Smart speed                                             |    |

|     | 3.9      | Power supply                                            |    |

|     | 3.10     | Digital Internal Function                               |    |

|     | 3.11     | IEEE802.3 1000BASE_T Test mode                          |    |

| 4   |          | ter Descriptions                                        |    |

|     | 4.1      | Control Register (Reg0)                                 |    |

|     | 4.2      | Status Register (Reg1)                                  |    |

|     | 4.3      | PHY Identifier Register (Reg2)                          |    |

|     | 4.4      | PHY Identifier Register (Reg3)                          |    |

|     | 4.5      | Advertisement Register (Reg4)                           |    |

|     | 4.6      | Link Partner's Ability Register (Base Page) (Reg5)      |    |

|     | 4.7      | Auto-Negotiation Expansion Register (Reg6)              |    |

|     | 4.8      | Auto-Negotiation Next Page Transmit Register (Reg7)     |    |

|     | 4.9      | Auto-Negotiation Link Partner Next Page Register (Reg8) |    |

|     | 4.10     | 1000BASE-T Control Register (Reg9)                      |    |

|     | 4.11     | 1000BASE-T Status Register (Reg10)                      |    |

|     | 4.12     | Extended Status Register (Reg15)                        | 37 |

|     | 4.13     | PHY Specific Control & Status Register (Reg16)          |    |

|     | 4.14     | PHY Link Status Register (Reg17)                        |    |

|     | 4.15     | PHY Specific Control Register2 (Reg20)                  |    |

| 5   |          | ical Characteristics                                    |    |

|     | 5.1      | Absolute Maximum Rating                                 |    |

|     | 5.2      | DC. Characteristic                                      |    |

|     | 5.3      | AC Timing                                               |    |

|     | 5.4      | Thermal Data                                            |    |

| 6   |          | Information                                             |    |

| 7   | Packa    | age Detail                                              | 48 |

# **Revision History**

| Revision #    | Change Description                                                                                                                                                                                                                               |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IP1001-DS-R01 | Initial release.                                                                                                                                                                                                                                 |

| IP1001-DS-R02 | Assign pin number to power pins. Modify CAP pin description. Modify package dimension.                                                                                                                                                           |

| IP1001-DS-R03 | Modify features description. Modify the pin desecration for X1. Change the part number to "IP1001 LF". Modify the LED pins description. Modify the RGMII/GMII driving current. Modify the operating temperature range. Modify RGMII/GMII timing. |

| IP1001-DS-R04 | Modify LED mode description of pin 55. Modify DC characteristics. Add thermal parameters.                                                                                                                                                        |

| IP1001-DS-R05 | Correct an editing error found on Page 4.                                                                                                                                                                                                        |

| IP1001-DS-R06 | Modify Maximum voltage of AVDD to 2.2V on Page 42 DC. Characteristic.                                                                                                                                                                            |

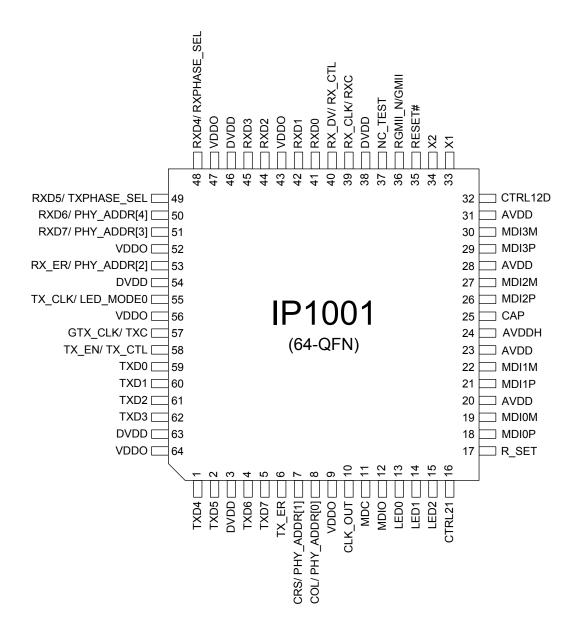

### 1 Pin diagram

# 2 Pin description

### Abbreviation

| Abbreviation | Description                                                          |  |  |  |  |  |  |

|--------------|----------------------------------------------------------------------|--|--|--|--|--|--|

| PWR          | Power and Ground Pin                                                 |  |  |  |  |  |  |

| I            | Schmitt trigger input                                                |  |  |  |  |  |  |

| LI           | The input is latched at the end of reset and used as a default value |  |  |  |  |  |  |

| 0            | Output                                                               |  |  |  |  |  |  |

| I/O          | Schmitt trigger input/ Output                                        |  |  |  |  |  |  |

| OD           | Open drain output                                                    |  |  |  |  |  |  |

| IPH          | Schmitt trigger input with 60 kohm internal pull high                |  |  |  |  |  |  |

| IPL          | Schmitt trigger input with 60 kohm internal pull low                 |  |  |  |  |  |  |

| IPECL        | PECL input                                                           |  |  |  |  |  |  |

| OPECL        | PECL output                                                          |  |  |  |  |  |  |

| Pin no.       | Label         | Туре         | Description                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------|---------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuration | n             |              |                                                                                                                                                                                                                                                                                                                                                                                               |

| 50,51,53,7,8  | PHY_ADDR[4:0] | LI/O,<br>IPH | PHY Address Configuration These pins are latched upon power-on reset to define the PHY address of IP1001. PHY_ADDR[1:0] are internally pulled high. PHY_ADDR[4:0] share the same pins with RXD6, RXD7, RX_ER, CRS and COL.                                                                                                                                                                    |

| 36            | RGMII_N/GMII  | IPL          | GMII (MII)/ RGMII MAC Interface Mode Selection This pin is latched upon power-on reset to define the RGMII/GMII interface mode. 0: RGMII mode (default) 1: GMII/MII mode                                                                                                                                                                                                                      |

| 48            | RXPHASE_SEL   | LI/O         | RX_CLK Phase Selection This pin is latched upon power-on reset, and acts as the initial value of register16 [0] to adjust timing of RX_CLK.  0: No output delay is added on RX_CLK  1: An output delay is added on RX_CLK (with respect to RXD, about 2ns delay in 100BASE-T, and about 4ns delay in 100BASE-TX and 10BASE-T).  RXPHASE_SEL shares the same pin with RXD4.                    |

| 49            | TXPHASE_SEL   | LI/O         | GTX_CLK/TXC Phase Selection This pin is latched upon power-on reset, and acts as the initial value of register16 [1] to adjust timing of GTX_CLK/TXC.  0: No input delay is added on GTX_CLK/TXC  1: An input delay is added on GTX_CLK/TXC (with respect to TXD, about 2ns delay in 1000BASE-T, and about 4ns delay in 100BASE-TX and 10BASE-T).  TXPHASE_SEL shares the same pin with RXD5. |

| Pin no. | Label         |       |        | Туре | Descripti     | on                           |                                                                                                                             |

|---------|---------------|-------|--------|------|---------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

|         | MAC Interface |       |        |      |               |                              |                                                                                                                             |

|         | GMII          | RGMII | MII    |      |               |                              |                                                                                                                             |

| 57      | GTX_CLK       | TXC   |        | I    | GMII/RG       | MII Transı                   | mit Clock                                                                                                                   |

|         |               |       |        |      | I/F           | MDI<br>speed                 | Description                                                                                                                 |

|         |               |       |        |      | GMII<br>Mode  | Gigabit                      | 125Mhz input. IP1001 utilizes this clock to sample TXD[7:0], TX_ER and TX_EN at the rising edge.                            |

|         |               |       |        |      |               | 10/100M<br>bps               | Not used.                                                                                                                   |

|         |               |       |        |      | RGMII<br>Mode | Gigabit                      | 125Mhz input. IP1001 utilizes this clock to sample TXD[3:0] and TX_CTL at both the rising edge and falling edge of GTX_CLK. |

|         |               |       |        |      |               | 100Mbps                      | 25Mhz input. IP1001 utilizes this clock to sample TXD[3:0] and TX_CTL at both the rising edge and falling edge.             |

|         |               |       |        |      |               | 10Mbps                       | 2.5Mhz input. IP1001 utilizes this clock to sample TXD[3:0] and TX_CTL at both the rising edge and falling edge.            |

| 55      |               |       | TX_CLK | 0    | MII Trans     | smit Clock                   |                                                                                                                             |

|         |               |       |        |      | I/F           | MDI<br>speed                 | Description                                                                                                                 |

|         |               |       |        |      | GMII<br>Mode  |                              | Not used.  25Mhz output. IP1001 uses the clock to sample TX_EN, TX_ER, and TXD[3:0].                                        |

|         |               |       |        |      |               | 10Mbps                       | 2.5Mhz output. IP1001 uses the clock to sample TX_EN, TX_ER, and TXD[3:0].                                                  |

|         |               |       |        |      | RGMII<br>Mode | Gigabit<br>100Mbps<br>10Mbps | Not used. This pin should be left open for normal operation.                                                                |

| Pin no.     | Label         |          |          | Туре | Description                                          | on                             |                                                                                                                                                                                          |

|-------------|---------------|----------|----------|------|------------------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | MAC Interface |          |          |      |                                                      |                                |                                                                                                                                                                                          |

|             | GMII          | RGMII    | MII      |      |                                                      |                                |                                                                                                                                                                                          |

| 58          | TX_EN         | TX_CTL   | TX_EN    | I    | GMII and MII Transmit Enable/ RGMII Transmit Control |                                |                                                                                                                                                                                          |

|             |               |          |          |      | I/F                                                  | MDI<br>speed                   | Description                                                                                                                                                                              |

|             |               |          |          |      | GMII<br>Mode                                         |                                | Indicates the valid data is present on the data bus of TXD. Synchronous to the rising edge of GTX_CLK (Gigabit) or TXC_CLK (10/100M).                                                    |

|             |               |          |          |      | RGMII<br>Mode                                        |                                | The TX_CTL indicates a signal like TX_EN at the rising edge of TXC. A signal like TX_ER is derived by the logical operation of latched "TX_EN" and the value at the falling edge of TXC. |

| 5,4,2,1     | TXD[7:4]      |          |          | I    |                                                      |                                | description of pin 57.                                                                                                                                                                   |

| 62,61,60,59 | TXD[3:0]      | TXD[3:0] | TXD[3:0] | I    | _                                                    |                                | ansmit Data<br>description of pin 57.                                                                                                                                                    |

| 6           | TX_ER         |          | TX_ER    | I    | GMII and                                             | I MII Trans                    | smit Error                                                                                                                                                                               |

|             |               |          |          |      | I/F<br>GMII                                          | MDI<br>speed<br>Gigabit        | Description  A "high" state present on this pin indicates transmit data                                                                                                                  |

|             |               |          |          |      | Mode                                                 |                                | error or carrier extension. It is synchronous to GTX_CLK                                                                                                                                 |

|             |               |          |          |      |                                                      | , 10Mbps                       | A "high" state present on this pin indicates transmit data error. It is synchronous to TX_CLK                                                                                            |

|             |               |          |          |      | RGMII<br>Mode                                        | Gigabit,<br>100Mbps,<br>10Mbps | Not used.                                                                                                                                                                                |

| Pin no.     | Label         |        |        | Туре | Descripti           | ion                                       |                                                                                                                                                                                      |

|-------------|---------------|--------|--------|------|---------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | MAC Interface |        |        |      |                     |                                           |                                                                                                                                                                                      |

|             | GMII          | RGMII  | MII    |      |                     |                                           |                                                                                                                                                                                      |

| 39          | RX_CLK        | RXC    | RX_CLK | 0    | GMII/ RO            | GMII Rece                                 | ive Clock.                                                                                                                                                                           |

|             |               |        |        |      | I/F                 | MDI<br>speed                              | Description                                                                                                                                                                          |

|             |               |        |        |      | GMII<br>Mode        | Gigabit                                   | IP1001 sends out RXD[7:0],<br>RXDV and RX_ER at the<br>rising edge of RX_CLK.                                                                                                        |

|             |               |        |        |      |                     | ·                                         | 25Mhz output. IP1001 sends out RXD[3:0], RXDV and RX_ER at the rising edge of RX_CLK.                                                                                                |

|             |               |        |        |      |                     | ·                                         | 2.5Mhz output. IP1001 sends out RXD[3:0], RXDV and RX_ER at the rising edge of RX_CLK.                                                                                               |

|             |               |        |        |      | RGMII<br>Mode       | Gigabit                                   | 125Mhz output. IP1001 sends out RXD[3:0] and RX_CTL at both the rising edge and falling edge of RXC.                                                                                 |

|             |               |        |        |      |                     | 100Mbps                                   | 25Mhz output. IP1001 sends out RXD[3:0] and RX_CTL at both the rising edge and falling edge of RXC.                                                                                  |

|             |               |        |        |      |                     | 10Mbps                                    | 2.5Mhz output. IP1001 sends out RXD[3:0] and RX_CTL at both the rising edge and falling edge of RXC.                                                                                 |

| 40          | RX_DV         | RX_CTL | RX_DV  | 0    | GMII and<br>Control | d MII Rece                                | eive Enable/ RGMII Receive                                                                                                                                                           |

|             |               |        |        |      | I/F                 | MDI<br>speed                              | Description                                                                                                                                                                          |

|             |               |        |        |      | GMII<br>Mode        | 100Mbps                                   | RX_DV indicates the valid data is present on the data bus of RXD. Synchronous to the rising edge of RX_CLK.                                                                          |

|             |               |        |        |      | RGMII<br>Mode       | Gigabit<br>100Mbps<br>10Mbps              | RX_CTL indicates a signal like RX_DV at the rising edge of TXC. A signal like RX_ER is derived by the logical operation of latched RX_DV and the value at the falling edge of RX_CLK |

| 51,50,49,48 | RXD[7:4]      |        |        | 0    | Please s<br>RXD[7:4 | see the pin<br>] share the<br>DDR[3:4], ] | a (high nibble) description of pin 39. e same pins with TXPHASE_SEL, and                                                                                                             |

| Pin no.     | Label         |          |          | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|-------------|---------------|----------|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|             | MAC Interface |          |          |       |                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|             | GMII          | RGMII    | MII      |       |                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 45,44,42,41 | RXD[3:0]      | RXD[3:0] | RXD[3:0] | 0     | GMII/RGMII/MII Receive Data Please see the pin description of pin 39.                                                                                                                                                                                                                                                                                                               |  |  |

| 53          | RX_ER         |          | RX_ER    | O     | GMII and MII Receive Error  RX_ER shares the same pin with PHY_ADDR2.  I/F MDI Description speed  Gigabit A "high" state present on this pin indicates received data error or carrier extension. It is synchronous to RX_CLK  100Mbps A "high" state present on this pin indicates received data error. It is synchronous to RX_CLK  Gigabit, Not used.  RGMII 100Mbps, Mode 10Mbps |  |  |

| 7           | CRS           |          | CRS      | IPH/O | GMII/MII Carrier Sense It asserts during either the transmission or the reception.  CRS charge the same pip with DHV ADDR1                                                                                                                                                                                                                                                          |  |  |

| 8           | COL           |          | COL      | IPH/O | CRS shares the same pin with PHY_ADDR1.  GMII/MII Collision If IP1001 operates in half mode, it asserts when both transmission and reception are running. If IP1001 works in full duplex mode, COL is always idle (logic low).  COL shares the same pin with PHY_ADDR0.                                                                                                             |  |  |

| Pin no.                                                       | Pin no. Label T                                                          |      | Description                                                                                                                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                           |  |  |  |  |

|---------------------------------------------------------------|--------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--|--|--|--|

| LED Display                                                   |                                                                          |      | •                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                           |  |  |  |  |

| 55 LED_MODE0                                                  |                                                                          | LI/O | LED_MODE[1:0] Mode3. LED_MODE1 is defined by pin or LED_MODE0 is After power up, t register during th  Since LED_MODE set pin 55 to sele | LED Mode Selection (MODE0~MODE3).  LED_MODE[1:0] can provide 4 LED display modes, Mode0-Mode3.  LED_MODE1 is set by register16[15]. LED_MODE0 is defined by pin or by register16[14]. The pin state of LED_MODE0 is latched upon reset and set to register 16[14 After power up, the designer can configure LED_MODE[1:0] register during the operation.  Since LED_MODE1 is set to "0" upon reset, the designer can set pin 55 to select "00" or "01" display mode if the register 16[15:14] is unchanged. |                                                                           |  |  |  |  |

| · · ·                                                         | 15,14,13 LED2, LED1,<br>LED0                                             |      | , LED output pins 0,1,2                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                           |  |  |  |  |

|                                                               | Mode0                                                                    |      | Mode1                                                                                                                                    | Mode2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Mode3                                                                     |  |  |  |  |

| LED_Mode1,<br>LED_Mode0                                       | 00                                                                       | (    | 01                                                                                                                                       | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 11                                                                        |  |  |  |  |

| LED0                                                          | 10/100M Link/A 0: link off 1: 10/100M link Flash: TX or RX 100M Link/Act | on ( | Bi-color mode<br>{LED0, LED1}=<br>10= 1G Link;<br>01=10/100M Link;                                                                       | 1G Link/Act 0: link off 1: Giga link on Flash: TX or RX 100M Link/Act                                                                                                                                                                                                                                                                                                                                                                                                                                       | Bi-triple-color mode<br>{LED0, LED1}=<br>10= 1G Link;<br>01= 100M Link    |  |  |  |  |

|                                                               | 0: link off<br>1: 100M link on<br>Flash: TX or RX                        |      | 00= link off<br>11= link off                                                                                                             | 0: link off<br>1: 100M link on<br>Flash: TX or RX                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 00= 10M Link;<br>11= link off                                             |  |  |  |  |

| LED2  1G Link/Act 0: link off 1: Giga link on Flash: TX or RX |                                                                          | (    | Act<br>0: link off or idle<br>1: TX or RX                                                                                                | 10M Link/Act<br>0: link off<br>1: 10M link on<br>Flash: TX or RX                                                                                                                                                                                                                                                                                                                                                                                                                                            | Link/ Act<br>0: link off<br>1: 10/100M/giga link<br>on<br>Flash: TX or RX |  |  |  |  |

| Pin no.     | Label                       | Type | Description                                                                                                                                                                                  |  |  |  |  |

|-------------|-----------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Serial Mana | Serial Management Interface |      |                                                                                                                                                                                              |  |  |  |  |

| 11          | MDC                         | I    | Management Data Clock. MDC is the management data clock reference. A continuous clock is not expected. The maximum frequency supported is 12.5 MHz.                                          |  |  |  |  |

| 12          | MDIO                        | I/O  | Management Data Input Output. MDIO transfers management data in and out of the device synchronous to MDC. This pin should be connected to VDDO through a $5.1$ -k $\Omega$ pull up resistor. |  |  |  |  |

| Pin no.                     | Label                   | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|-----------------------------|-------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Medium Inte                 | Medium Interface        |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 29,26,21,18,<br>30,27,22,19 | MDI[3:0]P,<br>MDI[3:0]M | I/O  | Twisted- Pair Media Dependent Interface In 1000BASE-T mode, all 4 pairs are both input and output at the same time. In 100BASE-TX and 10BASE-T mode, MDI[0]P/M are used for transmit pair under MDI configuration, and is used for receive pair under MDIX configuration. MDI[1]P/M are used for receive pair under MDI configuration, and is used for transmit pair under MDIX configuration. MDI[2]P/M and MDI[3]P/M are unused in 100BASE-TX and 10BASE-T mode. |  |  |  |  |

| Pin no.      | Label   | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Miscellaneou | IS      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

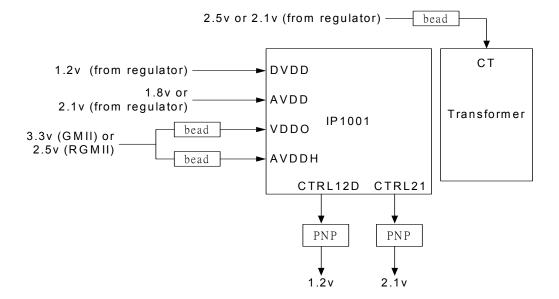

| 16           | CTRL21  | 0    | Regulator Control.  The internal linear regulator uses this pin to control an external PNP transistor to generate a 2.1v voltage source. IP1001 uses the AVDDH as a reference voltage, which can be 3.3v or 2.5v as shown in the following figure. The 2.1v power source is used for center tap of transformer and AVDD. The built in regulator works only if AVDD pins are connected to the collector of the external PNP as shown in the following figure. If AVDD pins are connected to an external power source instead of the collector of PNP, the function of CTRL21 doesn't work.  AVDDH (3.3v/ 2.5v)  CTRL21  AVDD (2.1v)               |

|              |         |      | This pin can be left open if it is not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 32           | CTRL12D | O    | Regulator Control.  The internal linear regulator uses this pin to control an external PNP transistor to generate a 1.2v voltage source. IP1001 uses the VDDO as a reference voltage, which can be 3.3v or 2.5v as shown in the following figure. The 1.2v power source is used for DVDD.  The built in regulator works only if DVDD pins are connected to the collector of the external PNP as shown in the following figure. If DVDD pins are connected an external power source instead of the collector of PNP, the function of CTRL12D doesn't work.  VDDO (3.3v/ 2.5v)  CTRL12D  DVDD (1.2v)  This pin can be left open if it is not used. |

| Pin no.   | Label   | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Miscellan | neous   | •    |                                                                                                                                                                                                                                                                                                                                                                                                                   |

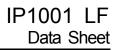

| 33        | X1      | I    | Reference Clock. 25 MHz crystal reference or oscillator input. Connects to crystal to provide the 25MHz crystal input. If a 25MHz oscillator is used, connect X1 to the oscillator's output. The input voltage of this pin should not exceed 1.8V. A voltage divider formed by 2 resistors is recommended if the output voltage of oscillator is over 1.8V. Please refer to the Crystal Specifications in detail. |

| 34        | X2      | 0    | Reference Clock. 25 MHz crystal reference.                                                                                                                                                                                                                                                                                                                                                                        |

| 35        | RESET#  | I    | Hardware reset Active low. IP1001 enters reset state when this pin is pulled low.                                                                                                                                                                                                                                                                                                                                 |

| 37        | NC_TEST | IPL  | It is used for scan test only. It should be left open for normal operation.                                                                                                                                                                                                                                                                                                                                       |

| 10        | CLK_OUT | 0    | 125M clock output It is used by external MAC device. This signal is always active after reset.                                                                                                                                                                                                                                                                                                                    |

| 25        | CAP     |      | Capacitor pin It should be connected to GND through an external 10uF capacitor. It is used to stabilize the internal analog power.                                                                                                                                                                                                                                                                                |

| 17        | R_SET   | I    | Band gap Reference $ Add \ an \ external \ 6.19k\Omega \pm 1\% \ resistor \ between \ this \ pin \ and \\ GND. \ IP1001 \ utilizes \ this \ resistor \ to \ set \ the \ current \ source. $                                                                                                                                                                                                                       |

| •                        | n description (continued) |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|--------------------------|---------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin no.                  | Label                     | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| Power pins               |                           |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 3, 38, 46,<br>54, 63     | DVDD                      |      | 1.2v digital power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 20, 23,<br>28,31,        | AVDD                      |      | 1.8v or 2.1v analog power  AVDD can be fed with external 1.8v or 2.1v power.  If there is no external 1.8v power source, AVDD can be connected the 2.1v power source generated by CTRL21. If an external 1.8v power is available, AVDD can be connected to 1.8v to reduce the power consumption.  If there is no external 2.5v power source, the center tap of transformer can be connected the 2.1v power source generated by CTRL21. If an external 2.5v power is available, the center tap of transformer can be connected to it, consuming the extra power consumption. |  |  |  |

| 9, 43, 47,<br>52, 56, 64 | VDDO                      |      | 3.3v/ 2.5v digial I/O power  VDDO is connected to 3.3v if IP1001 works in MII or GMII mode. VDDO is connected to 2.5v if IP1001 works at RGMII mode.                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 24                       | AVDDH                     |      | 3.3v/ 2.5v analog power  AVDDH can be fed with 3.3v or 2.5v, using the same power source of VDDO. Although VDDO and AVDDH use the same power source, user has to place a bead between VDDO and AVDDH to prevent the noise of AVDDH noise.                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                          | GND                       |      | Exposed PAD (E-PAD) (Thermal PAD) is Analog and Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

#### 3 Functional Description

The IP1001 is an Ethernet transceiver for 1000BASE-T, 100BASE-TX, and 10BASE-T. It uses one pair of UTP wires to transmit data and uses another pair to receive data when working in 100BASE-TX or 10BASE-T. It uses four pairs of UTP wires to transmit and to receive data when working in 1000BASE-T.

It supports auto-negotiation, including next page exchanging, speed (1000M, 100M, 100M), duplex (full/ half) mode and master/slave resolution. This device also supports RGMII/ GMII/ MII to interface a MAC device.

Registers in the IP1001 can be accessed via the SMI (MDC/MDIO). Three LEDs shows the various statuses of the device. Pair skews in the cables are automatically adjusted. Wiring errors are automatically corrected via pair swapping (automatic MDI/MDIX) and polarity correction.

#### 3.1 Medium Dependent Interface (MDI) for Twisted Pair Cable

The interface between IP1001 and CAT5 cable consists of four signal pairs, channel A, B, C and D, that are used for 1000BASE-T transmission/receiving. Each signal pair consists of two bi-directional pins that transmit and receive data stream at the same time.

When the IP1001 operates in 100BASE-TX or 10BASE-T mode, only channel A and B are used, one for transmission and the other for reception. IP1001 will handle the MDIX/MDI crossover issue of the twisted-pair wire automatically. Please refer to section 3.5 Auto MDI/MDIX Crossover for detail.

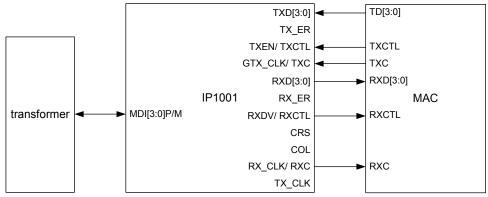

#### 3.2 MAC Interface (RGMII/ GMII/ MII)

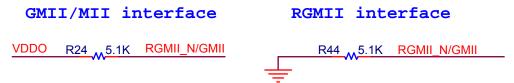

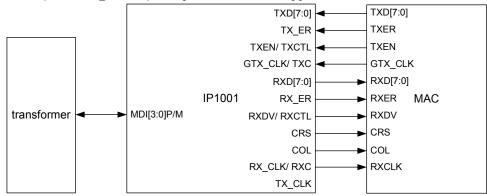

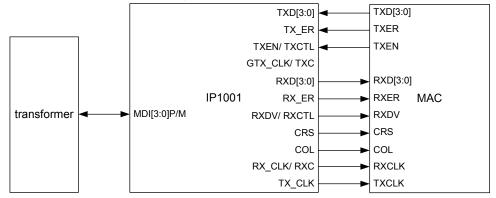

IP1001 supports RGMII and GMII/ MII interfaces. User can select the one of the interfaces by configure pin 36 and IP1001 will latch the setting at the end of hardware reset. If pin 36 is connected to GND through a resistor R44, RGMII is selected. If pin 36 is connected to VDDO through a resistor R24, GMII/ MII is selected.

If GMII mode is selected and IP1001 links in 1000BASE-T mode, GTX\_CLK, TX\_EN, TXD[7:0] and TX\_ER are input signals and should be driven by an external MAC device, TX\_CLK is driven low. RX\_CLK, CRS, RX\_DV, RXD[7:0], RX\_ER and COL are output signals to an external MAC device.

In the 100BASE-TX (10BASE-T) modes, both TX\_CLK and RX\_CLK source 25 MHz (2.5 MHz) clock respectively. TX\_EN, TXD[3:0] and TX\_ER are input signal and should be driven by an external MAC device. RX\_CLK, CRS, RX\_DV, RXD[3:0], RX\_ER and COL are output signals to an external MAC device. GTX\_CLK and TXD[7:4] signals are ignored and RXD[7:4] drives low.

If RGMII mode is selected, TXC, TX\_CTL and TXD[3:0] are input signals and should be driven by an external MAC device, TX\_CLK is driven low. RXC, RX\_CTL and RXD[3:0] are output signals to an external MAC device. RXC provides a 125 Mhz, 25 Mhz or 2.5 Mhz reference clock depending on the link speed is 1000M, 100M or 10M.

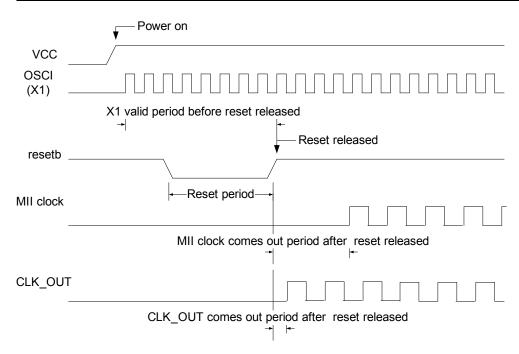

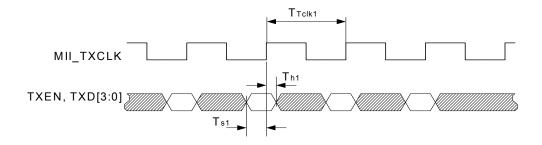

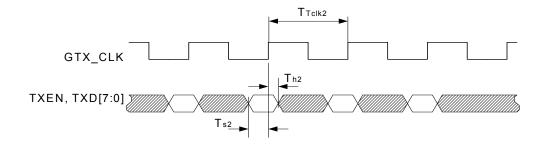

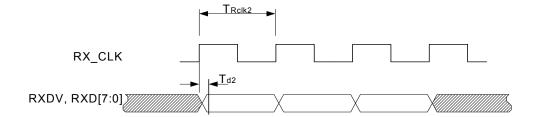

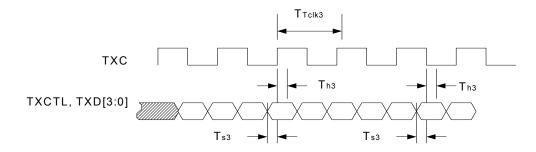

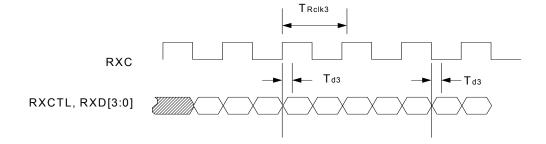

A timing adjustment on MAC interface is implemented in IP1001 by adding delay to the clock pins and changing driving capability on RX pins. User can add input delay to the GTX\_CLK(TXC) by programming pin 49 TXPHASE\_SEL or register 16.1 or add output delay to the RX\_CLK(RXC) by programming pin 48 RXPHASE\_SEL or register 16.0. The driving capability of RX signals can be configured by programming MII register 16[8:5]

#### MII/GMII/RGMII selection and signal direction

RGMII is active if pin 36 RGMII\_N/GMII is pulled low.

GMII is active if pin 15 RGMII\_N/GMII is pulled high and IP1001is linked at giga mode.

MII is active if pin 15 RGMII\_N/GMII is pulled high and IP1001 islinked at 100M, or 10M.

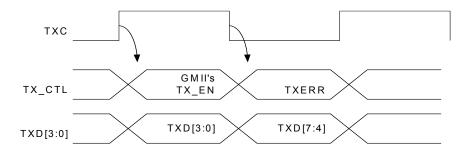

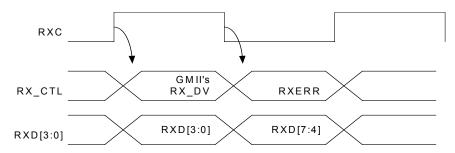

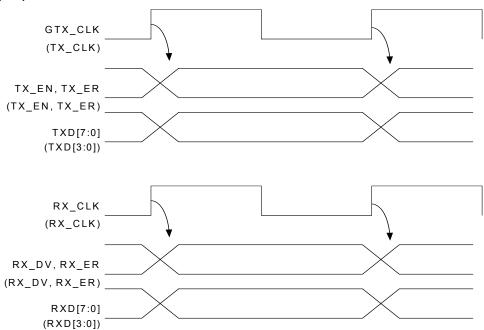

#### Waveform of RGMII and GMII (MII)

#### RGMII

#### TXERR = GMII'S TX\_EN (XOR) GMII'S TX\_ER

RXERR = GMII'S RX\_DV (XOR) GMII'S RX\_ER

#### GMII (MII)

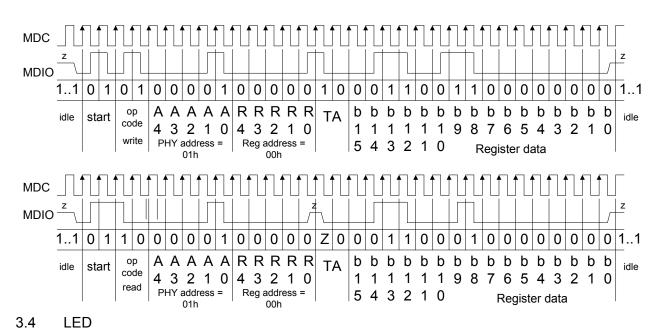

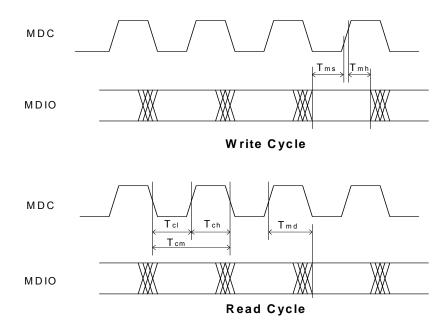

#### 3.3 Serial Management Interface

The serial management interface consisting of two pins, MDC and MDIO, provides access to the MII registers of IP1001. MDC is a clock input and runs at a maximum rate of 12.5 MHz. MDIO is a bi-directional data pin that runs synchronously to MDC. The MDIO pin requires a  $5.1-k\Omega$  pull up resistor. To access MII register in IP1001, MDC should be at least one more cycle than MDIO. That is, a complete command consists of 32 bits MDIO data and at least 33 MDC clocks.

| Frame<br>format    | <ld><ldle><start><op code=""><phy address=""><registers address=""><turnaround><data><idle></idle></data></turnaround></registers></phy></op></start></ldle></ld>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read<br>Operation  | $ <   d e > < 01 > < 10 > < A_4A_3A_2A_1A_0 > < R_4R_3R_2R_1R_0 > < Z0 > < b_{15}b_{14}b_{13}b_{12}b_{11}b_{10}b_9b_8b_7b_6b_5b_4b_3b_2b_1b_0 > <   d e > < C0 > <$ |

| Write<br>Operation | $ <  d e> < 01> < 01> < A_4A_3A_2A_1A_0> < R_4R_3R_2R_1R_0> < 10> < b_{15}b_{14}b_{13}b_{12}b_{11}b_{10}b_9b_8b_7b_6b_5b_4b_3b_2b_1b_0> <  d e> <  d $ |

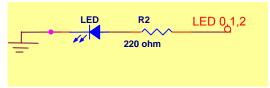

IP1001 provides 3 LED pins, LED0~2, and four LED display modes, mode0~3. User can select one of four LED modes by configuring LED\_MODE1 and LED\_MODE0. LED\_MODE1 and LED\_MODE0 are defined in register 16[15:14]. Pin 55 LED\_MODE0 defines the default value of register 16[14]. The functionality of the LED pins is shown in the table below. The driving capability of LED pins can be programmed by writing MII register 16[13].

LED mode setting

VDDO R24 M5.1K TX\_CLK/LED\_MODE0

R44 M5.1K TX\_CLK/LED\_MODE0

#### LED application circuit

#### Mode 0 & mode 2

#### Mode 1

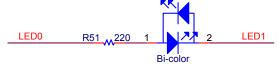

Bi-color LED configuration

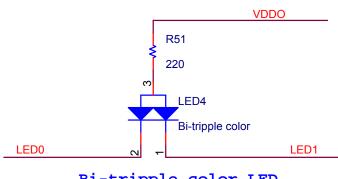

#### Mode 3

Bi-tripple color LED configuration

|                         | Mode0            | Mode1                                                                             | Mode2          | Mode3                                                                           |

|-------------------------|------------------|-----------------------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------|

| LED_MODE1,<br>LED_MODE0 | 0,0              | 0,1                                                                               | 1,0            | 1,1                                                                             |

| Pin 13 LED0             | 10/100M Link/Act | Bi-color mode                                                                     | 1G Link/ Act   | Bi-triple-color mode                                                            |

| Pin 14 LED1             | 100M Link/Act    | {LED0, LED1}=<br>10= 1G Link;<br>01=10/100M Link;<br>00= link off<br>11= link off | 100M Link/ Act | {LED0, LED1}=<br>10= 1G Link;<br>01= 100M Link<br>00= 10M Link;<br>11= link off |

| Pin 15 LED2             | 1G Link/Act      | Act                                                                               | 10M Link/ Act  | Link/ Act                                                                       |

Note:

Link: LED on

Act (activity): LED blinking (frequency is about 10Hz)

#### 3.5 Auto MDI/MDIX Crossover

The IP1001 implements auto-crossover function, that is, users don't have to care using a crossover or non-crossover cable. Its pin mapping in MDI and MDIX modes is shown in the following table. If IP1001 interoperates with a device that does not implement auto MDI/MDIX crossover, the IP1001 makes the necessary adjustment prior to performing auto-negotiation. If the IP1001 interoperates with a device that implements auto MDI/MDIX crossover, a random algorithm as described in IEEE 802.3 section 40.4.4 determines which device performs the crossover.

When the IP1001 interoperates with a 10BASE\_T PHY or a PHY that implements auto-negotiation, IP1001 decides the MDI/MDIX by the presence of link pulses. However, when interoperating with a 100BASE\_TX PHY that does not implement auto-negotiation (i.e. link pulses are not present), IP1001 uses signal energy of receiving MLT3 signals to determine whether or not to crossover.

The auto MDI/MDIX function is turned on automatically after hardware reset and users can disable it by programming MII register 20.2. User can check if IP1001 is in MDI or MDIX type by reading MII register 17.11. Auto MDI/MDIX function is not affected by disabling auto-negotiation function.

| Pin       | MDI        |            |          | MDIX       |            |          |  |

|-----------|------------|------------|----------|------------|------------|----------|--|

|           | 1000BASE-T | 100BASE-TX | 10BASE-T | 1000BASE-T | 100BASE-TX | 10BASE-T |  |

| MDI[0]P/M | BI_DA+/-   | TX+/-      | TX+/-    | BI_DB+/-   | RX+/-      | RX+/-    |  |

| MDI[1]P/M | BI_DB+/-   | RX+/-      | RX+/-    | BI_DA+/-   | TX+/-      | TX+/-    |  |

| MDI[2]P/M | BI_DC+/-   | Unused     | Unused   | BI_DD+/-   | Unused     | Unused   |  |

| MDI[3]P/M | BI_DD+/-   | Unused     | Unused   | BI_DC+/-   | Unused     | Unused   |  |

#### 3.6 Polarity Correction

The IP1001 performs polarity correction without any manual setting. It corrects polarity errors on the receive pairs in 1000BASE-T and 10BASE-T modes automatically.

In 1000BASE-T mode, polarity correction is based on the sequence of idle symbols. In 10BASE-T mode, polarity correction is based on the detection the polarity of valid normal link pulse and idle pulse. In 100BASE-TX mode, the polarity does not matter.

#### 3.7 Auto-Negotiation

IP1001 will performs Auto-Negotiation automatically if one of the following conditions happened:

- 1) Power up reset, hardware reset, or software reset (by programming MII register 0.15).

- 2) Restart Auto-Negotiation (by programming MII register 0.9).

- 3) Transition from power down to power up (by programming MII register 0.11).

- 4) Link is down.

Once Auto-Negotiation is initiated, IP1001 sends out the appropriate base pages/ next pages to advertise its capability and negotiate with the link partner to determine speed, duplex, and master/slave. Note that IP1001 handles the base page/ next page exchanges automatically without user intervention. To link at giga mode, the link partner of IP1001 has to support Auto-Negotiation, too. Once IP1001 completes Auto-Negotiation it updates the statuses in registers 1, 5, 6, 10 and 17. The advertised abilities can be changed by writing registers 4 and 9. It is noted that a write access to register 4 or 9 has no effect once the IP1001 begins transmitting Fast Link Pulses (FLPs). This guarantees that the transmitted FLPs are consistent. Register 7 is treated in a similar way as registers 4 and 9 during additional next page exchanges.

If the link partner doesn't support Auto-Negotiation, IP1001 determines the link speed using parallel detection and the link result is either 10M half duplex or 100M half duplex. Please refer to IEEE 802.3 clause 28 and 40 for more detailed description of Auto-Negotiation.

Auto-Negotiation can be disabled by programming register 0.12. When Auto-Negotiation is disabled, the speed and duplex of IP1001 can be changed by programming registers 0.13, 0.6 and 0.8, respectively.

#### 3.8 Smart speed

IP1001 supports smart speed function. If IP1001 can't link at Gigabit speed due to cable quality, the link speed is down shift to 100M automatically if smart speed option is turned on. If the function is turned off, IP1001 will link down if it can't link at giga mode due to cable quality. The function is default on and it can be enabled/disabled by programming MII register 16.11.

#### 3.9 Power supply

IP1001 has 4 sets of power pins, DVDD, AVDD, VDDO and AVDDH. VDDO is connected to 3.3v or 2.5v depending on MAC interface is GMII or RGMII. AVDDH can use the same power source of VDDO, that is 3.3v or 2.5v, but it needs a bead to prevent VDDO noise. AVDD can be connected to 1.8v or 2.1v. If there is no external 1.8v power source, user can use the 2.1v power generated by the built in regulator (CTRL21). DVDD is connected to 1.2v. The center tap of transformer can be connected to 2.1v or 2.5v. If there is no external 2.5v power source, user can use the 2.1v power generated by the built in regulator control(CTRL21). The current limit of bead should be large enough to prevent the IR drop in power supply input.

#### 3.10 Digital Internal Function

The IP1001 integrates all necessary function blocks to achieve the communication ability over CAT5 unshielded twisted pair cables. These function blocks include analog blocks and digital blocks.

Analog function blocks includes analog to digital converter (ADC), digital to analog converter (DAC), active hybrid, and high-speed 1.25GHz transmitter/receiver. Digital function blocks include digital adaptive feed-forward equalizer (FFE), decision-feedback equalizer (DFE), echo canceller (EC), near-end-cross-talk canceller, baseline wander canceller, and digital phase lock-loop (DPLL). Some other encoding/decoding blocks are also necessary in the transmission/receiving data path.

#### 3.11 IEEE802.3 1000BASE\_T Test mode

IP1001 supports four test modes for 1000BASE\_T defined in IEEE802.3 clause 40.6. User can force IP1001 to be in test mode to characterize its waveform, jitter, and distortion by programming MII register 9[15:13].

# **Register Descriptions**

Abbreviation description

| Abbreviation | Description                    |

|--------------|--------------------------------|

| SC           | Self-Clear                     |

| LH           | Latched High                   |

| LL           | Latched Low                    |

| RO           | Read Only                      |

| R/W          | Read and Write                 |

| NA           | Not Affected                   |

| HW Reset     | Reset by RESET# pin            |

| SW Reset     | Reset by MII register 0 bit 15 |

PHY registers

The IP1001 supports a full set of PHY registers, which can be accessed through the MDC/MDIO interface.

| Register | Description                                      |

|----------|--------------------------------------------------|

| Reg0     | Control Register                                 |

| Reg1     | Status Register                                  |

| Reg2     | PHY Identifier Register                          |

| Reg3     | PHY Identifier Register                          |

| Reg4     | Auto-Negotiation advertise register              |

| Reg5     | Link Partner Ability Register                    |

| Reg6     | Auto-Negotiation Expansion Register              |

| Reg7     | Auto-Negotiation Next Page Transmit Register     |

| Reg8     | Auto-Negotiation Link Partner Next Page Register |

| Reg9     | 1000BASE-T Control Register                      |

| Reg10    | 1000BASE-T Status Register                       |

| Reg11~14 | Reserved. Do not access to these registers.      |

| Reg15    | Extended Status Register                         |

| Reg16    | PHY Specific Control Register1                   |

| Reg17    | PHY Link Status Register                         |

| Reg18~19 | Reserved. Do not access to these registers.      |

| Reg20    | PHY Specific Control Register2                   |

| Reg21~31 | Reserved                                         |

# 4.1 Control Register (Reg0)

| Bit   | Name                       | Descri   | Description                                                                    |                                               |           | HW<br>Reset | SW<br>Reset |

|-------|----------------------------|----------|--------------------------------------------------------------------------------|-----------------------------------------------|-----------|-------------|-------------|

| 0.5:0 | Reserved                   |          |                                                                                |                                               | RO        | Always      | 0           |

| 0.6   | Speed Selection            | 0.6      | 0.13                                                                           |                                               | R/W       | 1           | NA          |

|       | (MSB)                      | 1        | 1                                                                              | Reserved                                      |           |             |             |

|       |                            | 1        | 0                                                                              | 1000Mb/s                                      |           |             |             |

|       |                            | 0        | 1                                                                              | 100Mb/s                                       |           |             |             |

|       |                            | 0        | 0                                                                              | 10Mb/s                                        |           |             |             |

| 0.7   | Collision Test             |          |                                                                                | . signal test<br>_ signal test                | R/W       | 0           | 0           |

| 0.8   | Duplex Mode                |          | 1: Full duplex<br>0: Half duplex                                               |                                               |           | 1           | NA          |

| 0.9   | Restart Auto-NEG           |          | tart Auto                                                                      | o-Negotiation Process<br>ration               | R/W<br>SC | 0           | SC          |

| 0.10  | Isolate                    | electric | 1: Isolate PHY from MII, GMII, or RGMII<br>electrically<br>0: normal operation |                                               |           | 0           | 0           |

| 0.11  | Power Down                 | _        | 1: Power down 0: Normal operation                                              |                                               |           | 0           | 0           |

| 0.12  | Auto-Negotiation<br>Enable |          |                                                                                | -Negotiation Process<br>o-Negotiation Process | R/W       | 1           | NA          |

| 0.13  | Speed Selection (LSB)      | Please   | Please refer to bit 0.6 for detail information                                 |                                               |           | 0           | NA          |

| 0.14  | Loopback                   |          | 1: Enable loop back mode<br>0: Disable loop back mode                          |                                               |           | 0           | 0           |

| 0.15  | Software Reset             |          | softwar                                                                        |                                               | R/W<br>SC | 0           | 0 (SC)      |

# 4.2 Status Register (Reg1)

| Bit  | Name                         | Description                                                                                                                 | Туре     | HW<br>Reset | SW<br>Reset |

|------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------|-------------|-------------|