## Fully integrated standalone light barrier driver & receiver

## **General Description**

The epc111/112 is a general purpose, fully integrated self-contained CMOS circuit family to be used in light-barrier applications.

The chip contains a controller which drives an LED, typically an IR-LED. The LED is used in a pulsed mode to increase the signal-to-noise ratio even when there is very strong sunlight biasing the photo diode.

It contains also a high sensitive photo diode amplifier and a signal conditioning circuitry to cancel unwanted environmental light including strong sunlight and pulsed light sources. The receiver is built around a synchronous demodulator circuitry. Two output signals with different threshold levels are implemented in order to trigger the light barrier output or to indicate light reserve.

The chip also includes a power supply circuitry to establish all internally required voltages from one source only.

It can be used as a standalone device forming the whole core of an industrial light barrier.

## **Features**

- Fully integrated light barrier chip

- Needs just a photo diode and a LED with a LED driver

- Various types are available, i.e. high sensitivity or high speed

- Integrated clock generator

- CSP10 package with very small footprint or standard QFN16 package available

## **Applications**

- Light barriers ranging from millimeters to tens of meters

- Smoke detectors

- Liquid detectors

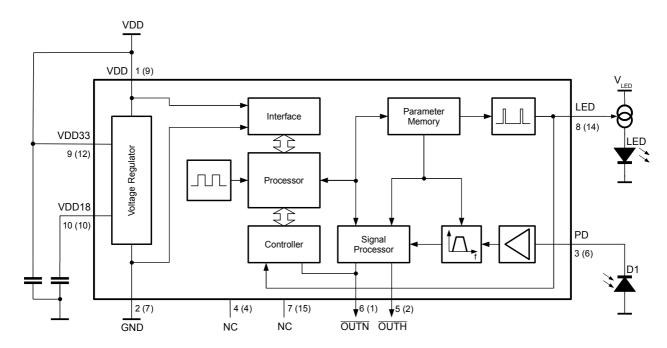

## **Functional Block Diagram**

for 10-Pin Chip Scale Package (for 16-pin QFN Package)

Figure 1: Block Diagram

| Туре   | Response Time | Sensitivity   | Typical Application       |

|--------|---------------|---------------|---------------------------|

| epc111 | Medium        | Medium (High) | Long range light barrier  |

| epc112 | Fast          | Medium        | High speed detection rate |

Table 1: Characteristics of available types

1

| Absolute Maximum Ratings                          | Recommended Operating Conditions |                                         |      |      |       |

|---------------------------------------------------|----------------------------------|-----------------------------------------|------|------|-------|

| Power Supply Voltage at pin VDD                   | -0.3V to +5.5V                   |                                         | Min. | Max. | Units |

| Voltage to any pin except VDD                     | -0.3V to VDD +0.3 V              | Supply voltage at VDD (=VDD33)          | 3.0  | 3.6  | V     |

| Output current at any pin except LED              | -6mA to +6mA                     | Supply voltage at VDD33 (=VDD)          | 3.0  | 3.6  | V     |

| Power Consumption with maximum load               | 125 mW                           | Operating Temperature (T <sub>o</sub> ) | -40° | +85° | С     |

| Lead Temperature solder, 4 sec. (T <sub>L</sub> ) | +260°C                           | Relative Humidity (non-condensing)      | +5   | +95  | %     |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Recommended operating conditions indicate conditions for which the device is intended to be functional, but do not guarantee specific performance limits. For guaranteed specific - ations and test conditions, see Electrical Characteristics.

**Note 2:** This device is a highly sensitive CMOS ac current amplifier with an ESD rating of JEDEC HBM class 0 (<250V). Handling and assembly of this device should only be done at ESD protected workstations.

## **Electrical Characteristics**

$3.0V < V_{DD} < 3.6V$ ,  $-40^{\circ}C < T_{A} < +85^{\circ}C$ , unless otherwise specified

### **General Data**

| Symbol             | Parameter                  | Conditions/Comments                   | Conditions/Comments                           |                       | Values |      |       |

|--------------------|----------------------------|---------------------------------------|-----------------------------------------------|-----------------------|--------|------|-------|

|                    |                            |                                       |                                               | Min.                  | Тур.   | Max. | 1     |

| V <sub>N</sub>     | Power supply voltage       | at VDD and VDD33                      |                                               | 3.0                   | 3.3    | 3.6  |       |

| $V_{PUP}$          | Power-up Threshold Voltage | Voltage at VDD33 when t               | he device starts up                           | 2.4                   |        | 3    | V     |

| $V_{PP}$           | Ripple on supply voltage,  | Туре                                  | Type Input pulse I <sub>PD NST</sub>          |                       |        |      |       |

|                    | peak to peak               | epc111                                | 60nA                                          |                       |        | 250  | mV    |

|                    |                            | epc112                                | 108nA                                         |                       |        | 600  | mV    |

| I <sub>DD_OP</sub> | Current consumption        | in operation mode I <sub>PD</sub> = 0 | mA, no load                                   |                       |        | 2    | mA    |

| V <sub>NOH</sub>   | Output high voltage OUTN   |                                       |                                               | V <sub>N</sub> - 0.5V |        |      | V     |

| V <sub>NOL</sub>   | Output low voltage OUTN    | @ 4mA source                          | @ 4mA source                                  |                       |        | 0.5  | V     |

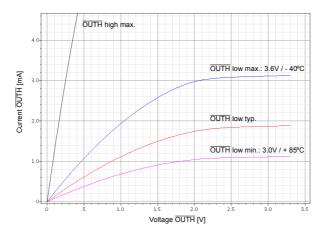

| V <sub>HOH</sub>   | Output high voltage OUTH   | see Figure 6                          | see Figure 6                                  |                       |        |      |       |

| V <sub>HOL</sub>   | Output low voltage OUTH    | @ 3mA source. See Figu                | @ 3mA source. See Figure 6.                   |                       |        | 0.5  | V     |

| $V_{LEDH}$         | Output high voltage        |                                       |                                               | V <sub>N</sub> - 0.5V |        |      | V     |

| $V_{LEDL}$         | Output low voltage         |                                       |                                               |                       |        | 0.5  | V     |

| I <sub>LED</sub>   | Source current maximum     | @ Pin LED                             | @ Pin LED                                     |                       |        |      | mA    |

| f <sub>clk</sub>   | Reference clock            | of internal oscillator - for i        | of internal oscillator - for information only |                       | 1      |      | MHz   |

| df <sub>clk</sub>  | Temperature drift          | of the oscillator - for inform        | of the oscillator - for information only      |                       | 640    |      | ppm/K |

| Symbol              | Parameter                      | Conditions/Comments                                                                                                                       | Types  | Values |      |      | Units             |  |

|---------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|------|------|-------------------|--|

|                     |                                |                                                                                                                                           |        | Min.   | Тур. | Max. | 1                 |  |

| I <sub>PDN</sub>    | Photo Current Sensitivity OUTN | Pulse height to trigger internal threshold                                                                                                | epc111 |        | 60   |      | nA                |  |

|                     |                                | OUTN. Refer to Functional Description                                                                                                     | epc112 |        | 108  |      | 1                 |  |

| I <sub>PDH</sub>    | Photo Current Sensitivity OUTH |                                                                                                                                           | epc111 |        | 96   |      | nA                |  |

|                     |                                | OUTH. Refer to Functional Description                                                                                                     | epc112 |        | 144  |      |                   |  |

| I <sub>pulse</sub>  | Maximum Input Pulse Current    | If the input current pulse is above this level,                                                                                           | epc111 |        |      | 100  | μA                |  |

|                     |                                | the recovery time $t_{\text{REC}}$ becomes $t_{\text{relax}}$ . (refer to parameter $t_{\text{relax}}$ )                                  | epc112 |        |      | 100  |                   |  |

| $I_{N\_Imin}$       | Input related noise            | @ I <sub>PDDC</sub> =0                                                                                                                    |        |        |      | 15   | nA <sub>RMS</sub> |  |

| I <sub>N_Imax</sub> | Input related noise            |                                                                                                                                           |        |        |      | 20   | nA <sub>RMS</sub> |  |

| I <sub>PDDC</sub>   | DC Photo Diode Current         | generated by ambient light with no effect to the sensitivity                                                                              |        | 0.0    |      | 2    | mA                |  |

| $C_{PD}$            | Photodiode Capacitance         | Refer to section Application Information, Photodiode Capacitance                                                                          |        |        |      | 50   | pF                |  |

| t <sub>Pulse</sub>  | LED Pulse Length               |                                                                                                                                           | epc111 |        | 2    |      | μs                |  |

|                     |                                |                                                                                                                                           | epc112 |        | 1    |      | 1                 |  |

| t <sub>Cycle</sub>  | LED Cycle Time                 |                                                                                                                                           | epc111 |        | 100  |      | μs                |  |

|                     |                                |                                                                                                                                           | epc112 |        | 10   |      |                   |  |

| t <sub>relax</sub>  | Recovery time                  | after a strong current pulse (I <sub>pulse</sub> = 100µA)                                                                                 | epc111 |        |      | 50   | μs                |  |

|                     |                                |                                                                                                                                           | epc112 |        |      | 50   |                   |  |

| t <sub>R</sub>      | Response Time                  | Minimum time from light beam detection to                                                                                                 | epc111 |        | 800  | 900  | μs                |  |

|                     |                                | status change of the output $\overline{\text{OUTN}}$ or $\overline{\text{OUTH}}$ .<br>$t_{R\_\text{MAX}}$ = ( $n_{V}$ + 1 ) * $t_{Cycle}$ | epc112 |        | 30   | 40   |                   |  |

| t⊧                  | Release Time (fall time)       | Minimum time from beam interruption to                                                                                                    | epc111 |        | 800  | 900  | μs                |  |

|                     |                                | status change of the output $\overline{OUTN}$ or $\overline{OUTH}$ .<br>$t_{F\_MAX}$ = ( $n_M$ + 1 ) * $t_{Cycle}$                        | epc112 |        | 20   | 30   |                   |  |

| $n_{\text{V}}$      | Valid pulse counts             | Number of valid (non-missing) pulses to                                                                                                   | epc111 |        | 8    |      |                   |  |

|                     |                                | trigger the output. Refer to Functional Description                                                                                       | epc112 |        | 3    |      |                   |  |

| n <sub>M</sub>      | Missing pulse counts           | Number of missing pulses to release the                                                                                                   | epc111 |        | 8    |      |                   |  |

|                     |                                | output. Refer to Functional Description                                                                                                   | epc112 |        | 2    |      |                   |  |

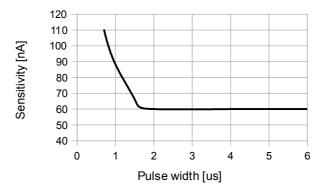

## **Other Parameters**

(typical values,  $T_{amb} = 25^{\circ}C$ ,  $V_{DD} = 3.3V$ )

Figure 2: Input Sensitivity vs. LED pulse width

#### **Connection Diagrams** NC\_GND VDD33 (8) LED (9) VDD33 6 OUTN 01 NC\_GND NC\_GND GND LED \_\_\_\_\_ (10) VDD18 OUTH (5) Top View Top View PD NC NC\_GND NC\_GND VDD **GND** PDNC (3) (2) 4 (1)0

| 10-Pin   | Chip Scale | Package  | (CSP) |

|----------|------------|----------|-------|

| 10 1 111 | Chip Benie | 1 ucmige | (CD1) |

NC\_GND

OUTH

| 10-Pin<br>CSP | 16-Pin<br>QFN             | Pin Name | Туре                          | Description                                                                                                                           |

|---------------|---------------------------|----------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 1             | 9                         | VDD      | Power Supply                  | Positive power supply. To be connect to VDD33.                                                                                        |

| 2             | 7                         | GND      | Power Supply                  | Negative power supply pin.                                                                                                            |

| 3             | 6                         | PD       | Analog Input                  | Photo diode input.                                                                                                                    |

| 4             | 4                         | NC       |                               | Do not connect this pin. Internally terminated.                                                                                       |

| 5             | 2                         | OUTH     | Digital Out<br>Load depending | Light reserve detected - see Figure 6. Threshold level around 50% above the threshold of the filtered signal level. Open drain output |

| 6             | 1                         | OUTN     | Digital Output                | Light pulses detected by the photo diode - see Functional Description Amplified and filtered signal Open drain output                 |

| 7             | 15                        | NC       |                               | Do not connect this pin. Internally terminated.                                                                                       |

| 8             | 14                        | LED      | Digital Out                   | Output to LED driver                                                                                                                  |

| 9             | 12                        | VDD33    | Power Supply                  | Positive power supply. To be connected to VDD.                                                                                        |

| 10            | 10                        | VDD18    | Decoupling                    | Pin for external filter/decoupling of the internal 1.8V supply: 4.7nF ceramic type Not for supply of external circuits                |

| n/a           | 3, 5, 8,<br>11, 13,<br>16 | NC_GND   |                               | Not connected. Connect this pins to GND (Guarding).                                                                                   |

## **Functional Description**

### Evaluation of single light pulse

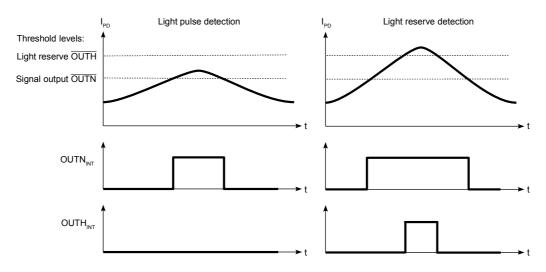

For each single light pulse, received and detected by the LED, the threshold levels are processed according to the following principle to propagate the output signals OUTN and OUTH resp. OUTN<sub>INT</sub> and OUTH<sub>INT</sub>. As far the received light pulse signal exceeds the corresponding threshold level, the pulse will be recognized as a valid pulse and the detection circuit sets the appropriate output signal OUTN INT or OUTHINT.

Figure 3: Pulse evaluation

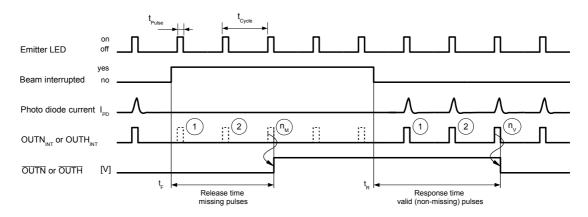

### Pulse Modulated Operation (e.g. OUTN<sub>int</sub> to OUTN)

The epc111/112 chip operates the LED and the receiver path on a pulse modulated concept. Thus, the LED is operated with short pulses whereas the receiver channel does synchronous demodulation of the received light pulses by reading the current pulses of the photodiode. This concept allows a very high sensitivity, high speed operation, and a high suppression of input ambient or foreign light (DC currents) generated by sunlight or other DC light sources like light bulbs.

In order to eliminate interference caused by modulated light, e.g. a flashing light or by other light barriers, the input signal from the photodiode is amplified, filtered, and processed by an integrated signal processor. If the photodiode signal meets the required frequency, pattern and amplitude, the output(s) are triggered. The following timing diagram shows the basic concept.

Figure 4: Pulse modulation concept

It is in fact a digital filter which counts missing and non-missing pulses to change the ou tput state of  $\overline{\text{OUTN}}$  or  $\overline{\text{OUTH}}$ .

Working principle of the digital filter e.g. for the signal OUTN<sub>int</sub> to OUTN Filter:

The aim of this programmable filter is to suppress single pulses, so they cannot trigger the output and generate a false signal.

This filter is based on a counter, which is counting up (increment) the valid pulses and counting down (decrement) the missing pulses in a weighted manner. There are separate weighting factors for valid pulses (parameter  $n_V$ ) and missing pulses (parameter  $n_M$ ). If the counter reaches the upper limit (maximum count, response time), the signal  $\overline{OUTN}$  is set to LOW. Similar in the opposite direction, if the counter reaches zero, the lower limit (minimum count, release time), the signal  $\overline{OUTN}$  is put to HIGH. With the parameters  $n_V$  and  $n_M$  the filter has the advantage of individual selectable gradients of the slopes. Counter will never exceed maximum nor minimum limit. In between it acts as an integrator of both parameters.

#### IF Pulse then

IF Pulse = valid then

Counter = Counter + ( $n_V$  \* 1024) IF counter >  $2^{15}$  (maximum limit) then Counter = maximum limit IF counter = maximum limit then  $\overline{OUTN}$  = 0

- IF Pulse = missing then

Counter = Counter - (2<sup>n</sup>M)

IF counter < 0 (minimum limit) then Counter = minimum limit

IF counter = minimum limit then OUTN = 1

### ELSE wait for Pulse

Lets assume that the photodiode does not receive light pulses for a long time: This means the light beam is interrupted. Then  $\overline{\text{OUTN}}$  is at high level. If the light beam is not interrupted anymore, the photodiode receives light pulses which are strong enough to trigger the  $\overline{\text{OUTN}}_{\text{INT}}$  threshold and the internal pulse evaluation unit (designated in Figure 3 with 'Pulse evaluation') starts to count the received pulses. If the number of received pulses reach the set level  $n_{\text{V}}$ , the output  $\overline{\text{OUTN}}$  turns to low level. Thus, single pulses cannot trigger the output and generate a false signal.

The same procedure is used when a beam changes from not interrupted to interrupted. The internal pulse evaluation unit counts the missing pulses. If the number of missing pulses reaches the level n<sub>M</sub>, OUTN is turned to high level.

The same principle applies to the counter and signal of OUTH.

The counter limit values are different, depending on the device:

| Туре   | No. of<br>Pulses n <sub>м</sub> | No. of missing Pulses n <sub>v</sub> |

|--------|---------------------------------|--------------------------------------|

| epc111 | 8                               | 8                                    |

| epc112 | 3                               | 2                                    |

Table 2: Filter coefficients

### **Light Pulse Detection Output OUTN**

The epc111/112 contains two digital outputs to indicate that a valid signal of light pulses are received by the photodiode. The first output is triggered, when the lower threshold is reached by the input signal (see Figure 3). This output is used usually to drive the output of the light barrier. This is a fully CMOS compatible digital output.

### Light Reserve Output OUTH

However, if the incoming signal is just at the trigger threshold of OUTN, an unstable situation can occur. Thus, a second output OUTH is integrated with a higher trigger threshold to indicate that a certain 'light reserve' is reached (see Figure 3). This output is usually used to drive a visible LED to indicate to the operator a stable detection function of the light barrier. To have not too short pulses OUTH, this signal is stimulated by signal OUTH Filter and synchronously reset by OUTN.

The trigger threshold of  $\overline{\text{OUTH}}$  is set approx. 50% above the trigger threshold of  $\overline{\text{OUTN}}$ .

Figure 5: synchronization  $\overline{OUTH}$  with  $\overline{OUTN}$

This output is not CMOS compatible. Its voltage is depending of the load according to Figure 6. To have still digital compatible signals a level conversion is necessary.

Figure 6: Output voltage versus output current of output  $\overline{OUTH}$

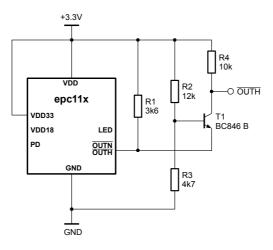

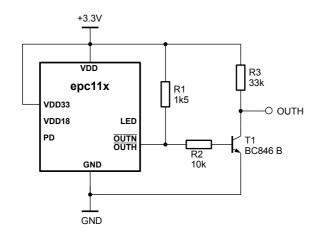

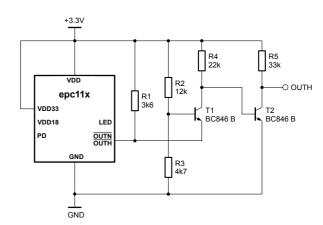

Below you find some examples for such circuits for converting OUTH levels to full CMOS compatible digital output.

Figure 7: Non-inverting, low power level shifter (additional current ca.0.6mA)

Figure 8: Simple inverting level shifter (additional current ca.1.6mA or 2.6mA)

Figure 9: Inverting, low power level shifter (additional current ca.0.8 ... 1.0mA)

# **Applications**

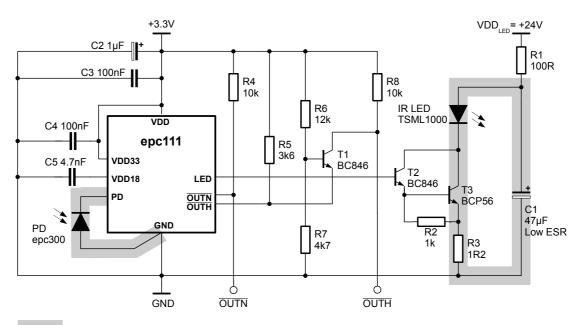

#### Long range light barrier application

Figure 10 shows the epc111 as an example in a long range light barrier application with minimal part count. The LED flashes according to the description of the previous chapter. Light of the LED is passing either direct, reflected from a reflecting object or a retro reflector to the photo diode PD. If the received light fulfills the criteria according to the description in the previous chapter, the output signals OUTN and OUTH are set.

The epc111 device is designed to operate at 3.3V power supply (VDD and VDD33).

#### LED Driver:

The output LED of the epc111 to drive the LED driver circuit is a current source capable to drive typically 1mA. For a high performance long range light barrier (>8m), an LED peak current of up to 1.5A is needed. To generate such a high LED current, an external driver circuit is necessary. The circuitry in Figure 10 is a simple implementation of such a driver circuit. The darlington circuit with T2 and T3 and R2 and R3 does the job. In order to avoid interference on the supply voltage, the supply is isolated (filtered) with R1 and C1. The high peak LED pulse current is delivered by the capacitor C1, which itself is charged by R1. Make sure, that there is no coupling of the high LED current to the ground of the epc111 or to the cathode of the photo diode. This driver circuit operates with a VDD LED in a range of 10 to 30 VDC.

Marked conductors must be short and low ohmic

C2 The epc111 device with its very sensitive input PD needs a well decoupled power supply

Figure 10: Long range light barrier application with minimal part count

#### Notice:

The schematic is for illustrating the basic circuit idea only. For the real built up the designer has to take all other additional influence factors in consideration too e.g. design rules, power rating, heat dissipation, ...

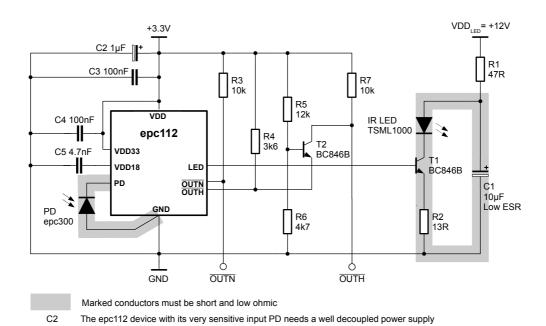

#### High speed detection rate design

Figure 11 shows the epc 112 as an example in a high speed detection rate light barrier application with minimal part count. This design is optimized for a fast reading of light beam interruptions. Whereas the working principle is similar to the above example. This driver circuit operates with a VDD<sub>LED</sub> in a range of 6 to 20 VDC.

The epc112 device is designed to operate at 3.3V power supply (VDD and VDD33).

Figure 11: High speed detection rate light barrier application with minimal part count

### Notice:

The schematic is for illustrating the basic circuit idea only. For the real built up the designer has to take all other additional influence factors in consideration too eg. design rules, power rating, heat dissipation, ...

### Design Precautions: EMC shielding

The sensitivity at pin PD is very high in order to achieve a long operation range of light barriers even without lenses in front of the IR LED and/or the photo diode. Thus, the pin PD is very sensitive to EMI. Special care should be taken to keep the PCB track at pin PD as short as possible (a few mm only!). This track should be kept away from the IR LED signal tracks and from other sources which may induce unwanted signals. It is strongly recommended to cover the chip, the photodiode and all passive components around the chip with a metal shield. A recommended part is shown in Figure 12. The pins at the bottom are to solder the shield to the PCB with electrical connection to GND. The hole in the front is the opening window for the photo diode. The backside of the PCB below the sensitive area (PD, epc111 or epc112) shall be a polygon connected to GND to shield the circuit from the backside as well.

Figure 12: Recommended EMC shield

#### **Ambient Light**

Photodiode DC current can be generated by ambient light, e.g. sunlight. DC current at pin PD does not generate a DC output signal. However, if I<sub>PDDC</sub> is above the stated maximal value, the input is saturated. This blocks the detection of AC current pulses.

### **Photodiode Capacitance**

If the photo diode capacity is above the specified value, a lower detection sensitivity and a possible higher sensitivity spread results.

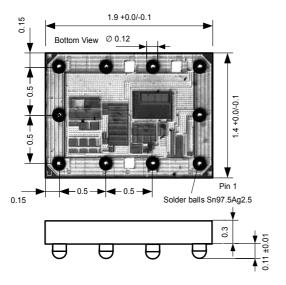

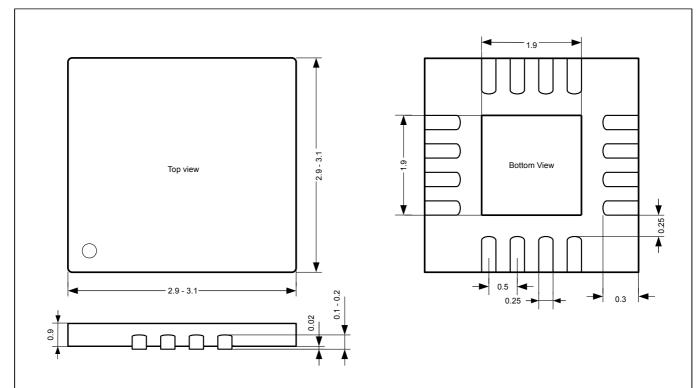

# Layout Information (all measures in mm,

### CSP-10 Package

no solder mask inside this area

0.1524

Figure 13: CSP10: Mechanical dimensions

Figure 14: CSP10: Layout recommendation

Recommendations for reliable soldering of solder balls:

- Use a pad layout similar to the one shown in Figure 14. Notice that all tracks should go underneath the solder mask area.

- Do not connect any pins direct pin to pin inside of the opening of the solder mask.

- In case of the conductors are with a Au-Ni surface finish the preferred landing pad design for the solder balls will be covering the

round landing pad with a gold surface finish as a solderable area only.

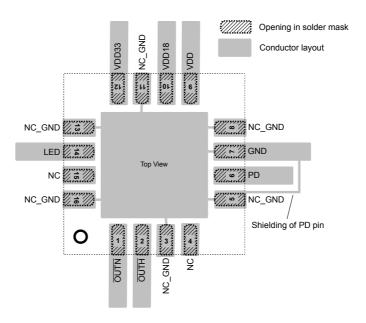

## QFN-16 Package

Figure 15: QFN-16: Layout recommendation

Figure 16: QFN-16: Mechanical dimensions

## **Reflow Solder Profile**

For infrared or conventional soldering the solder profile has to follow the recommendations of IPC/JEDEC J-STD-020C (min. revision C) for Pb-free assembly for both types of packages. The peak soldering t emperature  $(T_L)$  should not exceed +260°C for a maximum of 4 sec.

12

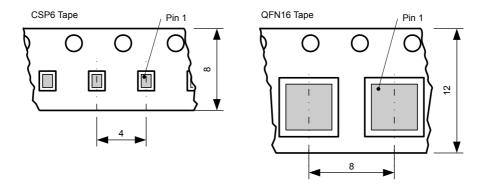

# Packaging Information (all measures in mm)

#### **Tape & Reel Information**

The devices are mounted on embossed tape for automatic placement systems. The tape is wound on 178 mm (7 inch) or 330 mm (13 inch) reels and individually packaged for shipment. General tape-and-reel specification data are available in a separate data sheet and indicate the tape sizes for various package types. Further tape-and-reel specifications can be found in the Electronic Industries Association (EIA) standard 481-1, 481-2, 481-3.

Figure 17: CSP10 and QFN16 Tape Dimension. Parts are placed with solder pads on bottom side

ESPROS Photonics AG does not guarantee that there are no empty cavities. Thus, the pick-and-place machine should check the presence of a chip during picking.

# **Ordering Information**

| Туре         | Response Time | Sensitivity | Package | RoHS compliance | Packaging Method |

|--------------|---------------|-------------|---------|-----------------|------------------|

| epc111-CSP10 | Medium        | High        | CSP10   | Yes             | Reel             |

| epc111-QFN16 | Medium        | High        | QFN16   | Yes             | Reel             |

| epc112-CSP10 | Fast          | Medium      | CSP10   | Yes             | Reel             |

| epc112-QFN16 | Fast          | Medium      | QFN16   | Yes             | Reel             |

## **IMPORTANT NOTICE**

ESPROS Photonics AG and its subsidiaries (epc) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to epc's terms and conditions of sale supplied at the time of order acknowledgment.

epc warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with epc's standard warranty. Testing and other quality control techniques are used to the extent epc deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

epc assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using epc components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

epc does not warrant or represent that any license, either express or implied, is granted under any epc patent right, copyright, mask work right, or other epc intellectual property right relating to any combination, machine, or process in which epc products or services are used. Information published by epc regarding third-party products or services does not constitute a license from epc to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from epc under the patents or other intellectual property of epc.

Resale of epc products or services with statements different from or beyond the parameters stated by epc for that product or service voids all express and any implied warranties for the associated epc product or service. epc is not responsible or liable for any such statements.

epc products are not authorized for use in safety-critical applications (such as life support) where a failure of the epc product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of epc products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by epc. Further, Buyers must fully indemnify epc and its representatives against any damages arising out of the use of epc products in such safety-critical applications.

epc products are neither designed nor intended for use in military/aerospace applications or environments unless the epc products are specifically designated by epc as military-grade or "enhanced plastic." Only products designated by epc as military-grade meet military specifications. Buyers acknowledge and agree that any such use of epc products which epc has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

epc products are neither designed nor intended for use in automotive applications or environments unless the specific epc products are designated by epc as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, epc will not be responsible for any failure to meet such requirements.