## Keysight M3102A

PXIe Digitizers with Optional Real-Time Sequencing and FPGA Programming 500 MSa/s, 14 Bits, 2/4 Channels

Data Sheet

# Improve Your Measurement Fidelity, Signal Integrity and Measurement Throughput

The M3102A are high-performance, high-bandwidth digitizers with an advanced data acquisition system (DAQ). Performance meets simplicity thanks to easy-to-use programming libraries, real-time sequencing technology (Hard Virtual Instrumentation or HVI), and graphical FPGA programming technology.

### **Features**

500 MSa/s simultaneous sampling, 14 bits, 2/4 channels, 200 MHz BW

### Advanced data acquisition system (DAQ)

- Flexible triggering (HW trigger, HVI trigger, SW trigger)

- Programmable cycles and data bursts to avoid PC saturation

### Optional HW programming for high-performance applications

- Real-time sequencing (HVI technology)

- FPGA programming

- Xilinx Kintex-7, 325T or 410T FPGA

### Up to 2 GB of onboard RAM (~ 1 Gsamples)

### Mechanical/interface

- 1 slot 3U (PXIe)

- Up to 200 MB/s transfer BW with P2P capabilities

- Independent DMA channels for fast and efficient data transfer

### **Applications**

General purpose digitizer

BB electronics designs and manufacturing in wireless devices

R&D/scientific research equipment

Aerospace & defense (A/D), angle of arrival (AoA)

### Programming Technology and Software Tools

### Software programming

Easy-to-use native programming libraries for most common languages: C, C++, Visual Studio, LabVIEW, MATLAB, Python, and more

### Hardware programming (optional)

- Real-time sequencing ((Hard Virtual Instrumentation or HVI technology))

- Graphical flowchart-style M3601A design environment (-HV1 option required on HW)

- Ultra-fast, fully-parallelized hard real-time execution

- Ultra-fast, time-deterministic decision-making

- Off-the-shelf inter-module synchronization & data exchange

- FPGA programming

- Graphical M3602A FPGA design environment (-FP1 option required on HW)

- No FPGA know-how required

- Include high-level to low-level design elements: off-the-shelf DSP blocks, MATLAB/Simulink designs, Xilinx CORE Generator IP cores, Xilinx VIVADO/ISE projects, VHDL or Verilog code

- Ultra-fast, one-click compiling and on-the-fly programming

### No programming

- Ready-to-use SD1 SPF (software front panels)

### PXIe Arbitrary Waveform Generators, Digitizers and Combination Modules

|         |           |                  | Outputs | (AWGs | )           | Ir               | nputs (Di | gitizers | s)          |

|---------|-----------|------------------|---------|-------|-------------|------------------|-----------|----------|-------------|

| Product | Туре      | Speed<br>(MSa/s) | Bits    | Ch    | BW<br>(MHz) | Speed<br>(MSa/s) | Bits      | Ch       | BW<br>(MHz) |

| M3202A  | AWG       | 1000             | 14      | 2/4   | 400         |                  |           |          |             |

| M3201A  | AWG       | 500              | 16      | 2/4   | 200         |                  |           |          |             |

| M3102A  | Digitizer |                  |         |       |             | 500              | 14        | 2/4      | DC-200      |

| M3100A  | Digitizer |                  |         |       |             | 100              | 14        | 4/8      | DC-100      |

| M3302A  | Combo     | 500              | 16      | 2     | 200         | 500              | 14        | 2        | DC-200      |

| M3300A  | Combo     | 500              | 16      | 2/4   | 200         | 100              | 14        | 4/8      | DC-100      |

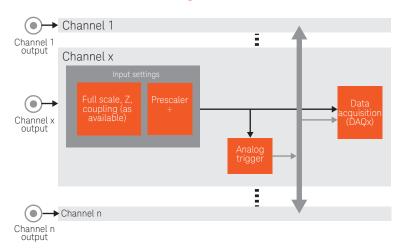

### Functional Block Diagram

Figure 1. M3102A input functional block diagram, all channels have identical input structure

### Ordering Information <sup>1</sup>

| Related software         | Description                                                                                            |  |  |  |  |  |

|--------------------------|--------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                          |                                                                                                        |  |  |  |  |  |

| M3102A-K32 / -K41        | FPGA, Xilinx 7K325T / 7K410T, required for -FP1 option only (needs memory option -M20)                 |  |  |  |  |  |

| M3102A-FP1               | Enabled FPGA programming, requires -K32 or -K41 option and an FPGA design environment license (M3602A) |  |  |  |  |  |

| M3102A-HVI               | Enabled HVI programming, requires an HVI design environment license (M3601A)                           |  |  |  |  |  |

| HW programming options   | Description                                                                                            |  |  |  |  |  |

| M3102A-M01 / -M12 / -M20 | Memory 16 MB, 8 MSamples <sup>2</sup> / 128 MB, 60 MSamples / 2 GB, 1 GSamples                         |  |  |  |  |  |

| M3102A-CLV / -CLF        | Variable sampling clock / Fixed sampling clock, low jitter <sup>2</sup>                                |  |  |  |  |  |

| M3102A-CH2/-CH4          | Two channels <sup>2</sup> / four channels                                                              |  |  |  |  |  |

| Options                  | Description                                                                                            |  |  |  |  |  |

| M3102A                   | PXIe digitizer: 500 MSa/s, 14 Bits                                                                     |  |  |  |  |  |

| Product                  | Description                                                                                            |  |  |  |  |  |

M3601A HVI design environment

M3602A FPGA design environment

<sup>1.</sup> All options must be selected at time of purchase and are not upgradable

<sup>2.</sup> These options represent the standard configuration

### Technical Specifications and Characteristics

### General characteristics

|                                  | M3102A-CH2 |      | МЗ   | 3102A-CI | H4   |      |        |                  |

|----------------------------------|------------|------|------|----------|------|------|--------|------------------|

| Parameter                        | Min        | Тур  | Max  | Min      | Тур  | Max  | Units  | Comments         |

| Inputs and outputs               |            |      |      |          |      |      |        |                  |

| Channels                         |            | 2    |      |          | 4    |      | Out    |                  |

| Reference clock <sup>1</sup>     |            | 1    |      |          | 1    |      | Out    |                  |

| Reference clock <sup>2</sup>     |            | 1    |      |          | 1    |      | In     |                  |

| Triggers/markers 1,3             |            | 1    |      |          | 1    |      | In/out | Reconfigurable   |

| Triggers/markers <sup>2, 3</sup> |            | 8    |      |          | 8    |      | In/out | Reconfigurable   |

| Input channels overview          |            |      |      |          |      |      |        |                  |

| Sampling rate <sup>4</sup>       |            | 500  |      |          | 500  |      | MSa/s  |                  |

| Voltage resolution               |            | 14   |      |          | 14   |      | Bits   |                  |

| Input frequency                  | 0          |      | 200  | 0        |      | 200  | MHz    |                  |

| Real-time BW                     |            | 200  |      |          | 200  |      | MHz    |                  |

| Time skew                        |            | < 50 |      |          | < 50 |      | ps     | Between channels |

| Built-in functionalities         |            |      |      |          |      |      |        |                  |

| Input conditioning blocks        |            | 2    |      |          | 4    |      |        | 1 per channel    |

| Analog trigger processors        |            | 2    |      |          | 4    |      |        | 1 per channel    |

| Data acquisition blocks          |            | 2    |      |          | 4    |      |        | 1 per channel    |

| Onboard memory                   |            |      |      |          |      |      |        |                  |

| RAM memory                       | 16         |      | 2048 | 16       |      | 2048 | MBytes |                  |

At front panel

At backplane

Markers available from firmware version v3.0 or later

<sup>4. 100</sup> to 500 MSa/s (-CLV) option with variable sampling clock

### I/O specifications

| Analog input characteristics                                                |                                                                   |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------|

| Number of channels                                                          | CH2 or CH4                                                        |

| Sampling rate                                                               | 500 MSa/s option CLF (Table 4) variable rate option CLV (Table 4) |

| Configurable inputs: impedance                                              | 50Ω or 1MΩ (HiZ)                                                  |

| Configurable inputs: Coupling                                               | AC or DC                                                          |

| Input voltage range (50Ω)                                                   | 125 mVpp to 8Vpp (7 scales: 0.125, 0.25, 0,5, 1, 2, 4, 8 Vpp)     |

| Input voltage range (HiZ)                                                   | 200 mVpp to 16Vpp (7 scales: 0.2, 0.4, 0.8, 2, 4, 8, 16 Vpp)      |

| Bandwidth limit filters                                                     | 200 MHz                                                           |

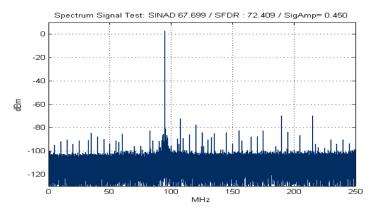

| Effective number of bits (ENOB) <sup>1</sup>                                | 10.6 bits @ 95 MHz (typical)                                      |

| Noise floor <sup>1</sup>                                                    | -146 dBm/Hz                                                       |

| SINAD <sup>1</sup>                                                          | 66 dB @ 95 MHz (typical)                                          |

| Spurious free dynamic range (SFDR) + Total Harmonic Distorsion <sup>1</sup> | 71 dBc @ 95 MHz (typical)                                         |

<sup>1.</sup> Measured at -1 DBFS input signal with 1 Vpp  $50\Omega$

|                             |     | M3102A                  |      |       |                                                    |

|-----------------------------|-----|-------------------------|------|-------|----------------------------------------------------|

| Parameter                   | Min | Тур                     | Max  | Units | Comments                                           |

| Reference clock output      |     |                         |      |       |                                                    |

| Frequency                   |     | 10 to 12.5 <sup>2</sup> |      | MHz   | Generated from the internal clock. User selectable |

| Voltage                     |     | 800                     |      | mVpp  | On a 50 Ω load                                     |

| Power                       |     | 2                       |      | dBm   | On a 50 Ω load                                     |

| Source impedance            |     | 50                      |      | Ω     | AC coupled                                         |

| External I/O trigger/marker |     |                         |      | ·     |                                                    |

| V <sub>IH</sub>             | 2   |                         | 5    | V     |                                                    |

| V <sub>IL</sub>             | 0   |                         | 0.8  | V     |                                                    |

| V <sub>OH</sub>             | 2.4 |                         | 3.3  | V     | On a high Z load                                   |

| V <sub>OL</sub>             | 0   |                         | 0.25 | V     | On a high Z load                                   |

| Input impedance             |     | 10                      |      | ΚΩ    |                                                    |

| Source impedance            |     | TTL                     |      | -     |                                                    |

| Speed                       |     | 100                     |      | MHz   |                                                    |

<sup>2.</sup> CLF option is set to 10 MHz while with CLV option varies from 12.5 MHz to 10 MHz

### Data acquisition blocks (DAQs) specifications

|                                 | M   | 3102A-0 | H2   | N   | 13102A-C | H4   |         |                                                                                         |

|---------------------------------|-----|---------|------|-----|----------|------|---------|-----------------------------------------------------------------------------------------|

| Parameter                       | Min | Тур     | Max  | Min | Тур      | Max  | Units   | Comments                                                                                |

| General specifications          |     |         |      |     |          |      |         |                                                                                         |

| DAQs                            |     | 2       |      |     | 4        |      |         | 1 per channel                                                                           |

| Aggregated speed                |     |         | 1000 |     |          | 2000 | MSa/s   | For all onboard DAQs combined                                                           |

| Acquisition burst multiple      |     | 5       |      |     | 5        |      | Samples | Burst length must be a multiple of this value                                           |

| Acquisition RAM capacity        | 15  |         | 957M | 15  |          | 957M | Samples | Maximum depends on onboard RAM                                                          |

| Acquisition RAM capacity effic. |     | 93.5    |      |     | 93.5     |      | %       | Effic. = waveform size / waveform size in RAM                                           |

| Trigger                         |     | Selec.  |      |     | Selec.   |      |         | Hardware trigger (analog channels, input trigger, backplane triggers), software trigger |

| DAQ specifications              |     |         |      |     |          |      |         |                                                                                         |

| Speed                           |     |         | 500  |     |          | 500  | MSa/s   | Per DAQ                                                                                 |

| Resolution                      |     | 14      |      |     | 14       |      | Bits    |                                                                                         |

### Clock system specifications

|                        | M3102A |     |       |                |

|------------------------|--------|-----|-------|----------------|

| Parameter              | Min    | Max | Units | Comments       |

| General specifications |        |     |       |                |

| Clock frequency (-CLF) | 500    | 500 | MHz   | Fixed clock    |

| Clock frequency (-CLV) | 100    | 500 | MHz   | Variable clock |

### System Specifications

### Environmental specifications (PXI Express)

|                        | M3102A-CH2 |     | M3102A-CH4 |       |     |       |       |                                               |

|------------------------|------------|-----|------------|-------|-----|-------|-------|-----------------------------------------------|

| Parameter              | Min        | Тур | Max        | Min   | Тур | Max   | Units | Comments                                      |

| System bus             |            |     |            |       |     |       |       |                                               |

| Slots                  |            | 1   |            |       | 1   |       | Slot  | PXI Express (CompactPCI Express compatible)   |

| PCI Express type       | Gen 1      |     | Gen 2      | Gen 1 |     | Gen 2 | _     | Automatic gen negotiation, chassis dependent  |

| PCI Express link       | 1          |     | 4          | 1     |     | 4     | Lanes | Automatic lane negotiation, chassis dependent |

| Power dissipation      |            |     |            |       |     |       |       |                                               |

| 3.3V PXIe power supply |            | 1.5 |            |       | 1.5 |       | А     | ~ 5 W                                         |

| 12V PXIe power supply  |            | 2   |            |       | 2   |       | А     | ~ 24 W                                        |

| Environmental <sup>1</sup>                  |                            |                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|---------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Temperature range                           | Operating<br>Non-operating | 0 to +55°C (10,000 feet)<br>-40 to +70°C (up to 15,000 feet)                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Max operative altitude                      |                            | 4000 m (10,000 feet)                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Operating Humidity range (%RH)              |                            | 10 to 95% at 40°C                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Non-operating Humidity range (%RH): 5 to 95 |                            | 5 to 95%                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Calibration interval                        |                            | 1 year                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| EMC                                         |                            | Complies with European EMC Directive  - IEC/EN 61326-1  - CISPR Pub 11 Group 1, class A  This ISM device is in compliance with Canadian ICES-001  Cet appareil ISM est conforme à la norme NMB-001 du Canada.  This ISM device is in compliance with Australian and New Zealand RCM  This ISM device is in compliance with South Korea EMC KCC |  |  |  |  |

<sup>1.</sup> Samples of this product have been type tested in accordance with the Keysight Environmental Test Manual and verified to be robust against the environmental stresses of Storage, Transportation and End-use; those stresses include but are not limited to temperature, humidity, shock, vibration, altitude and power line conditions. Test Methods are aligned with IEC 60068-2 and levels are similar to MIL-PRF-28800F Class 3.

### **Evolving Since 1939**

Our unique combination of hardware, software, services, and people can help you reach your next breakthrough. We are unlocking the future of technology. From Hewlett-Packard to Agilent to Keysight.

### myKeysight

#### myKeysight

#### www.keysight.com/find/mykeysight

A personalized view into the information most relevant to you.

### http://www.keysight.com/find/emt\_product\_registration

Register your products to get up-to-date product information and find warranty information.

### www.pxisa.org

PCI eXtensions for Instrumentation (PXI) modular instrumentation delivers a rugged, PC-based high-performance measurement and automation system.

#### **Keysight Services**

### www.keysight.com/find/service

Keysight Services can help from acquisition to renewal across your instrument's lifecycle. Our comprehensive service offerings—onestop calibration, repair, asset management, technology refresh, consulting, training and more—helps you improve product quality and lower costs.

### Keysight Assurance Plans

#### www.keysight.com/find/AssurancePlans

Up to ten years of protection and no budgetary surprises to ensure your instruments are operating to specification, so you can rely on accurate measurements.

### Keysight Channel Partners

#### www.keysight.com/find/channelpartners

Get the best of both worlds: Keysight's measurement expertise and product breadth, combined with channel partner convenience.

www.keysight.com/find/m3102a

For more information on Keysight Technologies' products, applications or services, please contact your local Keysight office. The complete list is available at: www.keysight.com/find/contactus

#### Americas

Canada (877) 894 4414 Brazil 55 11 3351 7010 Mexico 001 800 254 2440 United States (800) 829 4444

#### Asia Pacific

Australia 1 800 629 485 China 800 810 0189 Hong Kong 800 938 693 India 1 800 11 2626 Japan 0120 (421) 345 Korea 080 769 0800 1 800 888 848 Malaysia 1 800 375 8100 Singapore 0800 047 866 Taiwan Other AP Countries (65) 6375 8100

#### Europe & Middle East

For other unlisted countries: www.keysight.com/find/contactus (BP-9-7-17)

0800 0260637

United Kingdom

### www.keysight.com/go/quality

Keysight Technologies, Inc. DEKRA Certified ISO 9001:2015 Quality Management System

This information is subject to change without notice.

© Keysight Technologies, 2017 - 2018

Published in USA, February 20, 2018

5992-1805EN

www.keysight.com