## CAT823, CAT824, CAT825

# System Supervisory Voltage Reset with Watchdog and Manual Reset

## **FEATURES**

- Automatically restarts microprocessor after Power failure

- Monitors pushbutton for external override

- Accurate under voltage system monitoring

- Brownout detection system reset for use with 3.0, 3.3, and 5.0 volt systems

- Pin and function compatible with the MAX823/24/25 products

- Operating Range from -40°C to +85°C

- Available in TSOT-23 5-lead and SC-70 packages

For Ordering Information details, see page 13.

## **APPLICATIONS**

- Microprocessor and Microcontroller based systems

- Intelligent Instruments

- Control Systems

- Critical µP Monitors

- Portable Equipment

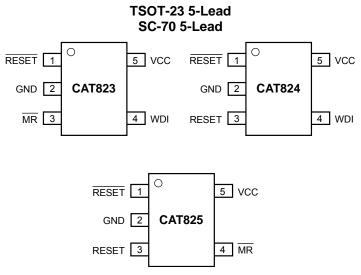

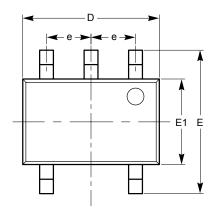

## **PIN CONFIGURATION**

## DESCRIPTION

The CAT823, CAT824, and CAT825 provide basic reset and monitoring functions for the electronic systems. Each device monitors the system voltage and maintains a reset output until that voltage reaches the device's specified trip value and then maintains the reset output active condition until the device's internal timer, after a minimum timer of 140ms; to allow the systems power supply to stabilize.

The CAT823 and CAT824 also have a watchdog input which can be used to monitor a system signal and cause a reset to be issued if the signal fails to change state prior to a timeout condition.

The CAT823 and CAT825 also provide a manual reset input which can be used to initiate reset if pulled low. This input can be directly attached to a push-button or a processor signal.

## **PIN FUNCTIONS**

| Pin Name        | Function                                                                                                                                                                  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET           | CMOS Push-Pull Active Low Reset<br>Output                                                                                                                                 |

| GND             | Ground                                                                                                                                                                    |

| MR              | Manual Reset input – Pulled high<br>Internally by a $52k\Omega$ resistor designed<br>to be driven low by a mechanical<br>pushbutton, open drain output or CMOS<br>output. |

| RESET           | CMOS Push-Pull Active High Reset<br>Output                                                                                                                                |

| WDI             | Watchdog Timer Input – Designed to be driven by a processor output or can be disabled by tri-stating or leaving open.                                                     |

| V <sub>CC</sub> | Power Supply                                                                                                                                                              |

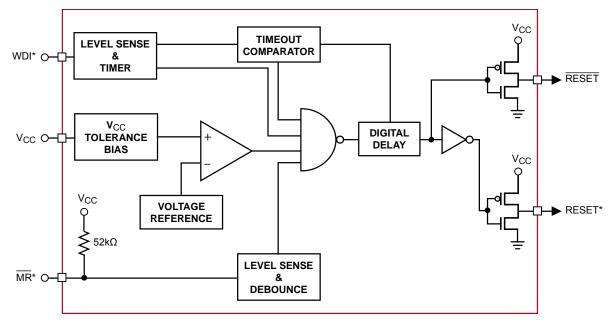

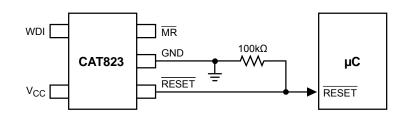

## **BLOCK DIAGRAM**

\* Functions Available by Device

| Device | RESET | RESET | MŔ | WDI |

|--------|-------|-------|----|-----|

| CAT823 | х     |       | х  | х   |

| CAT824 | х     | х     |    | х   |

| CAT825 | х     | х     | х  |     |

## ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Parameters                                             | Ratings                         | Units |

|--------------------------------------------------------|---------------------------------|-------|

| Supply Voltage                                         | 6                               | V     |

| All other pins                                         | -0.3 to (V <sub>CC</sub> + 0.3) | V     |

| Input Current, V <sub>CC</sub>                         | 20                              | mA    |

| Output Current RST, RST                                | 20                              | mA    |

| Continuous Power Dissipations (T <sub>A</sub> = +70°C) |                                 |       |

| SC-70 5-lead (derate 3.1mW/ºC above +70ºC)             | 247                             | mW    |

| TSOT-23 5-lead (derate 7.1mW/°C above +70°C)           | 571                             | mW    |

| Storage Temperature                                    | -65 to 150                      | °C    |

| Operating Ambient Temperature                          | -40 to +85                      | °C    |

| Lead Soldering (10 seconds max)                        | +300                            | °C    |

| ESD Rating: Low Voltage Pins                           |                                 |       |

| Human Body Model                                       | 2000                            | V     |

| Machine Model                                          | 200                             | V     |

#### **RECOMMENDED OPERATING CONDITIONS**

| Parameter                                  | Range                           | Units |

|--------------------------------------------|---------------------------------|-------|

| $V_{CC}$ (T <sub>A</sub> = 0°C to +70°C)   | 1.0 to 5.5                      | V     |

| $V_{CC}$ (T <sub>A</sub> = -40°C to +85°C) | 1.2 to 5.5                      | V     |

| All Other Pins                             | -0.1 to (V <sub>CC</sub> + 0.1) | V     |

| Ambient Temperature                        | -40 to +85                      | °C    |

Notes:

<sup>(1)</sup> Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.

#### **ELECTRICAL OPERATING CHARACTERISTICS**

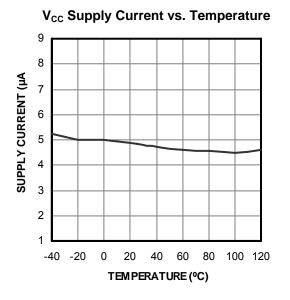

DC Characteristics:  $V_{CC}$  = 3.0V to 5.5V for L/M versions;  $V_{CC}$  = 2.0V to 3.6V for the R/S/T/Y/Z version, -40°C  $\leq T_A \leq +85$ °C unless otherwise noted. Typical Values at  $T_A$  = 25°C and  $V_{CC}$  = 5V for L/M versions;  $V_{CC}$  = 3.3V for the T/S versions;  $V_{CC}$  = 3.0V for the R version; and  $V_{CC}$  = 2.5V for the Y/Z versions.<sup>(1)</sup>

| Symbol           | Parameter                                                   | Conditions                                                                                   | Min                    | Тур  | Max  | Units  |  |

|------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------|------|------|--------|--|

|                  |                                                             | CAT823 (L/M Versions)<br>CAT824 (L/M Versions)                                               |                        | 6    | 17   | μA     |  |

| I <sub>CC</sub>  | Supply Current                                              | CAT823 (R/S/T/Y/Z Versions)<br>CAT824 (R/S/T/Y/Z Versions)                                   |                        | 4    | 12   | μA     |  |

|                  |                                                             | CAT825 (L/M Versions)                                                                        |                        | 3    | 8    | μA     |  |

|                  |                                                             | CAT825 (R/S/T/Y/Z Versions)                                                                  |                        | 2    | 6    | μA     |  |

|                  |                                                             | CAT82_L at -40°C ≤ T <sub>A</sub> ≤ +85°C                                                    | 4.50                   | 4.63 | 4.75 | V      |  |

|                  |                                                             | CAT82_M at -40°C ≤ T <sub>A</sub> ≤ +85°C                                                    | 4.25                   | 4.38 | 4.50 | V      |  |

|                  |                                                             | CAT82_T at -40°C ≤ T <sub>A</sub> ≤ +85°C                                                    | 3.00                   | 3.08 | 3.15 | V      |  |

| V <sub>RST</sub> | Reset Threshold                                             | CAT82_S at -40°C ≤ T <sub>A</sub> ≤ +85°C                                                    | 2.85                   | 2.93 | 3.00 | V      |  |

|                  |                                                             | CAT82_R at -40°C ≤ T <sub>A</sub> ≤ +85°C                                                    | 2.55                   | 2.63 | 2.70 | V      |  |

|                  |                                                             | CAT82_Z at -40°C ≤ T <sub>A</sub> ≤ +85°C                                                    | 2.25                   | 2.32 | 2.38 | V      |  |

|                  |                                                             | <br>CAT82_Y at -40°C ≤ T <sub>A</sub> ≤ +85°C                                                | 2.13                   | 2.19 | 2.25 | V      |  |

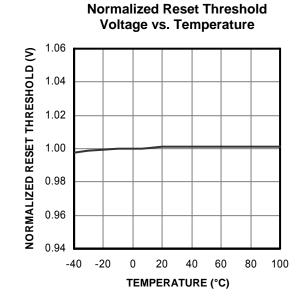

|                  | Reset Threshold<br>Tempco                                   |                                                                                              |                        | 40   |      | ppm/°C |  |

|                  | Reset Threshold                                             | CAT82_L/M                                                                                    |                        | 10   |      | mV     |  |

|                  | Hysteresis                                                  | CAT82_R/S/T/Y/Z                                                                              |                        | 5    |      | mV     |  |

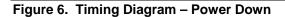

| t <sub>RD</sub>  | V <sub>CC</sub> to Reset Delay <sup>(2)</sup>               | $V_{CC} = V_{TH}$ to ( $V_{TH}$ - 100mV)                                                     |                        | 20   |      | μs     |  |

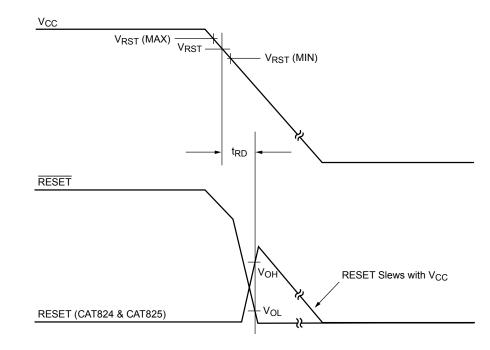

| t <sub>RP</sub>  | Reset Active<br>Timeout Period                              |                                                                                              | 140                    | 200  | 400  | ms     |  |

| M                | RESET Output High                                           | CAT82_L/M, $V_{CC} = V_{RST max}$ ,<br>I <sub>SOURCE</sub> = -120 $\mu$ A                    | V <sub>CC</sub> - 1.5V |      |      |        |  |

| V <sub>OH</sub>  | Voltage                                                     | CAT82_T/S/R/Z/Y, $V_{CC} = V_{RST max}$ ,<br>$I_{SOURCE} = -30\mu A$                         | $0.8 \times V_{CC}$    |      |      |        |  |

|                  |                                                             | CAT82_L/M, $V_{CC} = V_{RST min}$ ,<br>I <sub>SINK</sub> = 3.2mA                             |                        |      | 0.4  |        |  |

| V <sub>OL</sub>  | RESET Output Low                                            | $CAT82_T/S/R/Z/Y, V_{CC} = V_{RST min}, I_{SINK} = 1.2mA$                                    |                        |      | 0.3  | v      |  |

| V OL             | Voltage                                                     | $T_A = 0^{\circ}C$ to +70°C, $V_{CC} = 1V$ ,<br>$V_{CC}$ falling, $I_{SINK} = 50\mu A$       |                        |      | 0.3  |        |  |

|                  |                                                             | $T_A = T_{MIN}$ to $T_{MAX}$ , $V_{CC} = 1.2V$ ,<br>$V_{CC}$ falling, $I_{SINK} = 100 \mu A$ |                        |      | 0.3  | 3      |  |

| I                | RESET Output                                                | CAT82_L/M, Reset = 0V, V <sub>CC</sub> = 5.5V                                                |                        |      | 1.5  | mA     |  |

| ISOURCE          | Short-Circuit Current CAT82_L/M, Reset = 0V, $V_{CC}$ = 3.6 |                                                                                              |                        |      | 0.8  |        |  |

| V <sub>OH</sub>  |                                                             | $V_{CC}$ > 1.8V, $I_{SOURCE}$ = -150µA                                                       | $0.8 \times V_{CC}$    |      |      |        |  |

| V.               | Reset Output<br>Voltage                                     | CAT824L/M & CAT825L/M,<br>$V_{CC} = V_{RST max}$ , $I_{SINK} = 3.2mA$                        |                        |      | 0.4  | ] v    |  |

| V <sub>OL</sub>  |                                                             | CAT824R/S/T/Y/Z & CAT825R/S/T/Y/Z,<br>$V_{CC} = V_{RST max}$ , $I_{SINK} = 1.2mA$            |                        |      | 0.3  |        |  |

#### Notes:

(1) Over-temperature limits are guaranteed by design and not production tested.

(2) The RESET short-circuit current is the maximum pull-up current when reset is driven low by a bidirectional output.

#### **ELECTRICAL OPERATING CHARACTERISTICS (continued)**

DC Characteristics:  $V_{CC} = 3.0V$  to 5.5V for L/M versions;  $V_{CC} = 2.0V$  to 3.6V for the R/S/T/Y/Z version, -40°C  $\leq T_A \leq +85$ °C unless otherwise noted. Typical Values at  $T_A = 25$ °C and  $V_{CC} = 5V$  for L/M versions;  $V_{CC} = 3.3V$  for the T/S versions;  $V_{CC} = 3.0V$  for the R version; and  $V_{CC} = 2.5V$  for the Y/Z versions.

| Symbol            | Parameter                        | Conditions                                 | Min                    | Тур  | Max                           | Units |

|-------------------|----------------------------------|--------------------------------------------|------------------------|------|-------------------------------|-------|

| WATCHD            | OG INPUT (CAT823 & CAT824)       |                                            |                        |      |                               |       |

| t <sub>WD</sub>   | Watchdog Timeout Period          |                                            | 1.12                   | 1.60 | 3.20                          | S     |

| t <sub>wDI</sub>  | WDI Pulse Width                  | $V_{IL}$ = 0.4V, $V_{IH}$ = 0.8 x $V_{CC}$ | 50                     |      |                               | ns    |

| VIL               | WDI Input Voltage <sup>(3)</sup> |                                            |                        |      | $0.3 \text{ x V}_{\text{CC}}$ | V     |

| V <sub>IH</sub>   | WDI IIIput Voltage               |                                            | $0.7 \text{ x V}_{CC}$ |      |                               | v     |

|                   | WDI Input Current <sup>(4)</sup> | WDI = $V_{CC}$ , Time Average              |                        | 120  | 160                           |       |

|                   |                                  | WDI = 0V, Time Average                     | -20                    | -15  |                               | μA    |

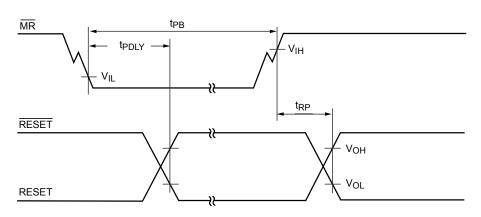

| MANUAL            | RESET INPUT(CAT823 & CAT825      | 5)                                         |                        |      |                               | -     |

| VIL               |                                  |                                            |                        |      | $0.3 \text{ x V}_{CC}$        | V     |

| V <sub>IH</sub>   | MR Input Voltage                 |                                            | $0.7 \times V_{CC}$    |      |                               | v     |

| t <sub>PB</sub>   | MR Pulse Width                   |                                            | 1                      |      |                               | μs    |

| t <sub>PDLY</sub> | MR low to Reset Delay            |                                            |                        |      | 5                             | μs    |

|                   | MR Noise Immunity                | Pulse Width with No Reset                  |                        | 100  |                               | ns    |

|                   | MR Pullup Resistance (internal)  |                                            | 35                     | 52   | 75                            | kΩ    |

Notes:

(3) WDI is internally serviced within the watchdog period if WDI is left open.

<sup>(4)</sup> The WDI input current is specified as an average input current when the WDI input is driven high or low. The WDI input if connected to a three-stated output device can be disabled in the tristate mode as long as the leakage current is less than 10µA and a maximum capacitance of less than 200pF. To clock the WDI input in the active mode the drive device must be able to source or sink at least 200µA when active.

## CAT823, CAT824, CAT825

#### TYPICAL ELECTRICAL OPERATING CHARACTERISTICS TABLES

## FUNCTIONAL DESCRIPTION

#### PROCESSOR RESET

The CAT823-825 detect supply voltage ( $V_{CC}$ ) conditions that are below the specified voltage trip value ( $V_{RST}$ ) and provide a reset output to maintain correct system operation. On power-up, RESET (and RESET if available) are kept active for a minimum delay t<sub>RP</sub> of 140ms after the supply voltage ( $V_{CC}$ ) rises above  $V_{RST}$  to allow the power supply and processor to stabilize. When  $V_{CC}$  drops below the voltage trip value ( $V_{RST}$ ), the reset output signals RESET (and RESET) are pulled active. RESET (and RESET) are pulled active. RESET (and RESET) if available) is specifically designed to provide the reset input signals for processors. This provides reliable and consistent operation as power is turned on, off or during brownout conditions by maintaining the processor operation in known conditions.

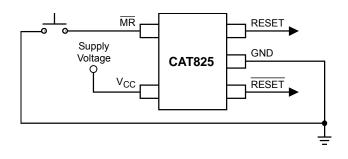

## MANUAL RESET

The CAT823 and CAT825 each have a Manual Reset (MR) input to allow for alternative control of the reset outputs. The  $\overline{\text{MR}}$  input is designed for direct connection to a pushbutton (see Figure 1). The  $\overline{\text{MR}}$  input is internally pulled up by 52k $\Omega$  resistor and must be pulled low to cause the reset outputs to go active. Internally, this input is debounced and timed such that RESET (and RESET) signals of at least 140ms minimum will be generated. The min 140ms t<sub>RP</sub> delay commences as the Manual Reset input is released from the low level. (see Figure 2)

#### Figure 1. Pushbutton RESET

Figure 2. Timing Diagram – Pushbutton RESET

#### WATCHDOG TIMER

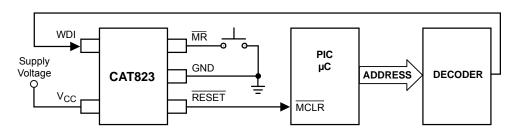

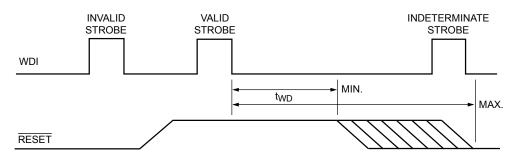

The CAT823 and CAT824 provide a Watchdog input (WDI). The watchdog timer function forces RESET (and RESET in the CAT824) signals active when the WDI input does not have a transition from low-to-high or high-to-low within 1.12 seconds. Timeout of the watchdog starts when RESET (RESET on the CAT824) becomes inactive. If a transition occurs on the WDI input pin prior to the watchdog time-out, the watchdog timer is reset and begins to time-out again. If the watchdog timer is allowed to time-out, then the reset output(s) will go active for t<sub>RP</sub> and once released will repeat the watchdog timeout process.

Figure 3 below shows a typical implementation of a watchdog function. Any processor signal that repeats dependant on the normal operation of the processor or directed by the software operating on the processor can be used to strobe the watchdog input. The most

reliable is a dedicated I/O output transitioned by a specific software instruction.

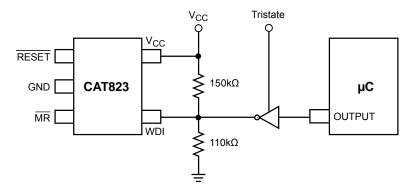

The watchdog can be disabled by floating (or tristating) the WDI input (see Figure 4). If the watchdog is disabled the WDI pin will be pulled low for the first  $7/8^{th}$ 's of the watchdog period ( $t_{WD}$ ) and pulled high for the last  $1/8^{th}$  of the watchdog period. This pulling low of the WDI input and then high is used to detect an open or tri-state condition and will continue to repeat until the WDI input is driven high or low.

For most efficient operation of devices with the watchdog function the WDI input should be held low the majority of the time and only strobed high as required to reset the watchdog timer.

#### Figure 3. Watchdog Timer

Figure 4. Watchdog Disable Circuit

#### Figure 5. Timing Diagram – Strobe Input

Figure 7. Timing Diagram – Power Up

## APPLICATION NOTES

#### µP's with Bidirectional Reset Pins

The RESET output can be pulled low by processors like the 68HC11 allowing for a system reset issued by the processor. The maximum pullup current that can be sourced by the CAT82\_L/M is 1.5mA (and by the CAT82\_T/R/S/Z/Y is 800µA) allowing the processor to pull the output low even when the CAT82x is pulling it high.

#### **Power Transients**

Generally short duration negative-going transients of less than  $2\mu$ s on the power supply at V<sub>RST</sub> minimum will not cause a reset condition. However the lower the voltage of the transient the shorter the required time to cause a reset output. These issues can usually be remedied by the proper location of bypass capacitance on the circuit board.

## **OUTPUT VALID CONDITIONS**

The RESET output uses a push-pull output which can maintain a valid output down to a  $V_{CC}$  of 1.0 volts. To sink current below 0.8V a resistor can be connected from RESET to Ground (see Figure 8.) This arrangement will maintain a valid value on the RESET output during both power up and down but will draw current when the RESET output is in the high state. A resistor value of about 100k $\Omega$  should be adequate in most situations to maintain a low condition valid output down to V<sub>CC</sub> equal to 0V.

Figure 8. RESET Valid to 0 Volts V<sub>cc</sub>

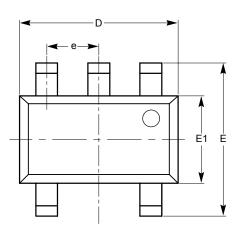

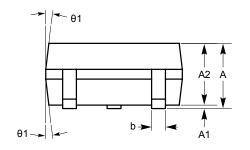

## PACKAGE OUTLINE DRAWING

TSOT-23 5-Lead (TD)<sup>(1)(2)</sup>

| SYMBOL | MIN            | NOM      | MAX  |  |

|--------|----------------|----------|------|--|

| A      |                |          | 1.00 |  |

| A1     | 0.01           | 0.05     | 0.10 |  |

| A2     | 0.80           | 0.87     | 0.90 |  |

| b      | 0.30           |          | 0.45 |  |

| с      | 0.12           | 0.15     | 0.20 |  |

| D      | 2.90 BSC       |          |      |  |

| E      |                | 2.80 BSC |      |  |

| E1     |                | 1.60 BSC |      |  |

| е      |                | 0.95 TYP |      |  |

| L      | 0.30 0.40 0.50 |          | 0.50 |  |

| L1     | 0.60 REF       |          |      |  |

| L2     | 0.25 BSC       |          |      |  |

| θ      | 0° 8°          |          |      |  |

TOP VIEW

For current Tape and Reel information, download the PDF file from: http://www.catsemi.com/documents/tapeandreel.pdf.

Notes:

(1) All dimensions in millimeters. Angles in degrees.

(2) Complies with JEDEC standard MO-193.

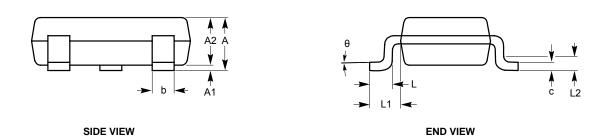

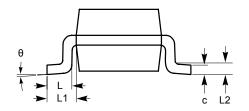

## SC-70 5-Lead (SD)<sup>(1)(2)</sup>

TOP VIEW

| SYMBOL | MIN      | NOM      | МАХ  |  |

|--------|----------|----------|------|--|

| A      | 0.80     |          | 1.10 |  |

| A1     | 0.00     |          | 0.10 |  |

| A2     | 0.80     |          | 1.00 |  |

| b      | 0.15     |          | 0.30 |  |

| С      | 0.10     |          | 0.18 |  |

| D      | 1.80     | 2.00     | 2.20 |  |

| E      | 1.80     | 2.10     | 2.40 |  |

| E1     | 1.15     | 1.25     | 1.35 |  |

| е      |          | 0.65 BSC |      |  |

| L      | 0.26     | 0.36     | 0.46 |  |

| L1     |          | 0.42 REF |      |  |

| L2     | 0.15 BSC |          |      |  |

| θ      | 0°       |          | 8°   |  |

| θ1     | 4°       |          | 10°  |  |

SIDE VIEW

END VIEW

For current Tape and Reel information, download the PDF file from: http://www.catsemi.com/documents/tapeandreel.pdf.

#### Notes:

- (1) All dimensions in millimeters. Angles in degrees.

- (2) Complies with JEDEC MO-203.

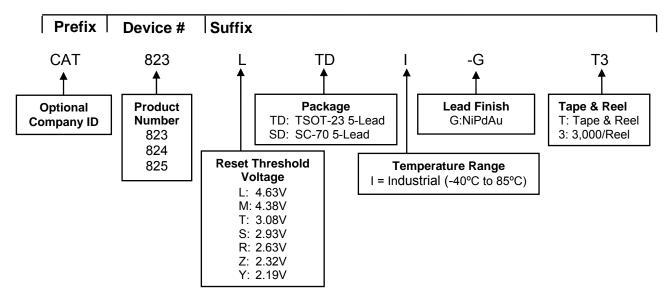

## **EXAMPLE OF ORDERING INFORMATION**

## **TOP MARKING INFORMATION (For all Thresholds)**

| Device # | Package | Top Marking |

|----------|---------|-------------|

| CAT823   | TSOT-23 | TS          |

| CAT824   | TSOT-23 | ТВ          |

| CAT825   | TSOT-23 | TD          |

| CAT823   | SC-70   | RG          |

| CAT824   | SC-70   | TB          |

| CAT825   | SC-70   | TD          |

## **ORDERING PART NUMBER**

| CAT823LTDI-G | CAT824LTDI-G <sup>(4)</sup> | CAT825LTDI-G |

|--------------|-----------------------------|--------------|

| CAT823MTDI-G | CAT824MTDI-G <sup>(4)</sup> | CAT825MTDI-G |

| CAT823TTDI-G | CAT824TTDI-G <sup>(4)</sup> | CAT825TTDI-G |

| CAT823STDI-G | CAT824TSDI-G <sup>(4)</sup> | CAT825STDI-G |

| CAT823RTDI-G | CAT824RTDI-G <sup>(4)</sup> | CAT825RTDI-G |

| CAT823ZTDI-G | CAT824ZTDI-G <sup>(4)</sup> | CAT825ZTDI-G |

| CAT823YTDI-G | CAT824YTDI-G <sup>(4)</sup> | CAT825YTDI-G |

| CAT823LSDI-G | CAT824LSDI-G <sup>(4)</sup> | CAT825LSDI-G |

| CAT823MSDI-G | CAT824MSDI-G <sup>(4)</sup> | CAT825MSDI-G |

| CAT823TSDI-G | CAT824TSDI-G <sup>(4)</sup> | CAT825TSDI-G |

| CAT823SSDI-G | CAT824SSDI-G <sup>(4)</sup> | CAT825SDI-G  |

| CAT823RSDI-G | CAT824RSDI-G <sup>(4)</sup> | CAT825RSDI-G |

| CAT823ZSDI-G | CAT824ZSDI-G <sup>(4)</sup> | CAT825ZSDI-G |

| CAT823YSDI-G | CAT824YSDI-G <sup>(4)</sup> | CAT825YSDI-G |

#### Notes:

- (1) All packages are RoHS-compliant (Lead-free, Halogen-free).

- (2) The standard lead finish is NiPdAu.

- (3) This device used in the above example is a CAT823LTDI -GT3 (4.63V, TSOT-23 5-Lead, Industrial Temperature, NiPdAu, Tape & Reel, 3,000/Reel,

- (4) Contact factory for package availability.

### **REVISION HISTORY**

| Date      | Rev. | Reason                                                         |

|-----------|------|----------------------------------------------------------------|

| 10-Sep-07 | А    | Initial Release                                                |

| 23-May-08 | В    | Update Package Outline Drawings<br>Update Top Mark Information |

#### Copyrights, Trademarks and Patents

© Catalyst Semiconductor, Inc.

Trademarks and registered trademarks of Catalyst Semiconductor include each of the following: Adaptive Analog<sup>™</sup>, Beyond Memory<sup>™</sup>, DPP<sup>™</sup>, EZDim<sup>™</sup>, LDD<sup>™</sup>, MiniPot<sup>™</sup>, Quad-Mode<sup>™</sup> and Quantum Charge Programmable<sup>™</sup>

Catalyst Semiconductor has been issued U.S. and foreign patents and has patent applications pending that protect its products.

CATALYST SEMICONDUCTOR MAKES NO WARRANTY, REPRESENTATION OR GUARANTEE, EXPRESS OR IMPLIED, REGARDING THE SUITABILITY OF ITS PRODUCTS FOR ANY PARTICULAR PURPOSE, NOR THAT THE USE OF ITS PRODUCTS WILL NOT INFRINGE ITS INTELLECTUAL PROPERTY RIGHTS OR THE RIGHTS OF THIRD PARTIES WITH RESPECT TO ANY PARTICULAR USE OR APPLICATION AND SPECIFICALLY DISCLAIMS ANY AND ALL LIABILITY ARISING OUT OF ANY SUCH USE OR APPLICATION, INCLUDING BUT NOT LIMITED TO, CONSEQUENTIAL OR INCIDENTAL DAMAGES.

Catalyst Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Catalyst Semiconductor product could create a situation where personal injury or death may occur.

Catalyst Semiconductor reserves the right to make changes to or discontinue any product or service described herein without notice. Products with data sheets labeled "Advance Information" or "Preliminary" and other products described herein may not be in production or offered for sale.

Catalyst Semiconductor advises customers to obtain the current version of the relevant product information before placing orders. Circuit diagrams illustrate typical semiconductor applications and may not be complete.

Catalyst Semiconductor, Inc. Corporate Headquarters 2975 Stender Way Santa Clara, CA 95054 Phone: 408.542.1000 Fax: 408.542.1200 www.catsemi.com

Document No: MD-3027 Revision: B Issue date: 05/23/08