#### **General Description**

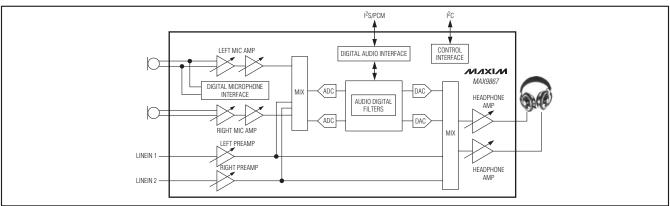

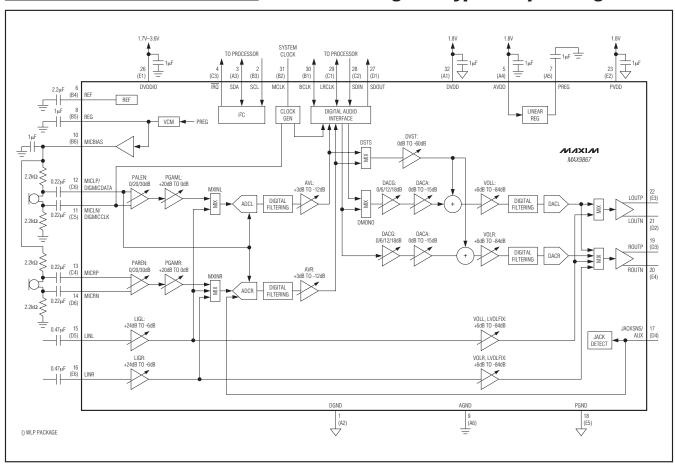

The MAX9867 is an ultra-low power stereo audio codec designed for portable consumer devices such as mobile phones and portable gaming consoles.

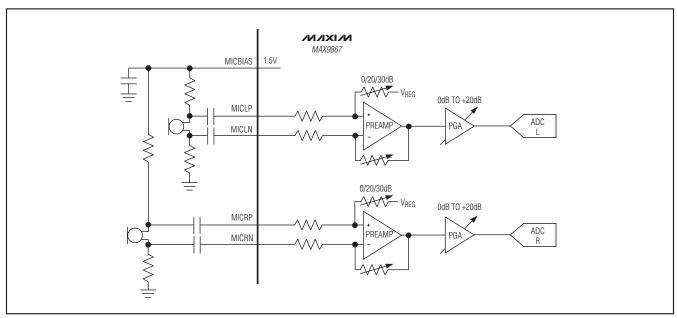

The device features stereo differential microphone inputs that can be connected to either analog or digital microphones. The single-ended line inputs, with configurable preamplifier, can be sent to the ADC for record or routed directly to the headphone amplifier for playback. An auxiliary ADC path can be used to track any DC voltage.

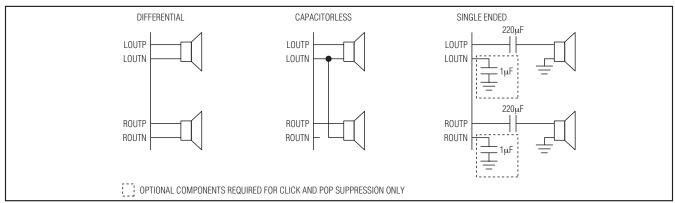

The stereo headphone amplifiers support differential. single-ended, and capacitorless output configurations. Using the capacitorless output configuration, the device can output 10mW into  $32\Omega$  headphones. Comprehensive click-and-pop circuitry suppresses audible clicks and pops during volume changes and startup or shutdown.

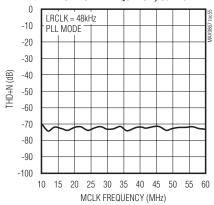

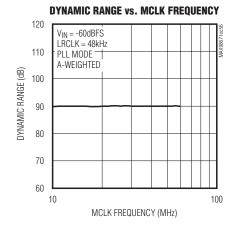

Utilizing Maxim's proprietary digital circuitry, the device can accept any available 10MHz to 60MHz system clock. This architecture eliminates the need for an external PLL and multiple crystal oscillators. The stereo ADC and DAC paths provide user-configurable voiceband or audioband digital filters. Voiceband filters provide extra attenuation at the GSM packet frequency and greater than 70dB stopband attenuation at fs/2.

The MAX9867 operates from a single 1.8V supply, and supports a 1.65V to 3.6V logic level. An I<sup>2</sup>C 2-wire serial interface provides control for volume levels, signal mixing, and general operating modes.

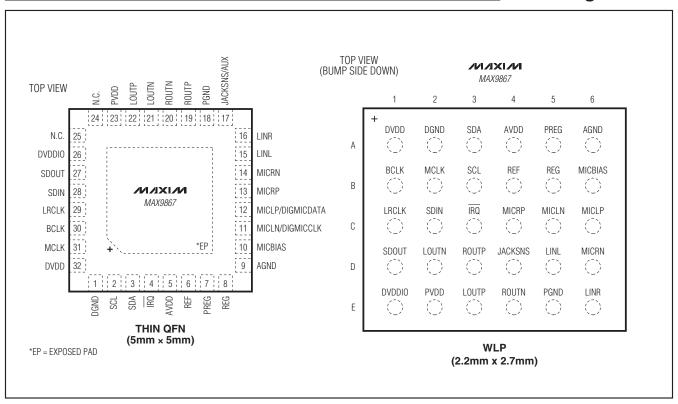

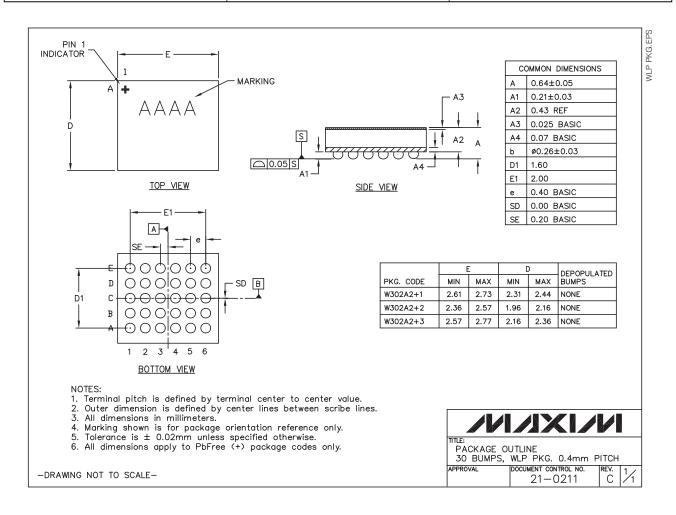

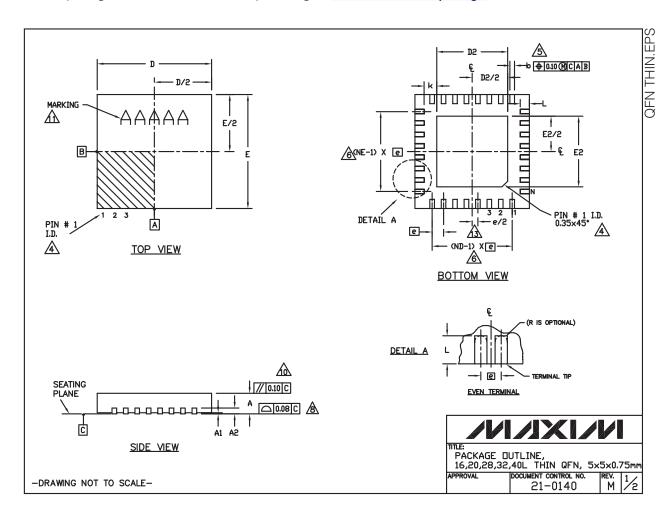

The MAX9867 is available in a tiny 2.2mm x 2.7mm, 0.4mm-ball-pitch, WLP package. A 32-pin 5mm x 5mm TQFN package is also available.

#### **Features ♦ 1.8V Single-Supply Operation**

- ♦ 6.7mW Playback Power Consumption

- ♦ 90dB Stereo DAC, 8kHz ≤ fs ≤ 48kHz

- ♦ 85dB Stereo ADC, 8kHz ≤ fs ≤ 48kHz

- **♦** Battery-Measurement Auxiliary ADC

- ♦ Support for Any Master Clock Between 10MHz to 60MHz

- ♦ Stereo Digital Microphone Input Support

- ♦ Stereo Analog Differential Microphone Inputs

- ♦ Stereo Headphone Amplifiers: Differential, Single-Ended, or Capacitorless

- ♦ Stereo Line Inputs

- ♦ Voiceband Filter with a Stopband Attenuation Greater than 70dB

- ♦ 1.65V to 3.6V Digital Interface Supply Voltage

- ♦ I<sup>2</sup>S/TDM-Compatible Digital Audio Bus

- ♦ 30-Bump, 2.2mm x 2.7mm 0.4mm-Pitch WLP

#### **Applications**

Cell Phones Portable Gaming Devices Portable Navigation Devices Portable Multimedia Players Wireless Headsets

#### **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE |

|-------------|----------------|-------------|

| MAX9867EWV+ | -40°C to +85°C | 30 WLP      |

| MAX9867ETJ+ | -40°C to +85°C | 32 TQFN-EP* |

<sup>+</sup>Denotes lead(Pb)-free/RoHS-compliant package.

### Simplified Block Diagram

Maxim Integrated Products 1

<sup>\*</sup>EP = Exposed pad.

#### **ABSOLUTE MAXIMUM RATINGS**

| (Voltages with respect to AGND.) DVDD, AVDD, and PVDD0.3V to +2V DVDDIO0.3V to +3.6V | LINL, LINR, JACKSNS/AUX, MICLP/DIGMICDATA, MICLN/DIGMICCLK, MICRP, MICRN0.3V to (AVDD + 0.3V) Continuous Power Dissipation (T <sub>A</sub> = +70°C) |

|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| DGND and PGND0.1V to +0.1V PREG, REF, REG, MICBIAS0.3V to (AVDD + 0.3V)              | 30-Bump WLP (derate 12.5mW/°C above +70°C)1000mW 32-Pin TQFN-EP (derate 34.5mW/°C above +70°C).2759mW                                               |

| MCLK, LRCLK, BCLK  SDOUT, SDIN0.3V to (DVDDIO + 0.3V)                                | Junction-to-Ambient Thermal Resistance (θJA) (Note 1) 30-Bump WLP80°C/W                                                                             |

| SDA, SCL, TRQ0.3V to +3.6V<br>LOUTP, LOUTN, ROUTP,                                   | 32-Pin TQFN-EP                                                                                                                                      |

| ROUTN(PGND - 0.3V) to (PVDD + 0.3V)                                                  | Storage Temp Range65°C to +150°C                                                                                                                    |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{AVDD} = V_{PVDD} = V_{DVDD} = V_{DVDDIO} = +1.8V, R_L = \infty$ , headphone load (R<sub>L</sub>) connected between \_OUTP and \_OUTN in differential mode,  $C_{REF} = 2.2\mu F$ ,  $C_{MICBIAS} = C_{PREG} = C_{REG} = 1\mu F$ ,  $AV_{PRE} = +20dB$ ,  $AV_{PGAM} = 0dB$ ,  $AV_{DAC} = 0dB$ ,  $AV_{LINE} = +20dB$ ,  $AV_{VOL} = 0dB$ ,  $AV_{LINE} = +20dB$ ,

| PARAMETER               | SYMBOL           | CONDI                                                                     | TIONS                   | MIN  | TYP   | MAX  | UNITS |

|-------------------------|------------------|---------------------------------------------------------------------------|-------------------------|------|-------|------|-------|

| Cupply Voltage Bange    |                  | PVDD, DVDD, AVDD                                                          |                         | 1.65 | 1.8   | 1.95 | V     |

| Supply Voltage Range    |                  | DVDDIO                                                                    |                         | 1.65 | 1.8   | 3.6  | V     |

|                         |                  | Full-duplex 8kHz<br>mono (voice mode)<br>(Note 3)                         | Analog (AVDD + PVDD)    |      | 4.65  | 7    |       |

|                         |                  |                                                                           | Digital (DVDD + DVDDIO) |      | 0.96  | 1.5  |       |

|                         |                  | DAC playback 48kHz                                                        | Analog (AVDD + PVDD)    |      | 3.28  | 5    |       |

| Total Supply Current    | lunn             | stereo (audio mode)<br>(Note 3)                                           | Digital (DVDD + DVDDIO) |      | 1.40  | 2    |       |

| Total Supply Current    | l <sub>VDD</sub> | Full-duplex 48kHz<br>stereo (audio mode)<br>(Note 3)  Stereo line-in only | Analog (AVDD + PVDD)    |      | 8.0   | 12   | mA    |

|                         |                  |                                                                           | Digital (DVDD + DVDDIO) |      | 2.0   | 3    |       |

|                         |                  |                                                                           | Analog (AVDD + PVDD)    |      | 3.8   | 6    |       |

|                         |                  |                                                                           | Digital (DVDD + DVDDIO) |      | 0.004 | 0.05 |       |

|                         |                  | T0500                                                                     | Analog (AVDD + PVDD)    |      | 1     | 5    |       |

| Shutdown Supply Current |                  | T <sub>A</sub> = +25°C                                                    | Digital (DVDD + DVDDIO) |      | 1     | 5    | μΑ    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{PVDD} = V_{DVDD} = V_{DVDDIO} = +1.8V, R_L = \infty, \ headphone \ load \ (R_L) \ connected \ between \_OUTP \ and \_OUTN \ in \ differential mode, C_{REF} = 2.2 \mu F, C_{MICBIAS} = C_{PREG} = C_{REG} = 1 \mu F, \ AV_{PRE} = +20 dB, \ AV_{PGAM} = 0 dB, \ AV_{DAC} = 0 dB, \ AV_{LINE} = +20 dB, \ AV_{VOL} = 0 dB, \ MCLK = 13 MHz, T_A = T_{MIN} \ to \ T_{MAX}, \ unless \ otherwise \ noted. Typical values are at T_A = +25 °C.) \ (Note 2)$

| PARAMETER                    | SYMBOL            | CONDITIONS                                                                        |                                      | MIN | TYP                       | MAX | UNITS |

|------------------------------|-------------------|-----------------------------------------------------------------------------------|--------------------------------------|-----|---------------------------|-----|-------|

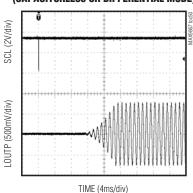

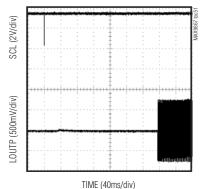

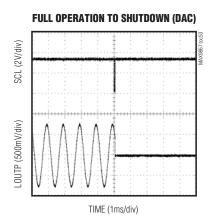

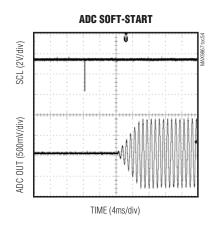

| Shutdown to Full Operation   |                   | Excludes PLL lock tim                                                             | ne                                   |     | 10                        |     | ms    |

| Soft-Start/-Stop Time        |                   |                                                                                   |                                      |     | 10                        |     | ms    |

| DAC (Note 4)                 |                   |                                                                                   |                                      |     |                           |     |       |

| Dynamic Range (Note 5)       | DR                | f <sub>S</sub> = 48kHz, AV <sub>VOL</sub> = +0dB, T <sub>A</sub> = +25°C          | Master or slave mode                 |     | 90                        |     | dB    |

|                              |                   | +00B, 1A = +20 0                                                                  | Slave mode                           | 84  |                           |     |       |

|                              |                   |                                                                                   | Differential mode                    |     | 1                         |     |       |

| Full-Scale Output            |                   | $V_{OLL}/V_{OLR} = 0 \times 09$                                                   | Capacitorless and single-ended modes |     | 0.56                      |     | VRMS  |

| Gain Error                   |                   | DC accuracy, measur full-scale output                                             | red with respect to                  |     | 1                         | 5   | %     |

| Voice Path Phase Delay       | P <sub>DLY</sub>  | f = 1kHz, 0dBFS, HP<br>filter disabled, digital                                   | f <sub>S</sub> = 8kHz                |     | 1.2                       |     | ms    |

| voice i aiii i nase belay    | I DLY             | input to analog output                                                            | f <sub>S</sub> = 16kHz               |     | 0.59                      |     | 1115  |

| Total Harmonic Distortion    | THD               | MCLK = 12.288MHz, fs = 48kHz, 0dBFS, measured at headphone outputs                |                                      |     | -80                       |     | dB    |

| DAC Attenuation Range        | AV <sub>DAC</sub> | DACA = 0xF to 0x0                                                                 |                                      | -15 |                           | 0   | dB    |

| DAC Gain Adjust              | AVGAIN            | DACG = 00 to 11                                                                   |                                      | 0   |                           | +18 | dB    |

|                              |                   | $V_{AVDD} = V_{PVDD} = 1.6$                                                       | 5V to 1.95V                          | 60  | 78                        |     |       |

|                              |                   | $f = 217Hz$ , $V_{RIPPLE} = 100mV_{P-P}$ , $AV_{VOL} = 0dB$                       |                                      |     | 78                        |     |       |

| Power-Supply Rejection Ratio | PSRR              | f = 1kHz, V <sub>RIPPLE</sub> = 100mV <sub>P-P</sub> ,<br>AV <sub>VOL</sub> = 0dB |                                      |     | 75                        |     | dB    |

|                              |                   | f = 10kHz, V <sub>RIPPLE</sub> = AV <sub>VOL</sub> = 0dB                          | 100mV <sub>P-P</sub> ,               | 62  |                           |     |       |

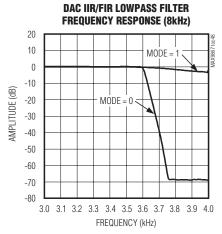

| DAC VOICE MODE DIGITAL IIR   | LOWPASS FI        | LTER                                                                              |                                      |     |                           |     |       |

| Passband Cutoff              | for o             | With respect to fs with 48kHz                                                     | nin ripple; f <sub>S</sub> = 8kHz to |     | 0.448 x<br>f <sub>S</sub> |     | LJ⇒   |

| rassuanu Culun               | fpLp              | -3dB cutoff                                                                       |                                      |     | 0.451 x<br>fs             |     | Hz    |

| Passband Ripple              |                   | f < f <sub>PLP</sub>                                                              | _                                    |     | ±0.1                      |     | dB    |

| Stopband Cutoff              | f <sub>SLP</sub>  | With respect to fs; fs =                                                          | = 8kHz to 48kHz                      |     | 0.476 x<br>fs             |     | Hz    |

| Stopband Attenuation         |                   | $f > f_{SLP}$ , $f = 20Hz$ to 2                                                   | 0kHz                                 | 75  |                           |     | dB    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{PVDD} = V_{DVDDD} = V_{DVDDIO} = +1.8V, R_L = \infty, headphone load (R_L) connected between _OUTP and _OUTN in differential mode, C_{REF} = 2.2 \mu F, C_{MICBIAS} = C_{PREG} = C_{REG} = 1 \mu F, AV_{PRE} = +20 dB, AV_{PGAM} = 0 dB, AV_{DAC} = 0 dB, AV_{LINE} = +20 dB, AV_{VOL} = 0 dB, MCLK = 13 MHz, T_A = T_{MIN} to T_{MAX}, unless otherwise noted. Typical values are at T_A = +25 °C.) (Note 2)$

| PARAMETER                                                                                 | SYMBOL      | CONDITIONS                                                       | MIN TYP MAX                | UNITS |

|-------------------------------------------------------------------------------------------|-------------|------------------------------------------------------------------|----------------------------|-------|

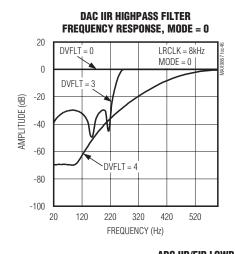

| DAC VOICE MODE DIGITAL 5th                                                                | ORDER IIR H | IGHPASS FILTER                                                   | <b>T</b>                   |       |

|                                                                                           |             | DVFLT = 0x1<br>(elliptical tuned for 16kHz GSM + 217Hz<br>notch) | 0.0161<br>× fs             |       |

|                                                                                           |             | DVFLT = 0x2<br>(500Hz Butterworth tuned for 16kHz)               | 0.0312<br>x fs             |       |

| 5th Order Passband Cutoff<br>(-3dB from Peak, I <sup>2</sup> C Register<br>Programmable)  | fDHPPB      | DVFLT = 0x3<br>(elliptical tuned for 8kHz GSM + 217Hz<br>notch)  | 0.0321<br>x fs             | Hz    |

|                                                                                           |             | DVFLT = 0x4<br>(500Hz Butterworth tuned for 8kHz)                | 0.0625<br>x fs             |       |

|                                                                                           |             | DVFLT = 0x5<br>(fg/240 Butterworth)                              | 0.0042<br>x fs             |       |

|                                                                                           |             | DVFLT = 0x1<br>(elliptical tuned for 16kHz GSM + 217Hz<br>notch) | 0.0139<br>× fs             |       |

|                                                                                           | fDHPSB      | DVFLT = 0x2<br>(500Hz Butterworth tuned for 16kHz)               | 0.0156<br>x f <sub>S</sub> |       |

| 5th Order Stopband Cutoff<br>(-30dB from Peak, I <sup>2</sup> C Register<br>Programmable) |             | DVFLT = 0x3<br>(elliptical tuned for 8kHz GSM + 217Hz<br>notch)  | 0.0279<br>x fs             | Hz    |

|                                                                                           |             | DVFLT = 0x4<br>(500Hz Butterworth tuned for 8kHz)                | 0.0312<br>x fs             |       |

|                                                                                           |             | DVFLT = 0x5<br>(fg/240 Butterworth)                              | 0.0021<br>x fs             |       |

| DC Attenuation                                                                            | DCATTEN     | DVFLT ≠ 000                                                      | 90                         | dB    |

| DAC STEREO AUDIO MODE DIG                                                                 | ITAL FIR LO | WPASS FILTER                                                     | T                          |       |

|                                                                                           |             | With respect to $f_S$ within ripple;<br>$f_S = 8kHz$ to $48kHz$  | 0.43 x<br>fs               |       |

| Passband Cutoff                                                                           | fPLP        | -3dB cutoff                                                      | 0.47 x<br>fs               | Hz    |

|                                                                                           |             | -6.02dB cutoff                                                   | 0.50 x<br>f <sub>S</sub>   |       |

| Passband Ripple                                                                           |             | f < fplp                                                         | ±0.1                       | dB    |

| Stopband Cutoff                                                                           | fSLP        | With respect to fs; fs = 8kHz to 48kHz                           | 0.58 x<br>fs               | Hz    |

| Stopband Attenuation                                                                      |             |                                                                  | 60                         | dB    |

\_\_ /N/XI/N

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{PVDD} = V_{DVDD} = V_{DVDDIO} = +1.8V, R_L = \infty, \ headphone \ load \ (R_L) \ connected \ between \_OUTP \ and \_OUTN \ in \ differential mode, C_{REF} = 2.2 \mu F, C_{MICBIAS} = C_{PREG} = C_{REG} = 1 \mu F, \ AV_{PRE} = +20 dB, \ AV_{PGAM} = 0 dB, \ AV_{DAC} = 0 dB, \ AV_{LINE} = +20 dB, \ AV_{VOL} = 0 dB, \ MCLK = 13 MHz, T_A = T_{MIN} \ to \ T_{MAX}, \ unless \ otherwise \ noted. Typical values are at T_A = +25 °C.) \ (Note 2)$

| PARAMETER                           | SYMBOL             | CONE                                                                                                                                                                  | DITIONS                         | MIN | TYP                          | MAX | UNITS            |

|-------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----|------------------------------|-----|------------------|

| DAC STEREO AUDIO MODE DI            | GITAL DC BLO       | OCKING HIGHPASS F                                                                                                                                                     | ILTER                           |     |                              |     |                  |

| Passband Cutoff<br>(-3dB from Peak) | f <sub>DHPPB</sub> | DVFLT = 0x1                                                                                                                                                           |                                 |     | 0.000625<br>x f <sub>S</sub> |     | Hz               |

| DC Attenuation                      | DCATTEN            | DVFLT = 0x1                                                                                                                                                           |                                 |     | 90                           |     | dB               |

| ADC (Note 6)                        |                    |                                                                                                                                                                       |                                 |     |                              |     |                  |

| Dynamia Danga (Nota E)              | DR                 | $f_S = 8kHz$ , $MODE = 0$                                                                                                                                             | (IIR voice)                     | 75  | 84                           |     | dB               |

| Dynamic Range (Note 5)              | DR                 | $f_S = 8kHz$ to $48kHz$ , $N$                                                                                                                                         | MODE = 1 (FIR audio)            |     | 85                           |     | αь               |

| Full-Scale Input                    |                    | Differential MIC input<br>AVPRE = 0dB, AVPG.                                                                                                                          | •                               |     | 1                            |     | V <sub>P-P</sub> |

| Gain Error (Note 7)                 |                    | DC accuracy, measu<br>80% of full-scale outp                                                                                                                          | · ·                             |     | 1                            | 5   | %                |

| Voice Delle Phase Delay             | D.                 | f = 1kHz, 0dBFS, HP filter disabled,                                                                                                                                  | f <sub>S</sub> = 8kHz           |     | 1.2                          |     |                  |

| Voice Path Phase Delay              | P <sub>DLY</sub>   | analog input to digital output                                                                                                                                        | f <sub>S</sub> = 16kHz          |     | 0.61                         |     | ms               |

| Total Harmonic Distortion           | THD                | $f = 1kHz$ , $f_S = 8kHz$ , $T_S = 1$                                                                                                                                 | T <sub>A</sub> = +25°C, 0dBFs   |     | -81                          | -70 | dB               |

| ADC Level Adjust Range              | AVADC              | AVL/VR = 0xF  to  0x0                                                                                                                                                 |                                 | -12 |                              | +3  | dB               |

|                                     |                    | $V_{AVDD} = 1.65V \text{ to } 1.9$                                                                                                                                    | 5V, input referred              | 60  | 85                           |     |                  |

|                                     |                    | f = 217Hz, V <sub>RIPPLE</sub> = 100mV, AV <sub>ADC</sub> = 0dB, input referred  PSRR  f = 1kHz, V <sub>RIPPLE</sub> = 100mV, AV <sub>ADC</sub> = 0dB, input referred |                                 |     | 85                           |     |                  |

| Power-Supply Rejection Ratio        | PSRR               |                                                                                                                                                                       |                                 |     | 80                           |     | dB               |

|                                     |                    | f = 10kHz, V <sub>RIPPLE</sub> = input referred                                                                                                                       | 100mV, AV <sub>ADC</sub> = 0dB, |     | 80                           |     |                  |

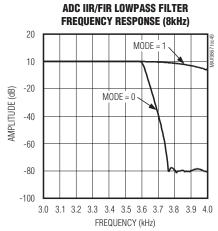

| ADC VOICE MODE DIGITAL IIR          | LOWPASS FI         | LTER                                                                                                                                                                  |                                 |     |                              |     |                  |

| 5 10 10 16                          | ,                  | With respect to fs with fs = 8kHz to 48kHz                                                                                                                            | nin ripple;                     |     | 0.445 x<br>f <sub>S</sub>    |     |                  |

| Passband Cutoff                     | fPLP               | -3dB cutoff                                                                                                                                                           |                                 |     | 0.449 x<br>f <sub>S</sub>    |     | Hz               |

| Passband Ripple                     |                    | f < fplp                                                                                                                                                              |                                 |     | ±0.1                         |     | dB               |

| Stopband Cutoff                     | f <sub>SLP</sub>   | With respect to fs; fs                                                                                                                                                | = 8kHz to 48kHz                 |     | 0.469 x<br>f <sub>S</sub>    |     | Hz               |

| Stopband Attenuation                |                    | $f > f_{SLP}$ , $f = 20Hz$ to 2                                                                                                                                       | 20kHz                           | 74  |                              |     | dB               |

|                                     |                    | •                                                                                                                                                                     |                                 |     |                              |     | •                |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{PVDD} = V_{DVDDD} = V_{DVDDIO} = +1.8V, R_L = \infty, headphone load (R_L) connected between _OUTP and _OUTN in differential mode, C_{REF} = 2.2 \mu F, C_{MICBIAS} = C_{PREG} = C_{REG} = 1 \mu F, AV_{PRE} = +20 dB, AV_{PGAM} = 0 dB, AV_{DAC} = 0 dB, AV_{LINE} = +20 dB, AV_{VOL} = 0 dB, MCLK = 13 MHz, T_A = T_{MIN} to T_{MAX}, unless otherwise noted. Typical values are at T_A = +25 °C.) (Note 2)$

| PARAMETER                                                                                | SYMBOL             | CONDITIONS                                                       | MIN TYP MAX                | UNITS |  |  |

|------------------------------------------------------------------------------------------|--------------------|------------------------------------------------------------------|----------------------------|-------|--|--|

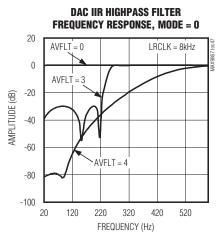

| ADC VOICE MODE DIGITAL 5th                                                               | ORDER IIR H        | IGHPASS FILTER                                                   |                            |       |  |  |

|                                                                                          |                    | AVFLT = 0x1<br>(elliptical tuned for 16kHz GSM + 217Hz<br>notch) | 0.0161<br>x fs             |       |  |  |

|                                                                                          |                    | AVFLT = 0x2<br>(500Hz Butterworth tuned for 16kHz)               | 0.0312<br>x fs             |       |  |  |

| 5th Order Passband Cutoff<br>(-3dB from Peak, I <sup>2</sup> C Register<br>Programmable) | f <sub>AHPPB</sub> | AVFLT = 0x3<br>(elliptical tuned for 8kHz GSM + 217Hz<br>notch)  | 0.0321<br>x fs             | Hz    |  |  |

|                                                                                          |                    | AVFLT = 0x4<br>(500Hz Butterworth tuned for 8kHz)                | 0.0625<br>x f <sub>S</sub> |       |  |  |

|                                                                                          |                    | AVFLT = 0x5<br>(fg/240 Butterworth)                              | 0.0042<br>x fs             |       |  |  |

|                                                                                          |                    | AVFLT = 0x1<br>(elliptical tuned for 16kHz GSM + 217Hz<br>notch) | 0.0139<br>x fs             |       |  |  |

|                                                                                          |                    | AVFLT = 0x2<br>(500Hz Butterworth tuned for 16kHz)               | 0.0156<br>x fs             |       |  |  |

| Stopband Cutoff (-30dB from Peak)                                                        | fAHPSB             | AVFLT = 0x3<br>(elliptical tuned for 8kHz GSM + 217Hz<br>notch)  | 0.0279<br>x fs             | Hz    |  |  |

|                                                                                          |                    | AVFLT = 0x4<br>(500Hz Butterworth tuned for 8kHz)                | 0.0312<br>x fs             |       |  |  |

|                                                                                          |                    | AVFLT = 0x5<br>(fg/240 Butterworth)                              | 0.0021<br>x fs             |       |  |  |

| DC Attenuation                                                                           | DCATTEN            | AVFLT ≠ 000                                                      | 90                         | dB    |  |  |

| ADC STEREO AUDIO MODE DIO                                                                | GITAL FIR LO       | WPASS FILTER                                                     |                            |       |  |  |

|                                                                                          |                    | With respect to $f_S$ within ripple;<br>$f_S = 8kHz$ to $48kHz$  | 0.43 x<br>fs               |       |  |  |

| Passband Cutoff                                                                          | f <sub>PLP</sub>   | -3dB cutoff                                                      | 0.48 x<br>fs               | Hz    |  |  |

|                                                                                          |                    | -6.02dB cutoff                                                   | 0.5 x f <sub>S</sub>       | 1     |  |  |

| Passband Ripple                                                                          |                    | f < fplp                                                         | ±0.1                       | dB    |  |  |

| Stopband Cutoff                                                                          | fSLP               | With respect to fs; fs = 8kHz to 48kHz                           | 0.58 x<br>fs               | Hz    |  |  |

| Stopband Attenuation                                                                     |                    | $f > f_{SLP}, f = 20Hz to 20kHz$                                 | 60                         | dB    |  |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{PVDD} = V_{DVDD} = V_{DVDDIO} = +1.8V, R_L = \infty, \ headphone \ load \ (R_L) \ connected \ between \_OUTP \ and \_OUTN \ in \ differential mode, C_{REF} = 2.2 \mu F, C_{MICBIAS} = C_{PREG} = C_{REG} = 1 \mu F, \ AV_{PRE} = +20 dB, \ AV_{PGAM} = 0 dB, \ AV_{DAC} = 0 dB, \ AV_{LINE} = +20 dB, \ AV_{VOL} = 0 dB, \ MCLK = 13 MHz, T_A = T_{MIN} \ to \ T_{MAX}, \ unless \ otherwise \ noted. Typical values are at T_A = +25 °C.) \ (Note 2)$

| PARAMETER                                              | SYMBOL     | CON                                          | IDITIONS                                                                                                    | MIN    | TYP              | MAX    | UNITS |

|--------------------------------------------------------|------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------|------------------|--------|-------|

| ADC STEREO AUDIO MODE DIG                              | TAL DC BLO | OCKING HIGHPASS                              | FILTER                                                                                                      |        |                  |        |       |

| Passband Cutoff<br>(-3dB from Peak)                    | fAHPPB     | AVFLT = 0x1                                  |                                                                                                             |        | 0.000625<br>x fs |        | Hz    |

| DC Attenuation                                         | DCATTEN    | AVFLT = 0x1                                  |                                                                                                             |        | 90               |        | dB    |

| OUTPUT VOLUME CONTROL                                  |            |                                              |                                                                                                             |        |                  |        |       |

|                                                        |            | VOLL/VOLR = 0x00                             |                                                                                                             | 14.55  | 14.9             | 15.15  |       |

|                                                        |            | VOLL/VOLR = 0x01                             |                                                                                                             | 14.1   | 14.4             | 14.6   |       |

| Line legent to Outer AValues                           |            | VOLL/VOLR = 0x02                             |                                                                                                             | 13.6   | 13.9             | 14.1   |       |

| Line Input to Output Volume<br>Control                 | AVvol      | VOLL/VOLR = 0x04                             |                                                                                                             | 12.6   | 12.9             | 13.1   | dB    |

| Control                                                |            | VOLL/VOLR = 0x08                             |                                                                                                             | 9.35   | 9.9              | 10.35  |       |

|                                                        |            | VOLL/VOLR = 0x10                             |                                                                                                             | 0.35   | 0.9              | 1.35   |       |

|                                                        |            | VOLL/VOLR = 0x20                             |                                                                                                             | -50.15 | -49.2            | -48.15 |       |

|                                                        |            | VOLL/VOLR = 0x00                             | to 0x06 (+6dB to +3dB)                                                                                      |        | 0.5              |        |       |

| Output Volume Control Step Size                        |            | VOLL/VOLR = 0x06                             | to 0x0F (+3dB to -6dB)                                                                                      |        | 1                |        | dB    |

| Output volume Control Step Size                        |            | VOLL/VOLR = $0x0F$ to $0x17$ (-6dB to -22dB) |                                                                                                             |        | 2                |        | ub    |

|                                                        |            | VOLL/VOLR = 0x17 to 0x3F (-22dB to mute)     |                                                                                                             |        | 4                |        |       |

| Output Volume Control Mute<br>Attenuation              |            | f = 1kHz                                     |                                                                                                             |        | 100              |        | dB    |

| HEADPHONE AMPLIFIER (Note 8                            | 3)         |                                              |                                                                                                             |        |                  |        |       |

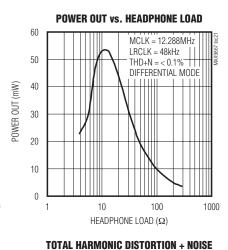

| Output Power per Channel                               | Роит       | f = 1kHz, THD <                              |                                                                                                             | 30     | 52               |        | mW    |

| (Differential Mode)                                    | 1 001      | 1%, T <sub>A</sub> = +25°C                   | $R_L = 32\Omega$                                                                                            |        | 32               |        | 11100 |

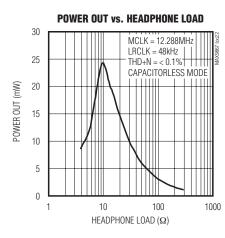

| Output Power per Channel                               | Роит       | f = 1kHz, THD <                              | $R_L = 16\Omega$                                                                                            |        | 19               |        | mW    |

| (Capacitorless Mode)                                   | . 001      | 1%, T <sub>A</sub> = +25°C                   | $R_L = 32\Omega$                                                                                            | 8      | 10               |        |       |

|                                                        |            | $R_L = 16\Omega$ , $P_{OUT} = 2$             |                                                                                                             |        | -76              |        |       |

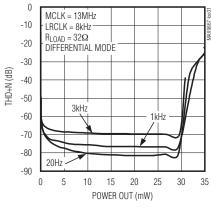

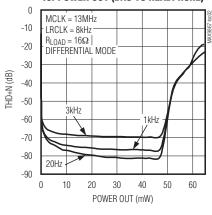

| Total Harmonic Distortion + Noise (Differential Mode)  | THD+N      | $R_L = 32\Omega$ , $P_{OUT} =$               | MCLK = 13MHz,<br>f <sub>S</sub> = 8kHz                                                                      |        | -77              | -70    | dB    |

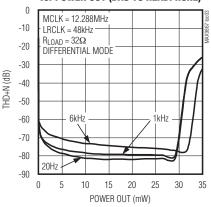

| (Sillororitial Mode)                                   |            | 25mW, f = 1kHz                               | $\begin{aligned} & \text{MCLK} = 12.288 \text{MHz}, \\ & \text{f}_{\text{S}} = 48 \text{kHz} \end{aligned}$ |        | -80              |        |       |

|                                                        |            | $R_L = 16\Omega$ , $P_{OUT} = 6$             | 6.25mW, f = 1kHz                                                                                            |        | -72              |        |       |

| Total Harmonic Distortion + Noise (Capacitorless Mode) | THD+N      | R <sub>L</sub> = 32Ω, P <sub>OUT</sub> =     | MCLK = 13MHz,<br>$f_S = 8kHz$                                                                               |        | -74              | -65    | dB    |

| (Capacitoriess Mode)                                   |            | 6.25mW, f = 1kHz                             | $MCLK = 12.288MHz,$ $f_S = 48kHz$                                                                           |        | -74              |        |       |

|                                                        |            | $R_L = 16\Omega$ , $P_{OUT} = 6$             | 6.25mW, f = 1kHz                                                                                            |        | -74              |        |       |

| Total Harmonic Distortion + Noise                      | THD+N      | R <sub>L</sub> = 32Ω, P <sub>OUT</sub> =     | MCLK = 13MHz,<br>f <sub>S</sub> = 8kHz                                                                      |        | -74              | -65    | dB    |

| (SE Mode)                                              |            | 6.25mW, f = 1kHz                             | MCLK = $12.288$ MHz,<br>$f_S = 48$ kHz                                                                      |        | -76              |        |       |

| Dynamic Range                                          | DR         | $AV_{VOL} = +6dB$ (Not                       | tes 5, 7)                                                                                                   | 76     | 90               |        | dB    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{PVDD} = V_{DVDDD} = V_{DVDDIO} = +1.8V, R_L = \infty, headphone load (R_L) connected between _OUTP and _OUTN in differential mode, C_{REF} = 2.2 \mu F, C_{MICBIAS} = C_{PREG} = C_{REG} = 1 \mu F, AV_{PRE} = +20 dB, AV_{PGAM} = 0 dB, AV_{DAC} = 0 dB, AV_{LINE} = +20 dB, AV_{VOL} = 0 dB, MCLK = 13 MHz, T_A = T_{MIN} to T_{MAX}, unless otherwise noted. Typical values are at T_A = +25 °C.) (Note 2)$

| PARAMETER                                        | SYMBOL            | COI                                                       | NDITIONS                                                                         | MIN  | TYP   | MAX  | UNITS |

|--------------------------------------------------|-------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------|------|-------|------|-------|

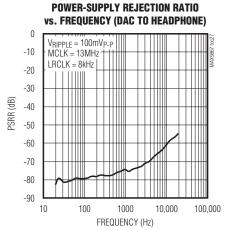

|                                                  |                   | V <sub>AVDD</sub> = V <sub>PVDD</sub> = <sup>3</sup>      | 1.65V to 1.95V                                                                   | 60   | 78    |      |       |

|                                                  |                   | f = 217Hz, V <sub>RIPPLE</sub><br>AV <sub>VOL</sub> = 0dB | = 100mV <sub>P-P</sub> ,                                                         |      | 78    |      |       |

| Power-Supply Rejection Ratio (Note 7)            | PSRR              | $f = 1kHz, V_{RIPPLE} = AV_{VOL} = 0dB$                   | 100mV <sub>P-P</sub> ,                                                           |      | 75    |      | dB    |

|                                                  |                   | f = 10kHz, V <sub>RIPPLE</sub><br>AV <sub>VOL</sub> = 0dB | = 10kHz, V <sub>RIPPLE</sub> = 100mV <sub>P-P</sub> ,<br>AV <sub>VOL</sub> = 0dB |      | 62    |      |       |

| Output Offset Voltage                            | Vos               | AV <sub>VOL</sub> = -84dB<br>differential mode            | (LOUTP-LOUTN,<br>ROUTP-ROUTN),<br>T <sub>A</sub> = +25°C                         |      | ±0.2  | ±1.3 | mV    |

| Output Offset Voltage                            | VOS               | AV <sub>VOL</sub> = -84dB<br>capacitorless<br>mode        | (LOUTP-LOUTN,<br>ROUTP-LOUTN),<br>T <sub>A</sub> = +25°C                         |      | ±0.8  | ±3   | TIIV  |

|                                                  |                   | Differential mode, F                                      | $P_{OUT} = 5$ mW, $f = 1$ kHz                                                    |      | 87    |      |       |

| Crosstalk                                        | X <sub>TALK</sub> | Capacitorless mode, POUT = 5mW, f = 1kHz                  | TQFN                                                                             |      | 55    |      | dB    |

|                                                  |                   |                                                           | WLP                                                                              |      | 60    |      |       |

| Capacitive Drive                                 |                   | No sustained                                              | $R_L = 32\Omega$                                                                 |      | 500   |      | рF    |

| Capacitive Drive                                 |                   | oscillations                                              | R <sub>L</sub> = ∞                                                               |      | 100   |      | рі    |

| Click-and-Pop Level (Differential, Capacitorless |                   | Peak voltage,<br>A-weighted, 32                           | Into shutdown                                                                    |      | -80   |      | dBV   |

| Modes)                                           |                   | samples per<br>second                                     | Out of shutdown                                                                  |      | -69   |      | GBV   |

| Click-and-Pop Level                              |                   | Peak voltage,<br>A-weighted, 32                           | Into shutdown                                                                    |      | -75   |      | dBV   |

| (SE Mode)                                        |                   | samples per second                                        | Out of shutdown                                                                  |      | -75   |      | иву   |

| MICROPHONE AMPLIFIER                             |                   |                                                           |                                                                                  |      |       |      |       |

|                                                  |                   | PALEN/PAREN = 0                                           | 1                                                                                | -0.5 | 0     | +0.5 |       |

| Preamplifier Gain                                | AVPRE             | PALEN/PAREN = 10                                          | 0                                                                                | 19.5 | 20    | 20.5 | dB    |

|                                                  |                   | PALEN/PAREN = 1                                           | 1                                                                                | 29.5 | 30    | 30.5 |       |

| MIC PGA Gain                                     | AVPGAM            | PGAML/PGAMR = 0                                           | 0x1F                                                                             | -0.6 | -0.1  | +0.4 | dB    |

|                                                  | / VFGAIVI         | PGAML/PGAMR = (                                           |                                                                                  | 19.3 | 19.75 | 20.3 | GD.   |

| Common-Mode Rejection Ratio                      | CMRR              | $V_{IN} = 100 \text{mV}_{P-P}, f =$                       | = 217Hz                                                                          |      | 50    |      | dB    |

| MIC Input Resistance                             | RIN_MIC           | All gain settings                                         |                                                                                  | 30   | 50    |      | kΩ    |

\_\_ /N/XI/M

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{PVDD} = V_{DVDD} = V_{DVDDIO} = +1.8V, \ R_L = \infty, \ headphone \ load \ (R_L) \ connected \ between \_OUTP \ and \_OUTN \ in \ differential mode, \ C_{REF} = 2.2 \mu F, \ C_{MICBIAS} = C_{REG} = 1 \mu F, \ AV_{PRE} = +20 dB, \ AV_{PGAM} = 0 dB, \ AV_{DAC} = 0 dB, \ AV_{LINE} = +20 dB, \ AV_{VOL} = 0 dB, \ MCLK = 13 MHz, \ T_A = T_{MIN} \ to \ T_{MAX}, \ unless \ otherwise \ noted. \ Typical \ values \ are \ at \ T_A = +25 °C.) \ (Note 2)$

| PARAMETER                         | SYMBOL               | CONDITIONS                                                                             | MIN               | TYP               | MAX               | UNITS             |

|-----------------------------------|----------------------|----------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|

|                                   |                      | $AV_{PRE} = 0dB,$ $V_{IN} = 1V_{P-P}, f = 1kHz$                                        |                   | -80               |                   |                   |

| Total Harmonic Distortion + Noise | THD+N                | $AV_{PRE} = +30dB,$ $V_{IN} = 32mV_{P-P}, f = 1kHz,$ $(1V_{P-P} \text{ at ADC input})$ |                   | -67               |                   | dB                |

|                                   |                      | V <sub>AVDD</sub> = 1.65V to 1.95V, input referred                                     | 60                | 85                |                   |                   |

|                                   |                      | f = 217Hz, V <sub>RIPPLE</sub> = 100mV,<br>AV <sub>ADC</sub> = 0dB, input referred     |                   | 85                |                   |                   |

| Power-Supply Rejection Ratio      | PSRR                 | f = 1kHz, V <sub>RIPPLE</sub> = 100mV,<br>AV <sub>ADC</sub> = 0dB, input referred      |                   | 80                |                   | dB                |

|                                   |                      | f = 10kHz, V <sub>RIPPLE</sub> = 100mV,<br>AV <sub>ADC</sub> = 0dB, input referred     |                   | 80                |                   |                   |

| MICROPHONE BIAS                   |                      |                                                                                        |                   |                   |                   |                   |

| Output Voltage                    | V <sub>MICBIAS</sub> | $V_{AVDD} = 1.8V$ , $I_{LOAD} = 1mA$                                                   | 1.5               | 1.525             | 1.55              | V                 |

| Load Regulation                   |                      | I <sub>LOAD</sub> = 1mA to 2mA                                                         |                   | 0.2               | 10                | V/A               |

| Line Regulation                   |                      | V <sub>AVDD</sub> = 1.65V to 1.95V                                                     |                   | 10                |                   | μV/V              |

| Power Supply Paigation Patio      | PSRR                 | $f = 217Hz$ , $V_{RIPPLE} = 100mV_{P-P}$                                               |                   | 85                |                   | dB                |

| Power-Supply Rejection Ratio      |                      | $f = 10kHz$ , $V_{RIPPLE} = 100mV_{P-P}$                                               |                   | 81                |                   | иБ                |

| Noise Voltage                     |                      | A-weighted                                                                             |                   | 9.1               |                   | μV <sub>RMS</sub> |

| LINE INPUT                        |                      |                                                                                        |                   |                   |                   |                   |

| Full-Scale Input                  | V <sub>IN</sub>      | AV <sub>LINE</sub> = 0dB                                                               |                   | 1.0               |                   | V <sub>P-P</sub>  |

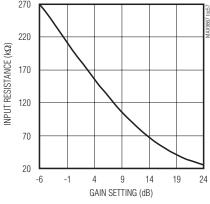

| Line Input Level Adjust Range     | AVLINE               | LIGL/LIGR = 0xF to 0x0                                                                 | -6.5              |                   | +24.5             | dB                |

| Line Input Mute Attenuation       |                      | f = 1kHz                                                                               |                   | 100               |                   | dB                |

| Input Resistance                  | R <sub>IN_LINE</sub> | AV <sub>LINE</sub> = +24dB                                                             | 20                |                   |                   | kΩ                |

| Total Harmonic Distortion + Noise | THD+N                | $V_{IN} = 0.1V_{P-P}$ , $f = 1kHz$ , differential output                               |                   | -83               |                   | dB                |

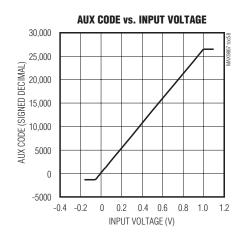

| AUXIN INPUT                       |                      |                                                                                        | 1                 |                   |                   | •                 |

| Input DC Voltage Range            |                      | AUXEN = 1                                                                              | 0                 |                   | 0.738             | V                 |

| AUXIN Input Resistance            | RIN                  | AUXEN = 1, 0V ≤ AUXIN ≤ 0.738                                                          | 10                | 40                |                   | $\Omega$ M        |

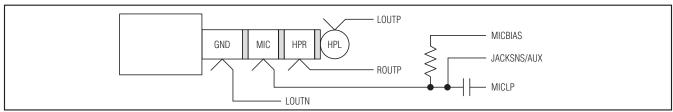

| JACK SENSE OPERATION              |                      |                                                                                        | T                 |                   |                   |                   |

| Throphold                         | VTH                  | JDETEN = 1, SHDN = 1, JACKSNS                                                          | 0.92 x<br>MICBIAS | 0.95 x<br>MICBIAS | 0.98 x<br>MICBIAS | V                 |

| Threshold                         | VIII                 | JDETEN = 1, SHDN = 0, JACKSNS,<br>LOUTP                                                | AVDD -<br>0.8     | AVDD -<br>0.4     | AVDD -<br>0.15    | V                 |

| Dullius Current                   | IDU                  | JDETEN = 1, SHDN = 1,<br>JACKSNS = GND                                                 |                   | 4                 |                   | ^                 |

| Pullup Current                    | IPU                  | JDETEN = 1, SHDN = 0,<br>JACKSNS = LOUTP = GND                                         |                   | 4                 | 20                | μA                |

| Pullup Voltage                    |                      | JDETEN = 1, JACKSNS, LOUTP                                                             |                   | AVDD              |                   | V                 |

|                                   | -                    |                                                                                        | •                 |                   |                   |                   |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{PVDD} = V_{DVDDD} = V_{DVDDIO} = +1.8V, R_L = \infty, headphone load (R_L) connected between _OUTP and _OUTN in differential mode, C_{REF} = 2.2 \mu F, C_{MICBIAS} = C_{PREG} = C_{REG} = 1 \mu F, AV_{PRE} = +20 dB, AV_{PGAM} = 0 dB, AV_{DAC} = 0 dB, AV_{LINE} = +20 dB, AV_{VOL} = 0 dB, MCLK = 13 MHz, T_A = T_{MIN} to T_{MAX}, unless otherwise noted. Typical values are at T_A = +25 °C.) (Note 2)$

| PARAMETER                                                             | SYMBOL                            | CONDITI                                      | ONS                                                                                                 | MIN             | TYP | MAX             | UNITS |

|-----------------------------------------------------------------------|-----------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------|-----|-----------------|-------|

| DIGITAL SIDETONE                                                      | <b>.</b>                          | 1                                            |                                                                                                     |                 |     |                 |       |

| Sidetone Gain Adjust Range                                            | AVSTGA                            | Differential output mode DVST = 0x1F to 0x01 | Differential output mode,<br>DVST = 0x1F to 0x01                                                    |                 |     | 0               | dB    |

| Voice Path Phase Delay                                                | P <sub>DLY</sub>                  |                                              | MIC input to headphone output, f = 1kHz,<br>HP filter disabled, fs = 8kHz                           |                 | 2.2 |                 | ms    |

| INPUT CLOCK CHARACTERISTI                                             | CS                                |                                              |                                                                                                     |                 |     |                 |       |

| MCLK Input Frequency                                                  | fMCLK                             | For any LRCLK sample                         | rate                                                                                                | 10              |     | 60              | MHz   |

| MCLK Input Duty Cycle                                                 |                                   | Prescaler = /1 mode                          |                                                                                                     | 40              |     | 60              | %     |

| MCER Input Duty Cycle                                                 |                                   | /2 or /4 modes                               |                                                                                                     | 30              |     | 70              | /0    |

| Maximum MCLK Input Jitter                                             |                                   | Maximum allowable RM limits                  | IS for performance                                                                                  |                 | 100 |                 | psRMS |

| LRCLK Sample Rate Range                                               |                                   |                                              |                                                                                                     | 8               |     | 48              | kHz   |

|                                                                       |                                   | Any allowable LRCLK                          | Rapid lock mode                                                                                     |                 | 2   | 7               |       |

| LRCLK PLL Lock Time                                                   |                                   | and PCLK rate, slave mode                    | Nonrapid lock mode                                                                                  |                 | 12  | 25              | ms    |

| LRCLK Acceptable Jitter for Maintaining PLL Lock                      |                                   | nominal for slave PLL m                      | Allowable LRCLK period change from nominal for slave PLL mode at any allowable LRCLK and PCLK rates |                 |     | ±100            | ns    |

|                                                                       |                                   | FREQ = 0x8 through 0x                        | F                                                                                                   | 0               |     | 0               | %     |

| LRCLK Average Frequency Error<br>(Master and Slave Modes)<br>(Note 9) |                                   | PCLK = 192xfs, 256xfs, 768xfs, and 1024xfs   | 384xfs, 512xfs,                                                                                     | 0               |     | 0               |       |

| (Note 9)                                                              |                                   | All other modes                              |                                                                                                     | -0.025          |     | +0.025          |       |

| DIGITAL INPUT (MCLK)                                                  |                                   |                                              |                                                                                                     |                 |     |                 |       |

| Input High Voltage                                                    | VIH                               |                                              |                                                                                                     | 1.2             |     |                 | V     |

| Input Low Voltage                                                     | VIL                               |                                              |                                                                                                     |                 |     | 0.6             | V     |

| Input Leakage Current                                                 | I <sub>IH</sub> , I <sub>IL</sub> | T <sub>A</sub> = +25°C                       |                                                                                                     |                 |     | ±1              | μΑ    |

| Input Capacitance                                                     |                                   |                                              |                                                                                                     |                 | 10  |                 | рF    |

| DIGITAL INPUTS (SDIN, BCLK, L                                         | RCLK)                             |                                              |                                                                                                     |                 |     |                 |       |

| Input High Voltage                                                    | V <sub>IH</sub>                   |                                              |                                                                                                     | 0.7 x<br>DVDDIO |     |                 | V     |

| Input Low Voltage                                                     | VIL                               |                                              |                                                                                                     |                 |     | 0.3 x<br>DVDDIO | V     |

| Input Hysteresis                                                      |                                   |                                              |                                                                                                     |                 | 200 |                 | mV    |

| Input Leakage Current                                                 | I <sub>IH</sub> , I <sub>IL</sub> | T <sub>A</sub> = +25°C                       |                                                                                                     |                 |     | ±1              | μΑ    |

| Input Capacitance                                                     |                                   |                                              |                                                                                                     |                 | 10  |                 | рF    |

\_\_ /N/XI/N

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{PVDD} = V_{DVDD} = V_{DVDDIO} = +1.8V, R_L = \infty, \ headphone \ load \ (R_L) \ connected \ between \_OUTP \ and \_OUTN \ in \ differential mode, C_{REF} = 2.2 \mu F, C_{MICBIAS} = C_{PREG} = C_{REG} = 1 \mu F, \ AV_{PRE} = +20 dB, \ AV_{PGAM} = 0 dB, \ AV_{DAC} = 0 dB, \ AV_{LINE} = +20 dB, \ AV_{VOL} = 0 dB, \ MCLK = 13 MHz, T_A = T_{MIN} \ to \ T_{MAX}, \ unless \ otherwise \ noted. Typical values are at T_A = +25 °C.) \ (Note 2)$

| PARAMETER                             | SYMBOL                            | CONDITIONS                                      | MIN TYP                               | MAX            | UNITS |

|---------------------------------------|-----------------------------------|-------------------------------------------------|---------------------------------------|----------------|-------|

| DIGITAL INPUTS (SDA, SCL)             |                                   |                                                 |                                       |                |       |

| Input High Voltage                    | VIH                               |                                                 | 0.7 x<br>DVDD                         |                | V     |

| Input Low Voltage                     | VIL                               |                                                 |                                       | 0.3 x<br>DVDD  | V     |

| Input Hysteresis                      |                                   |                                                 | 200                                   |                | mV    |

| Input Leakage Current                 | I <sub>IH</sub> , I <sub>IL</sub> | $T_A = +25^{\circ}C$                            |                                       | ±1             | μΑ    |

| Input Capacitance                     |                                   |                                                 | 10                                    |                | рF    |

| DIGITAL INPUT (DIGMICDATA)            |                                   |                                                 |                                       |                |       |

| Input High Voltage                    | VIH                               |                                                 | 0.65 x<br>DVDD                        |                | V     |

| Input Low Voltage                     | V <sub>IL</sub>                   |                                                 |                                       | 0.35 x<br>DVDD | V     |

| Input Hysteresis                      |                                   |                                                 | 100                                   |                | mV    |

| Input Leakage Current                 | I <sub>IH</sub> , I <sub>IL</sub> | $T_A = +25^{\circ}C$                            |                                       | ±35            | μΑ    |

| Input Capacitance                     |                                   |                                                 | 10                                    |                | рF    |

| CMOS DIGITAL OUTPUTS (BCI             | K, LRCLK, SE                      | POUT)                                           |                                       |                |       |

| Output Low Voltage                    | V <sub>OL</sub>                   | I <sub>OL</sub> = 3mA                           |                                       | 0.4            | V     |

| Output High Voltage                   | Voн                               | I <sub>OH</sub> = 3mA                           | DVDDIO<br>- 0.4                       |                | V     |

| CMOS DIGITAL OUTPUT (DIGN             | IICCLK)                           |                                                 | <b>'</b>                              |                |       |

| Output Low Voltage                    | V <sub>OL</sub>                   | I <sub>OL</sub> = 1mA                           |                                       | 0.4            | V     |

| Output High Voltage                   | Voн                               | I <sub>OH</sub> = 1mA                           | DVDD -<br>0.4                         |                | V     |

| OPEN-DRAIN DIGITAL OUTPUT             | S (SDA, IRQ)                      | ,                                               |                                       |                | l.    |

| Output High Current                   | Іон                               | V <sub>OUT</sub> = DVDD, T <sub>A</sub> = +25°C |                                       | 1              | μΑ    |

| Output Low Voltage                    | V <sub>OL</sub>                   | I <sub>OL</sub> = 3mA                           |                                       | 0.2 x<br>DVDD  | V     |

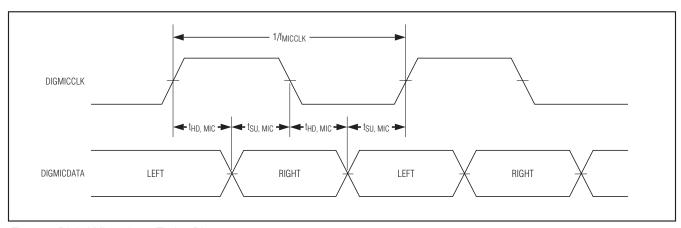

| DIGITAL MICROPHONE TIMING             | CHARACTER                         | RISTICS (V <sub>DVDD</sub> = 1.65V)             | · · · · · · · · · · · · · · · · · · · |                |       |

| DIGMICCLK Divide Ratio                | fMICCLK                           | MICCLK = 00<br>MICCLK = 01                      | PCLK,<br>PCLK,                        |                | MHz   |

| DIGMICDATA to DIGMICCLK<br>Setup Time | tsu,MIC                           | Either clock edge                               | 20                                    |                | ns    |

| DIGMICDATA to DIGMICCLK<br>Hold Time  | tHD,MIC                           | Either clock edge                               | 0                                     |                | ns    |

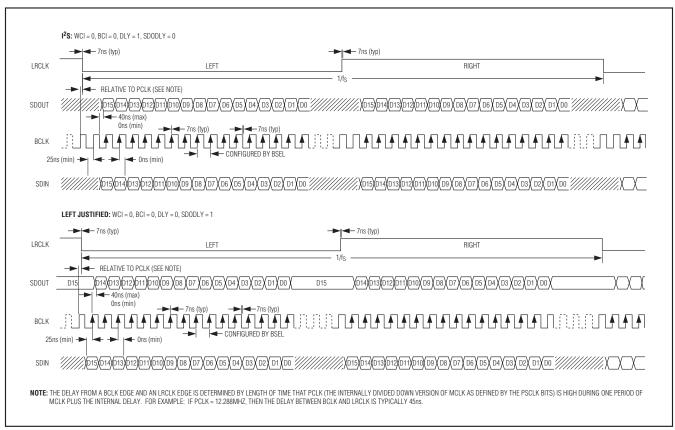

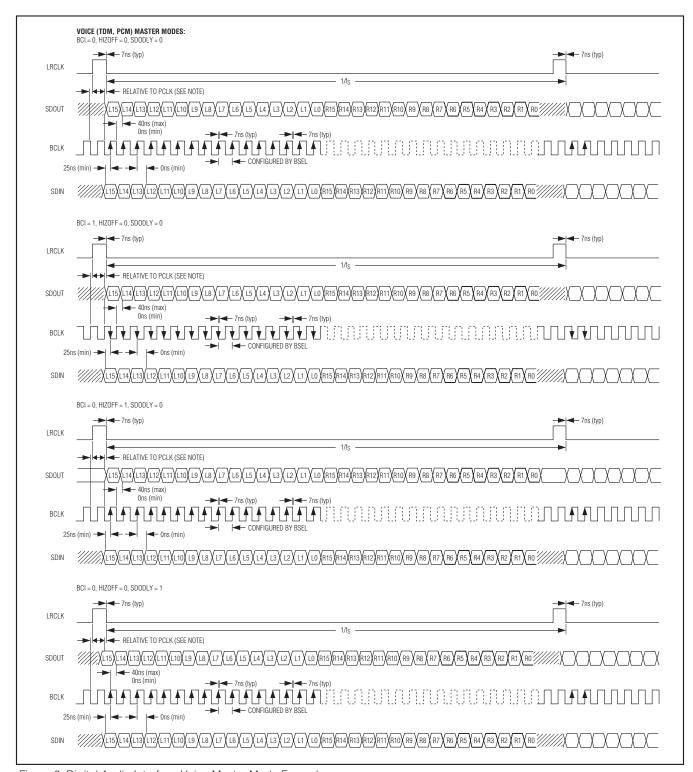

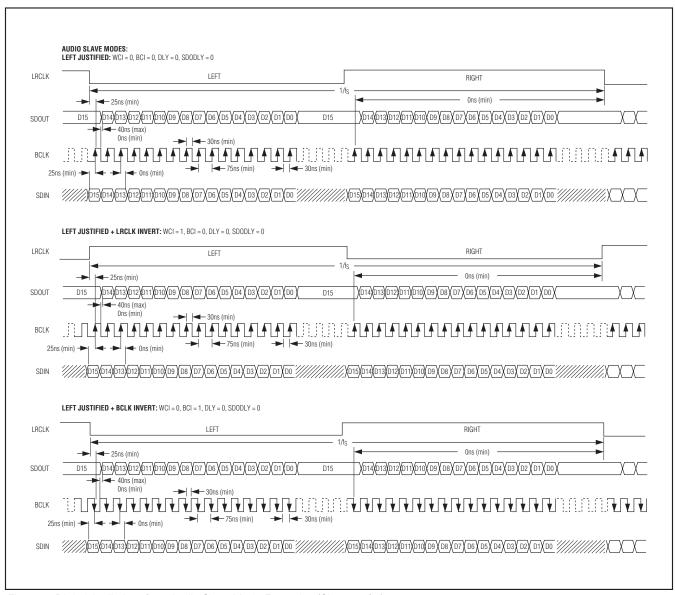

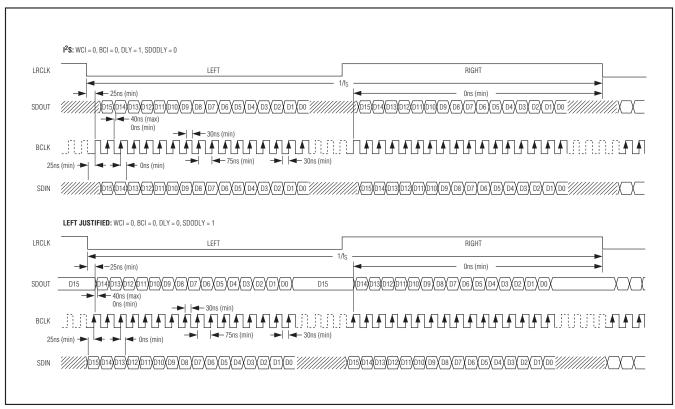

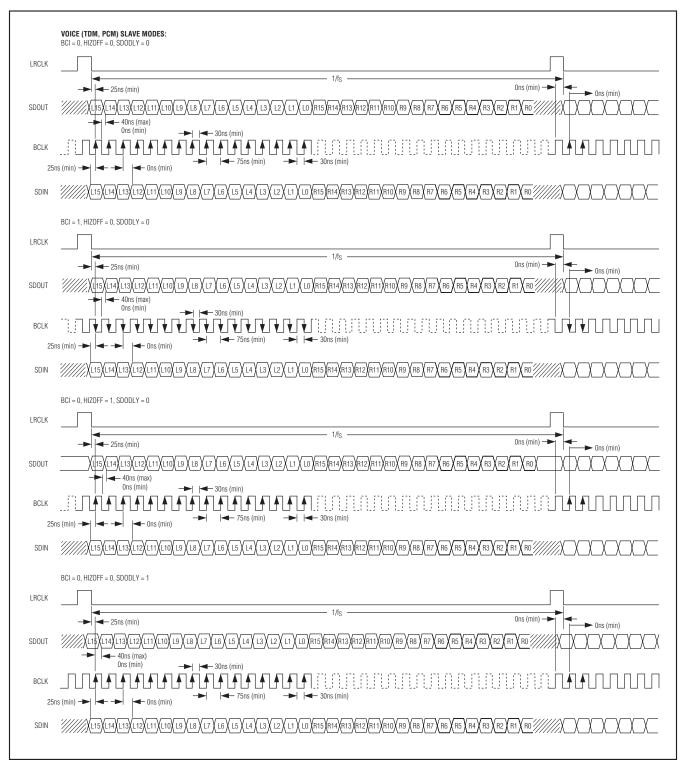

| DIGITAL AUDIO INTERFACE TI            | MING CHARA                        | CTERISTICS (V <sub>DVDD</sub> = 1.65V)          | <u>.</u>                              |                |       |

| Minimum PCLK Cycle Time               | †BCLKS                            | Slave operation                                 | 75                                    | -              | ns    |

| Minimum BCLK Cycle Time               | tBCLKM                            | Master operation                                | 325                                   |                | ns    |

|                                       |                                   | l .                                             |                                       |                |       |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{PVDD} = V_{DVDD} = V_{DVDDIO} = +1.8V, R_L = \infty, headphone load (R_L) connected between \_OUTP and \_OUTN in differential mode, C_{REF} = 2.2 \mu F, C_{MICBIAS} = C_{PREG} = C_{REG} = 1 \mu F, AV_{PRE} = +20 dB, AV_{PGAM} = 0 dB, AV_{DAC} = 0 dB, AV_{LINE} = +20 dB, AV_{VOL} = 0 dB, MCLK = 13 MHz, T_A = T_{MIN} to T_{MAX}, unless otherwise noted. Typical values are at T_A = +25 °C.) (Note 2)$

| PARAMETER                                       | SYMBOL                          | CONDITIONS                              | MIN                       | TYP | MAX | UNITS |

|-------------------------------------------------|---------------------------------|-----------------------------------------|---------------------------|-----|-----|-------|

| Minimum BCLK High Time                          | <sup>t</sup> BCLKH              | Slave operation                         |                           | 30  |     | ns    |

| Minimum BCLK Low Time                           | †BCLKL                          | Slave operation                         |                           | 30  |     | ns    |

| BCLK or LRCLK Rise and Fall                     | t <sub>R</sub> , t <sub>F</sub> | Master operation, C <sub>L</sub> = 15pF |                           | 7   |     | ns    |

| SDIN or LRCLK to BCLK Setup Time                | tsu                             |                                         | 20                        |     |     | ns    |

| SDIN or LRCLK to BCLK Hold Time                 | tHD                             |                                         | 0                         |     |     | ns    |

| SDOUT Delay Time from BCLK<br>Rising Edge       | t <sub>DLY</sub>                | C <sub>L</sub> = 30pF                   | 0                         |     | 40  | ns    |

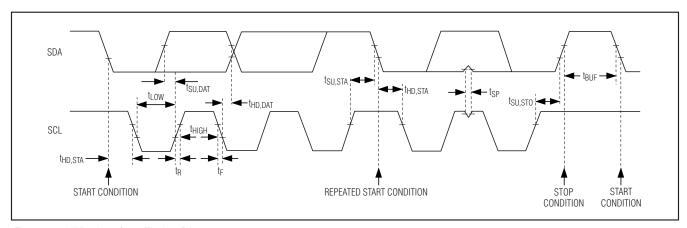

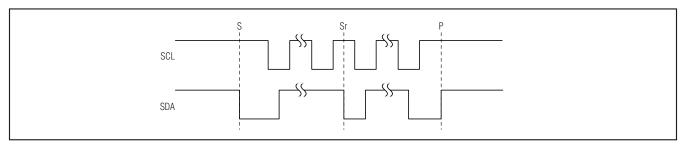

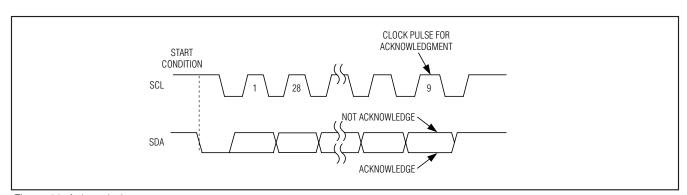

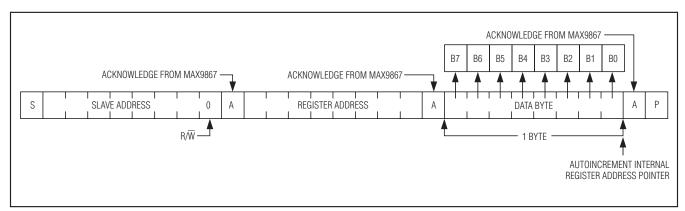

| I <sup>2</sup> C TIMING CHARACTERISTICS (       | V <sub>DVDD</sub> = 1.6         | 5V)                                     |                           |     |     |       |

| Serial-Clock Frequency                          | fscl                            |                                         | 0                         |     | 400 | kHz   |

| Bus Free Time Between STOP and START Conditions | tBUF                            |                                         | 1.3                       |     |     | μs    |

| Hold Time (REPEATED) START Condition            | thd,sta                         |                                         | 0.6                       |     |     | μs    |

| SCL Pulse-Width Low                             | tLOW                            |                                         | 1.3                       |     |     | μs    |

| SCL Pulse-Width High                            | thigh                           |                                         | 0.6                       |     |     | μs    |

| Setup Time for a REPEATED START Condition       | tsu,sta                         |                                         | 0.6                       |     |     | μs    |

| Data Hold Time                                  | thd,dat                         | $R_{PU,SDA} = 475\Omega$                | 0                         |     | 900 | ns    |

| Data Setup Time                                 | tsu,dat                         |                                         | 100                       |     |     | ns    |

| SDA and SCL Receiving Rise Time                 | t <sub>R</sub>                  | (Note 10)                               | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

| SDA and SCL Receiving Fall Time                 | t <sub>F</sub>                  | (Note 10)                               | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

| SDA Transmitting Fall Time                      | t <sub>F</sub>                  | $R_{PU,SDA} = 475\Omega$ (Note 10)      | 20 +<br>0.1C <sub>B</sub> |     | 250 | ns    |

| Setup Time for STOP Condition                   | tsu,sto                         |                                         | 0.6                       |     |     | μs    |

| Bus Capacitance                                 | CB                              |                                         |                           |     | 400 | рF    |

| Pulse Width of Suppressed Spike                 | tsp                             |                                         | 0                         |     | 50  | ns    |

- Note 2: The MAX9867 is 100% production tested at  $T_A = +25$ °C. Specifications over temperature limits are guaranteed by design.

- Note 3: Clocking all zeros into the DAC, master mode, and differential headphone mode.

- Note 4: DAC performance measured at the headphone outputs.

- Note 5: Dynamic range measured using the EIAJ method. -60dBFS 1kHz output signal, A-weighted, and normalized to 0dBFS. f = 20Hz to 20kHz.

- **Note 6:** Performance measured using microphone inputs, unless otherwise stated.

- Note 7: Performance measured using line inputs.

- Note 8: Performance measured using DAC, unless otherwise stated. LRCLK = 8kHz, unless otherwise stated.

- Note 9: In master-mode operation, the accuracy of the MCLK input proportionally determines the accuracy of the sample clock rate.

- Note 10: CB is in pF.

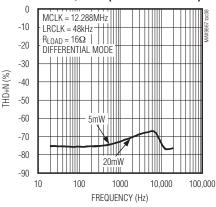

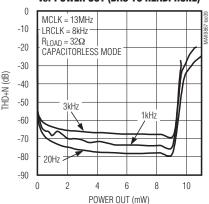

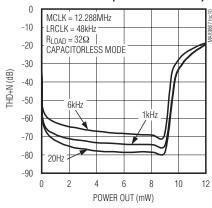

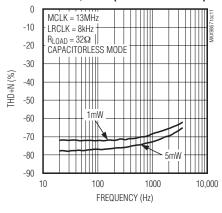

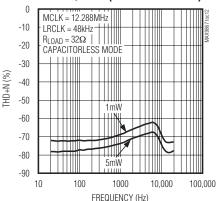

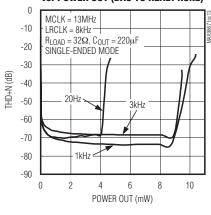

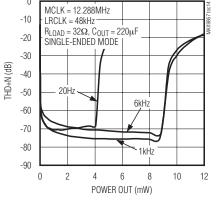

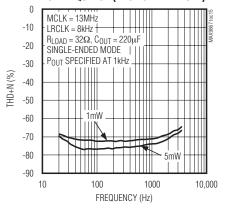

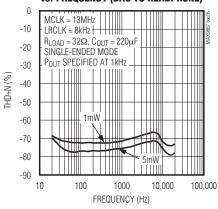

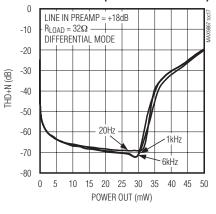

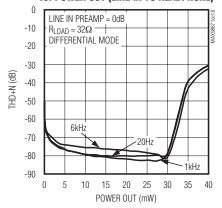

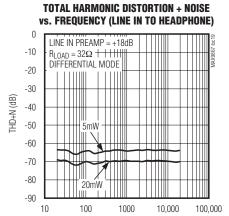

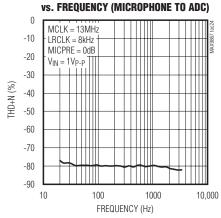

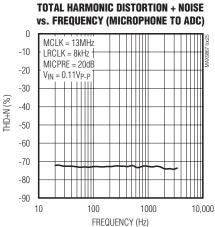

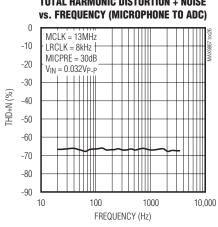

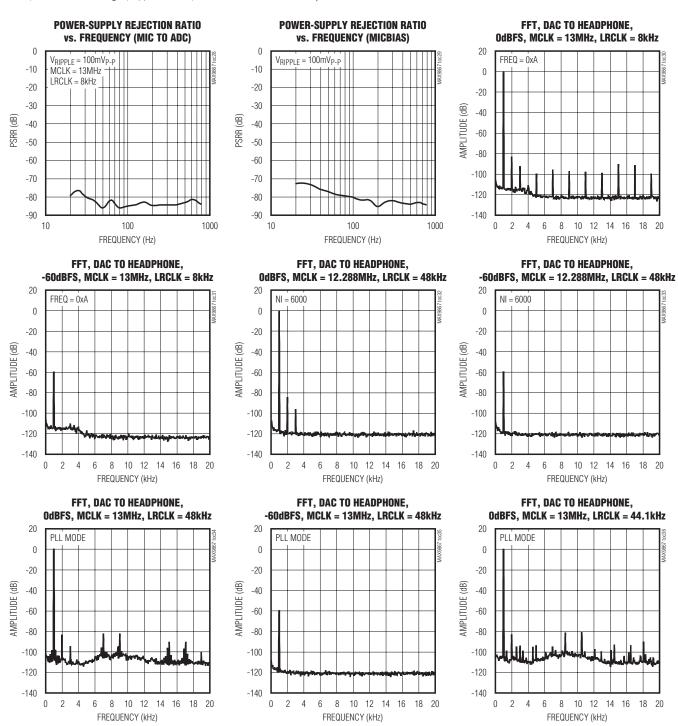

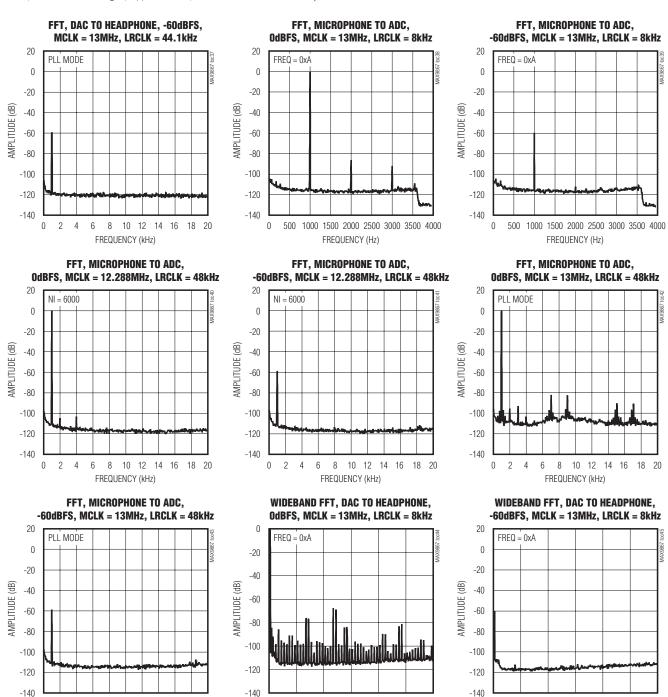

#### **Typical Operating Characteristics**

$(V_{AVDD} = V_{DVDD} = V_{PVDD} = +1.8V, C_{REF} = 2.2\mu F, C_{MICBIAS} = C_{PREG} = C_{REG} = 1\mu F, AV_{MICPGA} = 0dB, MCLK = 13MHz, LRCLK = 8kHz, BW = 20Hz to fs/2, T_A = +25°C, unless otherwise noted.)$

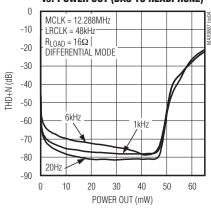

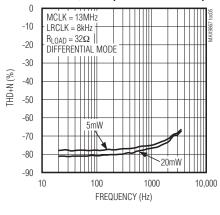

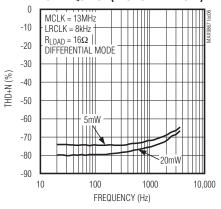

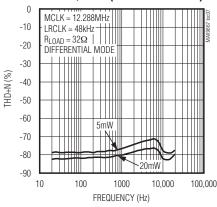

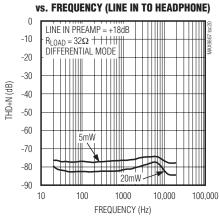

# TOTAL HARMONIC DISTORTION + NOISE vs. POWER OUT (DAC TO HEADPHONE)

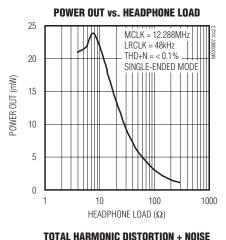

# TOTAL HARMONIC DISTORTION + NOISE vs. Power out (dac to headphone)

TOTAL HARMONIC DISTORTION + NOISE vs. POWER OUT (DAC TO HEADPHONE)

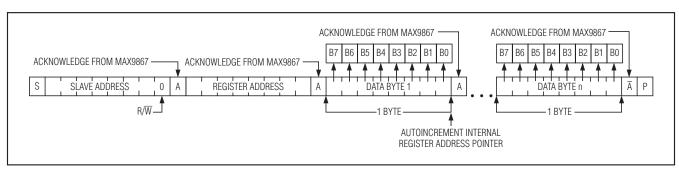

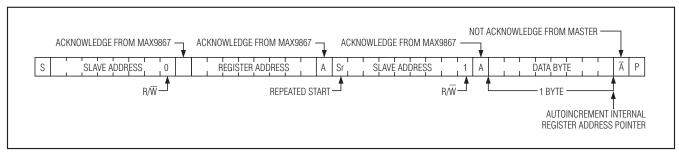

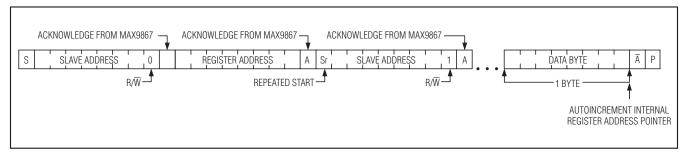

TOTAL HARMONIC DISTORTION + NOISE vs. POWER OUT (DAC TO HEADPHONE)