# 双通道数字隔离器

查询样品: ISO7221C-HT

#### 特性

- 1-, 5- 和 25-Mbps 信号传输速度选项

- 低通道到通道输出偏移; 1 ns 最大

- 低脉宽失真 (PWD); 1 ns 最大

- 低抖动(在速率为 **150Mbps** 时为 **1ns**) (典型 值)

- 4000-V<sub>峰值</sub>隔离, 560 V<sub>峰值</sub> V<sub>IORM</sub>

- UL 1577 经过检验

- 50-kV/μs 典型瞬变抗扰性

- 3.3-V 或 5-V 电源供电下运行

- 4-kV ESD 保护

- 高电磁抗扰度

#### 应用

- 潜孔钻进

- 高温环境

#### 支持极端温度应用

- 受控基线

- One Assembly and Test Site

- 一个制造场所

- 可在极端温度范围 (-55°C/175°C) 下工作 (1) (2)

- 产品生命周期有所延长

- 拓展的产品变更通知

- 产品可追溯性

- 德州仪器的高温产品运用了高度优化的硅片(芯片)解决方案,此类解决方案在设计与工艺方面均有所强化,以在扩展的温度范围内实现性能的最大化。

- (1) 可定制温度范围。

- (2) 在最大额定温度,设备能可靠运行1000小时。 这包括, 但并不限于温度烘烤, 温度循环, 电迁移, 内部粘合金属寿命, 和模具混合寿命。 不应该观看这样资格测试作为辩解对在指定的表现和环境极限之外的这个组分的用途。

#### 说明

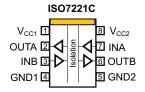

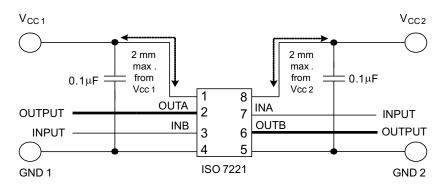

ISO7221是一个双通道数字隔离器。 为了使PCB布局更加便利, 通道都是面向相反的方向、 这个设备有一个由TI的 二氧化硅(SiO<sub>2</sub>)隔离栏栅分开的逻辑输入和输出缓冲器, 提供高达4000V的电流隔离. 与隔离电源联合使用, 这个设备能阻止高电压, 隔离接地, 并且在数据总线上防止噪声电流或者其它电路进入本地接地和干扰或者损坏敏感电路。

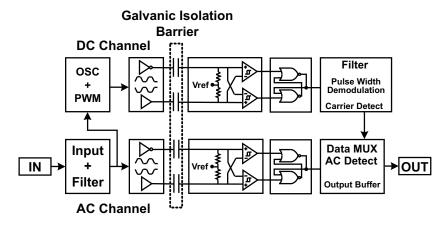

一个二进制输入信号经调节,翻译成平衡信号,然后由电容隔离栏栅进行区分。通过隔离栏栅后,一个差动比较器接收到逻辑信息,然后相应地设定或重置一个触发器和输出电路。周期性更新脉冲也会通过栏栅发送,以确保设置正确的 DC 级别。如果在每4µs内没有接收到这个DC刷新脉冲,则这个输入就被假定为没被供电或者没有被正常驱动,并且这个故障自动保险电路将输出驱动至一个逻辑高能状态。

这个小电容和结果时间持续提供信号速率在

0 Mbps (dc) 到150 Mbps间的快速运行. <sup>(3)</sup> A-, B- and C-选项设备有TTL输入阀值和一个输入端噪音过滤器,这能够防止瞬时脉冲通过设备的输出端。 M选项设备具有CMOS V<sub>CC</sub>/2个输入阀值并且没有输入噪音过滤和额外的传播延迟。

这个设备要求3.3 V, 5 V两个供电电压,或者任一组合。 当采用一个 3.3V 电源来供电并且所有的输出都是4-mA CMOS时,所有的输入均可容许 5V 电压。

ISO7221针对环境温度在-55°C 到 175°C间的操作。

(3) 一条线路的信号传输速率就是电压瞬变的次数,即每秒钟单位 bps (每秒比特数)。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### SINGLE-CHANNEL FUNCTION DIAGRAM

#### AVAILABLE OPTIONS(1)

| PRODUCT  | MAX<br>SIGNALING<br>RATE | PACKAGE <sup>(2)</sup> | INPUT<br>THRESHOLD                 | MARKED<br>AS | ORDERING<br>NUMBER |

|----------|--------------------------|------------------------|------------------------------------|--------------|--------------------|

| ISO7221C | 25 Mbps                  | SOIC-8                 | ≉ 1.5 V (TTL)<br>(CMOS compatible) | I7221H       | ISO7221CHD         |

- (1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

- Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

#### REGULATORY INFORMATION

| UL                                                                 |

|--------------------------------------------------------------------|

| Recognized under 1577 Component Recognition Program <sup>(1)</sup> |

| File Number: E181974                                               |

Production tested ≥3000 VRMS for 1 second in accordance with UL 1577.

#### ABSOLUTE MAXIMUM RATINGS(1)

|                |                         |                                                      |                                                                  |          | VALUE     | UNIT |

|----------------|-------------------------|------------------------------------------------------|------------------------------------------------------------------|----------|-----------|------|

| $V_{CC}$       | Supply voltage          | <sup>(2)</sup> , V <sub>CC1</sub> , V <sub>CC2</sub> |                                                                  |          | -0.5 to 6 | V    |

| VI             | Voltage at IN, 0        | DUT                                                  |                                                                  |          | -0.5 to 6 | V    |

| Io             | Output current          |                                                      |                                                                  |          | ±15       | mA   |

|                |                         | Human Body Model                                     | Electrostatic discharge JEDEC Standard 22, Test Method A114-C.01 |          | ±4        | kV   |

| ESD            | Electrostatic discharge | Field-Induced-Charged Device<br>Model                | JEDEC Standard 22, Test Method C101                              | All pins | ±1        |      |

|                |                         | Machine Model                                        | ANSI/ESDS5.2-1996                                                |          | ±200      | V    |

| T <sub>J</sub> | Maximum junct           | ion temperature                                      |                                                                  |          | 180       | °C   |

- (1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) All voltage values except differential I/O bus voltages are with respect to network ground terminal and are peak voltage values.

#### RECOMMENDED OPERATING CONDITIONS

|                   |                                                                     | MIN | TYP | MAX      | UNIT |

|-------------------|---------------------------------------------------------------------|-----|-----|----------|------|

| $V_{CC}$          | Supply voltage <sup>(1)</sup> , V <sub>CC1</sub> , V <sub>CC2</sub> | 3   |     | 5.5      | V    |

| I <sub>OH</sub>   | High-level output current                                           |     |     | 4        | mA   |

| I <sub>OL</sub>   | Low-level output current                                            | -4  |     |          | mA   |

| t <sub>ui</sub>   | Input pulse width <sup>(2)</sup>                                    | 40  | 33  |          | ns   |

| 1/t <sub>ui</sub> | Signaling rate <sup>(2)</sup>                                       | 0   | 30  | 25       | Mbps |

| $V_{IH}$          | High-level input voltage                                            | 2   |     | $V_{CC}$ | V    |

| $V_{IL}$          | Low-level input voltage                                             | 0   |     | 0.8      | V    |

| T <sub>A</sub>    | Operating temperature                                               | -55 |     | 175      | °C   |

<sup>(1)</sup> For the 5-V operation, V<sub>CC1</sub> or V<sub>CC2</sub> is specified from 4.5 V to 5.5 V. For the 3-V operation, V<sub>CC1</sub> or V<sub>CC2</sub> is specified from 3 V to 3.6 V.

(2) Typical signaling rate and Input pulse width are measured at ideal conditions at 25°C.

# ELECTRICAL CHARACTERISTICS: V<sub>CC1</sub> and V<sub>CC2</sub> at 5-V<sup>(1)</sup> OPERATION

over recommended operating conditions (unless otherwise noted)

|                     | PARAMETER                      | TEST CONDITIONS                                       | MIN                   | TYP | MAX | UNIT  |

|---------------------|--------------------------------|-------------------------------------------------------|-----------------------|-----|-----|-------|

| SUPPL               | Y CURRENT                      |                                                       |                       |     |     |       |

| I <sub>CC1</sub>    | 25 Mbps                        | V <sub>I</sub> = V <sub>CC</sub> or 0 V, no load      |                       | 12  | 22  | mA    |

| I <sub>CC2</sub>    | 25 Mbps                        | $V_I = V_{CC}$ or 0 V, no load                        |                       | 12  | 22  |       |

| V                   | Lligh lovel output valtage     | I <sub>OH</sub> = -4 mA, See Figure 1                 | $V_{CC} - 0.8$        | 4.6 |     | V     |

| V <sub>OH</sub>     | High-level output voltage      | $I_{OH} = -20 \mu A$ , See Figure 1                   | V <sub>CC</sub> - 0.1 | 5   |     | v     |

|                     | Laur laurel autout vallana     | I <sub>OL</sub> = 4 mA, See Figure 1                  |                       | 0.2 | 0.4 | V     |

| $V_{OL}$            | Low-level output voltage       | I <sub>OL</sub> = 20 μA, See Figure 1                 |                       | 0   | 0.1 | V     |

| V <sub>I(HYS)</sub> | Input voltage hysteresis       |                                                       |                       | 150 |     | mV    |

| I <sub>IH</sub>     | High-level input current       | IN from 0 V to V <sub>CC</sub>                        |                       |     | 11  | μΑ    |

| I <sub>IL</sub>     | Low-level input current        | IN from 0 V to V <sub>CC</sub>                        | -11                   |     |     | μΑ    |

| C <sub>I</sub>      | Input capacitance to ground    | IN at $V_{CC}$ , $V_{I} = 0.4 \sin (4E6\pi t)$        |                       | 1   |     | pF    |

| CMTI                | Common-mode transient immunity | V <sub>I</sub> = V <sub>CC</sub> or 0 V, See Figure 3 | 25                    | 50  |     | kV/µs |

<sup>(1)</sup> For the 5-V operation,  $V_{CC1}$  or  $V_{CC2}$  is specified from 4.5 V to 5.5 V. For the 3-V operation,  $V_{CC1}$  or  $V_{CC2}$  is specified from 3 V to 3.6 V.

# SWITCHING CHARACTERISTICS: $V_{CC1}$ and $V_{CC2}$ at 5-V OPERATION

over recommended operating conditions (unless otherwise noted)

|                                     | PARAMETER                                          | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-------------------------------------|----------------------------------------------------|-----------------|-----|-----|-----|------|

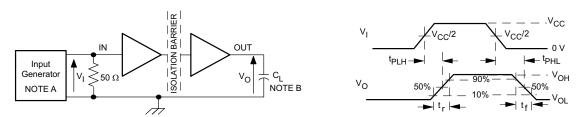

| t <sub>pLH</sub> , t <sub>pHL</sub> | Propagation delay                                  | See Figure 1    | 21  | 32  | 43  | ns   |

| PWD                                 | Pulse-width distortion $ t_{pHL} - t_{pLH} ^{(1)}$ | See Figure 1    |     | 1   | 2   | ns   |

| t <sub>sk(pp)</sub>                 | Part-to-part skew (2)                              |                 |     |     | 10  | ns   |

| t <sub>sk(o)</sub>                  | Channel-to-channel output skew (3)                 |                 |     | 0.2 | 5   | ns   |

| t <sub>r</sub>                      | Output signal rise time                            | See Figure 1    |     | 1   |     | ns   |

| t <sub>f</sub>                      | Output signal fall time                            | See Figure 1    |     | 1   |     | ns   |

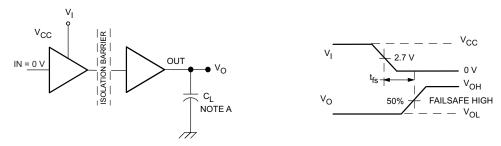

| t <sub>fs</sub>                     | Failsafe output delay time from input power loss   | See Figure 2    |     | 3   |     | μs   |

Also referred to as pulse skew.

$t_{sk(pp)}$  is the magnitude of the difference in propagation delay times between any specified terminals of two devices when both devices operate with the same supply voltages, at the same temperature, and have identical packages and test circuits.

t<sub>sk(o)</sub> is the skew between specified outputs of a single device with all driving inputs connected together and the outputs switching in the same direction while driving identical specified loads.

# ELECTRICAL CHARACTERISTICS: V<sub>CC1</sub> at 5 V, V<sub>CC2</sub> at 3.3 V<sup>(1)</sup> OPERATION

over recommended operating conditions (unless otherwise noted)

|                  | PARAMETER                      |            | TEST CONDITIONS                                       | MIN                   | TYP | MAX | UNIT  |

|------------------|--------------------------------|------------|-------------------------------------------------------|-----------------------|-----|-----|-------|

| SUPPL            | Y CURRENT                      |            |                                                       |                       |     |     |       |

| I <sub>CC1</sub> | 25 Mbps                        |            | V <sub>I</sub> = V <sub>CC</sub> or 0 V, no load      |                       | 12  | 22  | mA    |

| I <sub>CC2</sub> | 25 Mbps                        |            | V <sub>I</sub> = V <sub>CC</sub> or 0 V, no load      |                       | 6   | 12  | mA    |

| .,               | Lligh level output valtage     | (5-V side) | I <sub>OH</sub> = -4 mA, See Figure 1                 | $V_{CC} - 0.8$        |     |     | V     |

| V <sub>OH</sub>  | High-level output voltage      |            | I <sub>OH</sub> = -20 μA, See Figure 1                | V <sub>CC</sub> - 0.1 |     |     | V     |

| V                |                                |            | I <sub>OL</sub> = 4 mA, See Figure 1                  |                       |     | 0.4 | >     |

| $V_{OL}$         | Low-level output voltage       |            | I <sub>OL</sub> = 20 μA, See Figure 1                 |                       |     | 0.1 | V     |

| $V_{I(HYS)}$     | Input voltage hysteresis       |            |                                                       |                       | 150 |     | mV    |

| I <sub>IH</sub>  | High-level input current       |            | IN from 0 V to V <sub>CC</sub>                        |                       |     | 11  | μΑ    |

| I <sub>IL</sub>  | Low-level input current        |            | IN from 0 V to V <sub>CC</sub>                        | -11                   |     |     | μA    |

| Cı               | Input capacitance to ground    |            | IN at $V_{CC}$ , $V_{I} = 0.4 \sin (4E6\pi t)$        |                       | 1   |     | pF    |

| CMTI             | Common-mode transient immunity |            | V <sub>I</sub> = V <sub>CC</sub> or 0 V, See Figure 3 | 15                    | 40  |     | kV/μs |

<sup>(1)</sup> For the 5-V operation,  $V_{CC1}$  or  $V_{CC2}$  is specified from 4.5 V to 5.5 V. For the 3-V operation,  $V_{CC1}$  or  $V_{CC2}$  is specified from 3 V to 3.6 V.

## SWITCHING CHARACTERISTICS: V<sub>CC1</sub> at 5 V, V<sub>CC2</sub> at 3.3 V OPERATION

over recommended operating conditions (unless otherwise noted)

|                     | PARAMETER                                          | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|---------------------|----------------------------------------------------|-----------------|-----|-----|-----|------|

| $t_{pLH}, t_{pHL}$  | Propagation delay                                  |                 | 24  | 36  | 49  | ns   |

| PWD                 | Pulse-width distortion $ t_{pHL} - t_{pLH} ^{(1)}$ |                 |     | 1   | 2   | ns   |

| t <sub>sk(pp)</sub> | Part-to-part skew (2)                              |                 |     |     | 10  | ns   |

| t <sub>sk(o)</sub>  | Channel-to-channel output skew (3)                 |                 |     | 0.2 | 10  | ns   |

| t <sub>r</sub>      | Output signal rise time                            | See Figure 1    |     | 2   |     | ns   |

| t <sub>f</sub>      | Output signal fall time                            | See Figure 1    |     | 2   |     | ns   |

| t <sub>fs</sub>     | Failsafe output delay time from input power loss   | See Figure 2    |     | 3   |     | μs   |

<sup>(1)</sup> Also referred to as pulse skew.

# ELECTRICAL CHARACTERISTICS: $V_{CC1}$ at 3.3 V, $V_{CC2}$ at 5 V<sup>(1)</sup> OPERATION

over recommended operating conditions (unless otherwise noted)

|                  | PARAMETER                          |  | TEST CONDITIONS                                       | MIN                   | TYP | MAX | UNIT     |

|------------------|------------------------------------|--|-------------------------------------------------------|-----------------------|-----|-----|----------|

| SUPPLY           | CURRENT                            |  |                                                       |                       |     |     |          |

| I <sub>CC1</sub> | 25 Mbps                            |  | V <sub>I</sub> = V <sub>CC</sub> or 0 V, no load      |                       | 6   | 12  | mA       |

| I <sub>CC2</sub> | 25 Mbps                            |  | V <sub>I</sub> = V <sub>CC</sub> or 0 V, no load      |                       | 12  | 22  | mA       |

| V                |                                    |  | I <sub>OH</sub> = -4 mA, See Figure 1                 | V <sub>CC</sub> - 0.4 |     |     | <b>V</b> |

| V <sub>OH</sub>  | High-level output voltage          |  | I <sub>OH</sub> = -20 μA, See Figure 1                | V <sub>CC</sub> - 0.1 |     |     | V        |

|                  |                                    |  | IOL = 4 mA, See Figure 1                              |                       |     | 0.4 |          |

| V <sub>OL</sub>  | Low-level output voltage           |  | IOL = 20 μA, See Figure 1                             |                       | 0   | 0.1 |          |

| $V_{I(HYS)}$     | Input threshold voltage hysteresis |  |                                                       |                       | 150 |     | mV       |

| I <sub>IH</sub>  | High-level input current           |  | IN from 0 V or V <sub>CC</sub>                        |                       |     | 11  | μΑ       |

| I <sub>IL</sub>  | Low-level input current            |  | IN from 0 V or V <sub>CC</sub>                        | -11                   |     |     | μΑ       |

| Cı               | Input capacitance to ground        |  | IN at $V_{CC}$ , $V_I = 0.4 \sin (4E6\pi t)$          |                       | 1   |     | pF       |

| CMTI             | Common-mode transient immunity     |  | V <sub>I</sub> = V <sub>CC</sub> or 0 V, See Figure 3 | 15                    | 40  |     | kV/µs    |

<sup>(1)</sup> For the 5-V operation, V<sub>CC1</sub> or V<sub>CC2</sub> is specified from 4.5 V to 5.5 V. For the 3-V operation, V<sub>CC1</sub> or V<sub>CC2</sub> is specified from 3 V to 3.6 V.

<sup>(2)</sup> t<sub>sk(pp)</sub> is the magnitude of the difference in propagation delay times between any specified terminals of two devices when both devices operate with the same supply voltages, at the same temperature, and have identical packages and test circuits.

<sup>(3)</sup> t<sub>sk(o)</sub> is the skew between specified outputs of a single device with all driving inputs connected together and the outputs switching in the same direction while driving identical specified loads.

## SWITCHING CHARACTERISTICS: V<sub>CC1</sub> at 3.3 V, V<sub>CC2</sub> at 5 V OPERTAION

over recommended operating conditions (unless otherwise noted)

|                                        | PARAMETER                                          | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|----------------------------------------|----------------------------------------------------|-----------------|-----|-----|-----|------|

| t <sub>pLH</sub> ,<br>t <sub>pHL</sub> | Propagation delay                                  |                 | 24  | 36  | 49  | ns   |

| PWD                                    | Pulse-width distortion $ t_{pHL} - t_{pLH} ^{(1)}$ |                 |     | 1   | 3   | ns   |

| t <sub>sk(pp)</sub>                    | Part-to-part skew (2)                              |                 |     |     | 10  | ns   |

| t <sub>sk(o)</sub>                     | Channel-to-channel output skew (3)                 |                 |     | 0.2 | 10  | ns   |

| t <sub>r</sub>                         | Output signal rise time                            | See Figure 4    |     | 1   |     |      |

| t <sub>f</sub>                         | Output signal fall time                            | See Figure 1    |     | 1   |     |      |

| t <sub>fs</sub>                        | Failsafe output delay time from input power loss   | See Figure 2    |     | 3   |     | μs   |

<sup>(1)</sup> Also referred to as pulse skew.

## ELECTRICAL CHARACTERISTICS: V<sub>CC1</sub> and V<sub>CC2</sub> at 3.3 V<sup>(1)</sup> OPERATION

over recommended operating conditions (unless otherwise noted)

|                  | PARAMETER                      | TEST CONDITIONS                                       | MIN                   | TYP | MAX | UNIT  |

|------------------|--------------------------------|-------------------------------------------------------|-----------------------|-----|-----|-------|

| SUPPL            | Y CURRENT                      |                                                       |                       |     |     |       |

| I <sub>CC1</sub> | 25 Mbps                        | V <sub>I</sub> = V <sub>CC</sub> or 0 V, no load      |                       | 6   | 12  | mA    |

| I <sub>CC2</sub> | 25 Mbps                        | V <sub>I</sub> = V <sub>CC</sub> or 0 V, no load      |                       | 6   | 12  | mA    |

| V                | High-level output voltage      | I <sub>OH</sub> = -4 mA, See Figure 1                 | V <sub>CC</sub> - 0.4 | 3   |     | V     |

| V <sub>OH</sub>  | nigri-level output voltage     | $I_{OH} = -20 \mu A$ , See Figure 1                   | V <sub>CC</sub> - 0.1 | 3.3 | .3  | V     |

| V                | Low lovel output voltage       | I <sub>OL</sub> = 4 mA, See Figure 1                  |                       | 0.2 | 0.4 | V     |

| V <sub>OL</sub>  | Low-level output voltage       | $I_{OL} = 20 \mu A$ , See Figure 1                    |                       | 0   | 0.1 | V     |

| $V_{I(HYS)}$     | Input voltage hysteresis       |                                                       |                       | 150 |     | mV    |

| I <sub>IH</sub>  | High-level input current       | IN from 0 V or V <sub>CC</sub>                        |                       |     | 11  | μA    |

| I <sub>IL</sub>  | Low-level input current        | IN from 0 V or V <sub>CC</sub>                        | -11                   |     |     |       |

| Cı               | Input capacitance to ground    | IN at $V_{CC}$ , $V_{I} = 0.4 \sin (4E6\pi t)$        |                       | 1   |     | pF    |

| CMTI             | Common-mode transient immunity | V <sub>I</sub> = V <sub>CC</sub> or 0 V, See Figure 3 | 15                    | 40  |     | kV/µs |

<sup>1)</sup> For the 5-V operation,  $V_{CC1}$  or  $V_{CC2}$  is specified from 4.5 V to 5.5 V. For the 3-V operation,  $V_{CC1}$  or  $V_{CC2}$  is specified from 3 V to 3.6 V.

## SWITCHING CHARACTERISTICS: $V_{CC1}$ and $V_{CC2}$ at 3.3 V

over recommended operating conditions (unless otherwise noted)

|                       | PARAMETER                                          | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-----------------------|----------------------------------------------------|-----------------|-----|-----|-----|------|

| $t_{pLH}$ , $t_{pHL}$ | Propagation delay                                  |                 | 25  | 40  | 53  | ns   |

| PWD                   | Pulse-width distortion $ t_{pHL} - t_{pLH} ^{(1)}$ |                 |     | 1   | 3   | ns   |

| t <sub>sk(pp)</sub>   | Part-to-part skew <sup>(2)</sup>                   |                 |     |     | 10  | ns   |

| t <sub>sk(o)</sub>    | Channel-to-channel output skew (3)                 |                 |     | 0.2 | 5   | ns   |

| t <sub>r</sub>        | Output signal rise time                            | See Figure 1    |     | 2   |     | ns   |

| t <sub>f</sub>        | Output signal fall time                            | See Figure 1    |     | 2   |     | ns   |

| t <sub>fs</sub>       | Failsafe output delay time from input power loss   | See Figure 2    |     | 3   |     | μs   |

<sup>(1)</sup> Also referred to as pulse skew.

<sup>(2)</sup> t<sub>sk(pp)</sub> is the magnitude of the difference in propagation delay times between any specified terminals of two devices when both devices operate with the same supply voltages, at the same temperature, and have identical packages and test circuits.

<sup>(3)</sup> t<sub>sk(o)</sub> is the skew between specified outputs of a single device with all driving inputs connected together and the outputs switching in the same direction while driving identical specified loads.

<sup>(2)</sup> t<sub>sk(pp)</sub> is the magnitude of the difference in propagation delay times between any specified terminals of two devices when both devices operate with the same supply voltages, at the same temperature, and have identical packages and test circuits.

<sup>(3)</sup> t<sub>sk(o)</sub> is the skew between specified outputs of a single device with all driving inputs connected together and the outputs switching in the same direction while driving identical specified loads.

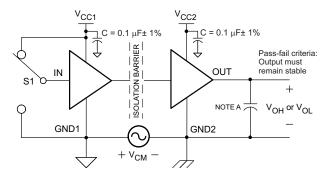

#### PARAMETER MEASUREMENT INFORMATION

- A. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  50 kHz, 50% duty cycle,  $t_r \leq$  3 ns,  $t_f \leq$  3 ns,  $Z_O = 50\Omega$ .

- B.  $C_L = 15$  pF and includes instrumentation and fixture capacitance within  $\pm 20\%$ .

Figure 1. Switching Characteristic Test Circuit and Voltage Waveforms

A.  $C_L = 15 \text{ pF}$  and includes instrumentation and fixture capacitance within  $\pm 20\%$ .

Figure 2. Failsafe Delay Time Test Circuit and Voltage Waveforms

A.  $C_L = 15 \text{ pF}$  and includes instrumentation and fixture capacitance within  $\pm 20\%$ .

Figure 3. Common-Mode Transient Immunity Test Circuit

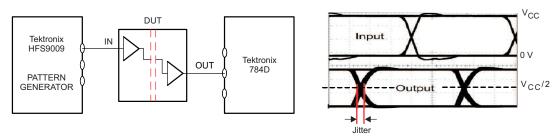

NOTE: PRBS bit pattern run length is  $2^{16} - 1$ . Transition time is 800 ps.

Figure 4. Peak-to-Peak Eye-Pattern Jitter Test Circuit and Voltage Waveform

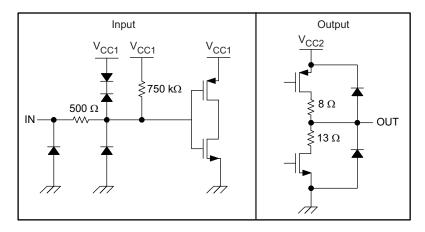

#### **DEVICE INFORMATION**

#### **DEVICE I/O SCHEMATICS**

#### **SOIC-8 PACKAGE THERMAL CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted)

|               | PARAMETER                            | TEST CONDITIONS                         | MIN | TYP  | MAX | UNIT   |

|---------------|--------------------------------------|-----------------------------------------|-----|------|-----|--------|

| $\theta_{JA}$ | Junction-to-air                      | Low-K Thermal Resistance <sup>(1)</sup> |     | 212  |     |        |

|               |                                      | High-K Thermal Resistance               |     | 122  |     | 00/14/ |

| $\theta_{JB}$ | Junction-to-Board Thermal Resistance |                                         |     | 37   |     | °C/W   |

| $\theta_{JC}$ | Junction-to-Case Thermal Resistance  |                                         |     | 69.1 |     | •      |

<sup>(1)</sup> Tested in accordance with the Low-K or High-K thermal metric definitions of EIA/JESD51-3 for leaded surface mount packages.

#### **DEVICE FUNCTION TABLE**

Table 1. Function Table<sup>(1)</sup>

| INPUT SIDE V <sub>CC</sub> | OUTPUT SIDE V <sub>CC</sub> | INPUT IN | OUTPUT OUT |  |  |

|----------------------------|-----------------------------|----------|------------|--|--|

|                            |                             | Н        | Н          |  |  |

| PU                         | PU                          | L        | L          |  |  |

|                            |                             | Open     | Н          |  |  |

| PD                         | PU                          | Х        | Н          |  |  |

<sup>(1)</sup> PU = Powered Up(Vcc  $\geq$  3.0V); PD = Powered Down (Vcc  $\leq$  2.5V); X = Irrelevant; H = High Level; L = Low Level

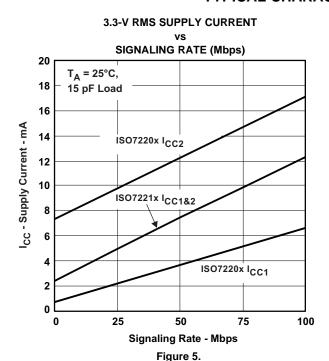

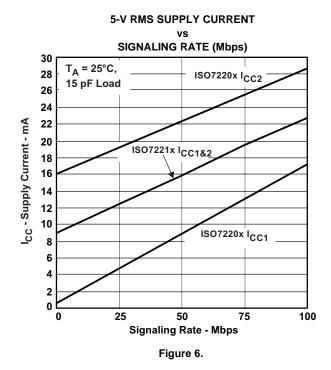

#### TYPICAL CHARACTERISTIC CURVES

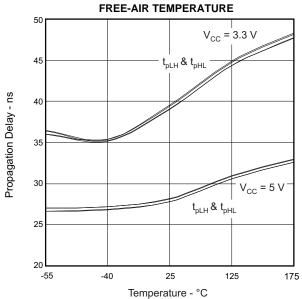

# PROPAGATION DELAY VS EDEE\_AID TEMPERATURE

Figure 7.

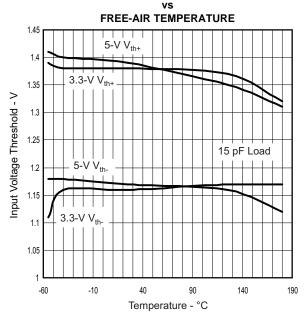

## INPUT VOLTAGE LOW-TO-HIGH SWITCHING THRESHOLD

Figure 8.

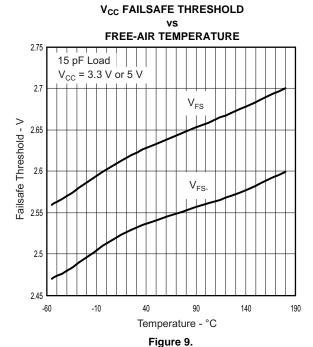

## **TYPICAL CHARACTERISTIC CURVES (continued)**

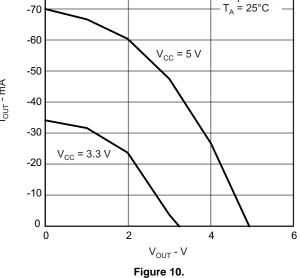

# HIGH-LEVEL OUTPUT VOLTAGE -80 15 pF Load - T<sub>A</sub> = 25°C -70 -60 $V_{CC} = 5 V$

HIGH-LEVEL OUTPUT CURRENT

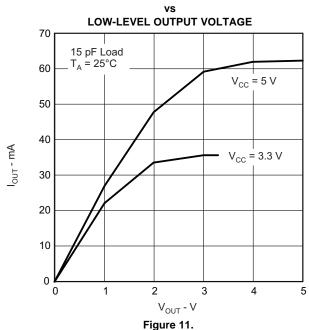

#### LOW-LEVEL OUTPUT CURRENT

Copyright © 2011–2012, Texas Instruments Incorporated

## **APPLICATION INFORMATION**

Figure 12. Typical ISO7221 Application Circuit

#### ISOLATION GLOSSARY

**Creepage Distance** — The shortest path between two conductive input to output leads measured along the surface of the insulation. The shortest distance path is found around the end of the package body.

**Clearance** — The shortest distance between two conductive input to output leads measured through air (line of sight).

**Input-to Output Barrier Capacitance** — The total capacitance between all input terminals connected together, and all output terminals connected together.

**Input-to Output Barrier Resistance** — The total resistance between all input terminals connected together, and all output terminals connected together.

**Primary Circuit** — An internal circuit directly connected to an external supply mains or other equivalent source which supplies the primary circuit electric power.

**Secondary Circuit** — A circuit with no direct connection to primary power, and derives its power from a separate isolated source.

Comparative Tracking Index (CTI) — CTI is an index used for electrical insulating materials which is defined as the numerical value of the voltage which causes failure by tracking during standard testing. Tracking is the process that produces a partially conducting path of localized deterioration on or through the surface of an insulating material as a result of the action of electric discharges on or close to an insulation surface -- the higher CTI value of the insulating material, the smaller the minimum creepage distance.

Generally, insulation breakdown occurs either through the material, over its surface, or both. Surface failure may arise from flashover or from the progressive degradation of the insulation surface by small localized sparks. Such sparks are the result of the breaking of a surface film of conducting contaminant on the insulation. The resulting break in the leakage current produces an overvoltage at the site of the discontinuity, and an electric spark is generated. These sparks often cause carbonization on insulation material and lead to a carbon track between points of different potential. This process is known as *tracking*.

#### Insulation:

Operational insulation — Insulation needed for the correct operation of the equipment.

Basic insulation — Insulation to provide basic protection against electric shock.

Supplementary insulation — Independent insulation applied in addition to basic insulation in order to ensure protection against electric shock in the event of a failure of the basic insulation.

Double insulation — Insulation comprising both basic and supplementary insulation.

Reinforced insulation — A single insulation system which provides a degree of protection against electric shock equivalent to double insulation.

#### **Pollution Degree:**

Pollution Degree 1 — No pollution, or only dry, nonconductive pollution occurs. The pollution has no influence.

Pollution Degree 2 — Normally, only nonconductive pollution occurs. However, a temporary conductivity caused by condensation must be expected.

Pollution Degree 3 — Conductive pollution occurs or dry nonconductive pollution occurs which becomes conductive due to condensation which is to be expected.

Pollution Degree 4 - Continuous conductivity occurs due to conductive dust, rain, or other wet conditions.

#### **Installation Category:**

Overvoltage Category — This section is directed at insulation co-ordination by identifying the transient overvoltages which may occur, and by assigning 4 different levels as indicated in IEC 60664.

- I: Signal Level Special equipment or parts of equipment.

- II: Local Level Portable equipment etc.

- III: Distribution Level Fixed installation

- IV: Primary Supply Level Overhead lines, cable systems

Each category should be subject to smaller transients than the category above.

## PACKAGE OPTION ADDENDUM

10-Dec-2020

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|----------------------|---------|

|                  |        |              |                    |      |                |              | (6)                           |                    |              |                      |         |

| ISO7221CHD       | ACTIVE | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -55 to 175   | I7221H               | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com 5-Jan-2022

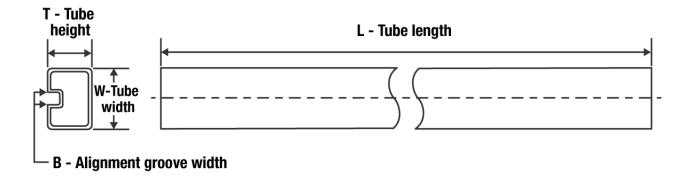

#### **TUBE**

#### \*All dimensions are nominal

| Device     | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| ISO7221CHD | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

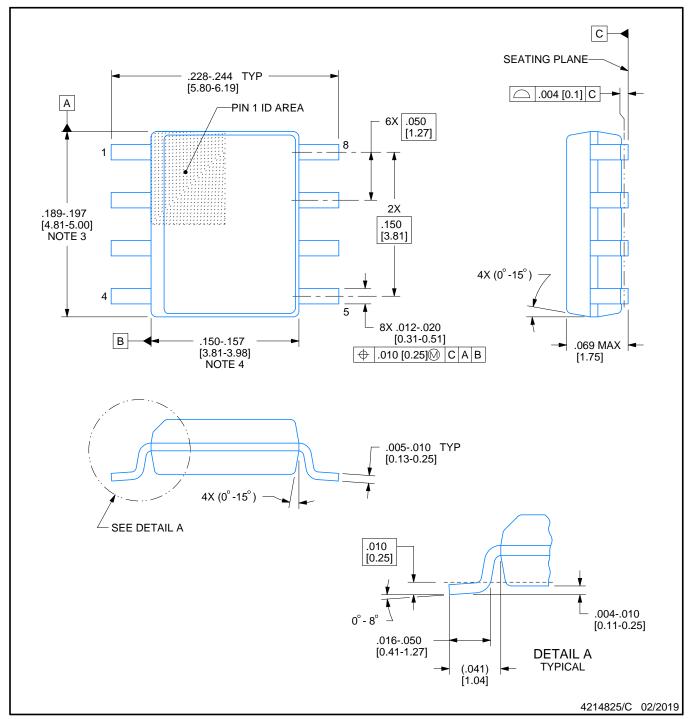

SMALL OUTLINE INTEGRATED CIRCUIT

#### NOTES:

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

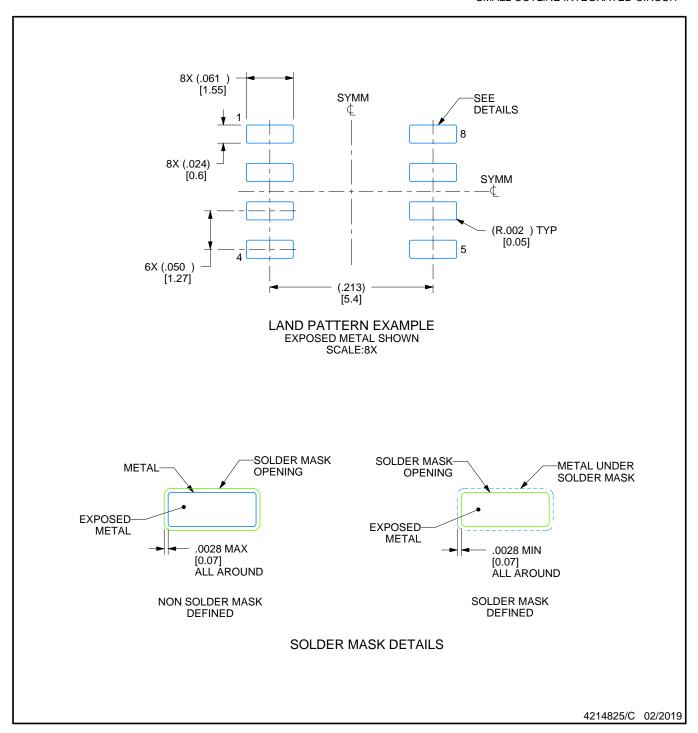

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

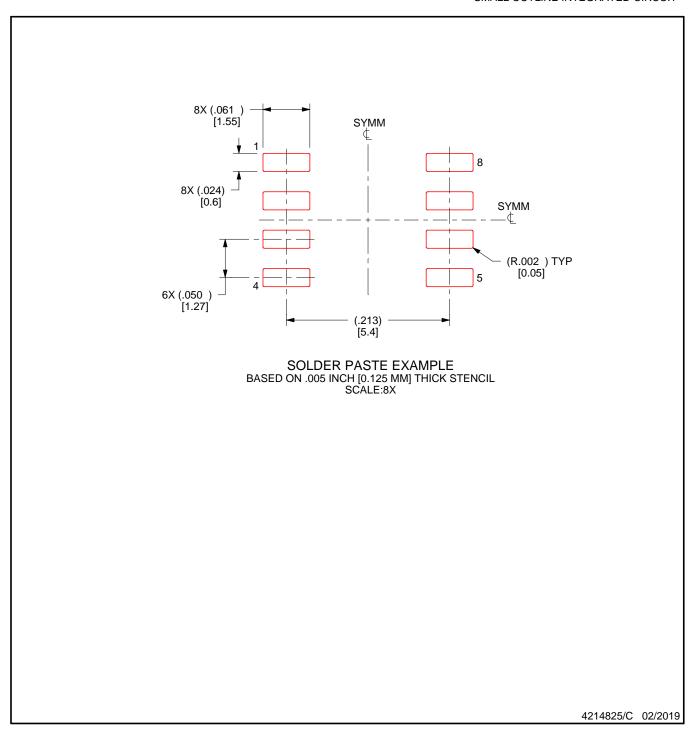

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

## 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022,德州仪器 (TI) 公司