**INA317**

ZHCSH47 - NOVEMBER 2017

# INA317 微功耗 (50µA)、零漂移、轨至轨输出仪表放大器

### 1 特性

- 低失调电压: **75µV**(最大值), **G≥100**

- 低温漂: 0.3µV/°C, G≥100

- 低噪声: 50nV/√Hz, G≥100

- 高共模抑制比 (CMRR): 100dB(最小值), G≥

10

- 低输入偏置电流: 200pA (最大值)

- 电源范围: 1.8V 至 5.5V

- 输入电压: (V-) 0.1V 至 (V+) -0.1V

- 电压范围: (V-) 0.05V 至 (V+) -0.05V

- 低静态电流: 50µA

- 工作温度范围: -40°C 至 +125°C

- 己过滤射频干扰 (RFI) 的输入

- 8 引脚 VSSOP 封装

#### 2 应用

- 桥式放大器

- 心电图 (ECG) 放大器

- 压力传感器

- 医疗仪表

- 便携式仪表

- 新器

- 热电偶放大器

- 电阻式温度检测器 (RTD) 传感器放大器

- 数据采集

#### 3 说明

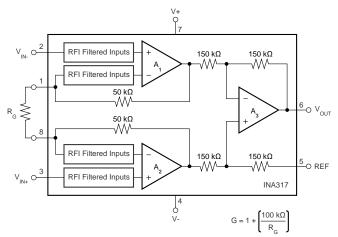

INA317 是一款具备出色精度的低功耗精密仪表放大器。INA317 采用 3 种多功能运算放大器设计,尺寸小巧,功耗较低,适用于各种便携式 应用。

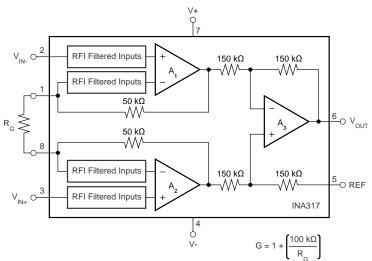

单个外部电阻器可根据行业标准增益等式 G=1+ (100  $k\Omega$  /  $R_G$ ) 的定义,设置 1 至 1000 范围内的任意增益。

该仪表放大器提供低失调电压( $75\mu$ V,G ≥ 100)、出色的失调电压漂移

(0.3  $\mu$ V/°C,G ≥ 100)和高共模抑制(G ≥ 10 时为 100dB)。INA317 采用低至 1.8V (±0.9V) 电压和 50 $\mu$ A 静态电流的电源供电,因而该器件适用于电池供电系统。INA317 器件采用自动校准技术确保广泛工业温度范围内的精度,可提供可扩展到直流的低噪声密度 (50 $\mu$ V/ $\mu$ Z)。

INA317 采用 8 引脚 VSSOP 表面贴装式封装,额定温度范围为  $T_A = -40^{\circ}\text{C}$  至  $+125^{\circ}\text{C}$ 。

#### 器件信息(1)

| HATTIA CO. |           |                 |  |  |  |  |  |  |  |

|------------|-----------|-----------------|--|--|--|--|--|--|--|

| 器件型号       | 封装        | 封装尺寸 (标称值)      |  |  |  |  |  |  |  |

| INA317     | VSSOP (8) | 3.00mm x 3.00mm |  |  |  |  |  |  |  |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

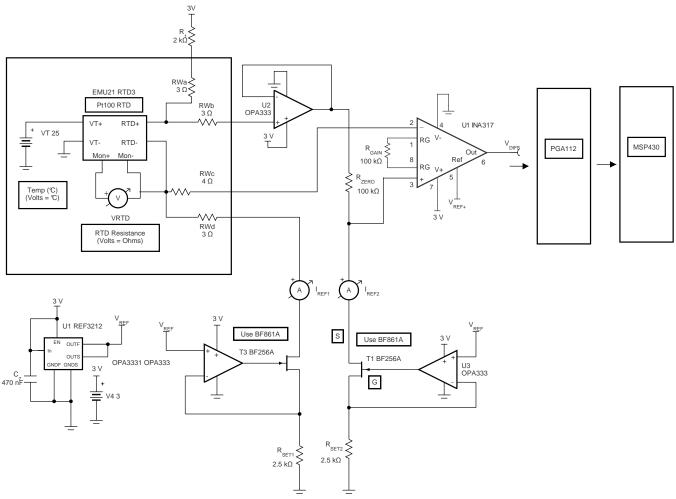

## 简化原理图

Copyright © 2017, Texas Instruments Incorporated

# 目录

| 1 | 特性1                                  | 7.4 Device Functional Modes      | 13              |

|---|--------------------------------------|----------------------------------|-----------------|

| 2 | 应用 1                                 | 8 Application and Implementation | 14              |

| 3 | 说明 1                                 | 8.1 Application Information      | 14              |

| 4 | 修订历史记录 2                             | 8.2 Typical Application          | 14              |

| 5 | Pin Configuration and Functions3     | 9 Power Supply Recommendations   | 19              |

| 6 | Specifications4                      | 10 Layout                        | 20              |

| • | 6.1 Absolute Maximum Ratings         | 10.1 Layout Guidelines           | 20              |

|   | 6.2 ESD Ratings                      | 10.2 Layout Example              | 21              |

|   | 6.3 Recommended Operating Conditions | <b>11</b> 器件和文档支持                | 22              |

|   | 6.4 Thermal Information 4            | 11.1 器件支持                        | <mark>22</mark> |

|   | 6.5 Electrical Characteristics       | 11.2 文档支持                        | 23              |

|   | 6.6 Typical Characteristics          | 11.3 商标                          |                 |

| 7 | Detailed Description                 | 11.4 静电放电警告                      | 24              |

|   | 7.1 Overview                         | 11.5 Glossary                    | 24              |

|   | 7.2 Functional Block Diagram         | <b>12</b> 机械、封装和可订购信息            | 25              |

|   | 7.3 Feature Description              |                                  |                 |

# 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| 日期       | 修订版本 | 说明    |

|----------|------|-------|

| 2017年11月 | *    | 初始发行版 |

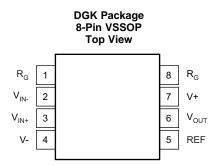

# **5 Pin Configuration and Functions**

### **Pin Functions**

| PIN                   |     | 1/0 | DESCRIPTION                                                                             |  |  |  |  |  |  |

|-----------------------|-----|-----|-----------------------------------------------------------------------------------------|--|--|--|--|--|--|

| NAME                  | NO. | 1/0 | DESCRIPTION                                                                             |  |  |  |  |  |  |

| REF                   | 5   | I   | Reference input. This pin must be driven by low impedance or connected to ground.       |  |  |  |  |  |  |

| R <sub>G</sub> 1, 8 — |     | _   | ain setting pins. For gains greater than 1, place a gain resistor between pins 1 and 8. |  |  |  |  |  |  |

| V <sub>+</sub>        | 7   | _   | Positive supply                                                                         |  |  |  |  |  |  |

| V_                    | 4   | _   | Negative supply                                                                         |  |  |  |  |  |  |

| $V_{IN+}$             | 3   | I   | Positive input                                                                          |  |  |  |  |  |  |

| $V_{IN-}$             | 2   | I   | Negative input                                                                          |  |  |  |  |  |  |

| V <sub>OUT</sub>      | 6   | 0   | Output                                                                                  |  |  |  |  |  |  |

#### 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                       | MIN      | MAX            | UNIT |

|---------------------------------------|----------|----------------|------|

| Supply voltage                        | 7        |                | V    |

| Analog input voltage (2)              | (V–) – ( | 0.3 (V+) + 0.3 | V    |

| Output short-circuit (3)              | C        | Continuous     |      |

| Operating temperature, T <sub>A</sub> | -40      | 150            | °C   |

| Junction temperature, T <sub>J</sub>  |          | 150            | °C   |

| Storage temperature, T <sub>stg</sub> | -65      | 150            | °C   |

- (1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) Input pins are diode-clamped to the power-supply rails. Input signals that can swing more than 0.3 V beyond the supply rails must be current limited to 10 mA or less.

- (3) Short-circuit to ground.

#### 6.2 ESD Ratings

|                                            |                                                                     | VALUE | UNIT |

|--------------------------------------------|---------------------------------------------------------------------|-------|------|

|                                            | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±4000 |      |

| V <sub>(ESD)</sub> Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±1000 | V    |

|                                            | Machine model (MM)                                                  | ±200  |      |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|    |                       | MIN | MAX | UNIT |

|----|-----------------------|-----|-----|------|

| VS | Supply voltage        | 1.8 | 5.5 | V    |

|    | Specified temperature | -40 | 125 | °C   |

#### 6.4 Thermal Information

|                      |                                              | INA317      |      |

|----------------------|----------------------------------------------|-------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | DGK (VSSOP) | UNIT |

|                      |                                              | 8 PINS      |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 169.5       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 62.7        | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 90.3        | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 7.6         | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 88.7        | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | _           | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.5 Electrical Characteristics

for  $V_S$  = 1.8 V to 5.5 V at  $T_A$  = 25°C,  $R_L$  = 10 k $\Omega$ ,  $V_{REF}$  =  $V_S$  / 2, and G = 1 (unless otherwise noted)

|                  | PARAMETER                                 | TEST CONDITIONS                                                                       | MIN        | TYP                        | MAX           | UNIT                   |

|------------------|-------------------------------------------|---------------------------------------------------------------------------------------|------------|----------------------------|---------------|------------------------|

| INPUT            |                                           |                                                                                       |            |                            |               |                        |

| V <sub>osi</sub> | Offset voltage, RTI <sup>(2)</sup>        |                                                                                       |            | ±10 ±25 / G                | ±75 ±75 / G   | μV                     |

|                  |                                           | vs temperature, T <sub>A</sub> = -40°C to 125°C                                       |            |                            | ±0.3 ±0.5 / G | μV/°C                  |

| PSR              |                                           | vs power supply,1.8 V $\leq$ V <sub>S</sub> $\leq$ 5.5 V                              |            | ±1 ±5 / G                  | ±5 ±15 / G    | μV/V                   |

|                  |                                           | Long-term stability                                                                   |            | See (3)                    |               |                        |

|                  | Turnon time to specified $V_{OSI}$        | $T_A = -40^{\circ}C \text{ to } 125^{\circ}C$                                         | See Typi   | ical Characteristi         | cs            |                        |

|                  | Impedance                                 |                                                                                       |            |                            |               |                        |

| Z <sub>IN</sub>  | Differential                              |                                                                                       |            | 100    3                   |               | $G\Omega \parallel pF$ |

| Z <sub>IN</sub>  | Common-mode                               |                                                                                       |            | 100    3                   |               | $G\Omega \mid\mid pF$  |

| $V_{CM}$         | Common-mode voltage range                 | V <sub>O</sub> = 0 V                                                                  | (V-) + 0.1 |                            | (V+) - 0.1    | V                      |

|                  |                                           | DC to 60 Hz                                                                           |            |                            |               |                        |

|                  |                                           | $V_{CM} = (V-) + 0.1 V$<br>to $(V+) - 0.1 V$ , $G = 1$                                | 80         | 90                         |               | dB                     |

| CMR              | Common-mode rejection                     | $V_{CM} = (V-) + 0.1 V$<br>to $(V+) - 0.1 V$ , $G = 10$                               | 100        | 110                        |               | dB                     |

|                  |                                           | V <sub>CM</sub> = (V-) + 0.1 V<br>to (V+) - 0.1 V, G = 100,                           | 100        | 115                        |               | dB                     |

|                  |                                           | V <sub>CM</sub> = (V-) + 0.1 V<br>to (V+) - 0.1 V, G = 1000                           | 100        | 115                        |               | dB                     |

| INPUT            | BIAS CURRENT                              |                                                                                       |            |                            |               |                        |

| I <sub>B</sub>   | Input bias current                        |                                                                                       |            | ±70                        | ±200          | pA                     |

| 'В               | vs temperature                            | $T_A = -40$ °C to 125°C                                                               | ;          | See 图 26                   |               | pA/°C                  |

| 1                | Input offset current                      |                                                                                       | ±50        |                            | ±200          | pA                     |

| I <sub>OS</sub>  | vs temperature                            | $T_A = -40^{\circ}\text{C to } 125^{\circ}\text{C}$                                   | ;          | See 图 28                   |               | pA/°C                  |

| INPUT            | VOLTAGE NOISE                             |                                                                                       |            |                            |               |                        |

| e <sub>NI</sub>  |                                           | G = 100, $R_S = 0 \Omega$ , $f = 10 Hz$                                               |            | 50                         |               | nV/√ <del>Hz</del>     |

|                  | Input valtage paige                       | G = 100, $R_S = 0 \Omega$ , $f = 100 Hz$                                              | 50         |                            |               | nV/√ <del>Hz</del>     |

|                  | Input voltage noise                       | G = 100, $R_S = 0 \Omega$ , $f = 1 \text{ kHz}$                                       |            | 50                         |               | nV/√ <del>Hz</del>     |

|                  |                                           | G = 100, $R_S = 0 \Omega$ , $f = 0.1 Hz$ to 10 Hz                                     |            | 1                          |               | $\mu V_{PP}$           |

|                  | Input current noise                       | f = 10 Hz                                                                             |            | 100                        |               | fA/√ <del>Hz</del>     |

| I <sub>N</sub>   | Input current noise                       | f = 0.1 Hz to 10 Hz                                                                   |            | 2                          |               | pA <sub>PP</sub>       |

| GAIN             |                                           |                                                                                       |            |                            |               |                        |

| G                | Gain equation                             |                                                                                       | 1+         | (100 kΩ / R <sub>G</sub> ) |               | V/V                    |

|                  | Range of gain                             |                                                                                       | 1          |                            | 1000          | V/V                    |

|                  |                                           | $V_S = 5.5 \text{ V}, (V-) + 100 \text{ mV}$<br>$\leq V_O \leq (V+) - 100 \text{ mV}$ |            |                            |               |                        |

|                  |                                           | G = 1                                                                                 |            | ±0.01%                     | ±0.1%         |                        |

|                  | Gain error                                | G = 10                                                                                |            | ±0.05%                     | ±0.25%        |                        |

|                  |                                           | G = 100                                                                               |            | ±0.07%                     | ±0.25%        |                        |

|                  |                                           | G = 1000                                                                              |            | ±0.25%                     | ±0.5%         |                        |

|                  | Gain vs temperature, G = 1                | $T_A = -40$ °C to 125°C                                                               |            | ±1                         | ±5            | ppm/°C                 |

|                  | Gain vs temperature, G > 1 <sup>(4)</sup> | $T_A = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}$                           |            | ±15                        | ±50           | ppm/°C                 |

|                  | Gain nonlinearity                         | $V_S = 5.5 \text{ V}, (V-) + 100 \text{ mV}$<br>$\leq V_O \leq (V+) - 100 \text{ mV}$ |            |                            |               |                        |

|                  | Gain nonlinearity, G = 1 to 1000          | $R_L = 10 \text{ k}\Omega$                                                            |            | 10                         |               | ppm                    |

| OUTP             | **                                        | <u> </u>                                                                              |            |                            |               |                        |

|                  | Output voltage swing from rail            | $V_S = 5.5 \text{ V}$ $R_L = 10 \text{ k}\Omega$                                      |            | See 图 29                   | 50            | mV                     |

|                  | Capacitive load drive                     | -                                                                                     |            | 500                        |               | pF                     |

<sup>(1)</sup> Total  $V_{OS}$ , referred-to-input =  $(V_{OSI})$  +  $(V_{OSO} / G)$ (2) RTI = Referred-to-input

<sup>300-</sup>hour life test at 150°C demonstrated randomly distributed variation of approximately 1  $\mu V$

<sup>(4)</sup> Does not include effects of external resistor R<sub>G</sub>

# **Electrical Characteristics (continued)**

for  $V_S$  = 1.8 V to 5.5 V at  $T_A$  = 25°C,  $R_L$  = 10 k $\Omega$ ,  $V_{REF}$  =  $V_S$  / 2, and G = 1 (unless otherwise noted)

|                | PARAMETER                        | TEST CONDITIONS                                          | MIN  | TYP    | MAX   | UNIT |

|----------------|----------------------------------|----------------------------------------------------------|------|--------|-------|------|

| $I_{SC}$       | Short-circuit current            | Continuous to common                                     |      | -40, 5 |       | mA   |

| FREG           | QUENCY RESPONSE                  |                                                          |      |        |       |      |

|                |                                  | G = 1                                                    |      | 150    |       | kHz  |

|                | Donatuidth 2 dD                  | G = 10                                                   |      | 35     |       | kHz  |

|                | Bandwidth, -3 dB                 | G = 100                                                  |      | 3.5    |       | kHz  |

|                |                                  | G = 1000                                                 |      | 350    |       | Hz   |

| SR             | Slew rate                        | V <sub>S</sub> = 5 V, V <sub>O</sub> = 4-V step, G = 1   |      | 0.16   |       | V/µs |

| SK             | Siew rate                        | V <sub>S</sub> = 5 V, V <sub>O</sub> = 4-V step, G = 100 |      | 0.05   |       | V/μs |

|                | Sottling time to 0.049/          | V <sub>STEP</sub> = 4 V, G = 1                           |      | 50     |       | μS   |

| t <sub>S</sub> | Settling time to 0.01%           | V <sub>STEP</sub> = 4 V, G = 100                         |      | 400    |       | μS   |

|                | Sottling time to 0.0019/         | V <sub>STEP</sub> = 4 V, G = 1                           |      | 60     |       | μS   |

| ts             | Settling time to 0.001%          | V <sub>STEP</sub> = 4 V, G = 100                         |      | 500    |       | μS   |

|                | Overload recovery                | 50% overdrive                                            |      | 75     |       | μS   |

| REFE           | RENCE INPUT                      |                                                          |      |        |       |      |

|                | R <sub>IN</sub>                  |                                                          |      | 300    |       | kΩ   |

|                | Voltage range                    |                                                          | V–   |        | V+    | V    |

| POW            | ER SUPPLY                        |                                                          |      |        |       |      |

|                | Voltogo rongo                    | Single voltage range                                     | 1.8  |        | 5.5   | V    |

|                | Voltage range                    | Dual voltage range                                       | ±0.9 |        | ±2.75 | V    |

|                | Outcoont ourrent ve temperature  | $V_{IN} = V_S / 2$                                       |      | 50     | 75    | μΑ   |

| ΙQ             | Quiescent current vs temperature | T <sub>A</sub> = -40°C to 125°C                          |      |        | 80    | μА   |

| TEMI           | PERATURE RANGE                   |                                                          |      |        | •     |      |

|                | Specified temperature range      |                                                          | -40  |        | 125   | °C   |

|                | Operating temperature range      |                                                          | -40  |        | 150   | °C   |

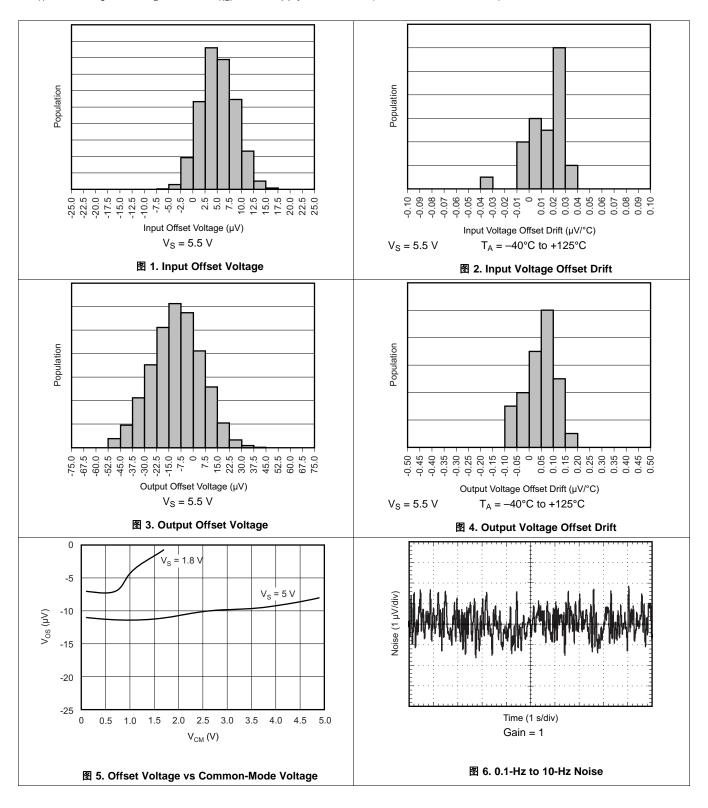

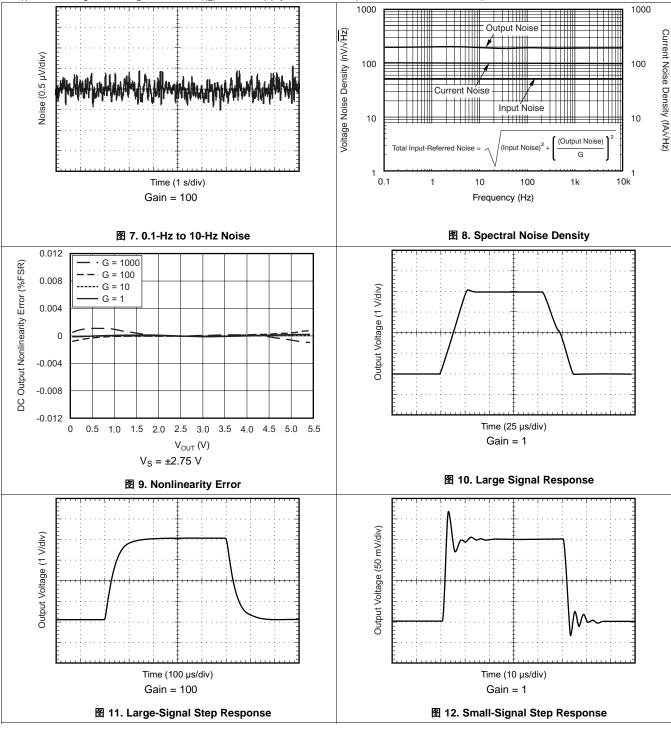

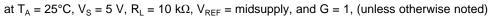

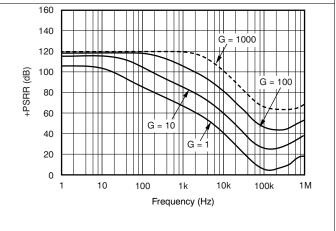

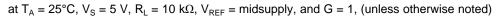

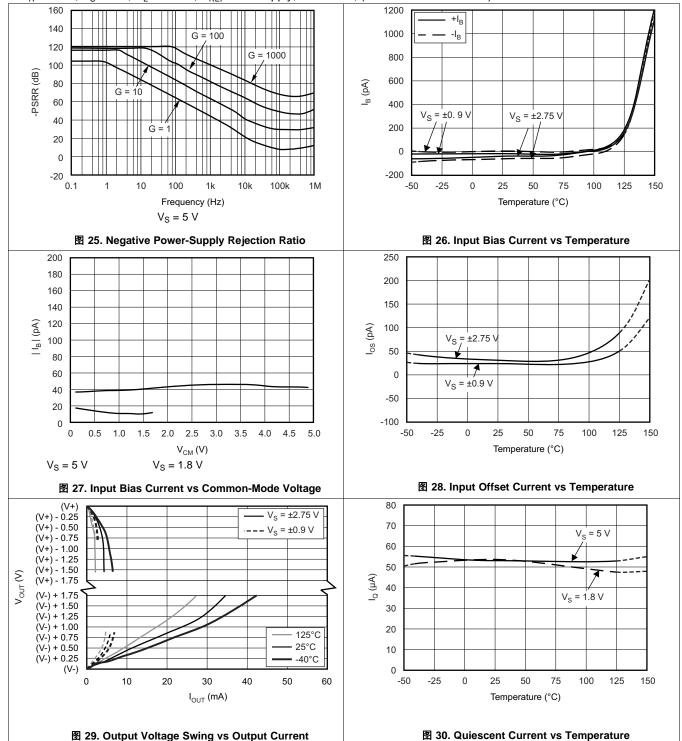

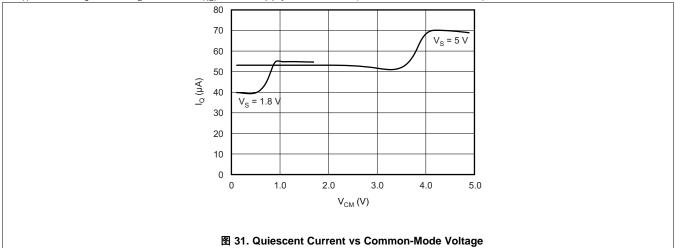

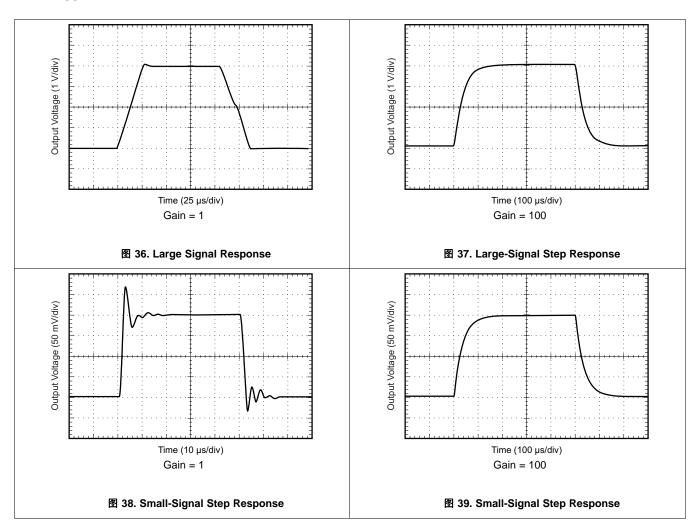

## 6.6 Typical Characteristics

at  $T_A = 25$ °C,  $V_S = 5$  V,  $R_L = 10$  k $\Omega$ ,  $V_{REF} =$  midsupply, and G = 1, (unless otherwise noted)

## Typical Characteristics (接下页)

at  $T_A = 25$ °C,  $V_S = 5$  V,  $R_L = 10$  k $\Omega$ ,  $V_{REF} =$  midsupply, and G = 1, (unless otherwise noted)

# Typical Characteristics (接下页)

### Typical Characteristics (接下页)

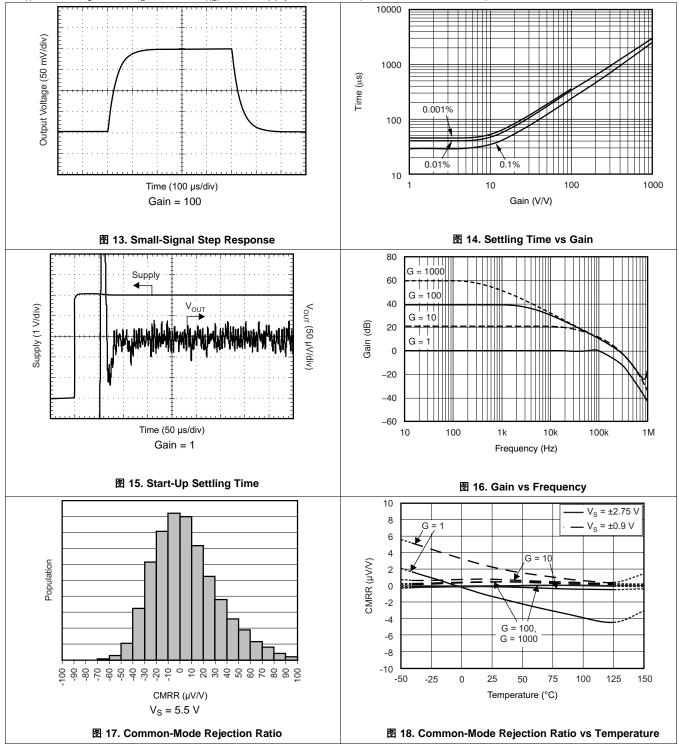

at  $T_A = 25$ °C,  $V_S = 5$  V,  $R_L = 10$  k $\Omega$ ,  $V_{REF} =$  midsupply, and G = 1, (unless otherwise noted)

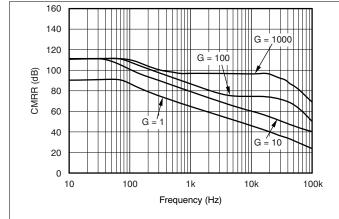

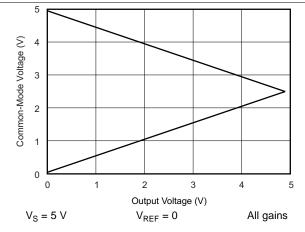

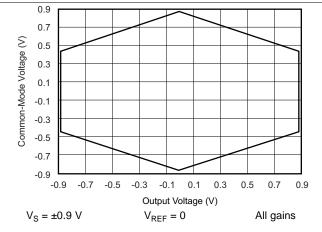

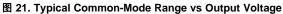

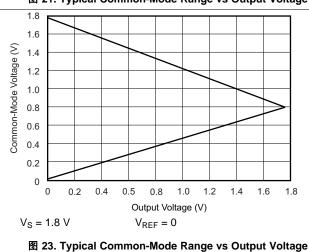

图 19. Common-Mode Rejection Ratio vs Frequency

图 20. Typical Common-Mode Range vs Output Voltage

图 22. Typical Common-Mode Range vs Output Voltage

图 24. Positive Power-Supply Rejection Ratio

# Typical Characteristics (接下页)

# Typical Characteristics (接下页)

at  $T_A$  = 25°C,  $V_S$  = 5 V,  $R_L$  = 10 k $\Omega$ ,  $V_{REF}$  = midsupply, and G = 1, (unless otherwise noted)

## 7 Detailed Description

#### 7.1 Overview

www.ti.com.cn

The INA317 is a monolithic instrumentation amplifier (INA) based on the precision zero-drift OPA333 (operational amplifier) core. The INA317 integrates laser-trimmed resistors to ensure excellent common-mode rejection and low gain error. The combination of the zero-drift amplifier core and the precision resistors allows this device to achieve outstanding DC precision and is designed for 3.3-V and 5-V industrial applications.

#### 7.2 Functional Block Diagram

Copyright © 2017, Texas Instruments Incorporated

#### 7.3 Feature Description

The INA317 is a low-power, zero-drift instrumentation amplifier that offers accuracy. The versatile three-operational-amplifier design and small size makes the amplifier designed for a wide range of applications. Zero-drift chopper circuitry provides DC specifications. A single external resistor sets any gain from 1 to 10,000. The INA317 is laser trimmed for high common-mode rejection (100 dB at  $G \ge 100$ ). Typically, the INA317 operates with power supplies as low as 1.8 V and quiescent current of 50  $\mu$ A.

#### 7.4 Device Functional Modes

#### 7.4.1 Internal Offset Correction

INA317 internal operational amplifiers use an autocalibration technique with a time-continuous 350-kHz operational amplifier in the signal path. The amplifier is zero-corrected every 8 µs using a proprietary technique. Upon power up, the amplifier requires approximately 100 µs to achieve specified VOS accuracy. This design has no aliasing or flicker noise.

#### 7.4.2 Input Common-Mode Range

The linear input voltage range of the input circuitry of the INA317 is from approximately 0.1 V below the positive supply voltage to 0.1 V above the negative supply. However, as a differential input voltage causes the output voltage to increase, the output voltage swing of amplifiers A1 and A2 limits the linear input range. As a result, the linear common-mode input range is related to the output voltage of the complete amplifier. This behavior depends on supply voltage; see 20.

Input overload conditions can produce an output voltage that appears normal. For example, if an input overload condition drives the input amplifiers to the respective positive output swing limit, the difference voltage measured by the output amplifier is approximately zero. The output of the INA317 is approximately 0 V even though the inputs are overloaded.

#### 8 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

The INA317 measures small differential voltage with high common-mode voltage that develops between the noninverting and inverting input. The high input impedance makes the INA317 designed for a wide range of applications. The ability to set the reference pin to adjust the functionality of the output signal offers additional flexibility that is practical for multiple configurations.

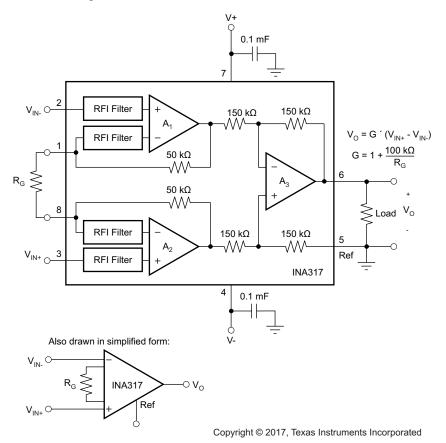

#### 8.2 Typical Application

The output of the INA317 device is referred to the output reference (REF) pin, which is normally grounded. This connection must be low-impedance to ensure good common-mode rejection. Although 15  $\Omega$  or less of stray resistance is tolerated while maintaining specified CMRR, small stray resistances of tens of ohms in series with the REF pin causes noticeable degradation in CMRR.

图 32. Basic Connections

ZHCSH47-NOVEMBER 2017 www.ti.com.cn

### Typical Application (接下页)

#### 8.2.1 Design Requirements

The device is configured to monitor the input differential voltage when the gain of the external resistor R<sub>G</sub> sets the input signal. The output signal references to the REF pin. The most common application is where the output is referenced to ground when no input signal is present by connecting the REF pin to ground. When the input signal increases, the output voltage at the OUT pin increases.

#### 8.2.2 Detailed Design Procedure

#### 8.2.2.1 Setting the Gain

A single external resistor (R<sub>G</sub>) that is connected between pins 1 and 8 sets the gain of the INA317. The value of  $R_G$  is selected according to  $\triangle$ 式 1:

$$G = 1 + (100 \text{ k}\Omega / \text{R}_G) \tag{1}$$

表 1 lists several commonly-used gains and resistor values. The 100 k $\Omega$  in 公式 1 is a result of the sum of the two internal feedback resistors (A<sub>1</sub> and A<sub>2</sub>.) These on-chip resistors are laser trimmed to accurate absolute values. The accuracy and temperature coefficient of these resistors are included in the gain accuracy and drift specifications of the INA317 device.

The stability and temperature drift of the external gain setting resistor (R<sub>G</sub>) also affects gain. The contribution of R<sub>G</sub> to gain accuracy and drift is inferred from the gain in公式 1. Low resistor values required for high gain make wiring resistance important. Sockets add to the wiring resistance and contribute additional gain error (possibly an unstable gain error) in gains of approximately 100 or greater. To ensure stability, avoid parasitic capacitance of more than a few picofarads at the R<sub>G</sub> connections. Careful matching of any parasitics on R<sub>G</sub> pins maintains optimal CMRR over frequency.

| DESIRED GAIN | R <sub>G</sub> (Ω) | NEAREST 1% R <sub>G</sub> ( $\Omega$ ) |

|--------------|--------------------|----------------------------------------|

| 1            | NC <sup>(1)</sup>  | NC                                     |

| 2            | 100 k              | 100 k                                  |

| 5            | 25 k               | 24.9 k                                 |

| 10           | 11.1 k             | 11 k                                   |

| 20           | 5.26 k             | 5.23 k                                 |

| 50           | 2.04 k             | 2.05                                   |

| 100          | 1.01 k             | 1 k                                    |

| 200          | 502.5              | 499                                    |

| 500          | 200.4              | 200                                    |

| 1000         | 100.1              | 100                                    |

表 1. Commonly-Used Gains and Resistor Values

#### 8.2.2.2 Internal Offset Correction

The INA317 device internal operational amplifiers use an autocalibration technique with a time-continuous 350kHz operational amplifier in the signal path. The amplifier is zero-corrected every 8 µs using a proprietary technique. At power-up, the amplifier requires approximately 100 µs to achieve specified Vos accuracy. This design has no aliasing or flicker noise.

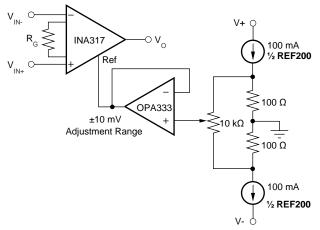

#### 8.2.2.3 Offset Trimming

Most applications require no external offset adjustment. However, apply a voltage to the REF pin to make adjustments if necessary.

33 shows an optional circuit for trimming the output offset voltage. The voltage applied to REF pin is added at the output. The operational amplifier buffer provides low impedance at the REF pin to preserve good common-mode rejection.

<sup>(1)</sup> NC denotes no connection. When using the SPICE model, the simulation does not converge unless a resistor is connected to the R<sub>G</sub> pins; use a large resistor value.

Copyright © 2017, Texas Instruments Incorporated

图 33. Optional Trimming of Output Offset Voltage

#### 8.2.2.4 Noise Performance

The autocalibration technique used by the INA317 device results in reduced low-frequency noise, typically only  $50 \text{ nV/}\sqrt{\text{Hz}}$  (G = 100). The spectral noise density is shown in  $\boxed{8}$  8. Low-frequency noise of the INA317 device is approximately 1  $\mu\text{V}_{PP}$  measured from 0.1 Hz to 10 Hz (G = 100).

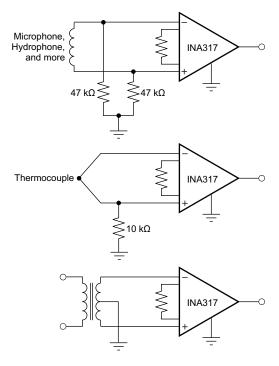

#### 8.2.2.5 Input Bias Current Return Path

The input impedance of the INA317 device is extremely high(approximately 100 G $\Omega$ .) However, a path must be provided for the input bias current of the inputs. This input bias current is typically  $\pm 70$  pA. High-input impedance means that this input bias current changes very little with varying input voltage.

For proper operation, input circuitry must provide a path for the input bias current. 34 shows various provisions for an input bias current path. Without a bias current path, the inputs float to a potential that exceeds the common-mode range of the INA317 device, and the input amplifiers saturate. If the differential source resistance is low, the bias current return path connects to one input (see the thermocouple example in 34). With higher source impedance, using two equal resistors provides a balanced input with possible advantages of lower input offset voltage as a result of bias current and better high-frequency common-mode rejection.

Copyright © 2017, Texas Instruments Incorporated

图 34. Providing an Input Common-Mode Current Path

#### 8.2.2.6 Input Common-Mode Range

The linear input voltage range of the input circuitry of the INA317 device is from approximately 0.1 V below the positive supply voltage to 0.1 V above the negative supply. As a differential input voltage causes the output voltage to increase, however, the linear input range is limited by the output voltage swing of amplifiers  $A_1$  and  $A_2$ . The linear common-mode input range is related to the output voltage of the complete amplifier. This behavior depends on supply voltage(see 20 to 20 in the *Typical Characteristics* section.)

Input overload conditions can produce an output voltage that appears normal. For example, if an input overload condition drives both input amplifiers to the respective positive output swing limit, the difference voltage measured by the output amplifier is near zero. The output of the INA317 is near 0 V even though both inputs are overloaded.

#### 8.2.2.7 Operating Voltage

The INA317 operates over a power-supply range of 1.8 V to 5.5 V ( $\pm 0.9$  V to  $\pm 2.75$  V). Supply voltages higher than 7 V (absolute maximum) can permanently damage the device. Parameters that vary over supply voltage or temperature are shown in the *Typical Characteristics* section of this data sheet.

#### 8.2.2.8 Low Voltage Operation

The INA317 device operates on power supplies as low as  $\pm 0.9$  V. Most parameters vary only slightly throughout this supply voltage range; see the *Typical Characteristics* section. Operation at very low supply voltage requires careful attention to ensure that the input voltages remain within the linear range. Voltage swing requirements of internal nodes limit the input common-mode range with low power supply voltage. 20 to 23 show the range of linear operation for various supply voltages and gains.

#### 8.2.2.9 Single-Supply Operation

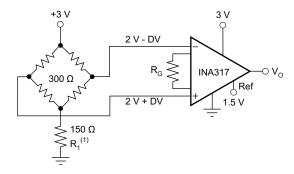

The INA317 device can be used on single power supplies of 1.8 V to 5.5 V. ☑ 35 shows a basic single-supply circuit. The output REF pin is connected to midsupply. Zero differential input voltage demands an output voltage of midsupply. Actual output voltage swing is limited to approximately 50 mV more than ground when the load is referred to ground as shown. ☑ 29 shows how the output voltage swing varies with output current.

With single-supply operation,  $V_{IN+}$  and  $V_{IN-}$  must be 0.1 V more than ground for linear operation. For instance, the inverting input cannot connect to ground to measure a voltage that is connected to the noninverting input.

To show the issues affecting low voltage operation, see 图 35. 图 35 shows the INA317 device operating from a single 3-V supply. A resistor in series with the low side of the bridge ensures that the bridge output voltage is within the common-mode range of the amplifier inputs.

Copyright © 2017, Texas Instruments Incorporated

(1) R<sub>1</sub> creates proper common-mode voltage only for low-voltage operation; see Single-Supply Operation.

#### 图 35. Single-Supply Bridge Amplifier

#### 8.2.2.10 Input Protection

The input pins of the INA317 device are protected with internal diodes that are connected to the power-supply rails. These diodes clamp the applied signal to prevent the signal from damaging the input circuitry. If the input signal voltage exceeds the power supplies by more than 0.3 V, the input signal current must be limited to less than 10 mA to protect the internal clamp diodes. Limit the current with a series input resistor. Some signal sources are inherently current limited and do not require limiting resistors.

#### 8.2.3 Application Curves

# 9 Power Supply Recommendations

The minimum power supply voltage for INA317 is 1.8 V and the maximum power supply voltage is 5.5 V. For optimum performance, 3.3 V to 5 V is recommended. TI recommends adding a bypass capacitor at the input to compensate for the layout and power supply source impedance.

#### 10 Layout

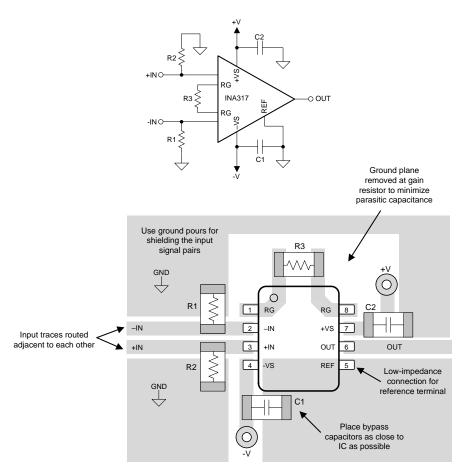

#### 10.1 Layout Guidelines

TI recommends paying attention to good layout practices. Keep traces short and use a printed-circuit-board (PCB) ground plane with surface-mount components placed as close to the device pins as possible. Place a 0.1-µF bypass capacitor as close as possible the supply pins. Apply these guidelines throughout the analog circuit to improve performance and reduce electromagnetic interference (EMI) susceptibility.

Instrumentation amplifiers vary in the susceptibility to radio-frequency interference (RFI). RFI is identified as a variation in offset voltage or DC signal levels with changes in the interfering RF signal. The INA317 device is designed to minimize susceptibility to RFI by incorporating passive RC filters with an 8-MHz corner frequency at the  $V_{\text{IN+}}$  and  $V_{\text{IN-}}$  inputs. As a result, the INA317 device demonstrates low sensitivity compared to previous generation devices. However, strong RF fields can cause varied offset levels and may require additional shielding.

### 10.2 Layout Example

Copyright © 2017, Texas Instruments Incorporated

图 40. INA317 Layout

#### 11 器件和文档支持

#### 11.1 器件支持

#### 11.1.1 开发支持

#### 11.1.1.1 TINA-TI (免费下载软件)

#### 针对 INA317 使用基于 SPICE 的 TINA-TI 模拟仿真程序

TINA 是一款简单、功能强大且易于使用的电路仿真程序,此程序基于 SPICE 引擎。TINA-TI 是 TINA 软件的一款免费全功能版本,除了一系列无源和有源模型外,此版本软件还预先载入了一个宏模型库。它提供所有传统的 SPICE 直流 (DC)、瞬态和频域分析以及其他设计功能。

TINA-TI 可从 Analog eLab Design Center (模拟电子实验室设计中心) 免费下载,它提供全面的后续处理能力,使得用户能够以多种方式形成结果。

虚拟仪器为用户提供选择输入波形和探测电路节点、电压和波形的功能,从而创建一个动态的快速入门工具。

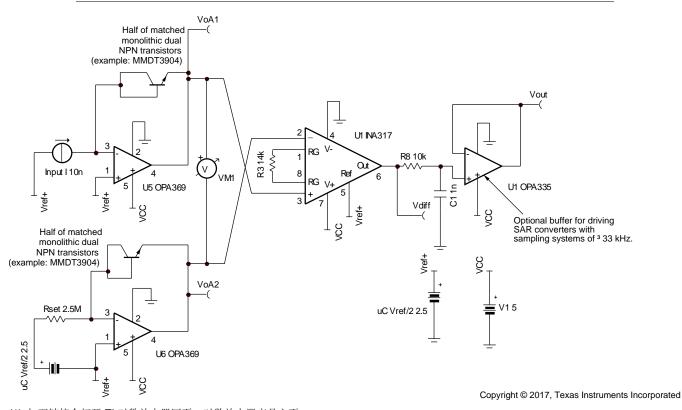

图 41 和图 42 给出了适用于 INA317 器件的 TINA-TI 电路示例,可用于开发、修改和评估特定 应用的电路设计。。下面给出了这些仿真文件的下载链接。

注 必须安装 TINA 软件(从 DesignSoft) 或者 TINA-TI 软件后才能使用这些文件。请从 TINA-TI 文件夹中下载免费的 TINA-TI 软件。

- (1) 如下链接会打开 TI 对数放大器网页: 对数放大器产品主页

- (2) 未显示对数晶体管的温度补偿。

- (3) 对于单片对数放大器(例如 LOG112 或 LOG114),请参阅注 1 中的链接。

图 41. 便携式电池供电类系统的低功耗对数函数电路 (例如血糖仪)

要下载包含此电路 TINA-TI 仿真文件的压缩文件,请点击如下链接:对数电路。

## 器件支持 (接下页)

Copyright © 2017, Texas Instruments Incorporated

RWa、RWb、RWc 和 RWd 用于仿真线电阻。包含这些电阻以展示 4 线感应技术对线路失配的抗扰性。这种方法假定使用 4 线 RTD。

#### 图 42. 带有可编程增益采集系统的适用于 PT100 RTD 的 4 线、3V 调节器

要下载包含此电路 TINA-TI 仿真文件的压缩文件,请点击如下链接: PT100 RTD。

#### 11.2 文档支持

#### 11.2.1 相关文档

请参阅如下相关文档:

- 精密、低噪声、轨至轨输出,36V,零漂移运算放大器

- 50µV VOS、0.25µV/℃、35µA CMOS 运算放大器零漂移系列

- 4ppm/℃、100µA、SOT23-6 系列电压基准

- 《电路板布局布线技巧》

## 11.3 商标

All trademarks are the property of their respective owners.

# 11.4 静电放电警告

这些装置包含有限的内置 ESD 保护。 存储或装卸时,应将导线一起截短或将装置放置于导电泡棉中,以防止 MOS 门极遭受静电损伤。

# 11.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

# 12 机械、封装和可订购信息

以下页面包含机械、封装和可订购信息。这些信息是指定器件的最新可用数据。数据如有变更,恕不另行通知和修订此文档。如欲获取此产品说明书的浏览器版本,请参阅左侧的导航。

### PACKAGE OPTION ADDENDUM

10-Dec-2020

#### PACKAGING INFORMATION

www.ti.com

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| INA317IDGKR      | ACTIVE | VSSOP        | DGK                | 8    | 2500           | RoHS & Green | NIPDAUAG                      | Level-2-260C-1 YEAR | -40 to 125   | l317                    | Samples |

| INA317IDGKT      | ACTIVE | VSSOP        | DGK                | 8    | 250            | RoHS & Green | NIPDAUAG                      | Level-2-260C-1 YEAR | -40 to 125   | l317                    | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

10-Dec-2020

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 17-Jul-2020

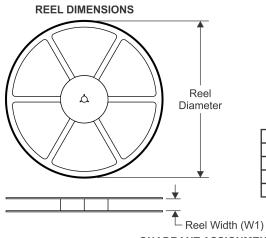

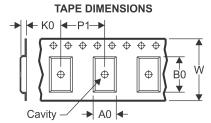

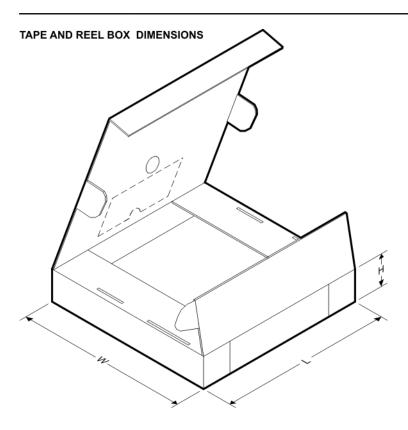

### TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

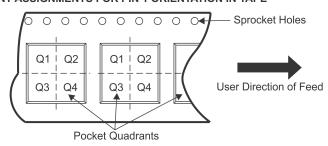

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| INA317IDGKR | VSSOP           | DGK                | 8 | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| INA317IDGKT | VSSOP           | DGK                | 8 | 250  | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

www.ti.com 17-Jul-2020

#### \*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| INA317IDGKR | VSSOP        | DGK             | 8    | 2500 | 366.0       | 364.0      | 50.0        |  |

| INA317IDGKT | VSSOP        | DGK             | 8    | 250  | 366.0       | 364.0      | 50.0        |  |

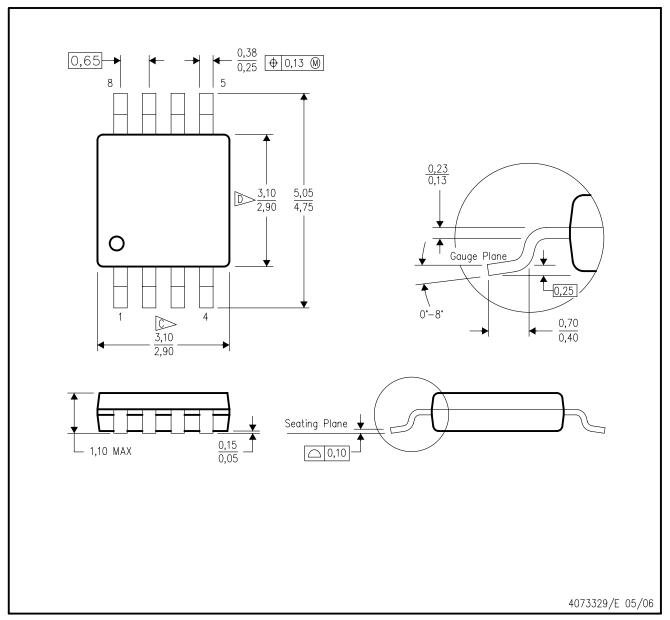

# DGK (S-PDSO-G8)

# PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 per end.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.50 per side.

- E. Falls within JEDEC MO-187 variation AA, except interlead flash.

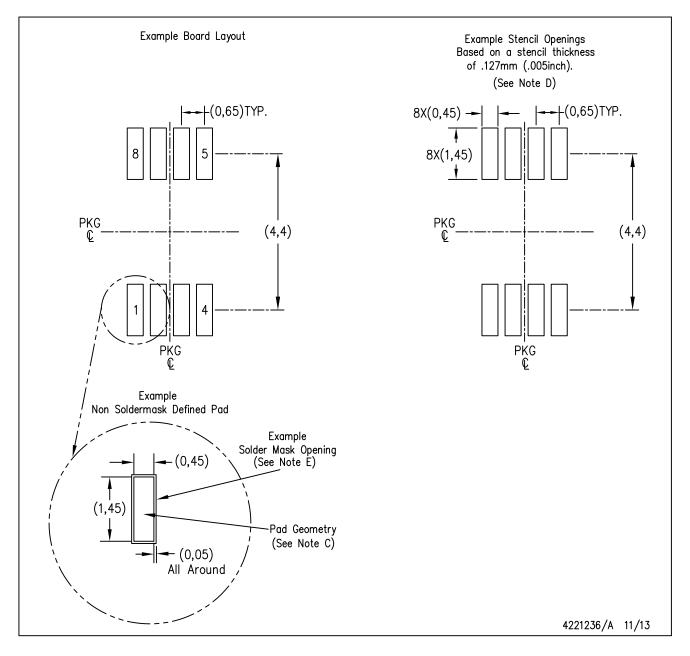

# DGK (S-PDSO-G8)

# PLASTIC SMALL OUTLINE PACKAGE

#### NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

#### 重要声明和免责声明

TI 均以"原样"提供技术性及可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证其中不含任何瑕疵,且不做任何明示或暗示的担保,包括但不限于对适销性、适合某特定用途或不侵犯任何第三方知识产权的暗示担保。

所述资源可供专业开发人员应用TI产品进行设计使用。您将对以下行为独自承担全部责任: (1)针对您的应用选择合适的TI产品; (2)设计、验证并测试您的应用; (3)确保您的应用满足相应标准以及任何其他安全、安保或其他要求。所述资源如有变更,恕不另行通知。TI对您使用所述资源的授权仅限于开发资源所涉及TI产品的相关应用。除此之外不得复制或展示所述资源,也不提供其它TI或任何第三方的知识产权授权许可。如因使用所述资源而产生任何索赔、赔偿、成本、损失及债务等,TI对此概不负责,并且您须赔偿由此对TI及其代表造成的损害。

TI 所提供产品均受TI 的销售条款 (http://www.ti.com.cn/zh-cn/legal/termsofsale.html) 以及ti.com.cn上或随附TI产品提供的其他可适用条款的约束。TI提供所述资源并不扩展或以其他方式更改TI 针对TI 产品所发布的可适用的担保范围或担保免责声明。

邮寄地址: 上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2020 德州仪器半导体技术(上海)有限公司