# 1.5MHz, 600mA Synchronous Step-Down Regulator in SOT

## **General Description**

The WD1012EA is a high efficiency monolithic synchronous buck regulator using a constant frequency, current mode architecture. The 2.7V to 5.5V input voltage range makes the WD1012EA ideally suited for single Li-lon battery-powered applications. Supply current with no load is  $22\mu$ A, dropping to <1 $\mu$ A in shutdown. PWM (Pulse Width Modulation) operation provides very low output ripple voltage for noise sensitive applications. 100% duty cycle capability provides low dropout operation, extending battery life in portable systems.

The switching frequency is internally set at 1.5MHz, allowing the use of tiny surface mount inductors and capacitors. Low output voltages are easily supported with the 0.6V feedback reference voltage. The WD1012EA is available in SOT23 package. The internal synchronous switch increases efficiency and eliminates the need for an external Schottky diode.

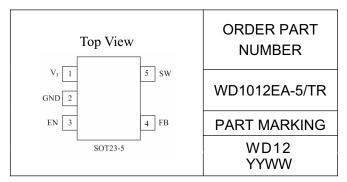

## **Ordering Information**

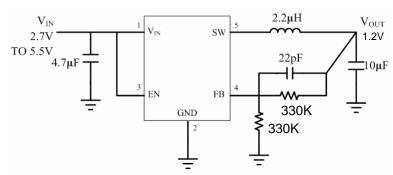

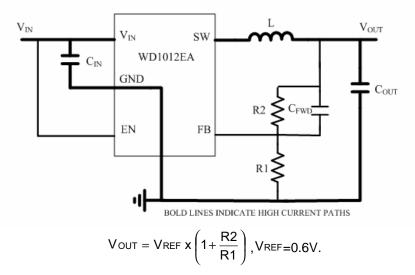

## **Typical Application Circuit**

### **Features**

- 600mA Output Current

- High Efficiency: Up to 95%

- Tiny 5-Pin SOT23 Package

- 1.5MHz Constant Frequency Operation

- 2.7V to 5.5V Input Voltage Range

- Low Dropout Operation: 100% Duty Cycle

- Low Quiescent Current: Only 22µA During Operation

- Shutdown Mode Draws < 1µA Supply Current

- No Schottky Diode Required

- 0.6V Reference Allows Low Output Voltages

- Overtemperature Protected

- Adjustable Output Voltage.

Current Mode Operation for Excellent Line and Load Transient Response

## Applications

- Cellular Telephones

- Personal Information Appliances

- Wireless and DSL Modems

- Digital Still Cameras

- MP3 Players

- Portable Instruments

## **Marking Information**

| Device        | Package | Shipping       |

|---------------|---------|----------------|

| WD1012EA-5/TR | SOT23-5 | 3000/Tape&Reel |

For marking information, contact our sales representative directly or through a willsemi distributor located in your area, otherwise visit our website for detail.

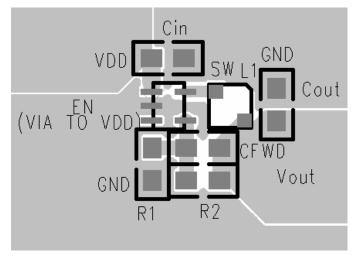

Figure 1. High Efficient Step-Down Converter

## Absolute Maximum Ratings (Note 1)

| • | Input Supply Voltage 0.3V to 6V                    |

|---|----------------------------------------------------|

| • | EN, FB Voltages – 0.3V to $V_{\text{IN}}$          |

| • | SW Voltage (DC)                                    |

| • | P-Channel Switch Source Current (DC)               |

| • | N-Channel Switch Sink Current (DC)                 |

| • | Peak SW Sink and Source Current 1.1A               |

| • | Operating Temperature Range (Note 2)40° C to 85° C |

| • | Maximum Junction Temperature (Notes 4) 125° C      |

| • | Storage Temperature Range                          |

| • | Lead Temperature (Soldering, 10 sec)               |

# **Electrical Characteristics**

$(V_{IN} = 3.6V, V_{EN} = V_{IN}, T_A = 0$  °C to 85 °C. Typical parameters are at  $T_A = +25$  °C, unless otherwise noted.)

| PARAMETER                             | SYMBOL              | CONDITIONS                                                          | MIN   | ТҮР   | MAX   | UNITS |

|---------------------------------------|---------------------|---------------------------------------------------------------------|-------|-------|-------|-------|

| Input Voltage Range                   | V <sub>IN</sub>     |                                                                     | 2.7   |       | 5.5   | V     |

| Under Voltage Lockout Threshold       | V <sub>UVLO</sub>   | $V_{IN}$ rising, hysteresis = 0.1V                                  | 2.25  | 2.40  | 2.60  | V     |

| Operating Supply Current              | I <sub>Q</sub>      | $(Note 3)V_{FB} = 60\%, I_{OUT} = 0A$                               |       | 150   | 250   | μΑ    |

| Standby Supply Current                | I <sub>Q</sub>      | $(Note 3)V_{FB} = 105\%, I_{OUT} = 0A$                              |       | 22    | 30    | μΑ    |

| Shutdown Supply Current               | I <sub>Q</sub>      | $V_{FB} = 0V, I_{OUT} = 0A$                                         |       | 0.1   | 1     | μΑ    |

|                                       |                     | $T_A = 25^{\circ}C$                                                 | 0.584 | 0.6   | 0.616 | V     |

| Adjustable Version Regulation Voltage | V <sub>FB</sub>     | $0^{\circ}\text{C} \le \text{T}_{\text{A}} \le 85^{\circ}\text{C}$  | 0.582 | 0.6   | 0.618 | V     |

|                                       |                     | $-40^{\circ}\mathrm{C} \le \mathrm{T_{A}} \le 85^{\circ}\mathrm{C}$ | 0.580 | 0.6   | 0.620 | V     |

| Output Voltage Line Regulation        | $\triangle V_{OUT}$ | $V_{IN} = 3V$ to $5V$                                               |       | 0.016 | 0.4   | %/V   |

| Output Voltage Load Regulation        | VLOADREG            | $I_{OUT} = 10$ mA to 500mA                                          |       | 0.5   |       | %     |

| Inductor Limit Current                | I <sub>LIM</sub>    | $V_{IN} = 3.6V, V_{OUT} = 90\%$<br>of $V_{OUT(NOM)}$                | 0.7   | 0.9   | 1.1   | А     |

|                                       |                     | $V_{FB}$ or $V_{OUT}$ in regulation                                 | 1.2   | 1.5   | 1.8   | MHz   |

| Oscillator Frequency                  | f <sub>OSC</sub>    | V <sub>FB</sub> or V <sub>OUT</sub> to GND                          | 230   | 280   | 330   | KHz   |

| R <sub>DS(ON)</sub> of P-Channel FET  | R <sub>PFET</sub>   | $I_{SW} = 100 \text{mA}$                                            |       | 0.37  | 0.6   | Ω     |

| R <sub>DS(ON)</sub> of N-Channel FET  | R <sub>NFET</sub>   | $I_{SW} = -100 \text{mA}$                                           |       | 0.36  | 0.6   | Ω     |

| Feedback Leakage Current              | I <sub>FB</sub>     |                                                                     |       |       | ±30   | nA    |

| SW Leakage Current                    | I <sub>LSW</sub>    | $V_{IN} = 5.5V, V_{SW} = 0V \text{ or } 5.5V$                       |       | ±0.01 | ±0.1  | μΑ    |

| EN Threshold Voltage                  | V <sub>EN</sub>     | $V_{IN} = 2.7$ to 5.5V                                              | 0.4   | 1     | 1.4   | V     |

| EN Leakage Current                    | I <sub>EN</sub>     | $V_{IN} = 5.5 V, V_{EN} = 0 V \text{ or } V_{IN}$                   |       | ±0.01 | ±0.1  | μΑ    |

- **Note1.** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

- Note2. The WD1012EA is guaranteed to meet performance specifications from 0°C to 70°C. Specifications over the -40 °C to 85 °C operating temperature range are assured by design, characterization and correlation with statistical process controls.

- Note3. Dynamic supply current is higher due to the

gate charge being delivered at the switching frequency.

Note4. This IC includes over temperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 125 °C when over temperature protection is active. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

### **Pin Functions**

$V_{IN}$  (Pin 1): Main Supply Pin. Must be closely decoupled to GND, Pin 2, with a 2.2µF or greater ceramic capacitor.

GND (Pin 2): Ground Pin.

**EN (Pin 3):** Enable pin of the device. Pulling this pin to ground forces the device into shutdown mode. Pulling this pin to  $V_{IN}$  enables the device. This pin must not be

left floating and must be terminated.

**FB (Pin 4):** Feedback pin of the device. Receives the feedback voltage from an external resistive divider across the output.

**SW (Pin 5):** Connect the inductor to this pin. This pin is the switch pin and connected to the internal MOSFET switches.

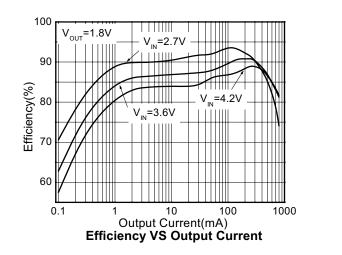

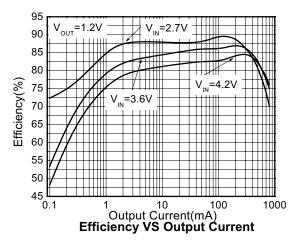

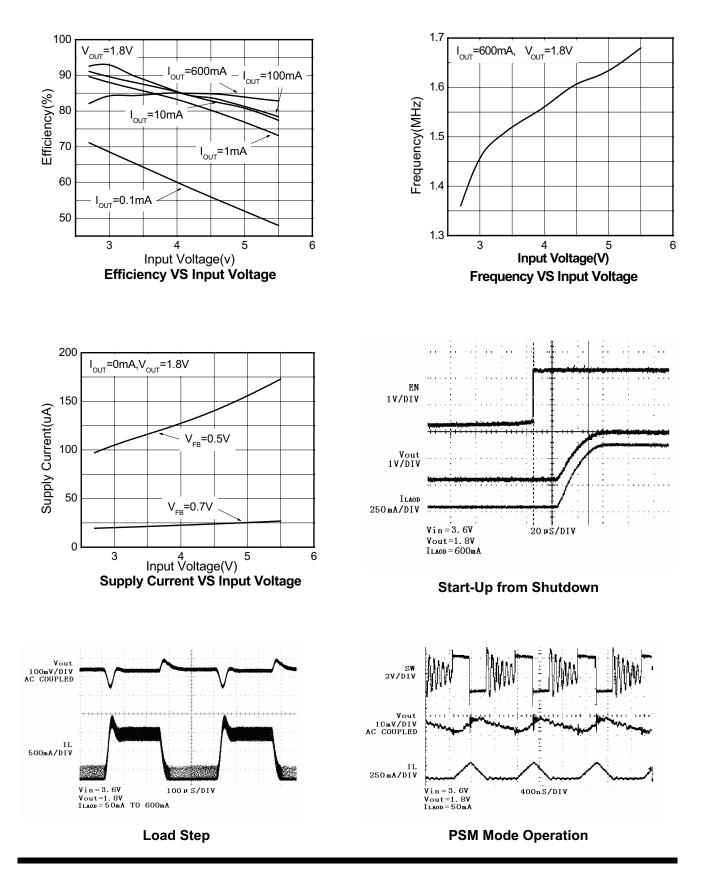

## **Typical Performance Characteristics**

# WD1012EA-5/TR

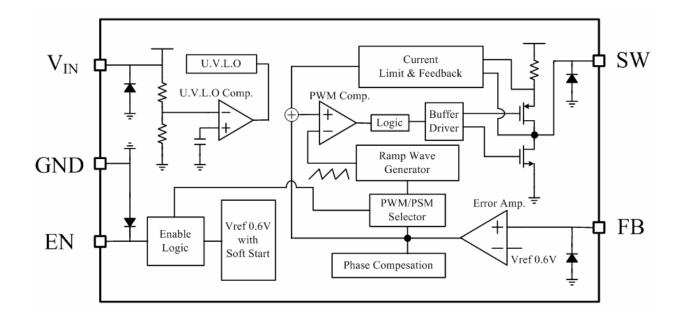

## **Function Diagram**

# Theory of Operation

### **PWM Control Mode**

The WD1012EA step-down converter operates with typically 1.5MHz fixed-frequency pulse width modulation (PWM) at moderate to heavy load currents. Both the main (P-channel MOSFET) and synchronous (N-channel MOSFET) switches are internal. During PWM operation, the converter uses a current-mode control scheme to achieve good line and load regulation. At the beginning of each clock cycle initiated by the clock signal, the main switch is turned on. The current flows from the input capacitor via the main switch through the inductor to the output capacitor and load. During this phase, the current ramps up until the PWM comparator trips and the control logic turns off the switch. After a dead time, which prevents shoot-through current, the synchronous switch is turned on and the inductor current ramps down. The current flows from the inductor to the output capacitor and to the load. It returns back to the inductor through the synchronous

switch.

The next cycle is initiated by the clock signal again turning off the synchronous switch and turning on the main switch.

### Pulse Skipping Mode (PSM)

At light loads, the inductor current may reach zero or reverse on each pulse. The synchronous switch is turned off by the current reversal comparator,  $I_{RCMP}$ , and the switch voltage will ring. This is discontinuous mode operation, and is normal behavior for the switching regulator. At very light loads, the WD1012EA will automatically skip pulses in pulse skipping mode (PSM) operation to maintain output regulation.

### **Short-Circuit Protection**

When the output is shorted to ground, the frequency of the oscillator is reduced to about 280KHz. This frequency foldback ensures that the inductor current has more time to decay, thereby preventing runaway. The oscillator's frequency will progressively increase to 1.5MHz when  $V_{FB}$  rises above 0V.

# WD1012EA-5/TR

### **Dropout Operation**

The device starts to enter 100% duty-cycle mode once the input voltage comes close to the nominal output voltage. In order to maintain the output voltage, the main switch is turned on 100% for one or more cycles. The output voltage will then be determined by the input voltage minus the voltage drop across the P-channel MOSFET and the inductor.

#### **Shutdown Mode**

Drive EN to GND to place the WD1012EA in shut-

## **Applications Information**

External component selection for the application circuit depends on the load current requirements. Certain tradeoffs between different performance parameters can also be made.

### **Inductor Selection**

The WD1012EA high switching frequency allows the use of a physically small inductor. The inductor ripple current is determined by

$$\Delta I_{L} = \frac{V_{OUT}}{(f)(L)} \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

Where  $\triangle I_L$  is the peak-to-peak inductor ripple current and f is the switching frequency. The inductor peak-topeak current ripple is typically set to be 40% of the maximum dc load current. Using this guideline and solving for L,

$$L = \frac{V_{OUT}}{f(40\% I_{LOAD(MAX)})} \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

It is important to ensure that the inductor is capable of handling the maximum peak inductor current,  $I_{LPK}$ , determined by

$I_{LPK} = I_{LOAD(MAX)} + \frac{\Delta I_L}{2}$

down mode. In shutdown mode, the reference, control circuity, main switch, and synchronous switch turn off and the output becomes high impedance. Input current falls to  $0.1\mu A$  (typ) during shutdown mode. Drive EN high to enable the IC.

### **Undervoltage Lockout (UVLO)**

The WD1012EA do not operate with battery voltages below the UVLO threshold of 2.4V(typ). The output remains off until the supply voltage exceeds the UVLO threshold. The UVLO hysteresis is 0.1V(typ). This guarantees the integrity of the output voltage regulation.

### **Inductor Core Selection**

Different core materials and shapes will change the size/current and price/current relationship of an inductor. Toroid or shielded pot cores in ferrite or permalloy materials are small and don't radiate much energy, but generally cost more than powdered iron core inductors with similar electrical characteristics. The choice of which style inductor to use often depends more on the price vs size requirements and any radiated field/EMI requirements than on what the WD1012EA requires to operate.

### **Input Capacitor Selection**

Capacitor ESR is a major contributor to input ripple in high-frequency DC-DC converters. Ordinary aluminum electrolytic capacitors have high ESR and should be avoided. Low-ESR tantalum or polymer capacitors are better and provide a compact solution for space constrained surface-mount designs. Ceramic capacitors have the lowest overall ESR.

The input filter capacitor reduces peak currents and noise at the input voltage source. Connect a low-ESR bulk capacitor ( $2.2\mu$ F to  $10\mu$ F) to the input. Select this bulk capacitor to meet the input ripple requirements and

voltage rating rather than capacitance value. Use the following equation to calculate the maximum RMS input current:

$$I_{RMS} = \frac{I_{OUT}}{V_{IN}} \sqrt{V_{OUT} \times (V_{IN} - V_{OUT})}$$

### **Output Capacitor Selection**

Ceramic capacitors with low-ESR values have the lowest output voltage ripple and are recommended. At nominal load current, the device operates in PWM mode, and the RMS ripple current is calculated as:

$$I_{RMSCout} = V_{OUT} \times \frac{1 - \frac{V_{OUT}}{V_{IN}}}{L \times f} \times \frac{1}{2 \times \sqrt{3}}$$

At nominal load current, the device operates in PWM mode, and the overall output voltage ripple is the sum of the voltage spike caused by the output capacitor ESR plus the voltage ripple caused by charging and discharging the output capacitor:

$$\Delta V = V_{OUT} \times \frac{1 - \frac{V_{OUT}}{V_{IN}}}{L \times f} \times \left(\frac{1}{8 \times C_{OUT} \times f} + ESR\right)$$

At light load currents, the converter operates in pulse skipping mode, and the output voltage ripple is dependent on the capacitor and inductor values. Larger output capacitor and inductor values minimize the voltage ripple in PSM operation and tighten dc output accuracy in PSM operation.

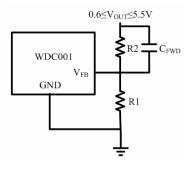

### **Output Voltage Setting**

The output voltage can be calculated as:

$$V_{OUT} = 0.6 \left( 1 + \frac{R2}{R1} \right)$$

The external resistive divider is connected to the output,

allowing remote voltage sensing as shown in Figure 2. To minimize the current through the feedback divider network, R1 should be larger than  $100k\Omega$ . The sum of R1 and R2 should not exceed 1 M $\Omega$ , to keep the network robust against noise. An external feedforward capacitor C<sub>FWD</sub>, is required for optimum load transient response. The value of C<sub>FWD</sub> should be in the range between 22pF and 33pF.

Route the FB line away from noise sources, such as the inductor or the SW line.

Figure 2. Setting the WD1012EA Output Voltage

### PC Board Layout Considerations

A good circuit board layout aids in extracting the most performance from the WD1012EA. Poor circuit layout degrades the output ripple and the electromagnetic interference (EMI) or electromagnetic compatibility (EMC) performance.

The evaluation board layout is optimized for the WD1012EA. Use this layout for best performance. If this layout needs changing, use the following guidelines:

- 1. Use separate analog and power ground planes. Connect the sensitive analog circuitry (such as voltage divider components) to analog ground; connect the power components (such as input and output bypass capacitors) to power ground. Connect the two ground planes together near the load to reduce the effects of voltage dropped on circuit board traces.

- Locate C<sub>IN</sub> as close to the V<sub>IN</sub> pin as possible, and use separate input bypass capacitors for the analog and power grounds indicated in Guideline 1.

# WD1012EA-5/TR

- 3. Route the high current path from  $C_{IN}$ , through L, to the SW and PGND pins as short as possible.

- 4. Keep high current traces as short and as wide as possible.

- 5. Place the feedback resistors as close as possible to the FB pin to prevent noise pickup.

- 6. Avoid routing high impedance traces, such as FB, near the high current traces and components or near the switch node (SW).

- 7. If high impedance traces are routed near high current and/or the SW node, place a ground plane shield between the traces.

Figure 3. WD1012EA Layout Diagram

Figure 4. WD1012EA Suggested Layout

### The Choose of External resistive divider

| Vout(V) | 1   | 1.2 | 1.5 | 1.8 | 2.5 | 2.8 | 3. 3 |

|---------|-----|-----|-----|-----|-----|-----|------|

| R1(KΩ)  | 470 | 330 | 200 | 180 | 150 | 110 | 150  |

| R2(KΩ)  | 130 | 330 | 300 | 360 | 470 | 402 | 680  |

# **Applications Information**

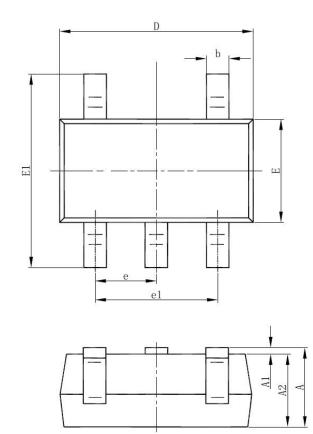

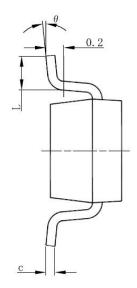

## SOT23-5L PACKAGE OUTLINE DIMENSIONS

| Symbol | <b>Dimensions</b> I | n Millimeters | <b>Dimensions In Inches</b> |       |  |

|--------|---------------------|---------------|-----------------------------|-------|--|

|        | Min                 | Max           | Min                         | Max   |  |

| Α      | 1.050               | 1.250         | 0.041                       | 0.049 |  |

| A1     | 0.000               | 0.100         | 0.000                       | 0.004 |  |

| A2     | 1.050               | 1.150         | 0.041                       | 0.045 |  |

| b      | 0.300               | 0.500         | 0.012                       | 0.020 |  |

| c      | 0.100               | 0.200         | 0.004                       | 0.008 |  |

| D      | 2.820               | 3.020         | 0.111                       | 0.119 |  |

| Е      | 1.500               | 1.700         | 0.059                       | 0.067 |  |

| E1     | 2.65                | 2.950         | 0.104                       | 0.116 |  |

| e      | 0.950(BSC)          |               | 0.037(BSC)                  |       |  |

| e1     | 1.800               | 2.000         | 0.071                       | 0.079 |  |

| L      | 0.300               | 0.600         | 0.012                       | 0.024 |  |

| θ      | 0°                  | 8°            | 0°                          | 8°    |  |