#### BQ24160, BQ24160A, BQ24161, BQ24161B, BQ24163, BQ24168

ZHCS384H - NOVEMBER 2011 - REVISED JULY 2022

# BQ2416xx 具有电源路径管理功能和 I<sup>2</sup>C 接口的 2.5A、双输出、单芯开关模式 锂离子电池充电器

## 1 特性

- 具有独立电源路径控制的高效开关模式充电器

- 从深度放电电池或者在无电池的情况下快速启动 系统

- 与 BQ27530 搭配使用时可与 MaxLife™ 技术兼 容,从而实现更快的充电速度

- 双输入、集成式 FET 充电器, 充电电流高达 2.5A

- 20V 输入额定值,具有过压保护 (OVP)

- USB 输入为 6.5V, 电流高达 1.5A

- IN 输入为 10.5V, 电流高达 2.5A (BQ24160\, BQ24160A\, BQ24161\, BQ24163)

- IN 输入为 6.5V, 电流高达 2.5A (BQ24168)

- 安全且准确的电池管理功能

- 电池调节精度为 1%

- 充电电流精度为 10%

- 可使用 I<sup>2</sup>C 接口对充电参数编程

- 基于电压的 NTC 监控输入

- 符合 JEITA 标准(BQ24160、BQ24160A、 BQ24161B、BQ24163、BQ24168)

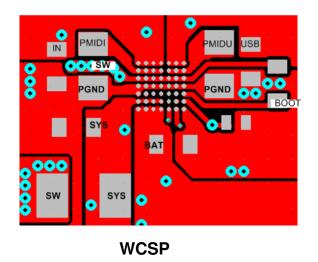

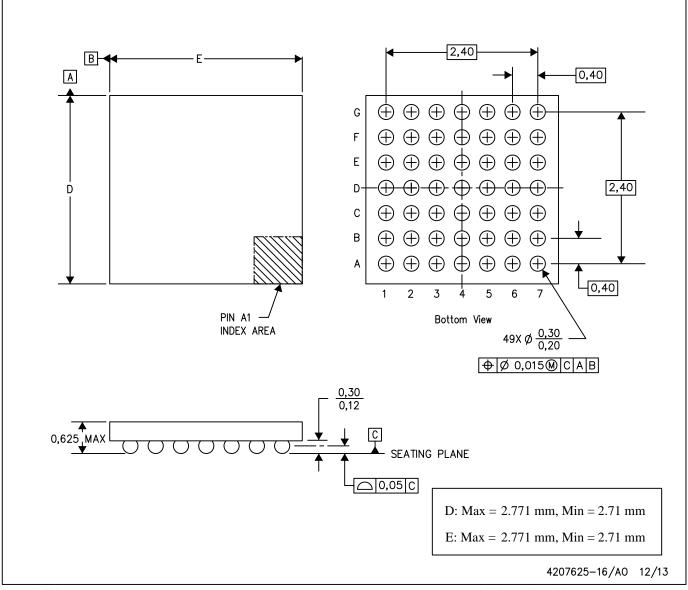

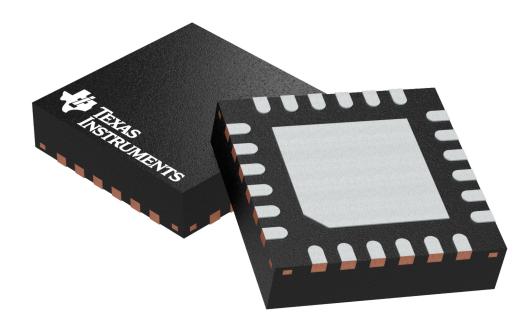

- 采用小型 2.8mm × 2.8mm 49 焊球 WCSP 或 4mm × 4mm VQFN-24 封装

### 2 应用

- 手持产品

- 便携式媒体播放器

- 便携式设备

- 上网本和便携式互联网设备

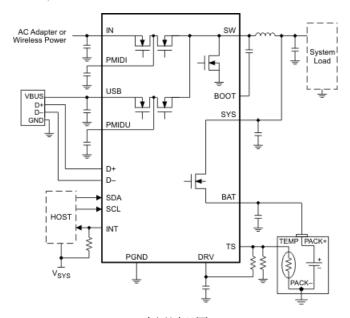

### 3 说明

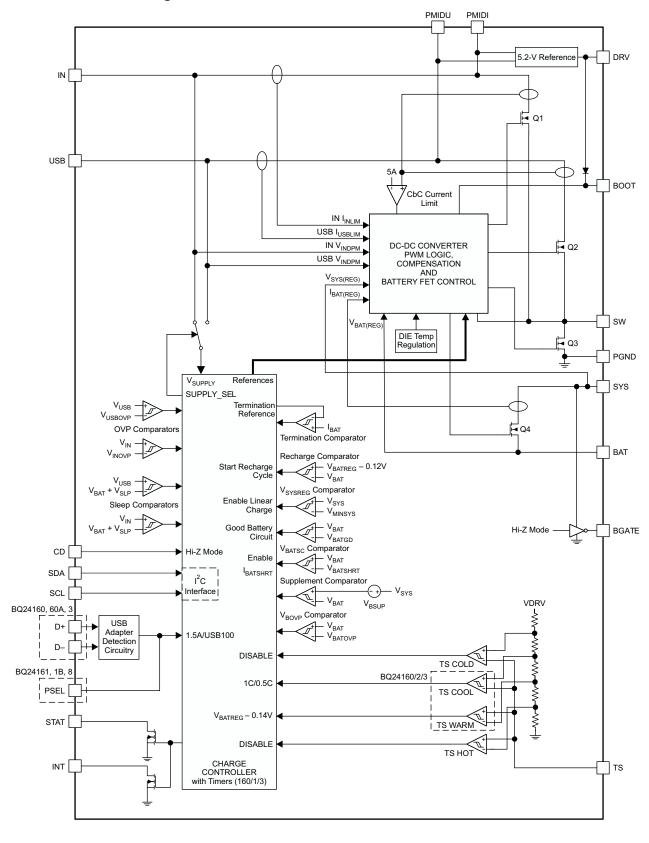

BQ24160 \ BQ24160A \ BQ24161 \ BQ24161B \ BQ24163 和 BQ24168 是高度集成的单芯锂离子电池 充电器和系统电源路径管理器件,旨在用于空间有限且 具有高容量电池的便携式应用。此单芯充电器具有双输 入,可由 USB 端口或更高功率的输入电源(即交流适 配器或无线充电输入)供电,适用于多用途解决方案。 这两个输入彼此完全隔离,并可以使用 I<sup>2</sup>C 接口方便地 进行选择。

凭借电源路径管理功能,BQ2416xx 能够在对电池进行 独立充电的同时通过一个高效的直流/直流转换器为系 统供电。电源路径管理架构使该系统能够在电池包有缺 陷或缺失的情况下运行,并且即使在电池完全放电或者 无电池的情况下也可实现即时系统启动。

#### 器件信息

| 器件型号     | 封装 <sup>(1)</sup> | 封装尺寸(标称值)       |  |  |

|----------|-------------------|-----------------|--|--|

| BO2416vv | VQFN (24)         | 4.00mm × 4.00mm |  |  |

| BQ2416xx | DSBGA (49)        | 2.80mm × 2.80mm |  |  |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

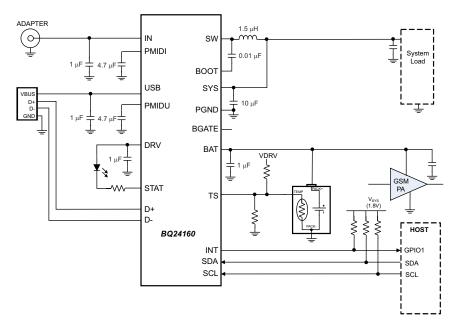

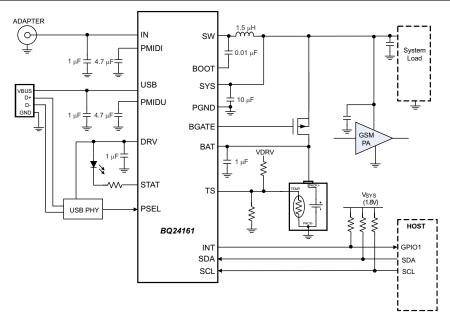

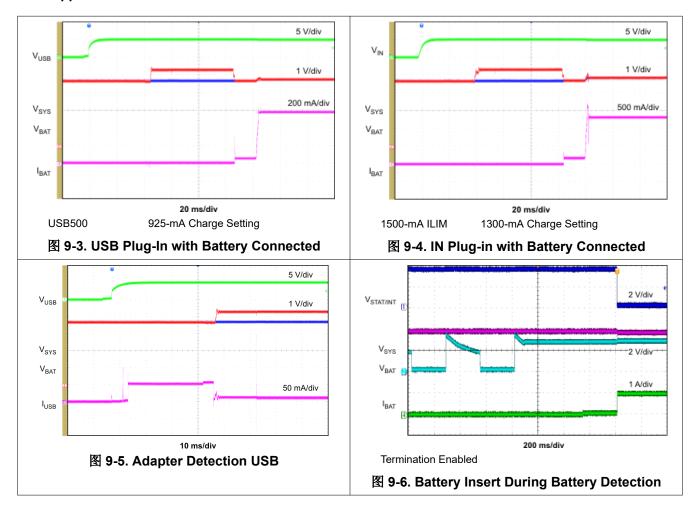

应用原理图

## **Table of Contents**

| 1 特性                                 | 1 | 8.5 Programming                      | 27              |

|--------------------------------------|---|--------------------------------------|-----------------|

| <u> </u>                             |   | 8.6 Register Maps                    |                 |

| - <i>—, -</i><br>3 说明                |   | 9 Application and Implementation     | 34              |

| 4 Revision History                   |   | 9.1 Application Information          | 34              |

| 5 Device Comparison Table            |   | 9.2 Typical Application              |                 |

| 6 Pin Configuration and Functions    |   | 10 Power Supply Recommendations      | 38              |

| 7 Specifications                     |   | 10.1 Requirements for SYS Output     | <mark>38</mark> |

| 7.1 Absolute Maximum Ratings         |   | 10.2 Requirements for Charging       |                 |

| 7.2 Handling Ratings                 |   | 11 Layout                            |                 |

| 7.3 Recommended Operating Conditions |   | 11.1 Layout Guidelines               |                 |

| 7.4 Thermal Information              |   | 11.2 Layout Example                  | 40              |

| 7.5 Electrical Characteristics       |   | 12 Device and Documentation Support  | 41              |

| 7.6 Typical Characteristics          |   | 12.1 Device Support                  | 41              |

| 8 Detailed Description               |   | 12.2 接收文档更新通知                        | 41              |

| 8.1 Overview                         |   | 12.3 支持资源                            |                 |

| 8.2 Functional Block Diagram         |   | 12.4 Trademarks                      |                 |

| 8.3 Feature Description              |   | 12.5 Electrostatic Discharge Caution |                 |

| 8.4 Device Functional Modes          |   | 12.6 术语表                             |                 |

| <u> </u>                             |   | —· - ·   ·                           |                 |

# **4 Revision History**

注:以前版本的页码可能与当前版本的页码不同

| С | hanges from Revision G (November 2015) to Revision H (July 2022)                                   | Page     |

|---|----------------------------------------------------------------------------------------------------|----------|

| • | Changed I <sub>TERM</sub> specification.                                                           | 3        |

| С | hanges from Revision F (July 2014) to Revision G (November 2015)                                   | Page     |

| • | Deleted hyperlink to unpublished application note SLUA727                                          | 26       |

| С | hanges from Revision E (November 2013) to Revision F (January 2014)                                | Page     |

| • | 添加了 <i>处理额定值</i> 表、特性说明部分、器件功能模式、应用和实施部分、电源相关建议部分、布度件和文档支持部分以及机械、封装和可订购信息部分                        | 1        |

| • | Changed the Ordering Information table to the Device Comparison Table                              | 4        |

| • | Changed to V <sub>BAD SOURCE</sub> include values for "During Bad Source Detection"                | 8        |

| • | Changed the Functional Block Diagram. Changed the device numbers above D+/D- and PSEL              | 14       |

| • | Changed the PWM Controller in Charge Mode section to include the soft-start function               | 15       |

| • | Changed the Battery Charging Process section. New text added starting with "The BQ2416xx moni      | tors the |

|   | charging current"                                                                                  |          |

| • | Changed the Input Source Connected section                                                         |          |

| • | Changed the Input Source Connected section                                                         |          |

| • | Added the Reverse Boost (Boost Back) Prevention Circuit section                                    |          |

| С | hanges from Revision D (November 2012) to Revision E (November 2013)                               | Page     |

| • | 添加了特性:与 BQ27530 搭配使用时可与 MaxLife 技术兼容,从而实现更快的充电速度                                                   | 1        |

| • | 在整个数据表中将 QFN-24 封装更改为 VQFN-24 封装                                                                   |          |

| С | hanges from Revision C (October 2012) to Revision D (November 2012)                                | Page     |

| • | Changed the Ordering Information table to include the WSCP package for BQ24161BRGR and BQ24161BYFF |          |

### www.ti.com.cn

| Changes from Revision B (September 2012) to Revision C (October 2012)                                                                                                                                                                                                                                     | Page      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Changed the Ordering Information table to include BQ24160A                                                                                                                                                                                                                                                | 4         |

| Changes from Revision A (March 2012) to Revision B (September 2012)                                                                                                                                                                                                                                       | Page      |

| Changed the Ordering Information table to include BQ24161B                                                                                                                                                                                                                                                | 4         |

| • Changed text From: "battery FET (Q6)" To: "battery FET (Q4)" in the Battery Only Connected                                                                                                                                                                                                              | section18 |

| <ul> <li>Changed From: V<sub>WARM</sub> &lt; V<sub>TS</sub> &lt; V<sub>HOT</sub> To: V<sub>WARM</sub> &gt; V<sub>TS</sub> &gt; V<sub>HOT</sub>, and Changed From: V<sub>COLD</sub> &lt; V<sub>COLD</sub> &gt; V<sub>TS</sub> &gt; V<sub>COOL</sub> in the External NTC Monitoring (TS) section</li> </ul> |           |

| • Changed 图 11-1                                                                                                                                                                                                                                                                                          |           |

| Changes from Revision * (November 2011) to Revision A (March 2012)                                                                                                                                                                                                                                        | Page      |

| • Changed the USB Pin numbers in the YFF pachkage for bq24160/3 From: A5-A6 To: A5-A7                                                                                                                                                                                                                     | 4         |

| Changed V <sub>BATREG</sub> - Voltage regulation accuracy                                                                                                                                                                                                                                                 | 8         |

| Changed 图 9-1                                                                                                                                                                                                                                                                                             |           |

| • Changed 图 9-2                                                                                                                                                                                                                                                                                           | 34        |

### **5 Device Comparison Table**

| PART NUMBER <sup>(1)</sup> (2) | USB OVP | IN OVP | USB DETECTION             | TIMERS<br>(Safety and<br>Watchdog) | NTC<br>MONITORING | V <sub>BATSHRT/</sub><br>I <sub>BATSHRT</sub> | V <sub>MINSYS</sub> |

|--------------------------------|---------|--------|---------------------------|------------------------------------|-------------------|-----------------------------------------------|---------------------|

| BQ24160                        | 6.5V    | 10.5V  | D+/D -                    | Yes                                | JEITA             | 3.0V<br>50mA                                  | 3.5V                |

| BQ24160A                       | 6.5V    | 10.5V  | D+/D -                    | No                                 | JEITA             | 3.0V<br>50mA                                  | 3.5V                |

| BQ24161                        | 6.5V    | 10.5V  | PSEL (0=1.5A,<br>1=100mA) | Yes                                | Standard          | 2.0V<br>50mA                                  | 3.5V                |

| BQ24161B                       | 6.5V    | 10.5V  | PSEL (0=1.5A,<br>1=500mA) | Yes                                | JEITA             | 3.0V<br>50mA                                  | 3.5V                |

| BQ24163                        | 6.5V    | 10.5V  | D+/D -                    | Yes                                | JEITA             | 2.0V<br>50mA                                  | 3.2V                |

| BQ24168                        | 6.5V    | 6.5V   | PSEL (0=1.5A,<br>1=100mA) | No                                 | JEITA             | 2.0V<br>50mA                                  | 3.5V                |

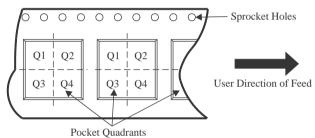

- (1) Each of the above are available in as YFF and RGE packages with the following options:

- R tabed and reeled in quantities of 3,000 devices per reel.

- T taped and reeled in quantities of 250 devices per reel.

- (2) This product is RoHS compatible, including a lead concentration that does not exceed 0.1% of total product weight, and is suitable for use in specified lead-free soldering processes. In addition, this product uses package materials that do not contain halogens, including bromine (Br) or antimony (Sb) above 0.1% of total product weight.

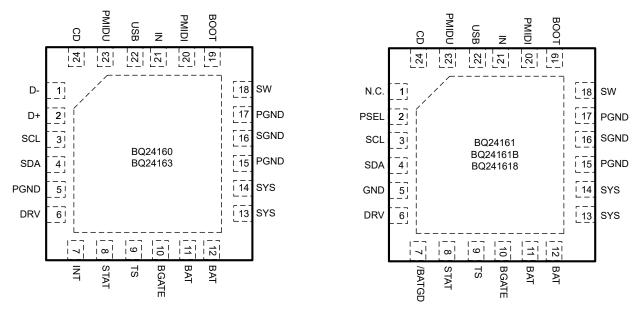

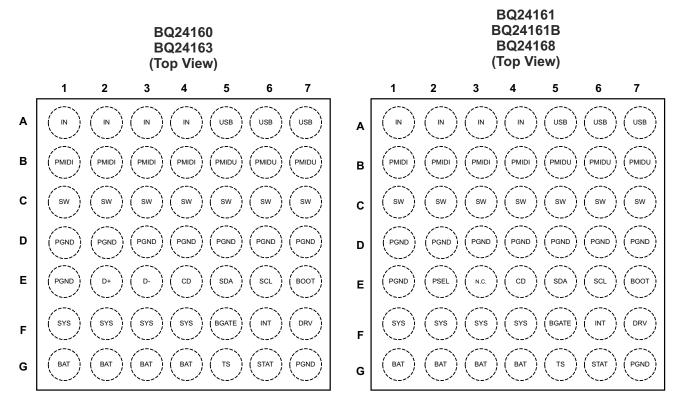

## 6 Pin Configuration and Functions

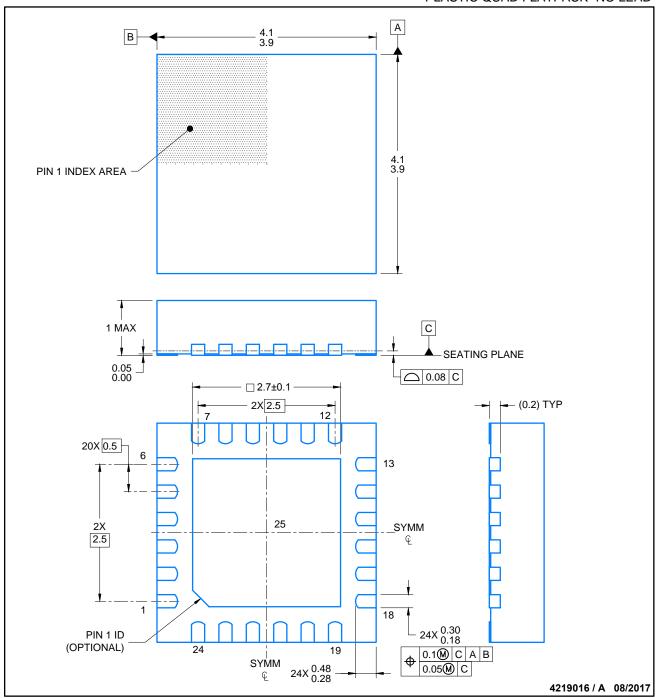

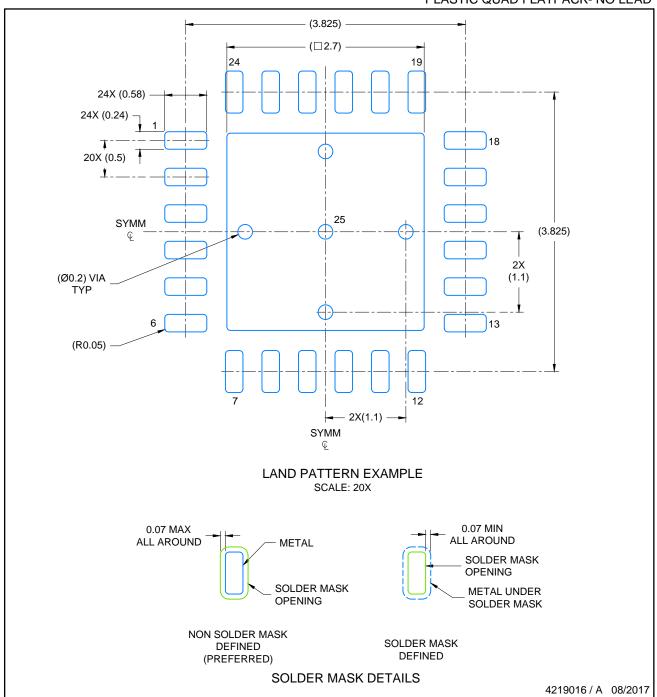

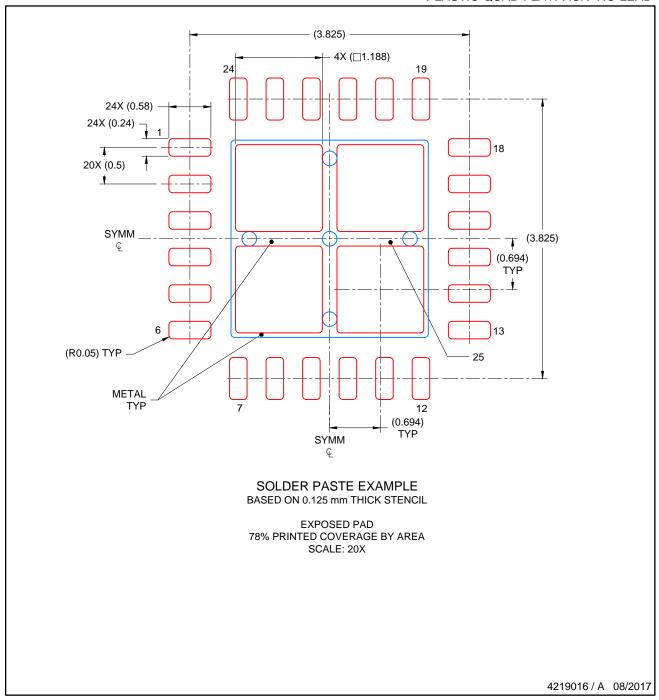

图 6-1. RGE Package VQFN 24 Pins Top View

图 6-2. YFF Package WCSP 49 Pins Top View

表 6-1. Pin Functions

|       |                  | PIN               |                  |                       |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|-------|------------------|-------------------|------------------|-----------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME  |                  | NO.<br>BQ24160, 3 |                  | NO.<br>BQ24161, 1B, 8 |     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|       | YFF              | RGE               | YFF              | RGE                   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| BAT   | G1-G4            | 11, 12            | G1-G4            | 11, 12                | I/O | <b>Battery Connection</b> – Connect to the positive terminal of the battery. Additionally, bypass BAT to GND with at least a 1- $\mu$ F capacitor.                                                                                                                                                                                                                                                                                                                         |  |  |

| BGATE | F5               | 10                | F5               | 10                    | 0   | External Discharge MOSFET Gate Connection - BGATE drives an external P-Channel MOSFET to provide a very low-resistance discharge path. Connect BGATE to the gate of the external MOSFET. BGATE is low during high impedance mode and when no input is connected.                                                                                                                                                                                                           |  |  |

| воот  | E7               | 19                | E7               | 19                    | I   | High Side MOSFET Gate Driver Supply - Connect a 0.01-μF ceramic capacitor (voltage rating > 10 V) from BOOT to SW to supply the gate drive for the high side MOSFETs.                                                                                                                                                                                                                                                                                                      |  |  |

| CD    | E4               | 24                | E4               | 24                    | I   | IC Hardware Chip Disable Input - Drive $\overline{CD}$ high to place the BQ2416xx in high-z mode. Drive $\overline{CD}$ low for normal operation. Do not leave CD unconnected.                                                                                                                                                                                                                                                                                             |  |  |

| D+    | E2               | 2                 | _                | _                     | ı   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| D -   | E3               | 1                 | _                | _                     | I   | D+ and D - Connections for USB Input Adapter Detection - When a charge cycle is initiated by the USB input, and a short is detected between D+ and D - , the USB input curror limit is set to 1.5 A. If a short is not detected, the USB100 mode is selected. The D+/D - detection has no effect on the IN input.                                                                                                                                                          |  |  |

| DRV   | F7               | 6                 | F7               | 6                     | 0   | Gate Drive Supply - DRV is the bias supply for the gate drive of the internal MOSFETs. Bypass DRV to PGND with a 1- $\mu$ F ceramic capacitor. DRV may be used to drive external loads up to 10 mA. DRV is active whenever the input is connected and $V_{SUPPLY} > V_{UVLO}$ and $V_{SUPPLY} > (V_{BAT} + V_{SLP})$                                                                                                                                                       |  |  |

| IN    | A1- A4           | 21                | A1- A4           | 21                    | I   | Input power supply - IN is connected to the external DC supply (AC adapter or alternate power source). Bypass IN to PGND with at least a 1- μ F ceramic capacitor.                                                                                                                                                                                                                                                                                                         |  |  |

| INT   | F6               | 7                 | F6               | 7                     | 0   | Status Output – INT is an open-drain output that signals charging status and fault interrupts. INT pulls low during charging. INT is high impedance when charging is complete or the charger is disabled. When a fault occurs, a 128- $\mu$ s pulse is sent out as an interrupt for the host. INT is enabled/disabled using the EN_STAT bit in the control register. Connect INT to a logic rail through a 100-k $\Omega$ resistor to communicate with the host processor. |  |  |

| PGND  | D1-D7,<br>E1, G7 | 5, 15,<br>16, 17  | D1-D7,<br>E1, G7 | 5, 15,<br>16, 17      | _   | Ground terminal - Connect to the thermal pad (for VQFN only) and the ground plane of the circuit.                                                                                                                                                                                                                                                                                                                                                                          |  |  |

## 表 6-1. Pin Functions (continued)

|                              |       | PIN          |       |       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|------------------------------|-------|--------------|-------|-------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO.<br>BQ24160, 3<br>YFF RGF |       | NO<br>BQ2416 |       | 1/0   | DESCRIPTION |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                              | YFF   | RGE          | YFF   | RGE   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| PMIDI                        | B1-B4 | 20           | B1-B4 | 20    | 0           | Reverse Blocking MOSFET and High Side MOSFET Connection Point for High Power Input - Bypass PMIDI to GND with at least a 4.7- µ F ceramic capacitor. Use caution when connecting an external load to PMIDI. The PMIDI output is not current limited. Any short on PMIDI will damage the IC.                                                                                                                                                                                                                             |  |

| PMIDU                        | B5-B7 | 23           | B5-B7 | 23    | 0           | Reverse Blocking MOSFET and High Side MOSFET Connection Point for USB Input – Bypass PMIDU to GND with at least a 4.7- µ F ceramic capacitor. Use caution when connectin an external load to PMIDU. The PMIDU output is not current limited. Any short on PMIDU will damage the IC.                                                                                                                                                                                                                                     |  |

| PSEL                         | _     | _            | E2    | 2     |             | USB Source Detection Input - Drive PSEL high to indicate that a USB source is connected to the USB input. When PSEL is high, the IC starts up with a 100 mA (BQ24161/8) or 500 mA (BQ24161B) input current limit for USB. Drive PSEL low to indicate that an AC Adapter is connected to the USB input. When PSEL is low, the IC starts up with a 1.5 A input current limit for USB. PSEL has no effect on the IN input. Do not leave PSEL unconnected.                                                                  |  |

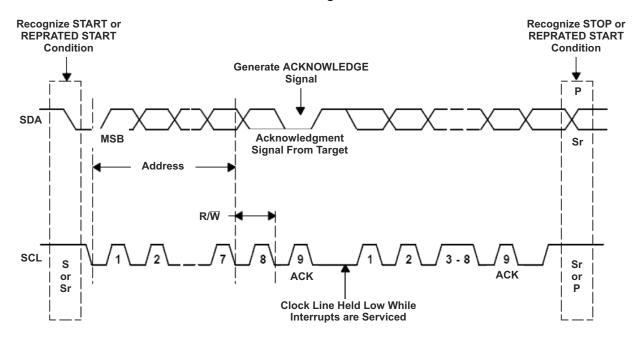

| SCL                          | E6    | 3            | E6    | 3     | ı           | <b>1<sup>2</sup>C Interface Clock</b> - Connect SCL to the logic rail through a 10-k Ω resistor.                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| SDA                          | E5    | 4            | E5    | 4     | I/O         | I <sup>2</sup> C Interface Data - Connect SDA to the logic rail through a 10-k Ω resistor.                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| STAT                         | G6    | 8            | G6    | 8     | 0           | Status Output – STAT is an open-drain output that signals charging status and fault interrupts. STAT pulls low during charging. STAT is high impedance when charging is complete or the charger is disabled. When a fault occurs, a 128- $\mu$ s pulse is sent out as an interrupt for the host. STAT is enabled /disabled using the EN_STAT bit in the control register. Pull STAT up to a logic rail thruogh an LED for visual indication or through a 10-k $\Omega$ resistor to communicate with the host processor. |  |

| sw                           | C1-C7 | 18           | C1-C7 | 18    | 0           | Inductor Connection - Connect to the switched side of the external inductor.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| SYS                          | F1-F4 | 13, 14       | F1-F4 | 13,14 | I           | System Voltage Sense and Charger FET Connection – Connect SYS to the system output at the output bulk capacitors. Bypass SYS locally with at least 10 $\mu$ F. A 47- $\mu$ F bypass capacitor is recommended for optimal transient response.                                                                                                                                                                                                                                                                            |  |

| TS                           | G5    | 9            | G5    | 9     | I           | Battery Pack NTC Monitor - Connect TS to the center tap of a resistor divider from DRV to GND. The NTC is connected from TS to GND. The TS function provides 4 thresholds for JEITA compatibility (160, 161B, 163, 168 only). TS faults are reported by the I <sup>2</sup> C interface. See the NTC Monitor section for more details on operation and selecting the resistor values. Connect TS to DRV to disable the TS function.                                                                                      |  |

| USB                          | A5-A7 | 22           | A5-A7 | 22    | I           | USB Input Power Supply - USB is connected to the external DC supply (AC adapter or USB port). Bypass USB to PGND with at least a 1- $\mu$ F ceramic capacitor.                                                                                                                                                                                                                                                                                                                                                          |  |

| Thermal<br>Pad               | _     | Pad          | _     | Pad   | _           | There is an internal electrical connection between the exposed thermal pad and the PGND pin of the device. The thermal pad must be connected to the same potential as the PGND pin on the printed circuit board. Do not use the thermal pad as the primary ground input for the device. PGND pin must be connected to ground at all times.                                                                                                                                                                              |  |

### 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                                                                                                                         |                                                                                                                                   | MIN   | MAX | UNIT |

|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------|-----|------|

| respect to VSS)  SW  SDA, SCL, SYS, B  BOOT to SW  Output current (continuous)  SW  SYS, BAT  Input current (continuous)  IN  USB  STAT | IN, USB                                                                                                                           | - 2   | 20  | V    |

|                                                                                                                                         | PMIDI, PMIDU, BOOT                                                                                                                | - 0.3 | 20  | V    |

|                                                                                                                                         | SW                                                                                                                                |       | 12  | V    |

|                                                                                                                                         | SDA, SCL, SYS, BAT, STAT, BGATE, DRV, TS, D+, D - , INT, PSEL, CD                                                                 | - 0.3 | 7   | V    |

| BOOT to SW                                                                                                                              | SW 4.5                                                                                                                            |       | 7   | V    |

| Output current (continuous)                                                                                                             | SW                                                                                                                                |       |     | Α    |

|                                                                                                                                         | SYS, BAT                                                                                                                          | 3.5   |     | Α    |

| Input ourrent (continuous)                                                                                                              | IN                                                                                                                                | 2.75  |     | Α    |

| input current (continuous)                                                                                                              | USB                                                                                                                               | 1.75  |     | Α    |

| Output sink current                                                                                                                     | - 0.7 1  , SCL, SYS, BAT, STAT, BGATE, DRV, TS, D+, D - , INT, PSEL, CD - 0.3 7 - 0.3 7 4.5 , BAT - 2.75 - 1.75 - 10 - 1 e - 40 8 |       | mA  |      |

| Output sink current                                                                                                                     | INT                                                                                                                               | 1     |     | mA   |

| Operating free-air temperatur                                                                                                           | e range                                                                                                                           | - 40  | 85  | °C   |

| Junction temperature, T <sub>J</sub>                                                                                                    |                                                                                                                                   | - 40  | 125 | °C   |

| Lead temperature (soldering,                                                                                                            | 10 s)                                                                                                                             | 300   |     | ° C  |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltage values are with respect to the network ground terminal unless otherwise noted.

## 7.2 Handling Ratings

|                  |                                            |                                                                                          | MIN | MAX | UNIT |

|------------------|--------------------------------------------|------------------------------------------------------------------------------------------|-----|-----|------|

| T <sub>stg</sub> | Storage temperature rang                   | - 65                                                                                     | 150 | °C  |      |

| V                | Electrostatic discharge                    | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              |     | 2   | kV   |

| V(ESD)           | V <sub>(ESD)</sub> Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> |     | 500 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  |                                          | MIN | MAX | UNIT |

|------------------|------------------------------------------|-----|-----|------|

|                  | IN voltage range                         | 4.2 | 18  |      |

| V <sub>IN</sub>  | IN operating voltage range (BQ24160/1/3) | 4.2 | 10  | V    |

|                  | IN operating voltage range (BQ24168)     | 4.2 | 6   |      |

| V                | USB voltage range                        | 4.2 | 18  | V    |

| V <sub>USB</sub> | USB operating range                      | 4.2 | 6   | v    |

| I <sub>IN</sub>  | Input current, IN input                  |     | 2.5 | Α    |

| I <sub>USB</sub> | Input current USB input                  |     | 1.5 | Α    |

| I <sub>SYS</sub> | Output Current from SW, DC               |     | 3   | Α    |

| 1                | Charging                                 |     | 2.5 | Α    |

| I <sub>BAT</sub> | Discharging, using internal battery FET  |     | 2.5 | Α    |

| $T_{J}$          | Operating junction temperature range     | 0   | 125 | °C   |

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 7.4 Thermal Information

|                 | Junction-to-case (top) thermal resistance  JB Junction-to-board thermal resistance  JT Junction-to-top characterization parameter | BQ2416xx      |               |      |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|------|--|

|                 | THERMAL METRIC                                                                                                                    | 49 PINS (YFF) | 24 PINS (RGE) | UNIT |  |

| θ ЈА            | Junction-to-ambient thermal resistance                                                                                            | 49.8          | 32.6          | °C/W |  |

| θ JCtop         | Junction-to-case (top) thermal resistance                                                                                         | 0.2           | 30.5          | °C/W |  |

| θ ЈВ            | Junction-to-board thermal resistance                                                                                              | 1.1           | 3.3           | °C/W |  |

| ψ <sub>JT</sub> | Junction-to-top characterization parameter                                                                                        | 1.1           | 0.4           | °C/W |  |

| ψ ЈВ            | Junction-to-board characterization parameter                                                                                      | 6.6           | 9.3           | °C/W |  |

| θ JCbot         | Junction-to-case (bottom) thermal resistance                                                                                      | n/a           | 2.6           | °C/W |  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see The IC Package Thermal Metrics Application Report.

### 7.5 Electrical Characteristics

Circuit of  $\boxtimes$  9-1,  $V_{SUPPLY} = V_{USB}$  or  $V_{IN}$  (whichever is supplying the IC),  $V_{UVLO} < V_{SUPPLY} < V_{OVP}$  and  $V_{SUPPLY} > V_{BAT} + V_{SLP}$ ,  $T_J = -40^{\circ}C - 125^{\circ}C$  and  $T_J = 25^{\circ}C$  for typical values (unless otherwise noted)

|                           | PARAMETER                                                            | TEST CONDIT                                                                                                 | IONS                                | MIN                           | TYP                           | MAX                            | UNIT   |

|---------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------|-------------------------------|--------------------------------|--------|

| NPUT CURR                 | ENTS                                                                 |                                                                                                             | -                                   |                               |                               | '                              |        |

|                           |                                                                      | V <sub>UVLO</sub> < V <sub>SUPPLY</sub> < V <sub>OVP</sub> and                                              | PWM switching                       |                               | 15                            |                                | mA     |

| SUPPLY                    | Supply current for control (V <sub>IN</sub> or V <sub>USB</sub> )    | V <sub>SUPPLY</sub> > V <sub>BAT</sub> +V <sub>SLP</sub>                                                    | PWM NOT switching                   |                               |                               | 5                              |        |

|                           |                                                                      | 0°C < T <sub>J</sub> < 85°C, High-Z Mode                                                                    |                                     |                               |                               | 175                            | μА     |

| BATLEAK                   | Leakage current from BAT to the Supply                               | 0°C < T <sub>J</sub> < 85°C, V <sub>BAT</sub> = 4.2V, V <sub>USB</sub>                                      | <sub>3</sub> = V <sub>IN</sub> = 0V |                               |                               | 5                              | μА     |

| I <sub>BAT_HIZ</sub>      | Battery discharge current in High Impedance mode, (BAT, SW, SYS)     | 0°C< T <sub>J</sub> < 85°C, V <sub>BAT</sub> = 4.2V, V <sub>SUPP</sub><br>SCL, SDA = 0 V or 1.8V, High-Z Mo |                                     |                               |                               | 55                             | μА     |

| POWER-PAT                 | H MANAGEMENT                                                         |                                                                                                             | ,                                   |                               |                               | '                              |        |

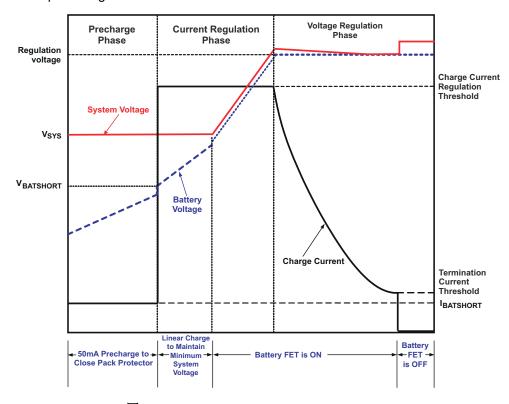

|                           |                                                                      | Chargo Enobled V                                                                                            | BQ24160, 1, 1B, 8                   | 3.60                          | 3.7                           | 3.82                           |        |

| V <sub>SYS(REG)</sub>     | System regulation voltage                                            | Charge Enabled, V <sub>BAT</sub> < V <sub>MINSYS</sub>                                                      | BQ24163                             | 3.3                           | 3.4                           | 3.5                            | V      |

| 0.0(1.20)                 | g                                                                    | Battery FET turned off (Charge Disa<br>Charging Terminated)                                                 | abled, TS Fault or                  | V <sub>BATREG</sub><br>+ 1.5% | V <sub>BATREG</sub><br>+ 3.0% | V <sub>BATREG</sub><br>+ 4.17% |        |

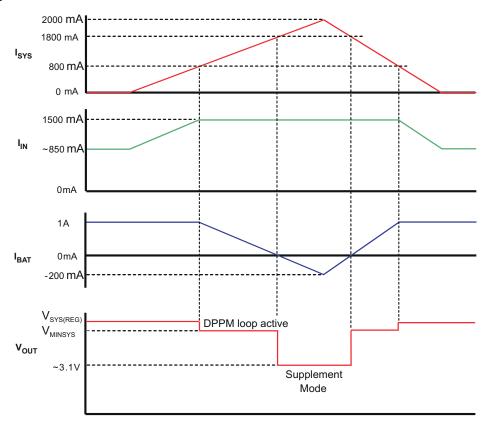

| .,                        | Minimum evetem regulation voltage                                    | Charge enabled, V <sub>BAT</sub> < V <sub>MINSYS</sub> ,                                                    | BQ24160, 1, 1B, 8                   | 3.4                           | 3.5                           | 3.62                           | V      |

| V <sub>MINSYS</sub>       | Minimum system regulation voltage                                    | Input current limit or V <sub>INDPM</sub> active                                                            | BQ24163                             | 3.1                           | 3.2                           | 3.3                            | V      |

| V <sub>BSUP1</sub>        | Enter supplement mode threshold                                      | V <sub>BAT</sub> > 2.5V                                                                                     |                                     |                               | V <sub>BAT</sub><br>- 30mV    |                                | ٧      |

| V <sub>BSUP2</sub>        | Exit supplement mode threshold                                       | V <sub>BAT</sub> > 2.5V                                                                                     |                                     |                               | V <sub>BAT</sub><br>- 10mV    |                                | ٧      |

| LIM(discharge)            | Current limit, discharge or supplement mode                          | Current monitored in internal FET o                                                                         | only.                               |                               | 7                             |                                | Α      |

| t <sub>DGL(SC1)</sub>     | Deglitch time, SYS short circuit during discharge or supplement mode | Measured from (V <sub>BAT</sub> - V <sub>SYS</sub> ) = 30 impedance                                         | 00mV to BAT high-                   |                               | 250                           |                                | μS     |

| t <sub>REC(SC1)</sub>     | Recovery time, SYS short circuit during discharge or supplement mode |                                                                                                             |                                     |                               | 60                            |                                | ms     |

|                           | Battery range for BGATE and supplement mode operation                |                                                                                                             |                                     | 2.5                           |                               | 4.5                            | V      |

| BATTERY CH                | IARGER                                                               |                                                                                                             |                                     |                               |                               |                                |        |

| R <sub>ON(BAT-SYS)</sub>  | Internal battery charger MOSFET on-resistance                        | Measured from BAT to SYS,                                                                                   | YFF pkg                             |                               | 37                            | 57                             | mΩ     |

| **ON(BAT-313)             | monal pattery oranger moon 2 r on resistance                         | V <sub>BAT</sub> = 4.2V                                                                                     | RGE pkg                             |                               | 50                            | 70                             | 111 00 |

| V <sub>BATREG</sub>       | Charge Voltage                                                       | Operating in voltage regulation, Pro                                                                        | ogrammable range                    | 3.5                           |                               | 4.44                           | V      |

| · BAIREG                  | Voltage regulation accuracy                                          |                                                                                                             |                                     | - 1%                          |                               | 1%                             |        |

| louanon                   | Fast charge current range                                            | $V_{BATSHRT} \leq V_{BAT} < V_{BAT(REG)}$ progr                                                             | rammable range                      | 550                           |                               | 2500                           | mA     |

| CHARGE                    | Fast charge current accuracy                                         | 0°C to 125°C                                                                                                |                                     | - 10%                         |                               | +10%                           |        |

| V <sub>BATSHRT</sub>      | Battery short circuit threshold                                      | 100mV Hysteresis                                                                                            | BQ24161, 3, 8                       | 1.9                           | 2.0                           | 2.1                            | V      |

| *BAISHRI                  | Sattley Street Ground Hill Sorring                                   | 11,000,000                                                                                                  | BQ24160, 1B                         | 2.9                           | 3.0                           | 3.1                            | •      |

| BATSHRT                   | Battery short circuit current                                        | V <sub>BAT</sub> < V <sub>BATSHRT</sub>                                                                     |                                     |                               | 50                            |                                | mA     |

| t <sub>DGL(BATSHRT)</sub> | Deglitch time for battery short circuit to fastcharge transition     |                                                                                                             |                                     |                               | 32                            |                                | ms     |

|                           |                                                                      | I <sub>TERM</sub> = 50mA                                                                                    |                                     | - 40%                         |                               | +40%                           |        |

| I <sub>TERM</sub>         | Termination charge current accuracy                                  | I <sub>TERM</sub> = 100mA                                                                                   |                                     | - 20%                         |                               | +20%                           |        |

|                           |                                                                      | I <sub>TERM</sub> ≥ 150mA                                                                                   |                                     | - 15%                         |                               | +15%                           |        |

## 7.5 Electrical Characteristics (continued)

Circuit of  $\boxtimes$  9-1,  $V_{SUPPLY} = V_{USB}$  or  $V_{IN}$  (whichever is supplying the IC),  $V_{UVLO} < V_{SUPPLY} < V_{OVP}$  and  $V_{SUPPLY} > V_{BAT} + V_{SLP}$ ,  $T_J = -40^{\circ}C$  - 125°C and  $T_J = 25^{\circ}C$  for typical values (unless otherwise noted)

|                          | PARAMETER                                                                     | TEST COND                                                                                                                                          | ITIONS                                               | MIN                            | TYP                            | MAX                            | UNIT                       |

|--------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------|--------------------------------|--------------------------------|----------------------------|

| DGL(TERM)                | Deglitch time for charge termination                                          | Both rising and falling, 2mV overc                                                                                                                 | drive, t <sub>RISE</sub> , t <sub>FALL</sub> = 100ns |                                | 32                             |                                | ms                         |

| V <sub>RCH</sub>         | Recharge threshold voltage                                                    | Below V <sub>BATREG</sub>                                                                                                                          |                                                      |                                | 120                            |                                | mV                         |

| DGL(RCH)                 | Deglitch time                                                                 | VBAT falling below VRCH, tFALL:                                                                                                                    |                                                      | 32                             |                                | ms                             |                            |

| / <sub>DETECT</sub>      | Battery detection threshold                                                   | During battery detection source c                                                                                                                  | ycle                                                 |                                | 3.3                            |                                | V                          |

|                          |                                                                               | During battery detection sink cycl                                                                                                                 | е                                                    |                                | 3.0                            |                                |                            |

| DETECT                   | Battery detection current before charge done (sink current)                   | Termination enabled (EN_TERM                                                                                                                       | = 1)                                                 |                                | 2.5                            |                                | mA                         |

| DETECT                   | Battery detection time                                                        | Termination enabled (EN_TERM                                                                                                                       | = 1)                                                 |                                | 250                            |                                | ms                         |

| V <sub>IH</sub>          | PSEL, CD Input high logic level                                               |                                                                                                                                                    |                                                      | 1.3                            |                                |                                | V                          |

| V <sub>IL</sub>          | PSEL, CD Input low logic level                                                |                                                                                                                                                    |                                                      |                                |                                | 0.4                            | V                          |

| NPUT CURR                | ENT LIMITING                                                                  |                                                                                                                                                    |                                                      |                                |                                |                                |                            |

|                          |                                                                               |                                                                                                                                                    | I <sub>USBLIM</sub> = USB100                         | 90                             | 95                             | 100                            |                            |

|                          |                                                                               |                                                                                                                                                    | I <sub>USBLIM</sub> = USB500                         | 450                            | 475                            | 500                            |                            |

|                          |                                                                               | USB charge mode, V <sub>USB</sub> = 5V,                                                                                                            | I <sub>USBLIM</sub> = USB150                         | 135                            | 142.5                          | 150                            |                            |

| I <sub>IN_USB</sub>      | Input current limit threshold (USB input)                                     | DC Current pulled from SW                                                                                                                          | I <sub>USBLIM</sub> = USB900                         | 800                            | 850                            | 900                            | mA                         |

|                          |                                                                               |                                                                                                                                                    | I <sub>USBLIM</sub> = USB800                         | 700                            | 750                            | 800                            |                            |

|                          |                                                                               |                                                                                                                                                    | I <sub>USBLIM</sub> = 1.5A                           | 1250                           | 1400                           | 1500                           |                            |

|                          |                                                                               | IN charge mode, V <sub>IN</sub> = 5V,                                                                                                              | I <sub>INLIM</sub> = 1.5A                            | 1.35                           | 1.5                            | 1.65                           |                            |

| IN_IN                    | Input current limit threshold (IN input)                                      | DC Current pulled from SW                                                                                                                          | I <sub>INLIM</sub> = 2.5A                            | 2.3                            | 2.5                            | 2.8                            | Α                          |

| V <sub>IN_DPM</sub>      | Input based DPM threshold range                                               | Charge mode, programmable via                                                                                                                      | _                                                    | 4.2                            |                                | 4.76                           | V                          |

| * IN_DPM                 | V <sub>IN DPM</sub> threshold accuracy                                        | Charge mode, programmable via                                                                                                                      | 1 O, Dour Inputo                                     | - 2                            |                                | +2%                            | •                          |

| VDDV BIAS E              | REGULATOR                                                                     |                                                                                                                                                    |                                                      |                                |                                | . 2,0                          |                            |

|                          |                                                                               | V > E 45V                                                                                                                                          |                                                      | -                              | F 0                            | E 45                           | V                          |

| V <sub>DRV</sub>         | Internal bias regulator voltage                                               | V <sub>SUPPLY</sub> > 5.45V                                                                                                                        |                                                      | 5                              | 5.2                            | 5.45                           |                            |

| DRV                      | DRV output current                                                            | 1 11 11 11 11 11 11 11 11 11 11 11 11 1                                                                                                            | 10                                                   |                                | 450                            | mA                             |                            |

| V <sub>DO_DRV</sub>      | DRV Dropout voltage (V <sub>SUPPLY</sub> - V <sub>DRV</sub> )                 | I <sub>SUPPLY</sub> = 1A, V <sub>SUPPLY</sub> = 5V, I <sub>DRV</sub>                                                                               | = 10mA                                               |                                |                                | 450                            | mV                         |

| STATUS OUT               | PUT ( STAT, INT)                                                              |                                                                                                                                                    |                                                      |                                |                                |                                |                            |

| V <sub>OL</sub>          | Low-level output saturation voltage                                           | I <sub>O</sub> = 10mA, sink current                                                                                                                |                                                      |                                |                                | 0.4                            | V                          |

| ІН                       | High-level leakage current                                                    | V <sub>STAT</sub> = V <sub>INT</sub> = 5V                                                                                                          |                                                      |                                |                                | 1                              | μA                         |

| PROTECTION               | N .                                                                           |                                                                                                                                                    |                                                      |                                |                                |                                |                            |

| V <sub>UVLO</sub>        | IC active threshold voltage                                                   | V <sub>IN</sub> rising                                                                                                                             |                                                      | 3.6                            | 3.8                            | 4                              | V                          |

| V <sub>UVLO_HYS</sub>    | IC active hysteresis                                                          | V <sub>IN</sub> falling from above V <sub>UVLO</sub>                                                                                               |                                                      | 120                            | 150                            |                                | mV                         |

| $V_{SLP}$                | Sleep-mode entry threshold, V <sub>SUPPLY</sub> -V <sub>BAT</sub>             | $2.0V \le V_{BAT} \le V_{BATREG}$ , $V_{IN}$ fallin                                                                                                | g                                                    | 0                              | 40                             | 100                            | mV                         |

| SLP_EXIT                 | Sleep-mode exit hysteresis                                                    | $2.0V \leq V_{BAT} \leq V_{BATREG}$                                                                                                                | 2.0V ≤V <sub>BAT</sub> ≤V <sub>BATREG</sub>          |                                | 100                            | 175                            | mV                         |

|                          | Deglitch time for supply rising above V <sub>SLP</sub> +V <sub>SLP_EXIT</sub> | Rising voltage, 2mV over drive, t <sub>F</sub>                                                                                                     | RISE = 100ns                                         |                                | 30                             |                                | ms                         |

| .,                       | Bad source detection threshold                                                | After Bad Source Detection completes  During Bad Source Detection                                                                                  |                                                      |                                | V <sub>IN_DPM</sub><br>- 80 mV |                                | V                          |

| V <sub>BAD_</sub> SOURCE | bad source detection timeshold                                                |                                                                                                                                                    |                                                      |                                | V <sub>IN_DPM</sub><br>+ 80 mV |                                | V                          |

| DGL(BSD)                 | Deglitch on bad source detection                                              |                                                                                                                                                    |                                                      |                                | 32                             |                                | ms                         |

|                          |                                                                               | USB, V <sub>USB</sub> Rising                                                                                                                       |                                                      | 6.3                            | 6.5                            | 6.7                            |                            |

| V <sub>OVP</sub>         | Input supply OVP threshold voltage                                            | IN, V <sub>IN</sub> Rising (BQ24160/1/1B/3)                                                                                                        |                                                      | 10.3                           | 10.5                           | 10.7                           | V                          |

|                          |                                                                               | IN, V <sub>IN</sub> Rising (BQ24168)                                                                                                               |                                                      | 6.3                            | 6.5                            | 6.7                            |                            |

| V <sub>OVP(HYS)</sub>    | V <sub>OVP</sub> hysteresis                                                   | Supply falling from V <sub>OVP</sub>                                                                                                               |                                                      |                                | 100                            |                                | mV                         |

| V <sub>BOVP</sub>        | Battery OVP threshold voltage                                                 | V <sub>BAT</sub> threshold over V <sub>OREG</sub> to turn                                                                                          | n off charger during charge                          | 1.025 ×<br>V <sub>BATREG</sub> | 1.05 ×<br>V <sub>BATREG</sub>  | 1.075 ×<br>V <sub>BATREG</sub> | V                          |

|                          | V <sub>BOVP</sub> hysteresis                                                  | Lower limit for V <sub>BAT</sub> falling from above V <sub>BOVP</sub>                                                                              |                                                      |                                | 1                              |                                | % of<br>V <sub>BATRE</sub> |

| DGL(BOVP)                | Battery OVP deglitch                                                          | BOVP fault shown in register once t <sub>DGL(BOVP)</sub> expires. Buck converter shut down immediately when V <sub>BAT</sub> > V <sub>BATOVP</sub> |                                                      |                                | 1                              |                                | ms                         |

| V <sub>BATUVLO</sub>     | Battery undervoltage lockout threshold                                        | V <sub>BAT</sub> rising, 100mV hysteresis                                                                                                          |                                                      |                                | 2.5                            |                                | V                          |

| LIMIT                    | Cycle-by-cycle current limit                                                  | V <sub>SYS</sub> shorted                                                                                                                           | 4.1                                                  | 4.9                            | 5.6                            | Α                              |                            |

| T <sub>SHTDWN</sub>      | Thermal trip                                                                  | -                                                                                                                                                  |                                                      |                                | 165                            |                                | °C                         |

| J J.                     | Thermal hysteresis                                                            |                                                                                                                                                    |                                                      |                                | 10                             |                                | -                          |

|                          | ,                                                                             | Charge current begins to cut off                                                                                                                   |                                                      |                                | 120                            |                                | °C                         |

## 7.5 Electrical Characteristics (continued)

Circuit of  $\boxtimes$  9-1,  $V_{SUPPLY} = V_{USB}$  or  $V_{IN}$  (whichever is supplying the IC),  $V_{UVLO} < V_{SUPPLY} < V_{OVP}$  and  $V_{SUPPLY} > V_{BAT} + V_{SLP}$ ,  $T_J = -40^{\circ}C$  - 125°C and  $T_J = 25^{\circ}C$  for typical values (unless otherwise noted)

|                         | PARAMETER                                          | TEST CONDITIONS                                           | MIN   | TYP  | MAX  | UNIT              |

|-------------------------|----------------------------------------------------|-----------------------------------------------------------|-------|------|------|-------------------|

|                         | Safety timer accuracy                              | (BQ24160/1/1B/3 Only)                                     | - 20% |      | 20%  |                   |

| PWM                     |                                                    |                                                           |       |      |      |                   |

|                         | lata and the second blocking MOOFFT and a sixteen  | I <sub>IN_LIMIT</sub> = 500mA, Measured from USB to PMIDU |       | 95   | 175  |                   |

|                         | Internal top reverse blocking MOSFET on-resistance | I <sub>IN_LIMIT</sub> = 500mA, Measured from IN to PMIDI  |       | 45   | 80   | mΩ                |

|                         | Internal top N-channel Switching MOSFET on-        | Measured from PMIDU to SW                                 |       | 100  | 175  | 0                 |

|                         | resistance                                         | Measured from PMIDI to SW                                 |       | 65   | 110  | mΩ                |

|                         | Internal bottom N-channel MOSFET on-resistance     | Measured from SW to PGND                                  |       | 65   | 115  | mΩ                |

| fosc                    | Oscillator frequency                               |                                                           | 1.35  | 1.50 | 1.65 | MHz               |

| D <sub>MAX</sub>        | Maximum duty cycle                                 |                                                           |       | 95%  |      |                   |

| D <sub>MIN</sub>        | Minimum duty cycle                                 |                                                           | 0%    |      |      |                   |

| BATTERY-PA              | ACK NTC MONITOR                                    |                                                           |       |      |      |                   |

| V <sub>HOT</sub>        | High temperature threshold                         | V <sub>TS</sub> falling                                   | 29.7  | 30   | 30.5 | 0/1/              |

| V <sub>HYS(HOT)</sub>   | Hysteresis on high threshold                       | V <sub>TS</sub> rising                                    |       | 1    |      | %V <sub>DRV</sub> |

| V <sub>WARM</sub>       | High temperature threshold                         | V <sub>TS</sub> falling                                   | 37.9  | 38.3 | 39.6 | 0/1/              |

| V <sub>HYS(WARM)</sub>  | Hysteresis on high threshold                       | V <sub>TS</sub> rising                                    |       | 1    |      | %V <sub>DRV</sub> |

| V <sub>COOL</sub>       | Low temperature threshold                          | V <sub>TS</sub> falling                                   | 56    | 56.5 | 56.9 | 0/1/              |

| V <sub>HYS(COOL)</sub>  | Hysteresis on low threshold                        | V <sub>TS</sub> rising                                    |       | 1    |      | %V <sub>DRV</sub> |

| V <sub>COLD</sub>       | Low temperature threshold                          | V <sub>TS</sub> falling                                   | 59.5  | 60   | 60.4 | 0/1/              |

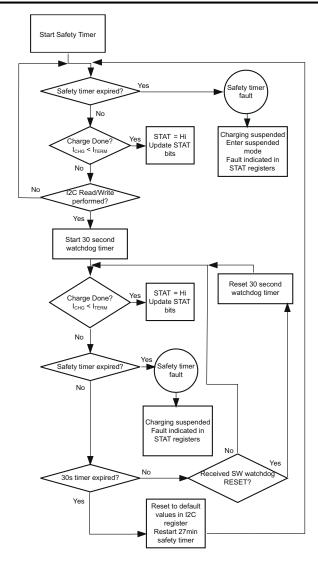

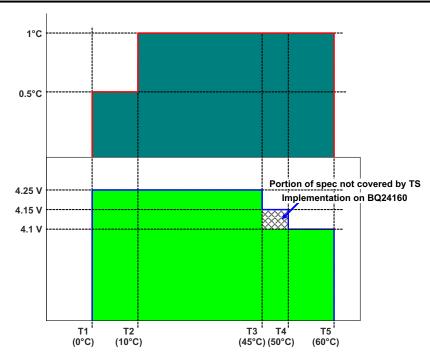

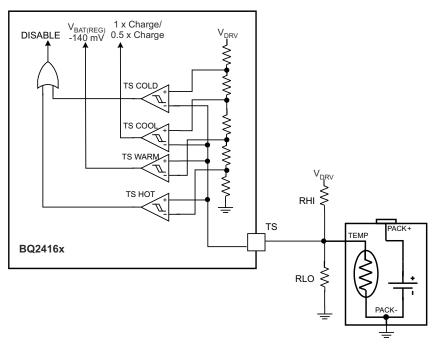

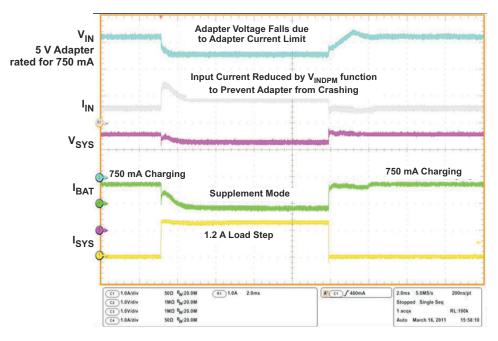

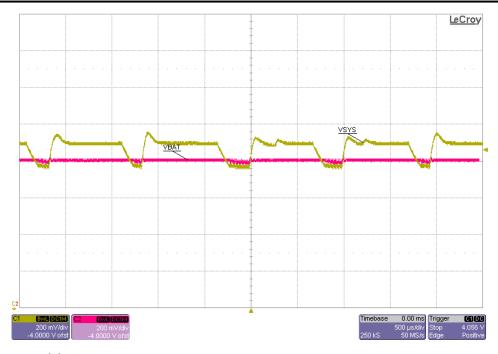

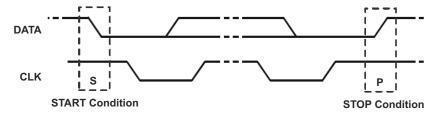

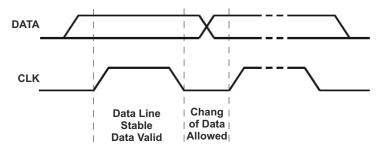

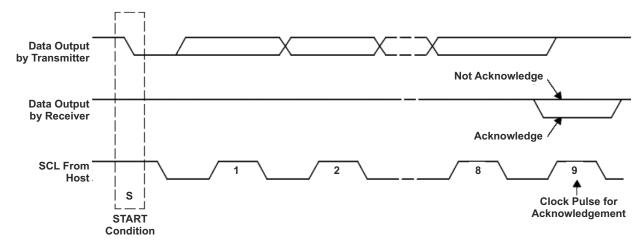

| V <sub>HYS(COLD)</sub>  | Hysteresis on low threshold                        | V <sub>TS</sub> rising                                    |       | 1    |      | %V <sub>DRV</sub> |