Everywhere you imagine.

# **RENESAS 8-BIT CISC SINGLE-CHIP MICROCOMPUTER** 740 FAMILY / 38000 SERIES mound

Before using this material, please visit our website to confirm that this is the most current document available.

Rev. 1.00 Revision date: Jan 14, 2005

0

~

RenesasTechnology www.renesas.com

#### Keep safety first in your circuit designs!

Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

- 2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/ or the country of destination is prohibited.

8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

#### **REVISION HISTORY**

#### 3804 Group (Spec. H) User's Manual

| Rev.  | Date         |      | Description          |

|-------|--------------|------|----------------------|

| 1.69. | Dale         | Page | Summary              |

| 1.00  | lan 14, 2005 |      |                      |

| 1.00  | Jan 14, 2005 |      | First edition issued |

|       |              |      | (4.14)               |

### **BEFORE USING THIS USER'S MANUAL**

This user's manual consists of the following three chapters. Refer to the chapter appropriate to your conditions, such as hardware design or software development.

#### 1. Organization

#### • CHAPTER 1 HARDWARE

This chapter describes features of the microcomputer and operation of each peripheral function.

#### CHAPTER 2 APPLICATION

This chapter describes usage and application examples of peripheral functions, based mainly on setting examples of relevant registers.

#### • CHAPTER 3 APPENDIX

This chapter includes necessary information for systems development using the microcomputer, such as the electrical characteristics, the notes, and the list of registers.

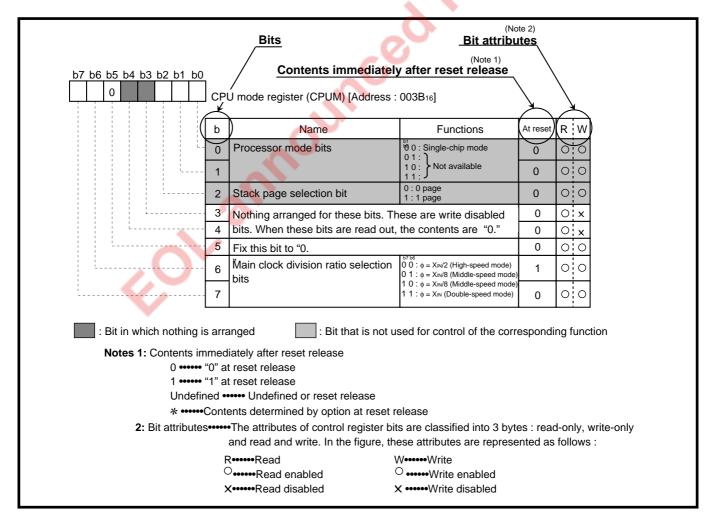

#### 2. Structure of Register

The figure of each register structure describes its functions, contents at reset, and attributes as follows:

#### 3. Supplementary

For details of related development tools and documents, refer to web page "3804 Group" on our website (http://www.renesas.com/eng/products/mpumcu/8bit/38000/index.html).

## **Table of contents**

#### CHAPTER 1 HARDWARE

| DESCRIPTION                                 | 1-2   |

|---------------------------------------------|-------|

| FEATURES                                    | 1-2   |

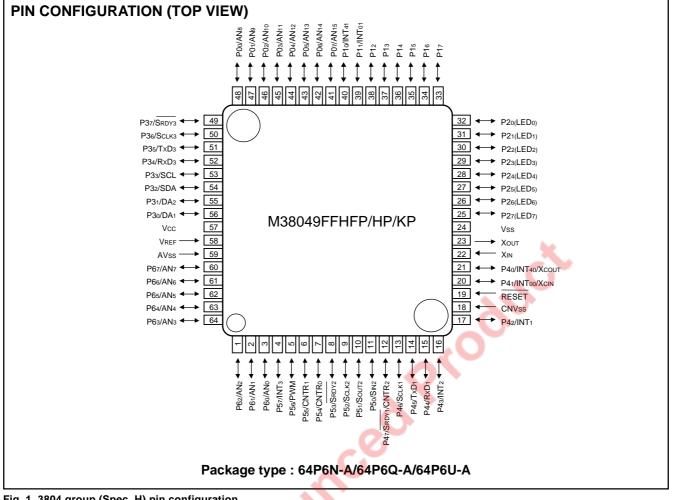

| PIN CONFIGURATION                           | 1-3   |

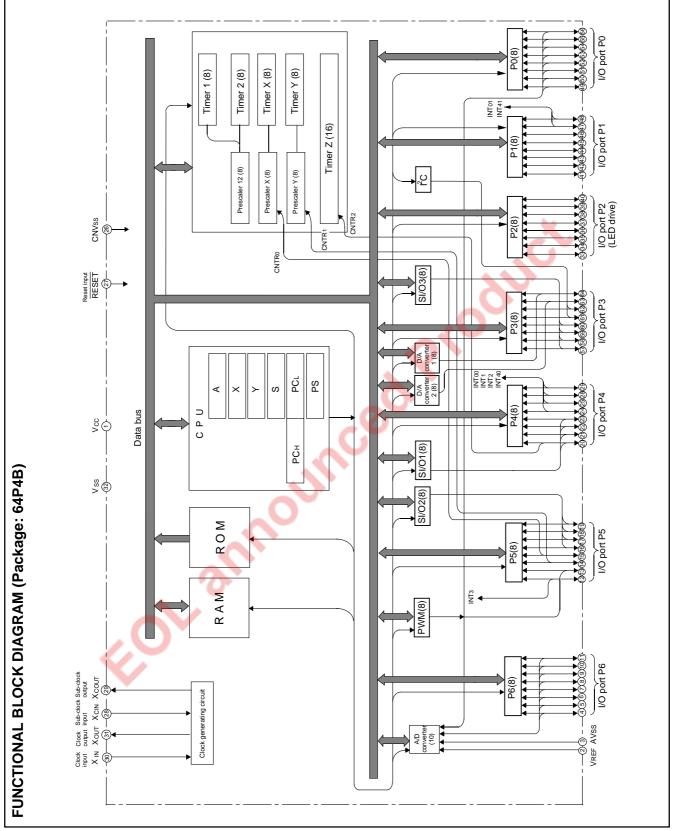

| FUNCTIONAL BLOCK                            | 1-4   |

| PIN DESCRIPTION                             | 1-5   |

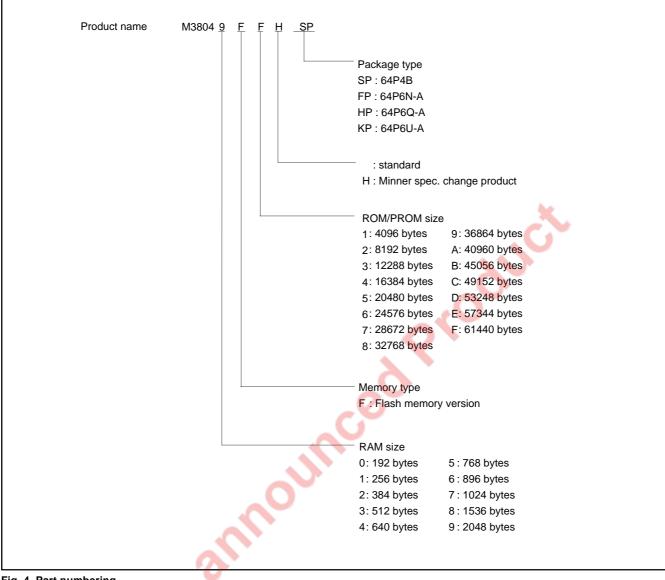

| PART NUMBERING                              |       |

| GROUP EXPANSION                             |       |

| Memory Size                                 |       |

| Packages                                    |       |

| FUNCTIONAL DESCRIPTION                      |       |

| CENTRAL PROCESSING UNIT (CPU)               | 1-8   |

| MEMORY                                      |       |

| I/O PORTS                                   |       |

| INTERRUPTS                                  |       |

| TIMERS                                      |       |

| SERIAL INTERFACE                            |       |

| PULSE WIDTH MODULATION (PWM)                |       |

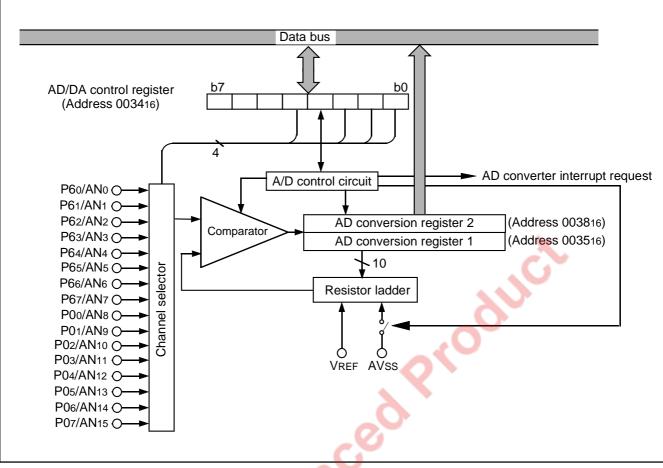

| A/D CONVERTER                               |       |

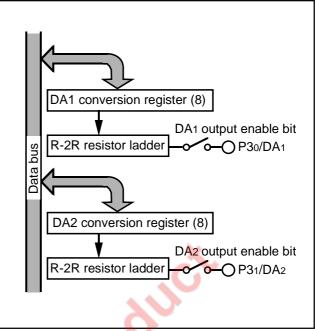

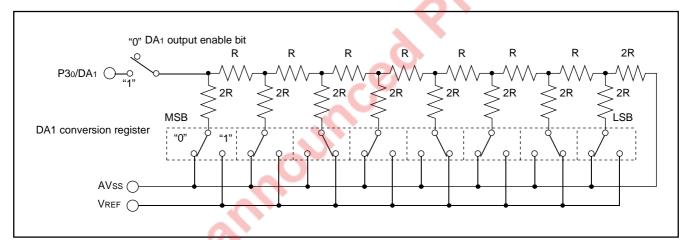

| D/A CONVERTER                               |       |

|                                             | 1-59  |

| MULTI-MASTER I <sup>2</sup> C-BUS INTERFACE |       |

| RESET CIRCUIT                               |       |

| CLOCK GENERATING CIRCUIT                    | 1-76  |

| FLASH MEMORY MODE                           |       |

| NOTES ON PROGRAMMING                        |       |

| NOTES ON USAGE                              |       |

| FUNCTIONAL DESCRIPTION SUPPLEMENT           |       |

| Interrupt                                   |       |

| Timing After Interrupt                      |       |

| A/D Converter                               | 1-103 |

|                                             |       |

#### **CHAPTER 2 APPLICATION**

| 2.1 I/O port                  |                |

|-------------------------------|----------------|

|                               |                |

| 2.1.2 Relevant registers      |                |

| 2.1.3 Port Pi pull-up control | l register 2-5 |

| 2.1.4 Terminate unused pin    | s              |

| 2.1.5 Notes on I/O port       |                |

| 2.1.6 Termination of unused   | d pins         |

| 2.2 Interrupt                 |                |

| 2.2.1 Memory map              |                |

|                               |                |

| 2.2.3 Interrupt source        |                |

| 2.2.4 Interrupt operation     |                |

|                               |                |

| 2.2.5 Interrupt control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2.6 INT interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-19                                                                                                                                                                                                                                            |

| 2.2.7 Notes on interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-20                                                                                                                                                                                                                                            |

| 2.3 Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                 |

| 2.3.1 Memory map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-22                                                                                                                                                                                                                                            |

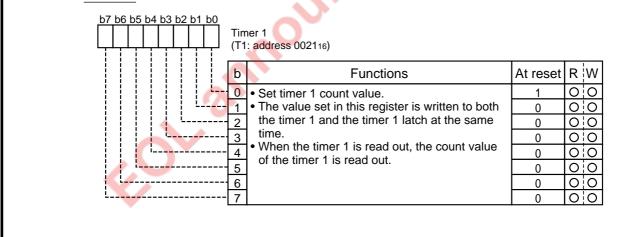

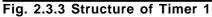

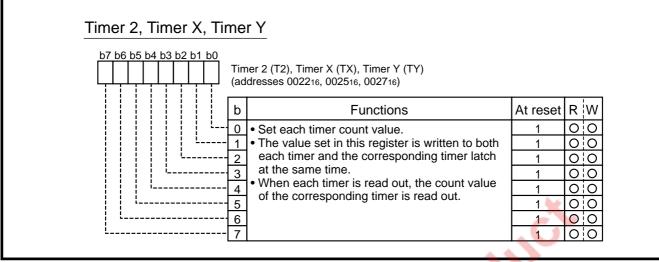

| 2.3.2 Relevant registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-23                                                                                                                                                                                                                                            |

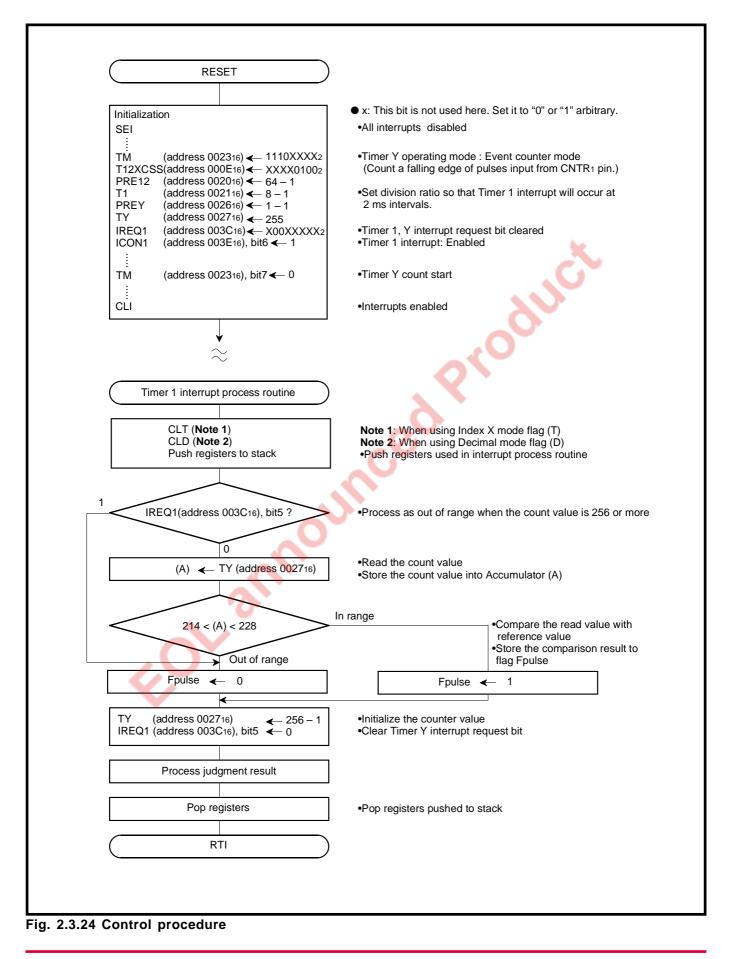

| 2.3.3 Timer application examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-32                                                                                                                                                                                                                                            |

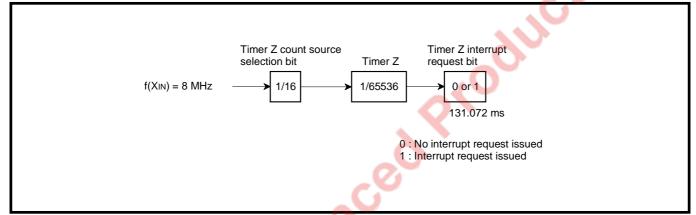

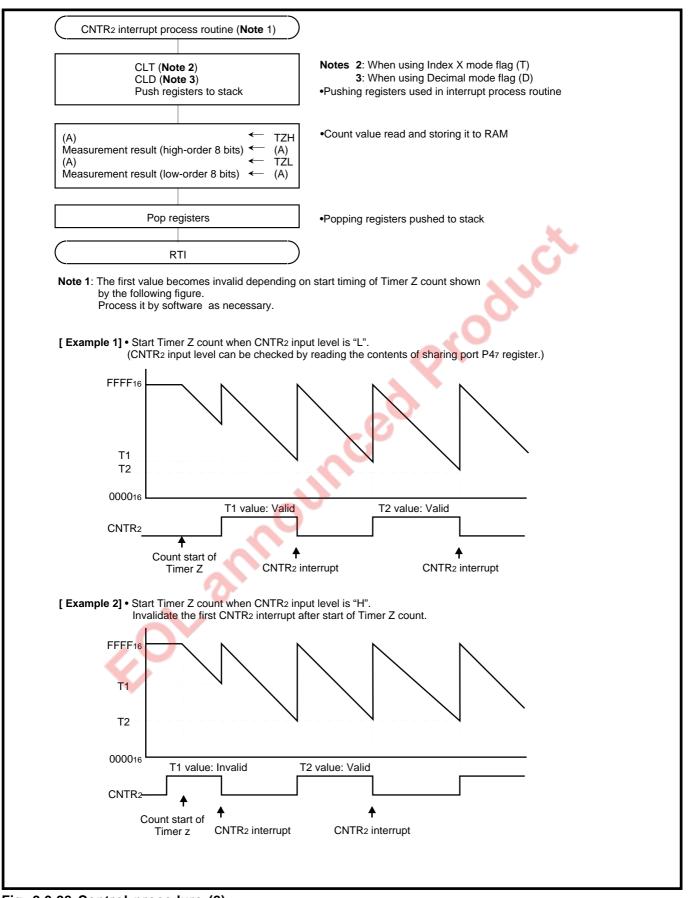

| 2.3.4 Notes on timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-45                                                                                                                                                                                                                                            |

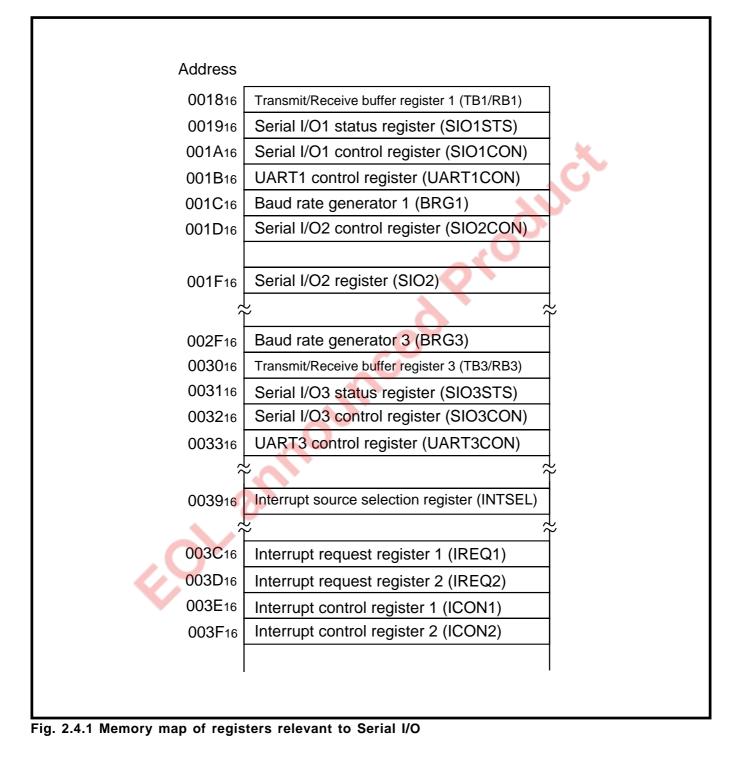

| 2.4 Serial interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-47                                                                                                                                                                                                                                            |

| 2.4.1 Memory map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                 |

| 2.4.2 Relevant registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                 |

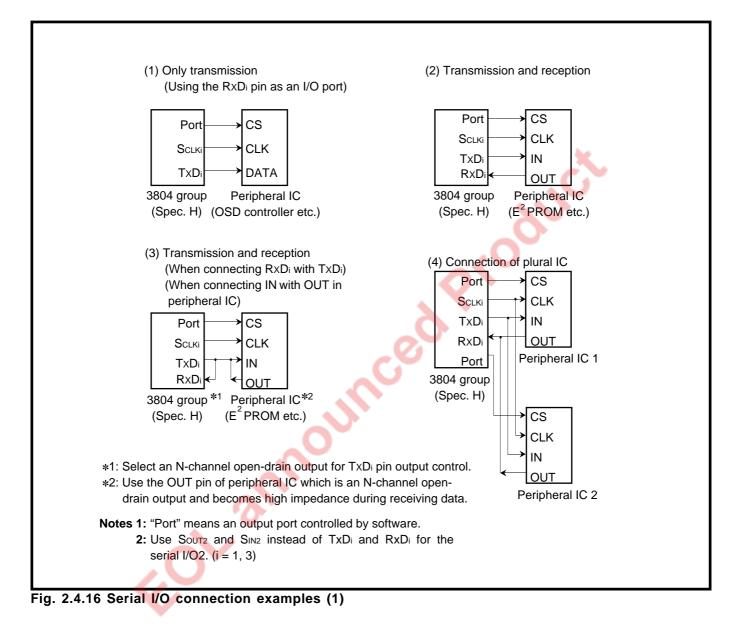

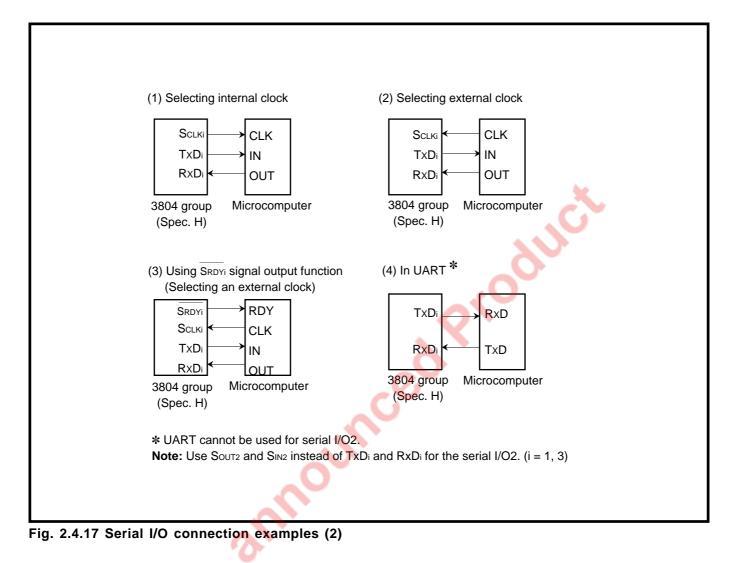

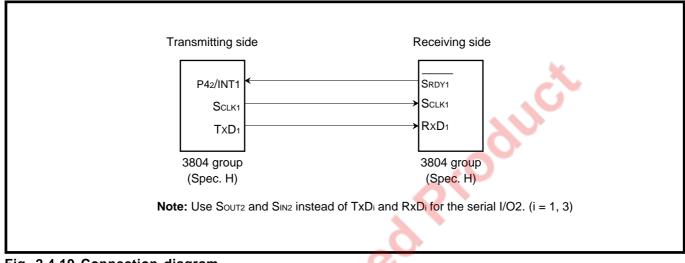

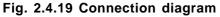

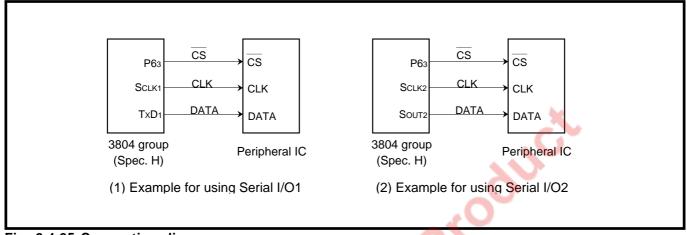

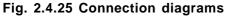

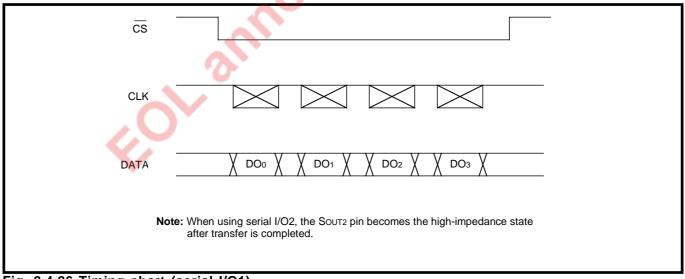

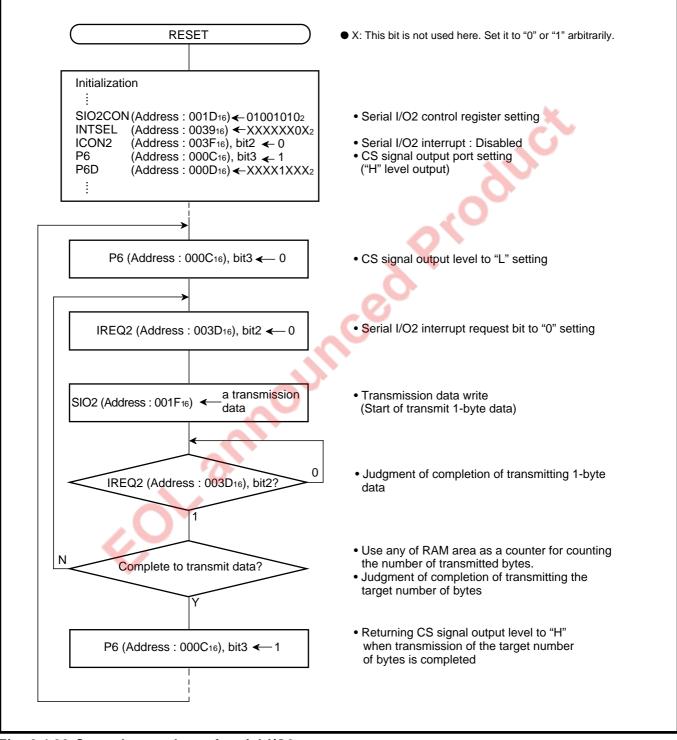

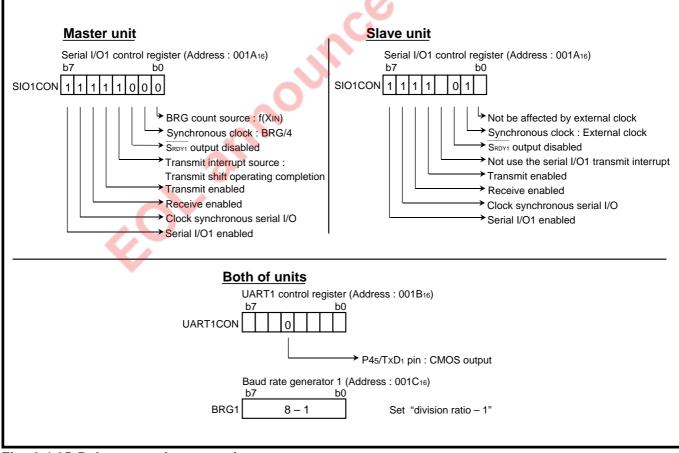

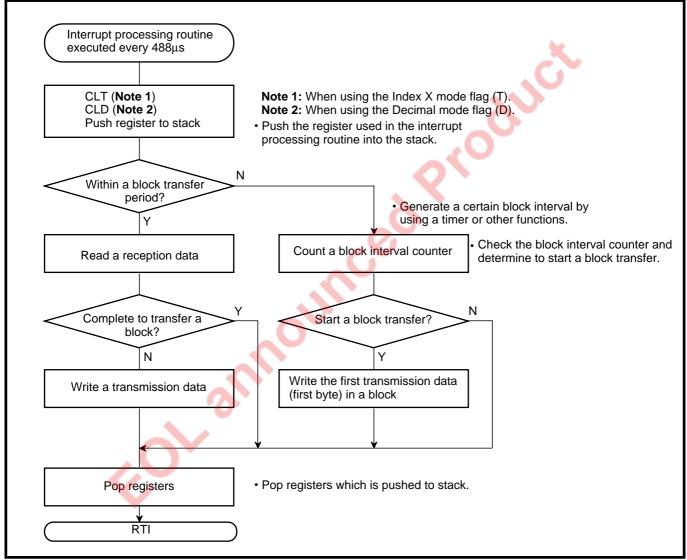

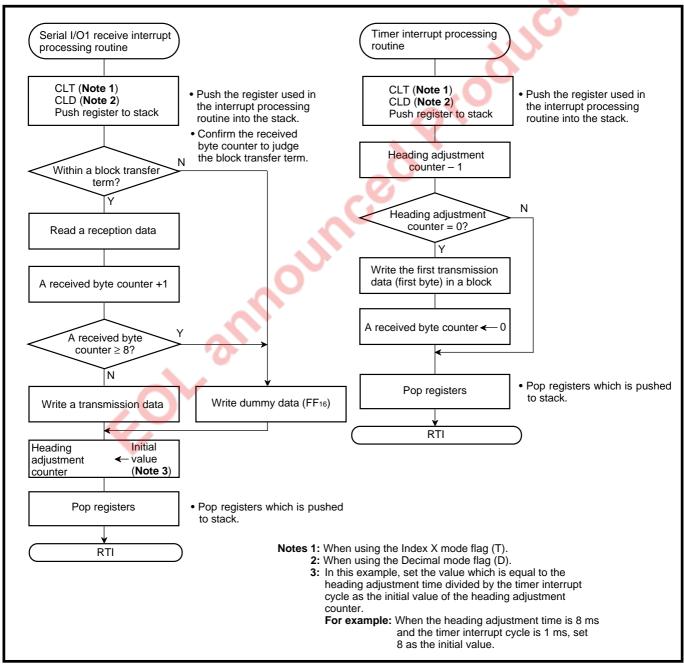

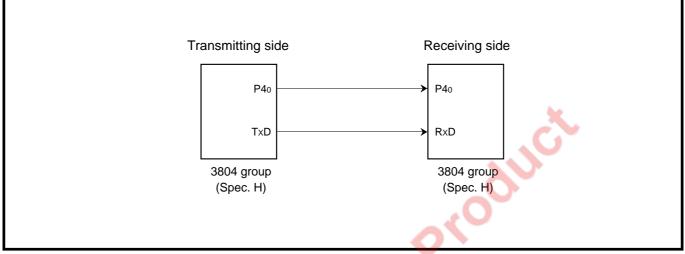

| 2.4.3 Serial I/O connection examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-56                                                                                                                                                                                                                                            |

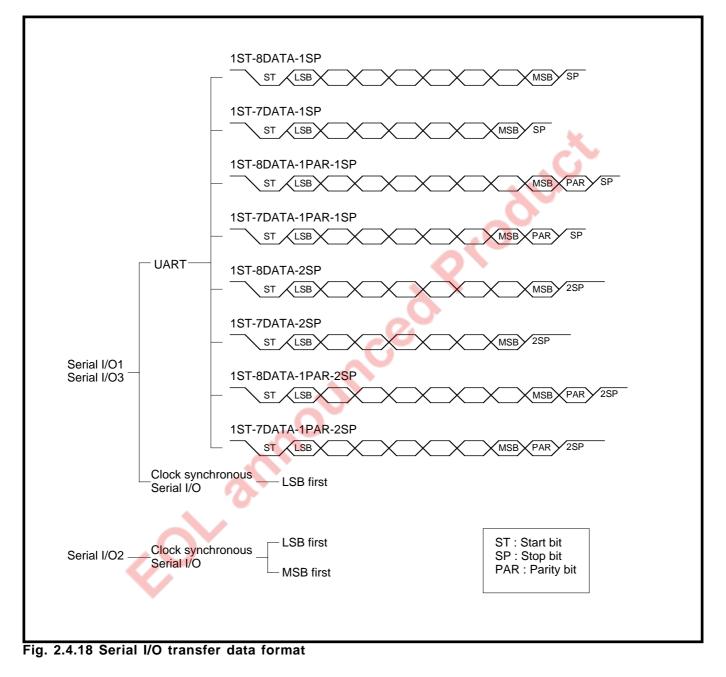

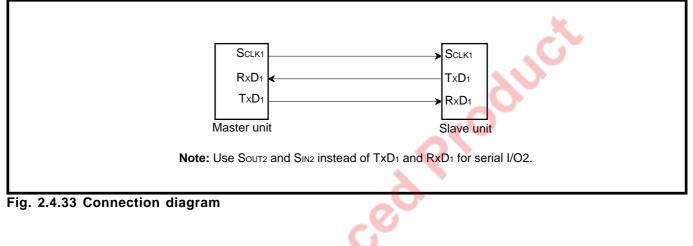

| 2.4.4 Setting of serial I/O transfer data format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-58                                                                                                                                                                                                                                            |

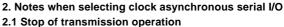

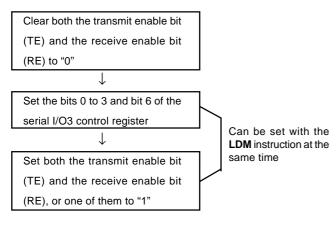

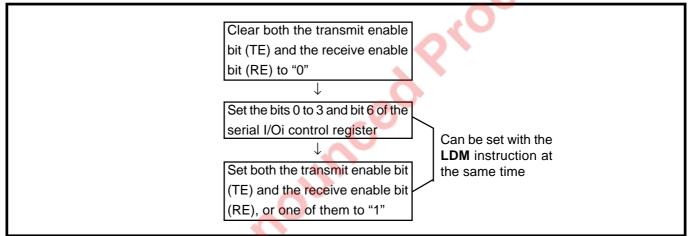

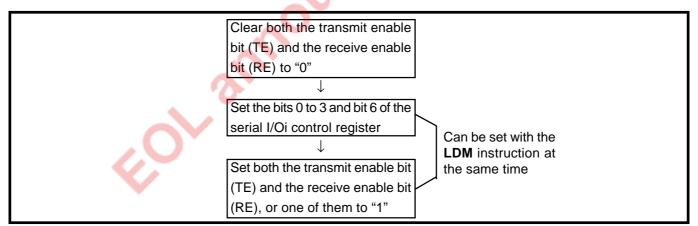

| 2.4.5 Serial I/O1, serial I/O3 operation: stop and initialize                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                 |

| 2.4.6 Serial I/O pin function and selection method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-60                                                                                                                                                                                                                                            |

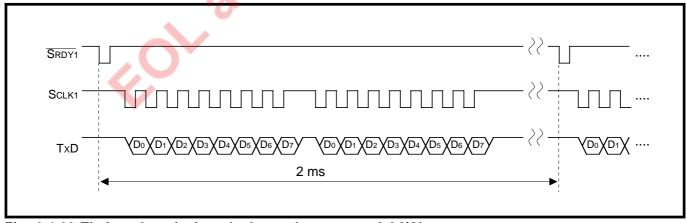

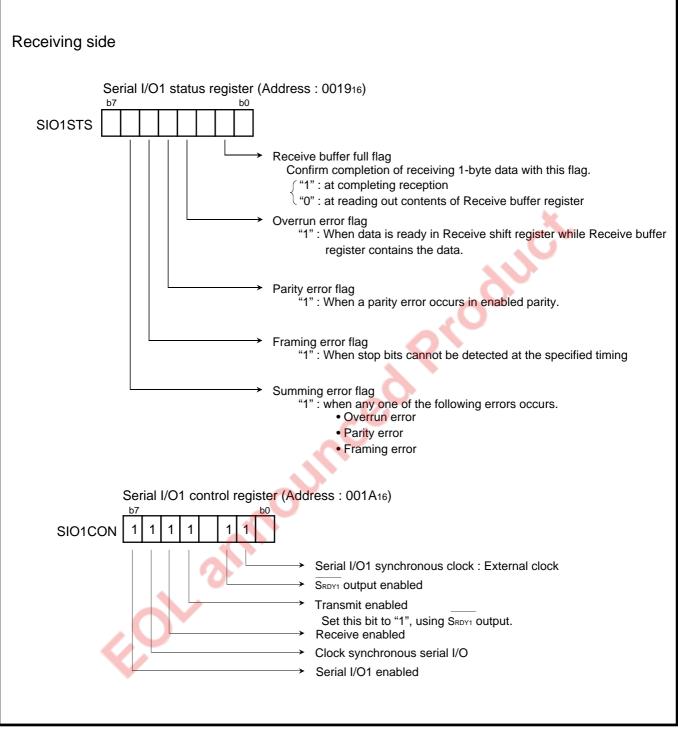

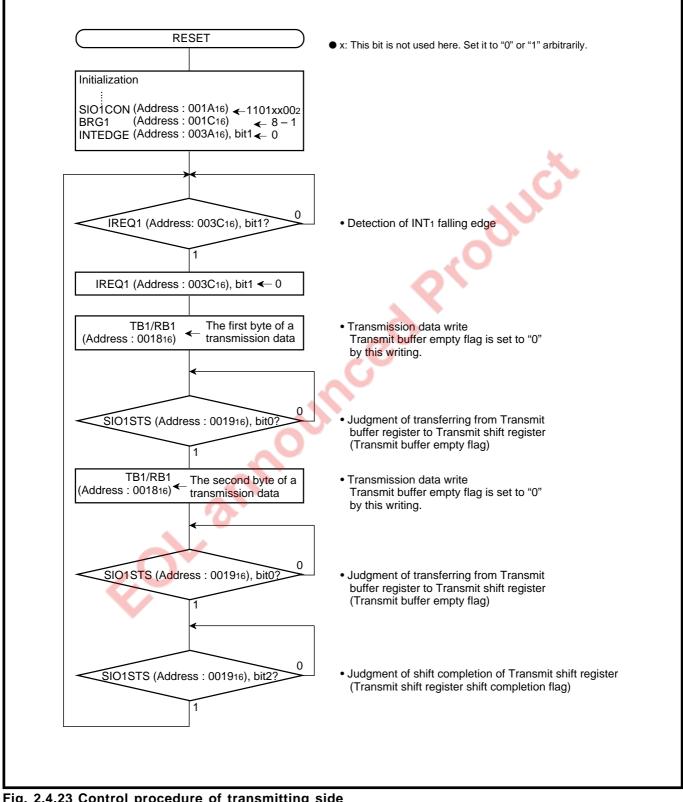

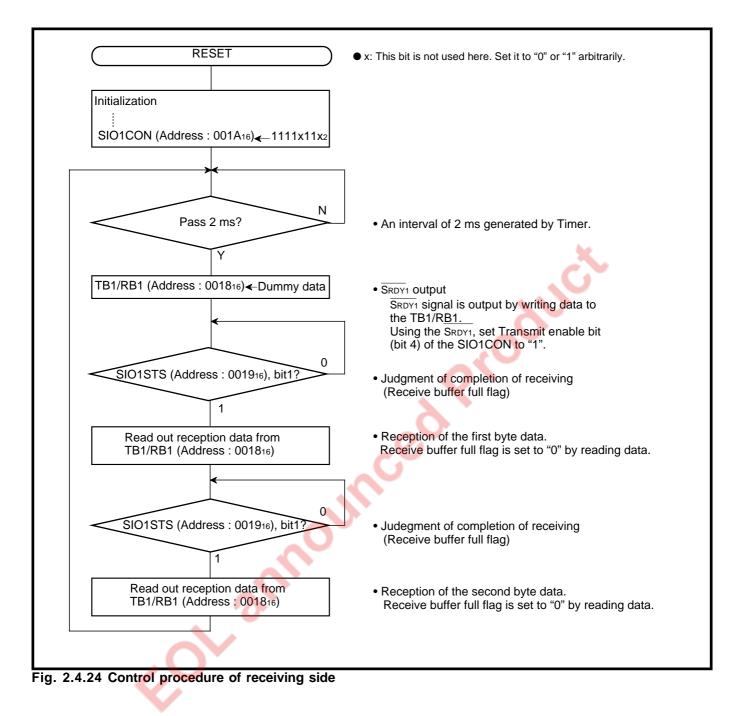

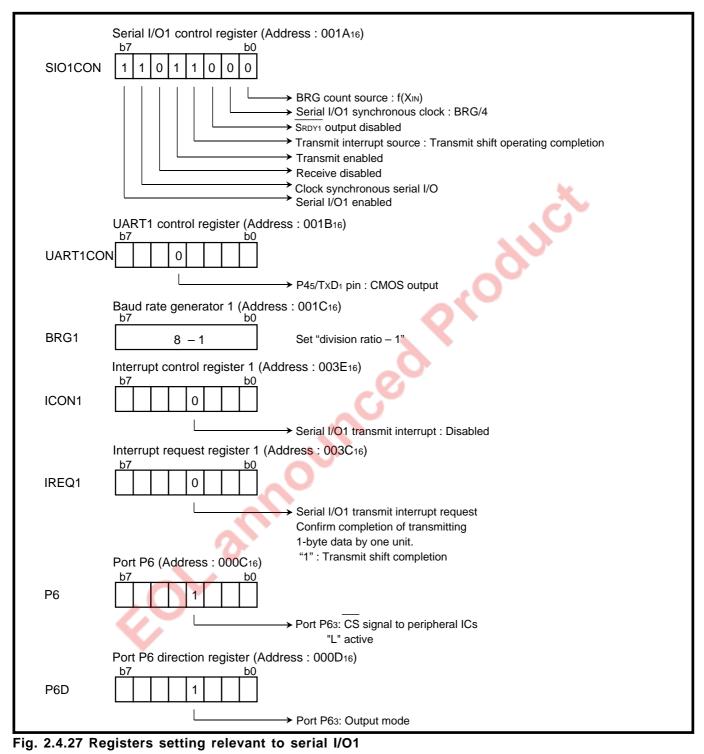

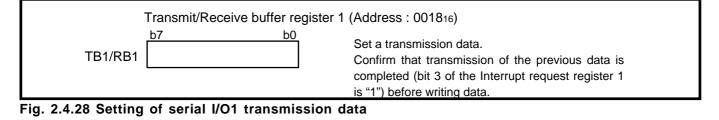

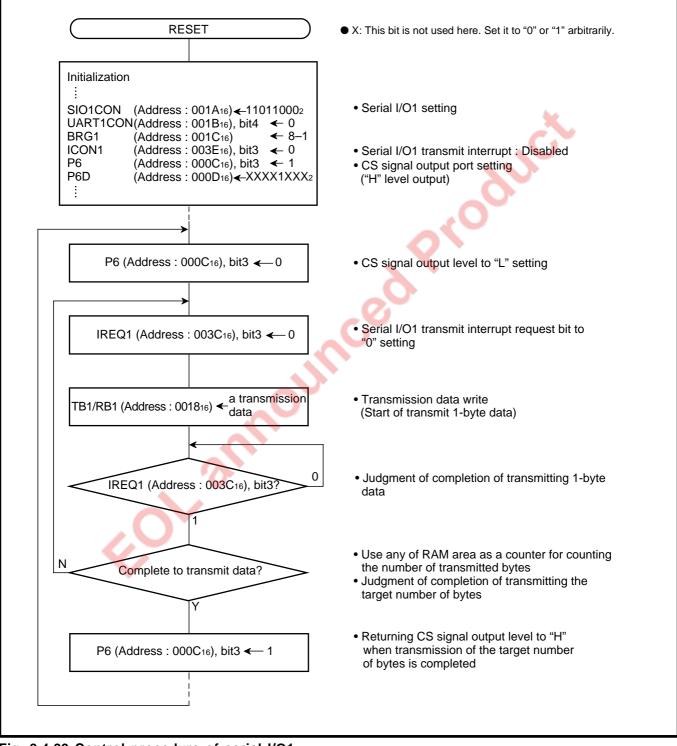

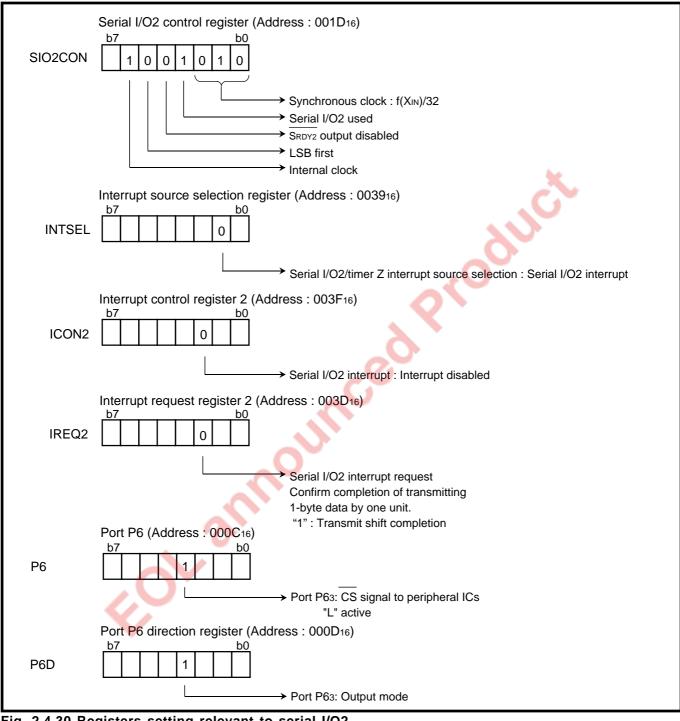

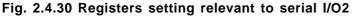

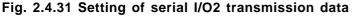

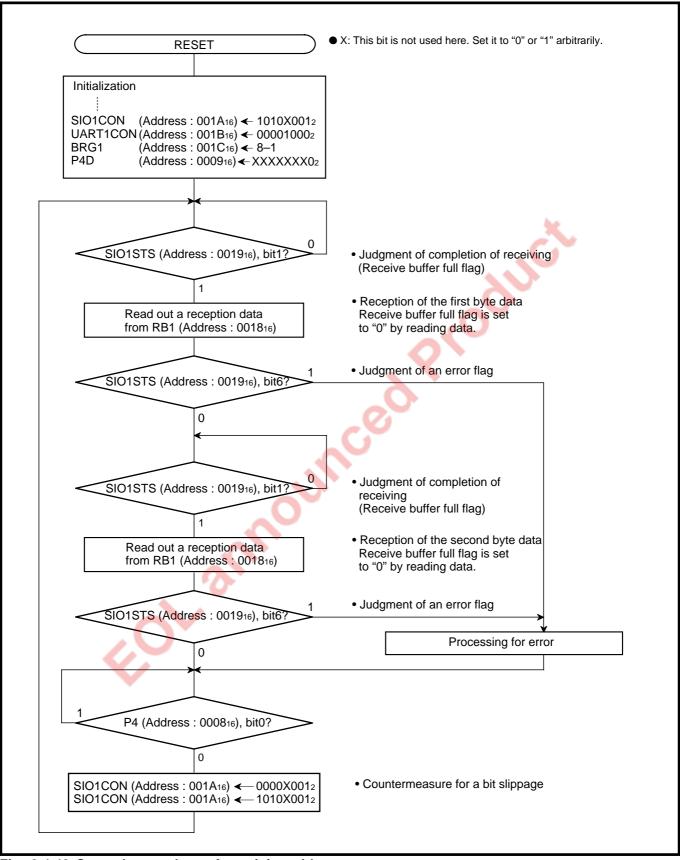

| 2.4.7 Serial I/O application examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-61                                                                                                                                                                                                                                            |

| 2.4.8 Notes on serial interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-81                                                                                                                                                                                                                                            |

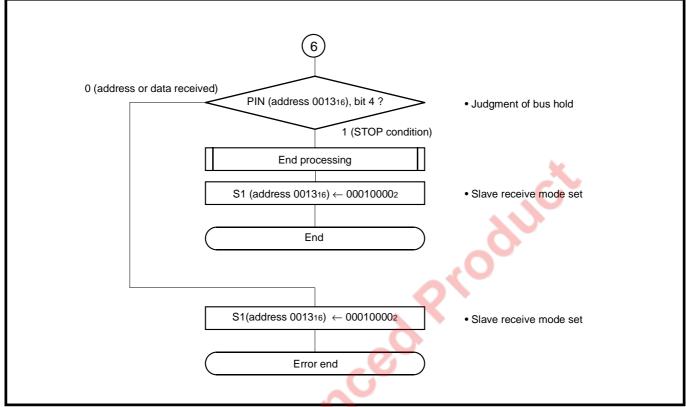

| 2.5 Multi-master I <sup>2</sup> C-BUS interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                 |

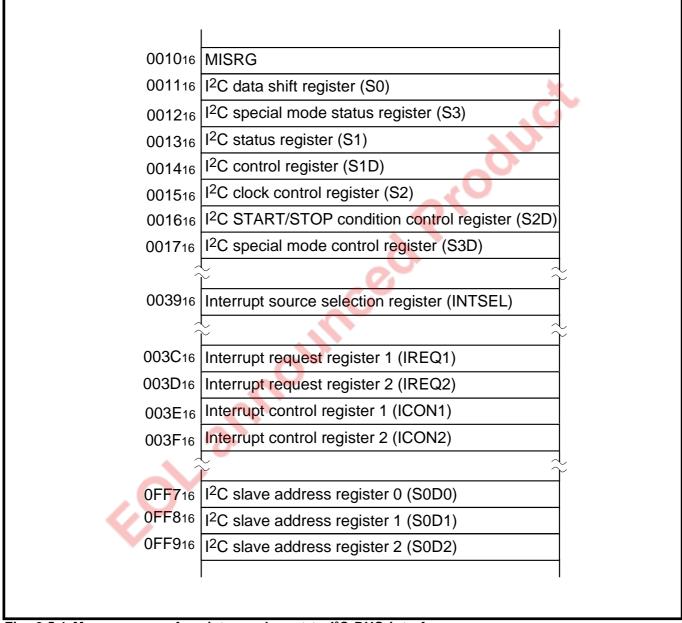

| 2.5.1 Memory map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                 |

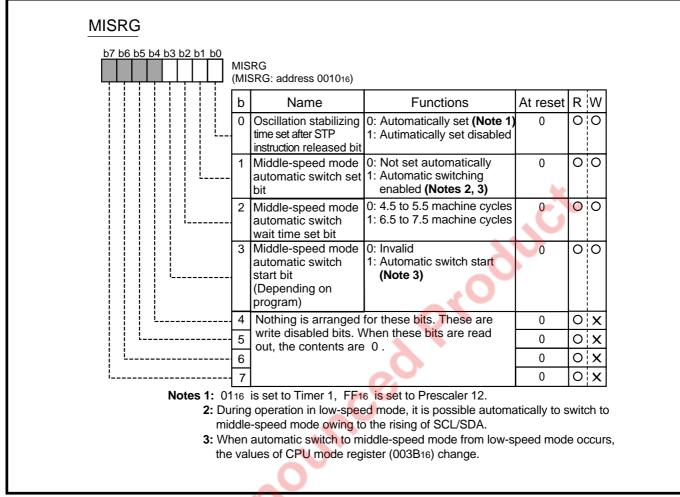

| 2.5.2 Relevant registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                 |

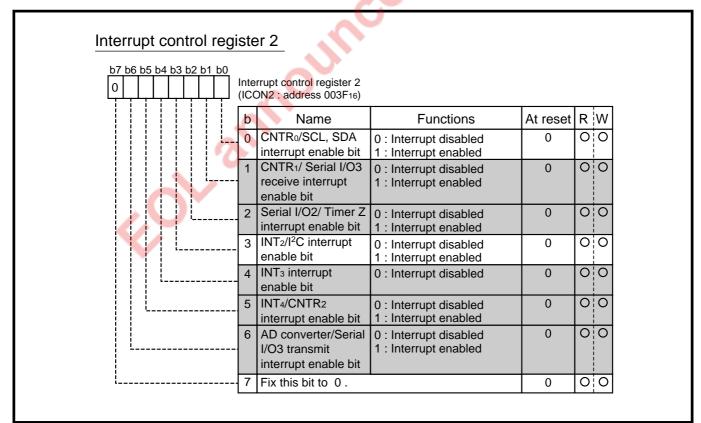

| 2.5.3 I <sup>2</sup> C-BUS overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-94                                                                                                                                                                                                                                            |

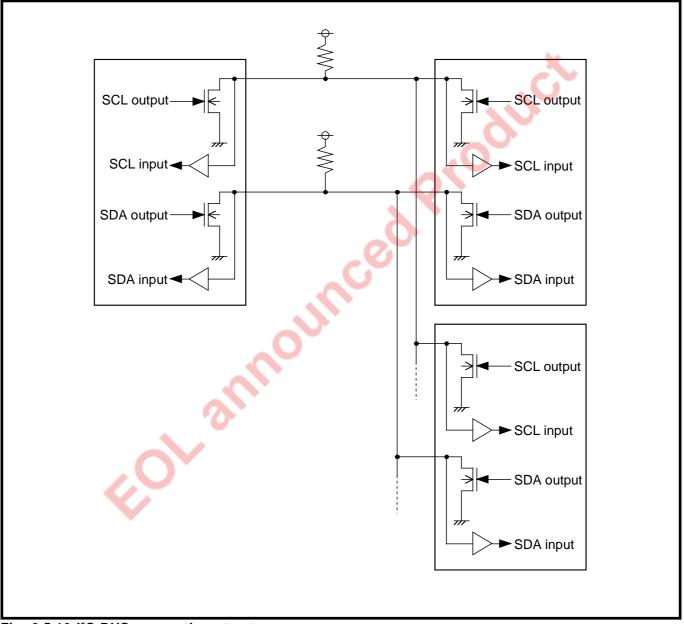

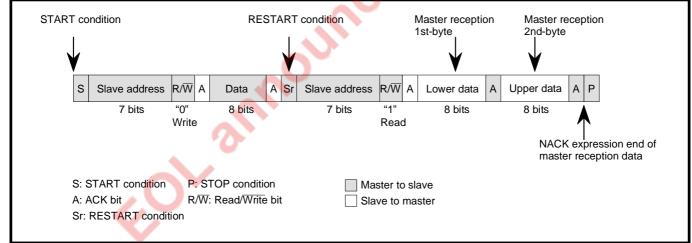

| 2.5.4 Communication format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-95                                                                                                                                                                                                                                            |

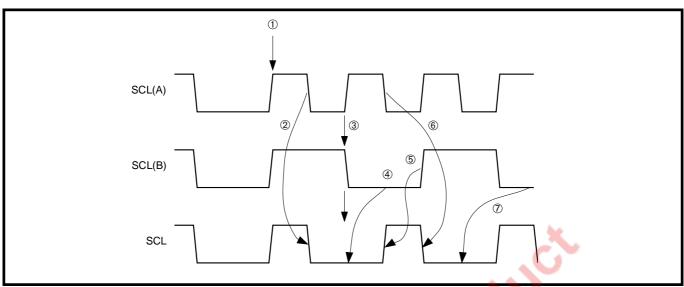

| 2.5.5 Synchronization and arbitration lost                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-96                                                                                                                                                                                                                                            |

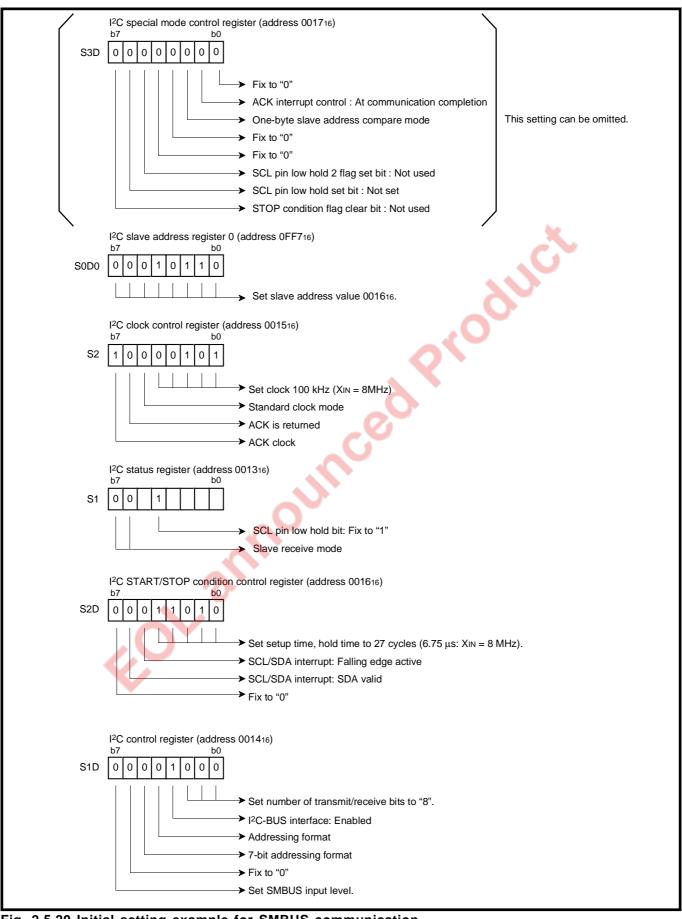

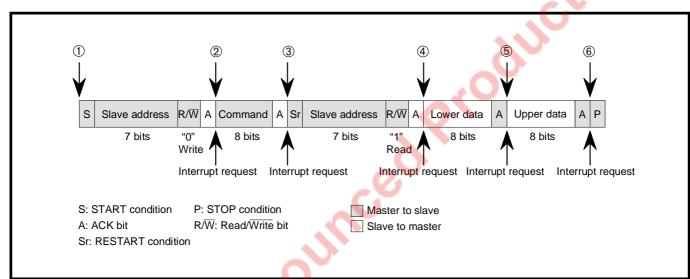

| 2.5.6 SMBUS communication usage example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-98                                                                                                                                                                                                                                            |

| 2.5.7 Notes on multi-master I <sup>2</sup> C-BUS interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-114                                                                                                                                                                                                                                           |

| 2.5.8 Notes on programming for SMBUS interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-117                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                 |

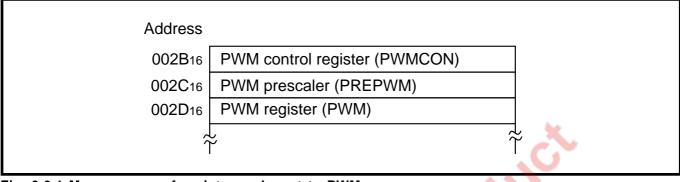

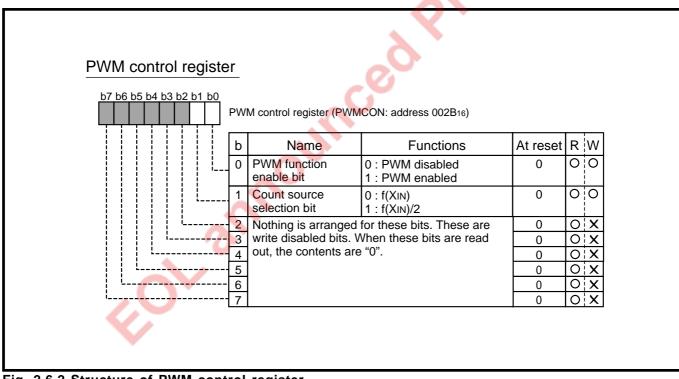

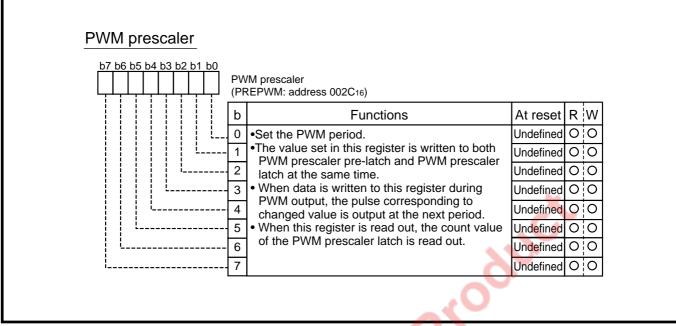

| 2.6 PWM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                 |

| 2.6.1 Memory map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-118                                                                                                                                                                                                                                           |

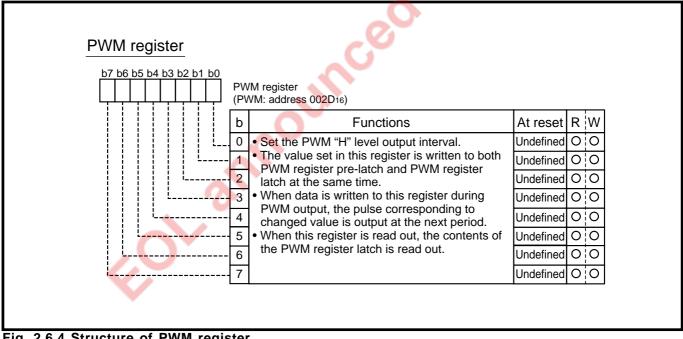

| 2.6.1 Memory map<br>2.6.2 Relevant registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-118<br>2-118                                                                                                                                                                                                                                  |

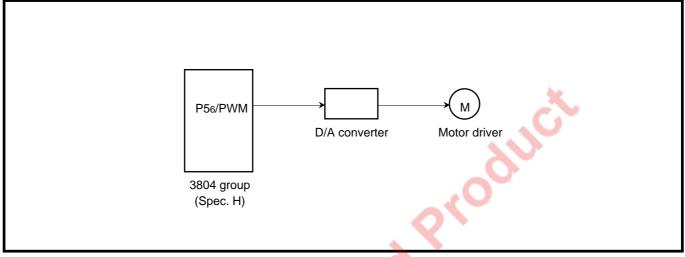

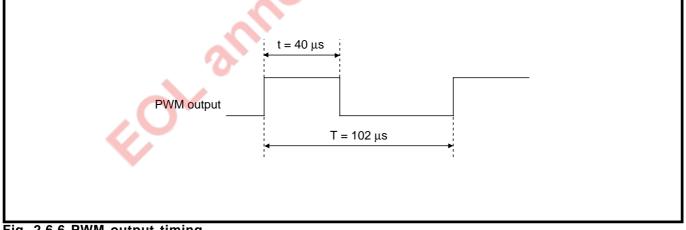

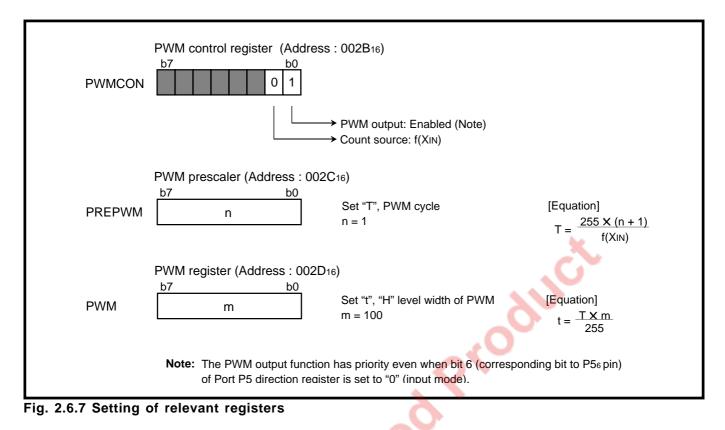

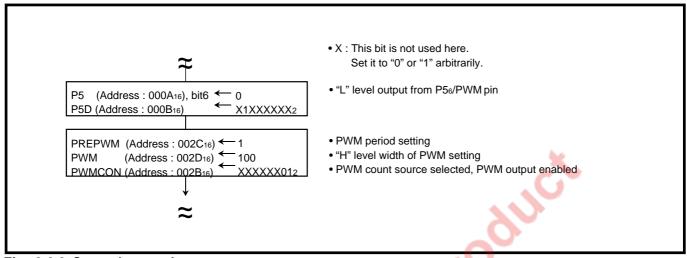

| 2.6.1 Memory map<br>2.6.2 Relevant registers<br>2.6.3 PWM output circuit application example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-118<br>2-118<br>2-120                                                                                                                                                                                                                         |

| <ul> <li>2.6.1 Memory map</li> <li>2.6.2 Relevant registers</li> <li>2.6.3 PWM output circuit application example</li> <li>2.6.4 Notes on PWM</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-118<br>2-118<br>2-120<br>2-122                                                                                                                                                                                                                |

| <ul> <li>2.6.1 Memory map</li> <li>2.6.2 Relevant registers</li> <li>2.6.3 PWM output circuit application example</li> <li>2.6.4 Notes on PWM</li> <li>2.7 A/D converter</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-118<br>2-118<br>2-120<br>2-122<br>2-123                                                                                                                                                                                                       |

| <ul> <li>2.6.1 Memory map</li> <li>2.6.2 Relevant registers</li> <li>2.6.3 PWM output circuit application example</li> <li>2.6.4 Notes on PWM</li> <li>2.7 A/D converter</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-118<br>2-118<br>2-120<br>2-122<br>2-123<br>2-123                                                                                                                                                                                              |

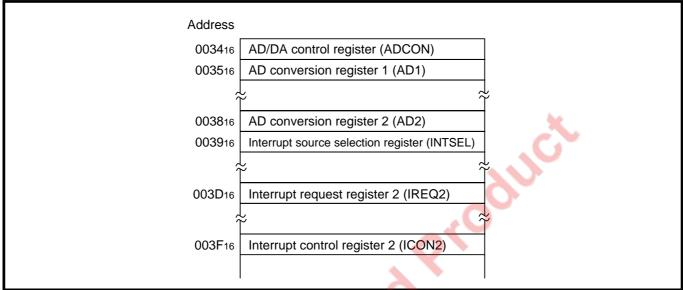

| <ul> <li>2.6.1 Memory map</li> <li>2.6.2 Relevant registers</li> <li>2.6.3 PWM output circuit application example</li> <li>2.6.4 Notes on PWM</li> <li>2.7 A/D converter</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-118<br>2-118<br>2-120<br>2-122<br>2-123<br>2-123<br>2-123                                                                                                                                                                                     |

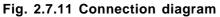

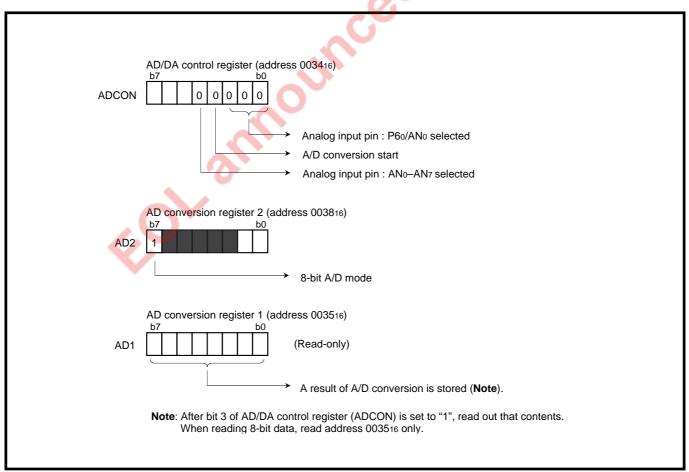

| <ul> <li>2.6.1 Memory map</li> <li>2.6.2 Relevant registers</li> <li>2.6.3 PWM output circuit application example</li> <li>2.6.4 Notes on PWM</li> <li>2.7 A/D converter</li> <li>2.7.1 Memory map</li> <li>2.7.2 Relevant registers</li> <li>2.7.3 A/D converter application examples</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-118<br>2-118<br>2-120<br>2-122<br>2-123<br>2-123<br>2-123<br>2-123<br>2-127                                                                                                                                                                   |

| <ul> <li>2.6.1 Memory map</li> <li>2.6.2 Relevant registers</li> <li>2.6.3 PWM output circuit application example</li> <li>2.6.4 Notes on PWM</li> <li>2.7 A/D converter</li> <li>2.7.1 Memory map</li> <li>2.7.2 Relevant registers</li> <li>2.7.3 A/D converter application examples</li> <li>2.7.4 Notes on A/D converter</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-118<br>2-118<br>2-120<br>2-122<br>2-123<br>2-123<br>2-123<br>2-127<br>2-131                                                                                                                                                                   |

| <ul> <li>2.6.1 Memory map</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-118<br>2-118<br>2-120<br>2-122<br><b>2-123</b><br>2-123<br>2-123<br>2-127<br>2-131<br>2-132                                                                                                                                                   |

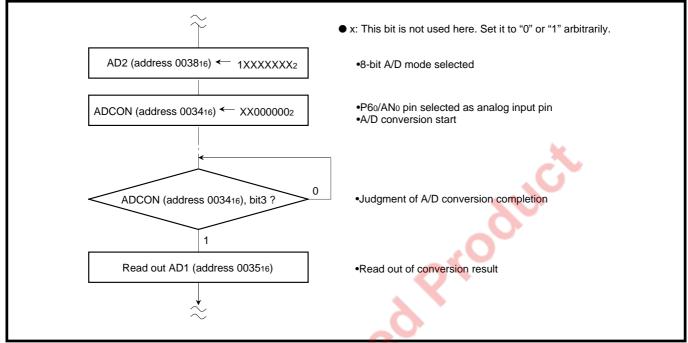

| <ul> <li>2.6.1 Memory map</li> <li>2.6.2 Relevant registers</li> <li>2.6.3 PWM output circuit application example</li> <li>2.6.4 Notes on PWM</li> <li>2.7 A/D converter</li> <li>2.7.1 Memory map</li> <li>2.7.2 Relevant registers</li> <li>2.7.3 A/D converter application examples</li> <li>2.7.4 Notes on A/D converter</li> <li>2.8 D/A Converter</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-118<br>2-118<br>2-120<br>2-122<br>2-123<br>2-123<br>2-123<br>2-127<br>2-131<br>2-132                                                                                                                                                          |

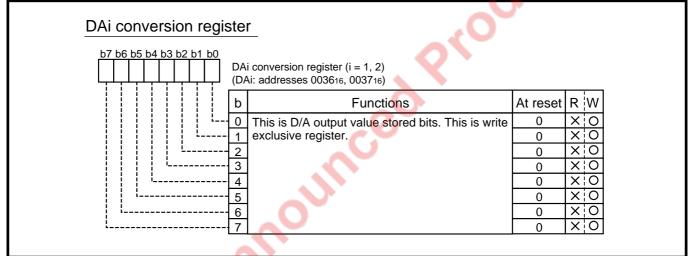

| <ul> <li>2.6.1 Memory map</li> <li>2.6.2 Relevant registers</li> <li>2.6.3 PWM output circuit application example</li> <li>2.6.4 Notes on PWM</li> <li>2.7 A/D converter</li> <li>2.7.1 Memory map</li> <li>2.7.2 Relevant registers</li> <li>2.7.3 A/D converter application examples</li> <li>2.7.4 Notes on A/D converter</li> <li>2.8 D/A Converter</li> <li>2.8.1 Memory map</li> <li>2.8.2 Relevant registers</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                        | 2-118<br>2-118<br>2-120<br>2-122<br><b>2-123</b><br>2-123<br>2-123<br>2-123<br>2-123<br>2-127<br>2-131<br><b>2-132</b><br>2-132<br>2-132                                                                                                        |

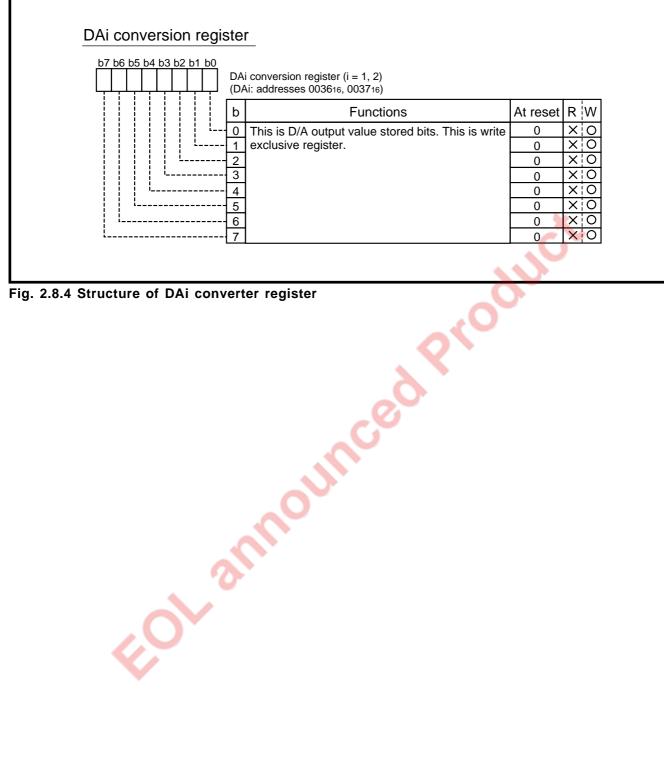

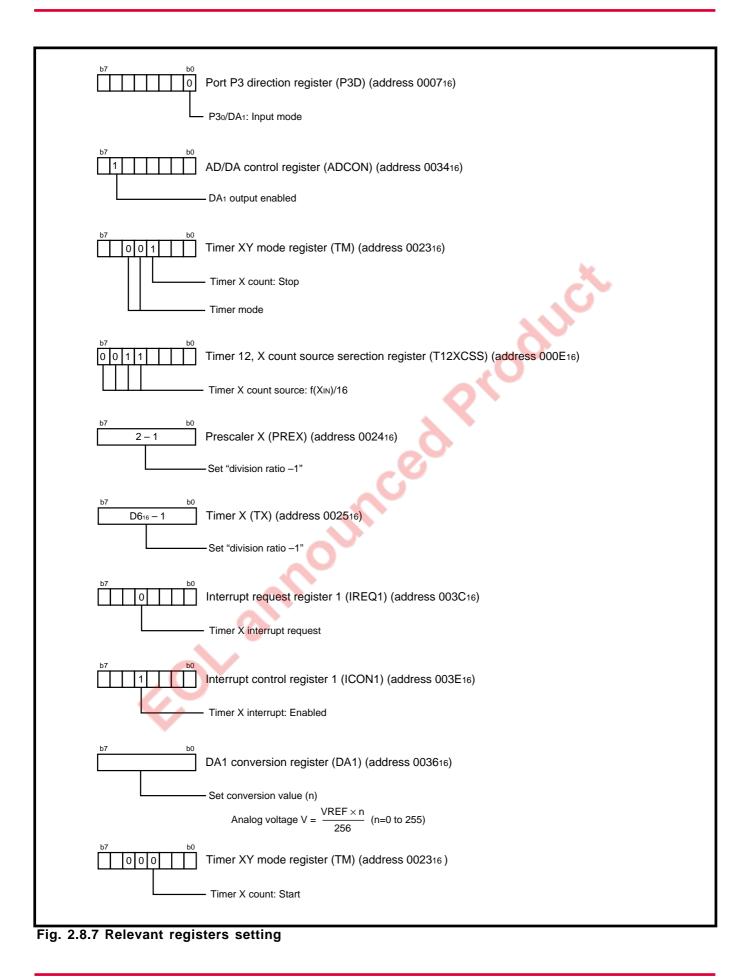

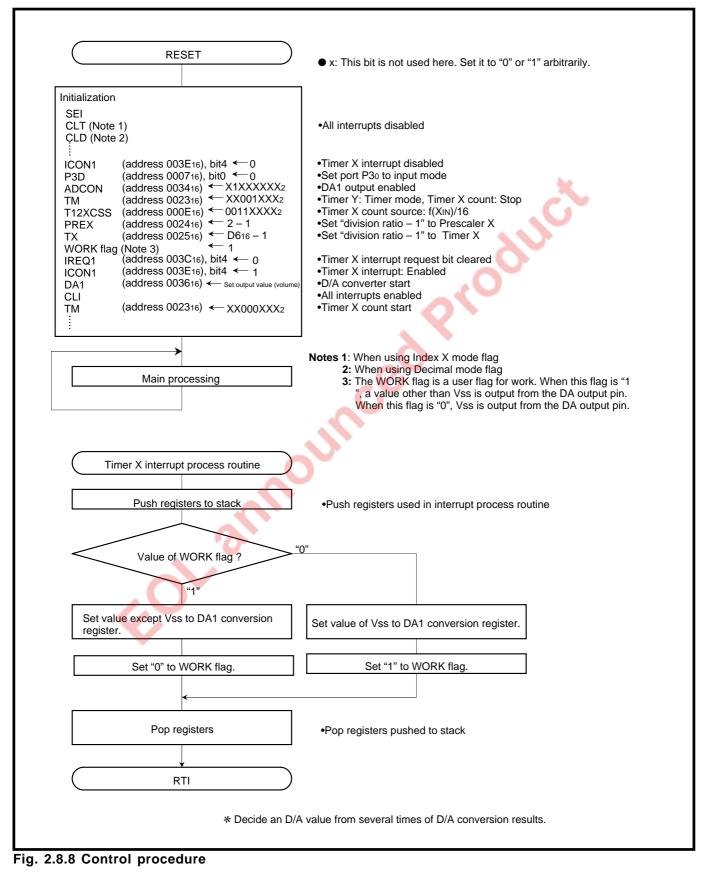

| <ul> <li>2.6.1 Memory map</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-118<br>2-118<br>2-120<br>2-122<br><b>2-123</b><br>2-123<br>2-123<br>2-123<br>2-127<br>2-131<br><b>2-132</b><br>2-132<br>2-133<br>2-133<br>2-133                                                                                               |

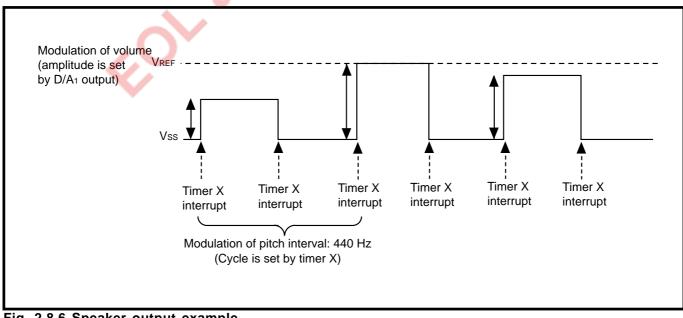

| <ul> <li>2.6.1 Memory map</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-118<br>2-118<br>2-120<br>2-122<br>2-123<br>2-123<br>2-123<br>2-127<br>2-131<br>2-132<br>2-132<br>2-133<br>2-135<br>2-138                                                                                                                      |

| <ul> <li>2.6.1 Memory map</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-118<br>2-118<br>2-120<br>2-122<br>2-123<br>2-123<br>2-123<br>2-123<br>2-123<br>2-123<br>2-123<br>2-131<br>2-132<br>2-132<br>2-132<br>2-133<br>2-138<br>2-138<br>2-139                                                                         |

| <ul> <li>2.6.1 Memory map</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-118<br>2-118<br>2-120<br>2-122<br>2-123<br>2-123<br>2-123<br>2-123<br>2-123<br>2-127<br>2-131<br>2-132<br>2-132<br>2-132<br>2-133<br>2-135<br>2-138<br>2-139                                                                                  |

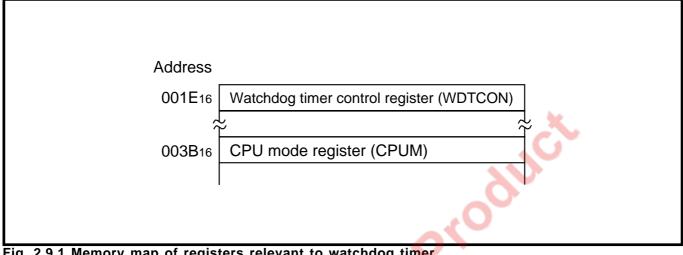

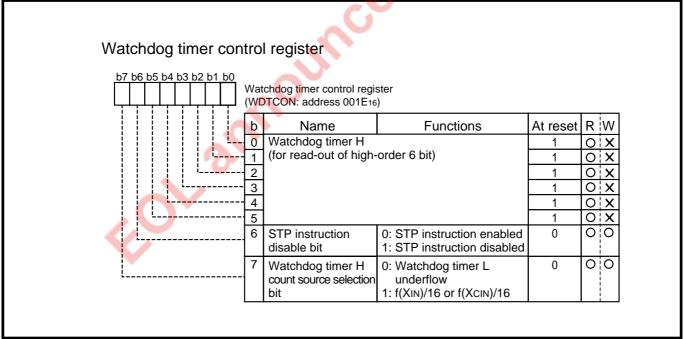

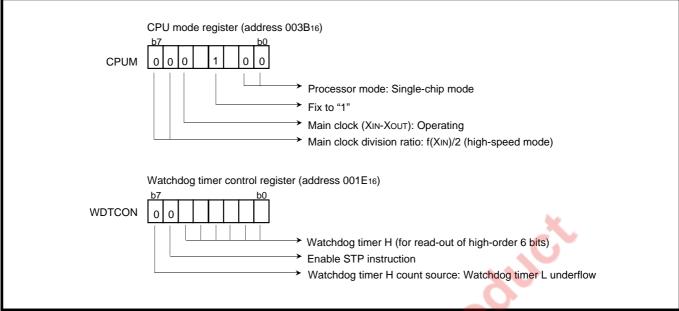

| 2.6.1 Memory map         2.6.2 Relevant registers         2.6.3 PWM output circuit application example         2.6.4 Notes on PWM         2.7 A/D converter         2.7.1 Memory map         2.7.2 Relevant registers         2.7.3 A/D converter application examples         2.7.4 Notes on A/D converter         2.8 D/A Converter         2.8.1 Memory map         2.8.2 Relevant registers         2.8.3 D/A converter application example         2.8.4 Notes on D/A converter         2.9 Watchdog timer         2.9.1 Memory map         2.9.2 Relevant registers                                                                                                                                                                                                                                             | 2-118<br>2-118<br>2-120<br>2-122<br>2-123<br>2-123<br>2-123<br>2-123<br>2-123<br>2-127<br>2-131<br>2-132<br>2-132<br>2-132<br>2-133<br>2-135<br>2-138<br>2-139<br>2-139<br>2-139                                                                |

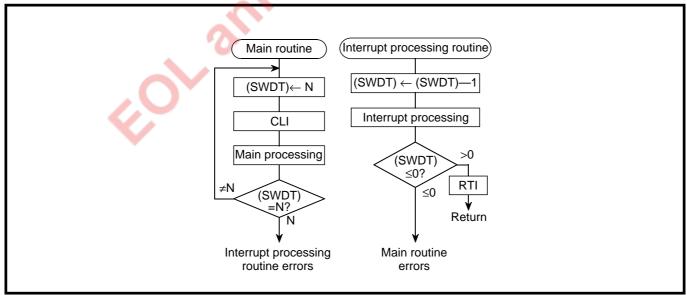

| <ul> <li>2.6.1 Memory map</li> <li>2.6.2 Relevant registers</li> <li>2.6.3 PWM output circuit application example</li> <li>2.6.4 Notes on PWM</li> <li>2.7 A/D converter</li> <li>2.7.1 Memory map</li> <li>2.7.2 Relevant registers</li> <li>2.7.3 A/D converter application examples</li> <li>2.7.4 Notes on A/D converter</li> <li>2.8 D/A Converter</li> <li>2.8.1 Memory map</li> <li>2.8.2 Relevant registers</li> <li>2.8.3 D/A converter application example</li> <li>2.8.4 Notes on D/A converter</li> <li>2.9 Watchdog timer</li> <li>2.9.2 Relevant registers</li> <li>2.9.3 Watchdog timer application examples</li> </ul>                                                                                                                                                                                | 2-118<br>2-118<br>2-120<br>2-122<br><b>2-123</b><br>2-123<br>2-123<br>2-123<br>2-123<br>2-127<br>2-131<br><b>2-132</b><br>2-132<br>2-132<br>2-133<br>2-138<br><b>2-139</b><br>2-139<br>2-139<br>2-139                                           |

| <ul> <li>2.6.1 Memory map</li> <li>2.6.2 Relevant registers</li> <li>2.6.3 PWM output circuit application example</li> <li>2.6.4 Notes on PWM</li> <li>2.7 A/D converter</li> <li>2.7.1 Memory map</li> <li>2.7.2 Relevant registers</li> <li>2.7.3 A/D converter application examples</li> <li>2.7.4 Notes on A/D converter</li> <li>2.8 D/A Converter</li> <li>2.8.1 Memory map</li> <li>2.8.2 Relevant registers</li> <li>2.8.3 D/A converter application example</li> <li>2.8.4 Notes on D/A converter</li> <li>2.9 Watchdog timer</li> <li>2.9.3 Watchdog timer application examples</li> <li>2.9.4 Notes on watchdog timer</li> </ul>                                                                                                                                                                           | 2-118<br>2-118<br>2-120<br>2-122<br>2-123<br>2-123<br>2-123<br>2-123<br>2-123<br>2-123<br>2-127<br>2-131<br>2-132<br>2-132<br>2-132<br>2-133<br>2-135<br>2-138<br>2-139<br>2-139<br>2-139<br>2-139<br>2-141<br>2-142                            |

| <ul> <li>2.6.1 Memory map</li> <li>2.6.2 Relevant registers</li> <li>2.6.3 PWM output circuit application example</li> <li>2.6.4 Notes on PWM</li> <li>2.7 A/D converter</li> <li>2.7.1 Memory map</li> <li>2.7.2 Relevant registers</li> <li>2.7.3 A/D converter application examples</li> <li>2.7.4 Notes on A/D converter</li> <li>2.8 D/A Converter</li> <li>2.8.1 Memory map</li> <li>2.8.2 Relevant registers</li> <li>2.8.3 D/A converter application example</li> <li>2.8.4 Notes on D/A converter</li> <li>2.9 Watchdog timer</li> <li>2.9.1 Memory map</li> <li>2.9.2 Relevant registers</li> <li>2.9.3 Watchdog timer application examples</li> <li>2.9.4 Notes on watchdog timer</li> </ul>                                                                                                               | 2-118<br>2-118<br>2-120<br>2-122<br>2-123<br>2-123<br>2-123<br>2-123<br>2-123<br>2-127<br>2-131<br>2-132<br>2-132<br>2-132<br>2-133<br>2-135<br>2-138<br>2-139<br>2-139<br>2-141<br>2-142<br>2-143                                              |

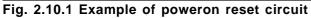

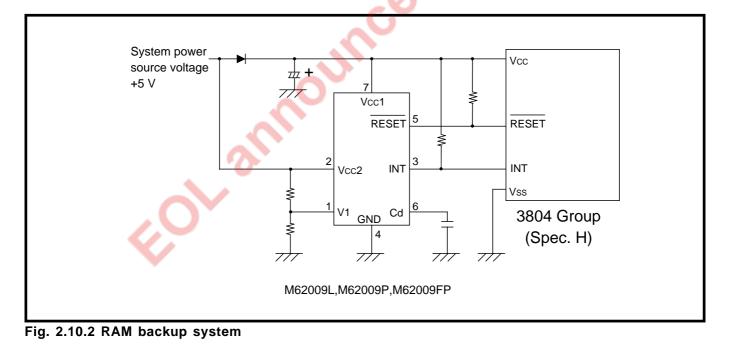

| <ul> <li>2.6.1 Memory map</li> <li>2.6.2 Relevant registers</li> <li>2.6.3 PWM output circuit application example</li> <li>2.6.4 Notes on PWM</li> <li>2.7 A/D converter</li> <li>2.7.1 Memory map</li> <li>2.7.2 Relevant registers</li> <li>2.7.3 A/D converter application examples</li> <li>2.7.4 Notes on A/D converter</li> <li>2.8 D/A Converter</li> <li>2.8.1 Memory map</li> <li>2.8.2 Relevant registers</li> <li>2.8.3 D/A converter application example</li> <li>2.8.4 Notes on D/A converter</li> <li>2.9 Watchdog timer</li> <li>2.9.1 Memory map</li> <li>2.9.2 Relevant registers</li> <li>2.9.3 Watchdog timer application examples</li> <li>2.9.4 Notes on watchdog timer</li> <li>2.10.1 Connection example of reset IC</li> </ul>                                                                | 2-118<br>2-118<br>2-120<br>2-122<br>2-123<br>2-123<br>2-123<br>2-123<br>2-123<br>2-127<br>2-131<br>2-132<br>2-132<br>2-133<br>2-133<br>2-133<br>2-139<br>2-139<br>2-139<br>2-139<br>2-141<br>2-142<br>2-143                                     |

| <ul> <li>2.6.1 Memory map</li> <li>2.6.2 Relevant registers</li> <li>2.6.3 PWM output circuit application example</li> <li>2.6.4 Notes on PWM</li> <li>2.6.4 Notes on PWM</li> <li>2.7 A/D converter</li> <li>2.7.1 Memory map</li> <li>2.7.2 Relevant registers</li> <li>2.7.3 A/D converter application examples</li> <li>2.7.4 Notes on A/D converter</li> <li>2.8 D/A Converter</li> <li>2.8.1 Memory map</li> <li>2.8.2 Relevant registers</li> <li>2.8.3 D/A converter application example</li> <li>2.8.4 Notes on D/A converter</li> <li>2.9 Watchdog timer</li> <li>2.9.1 Memory map</li> <li>2.9.2 Relevant registers</li> <li>2.9.3 Watchdog timer application examples</li> <li>2.9.4 Notes on watchdog timer</li> <li>2.10.1 Connection example of reset IC</li> <li>2.10.2 Notes on RESET pin</li> </ul> | 2-118<br>2-118<br>2-120<br>2-122<br>2-123<br>2-123<br>2-123<br>2-123<br>2-123<br>2-123<br>2-131<br>2-132<br>2-132<br>2-132<br>2-133<br>2-135<br>2-138<br>2-139<br>2-139<br>2-139<br>2-139<br>2-139<br>2-141<br>2-142<br>2-143<br>2-143          |

| 2.6.1 Memory map         2.6.2 Relevant registers         2.6.3 PWM output circuit application example         2.6.4 Notes on PWM         2.7 A/D converter         2.7.1 Memory map         2.7.2 Relevant registers         2.7.3 A/D converter application examples         2.7.4 Notes on A/D converter         2.8 D/A Converter         2.8.1 Memory map         2.8.2 Relevant registers         2.8.3 D/A converter application example         2.8.4 Notes on D/A converter         2.9 Watchdog timer         2.9.1 Memory map         2.9.2 Relevant registers         2.9.3 Watchdog timer application examples         2.9.4 Notes on watchdog timer         2.9.5 Notes on watchdog timer         2.10 1 Connection example of reset IC         2.10.2 Notes on RESET pin                               | 2-118<br>2-118<br>2-120<br>2-122<br>2-123<br>2-123<br>2-123<br>2-123<br>2-123<br>2-123<br>2-131<br>2-132<br>2-132<br>2-132<br>2-133<br>2-135<br>2-138<br>2-139<br>2-139<br>2-139<br>2-139<br>2-141<br>2-142<br>2-143<br>2-144<br>2-143          |

| <ul> <li>2.6.1 Memory map</li> <li>2.6.2 Relevant registers</li> <li>2.6.3 PWM output circuit application example</li> <li>2.6.4 Notes on PWM</li> <li>2.6.4 Notes on PWM</li> <li>2.7 A/D converter</li> <li>2.7.1 Memory map</li> <li>2.7.2 Relevant registers</li> <li>2.7.3 A/D converter application examples</li> <li>2.7.4 Notes on A/D converter</li> <li>2.8 D/A Converter</li> <li>2.8.1 Memory map</li> <li>2.8.2 Relevant registers</li> <li>2.8.3 D/A converter application example</li> <li>2.8.4 Notes on D/A converter</li> <li>2.9 Watchdog timer</li> <li>2.9.1 Memory map</li> <li>2.9.2 Relevant registers</li> <li>2.9.3 Watchdog timer application examples</li> <li>2.9.4 Notes on watchdog timer</li> <li>2.10.1 Connection example of reset IC</li> <li>2.10.2 Notes on RESET pin</li> </ul> | 2-118<br>2-118<br>2-120<br>2-122<br>2-123<br>2-123<br>2-123<br>2-123<br>2-123<br>2-123<br>2-131<br>2-132<br>2-132<br>2-132<br>2-133<br>2-135<br>2-138<br>2-139<br>2-139<br>2-139<br>2-139<br>2-141<br>2-142<br>2-144<br>2-144<br>2-144<br>2-145 |

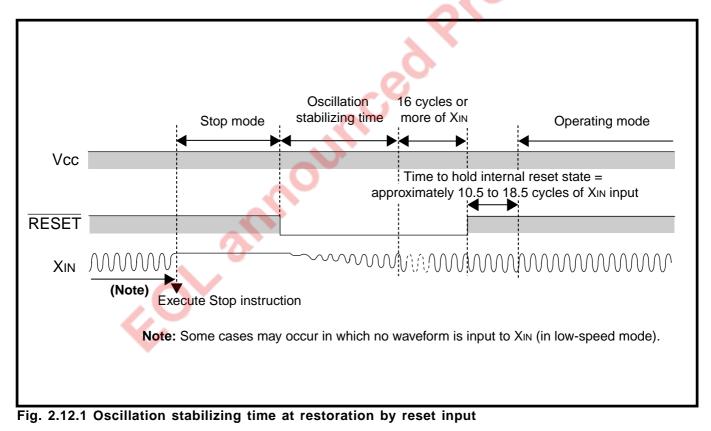

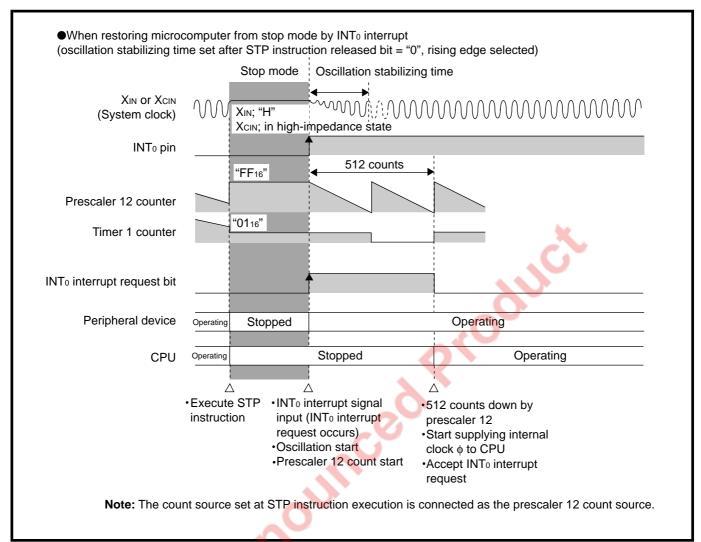

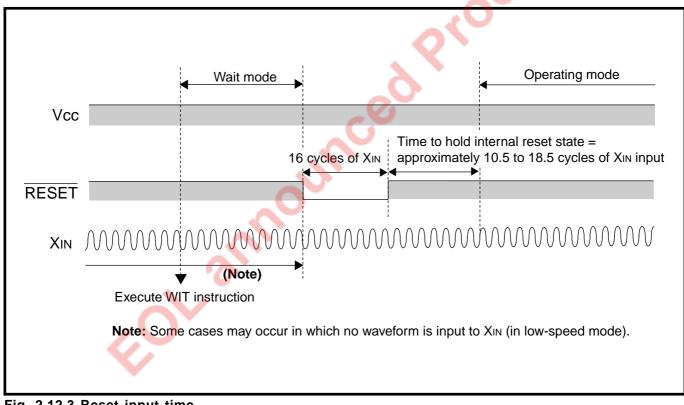

| 2.12 Standby function                         | 2-149 |

|-----------------------------------------------|-------|

| 2.12.1 Stop mode                              | 2-149 |

| 2.12.2 Wait mode                              |       |

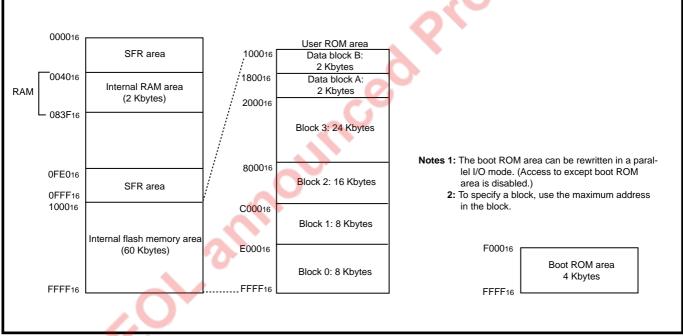

| 2.13 Flash memory mode                        | 2-156 |

| 2.13.1 Overview                               |       |

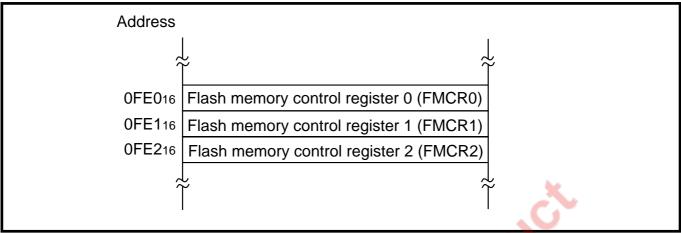

| 2.13.2 Memory map                             | 2-156 |

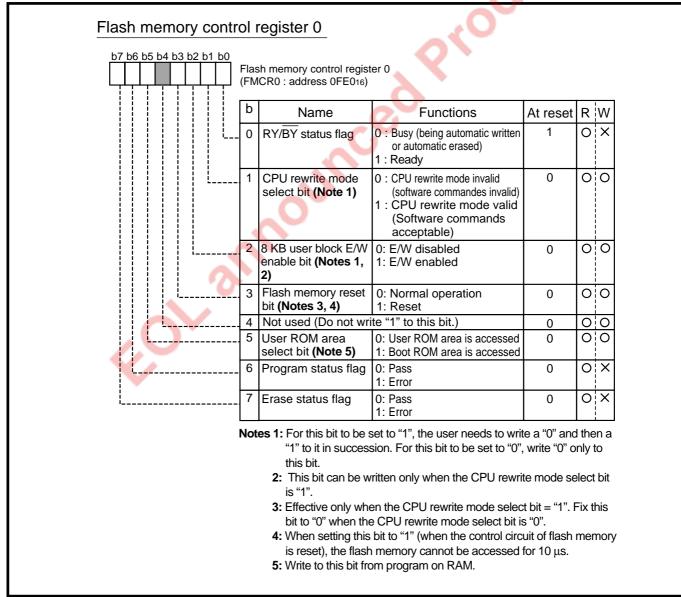

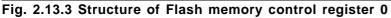

| 2.13.3 Relevant registers                     | 2-157 |

| 2.13.4 Parallel I/O mode                      | 2-159 |

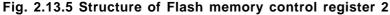

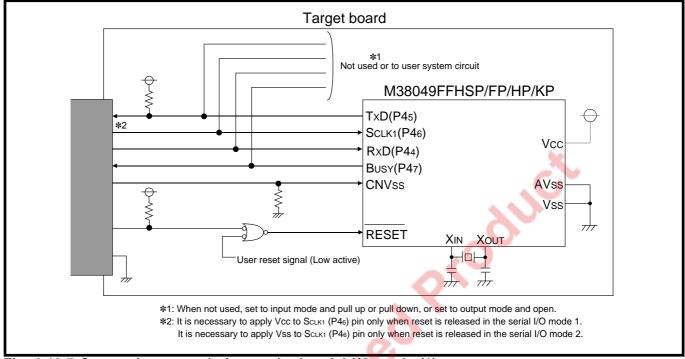

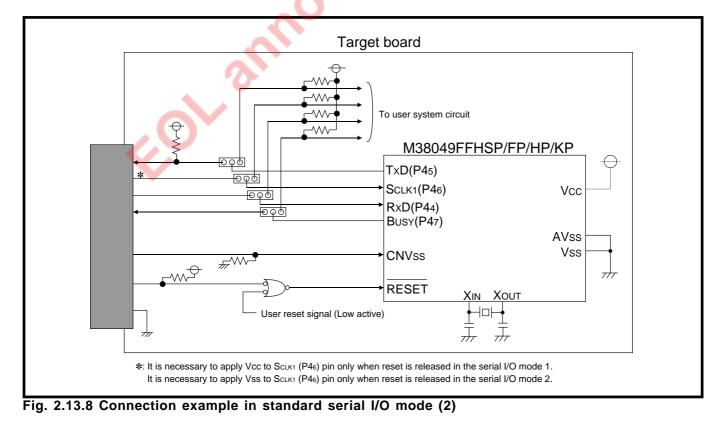

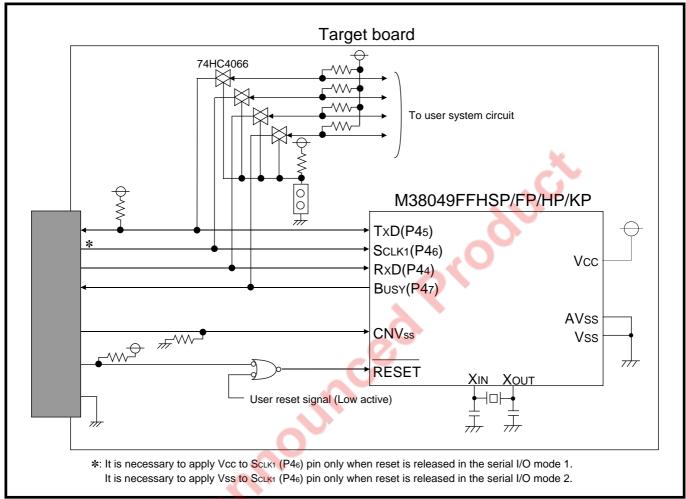

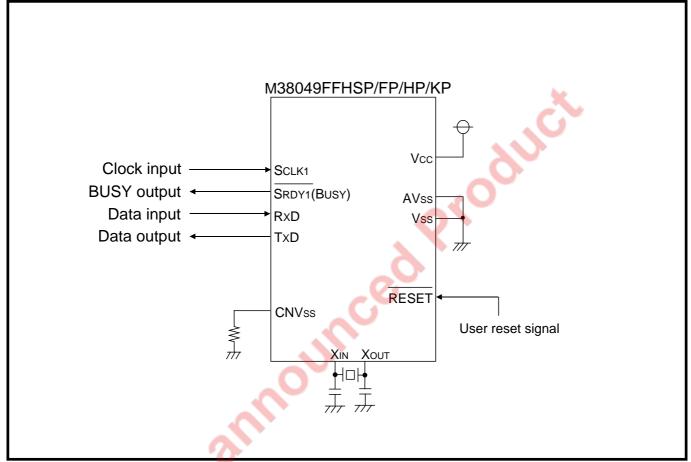

| 2.13.5 Standard serial I/O mode               | 2-159 |

| 2.13.6 CPU rewrite mode                       | 2-160 |

| 2.13.7 Flash memory mode application examples | 2-162 |

| 2.13.8 Notes on CPU rewrite mode              | 2-166 |

|                                               |       |

#### CHAPTER 3 APPENDIX

| 3.1 ELECTRICAL CHARACTERISTICS                                   | 3-2  |

|------------------------------------------------------------------|------|

| 3.1.1 Absolute maximum ratings                                   |      |

| 3.1.2 Recommended operating conditions                           | 3-3  |

| 3.1.3 Electrical characteristics                                 |      |

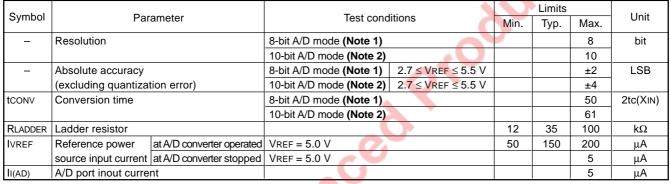

| 3.1.4 A/D converter characteristics                              | 3-8  |

| 3.1.5 D/A converter characteristics                              |      |

| 3.1.6 Power source circuit timing characteristics                | 3-8  |

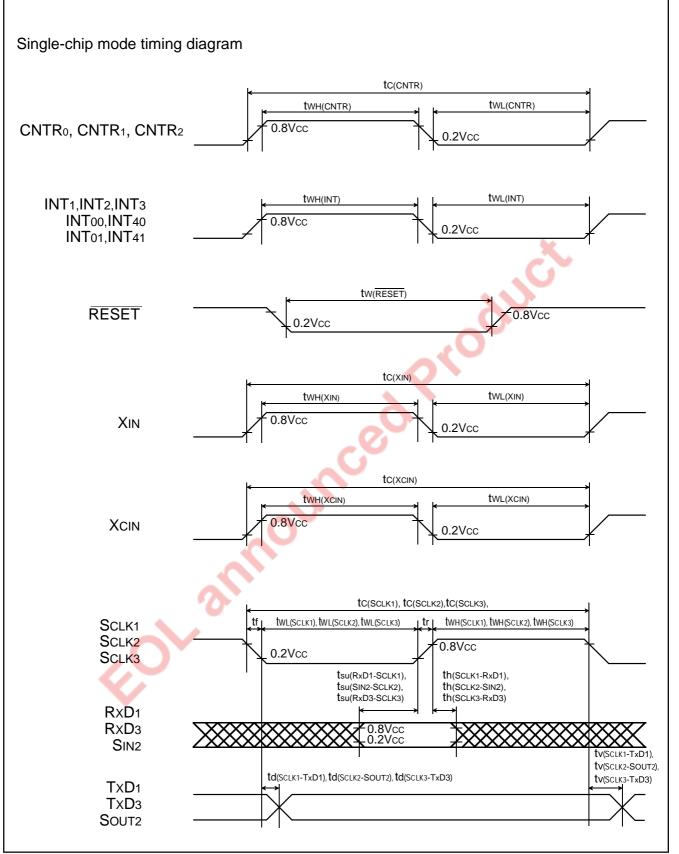

| 3.1.7 Timing requirements and switching characteristics          |      |

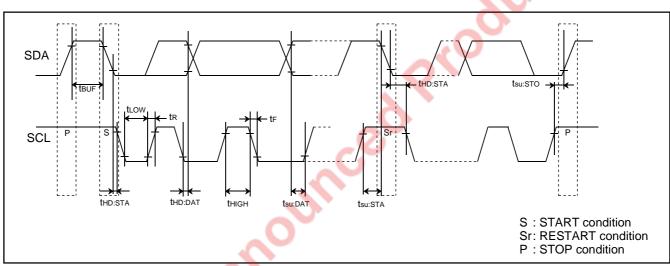

| 3.1.8 Multi-master I <sup>2</sup> C-BUS bus line characteristics |      |

| 3.2 Standard characteristics                                     |      |

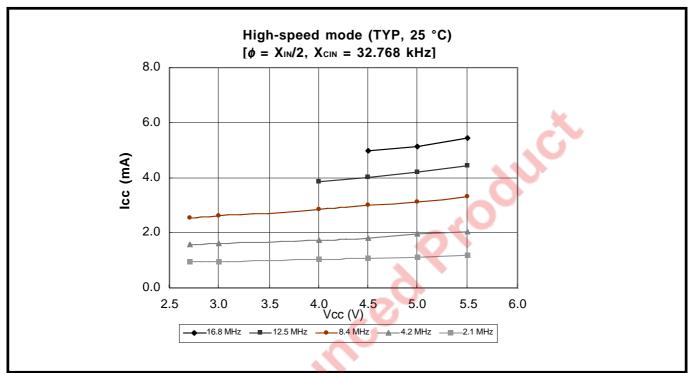

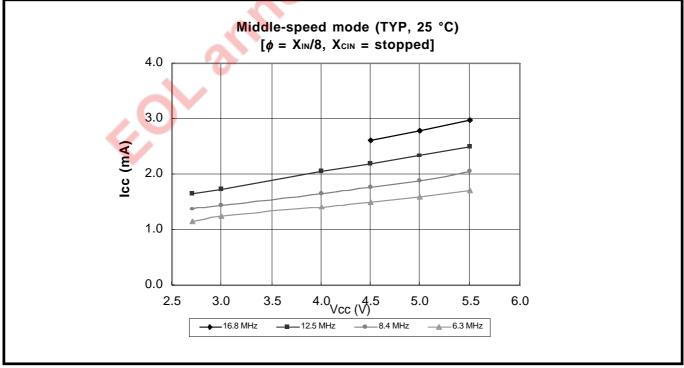

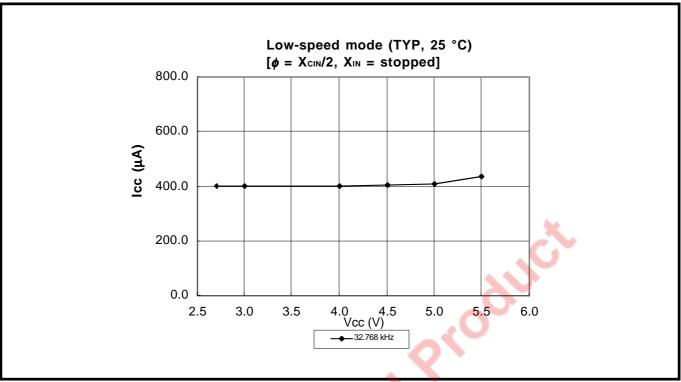

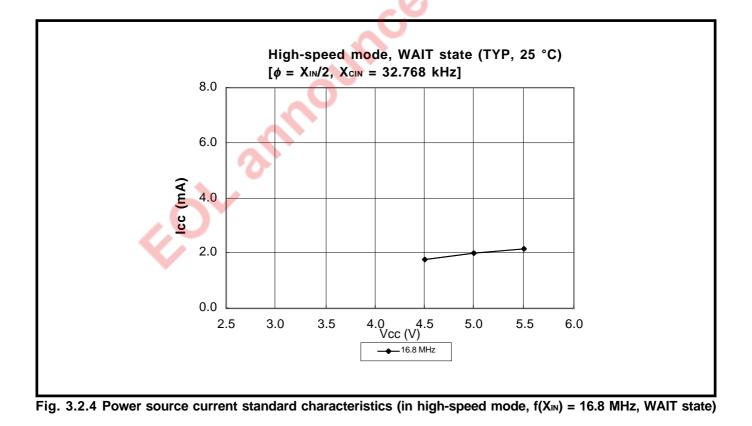

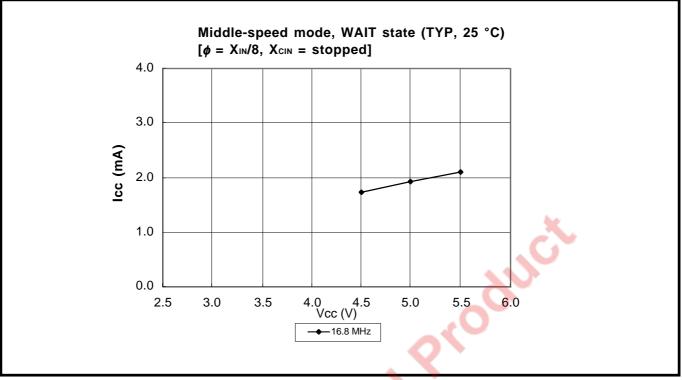

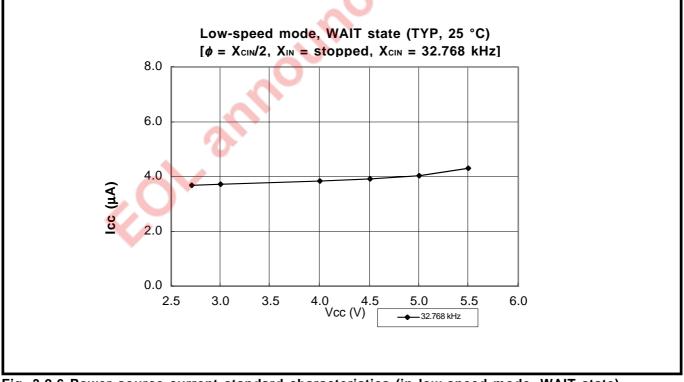

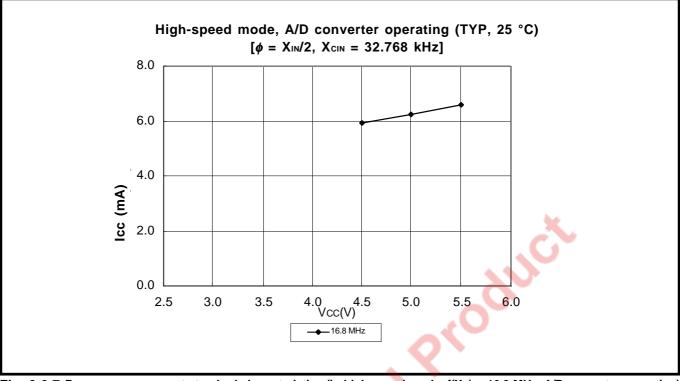

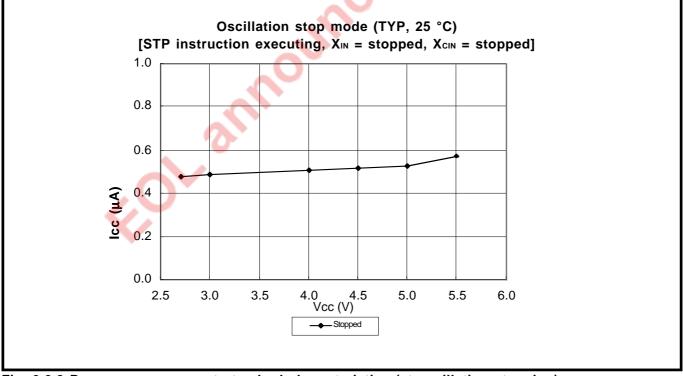

| 3.2.1 Power source current standard characteristics              |      |

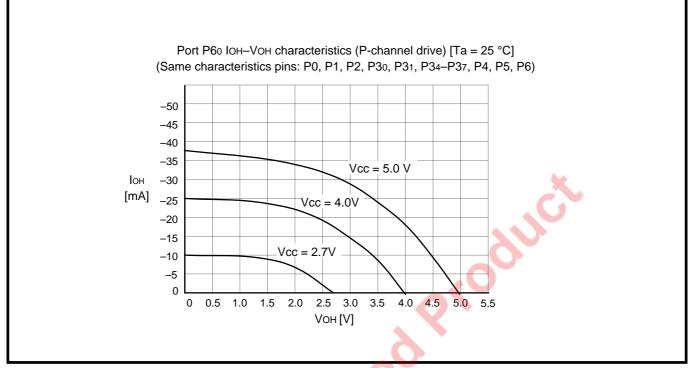

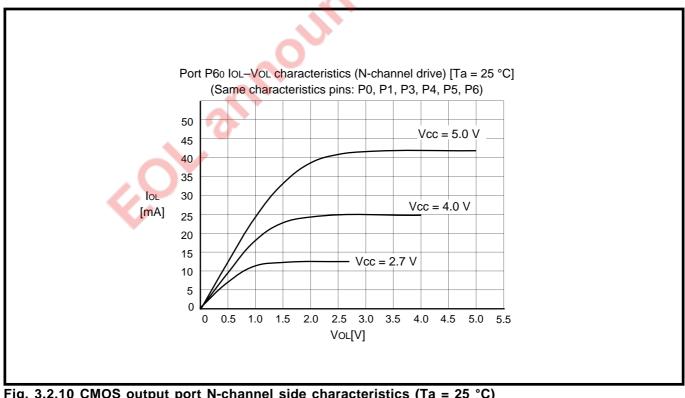

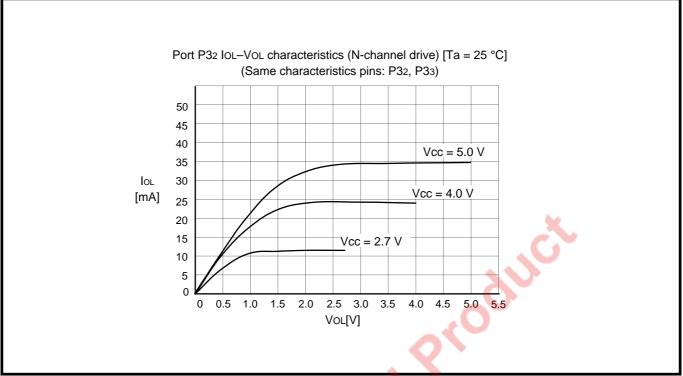

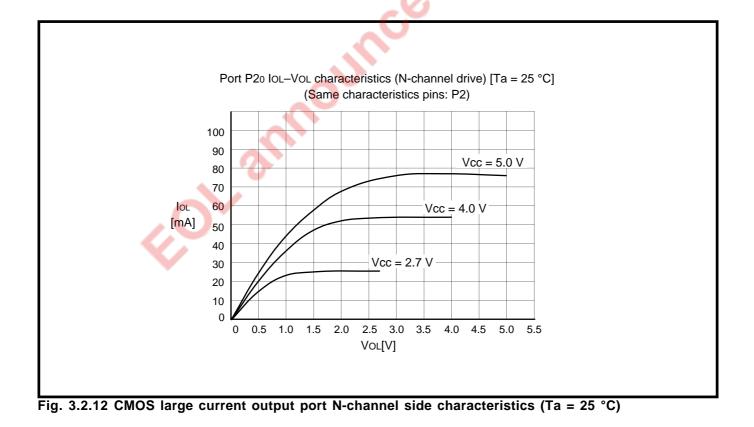

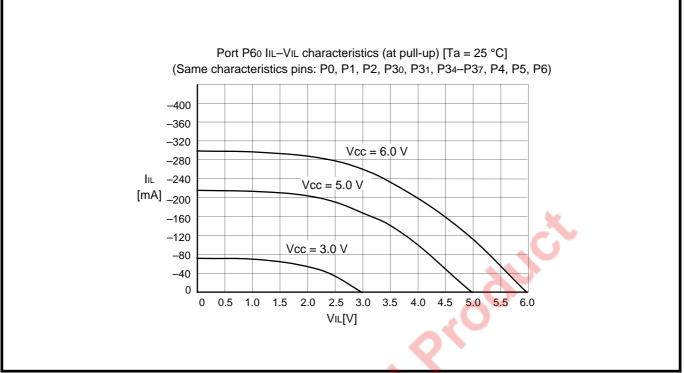

| 3.2.2 Port standard characteristics                              |      |

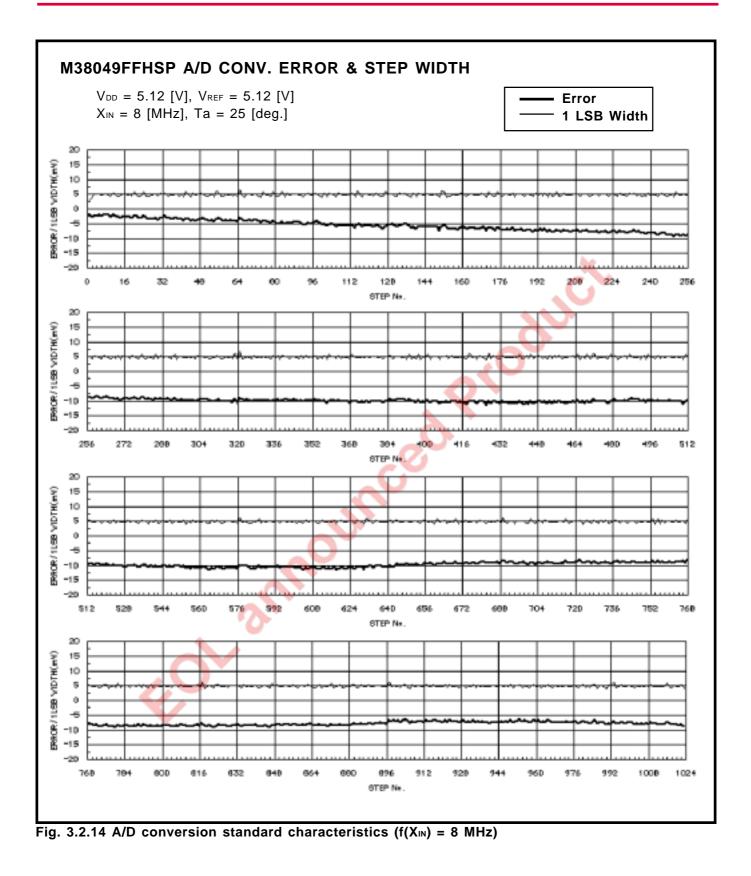

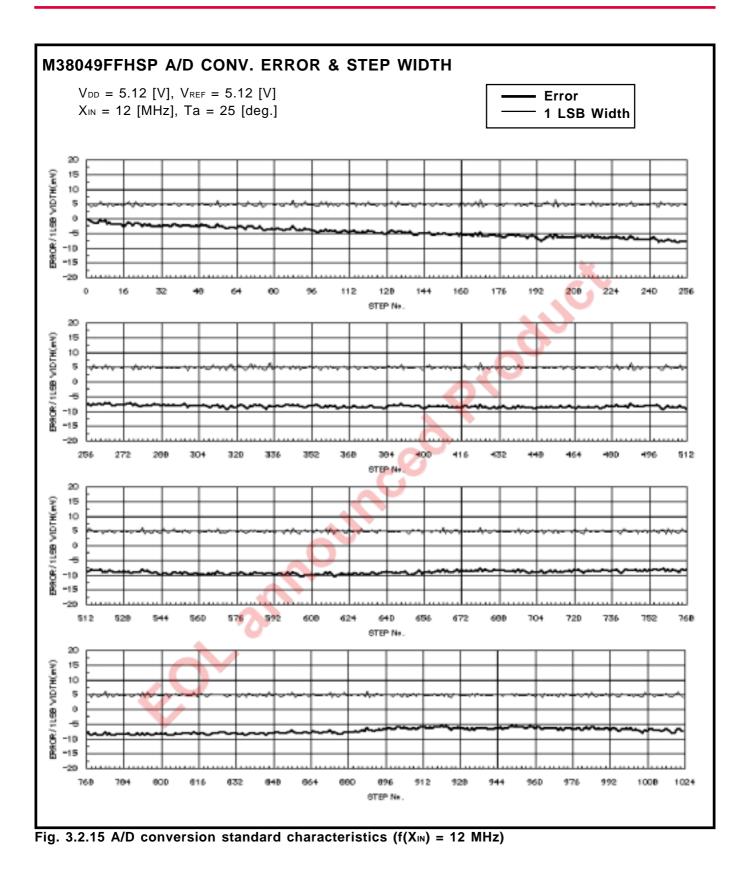

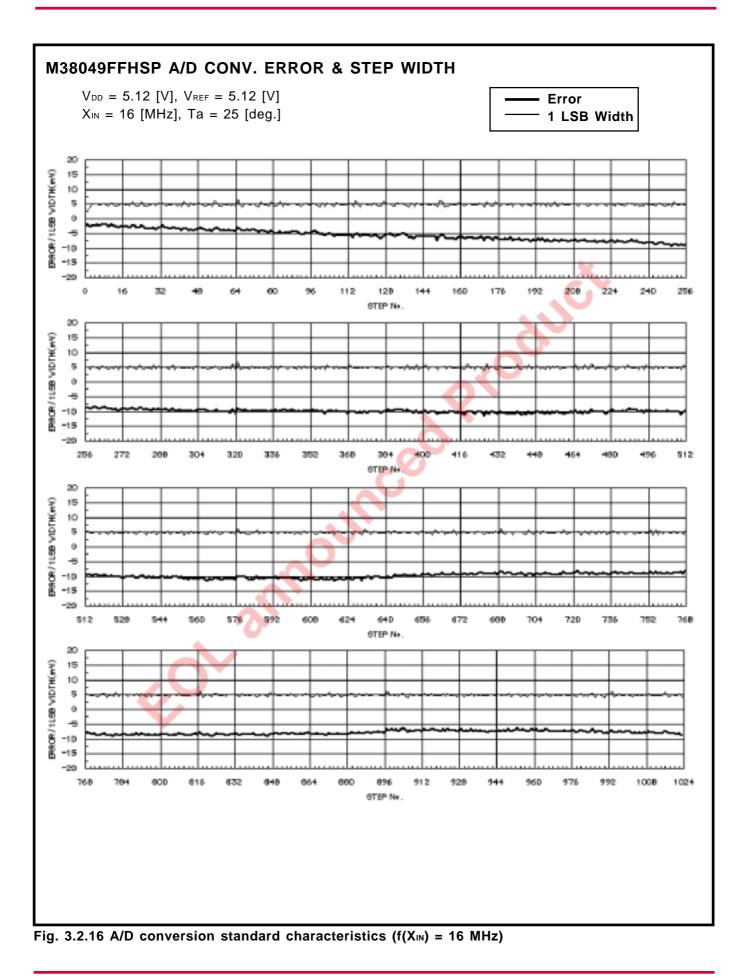

| 3.2.3 A/D conversion standard characteristics                    |      |

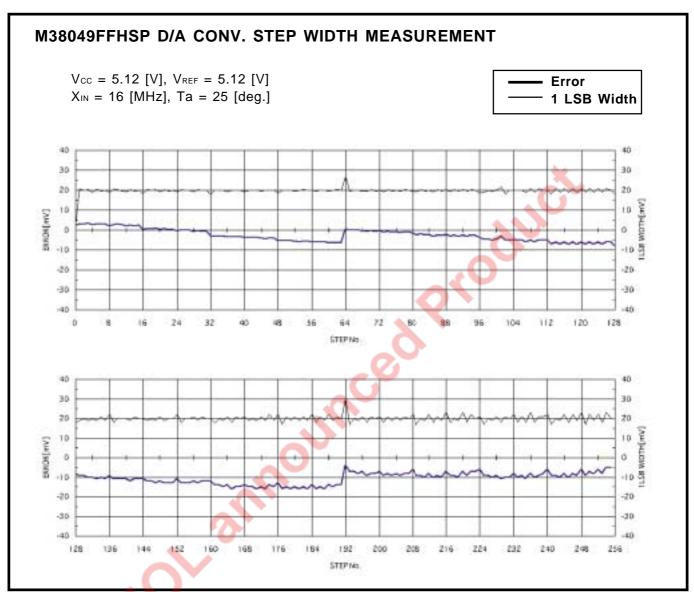

| 3.2.4 D/A conversion standard characteristics                    |      |

| 3.3 Notes on use                                                 |      |

| 3.3.1 Notes on input and output ports                            |      |

| 3.3.2 Termination of unused pins                                 | 3-28 |

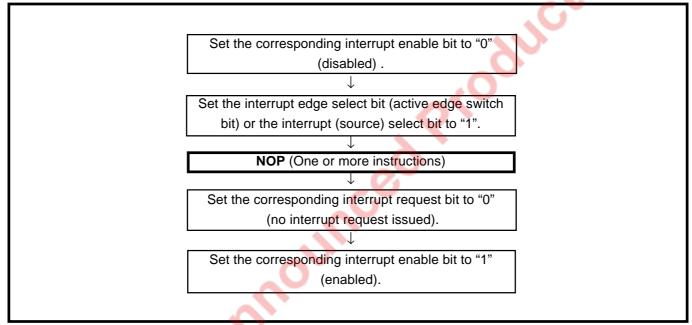

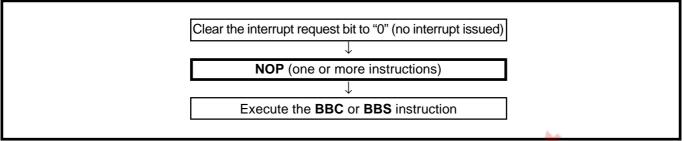

| 3.3.3 Notes on interrupts                                        |      |

| 3.3.4 Notes on 8-bit timer (timer 1, 2, X, Y)                    |      |

| 3.3.5 Notes on 16-bit timer (timer Z)                            |      |

| 3.3.6 Notes on serial interface                                  |      |

| 3.3.7 Notes on multi-master I <sup>2</sup> C-BUS interface       |      |

| 3.3.8 Notes on programming for SMBUS interface                   |      |

| 3.3.9 Notes on PWM                                               |      |

| 3.3.10 Notes on A/D converter                                    |      |

| 3.3.11 Notes on D/A converter                                    |      |

| 3.3.12 Notes on watchdog timer                                   |      |

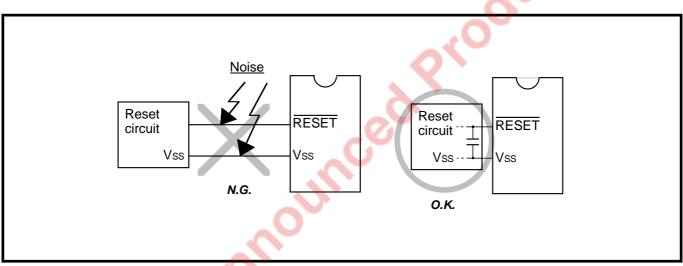

| 3.3.13 Notes on RESET pin                                        |      |

| 3.3.14 Notes on low-speed operation mode                         |      |

| 3.3.15 Quartz-crystal oscillator                                 |      |

| 3.3.16 Notes on restarting oscillation                           |      |

| 3.3.17 Notes on using stop mode                                  |      |

| 3.3.18 Notes on wait mode                                        |      |

| 3.3.19 Notes on CPU rewrite mode                                 |      |

| 3.3.20 Notes on programming                                      |      |

| 3.3.21 Notes on flash memory version                             | 3-42 |

| Vcc line |

|----------|

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

## List of figures

#### CHAPTER 1 HARDWARE

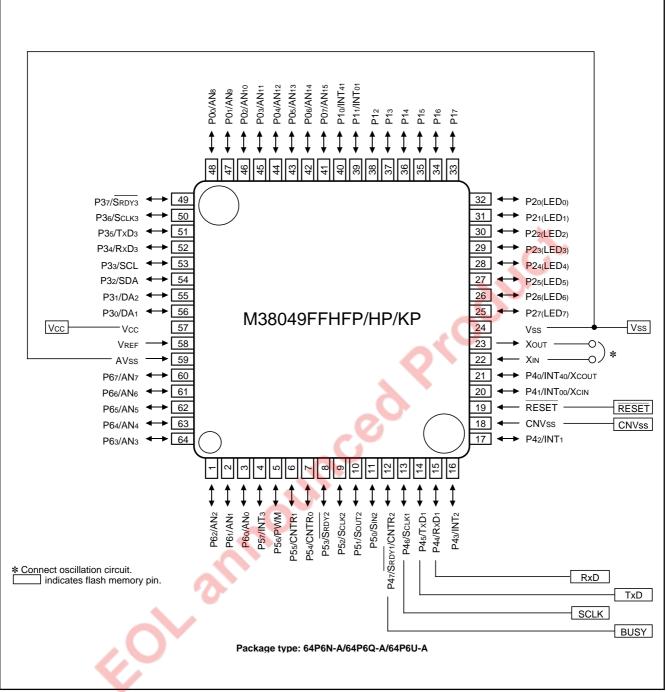

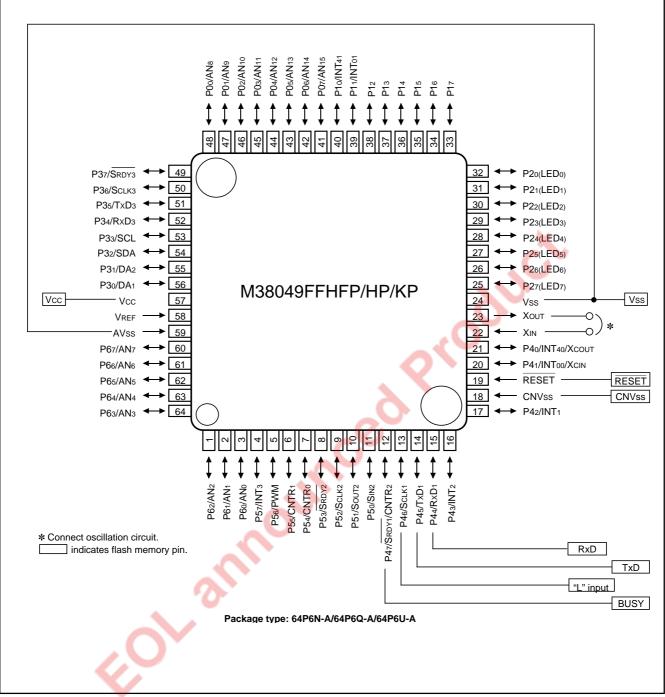

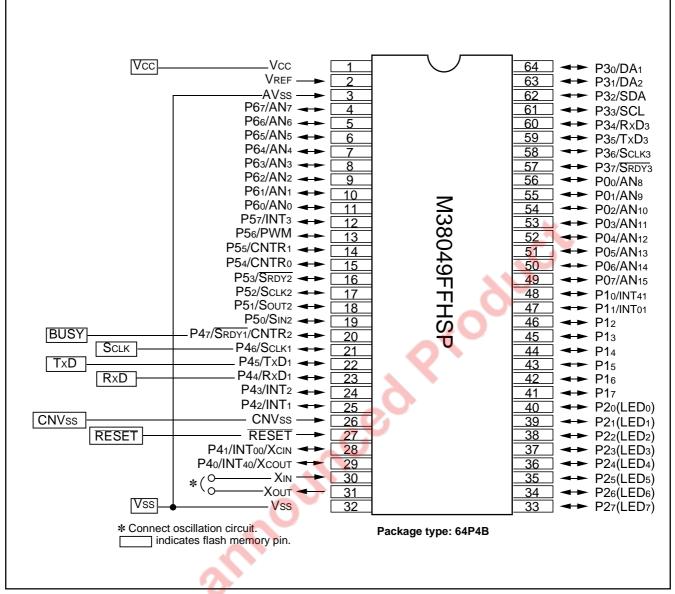

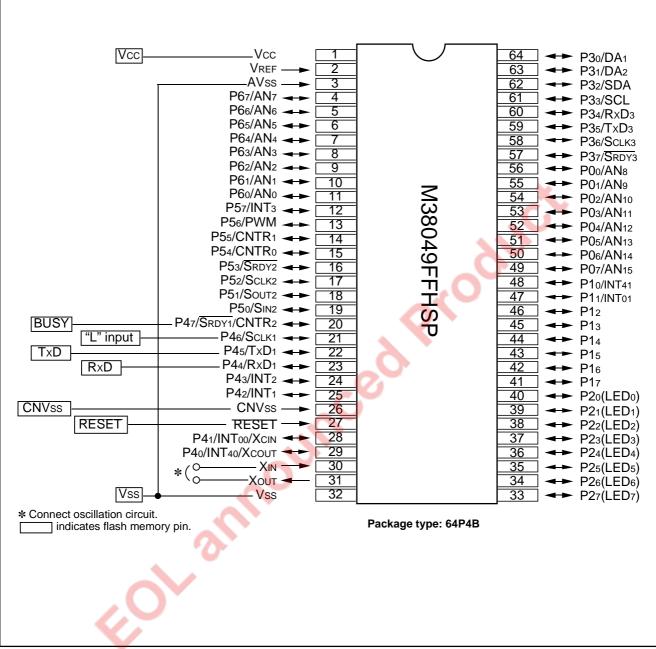

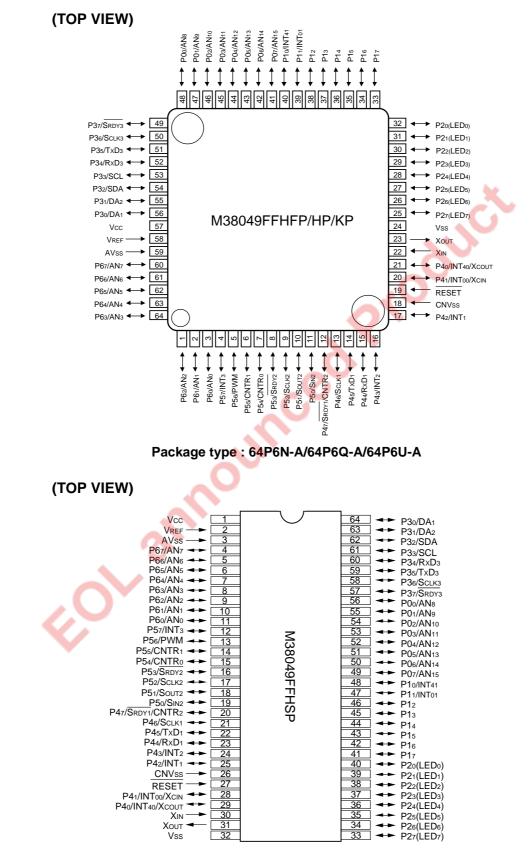

| Fig. 1 3  | 3804 group (Spec. H) pin configuration                                                   | 1-3    |

|-----------|------------------------------------------------------------------------------------------|--------|

| Fig. 2 3  | 3804 group (Spec. H) pin configuration                                                   | 1-3    |

| Fig. 3 F  | Functional block diagram                                                                 | 1-4    |

| Fig. 4    | Part numbering                                                                           | 1-6    |

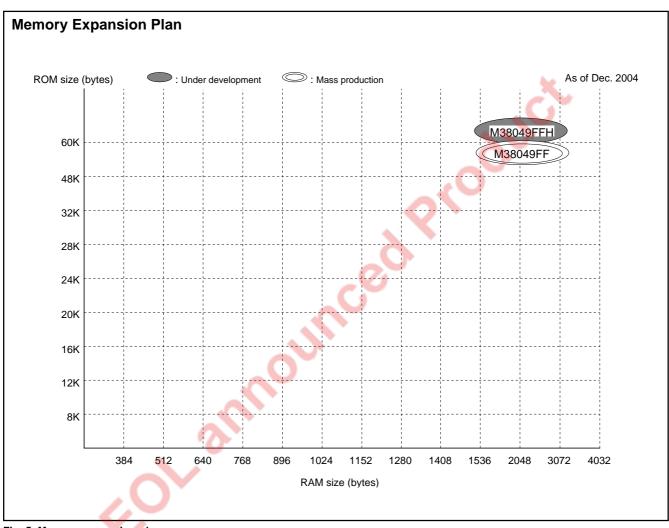

| Fig. 5 I  | Memory expansion plan                                                                    | 1-7    |

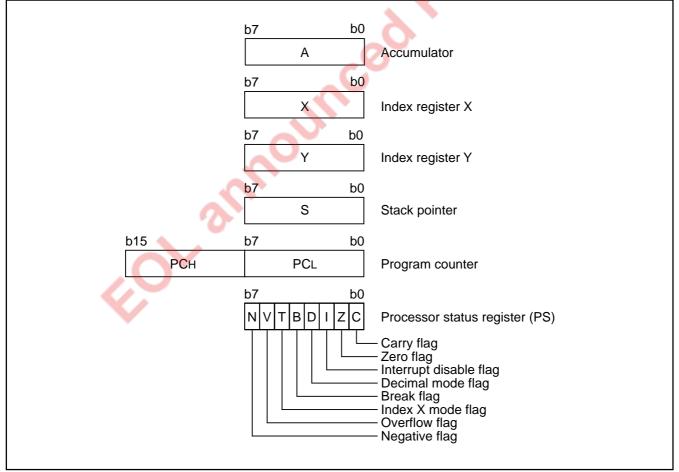

| Fig. 6 7  | 740 Family CPU register structure                                                        | 1-8    |

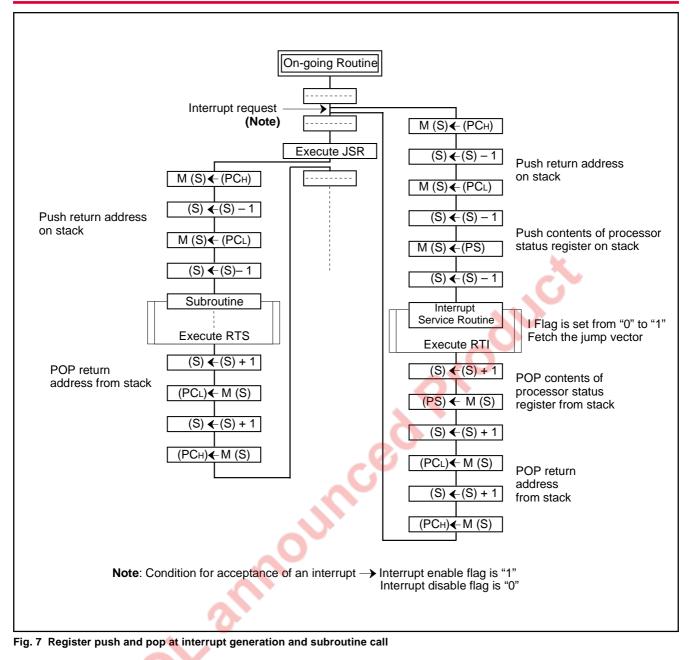

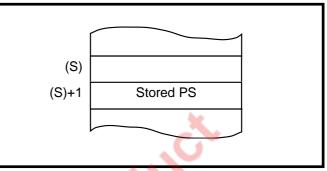

| Fig. 7 F  | Register push and pop at interrupt generation and subroutine call                        | 1-9    |

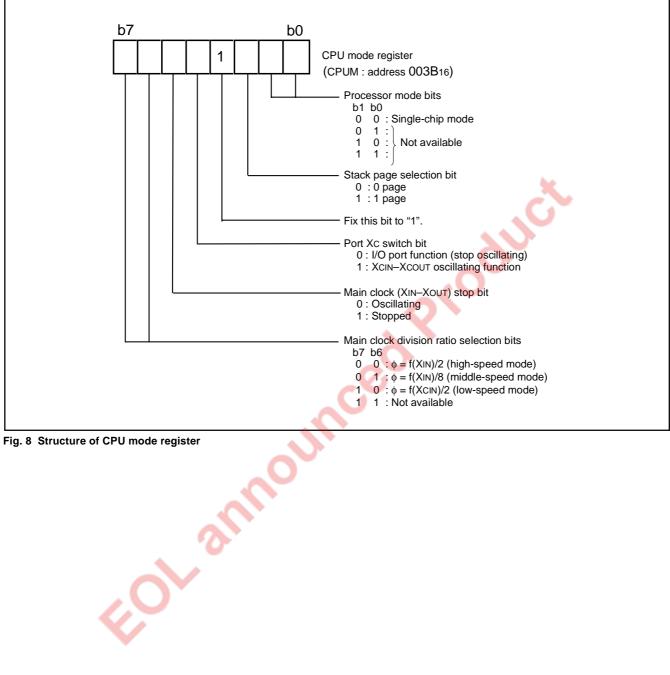

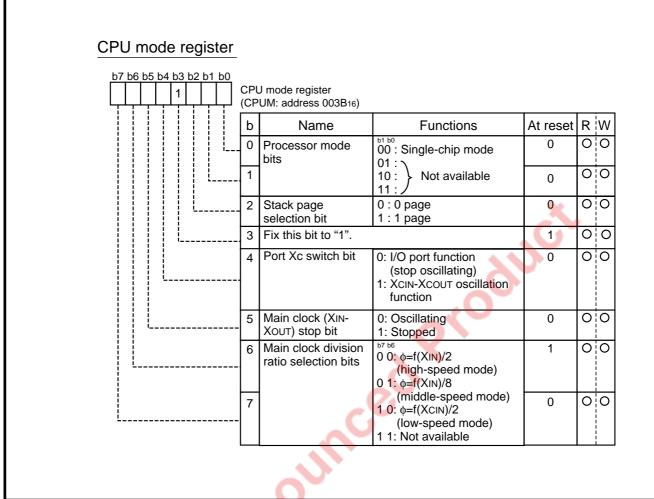

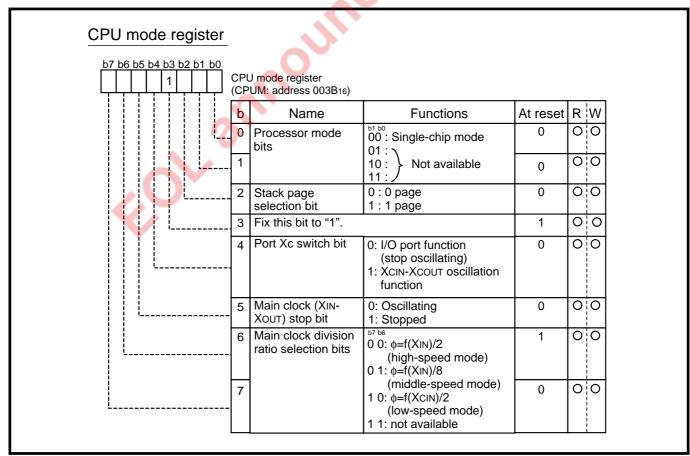

| Fig. 8 \$ | Structure of CPU mode register                                                           | . 1-11 |

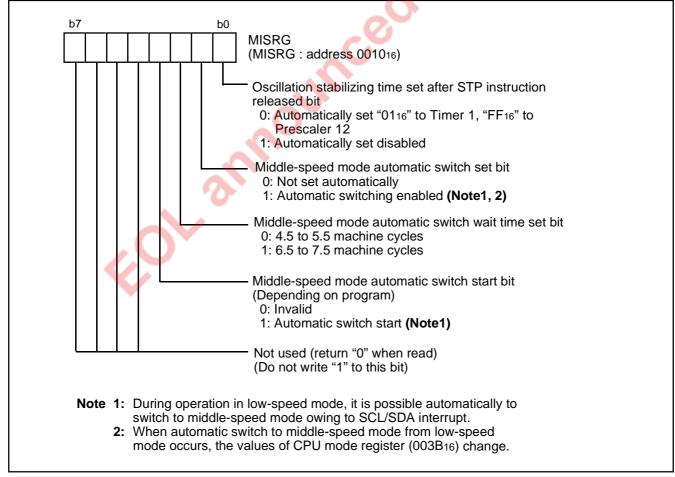

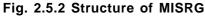

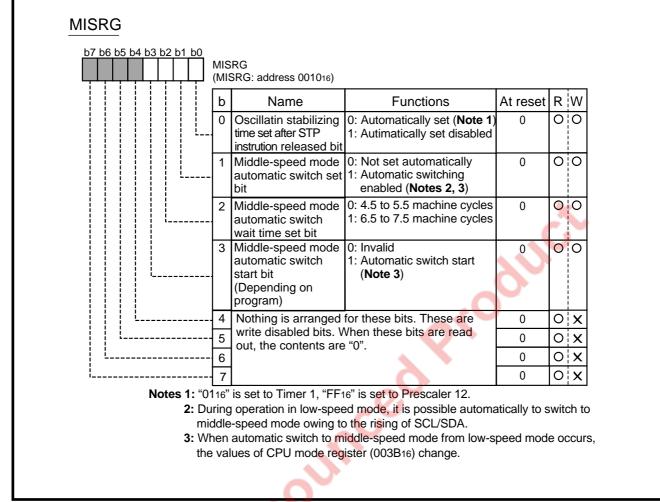

| Fig. 9 \$ | Structure of MISRG                                                                       | . 1-12 |

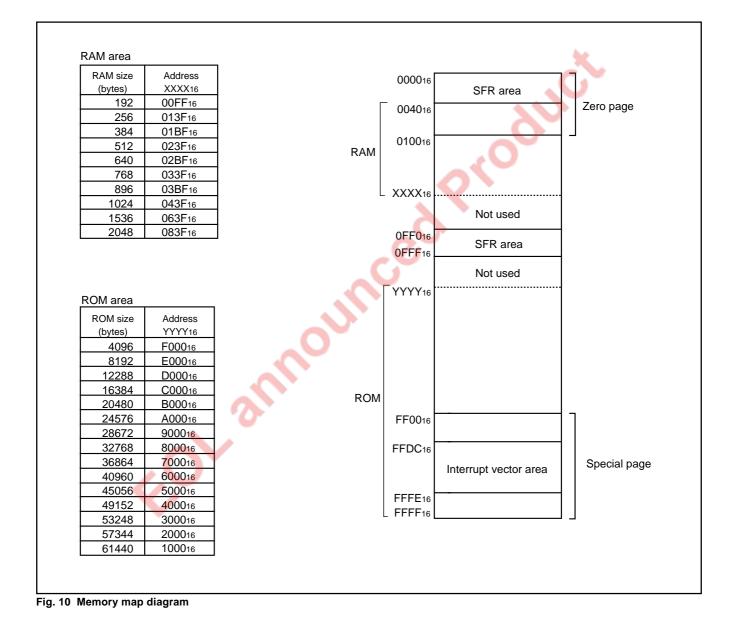

| Fig. 10   | Memory map diagram                                                                       | . 1-13 |

| Fig. 11   | Memory map of special function register (SFR)                                            | . 1-14 |

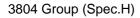

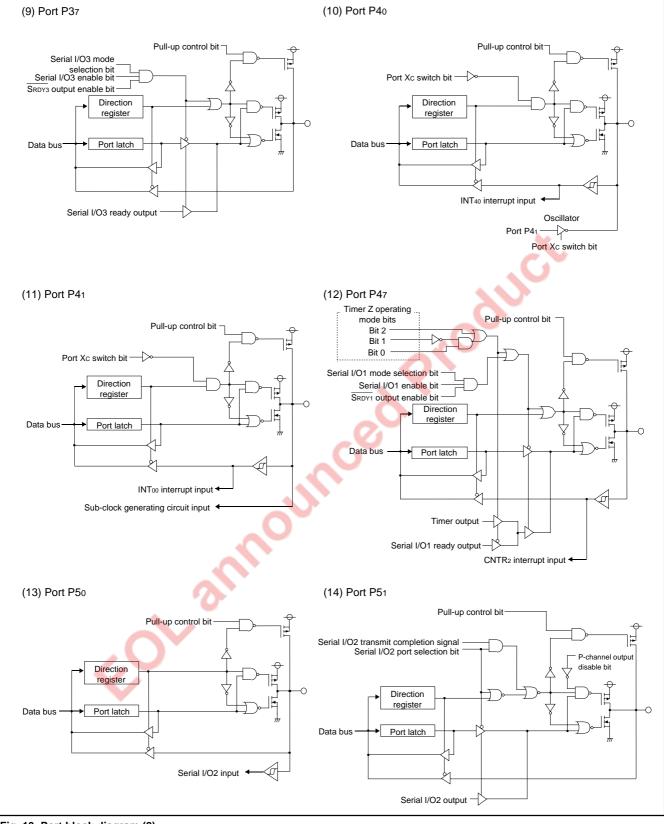

| Fig. 12   | Port block diagram (1)                                                                   | . 1-16 |

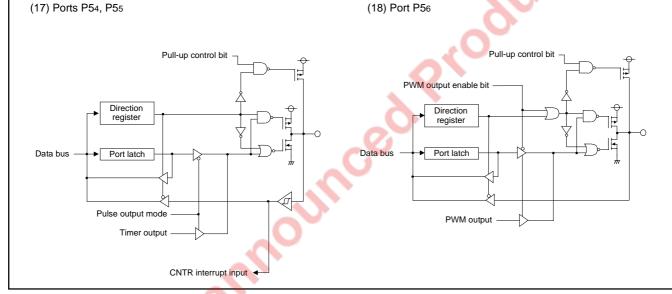

| Fig. 13   | Port block diagram (2)                                                                   | . 1-17 |

| Fig. 14   | Port block diagram (3)                                                                   | . 1-18 |

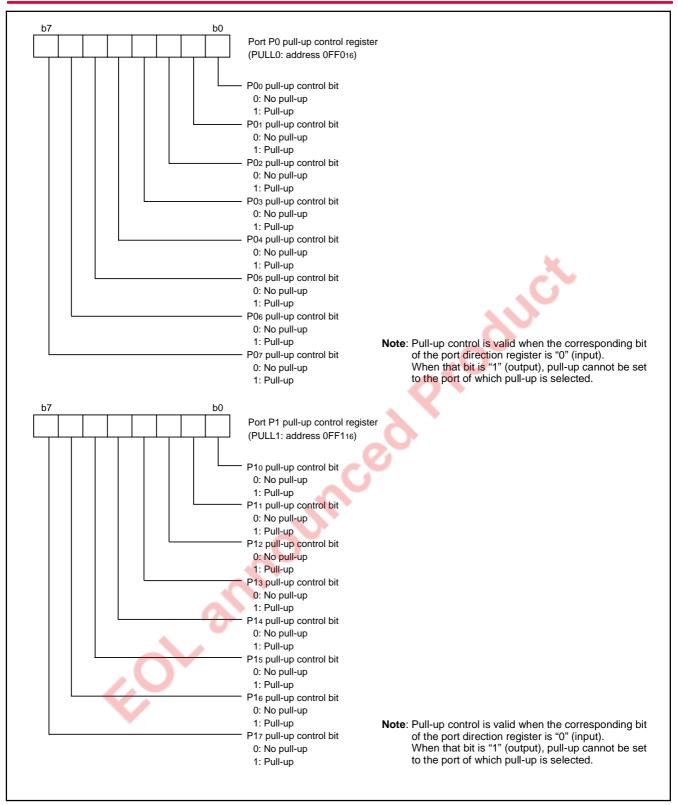

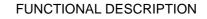

| Fig. 15   | Structure of port pull-up control register (1)                                           | . 1-19 |

| Fig. 16   | Structure of port pull-up control register (2)                                           |        |

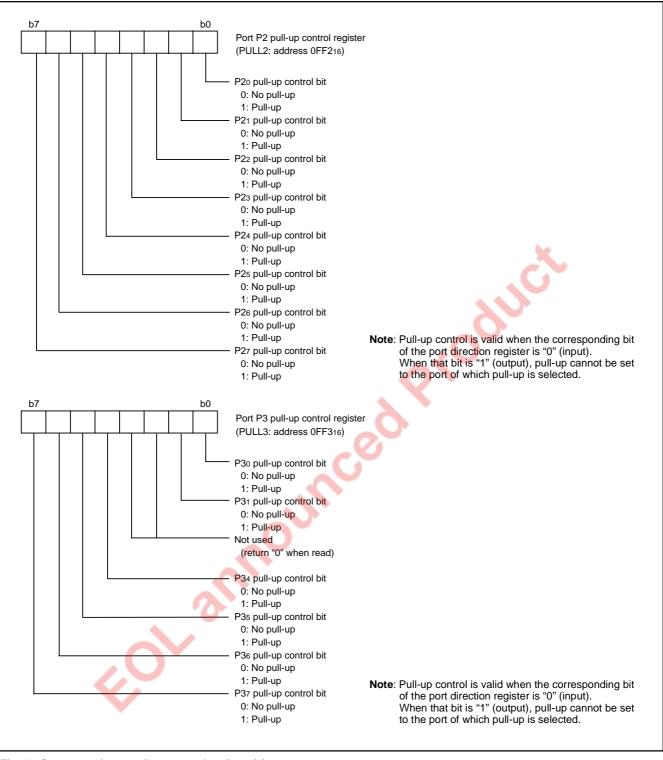

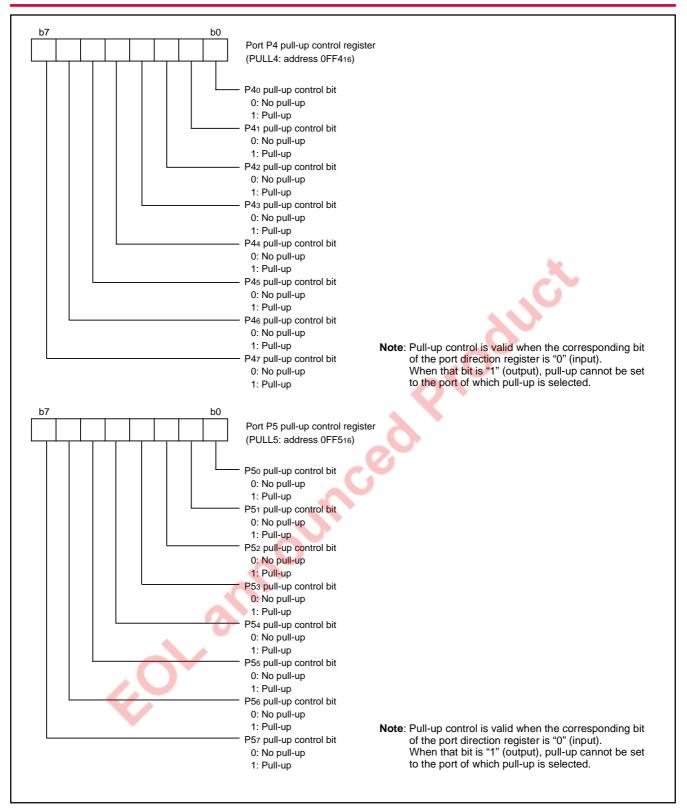

| Fig. 17   | Structure of port pull-up control register (3)                                           | . 1-21 |

| Fig. 18   | Structure of port pull-up control register (4)                                           | . 1-22 |

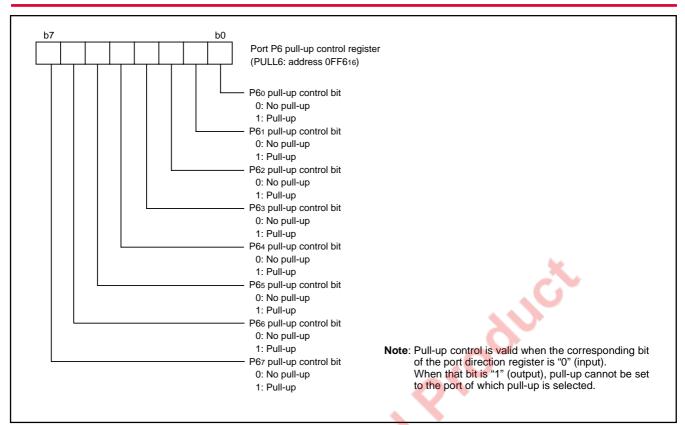

| Fig. 19   | Interrupt control                                                                        | . 1-25 |

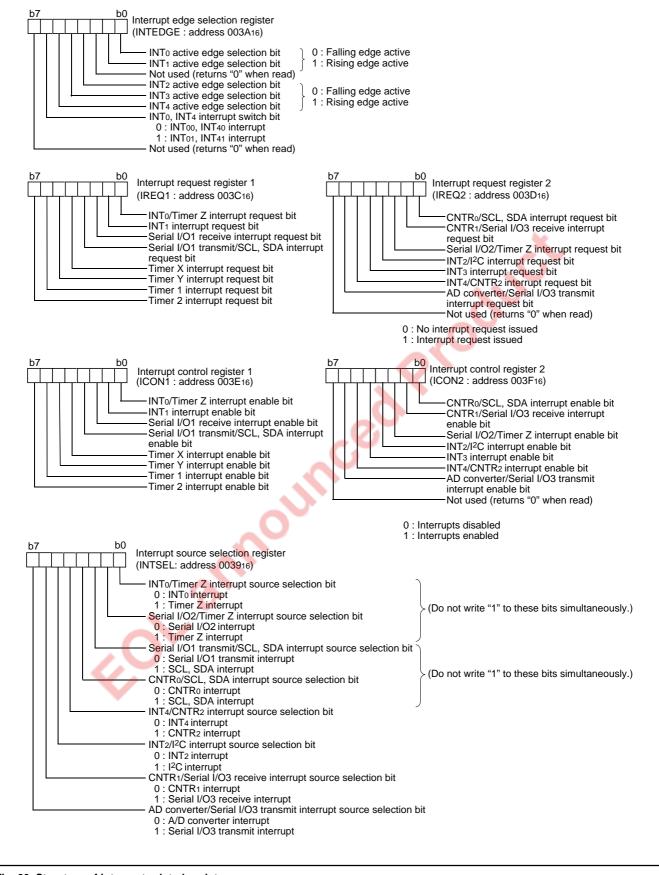

| Fig. 20   | Structure of interrupt-related registers                                                 | . 1-26 |

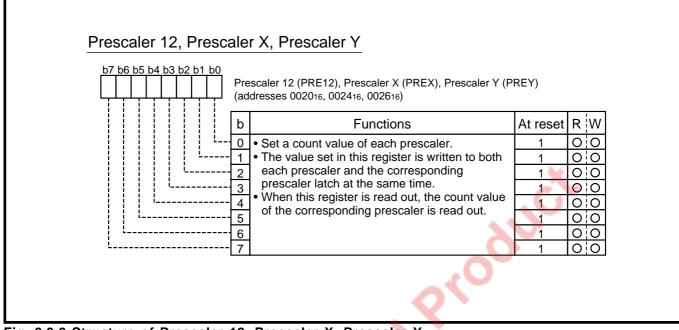

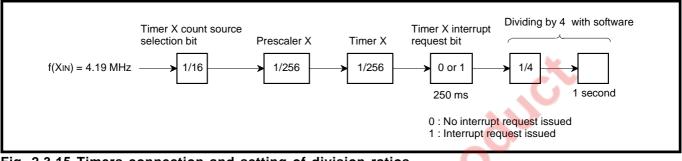

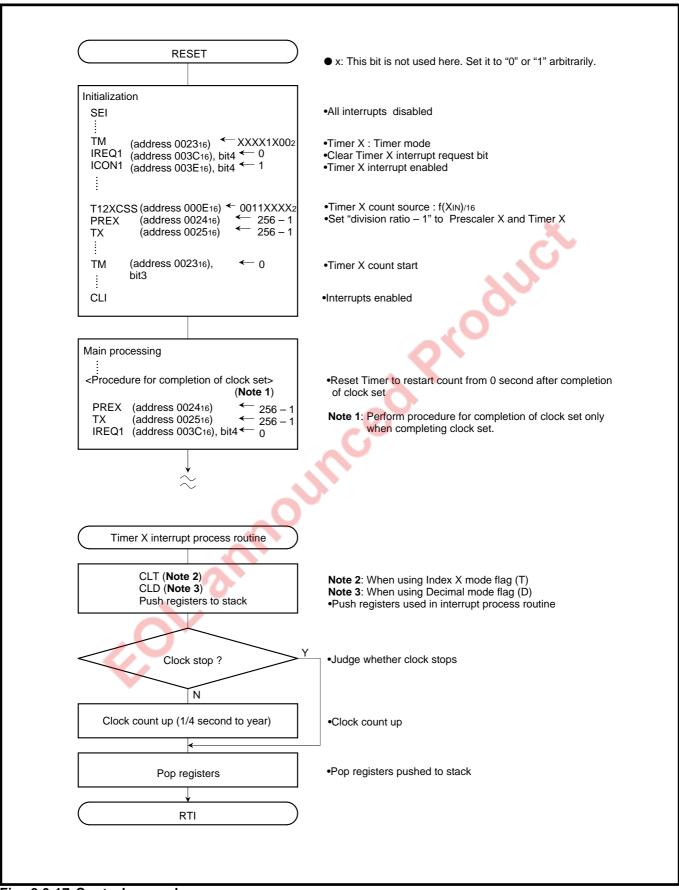

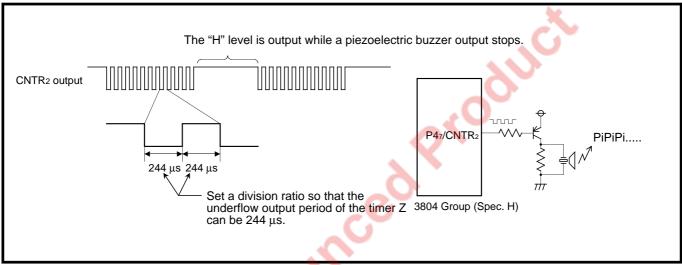

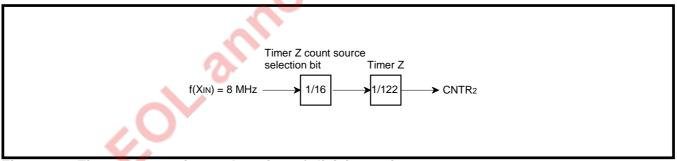

| Fig. 21   | Block diagram of timer X, timer Y, timer 1, and timer 2                                  |        |

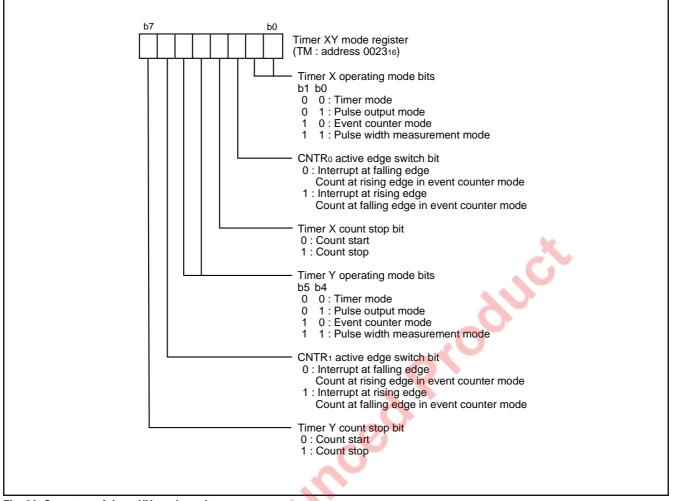

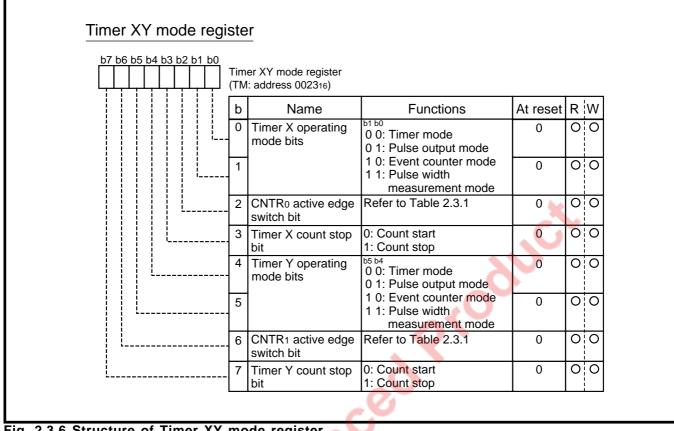

| Fig. 22   | Structure of timer XY mode register                                                      | . 1-30 |

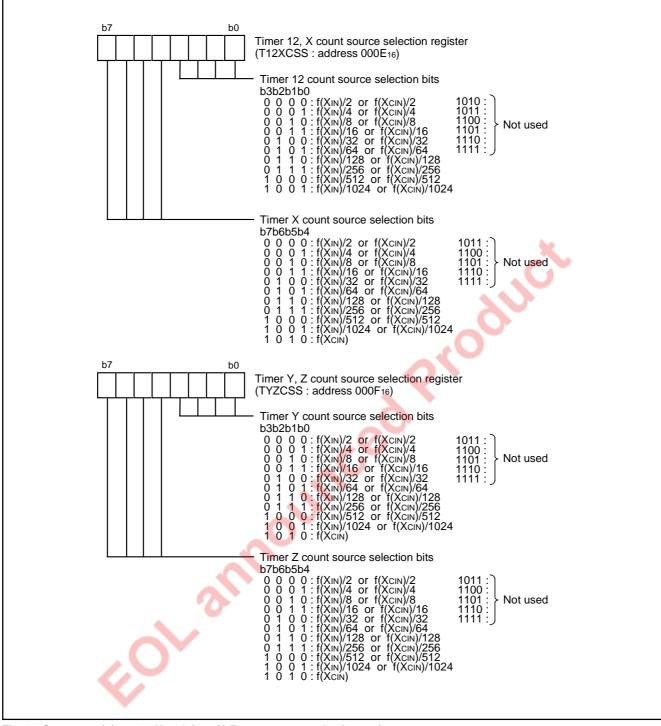

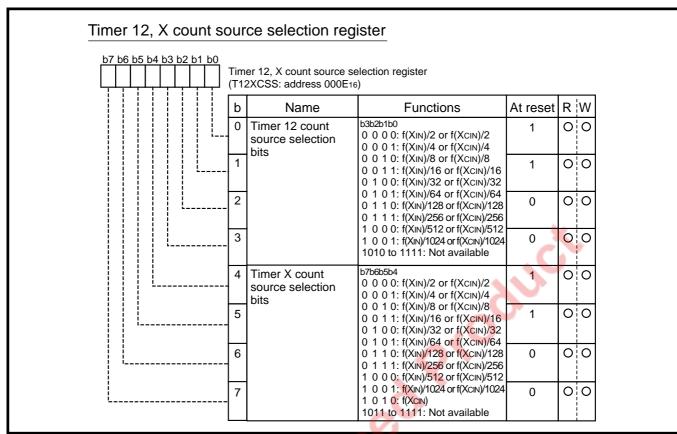

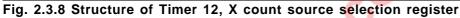

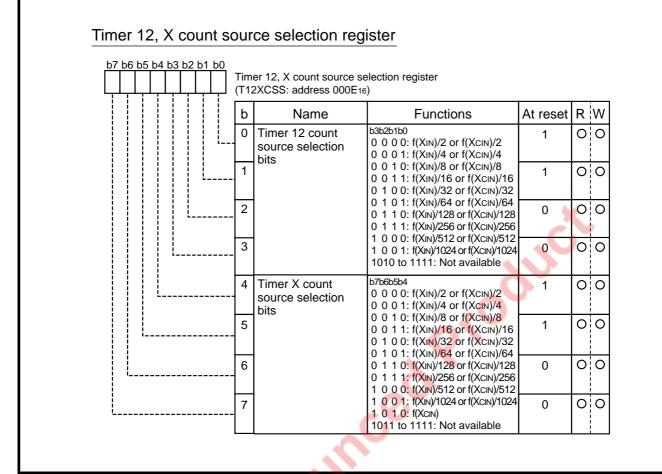

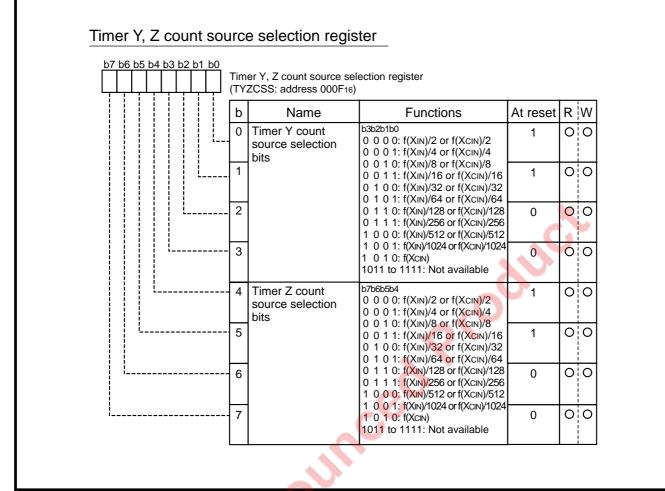

| Fig. 23   | Structure of timer 12, X and timer Y, Z count source selection registers                 | . 1-31 |

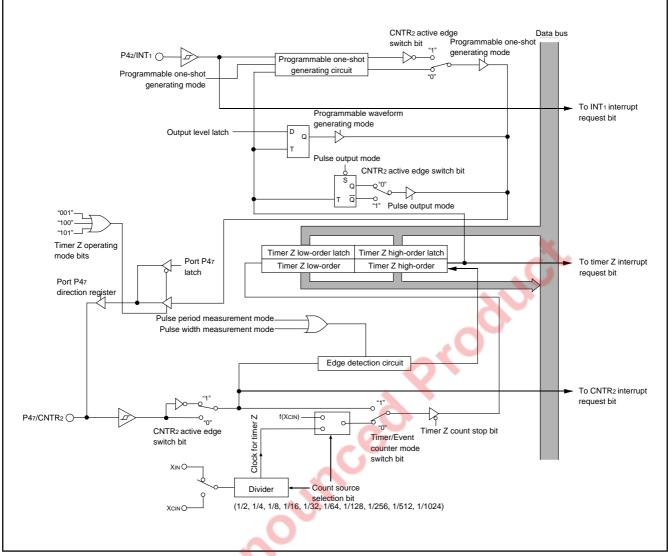

| Fig. 24   | Block diagram of timer Z                                                                 | . 1-35 |

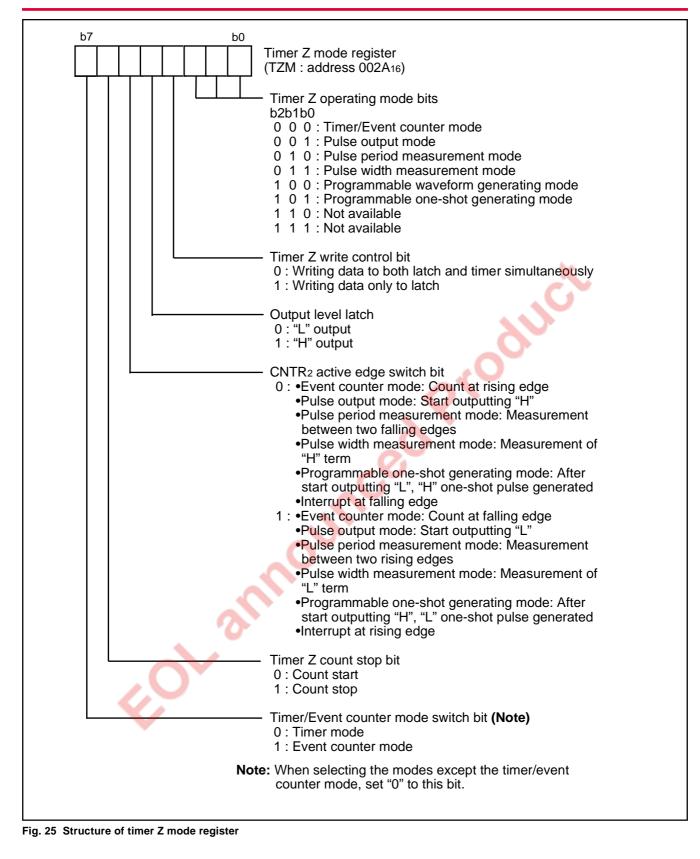

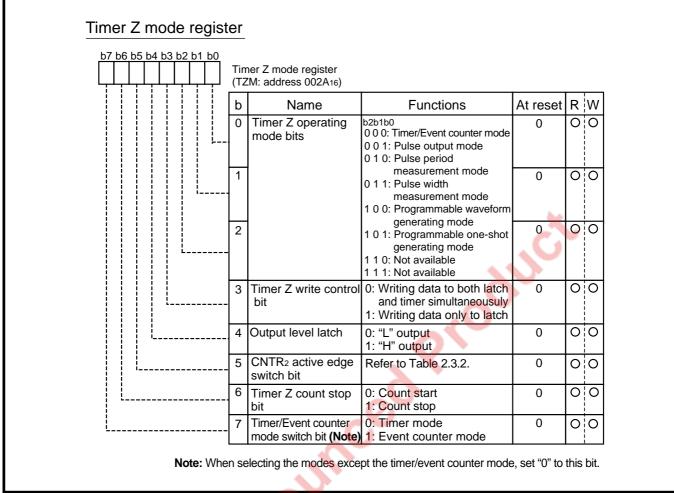

| Fig. 25   | Structure of timer Z mode register                                                       | . 1-36 |

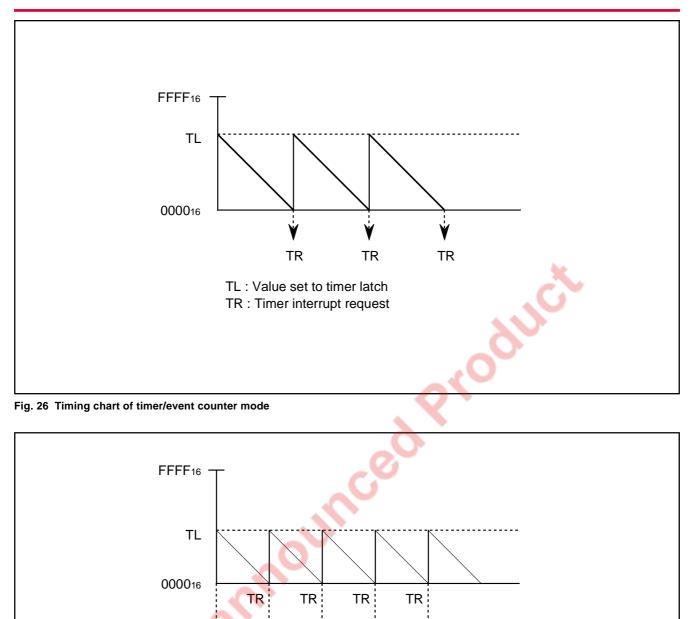

| Fig. 26   | Timing chart of timer/event counter mode                                                 |        |

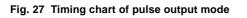

| Fig. 27   | Timing chart of pulse output mode                                                        | . 1-37 |

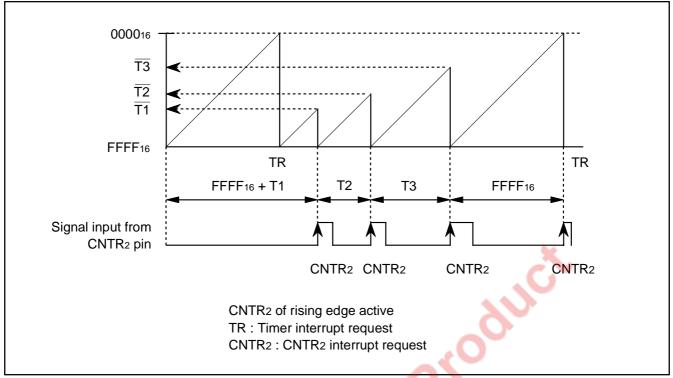

| Fig. 28   | Timing chart of pulse period measurement mode (Measuring term between two rising edges). | . 1-38 |

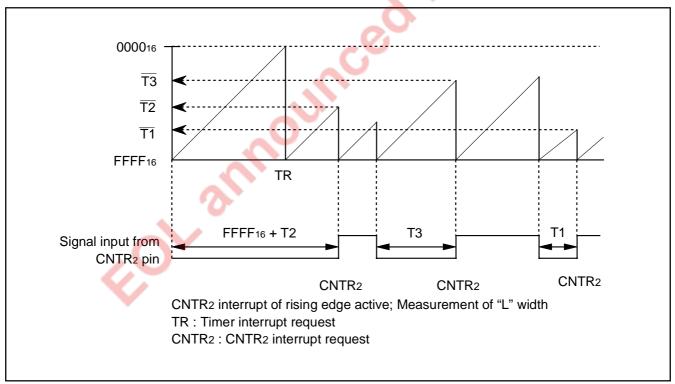

| Fig. 29   | Timing chart of pulse width measurement mode (Measuring "L" term)                        | . 1-38 |

| Fig. 30   | Timing chart of programmable waveform generating mode                                    | . 1-39 |

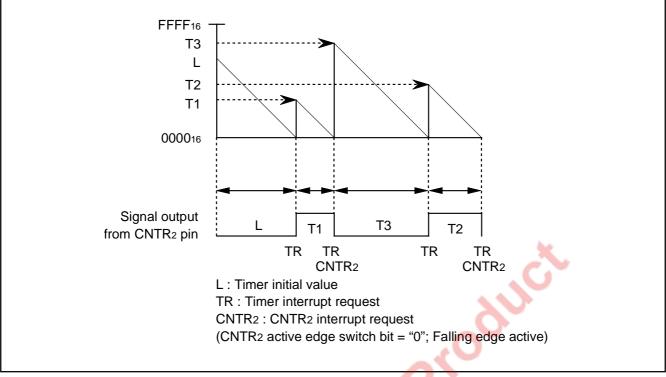

| Fig. 31   | Timing chart of programmable one-shot generating mode ("H" one-shot pulse generating)    | . 1-39 |

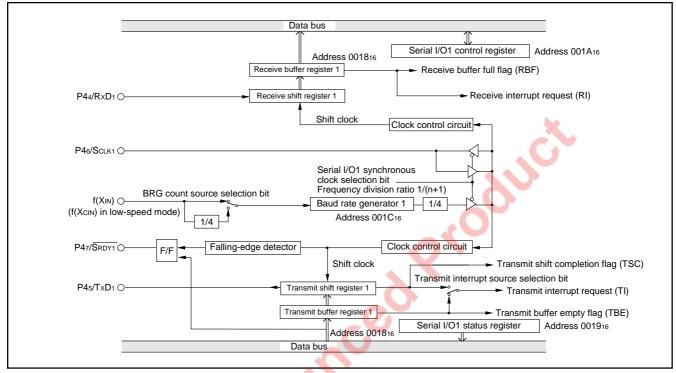

| Fig. 32   | Block diagram of clock synchronous serial I/O1                                           | . 1-40 |

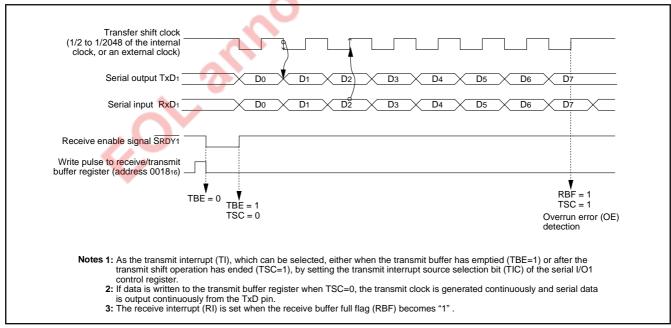

| Fig. 33   | Operation of clock synchronous serial I/O1                                               | . 1-40 |

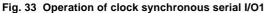

| Fig. 34   | Block diagram of UART serial I/O1                                                        | . 1-41 |

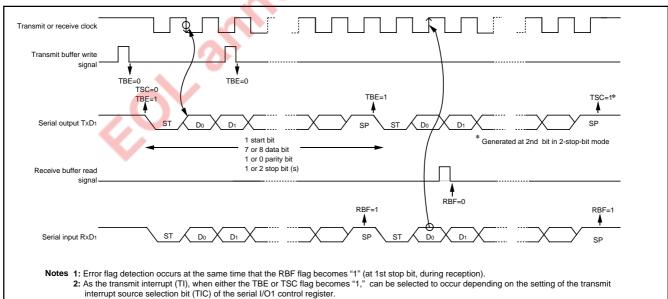

| Fig. 35   | Operation of UART serial I/O1                                                            | . 1-41 |

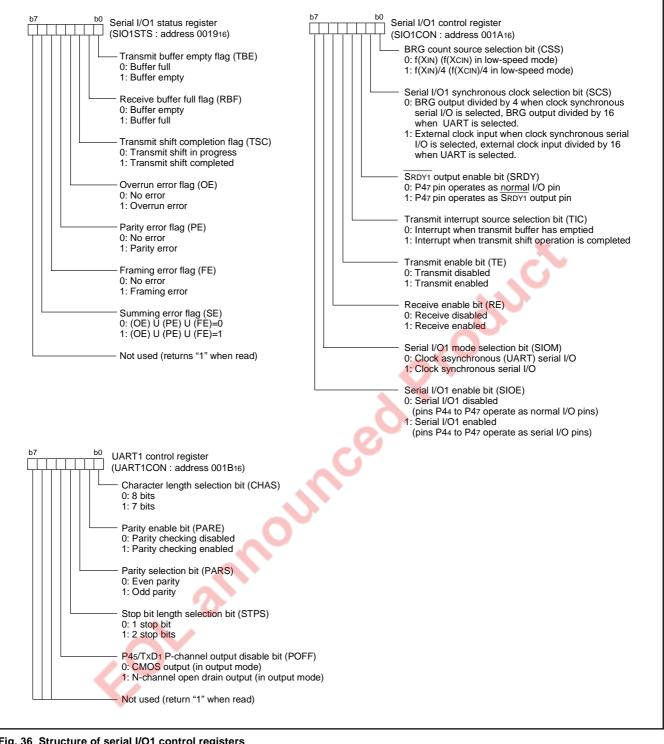

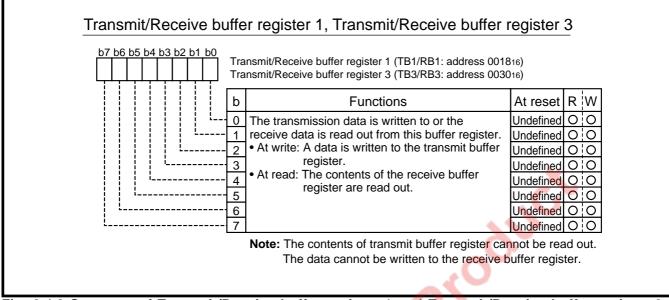

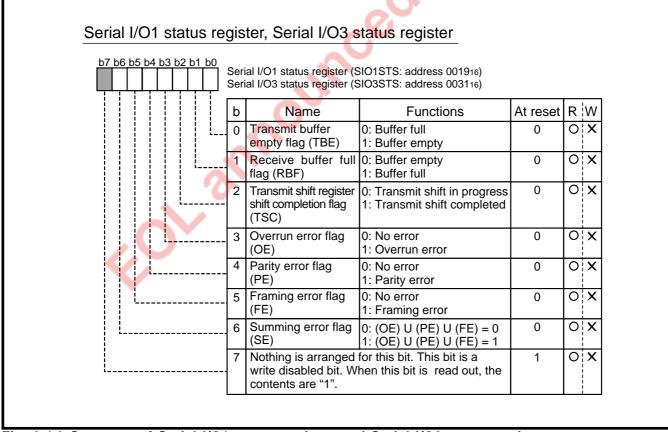

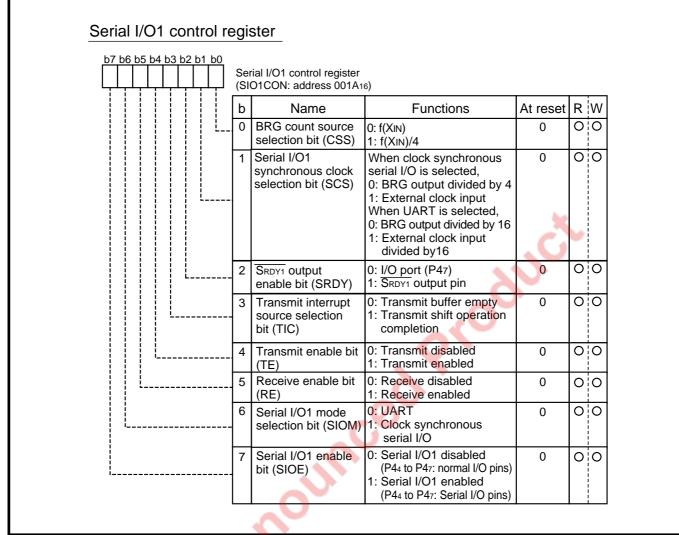

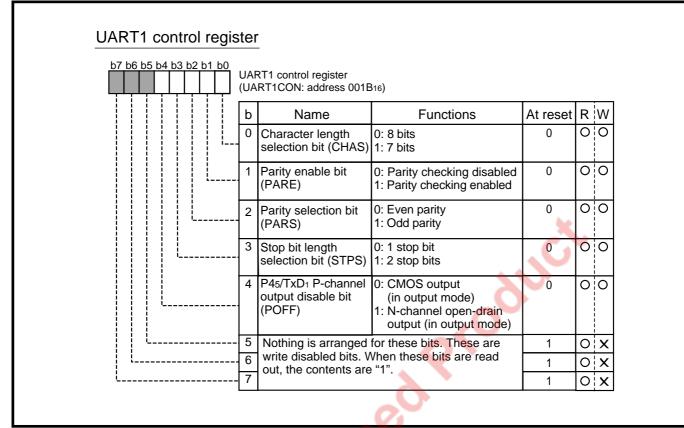

| Fig. 36   | Structure of serial I/O1 control registers                                               | . 1-43 |

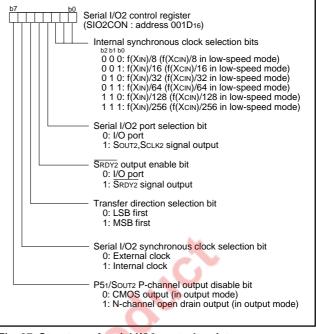

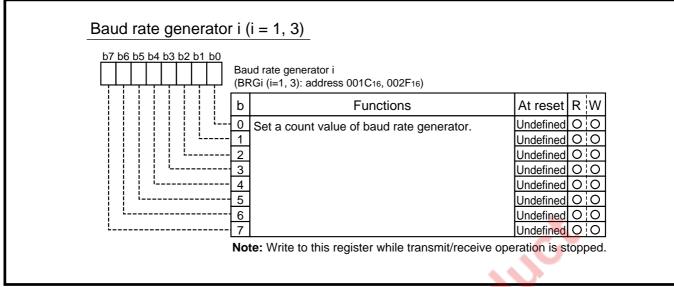

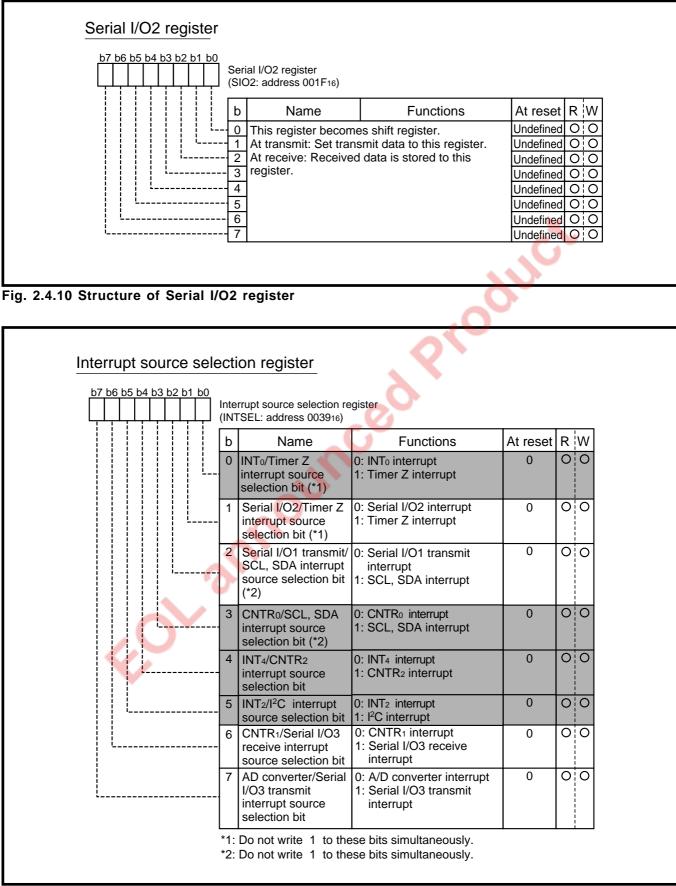

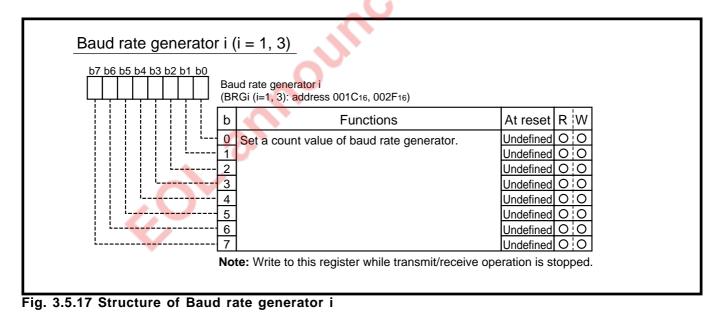

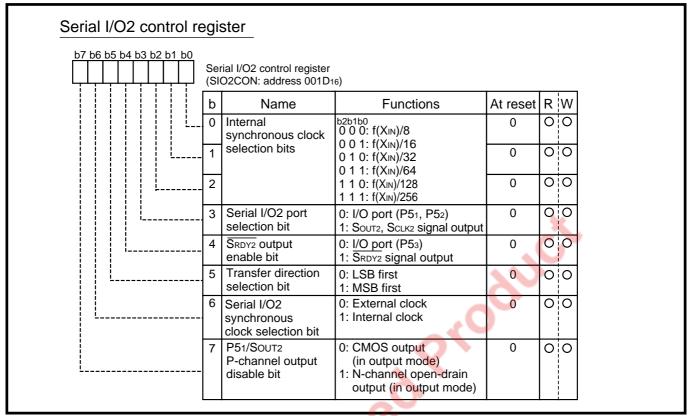

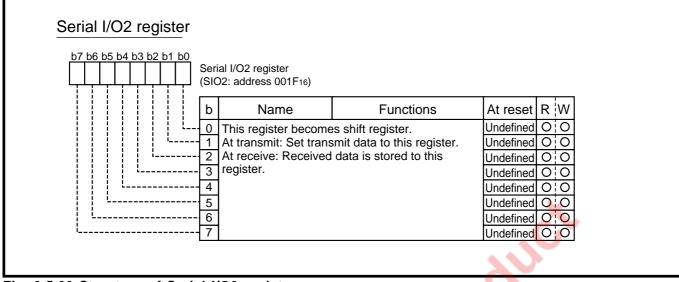

| Fig. 37   | Structure of serial I/O2 control register                                                | . 1-46 |

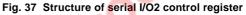

| Fig. 38   | Block diagram of serial I/O2                                                             | . 1-46 |

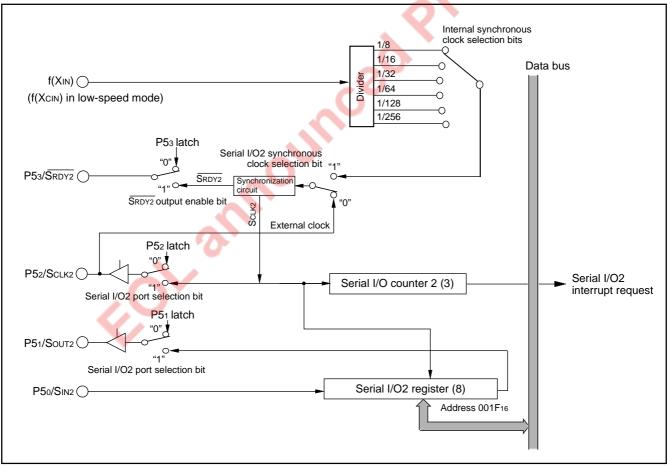

| Fig. 39   | Timing of serial I/O2                                                                    | . 1-47 |

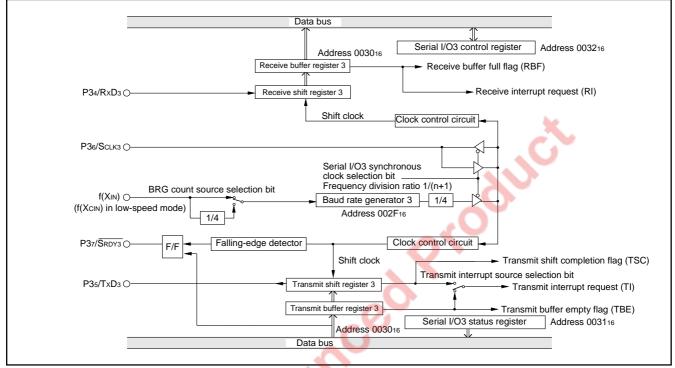

| Fig. 40   | Block diagram of clock synchronous serial I/O3                                           | . 1-48 |

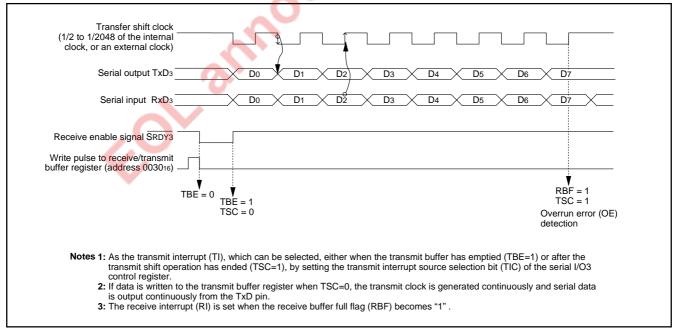

| Fig. 41   | Operation of clock synchronous serial I/O3                                               | . 1-48 |

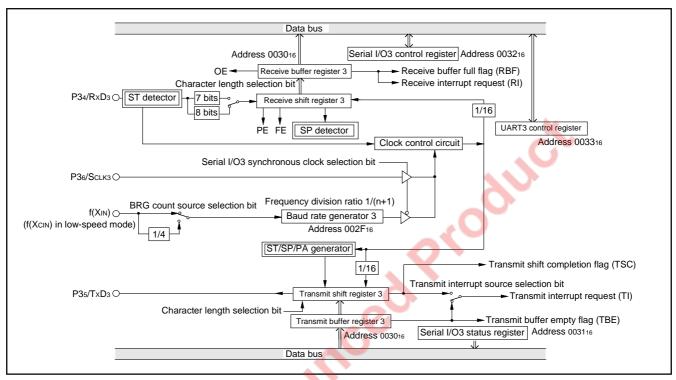

| Fig. 42   | Block diagram of UART serial I/O3                                                        | . 1-49 |

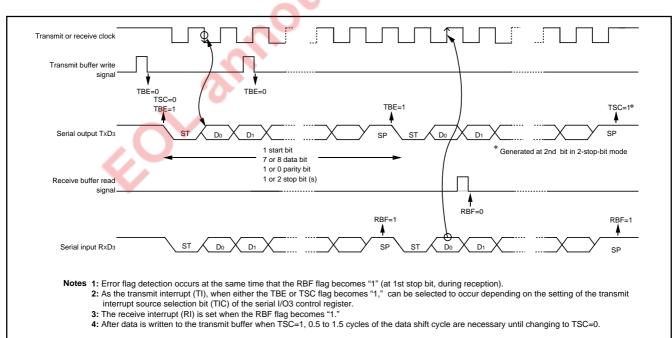

| Fig. 43   | Operation of UART serial I/O3                                                            |        |

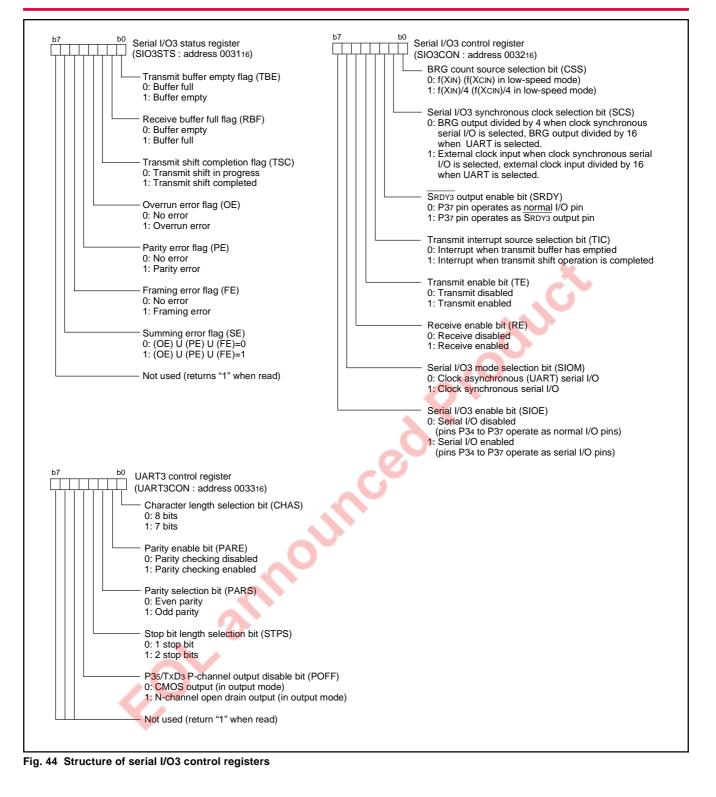

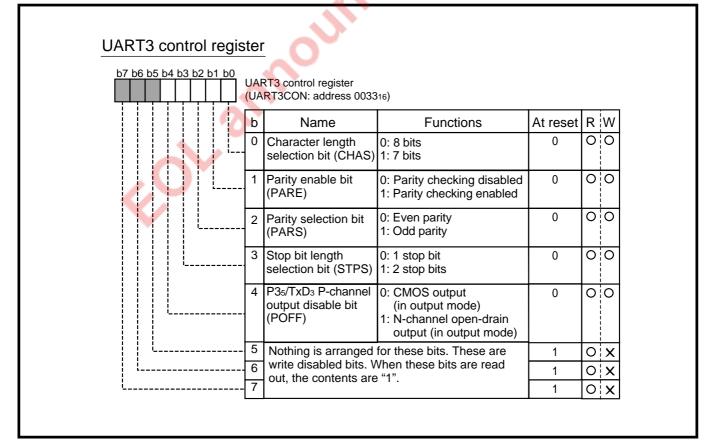

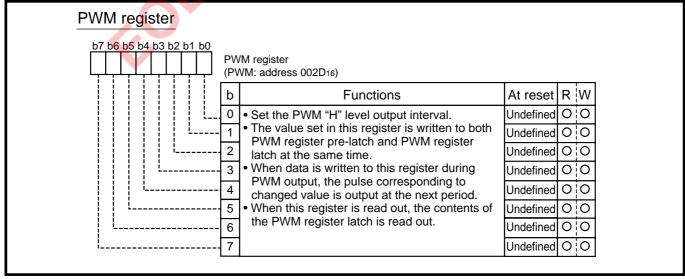

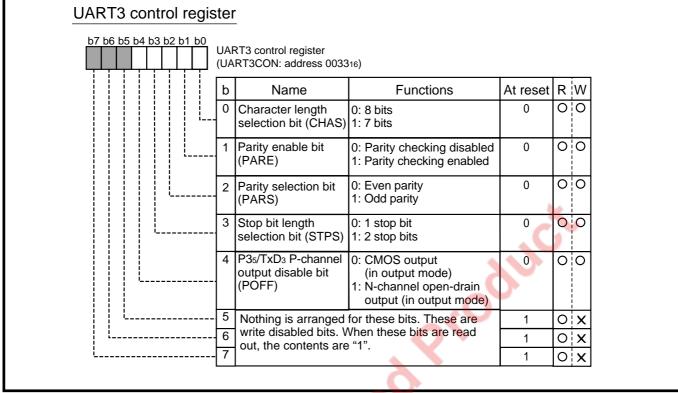

| Fig. 44   | Structure of serial I/O3 control registers                                               | . 1-51 |

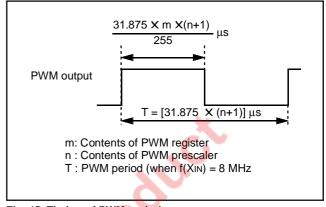

| Fig. 45   | Timing of PWM period                                                                     |        |

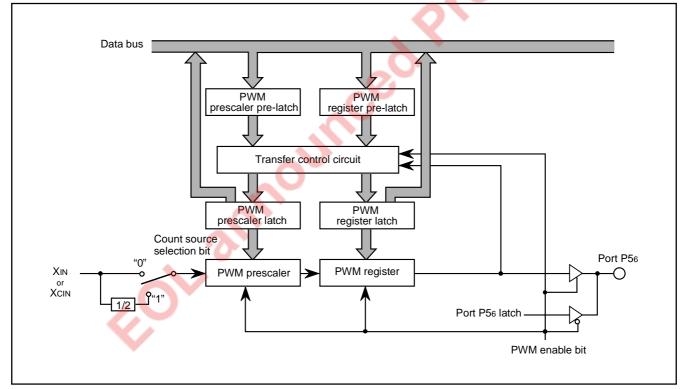

| Fig. 46   | Block diagram of PWM function                                                            |        |

| -         |                                                                                          |        |

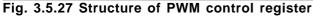

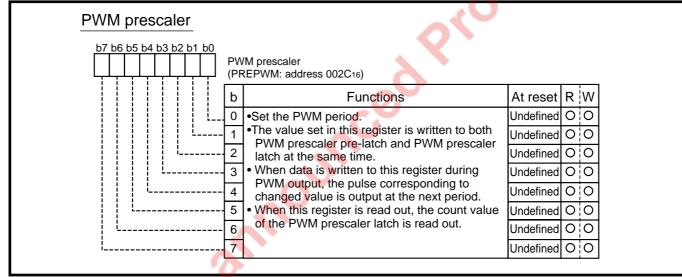

| Fig. 47 | Structure of PWM control register                               | 1-55  |

|---------|-----------------------------------------------------------------|-------|

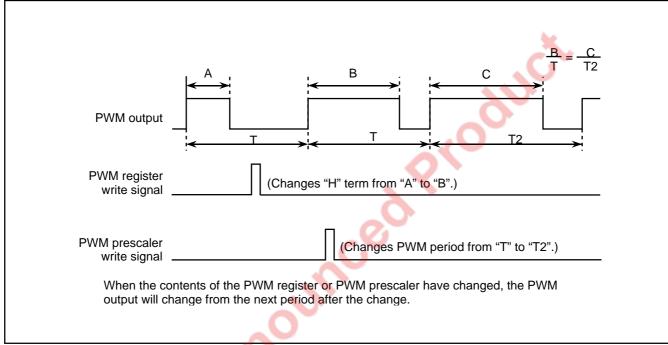

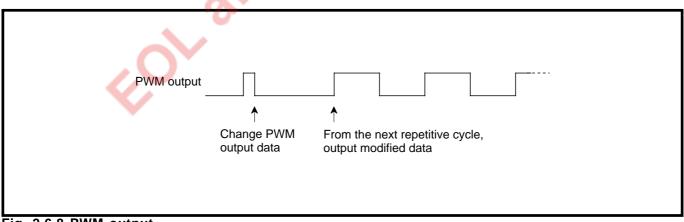

| Fig. 48 | PWM output timing when PWM register or PWM prescaler is changed | 1-55  |

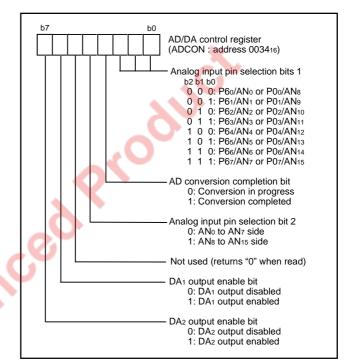

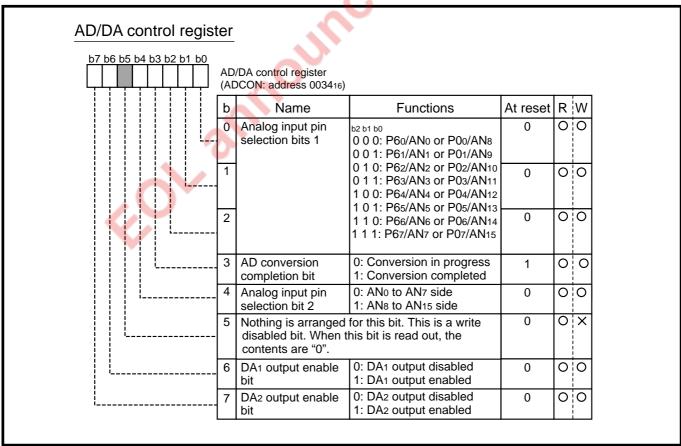

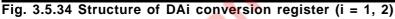

| Fig. 49 | Structure of AD/DA control register                             | 1-56  |

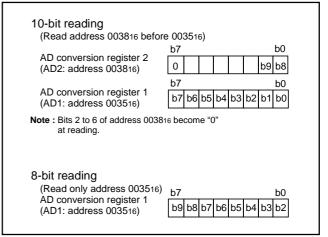

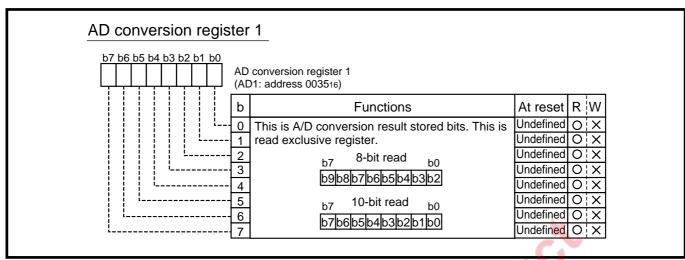

| Fig. 50 | Structure of 10-bit A/D mode reading                            | 1-56  |

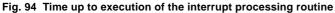

| Fig. 51 | Block diagram of A/D converter                                  | 1-57  |

| Fig. 52 | Block diagram of D/A converter                                  | 1-58  |

| Fig. 53 | Equivalent connection circuit of D/A converter (DA1)            | 1-58  |

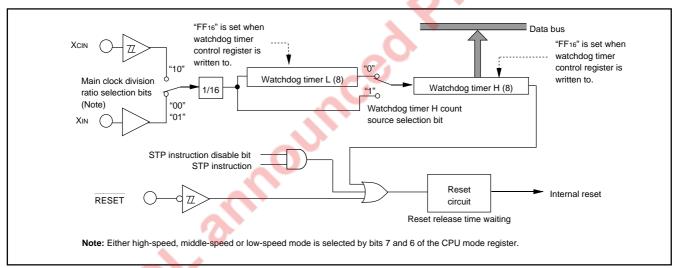

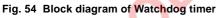

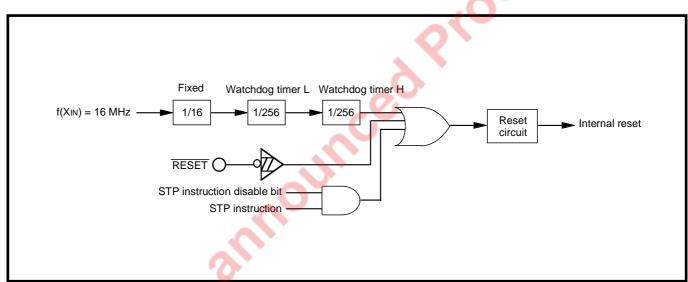

| Fig. 54 | Block diagram of Watchdog timer                                 | 1-59  |

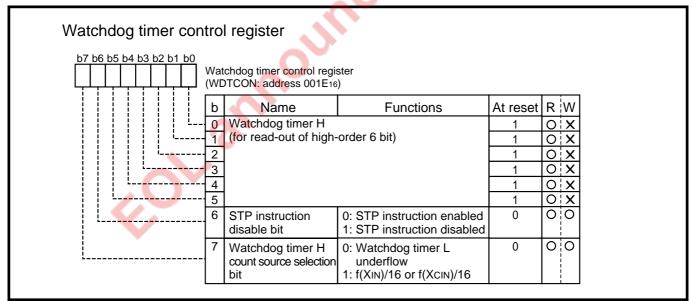

| Fig. 55 | Structure of Watchdog timer control register                    | 1-59  |

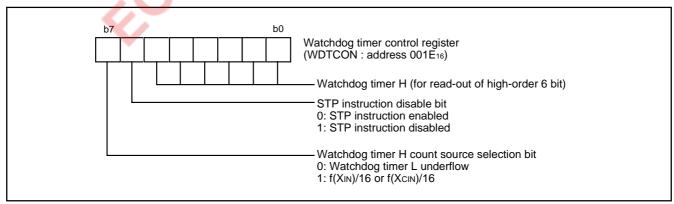

| Fig. 56 |                                                                 |       |

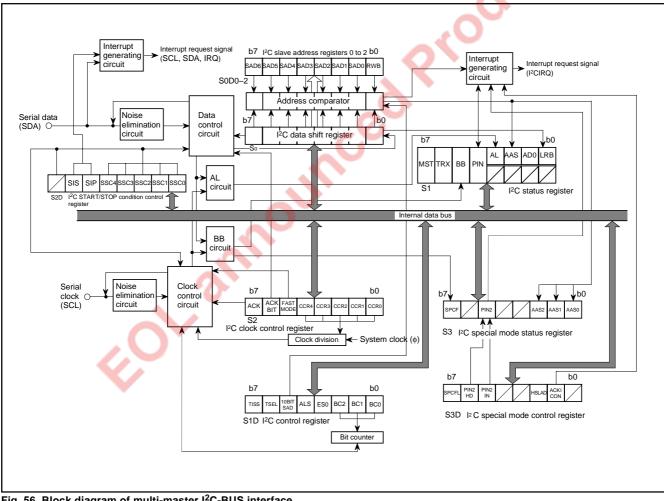

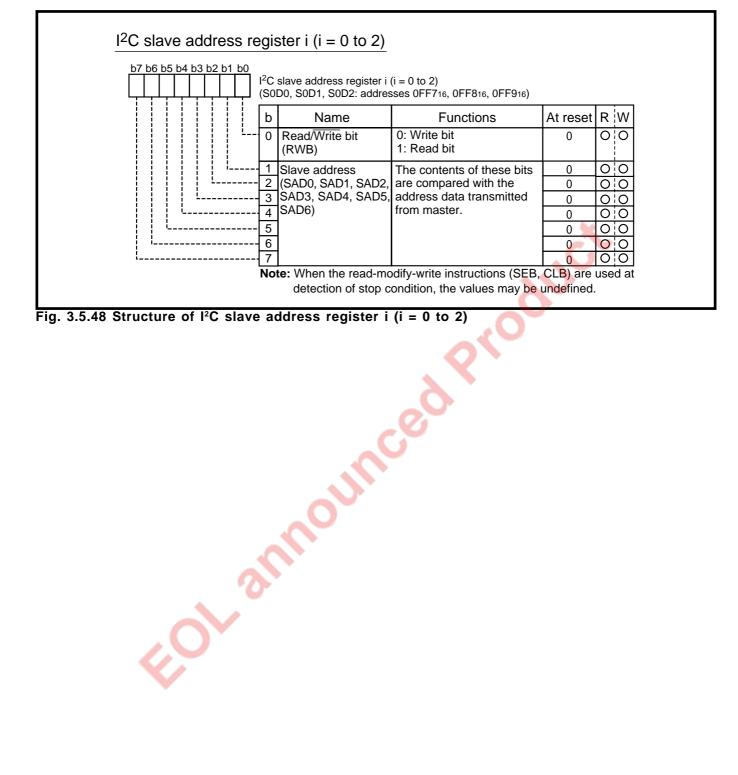

| Fig. 57 | Structure of I <sup>2</sup> C slave address registers 0 to 2    | 1-61  |

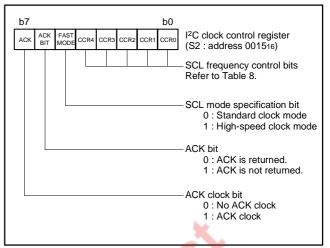

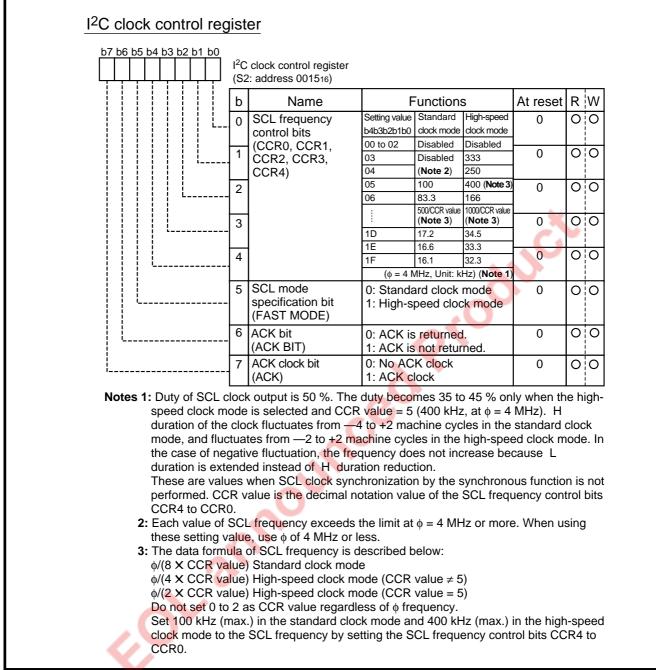

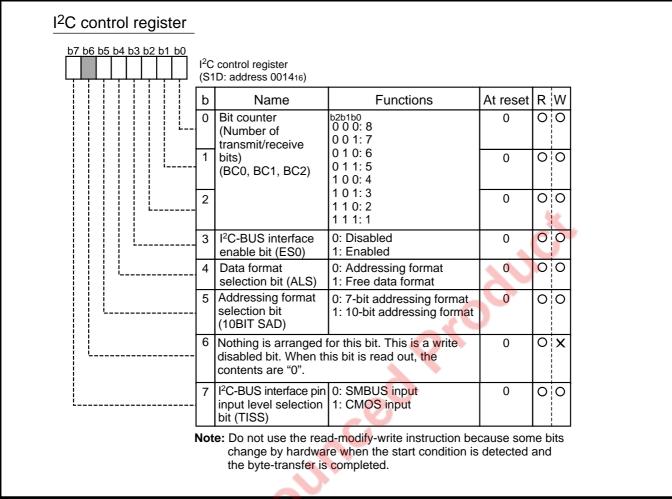

| Fig. 58 | Structure of I <sup>2</sup> C clock control register            | 1-62  |

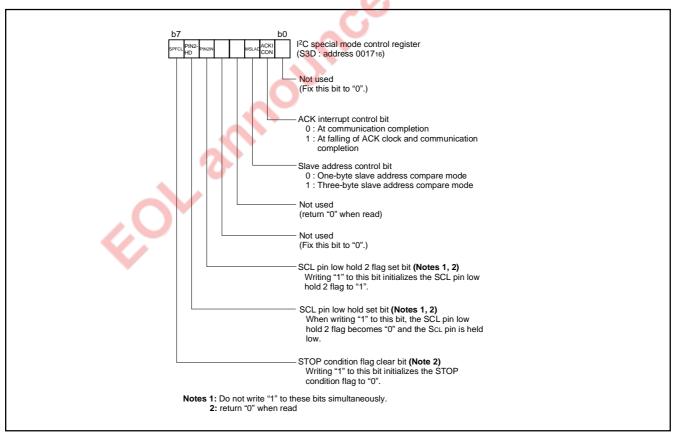

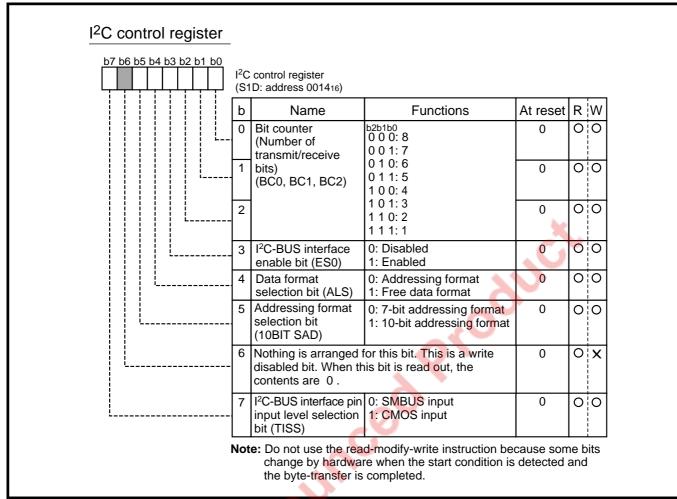

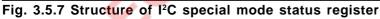

| Fig. 59 | Structure of I <sup>2</sup> C control register                  | 1-63  |

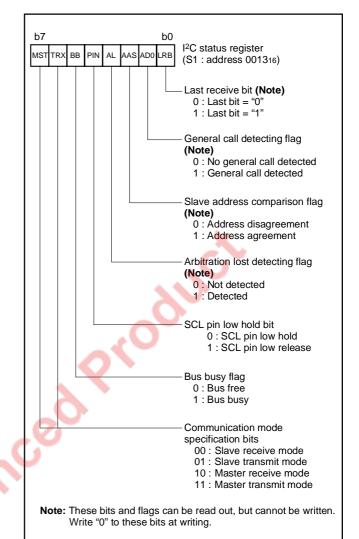

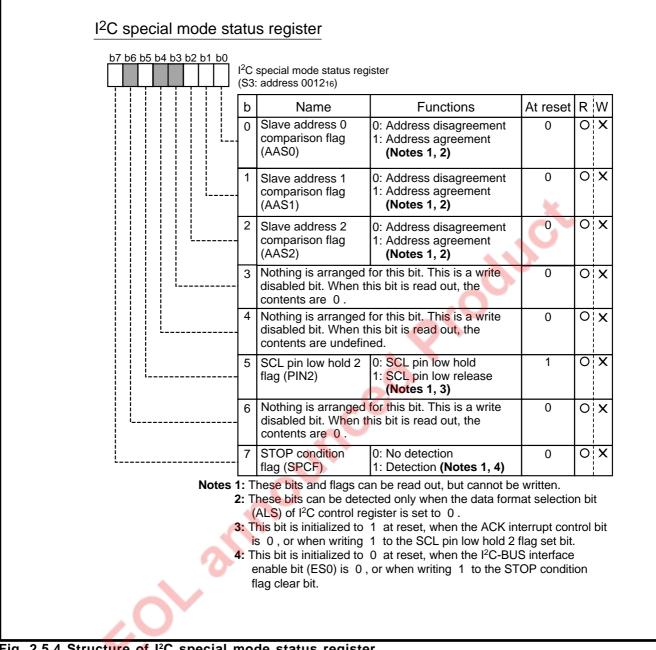

| Fig. 60 | Structure of I <sup>2</sup> C status register                   | 1-65  |

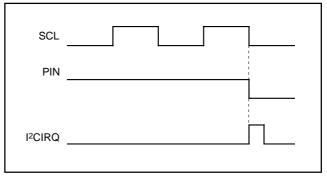

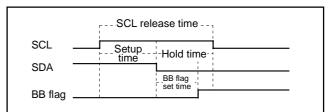

| Fig. 61 | Interrupt request signal generating timing                      | 1-65  |

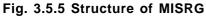

| Fig. 62 |                                                                 |       |

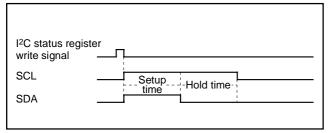

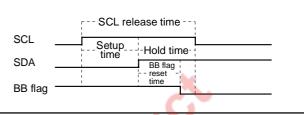

| Fig. 63 | STOP condition generating timing diagram                        | 1-66  |

| Fig. 64 | START/STOP condition detecting timing diagram                   | 1-67  |

| Fig. 65 | STOP condition detecting timing diagram                         | 1-67  |

| Fig. 66 |                                                                 |       |

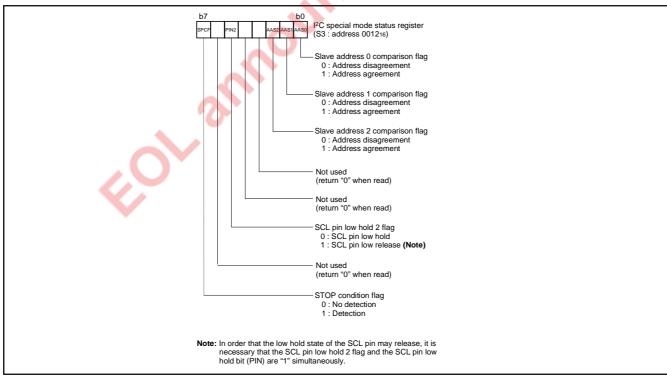

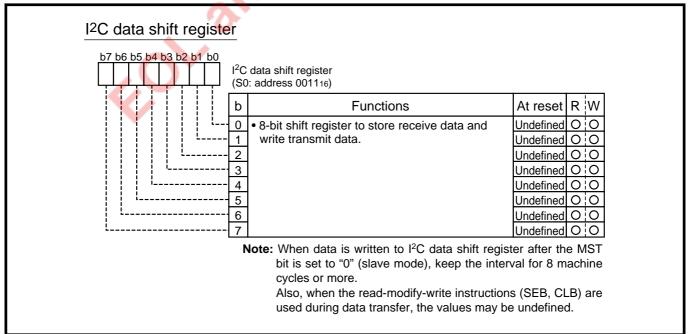

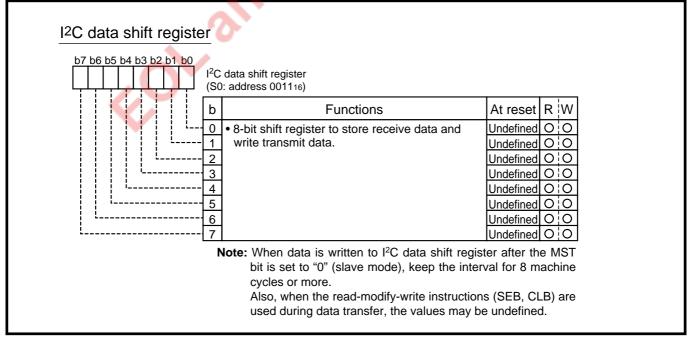

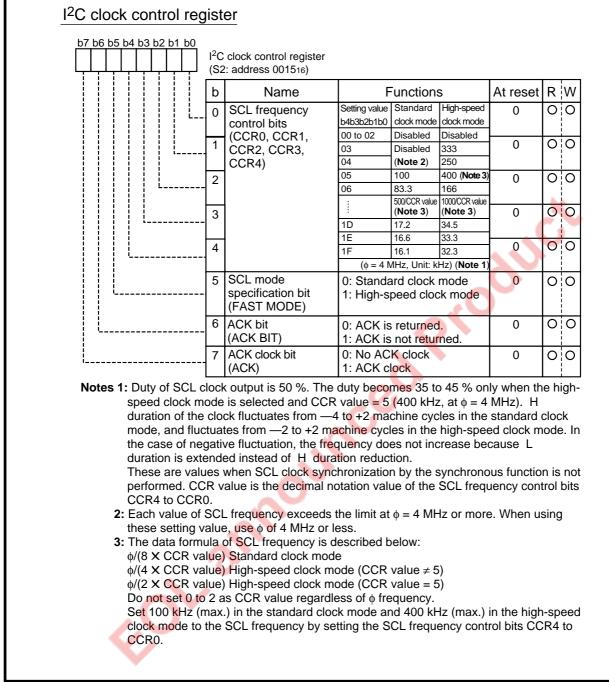

| Fig. 67 | Structure of I <sup>2</sup> C special mode status register      | 1-69  |

| Fig. 68 |                                                                 |       |

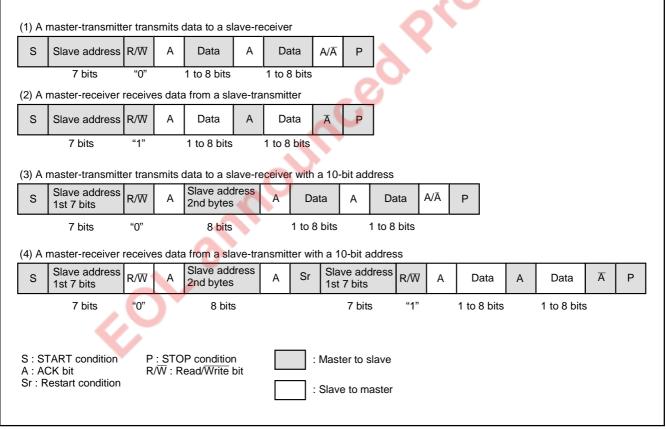

| Fig. 69 | Address data communication format                               | 1-71  |

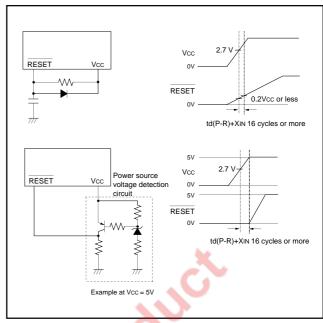

| Fig. 70 | Reset circuit example                                           | 1-74  |

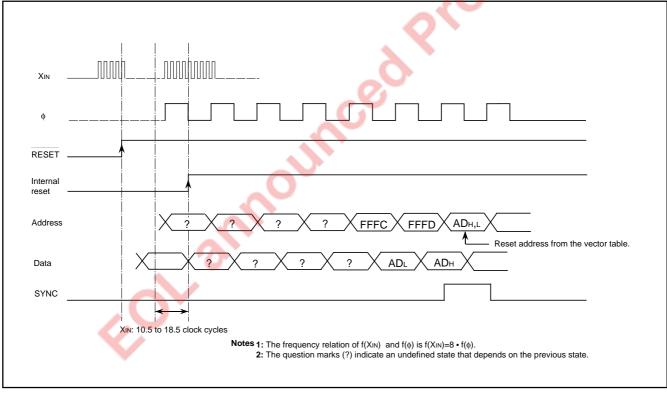

| Fig. 71 | Reset sequence                                                  | 1-74  |

| Fig. 72 | Internal status at reset                                        | 1-75  |

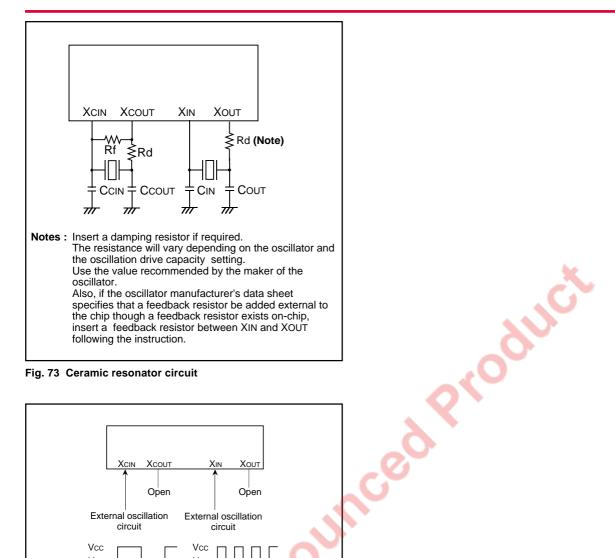

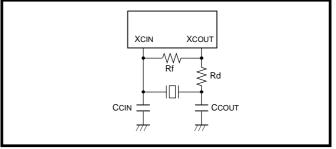

| Fig. 73 | Ceramic resonator circuit                                       | 1-77  |

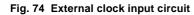

| Fig. 74 | External clock input circuit                                    | 1-77  |

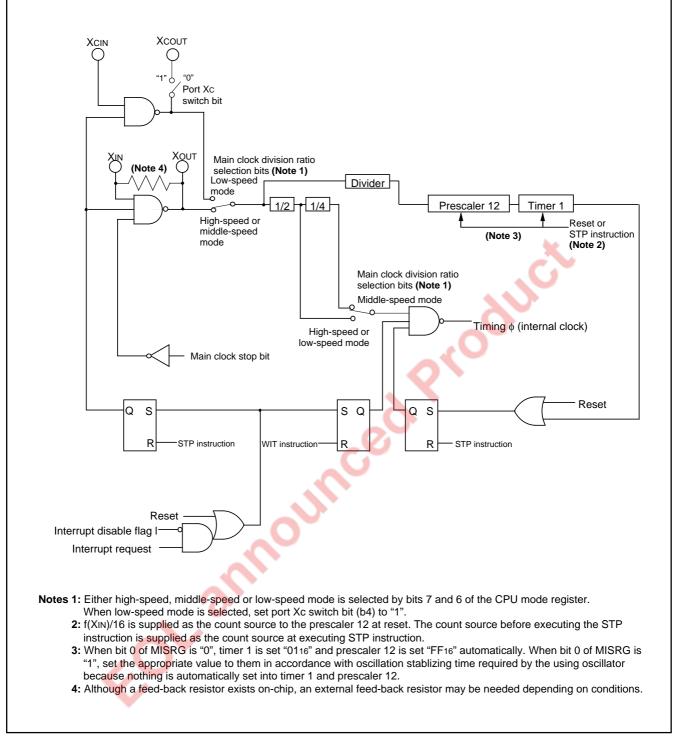

| Fig. 75 | System clock generating circuit block diagram                   | 1-78  |

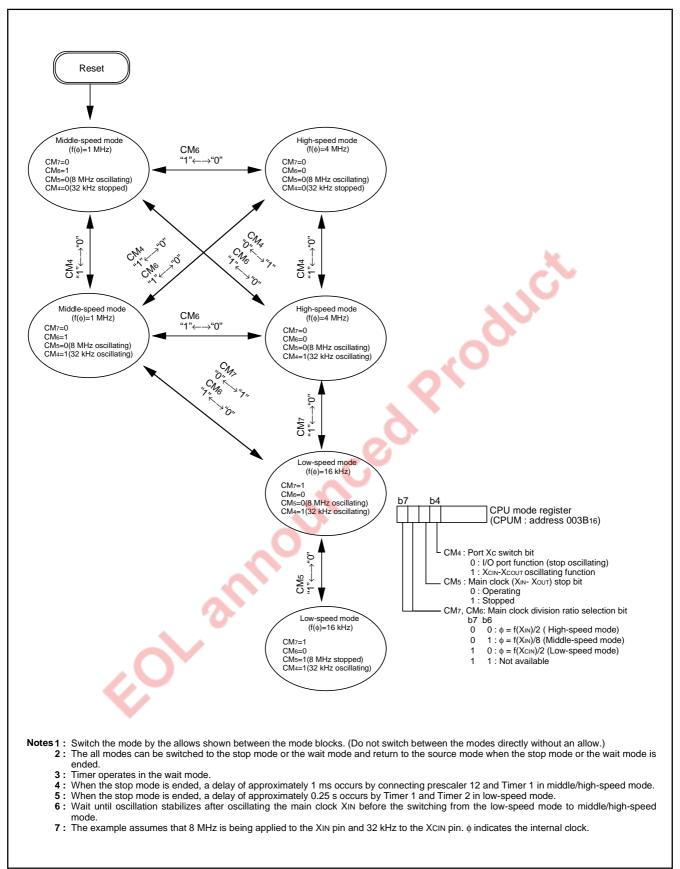

| Fig. 76 | State transitions of system clock                               | 1-79  |

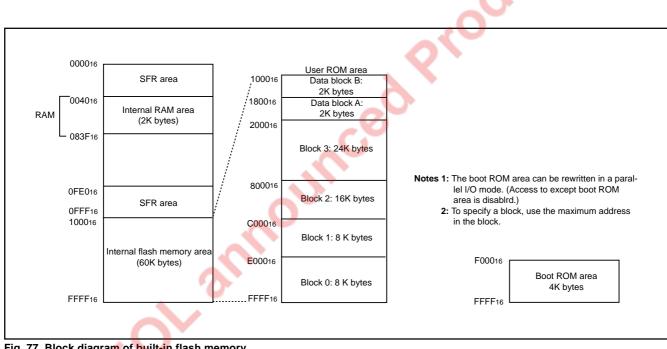

|         | Block diagram of built-in flash memory                          |       |

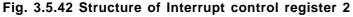

|         | Structure of flash memory control register 0                    |       |

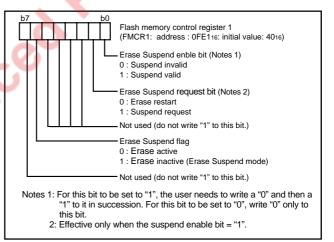

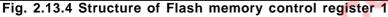

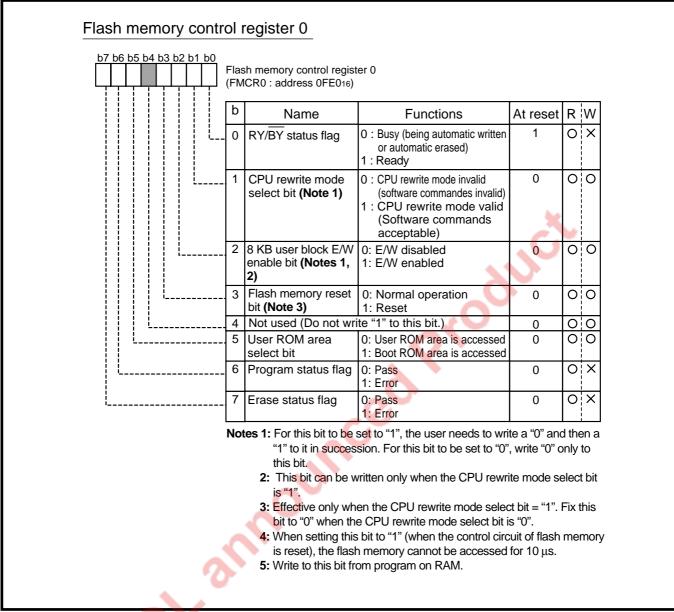

| Fig. 79 | Structure of flash memory control register 1                    | 1-82  |

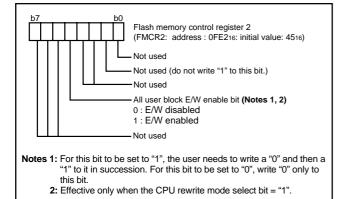

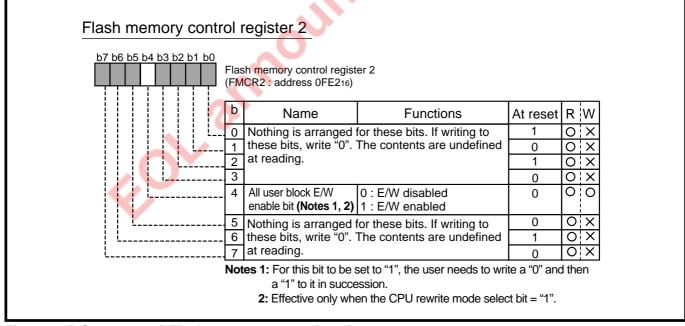

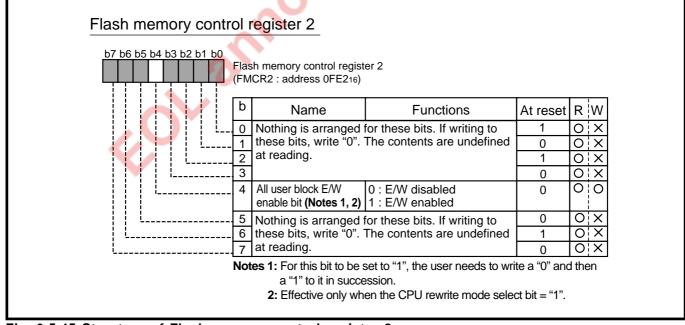

| Fig. 80 | Structure of flash memory control register 2                    | 1-83  |

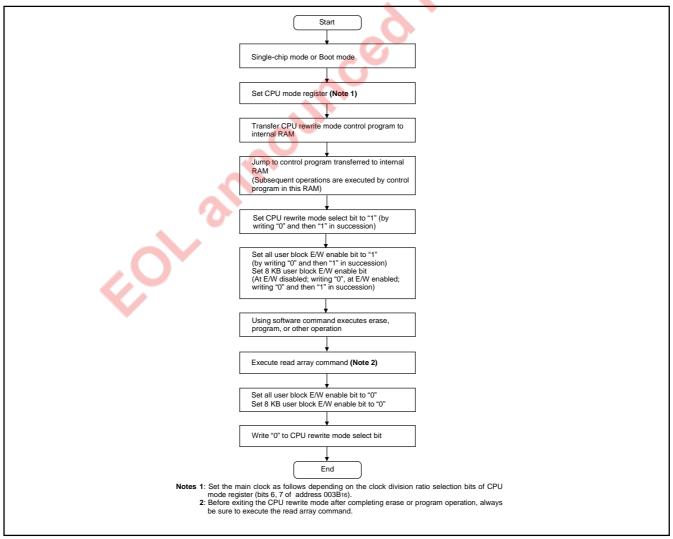

| Fig. 81 | CPU rewrite mode set/release flowchart                          | 1-83  |

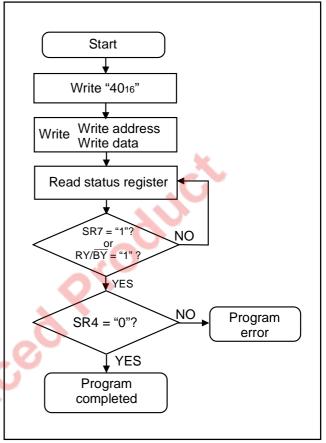

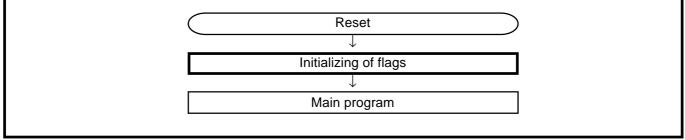

| Fig. 82 | Program flowchart                                               | 1-85  |

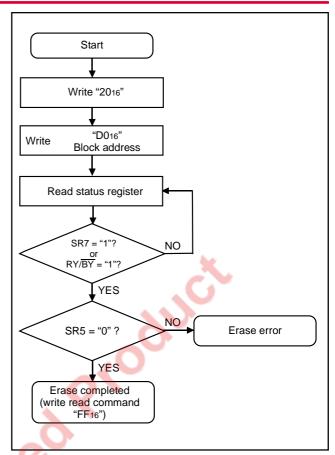

| Fig. 83 | Erase flowchart                                                 | 1-86  |

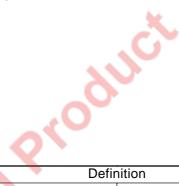

| Fig. 84 | Full status check flowchart and remedial procedure for errors   | 1-88  |

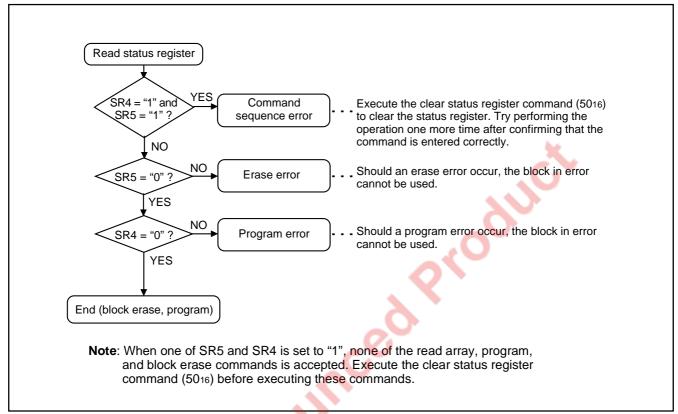

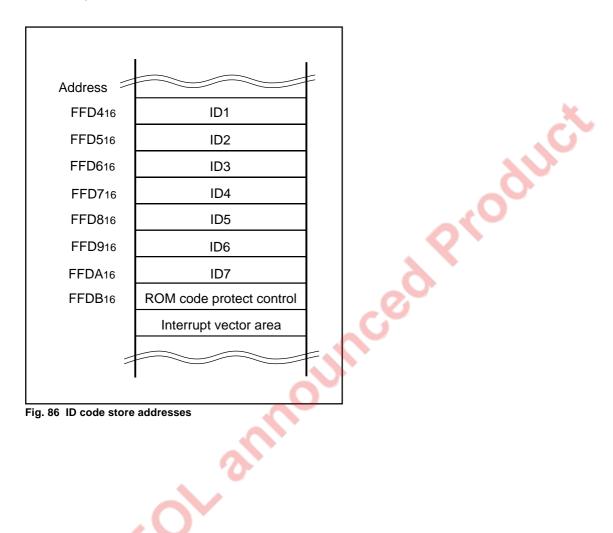

| Fig. 85 | Structure of ROM code protect control address                   | 1-89  |

| Fig. 86 |                                                                 |       |

| Fig. 87 |                                                                 |       |

| Fig. 88 | Connection for standard serial I/O mode 2 (M38049FFHFP/HP/KP)   | 1-95  |

| Fig. 89 | Connection for standard serial I/O mode 1 (M38049FFHSP)         |       |

| Fig. 90 | Connection for standard serial I/O mode 2 (M38049FFHSP)         | 1-97  |

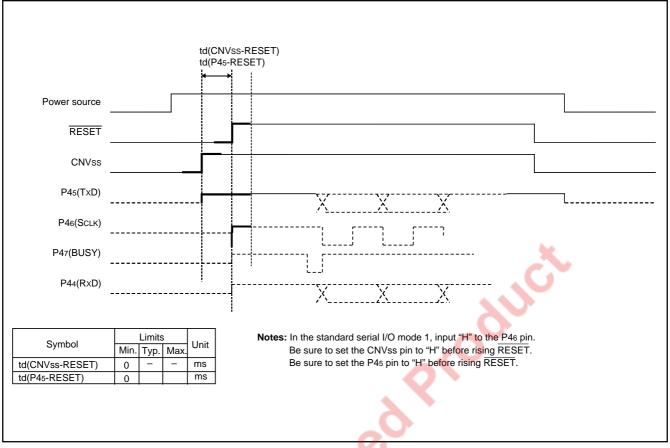

| Fig. 91 | Operating waveform for standard serial I/O mode 1               | 1-98  |

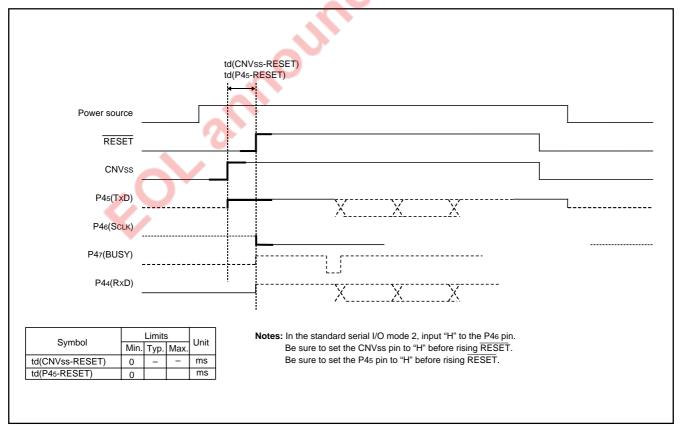

| Fig. 92 |                                                                 |       |

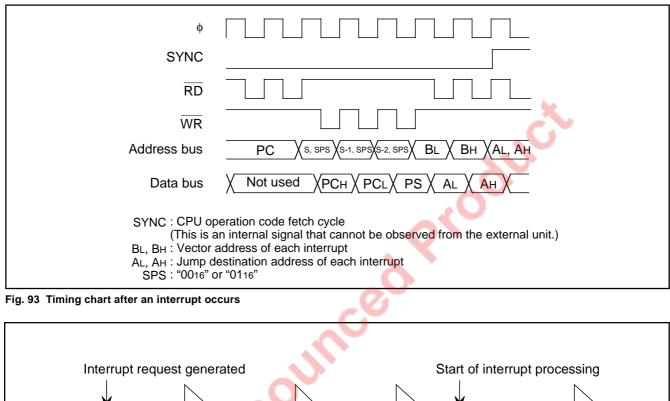

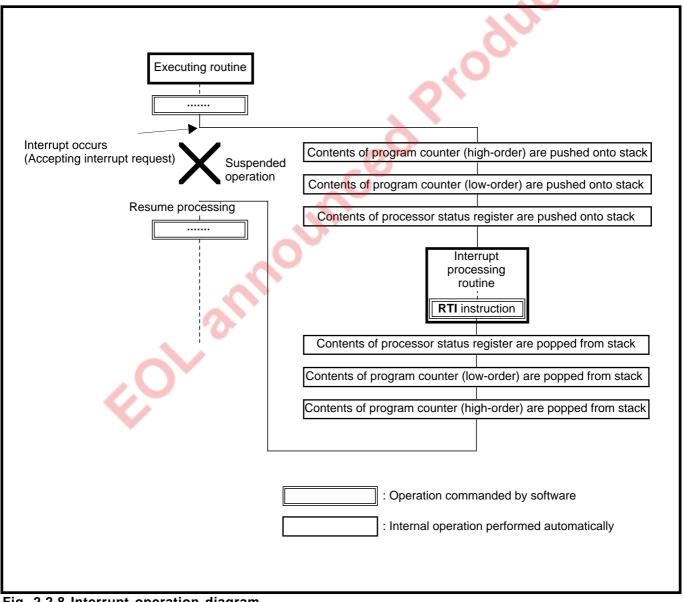

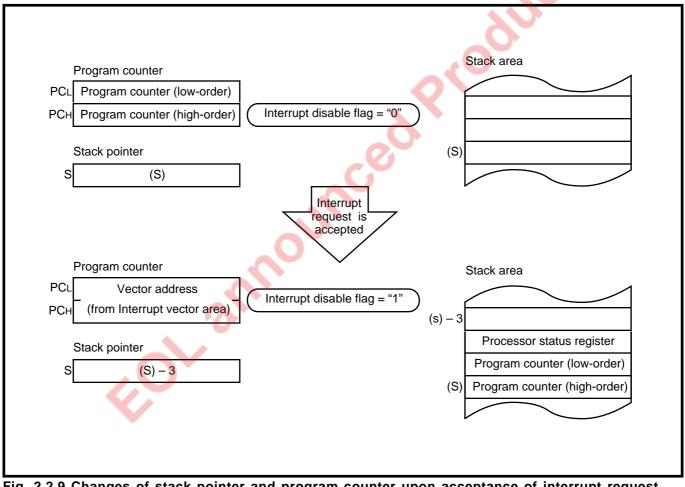

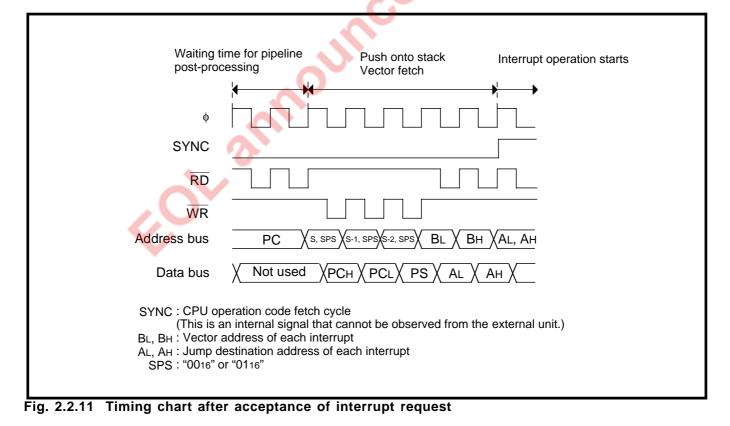

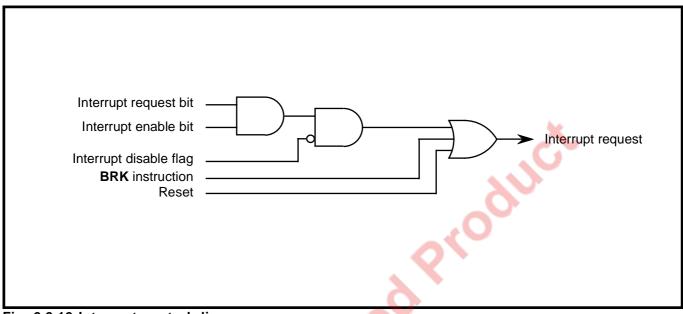

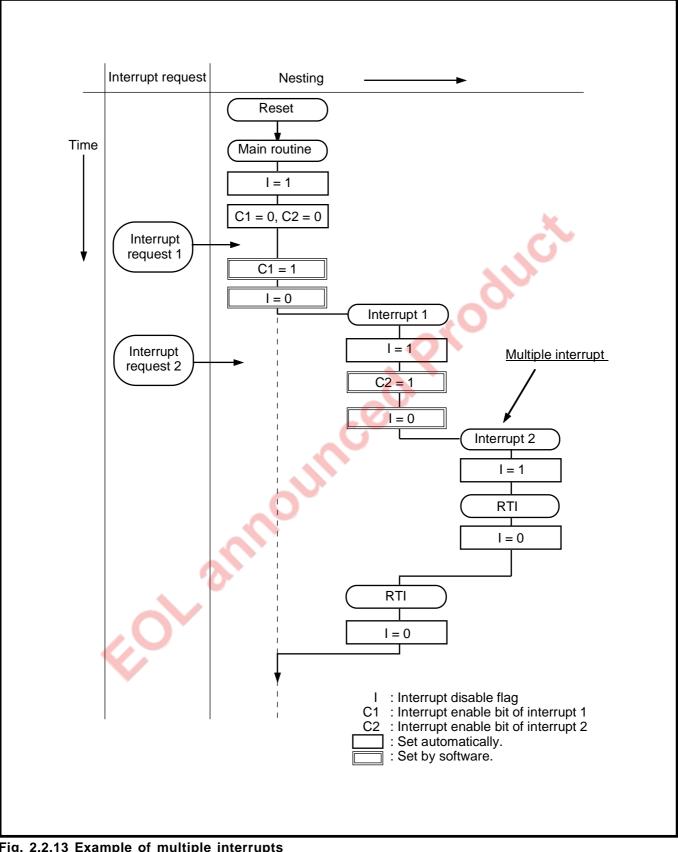

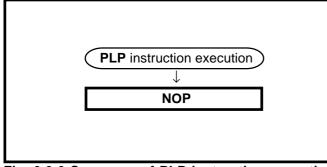

| Fig. 93 | Timing chart after an interrupt occurs                          | 1-102 |

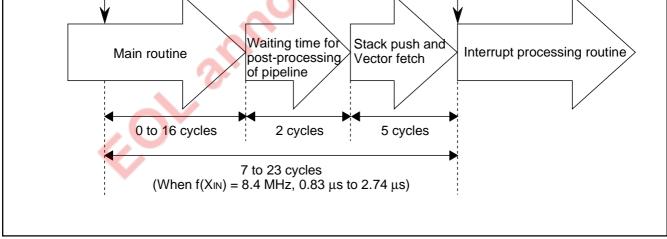

| Fig. 94 |                                                                 |       |

| -       | A/D conversion equivalent circuit                               |       |

| Fia. 96 | A/D conversion timing chart                                     | 1-105 |

#### CHAPTER 2 APPLICATION

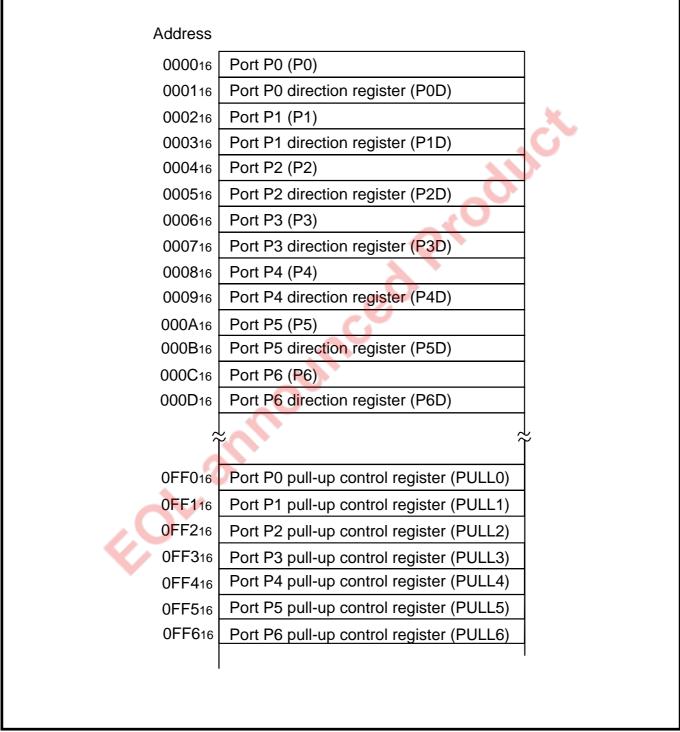

| Fig. 2.1.1 Memory map of I/O port relevant registers                                              | 2-2  |

|---------------------------------------------------------------------------------------------------|------|

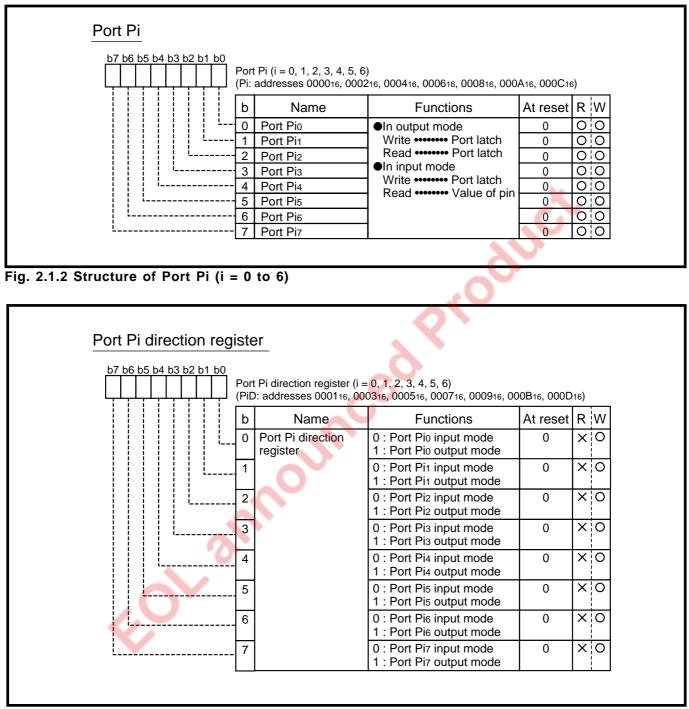

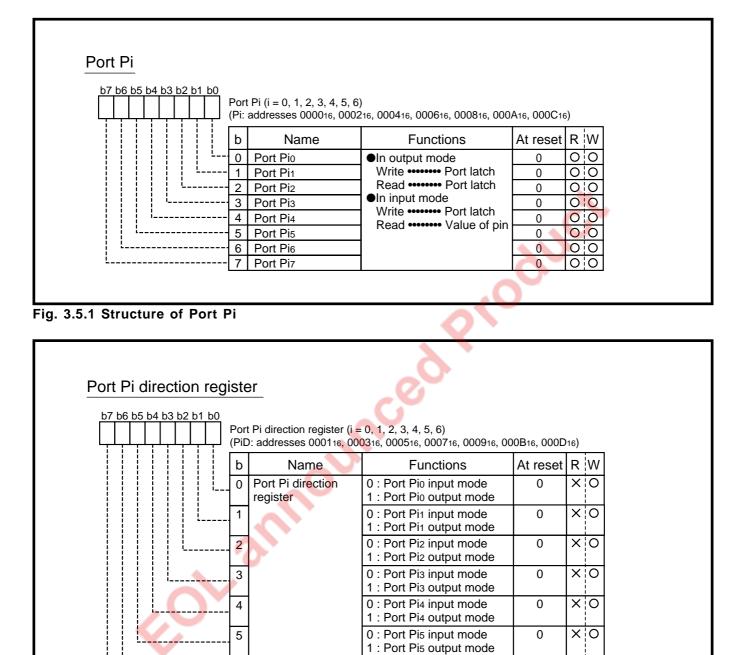

| Fig. 2.1.2 Structure of Port Pi (i = 0 to 6)                                                      |      |

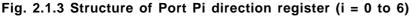

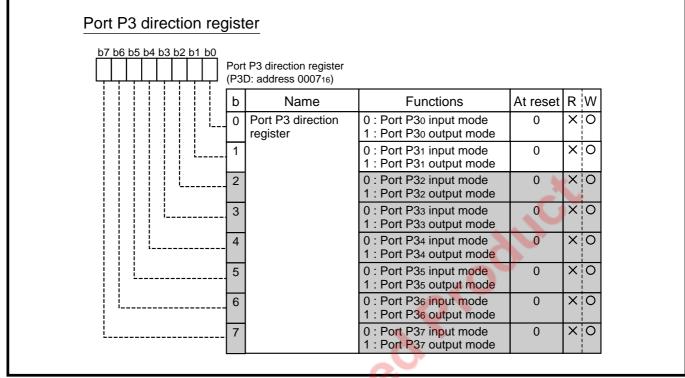

| Fig. 2.1.3 Structure of Port Pi direction register (i = 0 to 6)                                   |      |

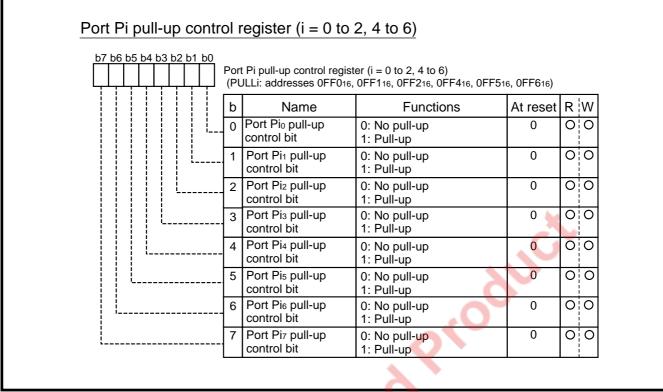

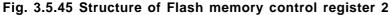

| Fig. 2.1.4 Structure of Port Pi pull-up control register (i = 0, 1, 2, 4, 5, 6)                   |      |

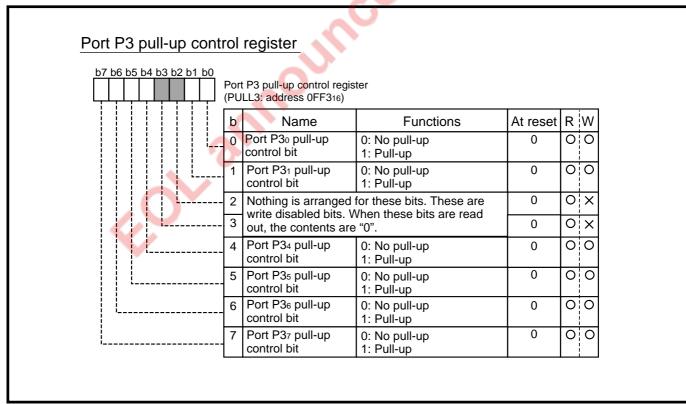

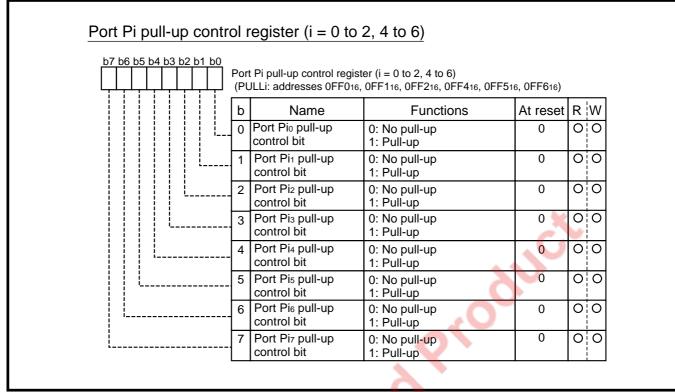

| Fig. 2.1.5 Structure of Port P3 pull-up control register                                          | 2-4  |

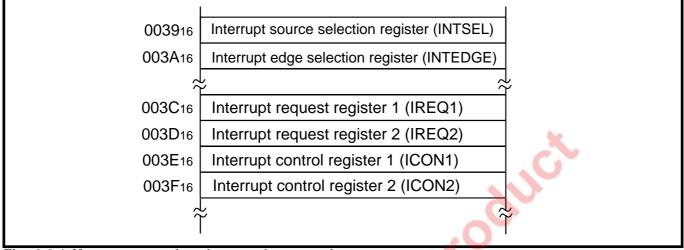

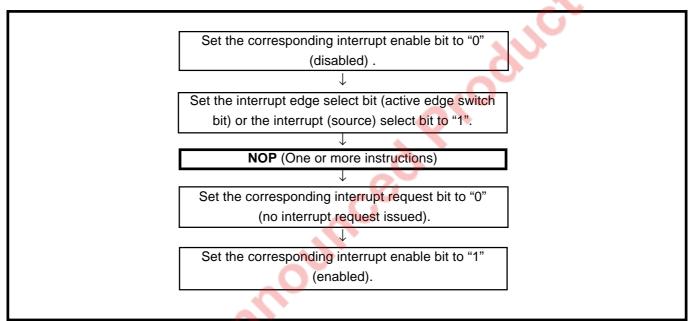

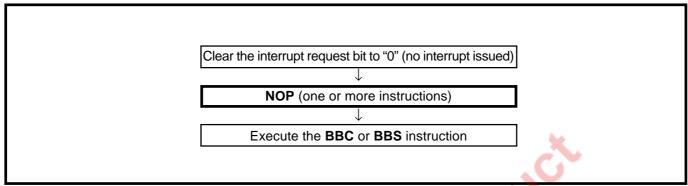

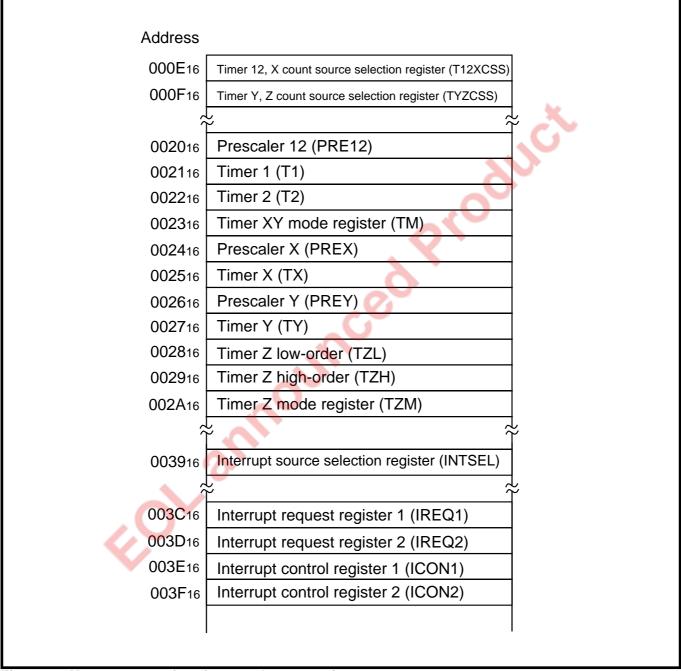

| Fig. 2.2.1 Memory map of registers relevant to interrupt                                          | 2-8  |

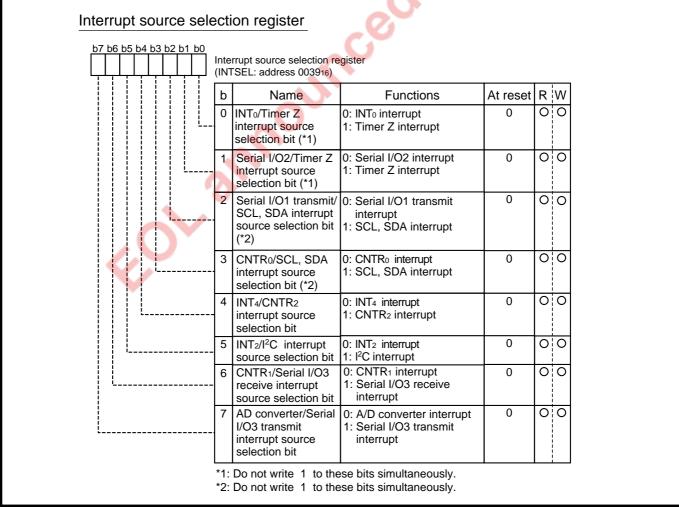

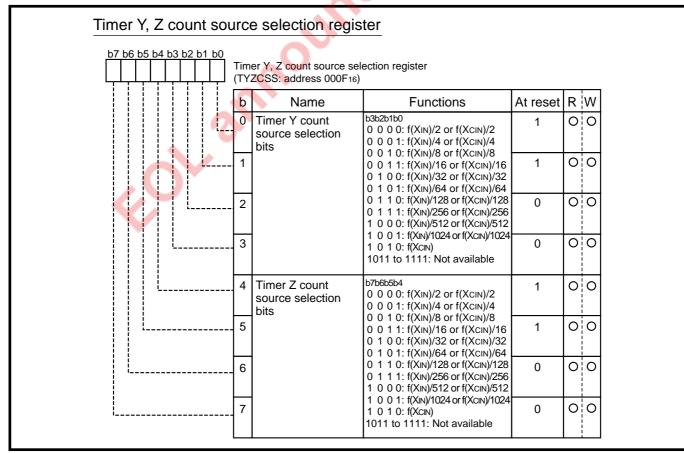

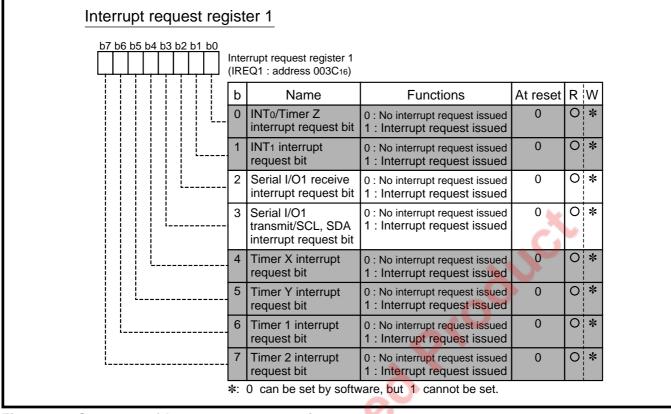

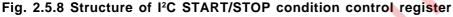

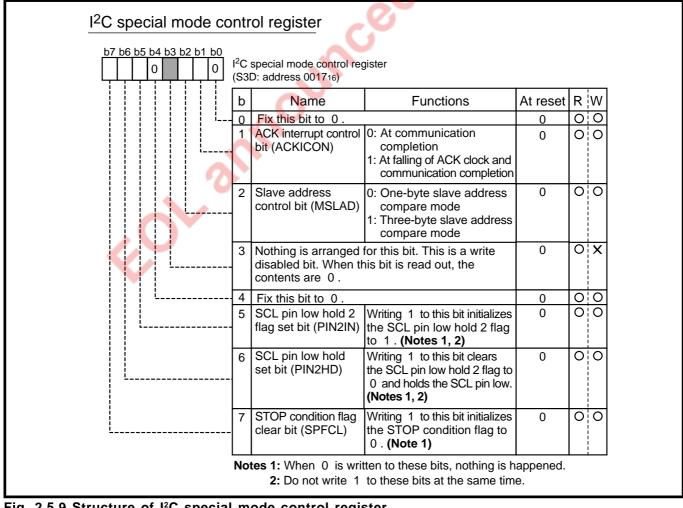

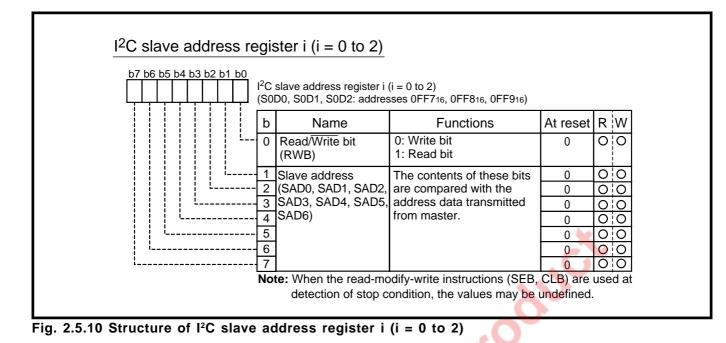

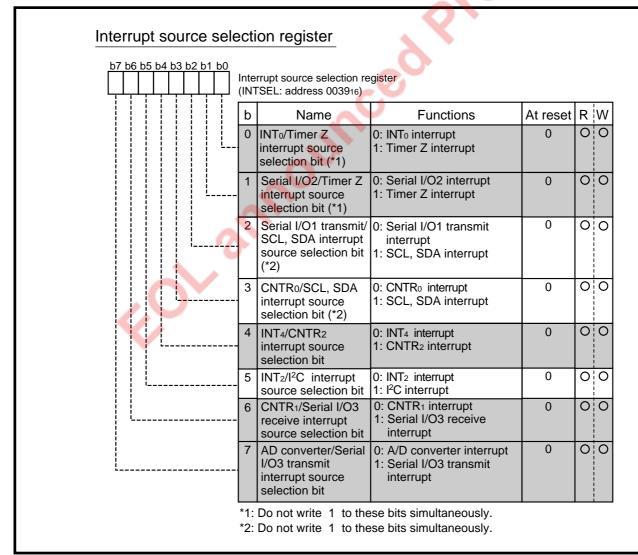

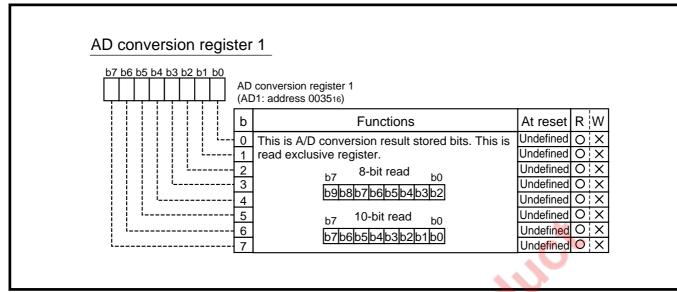

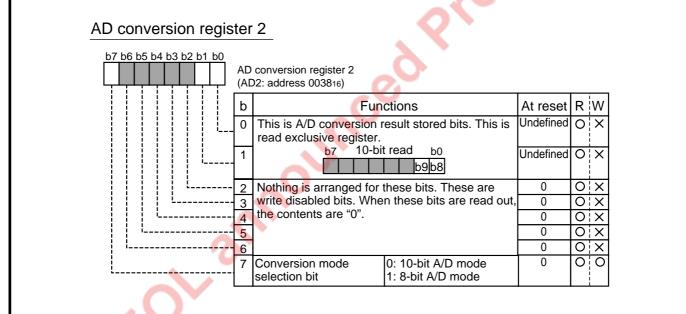

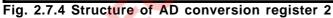

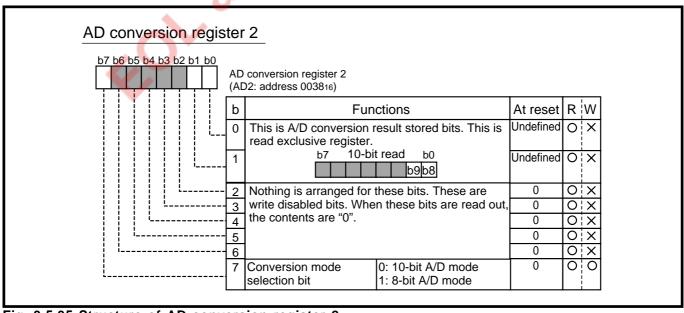

| Fig. 2.2.2 Structure of Interrupt source selection register                                       | 2-8  |

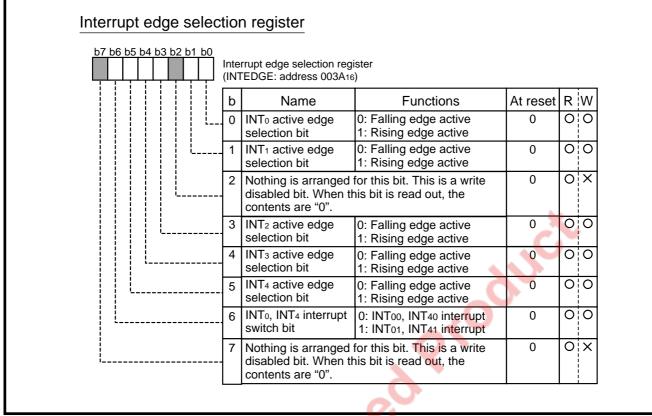

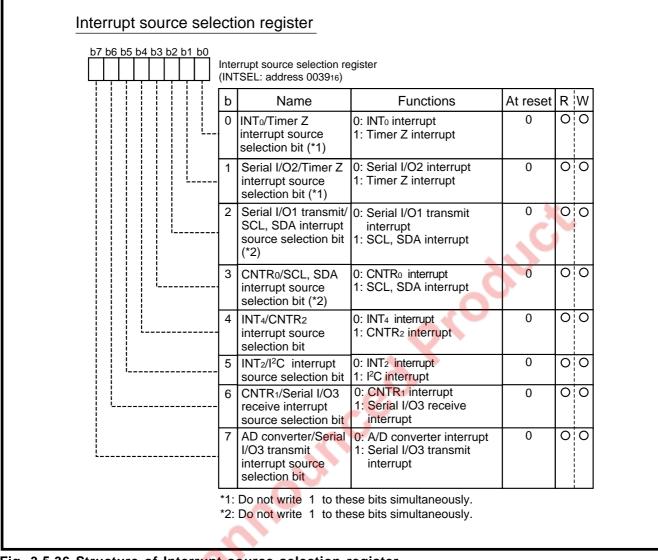

| Fig. 2.2.3 Structure of Interrupt edge selection register                                         | 2-9  |

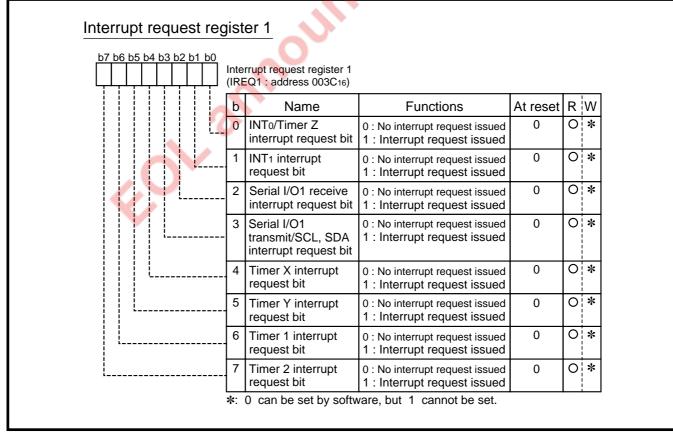

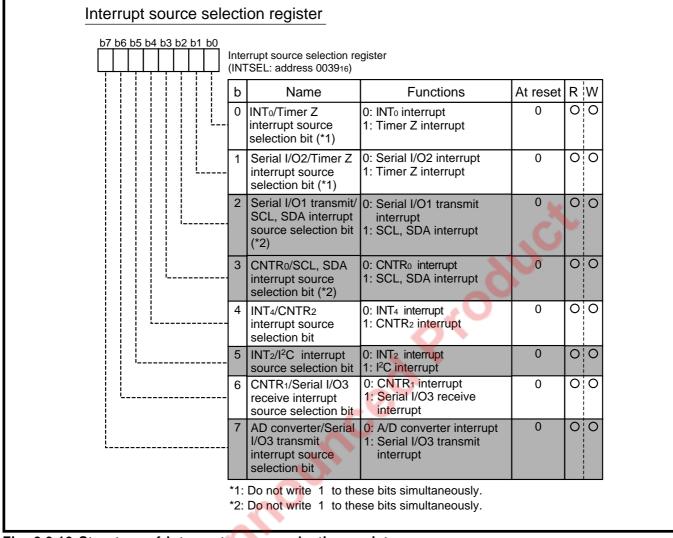

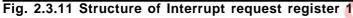

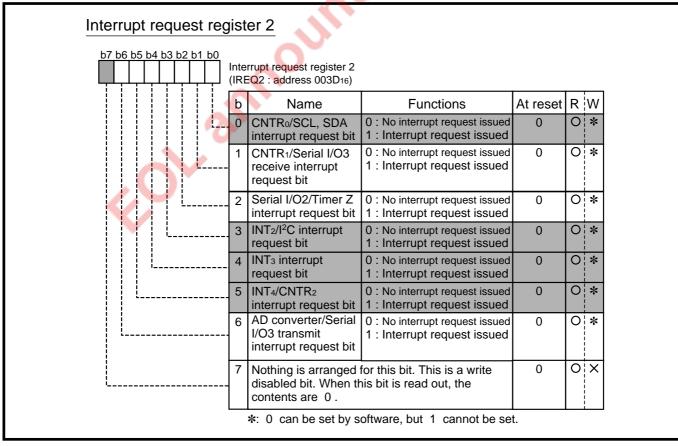

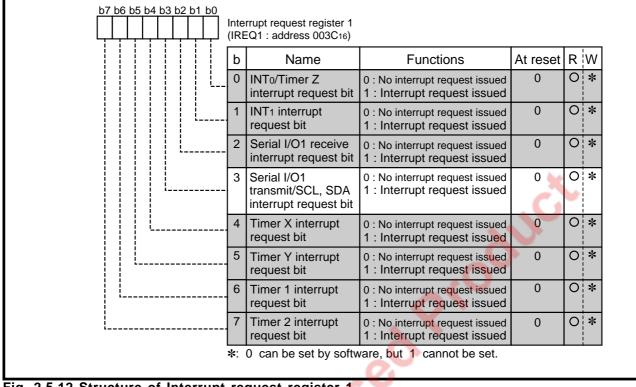

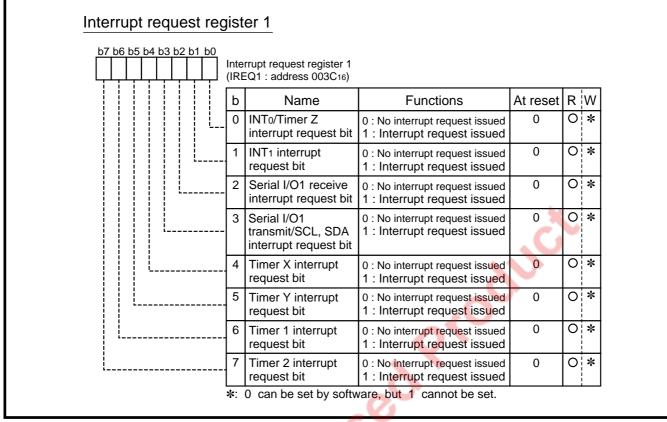

| Fig. 2.2.4 Structure of Interrupt request register 1                                              | 2-9  |

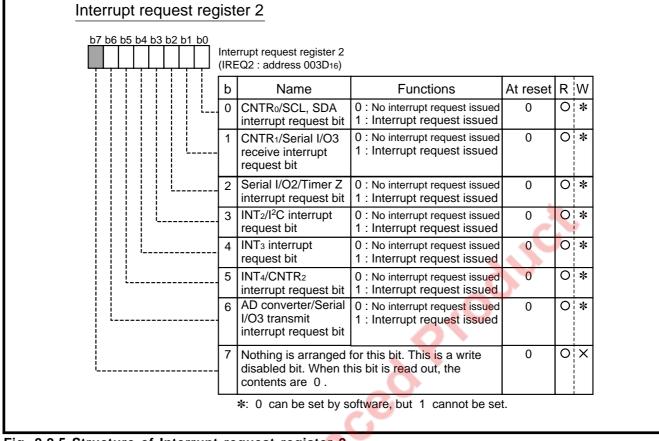

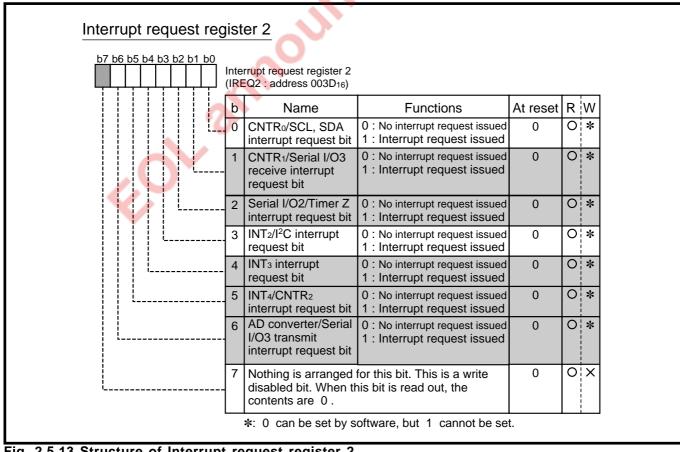

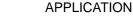

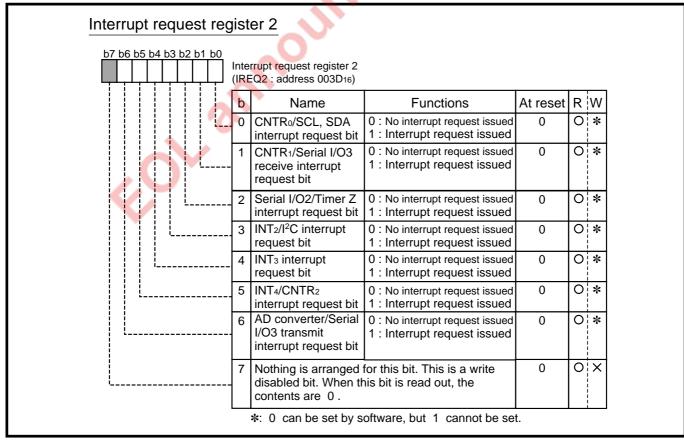

| Fig. 2.2.5 Structure of Interrupt request register 2                                              | 2-10 |

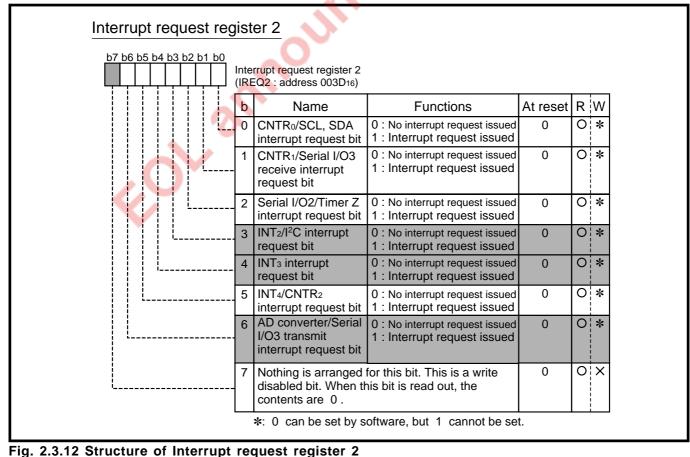

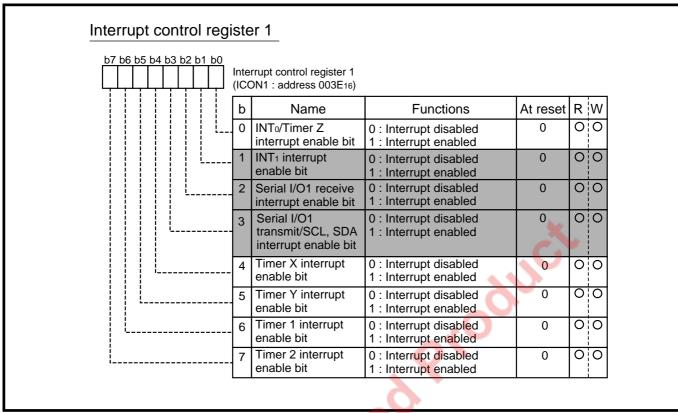

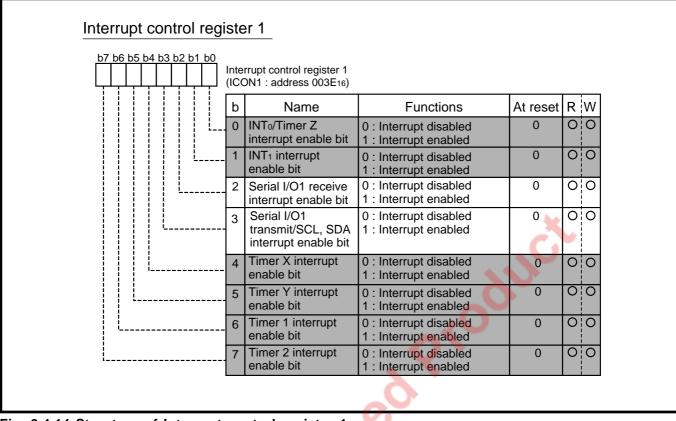

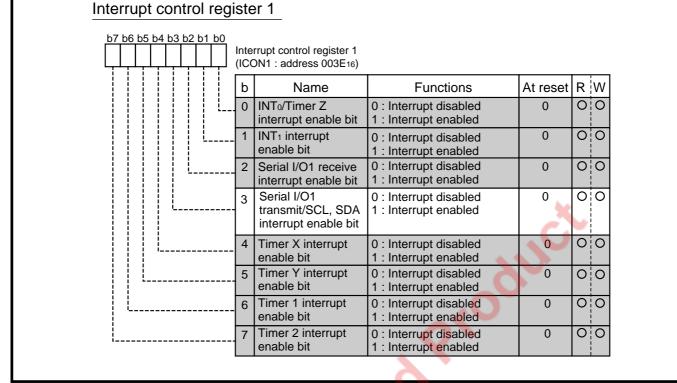

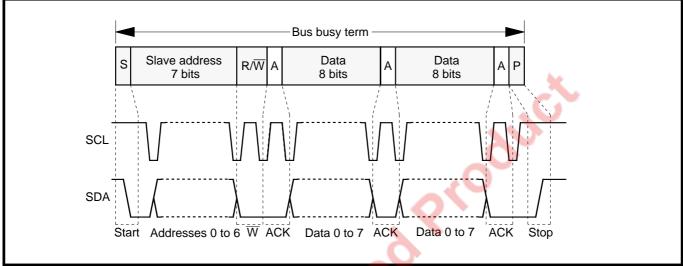

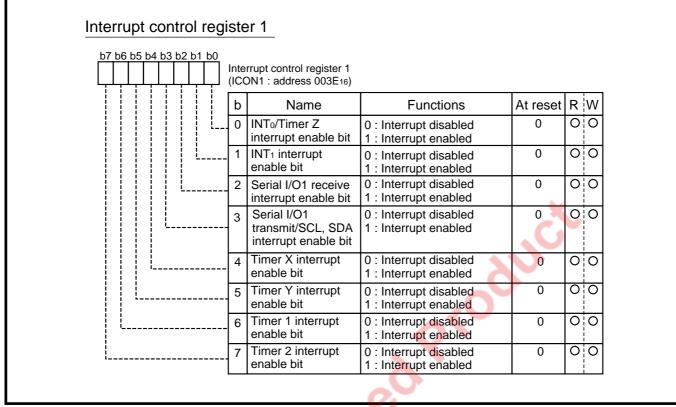

| Fig. 2.2.6 Structure of Interrupt control register 1                                              |      |

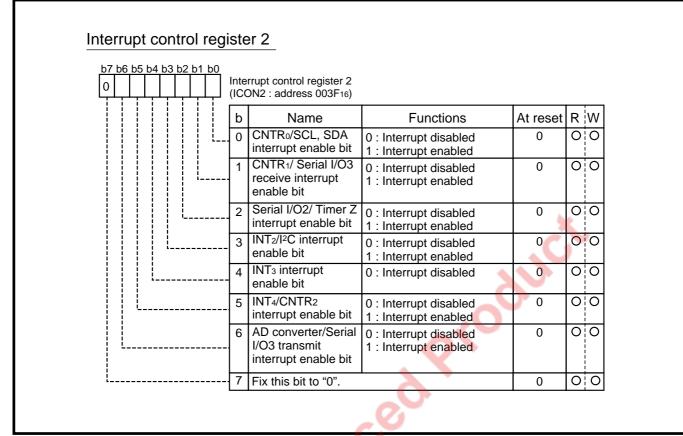

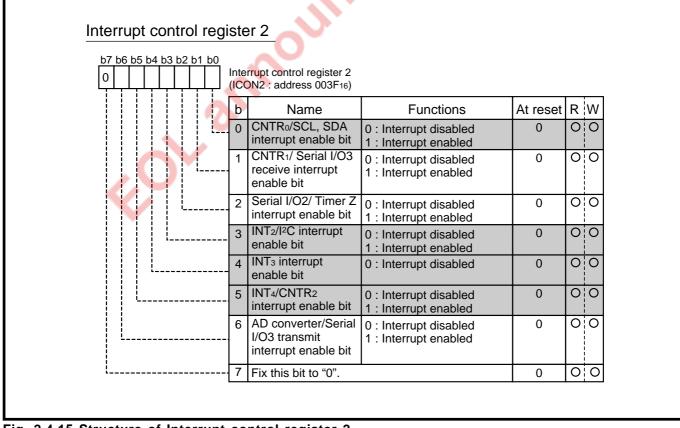

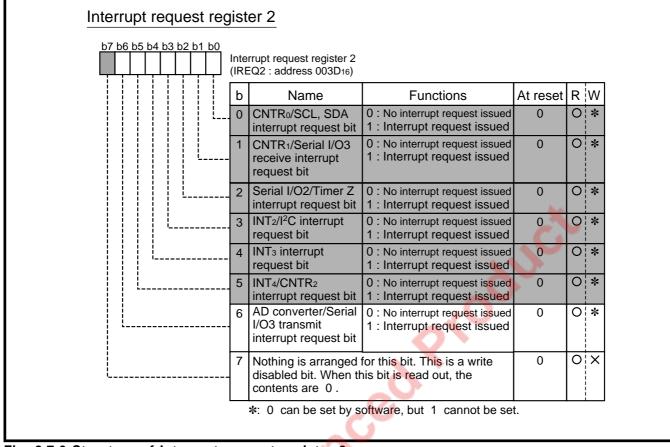

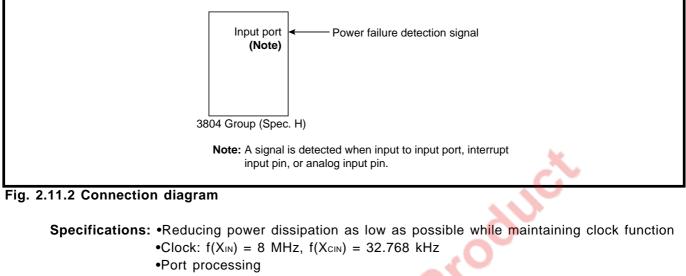

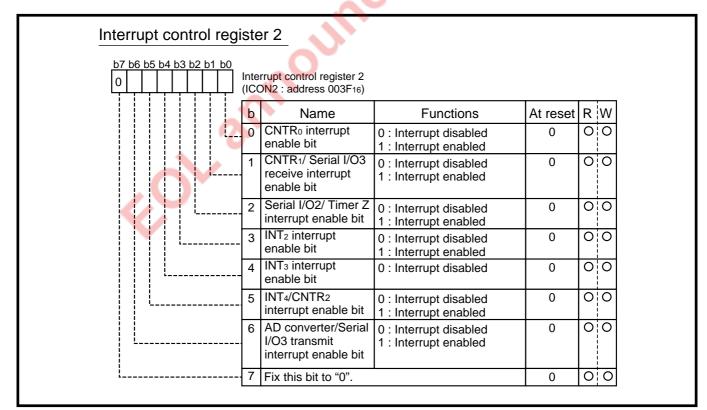

| Fig. 2.2.7 Structure of Interrupt control register 2                                              | 2-11 |