© Copyright — Cirrus Logic, Inc. 1994

All rights reserved. Permission is hereby granted for use, reproduction, republication, or abstraction of this material with attribution, by companies not involved in the sale or manufacture of integrated circuits.

### CL-GD543X Applications and Errata Book

Revision 1.2 April 1994

### **Publication Change Log**

| Rev. # | Rev. Date | Changes                                                                                                  |

|--------|-----------|----------------------------------------------------------------------------------------------------------|

| 1.0    | 2/9/94    | Preliminary Release: Includes AA02-AA05, B5, E1, SW Release Notes, and 5434 Errata for Revisions A and B |

| 1.1    | 3/25/94   | Added AA7, AA8, CAA1, CAA2, renamed AA6 as CAA3                                                          |

| 1.2    | 4/4/94    | Added TRM Errata, Added AJ Errata, Updated AA8, Updated AF Errata                                        |

### CL-GD5434 V1.00 Software Release Errata

### **Notice**

This document describes a potential application of Cirrus Logic integrated circuits. No warranty is given for the suitability of the circuitry or program code described herein for any purpose other than demonstrating functional operation. Cirrus Logic believes this information is accurate and reliable. However, it is subject to change without notice. No responsibility is assumed by Cirrus Logic for the use of this information, nor for infringements of patents or other rights of third parties. This document implies no license under patents or copyrights.

The following errata have been observed in the v1.00 release of CIR.DRV dated Feb 18, 1994.

### 1. Word for Windows v6.0 Help

If the help option is used with Word for Windows v6.0, and the Help window is moved on the screen, the screen is corrupted.

### 2. Video for Windows v1.1

If Video for Windows v.1.1 is used, Windows will hang the system.

### 3. CC Mail 2.0

Corrupted fonts appear in some menus.

The following enhancements will be implemented in the next release of drivers.

### 1. VL Configuration on PCI Systems

Some PCI system BIOSs have been observed to incorrectly report the CL-GD5434 as being on the PC bus when it is configured as a VL VGA in a PCI system. To avoid this in the future, the next release CIR.DRV will not request the PCI frame buffer address if the CL-GD5434 is configured as a VL device.

Mya 5, 1994

Dear Customer,

Thank you for your interest in the Cirrus Logic family of graphics products. Enclosed is the CL-GD5434 information you requested. The production revision A for VL Bus solutions and the production revision C for both VL Bus and PCI Bus systems are now available in production volumes.

The current revision of Driver software is version 1.01A dated May 4, 1994; the current BIOS revision is 1.00A dated March 1, 1994. Any updates will be available from the Cirrus Logic Bulletin Board (510-440-9080). Please contact your Cirrus Logic representative if you have any questions.

Thank you again for your interest in Cirrus Logic.

Very truly yours,

Cirrus Logic, Inc.

GDK5434-LTR1-1 May-94

### GDK5434-B-DM8-1

### **Kit License Agreement**

This document licenses you, under Cirrus Logic's patents, copyrights and other intellectual property, to make, have made, use, modify, sell, or otherwise dispose of boards that are based on the board design contained in the kit (including board specifications, board schematics, board net lists and bill of materials) provided such boards contain a Cirrus Logic CL-GD5434 integrated circuit purchased by you from Cirrus Logic, Inc.

The software in the kit is protected by copyright. It is licensed to you for the exclusive purpose of your evaluating the Cirrus Logic CL-GD5434 product. You may not copy, modify, reverse engineer, or transfer possession of the software contained in the kit, with the exception of the "CL-GD5434 VGA Demo" software (if available), for which Cirrus Logic grants you the license to reproduce and distribute. All the software contained in the kit can be made available for your use in production, but a separate signed license agreement is required.

The GDK5434-B-DM8-1 kit is delivered to you, and you are granted these licenses on the understanding that Cirrus Logic, Inc. makes no representation or warranty of any kind, express or implied, regarding the kit or any of its contents, including no warranty regarding their performance. THE KIT AND ITS CONTENTS ARE FURNISHED AS IS.

If for any reason you are unwilling to accept and use the GDK5434-B-DM8-1 kit on the terms set forth in this document, please return the kit to us and we will credit you account for any charges associated with it and reimburse you for return shipping cost.

Very truly yours,

Cirrus Logic, Inc.

GDK5434-B-DM8-LC1

### GDK5434-B-DM8-1 Bill of Materials

| Part No.        | Title                                                                                                                                                                                                | Description   |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| GDK5434-BOM1-01 | GDK5434-B-DM8-1 Bill of Materials                                                                                                                                                                    | Document.     |

| GDB5434-B-DM8-1 | PCI Bus Demo Board<br>with CL-GD5434 Chip Installed                                                                                                                                                  | PCI Bus Board |

| GDK5434-LTR1-1  | Customer Letter                                                                                                                                                                                      | Document,     |

| GDK5434-DM8-LC1 | GDK5434-B-DM8-1 Kit License Agreement                                                                                                                                                                | Document      |

|                 | CL-GD5434-HC-C Errata                                                                                                                                                                                | Document      |

|                 | Drivers, Release Release 1.01A, May 4, 1994 Dos Display Drivers & Utilities, Driver disk 1 of 4 Windows 3.1 & WIN/OS2, Driver disk 2 of 4 OS/2 2.1, Driver disk 3 of 4 Window NT, Driver disk 4 of 4 | 4 Diskettes   |

|                 | OEM Documentation, OEM disk 1 of 1<br>Release 1.01A, dated May 4, 1994                                                                                                                               | 1 Diskette    |

GDK5434-BOM1-01 May-94

|  |  | 1 |

|--|--|---|

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

### **Table of Contents**

### Revision 1.2

| Se         | ection      | Description                                                                                                         |

|------------|-------------|---------------------------------------------------------------------------------------------------------------------|

| 1.         |             | CL-GD543X Product Bulletin                                                                                          |

| 2.         | AA2         |                                                                                                                     |

| 3.         | Appendix B5 |                                                                                                                     |

| 4.         |             |                                                                                                                     |

| <b>5</b> . |             | Collateral Documention                                                                                              |

| 6.         | •••••       |                                                                                                                     |

| 7.         |             |                                                                                                                     |

| 8.         | ••••••      | CL-GD5434 Errata  CL-GD5434 Rev AE (Production A)  CL-GD5434 Rev AF (Production B)  CL-GD5434 Rev AJ (Production C) |

| 9.         | ••••••      | Technical Reference Manual: March 1994                                                                              |

•

# Section 1 Product Bulletin

CL-GD543X

### **FEATURES**

### ■ Pin- and software-compatible VGA graphics accelerator family

### **■** Enhanced GUI acceleration

- 64-bit Bit Block Transfer (BitBLT) engine (CL-GD5434)

- 32-bit BitBLT engine (CL-GD5430)

#### ■ 32-bit direct-connect CPU interface

- PCI™ bus (v2.0 compliant) with burst-cycle support

- VESA<sup>®</sup> VL-Bus<sup>™</sup> (v2.0 with 50 MHz)

- ISA bus (12.5 MHz) (CL-GD5434 only)

- Zero-wait-state write buffer for CPUs up to 33 MHz

### ■ 64-bit DRAM display memory interface

- 1-, 2-, and 4-Mbyte display memory support (CL-GD5434)

- 1/2-, 1-, and 2-Mbyte display memory support (CL-GD5430)

### ■ Resolutions to 1280 x 1024

- Up to 1024 x 768 x 64K colors, non-interlaced

- Up to 800 x 600 x 16M colors, non-interlaced

- Up to 1280 x 1024 x 64K colors, interlaced

#### ■ Integrated 24-bit DAC

### ■ 'Green PC' power-saving features:

- VESA® support for Display Power-Management Signalling (DPMS)

- Internal DAC with power-down mode

- Low-frequency DRAM refresh

- Static monitor sync signals

### ■ 100% hardware- and BIOS-compatible with IBM<sup>®</sup> VGA display standard

(cont.)

### VGA GUI Accelerator

CL-GD5434 — 64-bit GUI Accelerator CL-GD5430 — 32-bit GUI Accelerator

### **OVERVIEW**

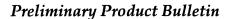

Based on a 64-bit GUI engine, the Alpine Graphics Accelerator Family incorporates a Bit Block Transfer (Bit-BLT) VGA controller with a 24-bit true-color DAC, dual-clock synthesizer, and direct-connect 32-bit PCI™ and VL-Bus™ interface. Designed to accelerate Microsoft® Windows and Windows NT 3.1, OS/2™ v2.1, and other graphic interfaces, the Alpine family offers performance surpassing current DRAM, and many VRAM-based GUI accelerators.

The software- and pin-compatible Alpine family allows OEMs to meet different price and performance targets with one graphic subsystem design. Built on a 1-Mbyte frame buffer and optimized for PCI and VL-Bus systems, the CL-GD5430 can be quickly upgraded to the higher-performance CL-GD5434. With a 2-Mbyte frame buffer, the CL-GD5434 offers performance beyond current 32-bit standard and interleaved architectures.

By combining a 32-bit external local bus interface with a 64-bit path to the DRAM frame buffer, the Alpine family eliminates the video-memory bottleneck in traditional DRAM architectures, and maximizes system-to-video bandwidth critical for outstanding graphics acceleration.

(cont.)

### **FEATURES** (cont.)

#### ■ Programmable dual-clock synthesizer

- Pixel clock programmable up to 110 MHz ('GD5434), and up to 86 MHz ('GD5430)

- Memory clock programmable up to 50 MHz ('GD5434), and up to 60 MHz ('GD5430)

#### **■** Multimedia-ready

- Video overlay with external video data and 'Color Keying'

- Genlock support with external HSYNC and/or VSYNC

- Alpha Channel ('GD5434)

- VESA® advanced-feature-connector (VAFC) support ('GD5430)

- 64 x 64 hardware cursor

- CL-GD5428/'GD5429 register- and software-compatible

- Glueless PCI™ bus interface with VGA BIOS ROM support for single 8-bit EPROM

- Low-power 5V CMOS, 208-pin PQFP/HQFP package

### **OVERVIEW** (cont.)

BitBLT support, linear addressing, hardware cursor, color expansion, and memory-mapped I/O are some of the many built-in CL-GD543X features that ensure outstanding GUI performance. The highly integrated 208-pin HQFP package makes the CL-GD543X ideal for both motherboard systems and add-in cards.

The only external support needed is cost-effective DRAM memory and a 14.31818-MHz frequency reference.

Operating at pixel clock rates programmable up to 110 MHz ('GD5434) and 86 MHz ('GD5430), the CL-GD543X chip supports standard and VESA high-resolution extended modes. The internal palette DAC may be configured for the industry-standard VGA modes of 16- or 256-color, or extended to high- and true-color modes of 32K, 64K, or 16.7 million colors. Display resolutions up to 1280 x 1024 are supported.

### **ADVANTAGES**

### Unique Features

#### Cost Effectiveness —

- Interface to as few as one DRAM, built-in true-color palette DAC and dual-frequency synthesizer

- Interface to x4, x16 DRAMs

### High Performance —

- Hardware BitBLT for Microsoft® Windows

- 32-bit PCI<sup>TM</sup>, VESA<sup>®</sup> VL-Bus<sup>TM</sup>, and local bus interface

- 64-bit-wide DRAM interface

- Independent video and DRAM timing

- Maximizes fast-page mode access to display-memory DRAMs

- Host access to DRAMs through advanced write buffers

- 32-bit memory-mapped BitBLT control registers

- 15-, 16-, or 24-bit true-color palette DAC

### Multimedia ---

Overlay, color keying, and Genlock

### Compatibility —

- Compatible with VGA and VESA® standards

- Drivers supplied at various resolutions for Windows™ 3.1, Windows NT™, AutoCAD®, OS/2™, and other key applications

- Connects directly to IBM® PS/2<sup>™</sup> and multifrequency analog monitors

### Benefits

- Minimizes chip count, system cost, and board space for cost-effective solution.

- Allows design flexibility for use of appropriate type and amount of memory.

- Accelerates GUIs such as Microsoft<sup>®</sup> Windows and similar applications.

- Increases system throughput.

- ☐ Eliminates display-memory bottleneck.

- Optimizes timing for increased performance.

- ☐ Improves CPU performance by accessing maximum bandwidth available from DRAM display memory.

- Provides faster host access for writes to display memory.

- ☐ Improves graphics-application performance.

- Provides high-color and true-color display for photorealistic images. 32K, 64K, or 16.8 million colors on screen at once for life-like images.

- Allows 16-bit-pixel interfacing through the VESA<sup>®</sup> connector for multimedia applications.

- Allows compatibility with installed base of systems and software.

- Provides a 'ready-to-go' solution that minimizes the need for additional driver development.

- ☐ Drives all PC-industry-standard, high-resolution monitors to ensure compatibility.

### CL-GD543X

Alpine Family VGA GUI Accelerators

### SOFTWARE SUPPORT

#### CL-GD543X VGA Software Drivers

Cirrus Logic provides an extensive — and expanding — range of software drivers to enhance the resolution and performance of many software packages. Note, however, that the CL-GD543X VGA graphics portion of a system *does not* require software drivers to run applications in standard-resolution mode.

Cirrus Logic software drivers for the CL-GD543X include:

| Software Drivers                                                          | Resolution Supported <sup>a</sup>                                                                                                                                                                                                    | No. of Colors                                                                    |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Microsoft® Windows v3.1                                                   | 640 x 480, 800 x 600, 1024 x 768, 1280 x 1024<br>640 x 480, 800 x 600, 1024 x 768, 1280 x 1024<br>640 x 480, 800 x 600, 1024 x 768                                                                                                   |                                                                                  |

| Microsoft® Windows NT v3.1                                                | 640 x 480, 800 x 600, 1024 x 768, 1280 x 1024                                                                                                                                                                                        | 16 and 256 colors                                                                |

| OS/2™ V2.1                                                                | 640 x 480, 800 x 600, 1024 x 768                                                                                                                                                                                                     | 256 colors                                                                       |

| AutoCAD® V11, V12<br>Autoshade® V2.0<br>w/ Renderman,<br>3D Studio V1, V2 | 640 x 480, 800 x 600, 1024 x 768, 1280 x 1024<br>640 x 480, 800 x 600, 1024 x 768, 1280 x 1024<br>640 x 480, 800 x 600, 1024 x 768, 1280 x 1024<br>640 x 480, 800 x 600, 1024 x 768, 1280 x 1024<br>640 x 480, 800 x 600, 1024 x 768 | 16 colors<br>256 colors<br>32,768 colors<br>65,536 colors<br>16.8 million colors |

| Lotus <sup>®</sup> 1-2-3 <sup>™</sup> v2.X,                               | 132 x 25, 132 x 43 (text)<br>800 x 600                                                                                                                                                                                               | 16 colors<br>16 colors                                                           |

| Lotus <sup>®</sup> 1-2-3 <sup>™</sup> v3.3                                | 800 x 600, 1024 x 768                                                                                                                                                                                                                | 16 colors                                                                        |

| Microsoft® Word v5.X                                                      | 132 x 25, 132 x 43 (text)<br>800 x 600, 1024 x 768                                                                                                                                                                                   | 16 colors                                                                        |

| WordPerfect® v5.1                                                         | 132 x 25, 132 x 43 (text)<br>800 x 600, 1024 x 768                                                                                                                                                                                   | 16 colors                                                                        |

| WordPerfect® v6.0b                                                        | 640 x 480, 800 x 600, 1024 x 768                                                                                                                                                                                                     | 16 and 256 colors                                                                |

| WordStar® v5.5-7.0                                                        | 800 x 600, 1024 x 768                                                                                                                                                                                                                | 16 colors                                                                        |

| SCO UNIX <sup>™C</sup>                                                    | 640 x 480, 800 x 600, 1024 x 768                                                                                                                                                                                                     | 16 and 256 colors                                                                |

All resolutions may not run on all monitor types; 640 x 480 drivers will run on PS/2-type monitors. Extended resolutions are dependent upon monitor type and VGA system implementation.

### **BIOS SUPPORT**

- Fully IBM® VGA-compatible BIOS

- Relocatable, 32K bytes with VESA® VL-Bus™ and PCI™ Local Bus support

- VESA® BIOS Extensions (VBE) support in ROM

- Support for Display Power Management Signaling (DPMS) in ROM

- VESA® monitor timing-compliant

### UTILITIES

- **■** Manufacturing test

- **■** Windows DOS/NT utilities

- Video mode configuration utility CLMODE

- Set resolution in Windows WINMODE

- Configured OEM system integration OEMSI

<sup>&</sup>lt;sup>b</sup> Supported by VESA<sup>®</sup> driver.

<sup>&</sup>lt;sup>c</sup> Shipped by Santa Cruz Operations.

### **Direct Sales Offices**

Domestic

**NORTHERN CALIFORNIA**

Fremont

TEL: 510/623-8300 FAX: 510/252-6020

**SOUTHERN CALIFORNIA**

Tustin

TEL: 714/258-8303 FAX: 714/258-8307

**Thousand Oaks** TEL: 805/371-5381 FAX: 805/371-5382

**ROCKY MOUNTAIN** AREA

Denver, CO

TEL: 303/786-9696 FAX: 303/786-9695 **SOUTH CENTRAL AREA**

Austin, TX

TEL: 512/794-8490 FAX: 512/794-8069

Dallas, TX

TEL: 214/252-6698 FAX: 214/252-5681

**CENTRAL AREA**

Chicago, IL

TEL: 708/981-6950 FAX: 708/981-6846

**NORTHEASTERN**

AREA

Andover, MA TEL: 508/474-9300 FAX: 508/474-9149

Philadelphia, PA TEL: 215/625-0781 FAX: 215/625-0731 SOUTHEASTERN **AREA**

Boca Raton, FL TEL: 407/362-5225 FAX: 407/362-5235

International

**GERMANY**

Herrsching

TEL: 49/8152-40084 FAX: 49/8152-40077

**HONG KONG**

Tsimshatusi TEL: 852/376-0801 FAX: 852/375-1202

**JAPAN**

Tokyo

TEL: 81/3-3340-9111 FAX: 81/3-3340-9120 **KOREA**

Seoul

TEL: 82/2-565-8561 FAX: 82/2-565-8565

**SINGAPORE**

TEL: 65/3532122 FAX: 65/3532166

**TAIWAN**

Taipei

TEL: 886/2-718-4533 FAX: 886/2-718-4526

**UNITED KINGDOM**

Hertfordshire, England TEL: 44/0727-872424 FAX: 44/0727-875919

### The Company

Headquartered in Fremont, California, Cirrus Logic, Inc., develops innovative architectures for analog and digital system functions. The Company implements those architectures in proprietary integrated circuits and related software for applications that include user interface and multimedia (graphics, audio, and video), mass storage, communications, and data acquisition.

Key markets for Cirrus Logic's products include desktop and portable computing, workstations, telecommunications, and consumer electronics.

The Cirrus Logic formula combines innovative architectures in silicon with system design expertise. We deliver complete solutions — chips, software, evaluation boards, and manufacturing kits — on-time, to help you win in the marketplace.

Cirrus Logic's manufacturing strategy, unique in the semiconductor industry, employs a full manufacturing infrastructure to ensure maximum product quality, availability, and value for our customers.

Talk to our systems and applications specialists; see how you can benefit from a new kind of semiconductor company.

© Copyright, Cirrus Logic, Inc., 1994

Preliminary product information describes products that are in production, but for which full characterization data is not yet available. Cirrus Logic, Inc., believes the information contained in this document is accurate and reliable. However, it is marked Preliminary and is subject to change without notice. No responsibility is assumed by Cirrus Logic, Inc., for its use, nor for infringements of patents or other rights of third parties. This document implies no license under patents or copyrights. Cirrus Logic, AutoMap, Fair Share, FeatureChips, Good Data, SimulSCAN, S/LA, SofTarget, and UXART are trademarks of Cirrus Logic, Inc. Other trademarks in this document belong to their respective companies. Cirrus Logic, Inc., products are covered under one or more of the following U.S. patents: 4,293,783; Re. 31,287; 4,763,332; 4,777,635; 4,839,896; 4,931,946; 4,975,828; 4,979,173; 5,032,981; 5,122,783; 5,131,015; 5,140,595; 5,157,618; 5,179,292; 5,185,602; 5,220,295; 5,280,488; 5,287,241.

CIRRUS LOGIC, Inc.,

3100 West Warren Ave. Fremont, CA 94538

TEL: 510/623-8300

FAX: 510/226-2180

# Section 2 Application Alerts

CL-GD543X

# CL-GD543X Application Alert 2 Memory Configurations for CL-GD5430/34

### User Interface Group Cirrus Logic, Inc.

### **Scope and Applicability**

This Application Alert presents information not found in previous documentation for the CL-GD543x. It is intended to be used in conjunction with applicable CL-GD543x literature

### **Related Documents**

Alpine VGA Family - CL-GD543x Technical Reference Manual - November 1993

© Copyright — Cirrus Logic, Inc. 1993

All rights reserved. Permission is hereby granted for use, reproduction, republication, or abstraction of this material with attribution, by companies not involved in the sale or manufacture of integrated circuits.

### **Notice**

This document describes a potential application of Cirrus Logic integrated circuits. No warranty is given for the suitability of the circuitry or program code described herein for any purpose other than demonstrating functional operation. Cirrus Logic believes this information is accurate and reliable. However, it is subject to change without notice. No responsibility is assumed by Cirrus Logic for the use of this information, nor for infringements of patents or other rights of third parties. This document implies no license under patents or copyrights.

### Introduction

The purpose of this Application Alert is to summarize the memory configurations for the CL-GD5430/34. It is possible to design a common board that can be populated with 512K (CL-GD5430 only) or up to 4M (CL-GD5434 only).

### **Summary Table**

The following table summarizes the various memory configurations defined for the CL-GD5430/34. The column headed "Connection Table" refers to tables in the November 1993 issue of the Alpine TRM.

| DRAM Configuration              | Number of DRAMs | Total Memory | Connection<br>Table | '30 | '34 | Ras*<br>Note |

|---------------------------------|-----------------|--------------|---------------------|-----|-----|--------------|

| 256K x 4                        | 4               | 512 Kbyte    | B7-3                | ~   |     |              |

| 256K x 4                        | 8               | 1 Mbyte      | B7-4                | ~   | ~   |              |

| 256k x 4                        | 16              | 2 Mbyte      | B7-5                | ~   | ~   | . 🗸          |

| 256k x 16, Dual-CAS*, Symmetric | 1               | 512 Kbyte    | B7-6                | ~   |     |              |

| 256K x 16, Dual-CAS*, Symmetric | 2               | 1 Mbyte      | B7-7                | ~   | ~   |              |

| 256K x 16, Dual-CAS*, Symmetric | 4               | 2 Mbyte      | B7-8                | ~   | ~   | ~            |

| 256K x 16, Dual-CAS*, Symmetric | 8               | 4 Mbyte      | B7-9                |     | ~   |              |

| 256K x 16, Dual-WE*, Asymmetric | 1               | 512 Kbyte    | B7-10               | ~   |     |              |

| 256K x 16, Dual-WE*, Asymmetric | 2               | 1 MByte      | B7-11               | ~   | ~   |              |

| 256K x 16, Dual-WE*, Asymmetric | 4               | 2 MByte      | B7-12               |     | ~   |              |

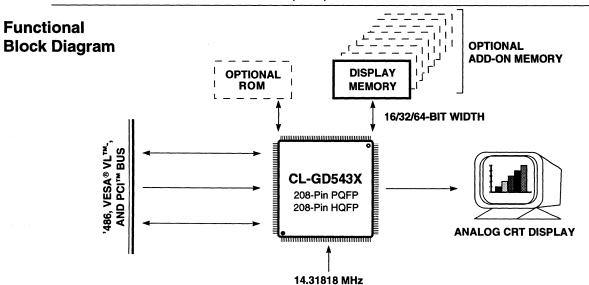

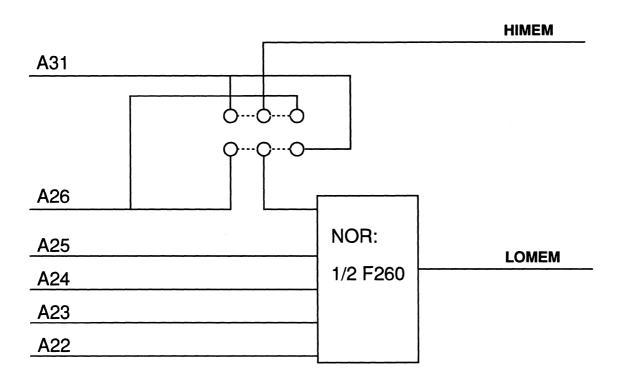

### **RAS\* Connection Note**

To ensure the layout can be used with up to 2 MBytes with either the CL-GD5430 or CL-GD5434, the RAS\* connections to the 2nd MByte (devices 3 and 4 in Table B7-8) (or devices 9-16 in Table B7-5) should be either RAS1\* (CL-GD5434 case) or RAS0\*/OE\* (CL-GD5430 case). An obvious way to mechanize this is with zero ohm resistors (or damping resistors if they prove necessary) that are optionally populated. See the diagram below.

### **Notes**

R1 is installed for all configurations.

R2 is installed for CL-GD5434 only.

R3 is installed for CL-GD5430 only.

### **WE\* Steering Note**

If WE\* steering is used, the CL-GD5430 will support up to only 1 MByte of Display Memory since RAS0/OE\* is not available to control the 2nd MByte.

## CL-GD543X Application Alert 3 Calculated Maximum MCLK for CL-GD5430/34

### User Interface Group Cirrus Logic, Inc.

### **Scope and Applicability**

This Application Alert presents information not found in previous documentation for the CL-GD543x. It is intended to be used in conjunction with applicable CL-GD543x literature

#### **Related Documents**

Alpine VGA Family - CL-GD543x Technical Reference Manual - November1993

© Copyright — Cirrus Logic, Inc. 1994

All rights reserved. Permission is hereby granted for use, reproduction, republication, or abstraction of this material with attribution, by companies not involved in the sale or manufacture of integrated circuits.

### **Notice**

This document describes a potential application of Cirrus Logic integrated circuits. No warranty is given for the suitability of the circuitry or program code described herein for any purpose other than demonstrating functional operation. Cirrus Logic believes this information is accurate and reliable. However, it is subject to change without notice. No responsibility is assumed by Cirrus Logic for the use of this information, nor for infringements of patents or other rights of third parties. This document implies no license under patents or copyrights.

### Introduction

The purpose of this Application Alert is to document the results of evaluation of the equations described in the CL-GD543X Technical Reference Manual, Appendix B7 (*Memory Configurations and Timing*). The numbers have been compared to 256K x 16 from several vendors. The results of these comparisons are listed in the table below. The devices are ordered alphabetically by vendor. The calculated numbers were rounded to the nearest ns for the purposes of this this comparision.

▼ Note: In some cases, the results of the comparison indicates that the memory device supports a Memory

Clock (MCLK) greater than 50 Mhz. This is not to be taken as a guarantee that any particular mem-

ber of the Alpine family is rated to operate with an MCLK greater than 50 MHz.

▼ Note: The appearance of any particular device from any vendor is not to be taken as a guarantee that it

has been tested with any particular Cirrus Logic device, or as an endorsement from Cirrus Logic.

▼ Note: Fast Page Mode cycle time (tPC) and Random Cycle time (tRC) were not considered as limiting

parameters since they are calculated, not measured, by the DRAM vendors. The calculations

assume very slow signal rise and fall times.

| Vendor     | Vendor<br>Part Number | Configuration | Speed<br>Grade | Standard RAS Timing |                       | Extended RAS Timin (not CL-GD5434-A) |                       |

|------------|-----------------------|---------------|----------------|---------------------|-----------------------|--------------------------------------|-----------------------|

|            |                       |               |                | Max MCLK<br>MHz     | Limiting<br>Parameter | Max MCLK<br>MHz                      | Limiting<br>Parameter |

| Hitachi    | HMS14260              | Dual CAS      | -70            | 48.3                | tRP                   | 55.5                                 | tRAS                  |

| Hitachi    | HMS14260              | Dual CAS      | -80            | 39.4                | tRP                   | 48.3                                 | tRAS                  |

| Hitachi    | HMS41260              | Dual CAS      | -100           | NR                  | tRP                   | 39.4                                 | tRAS                  |

| Hitachi    | HMS51470              | Dual WE       | -70            | 48.3                | tRP                   | 55.5                                 | tRAS                  |

| Hitachi    | HMS51470              | Dual WE       | -80            | 39.4                | tRP                   | 48.3                                 | tRAS                  |

| Hitachi    | HMS51470              | Dual WE       | -100           | NR                  | tRP                   | 39.4                                 | tRAS                  |

| Micron     | MT4C16256             | Dual WE       | -70            | 48.3                | tRP                   | 55.5                                 | tRAS                  |

| Micron     | MT4C16256             | Dual WE       | -80            | 39.4                | tRP                   | 48.3                                 | tRAS                  |

| Micron     | MT4C16256             | Dual WE       | -100           | NR                  | tRP                   | 39.4                                 | tRAS                  |

| Micron     | MT4C16257             | Dual CAS      | -70            | 48.3                | tRP                   | 55.5                                 | tRAS                  |

| Micron     | MT4C16257             | Dual CAS      | -80            | 39.4                | tRP                   | 48.3                                 | tRAS                  |

| Micron     | MT4C16257             | Dual CAS      | -100           | NR                  | tRP                   | 39.4                                 | tRAS                  |

| Mitsubishi | M5M44170A             | Dual WE       | -60            | 48.3                | tRP                   | 59.1                                 | tRP                   |

| Vendor     | Vendor<br>Part Number | Configuration | Speed<br>Grade | Standard RAS Timing |     |      | RAS Timing<br>iD5434-A) |

|------------|-----------------------|---------------|----------------|---------------------|-----|------|-------------------------|

| Mitsubishi | M5M44170A             | Dual WE       | -70            | 39.4                | tRP | 50.1 | tRP                     |

| Mitsubishi | M5M44170A             | Dual WE       | -80            | NR                  | tRP | 43.0 | tRP                     |

| Mitsubishi | M5M44170A             | Dual WE       | -100           | NR                  | tRP | 37.6 | tRP                     |

| Mitsubishi | M5M44260A             | Dual CAS      | -80            | NR                  | tRP | 43.0 | tRP                     |

| Mitsubishi | M5M44260A             | Dual CAS      | -100           | NR                  | tRP | 37.6 | tRP                     |

| NEC        | uPD42170              | Dual WE       | -60            | 48.3                | tRP | 59.1 | tCAC                    |

| NEC        | uPD42170              | Dual WE       | -70            | 48.3                | tRP | 55.5 | tRAS                    |

| NEC        | uPD42170              | Dual WE       | -80            | 39.4                | tRP | 48.3 | tRAS                    |

| NEC        | uPD424260A            | Dual CAS      | -60            | 48.3                | tRP | 59.1 | tCAC                    |

| NEC        | uPD424260A            | Dual CAS      | -70            | 39.4                | tRP | 50.1 | tRP                     |

| NEC        | uPD424260 <b>A</b>    | Dual CAS      | -80            | 39.4                | tRP | 48.3 | tRAS                    |

| Toshiba    | TC51470B              | Dual WE       | -70            | 48.3                | tRP | 55.5 | tRAS                    |

| Toshiba    | TC51470B              | Dual WE       | -80            | 39.4                | tRP | 48.3 | tRAS                    |

| Toshiba    | TC51470B              | Dual WE       | -100           | NR                  | tRP | 39.4 | tRAS                    |

Note: "NR" indicates this configuration is not recommended.

# CL-GD543X Application Alert 4 Linear Addressing Space for VESA-VL

### User Interface Group Cirrus Logic, Inc.

### **Scope and Applicability**

This Application Alert presents information not found in previous documentation for the CL-GD543x. It is intended to be used in conjunction with applicable CL-GD543x literature

### **Related Documents**

Alpine VGA Family - CL-GD543x Technical Reference Manual - June 1993

© Copyright — Cirrus Logic, Inc. 1994

All rights reserved. Permission is hereby granted for use, reproduction, republication, or abstraction of this material with attribution, by companies not involved in the sale or manufacture of integrated circuits.

### **Notice**

This document describes a potential application of Cirrus Logic integrated circuits. No warranty is given for the suitability of the circuitry or program code described herein for any purpose other than demonstrating functional operation. Cirrus Logic believes this information is accurate and reliable. However, it is subject to change without notice. No responsibility is assumed by Cirrus Logic for the use of this information, nor for infringements of patents or other rights of third parties. This document implies no license under patents or copyrights.

### Introduction

The purpose of this Application Alert is to explain how the linear address space is chosen for the Cirrus Logic VESA-VL reference designs. An implementor can choose to copy this method directly, or can use this as an example on which to model a design.

### **Background**

There was never any real problems with memory space address conflicts when using the standard VGA address range at A000:0 - AFFF:F. This stemmed from this range having been assigned on the original IBM PC. Of course, this 64kbyte window is much too small to directly address a large (1-4 Mbyte) display memory and requires a paging mechanism with its attendant overhead.

Linear addressing of display memory avoids the problems associated with this small window by assigning a contiguous address space large enough for all of display memory. However, we have not been so fortunate as to have a well-defined area reserved for this address space. This lack of definition has been exacerbated by designers not decoding the entire address bus, thereby saving pins.

Originally, we placed our linear address space at 128MB. HIMEM was tied to A27 and LOMEM was the decode of A[26:22] all zero. However, the ZEOS platform decoded only to address bit A26, so it can not distinguish between 128MB and 0MB. When our drivers wrote into display memory at 128MB, a write would also take place to location 0. It can be seen that this quickly led to problems.

Next we tried 64MB. HIMEM was tied to A26 and LOMEM was the decode of A[25:22] all zero. However the EFAR platform decodes only up to address bit A25, so they can not distinguish between 64MB and 0MB.

### The Current Solution

We are now changing our reference design so that the linear address space can begin at either 64MB or 2048MB. We expect that 64MB will be satisfactory for all platforms other than EFAR and that 2048MB will be satisfactory for them. The choice is made by moving two jumper blocks (or populating two zero ohm resistors). The following table indicates how HIMEM and LOMEM are generated for the two cases. The right-most column indicates how the jumpers in the schematic fragment on the next page are populated.

Please note that only the two choices of 64 MB or 2048 MB are possible with this design. If additional flexibility is required, or if the address space is to be placed at any other location, the design will change.

| Address<br>Space | HIMEM       | LOMEM                | Jumpers |

|------------------|-------------|----------------------|---------|

| 64MB             | A26         | NOR of A31, A[25:22] | right   |

| 2048MB           | <b>A</b> 31 | NOR of A[26:22]      | left    |

### Why 2048MB was Selected

There will soon be motherboards on the market that support both VESA and PCI. We understand that these platforms will allocate memory for PCI devices above 2048MB. This means that we must decode A31 when we are configurated at 64 MB to avoid erroneously responding to accesses intended for PCI devices. Since A31 is decoded in most core logic chip sets, placing the frame buffer at 2048 MB will ensure that the core logic will ignore cycles directed to us.

### **Software Note**

The Windows drivers must know where the linear address space has been placed. This is done with an entry in the SYSTEM.INI file. The entry is Linearaddr = 2048 for the 2048 MB case or Linearaddr = 64 for the 64 MB case. If the address space is moved to some other location, this entry will have to be modified appropriately.

### **Schematic Fragment**

The following schematic fragment shows how this might be implemented. The jumpers are connected as indicated with the dotted lines. The only two cases described in this Ap Alert are both jumpers to the left or both jumpers to the right.

## **CL-GD543X Application Alert 5 BitBLT Check List for CL-GD5434**

### User Interface Group Cirrus Logic, Inc.

### **Scope and Applicability**

This Application Alert presents information not found in previous documentation for the CL-GD543x. It is intended to be used in conjunction with applicable CL-GD543x literature

### **Related Documents**

Alpine VGA Family - CL-GD543x Technical Reference Manual - November 1993

© Copyright — Cirrus Logic, Inc. 1994

All rights reserved. Permission is hereby granted for use, reproduction, republication, or abstraction of this material with attribution, by companies not involved in the sale or manufacture of integrated circuits.

Version 1.0 February 1994

### **Notice**

This document describes a potential application of Cirrus Logic integrated circuits. No warranty is given for the suitability of the circuitry or program code described herein for any purpose other than demonstrating functional operation. Cirrus Logic believes this information is accurate and reliable. However, it is subject to change without notice. No responsibility is assumed by Cirrus Logic for the use of this information, nor for infringements of patents or other rights of third parties. This document implies no license under patents or copyrights.

#### Introduction

This application alert is intended for BitBLT programmers who have been working on the CL-GD5426/28 and will be moving on the the CL-GD5434. There are a few differences, mostly resulting from the enhancements available on the '34, that should be taken into consideration. These differences are listed here, in no particular order.

### **Extension Register GRB**

GRB[4] and GRB[1] must be programmed to '0' when executing Screen to Screen BLTs. This is a new restriction. Applications that alternate between Extended Write Modes 4 and 5 and Screen to Screen BLTs will need to pay particular attention to this item.

### Mixed I/O

The CL-GD5434 has the capability of accessing the BLT control registers as memory. This speeds the register loading since 4 bytes of data can be transferred per access rather than one. This capability is called Memory Mapped I/O and is described in some detail in the Technical Reference Manual. In general, Memory Mapped I/O should not be mixed with "normal" I/O. An application should choose one or the other and stick with it.

### **Pitch Register LSBs**

The two LSBs of both pitch registers should be programmed to '0's. This restriction was not previously present.

### **Delay Prior to Reading Status**

If a BitBLT is started while the write buffer is completely filled, the Status register will not report "busy" immediately. Placing the operations that program the BLT registers after any memory writes will insert enough time to guarantee valid status immediately after the BLT is started.

### Transparency uses ALL Color Registers

The concept of Color Expand with Transparent is completely re-defined on the CL-GD5434. It is much more nearly analogous to Extended Write Mode 4. This is described in some detail in the TRM. Please observe that the application must load all eight color registers: (GR0,1,10,11,12,13,14,15), even for 8- and 16-bit pixels.

### Screen-to-Screen with Color Expand

The source for Screen-to-screen with Color Expand must be on a DWORD boundary. The two LSBs must be '0's.

2

## CL-GD543X Application Alert 7 PCI Configuration Registers 32 Bits Only

### User Interface Group Cirrus Logic, Inc.

#### Scope and Applicability

This Application Alert presents information not found in previous documentation for the CL-GD543x. It is intended to be used in conjunction with applicable CL-GD543x literature

#### **Related Documents**

Alpine VGA Family - CL-GD543x Technical Reference Manual - November 1993

© Copyright — Cirrus Logic, Inc. 1994

All rights reserved. Permission is hereby granted for use, reproduction, republication, or abstraction of this material with attribution, by companies not involved in the sale or manufacture of integrated circuits.

#### **Notice**

This document describes a potential application of Cirrus Logic integrated circuits. No warranty is given for the suitability of the circuitry or program code described herein for any purpose other than demonstrating functional operation. Cirrus Logic believes this information is accurate and reliable. However, it is subject to change without notice. No responsibility is assumed by Cirrus Logic for the use of this information, nor for infringements of patents or other rights of third parties. This document implies no license under patents or copyrights.

#### Introduction

The following issue affects Alpine only when configured for PCI Bus.

Recently a problem was discovered with Microsoft Windows 3.11 EMM386 relating to DWORD I/O cycles. When EMM386 is running it will trap DWORD I/O cycles and will occasionally hang. To work around this, Phoenix, Award, and System Soft BIOS vendors modified their Int 1A routines to never use DWORD I/O.

This uncovered a previously unknown problem in some members of our Alpine family of VGA controllers. If a PCI configuration register is written with a BYTE or WORD I/O cycle, the portion of the register which is not written is cleared to zeroes. The registers effected in this manner are listed in the following table.

#### **List of Registers**

| Address | Name                                       |

|---------|--------------------------------------------|

| 04      | PCI Command/Status Register                |

| 10      | PCI Base Address Register                  |

| 30      | PCI Expansion ROM Base<br>Address Register |

This applies to the following Cirrus Logic Devices:

#### **List Of Devices**

| Device            |

|-------------------|

| CL-GD5430-1MB-Q-X |

| CL-GD5434-HC-B    |

This has been corrected in silicon for the CL-GD5430-1MB-Q-Y and the CL-GD5434-HC-C.

#### Solution

We have requested that Phoenix, Award, and System Soft modify their POST routine to avoid this problem. We have also contacted AMI and confirmed that there is no problem with their BIOS. We are recommending the following changes.

- When initializing the VGA BIOS Base Address register, a DWORD write to 30h should be used. Once the ROM has been transferred and shadowed, access is disabled using bit 0 of 30h (with a DWORD write).

- The PCI Base Address Register at 10h specifies the Display Memory Base Address. This should always be written as a DWORD.

- The PCI Status register is at offset 6 in the PCI configuration space. The POST routine should check this

register for error bits and not clear it if no error bits are set. Since no member of the Alpine family will ever

set any error bits, the write to 06h will never be necessary.

# CL-GD543X Application Alert 8 PCI Non-Contiguous Byte Writes on CL-GD5434 and CL-GD5430-1MB

### User Interface Group Cirrus Logic, Inc.

#### Scope and Applicability

This Application Alert presents information not found in previous documentation for the CL-GD543x. It is intended to be used in conjunction with applicable CL-GD543x literature

#### **Related Documents**

Alpine VGA Family - CL-GD543x Technical Reference Manual - November 1993

© Copyright — Cirrus Logic, Inc. 1994

All rights reserved. Permission is hereby granted for use, reproduction, republication, or abstraction of this material with attribution, by companies not involved in the sale or manufacture of integrated circuits.

#### **Notice**

This document describes a potential application of Cirrus Logic integrated circuits. No warranty is given for the suitability of the circuitry or program code described herein for any purpose other than demonstrating functional operation. Cirrus Logic believes this information is accurate and reliable. However, it is subject to change without notice. No responsibility is assumed by Cirrus Logic for the use of this information, nor for infringements of patents or other rights of third parties. This document implies no license under patents or copyrights.

#### **Revision History**

This is the second version of this document. We have added the 5430-1MB to the list of Cirrus chips which exhibit the problem. A brief description of this item appears in the errata for each chip on which it occurs.

#### Introduction

The PCI bus has the capability of writing multiple bytes that are not contiguous. For example, a write of byte 0 and byte 2, but not byte 1 can occur. When the CL-GD5434 is the target of such a write, it will fail.

#### **Expansion**

Byte merging is where the PCI chipset takes multiple byte writes from the CPU and merges them into one write on a 32-bit boundary. When this occurs, the bytes to be written may not be contiguous (for example, BE1 and BE3 may be active while BE0 and BE2 are not). The Intel Saturn (82420) and Mercury I (82430) chipsets do not support byte merge. Newer chips set from Intel, currently not in volume production, will support byte merge.

This was first observed when loading Windows NT. The CPU was writing odd bytes to B800, B802, etc. The chipset merged these writes into DWORD operations with non-contiguous bytes. On the third such operation, the CL-GD5434 failed to assert TRDY, hanging the system.

This problem occurs only during planar mode writes; it will not occur in packed-pixel modes. The cause of the problem is well understood.

This problem occurs with the CL-GD5434-HC-AF (production B), the CL-GD5434-HC-AJ (production C), the CL-GD5430-1MB-Q-X, and the CL-GD5430-1MB-Q-Y. This problem will not occur in the CL-GD5430-QC-A.

#### Solution

The exposure to this item is minimal at this time because there are very few platforms available today based on chip sets which support byte merging. No chip set available from any vendor other than Intel supports byte merging. We have asked the system BIOS vendors to disable the feature for any chip sets which do support it, or at least to make provisions in the CMOS setup to disable it. All BIOS vendors have responded positively to this request.

This will be fixed in a future revision of the CL-GD5434.

#### **CL-GD543X APPLICATION ALERT 8**

## CL-GD54XX Combined Application Alert 1 Colored Borders

User Interface Group Cirrus Logic, Inc.

#### Scope and Applicability

This Application Alert presents information not found in previous documentation for the CL-GD54XX. It is intended to be used in conjunction with applicable CL-GD54XX literature

#### **Related Documents**

- Alpine VGA Family CL-GD543x Technical Reference Manual - November 1993

- True Color VGA Family- CL-GD542X Technical Reference Manual - January 1994

Version 1.0 March 1994

#### **Notice**

This document describes a potential application of Cirrus Logic integrated circuits. No warranty is given for the suitability of the circuitry or program code described herein for any purpose other than demonstrating functional operation. Cirrus Logic believes this information is accurate and reliable. However, it is subject to change without notice. No responsibility is assumed by Cirrus Logic for the use of this information, nor for infringements of patents or other rights of third parties. This document implies no license under patents or copyrights.

**Revision History**

This is the initial release of this document.

#### Introduction

It is possible to program the members of the CL-GD542X and CL-GD543X families for a border around the active portion of the screen in standard and extended video modes. The display of such a border is popular in Europe but less so in North America. This is also referred to as overscan.

In the standard VGA the border color is taken from the palette entry which is pointed to by AR11. The Cirrus Logic controllers provide an alternative location for the border color that is protected from normal palette accesses and which does not use a standard palette entry.

#### **Exposition**

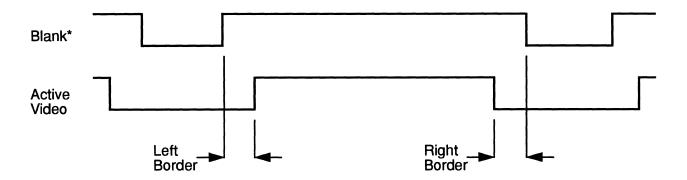

The following diagram shows the timing for the horizontal sweep. There is a period on the left edge of the

screen after Blank has gone inactive but before the Active Video begins. If the video presented during this period is black, then it is not distinguishable from Blank. If the video is some other color then a colored bar will appear on the left edge of the screen. Similarly, it the right border is programmed a color other than black, a bar will appear on the right edge of the screen.

When this has been extended to the top and bottom, a border will appear completely around the active video. In European standards, this border is large enough to fill the screen to the bezel.

The Cirrus Logic CL-GD542X and CL-GD543X controller chips provide an extended entry in the Palette to contain the color for this border. This entry is referred to as entry 258. It can be accessed at palette entry 02 when SR12[1] is programmed to a '1'. Once the entry is programmed to the desired color, SR12[1] should be programmed to a '0' to enable access to the normal palette entries and SR12[7] should be programmed to a '1' to enable the extended entry for the border.

#### **Extended Video Modes**

The VESA specifications for extended video modes specify zero border timing. However, the Cirrus Logic BIOSs program a small border and then suppress it by programming CR1B[5] to a one. The border can be enabled by programming CR1B[5] to a '0'. The border programmed by the BIOS is not guaranteed to

be any particular size (and is certainly not suitable for the European overscan) and will therefore have to be modified by the OEM.

#### **Program**

The following program shows how to program the extra palette entry and how to program CR1B[5]. It is written in C++.

```

#include <dos.h>

#include <stdio.h>

#include <stdlib.h>

main(int argc, char **argv)

unsigned char red, green, blue;

unsigned int temp, crreg;

setcbrk(1);

if (argc < 4)

printf ("BORDER.EXE, an overscan programming tool \n");

printf ("Ver 1.00 3/14/94 YBK/tc \n");

printf ("Usage: BORDER red green blue \n");

printf ("red = 0..63 \n");

printf ("green = 0..63 \n");

printf ("blue = 0..63 \n");

exit(1);

red = atoi(argv[1]);

green = atoi(argv[2]);

blue = atoi(argv[3]);

crreg = 0x3b4;

//assume monochrome mode

//read the MISC register

temp = inportb(0x3cc);

if (temp & 1) crreg= 0x3d4;

//color case

outportb(0x3c4,0x12);

//point to SR12

temp = inportb(0x3c5);

outportb(0x3c5, temp | 2);

/set SR12[1] to enable access to

//to DAC extended entries

//RAMDAC address 2

outportb(0x3c8,2);

outportb(0x3c9,red);

//set color bytes

outportb(0x3c9,green);

outportb(0x3c9,blue);

outportb(0x3c5, temp | 0x80);

//enable overlay

//point to cr1b

outportb(crreg, 0x1b);

temp = inportb(crreg + 1);

outportb(crreg+1, temp & 0xdf); //clear cr1b[5]

}

```

#### 1 Introduction

The Cirrus Logic families of VGA controllers (CL-GD542X, CL-GD543X, and CL-GD545X) comprise highly integrated, mixed signal circuits with high operating frequencies. These chips are designed into video subsystems with very high bandwidth busses. Boards based on these controllers will provide a reliable, compact circuit if designed with care.

This note distills the experiences gathered by Cirrus Logic in the course of completing our reference designs and in the course of helping our customers solve their problems into a single document.

#### 2 Parts Placement and Adapter Card Considerations

The first consideration is component placement. This section covers the placement of the Cirrus Logic chip. In addition, specific considerations for various Adapter Cards are covered. Subsequent sections will cover how to place the passive devices around the main chip.

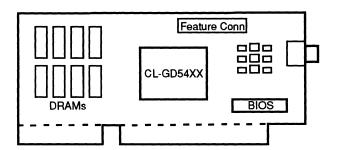

#### 2.1 ISA Bus Adapter Card

The general parts placement for an ISA adapter should follow the diagram below. The Cirrus Logic chip is positioned close to the ISA interface and relatively close to the VGA feature connector.

The following considerations apply to adapter boards for ISA bus. RESET and IOCHRDY should be isolated from the system data and system address bus lines to avoid coupling noise into them. This can be done by placing them on the other side of a multi-layer board, or by using ground lines as shields. The layout should provide for RC filters for RESET, IOR\*, IOW\*, MEMR\*, and MEMW\*. Generally, they will not be required but it is better to make provisions that are unnecessary than the converse. These filters should be close to the Cirrus Logic chip. Finally, it may be necessary to provide termination resistors for SD[7:0]. These should be Thevinin equivalents with 330 ohms to VCC and 470 ohms to ground. A single 10-pin SIP contains the eight terminators required for the eight data lines.

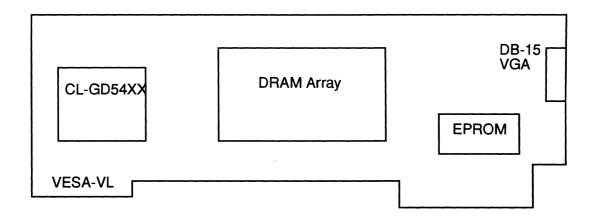

#### 2.2 VESA-VL Bus Adapter Card

Due to the three inch trace maximum imposed by the VESA-VL specification, there is no choice as to where to position the Cirrus Logic controller on a VESA-VL adapter card. It will have to be very near the VESA connector, even though this means placing it far from the DB15 VGA connector. This is shown in the diagram which follows.

The following considerations apply to adapter boards for VESA-VL and PCI bus. The CLK signal is critical and special care should be given to its routing. It should be as short as possible and dressed away from other signals that are apt to induce noise. LDEV# is also critical; it should be routed next.

The RGB traces must be designed to have a characteristic impedance of 75 ohms with no vias or sharp turns. They should be isolated from the DRAM array, either by being routed around the array or on the other side of the board from the traces going to the array.

For information regarding VESA, please contact:

**VESA**

2150 North First Street, Suite 440 San Jose, CA, 95131-2029 (408) 435-0333

FAX: (408) 435-8225

## CL-GD54XX Combined Application Alert 2 Layout Guidelines

User Interface Group Cirrus Logic, Inc.

#### **Scope and Applicability**

This Application Alert presents information not found in previous documentation for the CL-GD54XX. It is intended to be used in conjunction with applicable CL-GD54XX literature

#### **Related Documents**

- Alpine VGA Family Technical Reference Manual- Nov 93

- True Color VGA Family Technical Reference Manual Jan 94

#### **Notice**

This document describes a potential application of Cirrus Logic integrated circuits. No warranty is given for the suitability of the circuitry or program code described herein for any purpose other than demonstrating functional operation. Cirrus Logic believes this information is accurate and reliable. However, it is subject to change without notice. No responsibility is assumed by Cirrus Logic for the use of this information, nor for infringements of patents or other rights of third parties. This document implies no license under patents or copyrights.

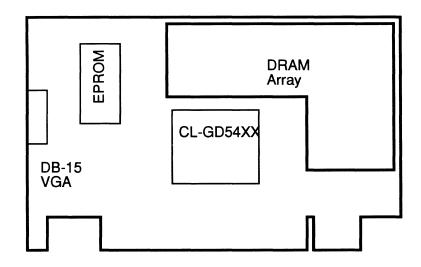

#### 2.3 PCI Bus Adapter Card

The requirements of the PCI specification leave little latitude in the placement of the Cirrus Logic chip. The reference design places the chip near the center of the board with the DRAM array in the upper right portion. The PCI board is much smaller that the VESA-VL board, allowing the chip to be placed in close proximity. This is shown in the diagram which follows.

Questions regarding the PCI specification or membership in the PCI Special Interest Group may be forwarded to:

PCI Special Interest Group M/S HF3-15A 5200 N.E. Elam Young Parkway Hillsboro, OR, 97124-6497 (503) 696-2000

#### 2.4 Motherboard

Parts placement is as important in a motherboard design as in any adapter card. The Cirrus Logic controller should simultaneously be close to the CPU and the Core Logic, its DRAM array, and the VGA DB15 connector. At the same time, it should be well away from components on the motherboard which could induce noise, such as the main memory, keyboard controller and other peripherals, and the adapter slots.

#### 3 Power

Cirrus Logic recommends the use of multi-layer boards for its components, especially when designed into high performance systems. As frequencies continue to get higher, it becomes less and less likely that one can obtain acceptable results with a two-layer board. One plane should be dedicated exclusively to the distribution of power and one plane should be dedicated exclusively to ground.

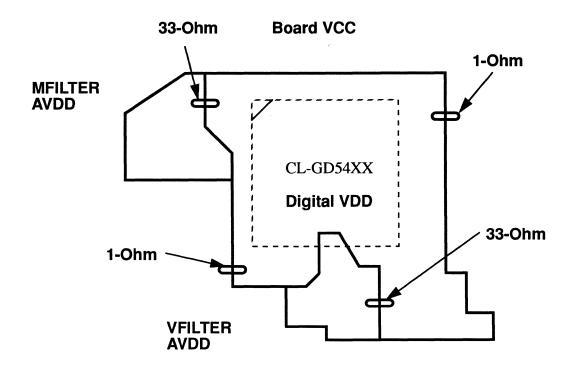

There should be cuts in the power plane to completely isolate the three power rails distributed to the Cirrus Logic chip from the VCC on the board and from each other. The diagram which follows shows how the cuts are made on a typical board.

It can be seen in the diagram which follows- and in the schematics for the Cirrus Logic Reference designs - that a 1/2 ohm resistor is placed in series between the board VCC and the digital VDD pins of the Cirrus Logic chip (the 1/2 ohm resistor is actually mechanized as two 1 ohm resistors in parallel with each other). This resistor serves as part of an RC filter to isolate the Cirrus chip from noise on the VCC rail, and to provide additional latch-up protection.

Two areas of the power plane must be further isolated. One of these is for AVDD1 (VCLK synthesizer) and one is for AVDD4 (MCLK synthesizer). As shown in the reference designs, these areas are individually further isolated with 33 ohm series resistors that serve as RC filter components.

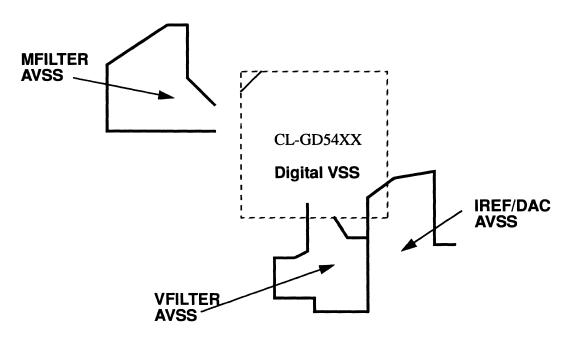

#### 4 Ground

One plane on the board must be dedicated to ground. The ground should have cuts that suppress currents between the various areas (but that do not provide complete isolation). These cuts are shown in the following diagram for a typical reference design.

There is a certain amount of art involved in the exact positioning and size of the cuts in the ground plane and the power plane. Some experimentation may be required to obtain satisfactory results.

The power plane and ground plane cuts should follow each other. It is critical that an isolated ground or power plane not overlay a noisy digital power or ground plane. If such an overlay were to be allowed, the result would be a capacitor composed of the overlay conductors separated by the relatively thin dielectric between the two pieces of epoxy that make up a four-layer board. Noisy busses (such as data or address) should not be allowed to cross any isolated area.

The ground cuts should not interfere in any way with the return currents between the controller and the DRAM array. Any ground differential between the controller and the DRAM array will directly subtract from the TTL margins.

Cirrus Logic can provide reference designs of adapter cards for various chips which yield satisfactory results and pass FCC Class B emission tests.

Designers with prior experience using discrete RAMDACs and clock sources may have found that such care with power distribution and isolation was not necessary, especially at relatively low frequencies. The integrated solution available from Cirrus Logic, operating at high frequencies, has changed this, making these precautions necessary.

#### 5 Decoupling Capacitors

The Cirrus Logic chips operate at high frequencies (over 100 MHz in some cases). Adequate power decoupling is absolutely crucial to a successful design. Each power pin on the chip should have a 0.1 uF capacitor returned to the local ground. These capacitors should be placed as closely to the respective power pins as possible. These capacitors must have excellent high frequency characteristics; Cirrus Logic has found the surface mount ceramic chip capacitors perform adequately.

The high frequency capacitors for AVDD must be on the power pin side of the respective 33 ohm resistors, should be as close to the power pin as possible, and must be returned to the appropriate local ground.

The board design must include adequate bulk bypassing; typically Tantalum capacitors will serve this function. The high frequency characteristics of the bulk bypass capacitors is not as critical as that of the high frequency caps.

#### 6 Synthesizer Filters

The two synthesizer filter pins, MFILTER and VFILTER, must each be connected to a PI RC filter as shown in the reference schematic designs. The filter components, especially the input capacitor and the resistor, must be located as closely to the respective filter pins as possible. The capacitors must be returned to the appropriate AVSS. The traces to the filter pins should be wide (25 mils).

#### 7 IREF Circuitry

The current reference to the DAC (IREF) should be generated using the LM334 circuit shown in the reference designs. The components should be returned to DAC/IREF section of ground plane shown in the previous diagram. A capacitor on the order of 0.1 uF between IREF and AVDD may be necessary to suppress noise in some layouts. Provisions should be made for such a capacitor. During system evaluation the decision can be made as to whether to use the capacitor, and if so, its exact value.

#### 8 RGB Lines

The RGB traces are likely to be fairly long, especially on a VESA-VL adapter card. The rise and fall times on these traces are going to be on the order of 2-4 ns, causing them to behave as transmission lines. This means that the characteristic impedance must be controlled and should be close to the nominal monitor termination value of 75 ohms.

There must be PI LC filters on each of the RGB lines, as shown in the reference designs. The recommended component values are 10 pF for the capacitors. The inductor is a ferrite bead, with 10-20 ohms impedance at 100 MHz.

There is a trade-off involved in the selection of these component values. Obtaining crisp video on the screen requires that the rise and fall times be as short as possible. However, to obtain acceptable emissions testing results, one would like relatively slow rise and fall times. As the pixel rates get higher and higher, there will be less and less margin between these two conflicting requirements. The component values recommended above represent our recommendation as of the time of this writing. The filter components must be placed as closely to the VGA DB15 connector as possible.

A 75 ohm resistor to AVSS is specified for each of the RGB lines. These resistors should be placed as closely to the Cirrus Logic chip as possible.

#### 9 DRAM Array

The DRAMs in Display Memory typically operate as fast as or faster than those in the system memory. The layout of this array should be given as much consideration as that of the system memory. The following general rules apply.

The devices should be placed close to the Cirrus Logic controller. In addition, they should be organized so that each individual device is close to the respective MD pins on the controller. The pin-outs on the controller were carefully optimized to allow this.

The control lines should be treated as the fast, heavily loaded lines they are. Relatively wide traces should be used (8 to 10 mils is typical) and they should be adequately spaced. Placing the traces on 25 mil centers would be ideal. Insofar as it is possible, long parallel runs should be avoided.

Provisions should be made for damping resistors to minimize noise in the array. The damping resistors should be placed at the controller end of the lines.

#### 10 DCLK Line to Feature Connector

Provisions should be made to insert a resistor or inductor in the DCLK line to the Feature Connector. This may prove to be very useful in emissions testing.

Mar 1994

## CL-GD54XX Combined Application Alert 3 Designing for VESA Display Data Channel (DDC1)

### User Interface Group Cirrus Logic, Inc.

#### **Scope and Applicability**

This Application Alert presents information not found in previous documentation for the CL-GD543x. It is intended to be used in conjunction with applicable CL-GD543x literature

#### **Related Documents**

Alpine VGA Family - CL-GD543x Technical Reference Manual - November 1993

© Copyright — Cirrus Logic, Inc. 1994

All rights reserved. Permission is hereby granted for use, reproduction, republication, or abstraction of this material with attribution, by companies not involved in the sale or manufacture of integrated circuits.

Version 1.2 March 1994

#### **Notice**

This document describes a potential application of Cirrus Logic integrated circuits. No warranty is given for the suitability of the circuitry or program code described herein for any purpose other than demonstrating functional operation. Cirrus Logic believes this information is accurate and reliable. However, it is subject to change without notice. No responsibility is assumed by Cirrus Logic for the use of this information, nor for infringements of patents or other rights of third parties. This document implies no license under patents or copyrights.

#### **Revision History**

This corrects Version 1.0 of this document, which incorrectly stated that ID3 is used for level 1 DDC, and Version 1.1 which incorrectly stated that ID2 is used.

#### Introduction

The VESA Display Data Channel (DDC) Proposal defines a communication channel between a computer display and the host system. The channel may be used to carry configuration information for optimum use of the display as well as carry additional display control information.

This application alert shows how Cirrus Logic recommends that its CL-GD542X and CL-GD543X chips be configured to support DDC level 1.

#### **Hardware**

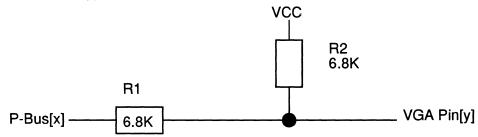

Since late 1993, all Cirrus Logic reference designs have included (passive) components that allow software to sense TTL levels on the monitor ID pins 15-pin VGA connector. The following diagram indicates how this is mechanized for a typical pin.

If the pin on the VGA connector is open or is being driven to a TTL HIGH, a soft high will appear on the P-Bus pin. If the pin on the VGA connector is grounded or is being driven to a TTL LOW, a soft low will appear on the P-Bus pin. If the overlay control field in CR1A[3:2] is programmed to any value other than 0,0 the P-Bus pins will be inputs and their levels can be sensed in the STAT register (3DA or 3BA). The following table shows how the pins are allocated and how they are sensed.

| Mon ID Bit | VGA Pin | P-Bus | Program<br>AR12[5:4] to | Sense on STAT[x] |  |

|------------|---------|-------|-------------------------|------------------|--|

| 0          | 11      | P0    | 00                      | 4                |  |

| 1          | 12      | P1    | 10                      | 4                |  |

| 2          | 4       | P2    | 00                      | 5                |  |

| 3          | 15      | P3    | 10                      | 5                |  |

For DDC1, only Mon ID1 needs to be connected. Connecting bits 0 and 2 will allow the implementation to support the old method of monitor ID sensing.

### CL-GD54XX COMBINED APPLICATION ALERT 3

#### **Software Note**

For DDC1, the only Monitor ID bit that needs to be sensed is ID1. The following psuedo-code fragment shows how to sense ID1. It may be possible to move the save and restore code to the outside of a loop that recovers the entire byte or string from ID1.

read, save AR12 read, save CR1A AR12[5:4] = 10 CR1A[3:2]= 10 P1\_Val = STAT[4] restore CR1A restore AR12

;will read the data on P[1] ;set to switch with EVIDEO (EVIDEO remains input) ;read stat register; keep bit 4

# Section 3 Application Notes

CL-GD543X

## Appendix B5

**CL-GD5430 Differences**

#### 1. Introduction

The purpose of the Appendix is to summarize how the CL-GD5430 is different from the CL-GD5434. This is written for someone who is familiar with the '34 and simply wishes to understand how the '30 differs.

#### 2. Several Video modes/Frequencies not supported

The 5430 supports only 2 MBytes of display memory, and effectively has only a 32-bit memory interface. This restricts the memory modes/refresh frequencies that are supported. See Appendix E1. See App Alert 2 to see how to connect the RAS lines for a compatible 5430/34 board.

#### 3. 5430 does not support 32-bit-pixel modes.

SR7[3:1] must not be programmed to 100. GR30[5:4] must not be programmed to 11. Registers GR12-GR15 do not exist on the 5430.

#### 4. 5430 does not support ISA bus

The CL-GD5430 is a local bus device.

#### 5. Extension Registers Always Enabled

SR6 returns the values 12h or 0fh, depending on the value last written to it. The extension registers are always enabled.

#### 6. SRF[7]

Bank switching is always enabled on the 5430. RAS1\* connects to the first MB, RAS\* connects to the 2nd MB.

#### 7. CRT FIFO Depth Control: SRF[5]

Programming this bit to a '1' sets the FIFO depth to 20 rather than 32.

#### 8. MCLK

Since we are quoting a maximum MCLK of 60 MHz, the maximum value SR1F[5:0] can be programmed to will increase from 1Ch to 22h. This is certainly subject to our evaluation of the silicon.

#### 9. SR17[7]

The 5430 does not support this bit (Disable DRAM Refresh).

#### 10. Power Management Features

GRE[3] selects Static Clock Mode. MCLK and VCLK are gated off; the chip dissipates only static power. The RAMDAC is powered off. DRAM refresh continues. I/O reads and writes may take place except to the palette. Memory reads and writes and I/O reads and writes to the palette will not hang the system, but will not *product* deterministic results.

Appendix B21 describes Power Management in detail.

#### 11. BLT Destination/Source Start Registers

The 5430 supports only 2 MB. GR2A[5], GR2E[5] are not used.

#### 12. BLT Destination Write Mask: GR2F[2:0]

If this field is programmed to any value other than '0', then n pixels will not be written on the left edge of each scanline for a color-expanded BLT. This is described in detail in Appendix D8.

#### 13. Vertical Preset for Color-Expanded BLT

The three low-order bits of the source address chose the scan line of source data to be used for the first (or only) scanline. This makes it possible to force vertical alignment of the pattern. The source must be aligned.

#### 14. BLT Transparency

For Color Expand with Transparency, the CL-GD5430 does not require that the background color registers be loaded. Also GR11 need not be programmed for 8 bit-per-pixel color expand with transparency.

#### 15. Memory-mapped I/O at Selectable Locations

SR17[6] selects the address space for memory-mapped I/O

#### 16. Overlay/DAC Mode Switching Controls

The internal OVRW\* can be chosen for the SWITCH signal without being fed back as EV-IDEO\*. Refer to CR1D[6]

Choosing EVIDEO\* ANDed with OVRW\* (CR1A[3:2] = 1,0) functions as originally intended.

Color Key Compare type is always identity (no arithmetic compares) CR1D[5:4]

See Appendix B14 for a complete description of Overlay functions.

#### 17. VAFC Baseline Input

Bit 5 of the Hidden DAC Register is redefined to support VESA VAFC baseline input. It controls Pixel Doubling in 16 bit/pixel display modes.

The VCLK VCO is available on the MCLK pin.

#### 18. Chip ID Updated

The device ID in CR27[7:2] and PCI[0] is changed as indicated in the following table:

Table 1: Device ID

| Product   | ID     |

|-----------|--------|

| CL-GD5430 | 101000 |

| CL-GD5434 | 101010 |

#### 19. Configuration options changes:

5430 supports MCLK pin source (VCLK VCO on MCLK)

5430 does not support "Disable Internal DAC"

#### 20. CR1C Removed

GENLOCK and Sync Adjust are not present on the 5430

It is actually unknown at this time whether we will have Genlock on the '30.

#### 21. Hidden DAC Register Mode 01xx1010

The palette clock doubling mode is not supported on the 5430.

#### 22. PCI Relocatable I/O

The 5430 supports relocated I/O addresses for PCI only.

## Appendix E1

VGA BIOS

External Function Specification