### TPS544B20, TPS544C20

ZHCSCI5B - MAY 2014 - REVISED JULY 2016

# TPS544x20 4.5V 至 18V, 20A 和 30A SWIFT ™ 同步降压控制器(具有 PMBus™

## 1 特性

- 启用 PMBus 的转换器: 20A, 30A

- 4.5V 至 18V 输入, 0.6V 至 5.5V 输出

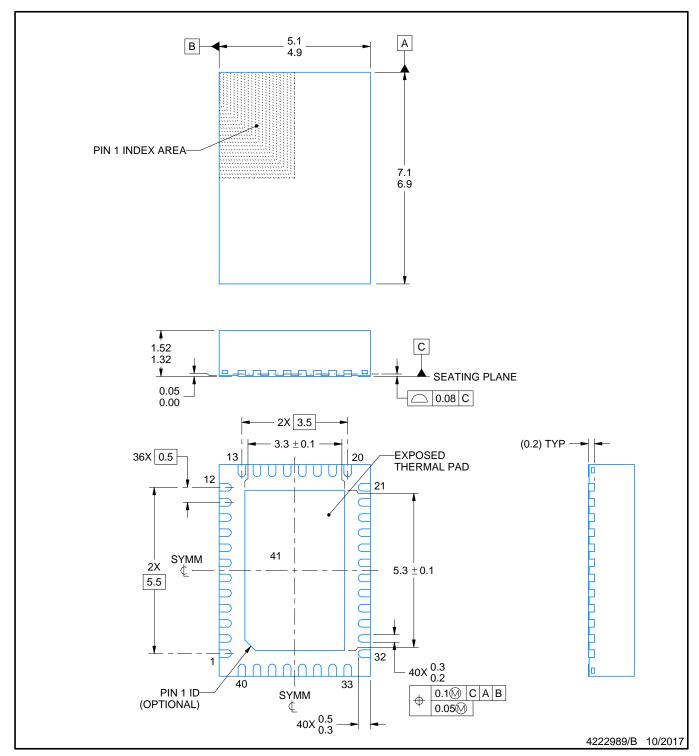

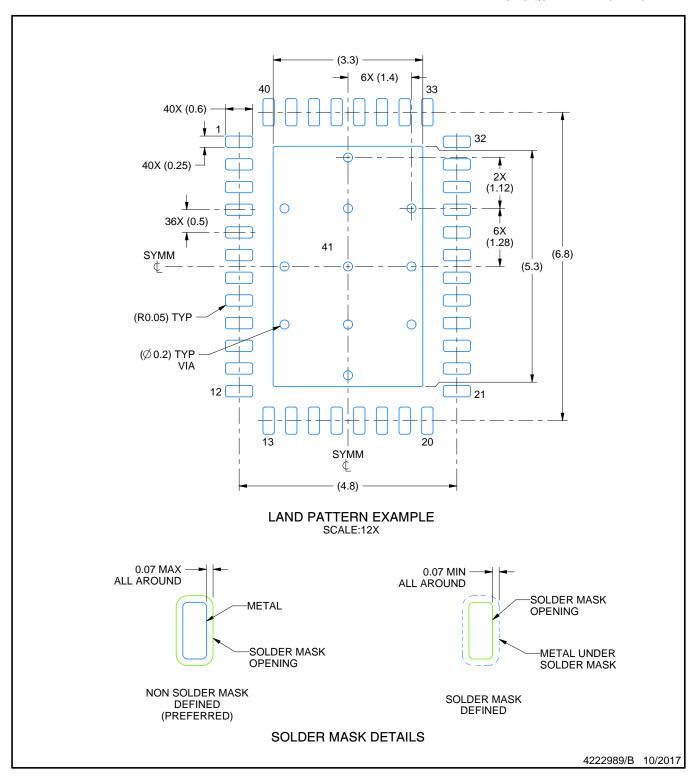

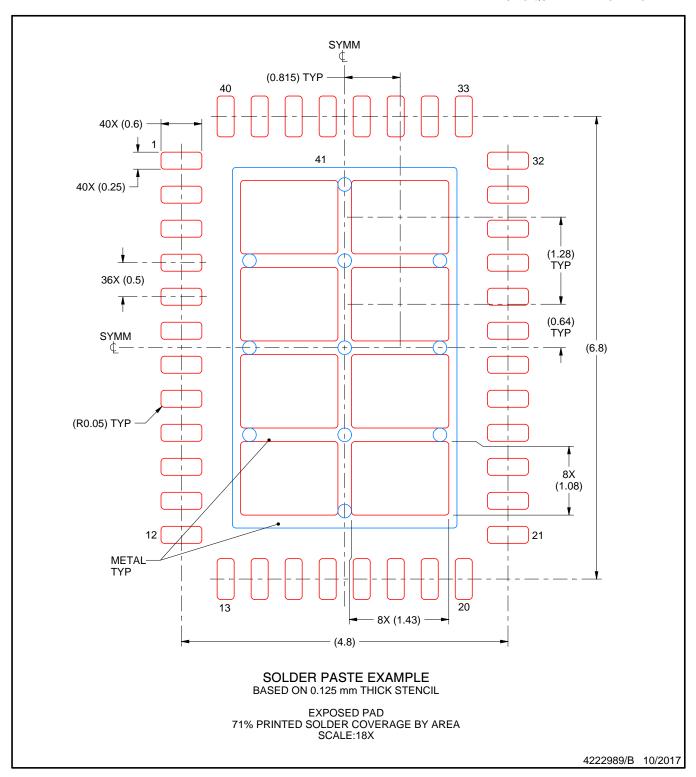

- 5mm x 7mm 薄型四方扁平无引线 (LQFN) 封装, 焊球间距为 0.5mm

- 单个散热焊盘

- 集成 4.5mΩ 和 2.0mΩ 堆叠 NexFET™功率级

- 600mV, 0.5% 基准

- 无损耗、低侧金属氧化物半导体场效应晶体管 (MOSFET) 电流感测

- 可选 D-CAP™和 D-CAP2™模式控制

- 差分远程感应

- 单启动至预偏置输出

- 输出电压裕度和修整

- 输出电压和输出电流报告

- 使用 2N3904 时的外部温度监视

- 可经由 PMBus 编程

- 过流保护

- 欠压闭锁 (UVLO), 软启动

- 电源正常 (PGOOD),过压 (OV),欠压 (UV), 过热 (OT) 电平

- 故障响应

- 接通和关闭延迟

- 热关断

- 引脚兼容 20A, 30A 转换器

## 2 应用范围

- 测试和测量仪器

- 以太网交换机、光交换机、路由器、基站

- 服务器

- 企业级存储固态硬盘 (SSD)

- 高密度电源解决方案

#### 3 说明

TPS544B20 和 TPS544C20 器件是 PMBus 兼容型非隔离式直流/直流集成式 FET 转换器,支持高频运行并提供 20A 或 30A 电流输出,采用 5mm × 7mm 封装,可实现高功率密度和快速瞬态性能,具有最小的 PCB面积。PMBus 接口用于转换器配置,并监视关键参数,其中包括输出电压、电流和一个可选外部温度。由集成 NexFET 功率级和经优化驱动器提供的高频、低损耗开关可实现极高密度电源解决方案以及减小的电感器和滤波电容器尺寸。根据系统要求,对故障情况的响应可被设定为重新启动或锁断。

表 1. 器件信息(1)

| 部件名称      | 封装        | 封装尺寸 (标称值)      |  |  |

|-----------|-----------|-----------------|--|--|

| TPS544B20 | LOEN (40) | 5.00mm v 7.00mm |  |  |

| TPS544C20 | LQFN (40) | 5.00mm x 7.00mm |  |  |

(1) 如需了解所有可用封装,请见数据表末尾的可订购产品附录。

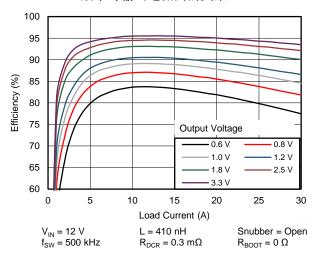

## 效率与输出电流间的关系

| - TA |

|------|

| אניו |

|      |

| 1 | 特性1                                  |    | 8.5 Programming                 | 28              |

|---|--------------------------------------|----|---------------------------------|-----------------|

| 2 | 应用范围 1                               |    | 8.6 Register Maps               |                 |

| 3 |                                      | 9  | Applications and Implementation | <mark>52</mark> |

| 4 | 修订历史记录                               |    | 9.1 Application Information     | 52              |

| 5 | Device Comparison Table 4            |    | 9.2 Typical Application         | 52              |

| 6 | Pin Configuration and Functions4     | 10 | Power Supply Recommendations    | 61              |

| 7 | Specifications                       | 11 | Layout                          | <mark>62</mark> |

| • | 7.1 Absolute Maximum Ratings         |    | 11.1 Layout Guidelines          | 62              |

|   | 7.2 ESD Ratings                      |    | 11.2 Layout Example             | 63              |

|   | 7.3 Recommended Operating Conditions | 12 | 器件和文档支持                         | 65              |

|   | 7.4 Thermal Information              |    | 12.1 器件支持                       | 65              |

|   | 7.5 Electrical Characteristics       |    | 12.2 相关链接                       | 66              |

|   | 7.6 Switching Characteristics        |    | 12.3 商标                         | 66              |

|   | 7.7 Typical Characteristics          |    | 12.4 接收文档更新通知                   | 67              |

| 8 | Detailed Description                 |    | 12.5 社区资源                       | 67              |

| _ | 8.1 Overview                         |    | 12.6 静电放电警告                     | 67              |

|   | 8.2 Functional Block Diagram         |    | 12.7 Glossary                   |                 |

|   | 8.3 Feature Description              | 13 | 机械、封装和可订购信息                     | 67              |

|   | 8.4 Device Functional Modes          |    |                                 |                 |

#### 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| O. | hanges from Revision A (February 2016) to Revision B                                                                                                                                     | Page |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •  | Changed From: PGND to GND in the <i>Pin Functions</i> table Description for pins BP6 and BPEXT                                                                                           | 4    |

| •  | Changed <i>Pin Functions</i> table Description for VDD pin To: "Bypass with a 0.1-µF to 1.0-µF capacitor to GND (thermal pad or GND pins) or through a dedicated connection to AGNDSNS." | 5    |

| •  | Changed From: "PGND" To: "GND" in Linear Regulators BP3 and BP6 and External Bypass (BPEXT) Section text.                                                                                | 20   |

| •  | Changed instances From: "PGND" To: "GND" in the Device Functional Modes                                                                                                                  | 27   |

| •  | Changed From: " a value of 4.7 μF" To: " a value of 0.1 μF to 1.0 μF" in the <i>Input Capacitor Selection</i>                                                                            | 55   |

| •  | Changed text string From: "one 4.7-μF, 25-V ceramic capacitor" To: "one 1.0-μF, 25-V ceramic capacitor" in the Input Capacitor Selection description.                                    |      |

| •  | Changed From: "PGND" To: "GND" in the BP6, BP3 and BPEXT section                                                                                                                         | 56   |

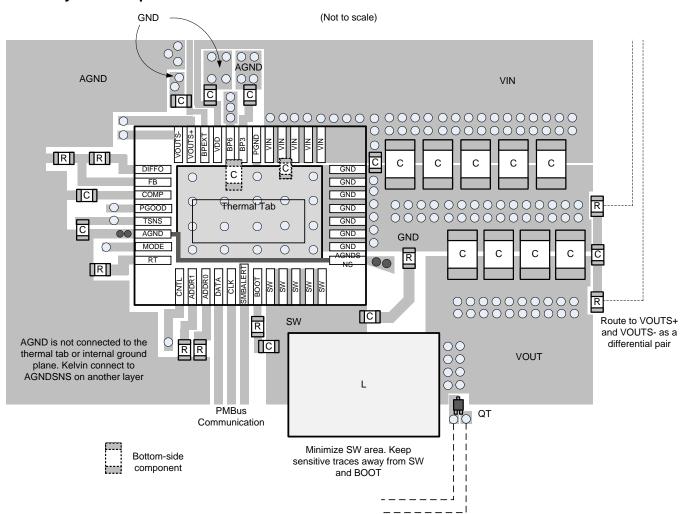

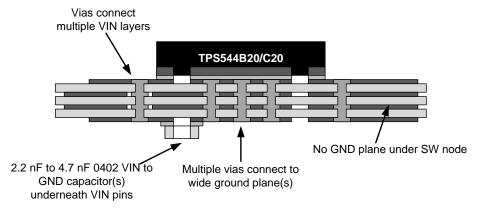

| •  | Added text to Layout Guidelines section for emphasis on grounding schemes.                                                                                                               | 62   |

| •  | Changed PCB Layout Recommendation figure.                                                                                                                                                | 63   |

| •  | 已添加 接收文档更新通知 部分                                                                                                                                                                          | 67   |

##

Changed "IVADDR" to "IVFREQ" for Function at Bit Position 4 of the STATUS MFR SPECIFIC (80h); and also in

| www |  |  |  |  |

|-----|--|--|--|--|

|     |  |  |  |  |

## 5 Device Comparison Table

| DEVICE NUMBER | CURRENT OPTION (A) |

|---------------|--------------------|

| TPS544B20     | 20                 |

| TPS544C20     | 30                 |

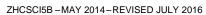

## 6 Pin Configuration and Functions

#### **Pin Functions**

| PIN YO (1)                                                                                                                                                                                                                                                                                                                                                        |     | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                                                                                                                                                                                                                                                                                                                              | NO. | 1/0("/             | DESCRIPTION                                                                                                                                                          |

| ADDR0                                                                                                                                                                                                                                                                                                                                                             | 3   | 0                  | Sets low order 3-bits of the PMBus address. Connect a resistor from this pin to AGND.                                                                                |

| ADDR1                                                                                                                                                                                                                                                                                                                                                             | 2   | 0                  | Sets high order 3-bits of the PMBus address. Connect a resistor from this pin to AGND.                                                                               |

| AGNDSNS  Analog ground sense. Provides Kelvin connection point to analog ground for precise current measurement. AGNDSNS is internally connected to the thermal tab. Do not connect to the thermal taexternally. Kelvin connect back to AGND pin with a low impedance, low noise path. This kelvin connection serves as the only connection between AGND and GND. |     |                    |                                                                                                                                                                      |

| AGND                                                                                                                                                                                                                                                                                                                                                              | 38  | G                  | Analog ground return for control circuitry. AGND should not be connected to the exposed thermal pad, GND or PGND, but should be Kelvin connected to the AGNDSNS pin. |

| BP3                                                                                                                                                                                                                                                                                                                                                               | 27  | S                  | Output of the 3.3-V on-board regulator. This regulator powers the controller and should be bypassed with a minimum of 100-nF capacitor to AGND.                      |

| BP6                                                                                                                                                                                                                                                                                                                                                               | 28  | S                  | Output of the 6-V on-board regulator. This regulator powers the driver stage of the controller and should be bypassed with a 4.7-µF ceramic capacitor to GND.        |

| воот                                                                                                                                                                                                                                                                                                                                                              | 7   | S                  | Bootstrap pin for the internal flying high-side driver. Connect a typical 100-nF capacitor from this pin to the SW pins.                                             |

(1) I = Input, O = Output, P = Supply, G = Ground

## Pin Functions (continued)

| PIN         |     | VO <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                   |

|-------------|-----|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | NO. | 1/0               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                   |

| BPEXT       | 30  | I                 | External BP voltage for BP crossover function. Bypass with a 4.7-µF ceramic capacitor to GND if used Connect to GND if not used.                                                                                                                                                                                                                              |

| CLK         | 5   | I                 | PMBus CLK pin. See PMBus specification.                                                                                                                                                                                                                                                                                                                       |

| CNTL        | 1   | I                 | PMBus CNTL pin. See PMBus specification.                                                                                                                                                                                                                                                                                                                      |

| СОМР        | 35  | 0                 | Output of the error amplifier. This regulates the D-CAP and D-CAP2 valley voltage reference for output regulation and should be bypassed with a 10-nF capacitor to AGND.                                                                                                                                                                                      |

| DATA        | 4   | I/O               | PMBus DATA pin. See PMBus specification.                                                                                                                                                                                                                                                                                                                      |

| DIFFO       | 33  | 0                 | Output of the differential sense amplifier.                                                                                                                                                                                                                                                                                                                   |

| FB          | 34  | I                 | Feedback pin for the control loop. Regulates to a nominal 600 mV if there is no trim applied to the device using VREF_TRIM.                                                                                                                                                                                                                                   |

|             | 14  |                   |                                                                                                                                                                                                                                                                                                                                                               |

|             | 15  |                   |                                                                                                                                                                                                                                                                                                                                                               |

|             | 16  |                   |                                                                                                                                                                                                                                                                                                                                                               |

| GND         | 17  | G                 | Power stage ground return.                                                                                                                                                                                                                                                                                                                                    |

|             | 18  |                   |                                                                                                                                                                                                                                                                                                                                                               |

|             | 19  |                   |                                                                                                                                                                                                                                                                                                                                                               |

|             | 20  |                   |                                                                                                                                                                                                                                                                                                                                                               |

| PGND        | 26  | G                 | Power ground return for controller device. Connect to GND at the thermal tab with a minimum 8 mil wide PCB trace                                                                                                                                                                                                                                              |

| PGOOD       | 36  | 0                 | Power good output. Open drain output that floats up when the device is operating and in regulation. Any fault condition causes this pin to pull low.                                                                                                                                                                                                          |

| RT          | 40  | 0                 | Frequency-setting resistor. Connect a resistor from this pin to AGND to program the switching frequency.                                                                                                                                                                                                                                                      |

| SMBALERT    | 6   | 0                 | SMBus alert pin. See SMBus specification.                                                                                                                                                                                                                                                                                                                     |

|             | 8   |                   |                                                                                                                                                                                                                                                                                                                                                               |

|             | 9   |                   |                                                                                                                                                                                                                                                                                                                                                               |

| SW          | 10  | 0                 | Switched power output of the device. Connect the output averaging filter and bootstrap capacitor to this group of pins.                                                                                                                                                                                                                                       |

|             | 11  |                   |                                                                                                                                                                                                                                                                                                                                                               |

|             | 12  |                   |                                                                                                                                                                                                                                                                                                                                                               |

| MODE        | 39  | I                 | D-CAP and D-CAP2 control mode selection pin. Connect to BP3 for D-CAP2 mode control. Connect to AGND for D-CAP mode control.                                                                                                                                                                                                                                  |

| TSNS        | 37  | 0                 | External temperature sense signal input. TSNS can be connected to AGND to disable external temperature measurement.                                                                                                                                                                                                                                           |

| VDD         | 29  | I                 | Input Voltage for analog control circuitry. Bypass with a 0.1-µF to 1.0-µF capacitor to GND (thermal pad or GND pins) or through a dedicated connection to AGNDSNS. The VDD voltage is also used for input feed-forward, ON-time generation and High Side Over Current (HSOC). VIN and VDD must be at the same voltage for accurate short circuit protection. |

|             | 21  |                   |                                                                                                                                                                                                                                                                                                                                                               |

|             | 22  |                   |                                                                                                                                                                                                                                                                                                                                                               |

| VIN         | 23  | - 1               | Input power to the power stage. Bypass High-Frequency bypassing with multiple ceramic capacitors to GND is critical. See Layout Recommendations                                                                                                                                                                                                               |

|             | 24  |                   | OND IS ORIGIN. OCC Layout Necommendations                                                                                                                                                                                                                                                                                                                     |

|             | 25  |                   |                                                                                                                                                                                                                                                                                                                                                               |

| VOUTS+      | 31  | I                 | Output voltage sensing, positive side. This sensing provides remote sensing for PMBus reporting and the voltage control loop. Connect to $V_{OUT}$ at desried regulation point through < $100-\Omega$ resistor. Route with GND to VOUT- using coupled differential pair PCB routing.                                                                          |

| VOUTS-      | 32  | I                 | Output voltage sensing, negative or common side. This sensing provides remote sensing for PMBus reporting and the voltage control loop. Connect to Ground at desried regulation point through < $100-\Omega$ resistor. Route with $V_{OUT}$ to VOUT+ using coupled differential pair PCB routing.                                                             |

| Thermal tab |     |                   | Package thermal tab. Connect to GND. The thermal tab must have adequate solder coverage for proper operation.                                                                                                                                                                                                                                                 |

## 7 Specifications

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) See (1)(2)(3)

|                                             |                                       | MIN  | MAX | UNIT |

|---------------------------------------------|---------------------------------------|------|-----|------|

|                                             | VIN, VDD                              | -0.3 | 20  |      |

|                                             | воот                                  | -0.3 | 37  |      |

| Input voltage                               | BOOT – SW (BOOT to SW differential)   | -0.3 | 7   | V    |

|                                             | CLK, DATA                             | -0.3 | 3.6 |      |

|                                             | FB, SYNC, CNTL, VOUTS-, VOUTS+, BPEXT | -0.3 | 7   |      |

|                                             | BP6                                   | -0.3 | 7   |      |

|                                             | SW                                    | -1   | 30  |      |

| Output voltage                              | SW ( > 50 ns, > 10 μJ)                | -5   | 30  | V    |

|                                             | COMP, DIFFO, SMBALERT, PGOOD          | -0.3 | 7   |      |

|                                             | ADDR0, ADDR1, BP3, RT, TSNS           | -0.3 | 3.6 |      |

| T <sub>J</sub> , operating junction tempera | ture                                  | -40  | 150 | °C   |

| T <sub>stg</sub> , Storage temperature      |                                       | -55  | 150 | °C   |

<sup>(1)</sup> Absolute Maximum Ratings indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Operating Ratings is not implied. The recommended Operating Ratings indicate conditions at which the device is functional and the device should not be operated beyond such conditions.

#### 7.2 ESD Ratings

|                    |                                            |                                                                               | VALUE | UNIT |

|--------------------|--------------------------------------------|-------------------------------------------------------------------------------|-------|------|

| V                  | V <sub>(ESD)</sub> Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>   | ±2000 | V    |

| V <sub>(ESD)</sub> |                                            | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|          |                           | MIN | TYP MA | X UNIT |

|----------|---------------------------|-----|--------|--------|

| $V_{DD}$ | Controller input voltage  | 4.5 | •      | 8 V    |

| $V_{IN}$ | Power stage input voltage | 4.5 | •      | 8 V    |

| $T_{J}$  | Junction temperature      | -40 | 12     | 5 °C   |

<sup>(2)</sup> The human body model is a 100-pF capacitor discharged through a 1.5-k $\Omega$  resistor into each pin.

<sup>(3)</sup> If Military or Aerospace specified devices are required, contact the Texas Instruments Sales/Office/Distributors for availability and specifications.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 7.4 Thermal Information

|                    | THERMAL METRIC <sup>(1)</sup>                               | TPS544B20<br>TPS544C20 | UNIT |

|--------------------|-------------------------------------------------------------|------------------------|------|

| $R_{\theta JA}$    | Junction-to-ambient thermal resistance (2)                  | 27.5                   | °C/W |

| $R_{\theta JCtop}$ | Junction-to-case (top) thermal resistance (3)               | 13.9                   | °C/W |

| $R_{\theta JB}$    | Junction-to-board thermal resistance                        | 4.0                    | °C/W |

| ΨЈТ                | Junction-to-top characterization parameter <sup>(4)</sup>   | 0.3                    | °C/W |

| ΨЈВ                | Junction-to-board characterization parameter <sup>(5)</sup> | 3.9                    | °C/W |

| $R_{\theta JCbot}$ | Junction-to-case (bottom) thermal resistance (6)            | 0.9                    | °C/W |

- (1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

- (2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- (3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- (4) The junction-to-top characterization parameter, ψ<sub>JT</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining R<sub>θJA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

- (5) The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining R<sub>0JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

- (6) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

#### 7.5 Electrical Characteristics

$T_J = -40$ °C to 125°C,  $V_{IN} = V_{VDD} = 12$  V,  $R_{RT} = 38.3$  k $\Omega$ ; zero power dissipation (unless otherwise noted)

|                            | PARAMETER                               | TEST CONDITIONS                                                             | MIN      | TYP  | MAX   | UNIT |

|----------------------------|-----------------------------------------|-----------------------------------------------------------------------------|----------|------|-------|------|

| INPUT SUPPL                | Υ                                       |                                                                             |          |      | '     |      |

| $V_{VDD}$                  | Input supply voltage range              |                                                                             | 4.5      |      | 18    | V    |

| V <sub>VIN</sub>           | Power stage voltage range               |                                                                             | 4.5      |      | 18    | V    |

| I <sub>VDD</sub>           | Input Operating Current                 | Not switching                                                               |          |      | 10    | mA   |

| UVLO                       |                                         |                                                                             | <u> </u> |      |       |      |

| V <sub>IN(on)</sub>        | Input turn on voltage                   | Default settings                                                            | 4.05     | 4.25 | 4.45  | V    |

| V <sub>IN(off)</sub>       | Input turn off voltage                  | Default settings                                                            | 3.8      | 4    | 4.2   | V    |

| V <sub>INON(rng)</sub>     | Programmable range for turn-on voltage  |                                                                             | 4.25     |      | 16    | ٧    |

| V <sub>INOFF(rng)</sub>    | Programmable range for turn-off voltage |                                                                             | 4        |      | 15.75 | ٧    |

| ERROR AMPL                 | IFIER AND FEEDBACK VOLTAGE              |                                                                             | <u> </u> |      |       |      |

| W                          | Foodbook Volto :                        | 0°C ≤ T <sub>J</sub> ≤ 70°C                                                 | 597      | 600  | 603   | mc\/ |

| $V_{FB}$                   | Feedback Voltage                        | -40°C ≤ T <sub>J</sub> ≤ 125°C                                              | 594      | 600  | 606   | mV   |

| g <sub>м</sub>             | Transconductance                        |                                                                             |          | 130  |       | μS   |

| I <sub>FB</sub>            | FB pin bias current (out of pin)        | V <sub>FB</sub> = 0.6 V                                                     |          |      | 50    | nA   |

| $V_{LOOP\_COMP}$           | Loop comparator offset voltage          | V <sub>FB</sub> = 0.6 V, T <sub>J</sub> = 25°C                              | -7.5     |      | 7.5   | mV   |

| BP6 REGULA                 | TOR                                     |                                                                             |          |      |       |      |

| V <sub>BP6</sub>           | Output voltage                          | I <sub>BP6</sub> = 10 mA                                                    | 6.2      | 6.5  | 6.8   | V    |

| V <sub>BP6(do)</sub>       | Dropout voltage                         | $V_{VIN} - V_{BP6}$ , $V_{VDD} = 4.5 \text{ V}$ , $I_{BP6} = 25 \text{ mA}$ |          |      | 100   | mV   |

| I <sub>BP6</sub>           | Output current <sup>(1)</sup>           | V <sub>VDD</sub> = 12 V                                                     | 120      |      |       | mA   |

| V <sub>BP6UV</sub>         | Regulator UVLO voltage <sup>(1)</sup>   |                                                                             | 3.3      | 3.55 | 3.8   | V    |

| V <sub>BP6UV(hyst)</sub>   | Regulator UVLO voltage hysteresis (1)   |                                                                             | 230      | 255  | 270   | mV   |

| BPEXT                      |                                         |                                                                             |          |      |       |      |

| V <sub>BPEXT(swover)</sub> | BPEXT switch-over voltage               | VDD > V <sub>IN(on)</sub>                                                   | 4.5      | 4.65 |       | V    |

| V <sub>hys(swover)</sub>   | BPEXT switch-over hysteresis            |                                                                             | 100      |      | 200   | mV   |

| $V_{BPEXT(do)}$            | BPEXT dropout voltage                   | $V_{BPEXT}$ - $V_{BP6}$ , $V_{BPEXT}$ = 4.8 V, $I_{BP6}$ = 25 mA            |          |      | 100   | mV   |

| BOOTSTRAP                  |                                         |                                                                             |          |      |       |      |

| $V_{BOOT(drop)}$           | Bootstrap voltage drop                  | $I_{BOOT} = 5 \text{ mA}$                                                   |          |      | 150   | mV   |

| BP3 REGULA                 | TOR                                     |                                                                             |          |      |       |      |

| $V_{BP3}$                  | Output voltage                          | $V_{VDD} = 4.5 \text{ V}, I_{BP3} \le 5 \text{ mA}$                         | 3.1      | 3.3  | 3.5   | V    |

| SOFT START                 |                                         |                                                                             |          |      |       |      |

| t <sub>SS</sub>            | Soft-start time <sup>(2)</sup>          | Factory default settings                                                    |          | 2.7  |       | ms   |

|                            | Programmable range <sup>(1)</sup>       |                                                                             | 0.6      |      | 9     | ms   |

|                            | Accuracy over range <sup>(1)</sup>      |                                                                             |          | ±10% |       |      |

| t <sub>ON(DELAY)</sub>     | Turn-on delay                           | Factory default settings                                                    |          | 0    |       | ms   |

| t <sub>OFF(DELAY)</sub>    | Turn-off delay                          | Factory default settings                                                    |          | 0    |       | ms   |

<sup>(1)</sup> Specified by design. Not production tested.

(2) Soft-start time is defined by the rise time of the internal reference, V<sub>REF</sub>

## **Electrical Characteristics (continued)**

$T_J = -40$ °C to 125°C,  $V_{IN} = V_{VDD} = 12$  V,  $R_{RT} = 38.3$  k $\Omega$ ; zero power dissipation (unless otherwise noted)

|                           | PARAMETER                                                         | TEST CONDITIONS                                           |             | MIN                   | TYP                 | MAX  | UNIT |

|---------------------------|-------------------------------------------------------------------|-----------------------------------------------------------|-------------|-----------------------|---------------------|------|------|

| REMOTE SEN                | SE AMPLIFIER                                                      |                                                           |             |                       |                     |      |      |

|                           |                                                                   | $(V_{OUTS+} - V_{OUTS-}) = 0.6 \text{ V}$                 |             | -5                    |                     | 5    |      |

| V <sub>DIFFO(ERROR)</sub> | Error voltage from DIFFO to V <sub>SNS</sub>                      | $(V_{OUTS+} - V_{OUTS-}) = 1.2 \text{ V}$                 |             | -8                    |                     | 8    | mV   |

| ,                         |                                                                   | (V <sub>OUTS+</sub> – V <sub>OUTS</sub> ) = 3.0 V         |             | -17                   |                     | 17   |      |

| BW                        | Closed-loop bandwidth <sup>(1)</sup>                              |                                                           | 2           |                       |                     | MHz  |      |

| R <sub>VOUTx</sub>        | Output voltage sense input impedance                              | V <sub>OUT+</sub> = 1.2V                                  | 55          | 80                    | 105                 | kΩ   |      |

| V <sub>DIFFO(max)</sub>   | Maximum DIFFO output voltage                                      |                                                           |             | V <sub>BP6</sub> -0.2 |                     |      | V    |

|                           | DIFFO sourcing current                                            |                                                           |             | 1                     |                     |      |      |

| I <sub>DIFFO</sub>        | DIFFO sinking current                                             |                                                           |             | 1                     |                     |      | mA   |

| POWER STAG                |                                                                   |                                                           |             |                       |                     |      |      |

|                           |                                                                   | V <sub>VDD</sub> = 4.5 V, T <sub>J</sub> = 25°C           |             |                       | 4.9                 |      |      |

| R <sub>HS</sub>           | High-side on-resistance                                           | $V_{VDD} \ge 12 \text{ V}, T_J = 25^{\circ}\text{C}$      |             |                       | 4.5                 |      | mΩ   |

|                           |                                                                   | V <sub>VDD</sub> = 18 V, T <sub>J</sub> = 25°C            |             |                       | 0.4                 | 0.7  |      |

| I <sub>HS(leak)</sub>     | High-side leakage current                                         | $V_{VDD} = 18 \text{ V}, T_J = 125^{\circ}\text{C}^{(1)}$ |             |                       | 1.5                 |      | μA   |

|                           |                                                                   | V <sub>VDD</sub> = 4.5 V, T <sub>J</sub> = 25°C           |             |                       | 2.2                 |      |      |

| R <sub>LS</sub>           | Low-side on-resistance                                            | $V_{VDD} \ge 12 \text{ V}, T_{II} = 25^{\circ}\text{C}$   |             |                       | 2.0                 |      | mΩ   |

| CURRENT LIM               | IIT                                                               | VOD 7 3                                                   |             |                       |                     |      |      |

| t <sub>OFF(OC)</sub>      | Off time between restart attempts                                 | Hiccup mode                                               |             |                       | 7 × t <sub>SS</sub> |      | ms   |

| 011(00)                   | р                                                                 | Factory default settings                                  |             |                       | 26                  |      |      |

|                           | Output current overcurrent fault                                  | Programmable range                                        | TPS544B20 5 | 5                     |                     | 30   |      |

| I <sub>OC(flt)</sub>      | threshold                                                         | Factory default settings                                  |             |                       | 39                  |      | Α    |

|                           |                                                                   | Programmable range                                        | TPS544C20   | 5                     |                     | 45   |      |

|                           |                                                                   | Factory default settings                                  |             |                       | 20                  |      |      |

|                           | Output current overcurrent warning                                | Programmable range                                        | TPS544B20   | 4                     |                     | 29.5 |      |

| I <sub>OC(warn)</sub>     | threshold                                                         | Factory default settings                                  |             |                       | 30                  |      | Α    |

|                           |                                                                   | Programmable range                                        | TPS544C20   | 4                     |                     | 44.5 |      |

| I <sub>OC(acc)</sub>      | Output current overcurrent fault and warning accuracy             | I <sub>OCF</sub> = 20 A <sup>(1)</sup>                    |             |                       | ±3                  |      | А    |

| t <sub>LSOC(min)</sub>    | Minimum LDRV pulse width for valid current sensing <sup>(1)</sup> |                                                           |             |                       | 400                 | 500  | ns   |

| HIGH-SIDE SH              | ORT CIRCUIT PROTECTION                                            |                                                           |             |                       |                     | ı    |      |

|                           | High-side short-circuit protection                                |                                                           | TPS544B20   | 30                    |                     | 58   |      |

| I <sub>HSOC</sub>         | fault threshold                                                   | $T_J = 25^{\circ}C$                                       | TPS544C20   | 45                    |                     | 75   | Α    |

| POWER GOOD                | O (PGOOD)                                                         |                                                           | 1           |                       |                     |      |      |

| $V_{FBPGH}$               | FB PGOOD high threshold                                           | Factory default settings                                  |             |                       | 675                 |      | mV   |

| V <sub>FBPGL</sub>        | FB PGOOD low threshold                                            | Factory default settings                                  |             |                       | 525                 |      | mV   |

| V <sub>PG(acc)</sub>      | PGOOD accuracy over range                                         | Factory default settings                                  |             | -5%                   |                     | 5%   |      |

| V <sub>pg(hyst)</sub>     | FB PGOOD hysteresis voltage                                       |                                                           |             | 10                    |                     | 50   | mV   |

| R <sub>PGOOD</sub>        | PGOOD pull-down resistance                                        | V <sub>FB</sub> = 0, I <sub>PGOOD</sub> = 5 mA            |             |                       | 30                  | 70   | Ω    |

| I <sub>PGOOD(Ik)</sub>    | PGOOD pin leakage current                                         | Factory default settings, V <sub>PGOOD</sub> = 5 V        |             |                       |                     | 20   | μA   |

|                           | RVOLTAGE AND UNDERVOLTAGE F                                       |                                                           |             |                       |                     |      |      |

| V <sub>FBOV</sub>         | FB pin over voltage threshold                                     | Factory default settings                                  |             |                       | 700                 |      | mV   |

| V <sub>FBUV</sub>         | FB pin under voltage threshold                                    | Factory default settings                                  |             |                       | 499                 |      | mV   |

| V <sub>UVOV(acc)</sub>    | FB UV, OV accuracy over range                                     | Factory default settings                                  |             | -4.5%                 |                     | 4.5% |      |

## **Electrical Characteristics (continued)**

$T_J = -40$ °C to 125°C,  $V_{IN} = V_{VDD} = 12$  V,  $R_{RT} = 38.3$  k $\Omega$ ; zero power dissipation (unless otherwise noted)

|                          | PARAMETER                                                         | TEST CONDITIONS                                            | MIN   | TYP   | MAX   | UNIT  |

|--------------------------|-------------------------------------------------------------------|------------------------------------------------------------|-------|-------|-------|-------|

| OUTPUT VOL               | TAGE TRIMMING AND MARGINING                                       |                                                            |       |       |       |       |

| V <sub>FBTM(step)</sub>  | Resolution of FB steps with trim and margin                       |                                                            |       | 2     |       | mV    |

| t <sub>FBTM(step)</sub>  | Transition time per trim or margin step                           | After soft-start time                                      |       | 30    |       | μs    |

| $V_{FBTM(max)}$          | Maximum FB voltage with trim or margin only                       |                                                            |       | 660   |       | mV    |

| V <sub>FBTM(min)</sub>   | Minimum FB voltage with trim or margin only                       |                                                            |       | 480   |       | mV    |

| V <sub>FBTM(rng)</sub>   | FB voltage range with trim and margin combined                    |                                                            | 420   |       | 660   | mV    |

| $V_{FBMH}$               | Margin high FB pin voltage                                        | Factory default settings                                   |       | 660   |       | mV    |

| $V_{FBML}$               | Margin low FB pin voltage                                         | Factory default settings                                   |       | 540   |       | mV    |

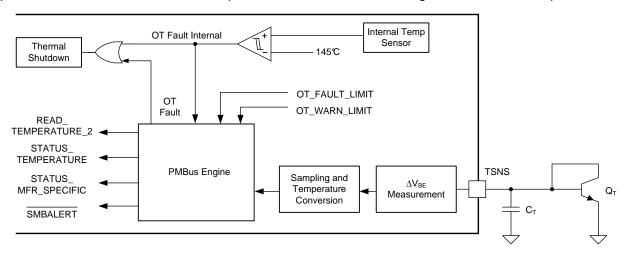

| TEMPERATU                | RE SENSE AND THERMAL SHUTDOV                                      | vn                                                         |       |       |       |       |

| T <sub>SD</sub>          | Junction shutdown temperature (1)                                 |                                                            | 135   | 145   | 155   | °C    |

| T <sub>HYST</sub>        | Thermal shutdown hysteresis (1)                                   |                                                            | 20    | 25    | 30    | °C    |

| I <sub>TSNS(ratio)</sub> | Ratio of bias current flowing out of TSNS pin, state 2 to state 1 |                                                            | 9.7   | 10.0  | 10.3  | μΑ/μΑ |

| I <sub>TSNS</sub>        | State 1 current out of TSNS pin                                   |                                                            |       | 10    |       | μΑ    |

| I <sub>TSNS</sub>        | State 2 current out of TSNS pin                                   |                                                            |       | 100   |       | μΑ    |

| V <sub>TSNS</sub>        | Voltage range on TSNS pin <sup>(1)</sup>                          |                                                            | 0     |       | 1.00  | V     |

| -                        | Overtemperature fault limit <sup>(1)</sup>                        | Factory default settings                                   |       | 150   |       | 20    |

| $T_{OT(flt)}$            | OT fault limit range <sup>(1)</sup>                               |                                                            | 120   |       | 165   | °C    |

| _                        | Overtemperature warning limit <sup>(1)</sup>                      | Factory default settings                                   |       | 125   |       |       |

| T <sub>OT(warn)</sub>    | OT warning limit range <sup>(1)</sup>                             |                                                            | 100   |       | 140   | °C    |

| T <sub>OT(step)</sub>    | OT fault, warning step <sup>(1)</sup>                             |                                                            |       | 5     |       | °C    |

| T <sub>OT(hys)</sub>     | OT fault, warning hysteresis <sup>(1)</sup>                       |                                                            | 15    | 20    | 25    | °C    |

| MEASUREME                | ENT SYSTEM                                                        |                                                            | -     |       |       |       |

| M <sub>VOUT(rng)</sub>   | Output voltage measurement range                                  |                                                            | 0.5   |       | 5.8   | ٧     |

| M <sub>VOUT(acc)</sub>   | Output voltage measurement accuracy                               |                                                            | -2.0% |       | 2.0%  |       |

| M <sub>VOUT(Isb)</sub>   | Output voltage measurement bit resolution                         |                                                            |       | 1.95  |       | mV    |

|                          | Output current measurement                                        | I <sub>OUT</sub> ≥ 20 A, -40 ≤ T <sub>A</sub> ≤ 85°C       | -15%  |       | +15%  |       |

| M <sub>IOUT(acc)</sub>   | accuracy <sup>(3)</sup>                                           | 3 A ≤ I <sub>OUT</sub> < 20 A, -40 ≤ T <sub>A</sub> ≤ 85°C | -3    |       | +3    | Α     |

| M <sub>IOUT(Isb)</sub>   | Output current measurement bit resolution <sup>(1)</sup>          |                                                            |       | 62.5  |       | mA    |

| M <sub>TSNS(rng)</sub>   | External temperature sense range <sup>(1)</sup>                   |                                                            | -40   |       | 165   | °C    |

| M <sub>TSNS(acc)</sub>   | External temperature sense accuracy <sup>(1)</sup>                | -40°C ≤ T <sub>J(sensor)</sub> ≤ 165°C                     | -8    |       | 8     | °C    |

| M <sub>TSNS(Isb)</sub>   | External temperature sense bit resolution <sup>(1)</sup>          |                                                            |       | 1.238 |       | °C    |

| PMBus INTE               | RFACE ADDRESSING                                                  | ,                                                          |       |       |       |       |

| I <sub>ADD</sub>         | Address pin bias current                                          |                                                            | 8.23  | 9.75  | 11.21 | μA    |

| V <sub>ADD(rng)</sub>    | Address pin legal address voltage range                           |                                                            | 0.08  |       | 2.35  | V     |

|                          |                                                                   | 1                                                          | - 1   |       |       |       |

<sup>(3)</sup> Current sense amplifier gain and offset are production tested. Output current monitoring guaranteed by correlation.

## 7.6 Switching Characteristics

$V_{IN}$  =  $V_{DD}$  = 12 V,  $T_A$  = 25 °C,  $R_{RT}$  = 38.3 k $\Omega$  (unless otherwise specified).

|                       | PARAMETER                            | TEST CONDITIONS                                                    | MIN | TYP  | MAX  | UNIT |

|-----------------------|--------------------------------------|--------------------------------------------------------------------|-----|------|------|------|

| TON GEN               | ERATOR AND SW TIMING                 |                                                                    |     |      |      |      |

|                       |                                      | Adjustment range                                                   | 250 |      | 1000 |      |

|                       |                                      | $R_{RT} = 10.0 \text{ k}\Omega$                                    | 210 | 250  | 290  |      |

|                       |                                      | $R_{RT} = 17.8 \text{ k}\Omega$                                    | 250 | 300  | 350  |      |

|                       |                                      | $R_{RT} = 27.4 \text{ k}\Omega$                                    | 340 | 400  | 460  |      |

| $f_{SW}$              | Switching frequency <sup>(1)</sup>   | R <sub>RT</sub> = 38.3 kΩ                                          | 425 | 500  | 575  | kHz  |

|                       |                                      | $R_{RT} = 56.2 \text{ k}\Omega$                                    | 550 | 650  | 750  |      |

|                       |                                      | $R_{RT} = 86.6 \text{ k}\Omega$                                    | 640 | 750  | 860  |      |

|                       |                                      | R <sub>RT</sub> = 133 kΩ                                           | 720 | 850  | 980  |      |

|                       |                                      | R <sub>RT</sub> = 205 kΩ                                           | 850 | 1000 | 1150 |      |

| I <sub>RT</sub>       | RT output current                    |                                                                    |     | 9.75 |      | μΑ   |

| t <sub>OFF(min)</sub> | Minimum off-time (2) (3)             |                                                                    |     | 175  |      | ns   |

| t <sub>ON(min)</sub>  | Minimum controllable pulse width (2) |                                                                    |     |      | 80   | ns   |

| V <sub>DCAP2</sub>    | D-CAP2 mode threshold                |                                                                    |     |      | 2.10 | V    |

| V <sub>DCAP</sub>     | D-CAP mode threshold                 |                                                                    | 0.8 |      |      | V    |

| I <sub>MODE</sub>     | MODE output current                  |                                                                    | 7   |      | 13   | μΑ   |

|                       | Dower stage driver dead time (2)     | SW rising                                                          |     | 15   |      |      |

| t <sub>DEAD</sub>     | Power stage driver dead-time (2)     | SW falling                                                         |     | 15   |      | ns   |

|                       | SW claw rata (2)                     | SW rising (10% to 90%), $I_{OUT} = 30$ A, $R_{BOOT} = 0$ $\Omega$  |     | 9.2  |      | V/ns |

| t <sub>SLEW(SW)</sub> | SW slew rate <sup>(2)</sup>          | SW falling (90% to 10%), $I_{OUT}$ = 30 A, $R_{BOOT}$ = 0 $\Omega$ |     | 6.2  |      | v/ns |

On-times are production tested, but steady-state switching frequency is not. Specified by design. Not production tested.

<sup>(2)</sup> Specified by design. Not production tested.(3) Minimum off time for valid current sensing is 400-ns typical, 500-ns maximum.

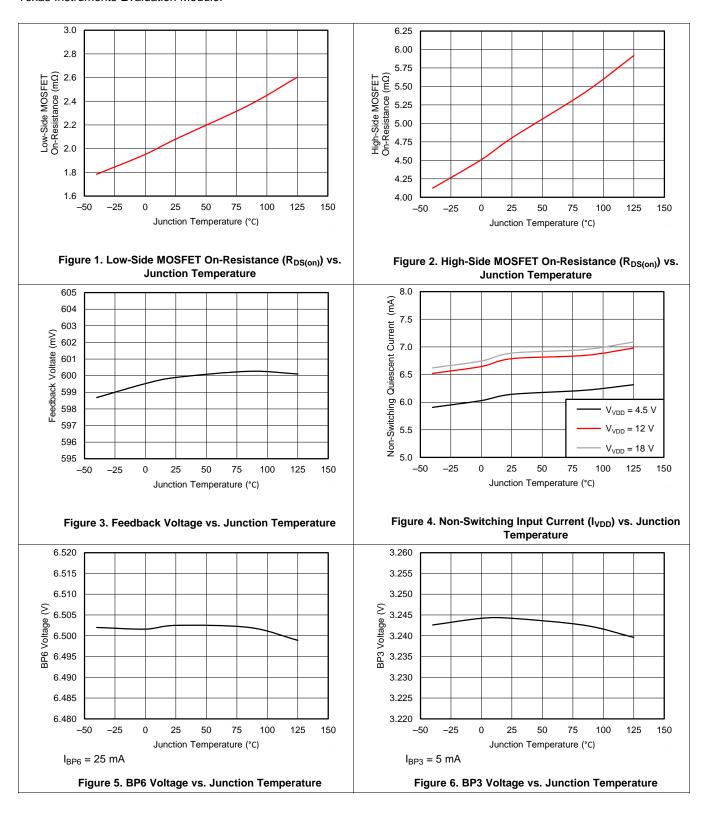

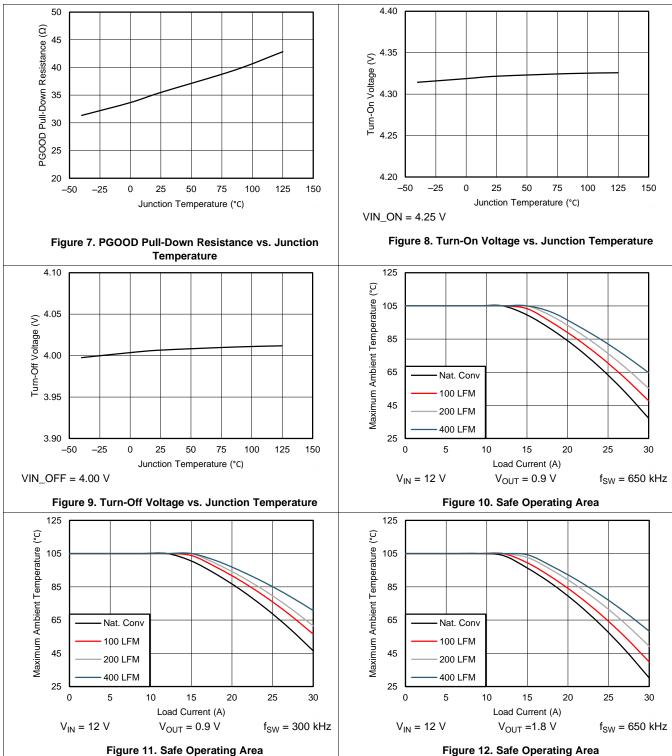

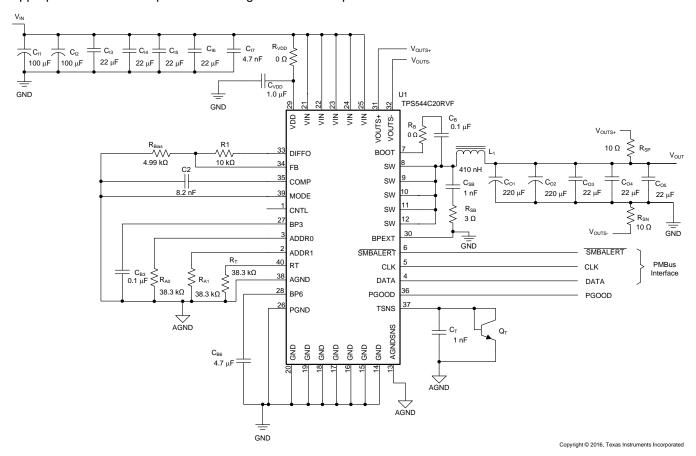

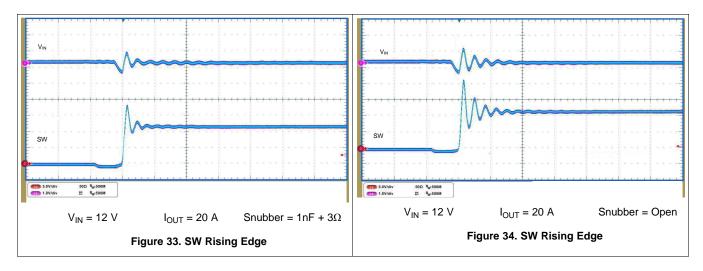

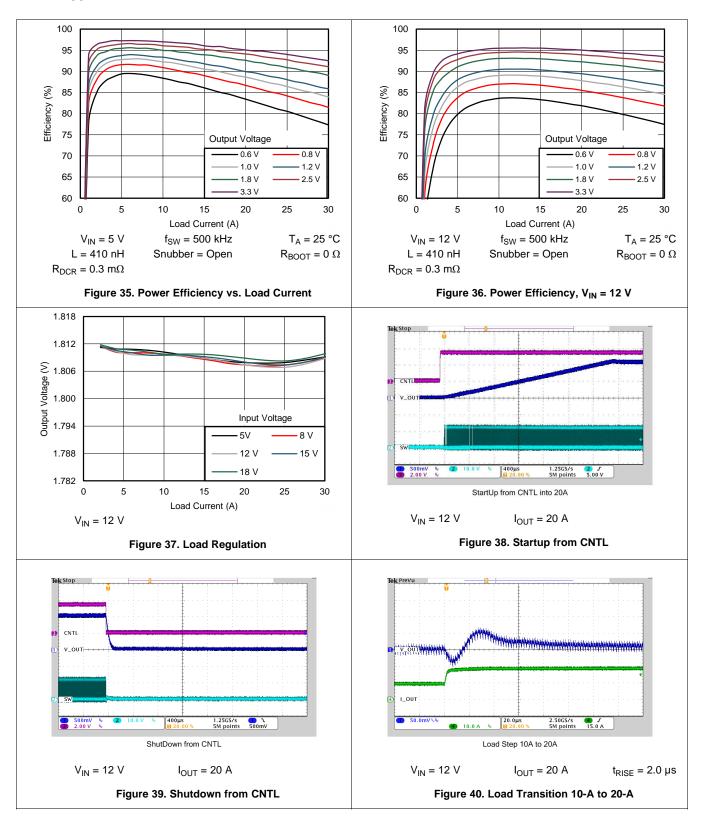

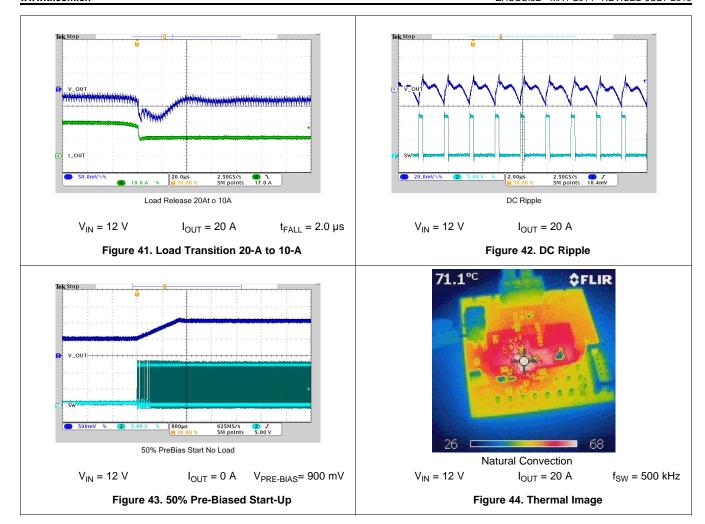

#### 7.7 Typical Characteristics

$V_{IN} = V_{DD} = 12 \text{ V}$ ,  $T_A = 25 \, ^{\circ}\text{C}$ ,  $R_{RT} = 38.3 \, k\Omega$  (unless otherwise specified). Safe operating area curves were measured using a Texas Instruments Evaluation Module.

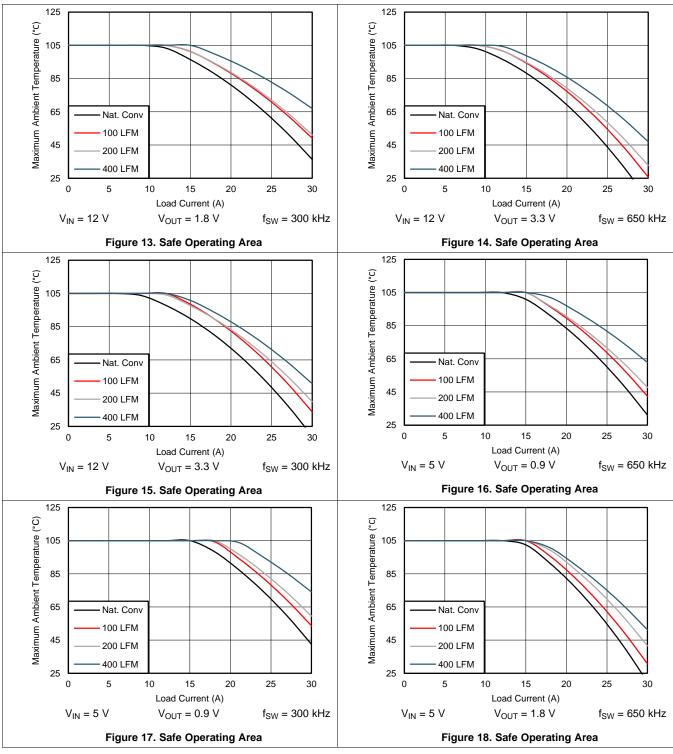

## **Typical Characteristics (continued)**

$V_{IN} = V_{DD} = 12 \text{ V}$ ,  $T_A = 25 \, ^{\circ}\text{C}$ ,  $R_{RT} = 38.3 \, \text{k}\Omega$  (unless otherwise specified). Safe operating area curves were measured using a Texas Instruments Evaluation Module.

## TEXAS INSTRUMENTS

## **Typical Characteristics (continued)**

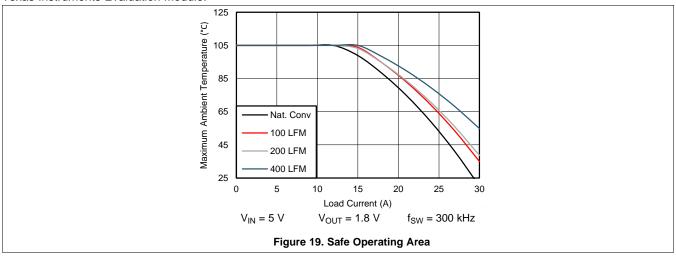

$V_{IN} = V_{DD} = 12 \text{ V}$ ,  $T_A = 25 \, ^{o}\text{C}$ ,  $R_{RT} = 38.3 \, k\Omega$  (unless otherwise specified). Safe operating area curves were measured using a Texas Instruments Evaluation Module.

## **Typical Characteristics (continued)**

$V_{IN} = V_{DD} = 12 \text{ V}$ ,  $T_A = 25 \, ^{\circ}\text{C}$ ,  $R_{RT} = 38.3 \, \text{k}\Omega$  (unless otherwise specified). Safe operating area curves were measured using a Texas Instruments Evaluation Module.

## 8 Detailed Description

#### 8.1 Overview

The TPS544B20 and TPS544C20 devices are 20-A, and 30-A, high-performance, synchronous buck converters with two integrated N-channel NexFET™ power MOSFETs. These devices implement Tl's proprietary D-CAP and D-CAP2 mode control providing natural input voltage feed-forward and fast transient response with a precision error amplifier and low-offset differential remote sense amplifier for precise output voltage regulation with minimal external compensation. Monotonic pre-bias capability eliminates concerns about damaging sensitive loads. Integrated PMBus capability provides current, voltage and on-board temperature monitoring, as well as many user-programmable configuration options as well as Adaptive Voltage Scaling (AVS) and output voltage margin testing.

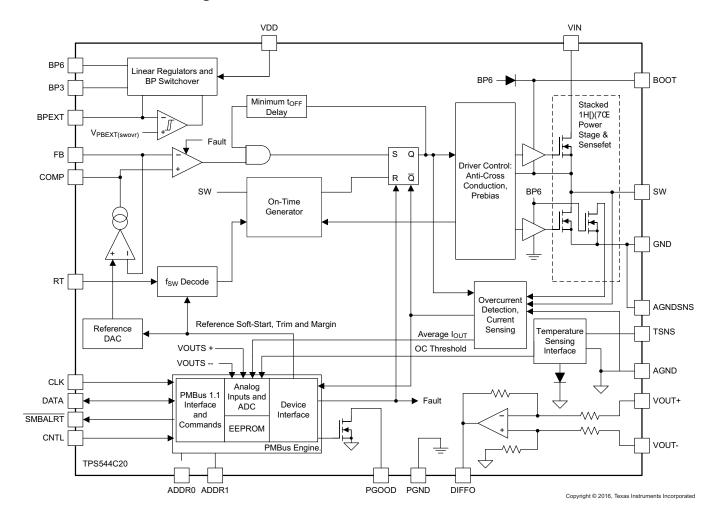

#### 8.2 Functional Block Diagram

#### 8.3 Feature Description

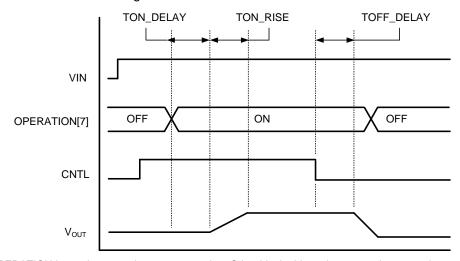

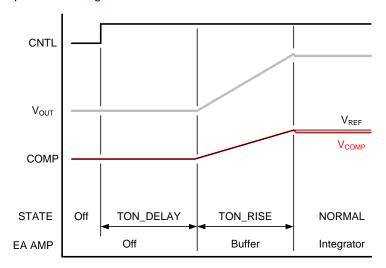

#### 8.3.1 Turn-On and Turn-Off Delay and Sequencing

The TPS544C20 and TPS544B20 devices provide many sequencing options. Using the ON\_OFF\_CONFIG command, the device can be configured to start up when the input voltage is above the undervoltage lockout (UVLO) threshold, or to additionally require a signal on the CNTL pin and/or receive an update to the OPERATION command according to the PMBus protocol. When the gating signal as specified by ON\_OFF\_CONFIG command is asserted, a programmable turn-on delay can be set with the TON\_DELAY command to delay the start of regulation. Similarly, a programmable turn-off delay can be set with the TOFF\_DELAY command to delay the stop of regulation once the gating signal is de-asserted. Delay times are specified as an integer multiple of the soft-start time.

When the output voltage remains within the PGOOD window after the start-up period, PGOOD is released, and rises to an externally supplied logic level. The PGOOD signal can be connected to the CNTL pin of another device to provide additional controlled turn-on and turn-off sequencing.

Figure 20 shows control of the start-up and shutdown operations of the device, when the device is configured to respond to a logical AND of both CNTL and the OPERATION command. The device can also be configured to respond to only the CNTL signal, only the OPERATION command, or to convert power whenever VDD is greater than the VIN ON command value setting.

(1) Bit 7 of OPERATION is used to control power conversion. Other bits in this register control output voltage margining.

Figure 20. Turn-On Controlled By Both Operation and Control

#### 8.3.2 Pre-Biased Output Start-Up

The TPS544C20 and TPS544B20 devices prevent current from discharging from the output during start-up, when a pre-biased output condition exists. No SW pulses occur until the internal soft-start voltage rises above the error amplifier input voltage (FB pin), if the output is pre-biased. When the soft-start voltage exceeds the error amplifier input, and SW pulses start, the device limits synchronous rectification time after each SW pulse with a narrow on-time. The low-side MOSFET on-time slowly increases each switching cycle until it generates 128 pulses. After 128 pulses, the synchronous rectifier runs fully complementary to the high-side MOSFET. This approach prevents the sinking of current from a pre-biased output, and ensures the output voltage start-up and ramp-to-regulation sequences are smooth and monotonic. These devices respond to a pre-biased output over-voltage condition immediately upon power-up, even during soft-start, while disabled or below the PMBus programmable undervoltage lockout on-time (UVLO $_{\rm ON}$ ).

The combination of D-CAP and D-CAP2 mode control and the limited on-time of the low-side MOSFET during the pre-bias sequence allows these devices to operate at low switching frequencies for the first 128 switching cycles, after which the device operates using pseudo-constant frequency.

#### **Feature Description (continued)**

#### 8.3.3 Voltage Reference

A 600-mV bandgap cell connects internally to the non-inverting input of the error amplifier. The 0.5% tolerance on the reference voltage allows for a power supply design that yields very high DC accuracy.

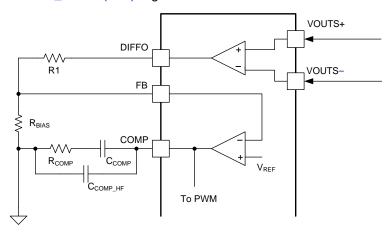

#### 8.3.4 Differential Remote Sense and Output Voltage Setting

The TPS544C20 and TPS544B20 devices implement a differential remote sense amplifier to provide excellent load regulation by cancelling IR-drop in high current applications. The VOUTS+ and VOUTS- pins should be kelvin-connected to the output capacitor bank directly at the load, and routed back to the device as a tightly coupled differential pair. Ensure that these traces are isolated from fast switching signals and high current paths on the final PCB layout to mitigate differential-mode noise. Optionally, use a small coupling capacitor (330-pF typical) between the VOUTS+ and VOUTS- pins to improve noise immunity. The output of the differential remote sense amplifier (DIFFO) sets the output voltage.

A voltage divider from the DIFFO pin to the FB pin sets the nominal output voltage. The output voltage must be divided down to the nominal reference voltage of 600 mV. The feedback voltage can be adjusted within –30% and +10% from the nominal 600 mV using PMBus commands, allowing the output voltage to vary by the same percentage. During the power-up sequence, the feedback reference is 600 mV plus any offset generated by the MARGIN command or VREF\_TRIM command values which were previously stored in EEPROM. The initial output voltage equals the feedback voltage scaled by the divider ratio. See the *PMBus Output Voltage Adjustment* section for further details.

The device enables telemetry by digitizing the voltage at the DIFFO pin, averaging it to reduce measurement noise, and storing it in the READ\_VOUT (8Bh) register.

Figure 21. Output Voltage Setting

Equation 1 calculates the nominal output voltage. R1 can be arbitrarily selected to be 10-k $\Omega$ , with R<sub>BIAS</sub> being scaled appropriately.

$$V_{OUT} = \left(1 + \frac{R1}{R_{Bias}}\right) \times V_{FB} \tag{1}$$

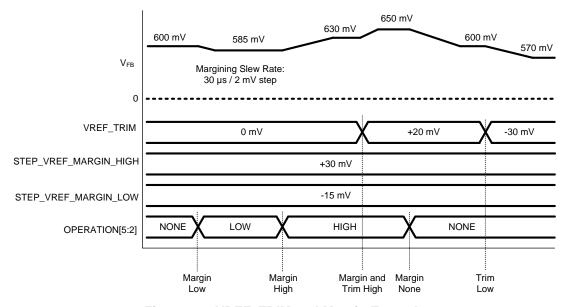

#### 8.3.5 PMBus Output Voltage Adjustment

The nominal output voltage of the converter can be adjusted by changing the feedback voltage,  $V_{FB}$ , using the VREF\_TRIM command. The adjustment range is between -20% and +10% from the nominal output voltage. This command adjusts the final output voltage of the converter to a high degree of accuracy, without relying on high-precision feedback resistors. The resolution of the adjustment is 7 bits, with a resulting minimum step size of approximately 2 mV, or 0.4%. The total output voltage adjustable range, including MARGIN and VREF\_TRIM is -30% to +10%.

#### **Feature Description (continued)**

The TPS544C20 and TPS544B20 devices allow simple output voltage margin testing, by applying a either a positive or negative offset to the feedback voltage. The STEP\_VREF\_MARGIN\_HIGH and STEP\_VREF\_MARGIN\_LOW commands control the size of the applied high or low offset respectively. The OPERATION command toggles the converter between three states:

- Margin none (no output margining). See Equation 2

- Margin high. See Equation 3

- Margin low. See Equation 4

$$V_{FB} = VREF\_TRIM + 0.6 V \tag{2}$$

$$V_{FB} = VREF\_TRIM + STEP\_VREF\_MARGIN\_HIGH + 0.6 V$$

(3)

$$V_{FB} = VREF\_TRIM + STEP\_VREF\_MARGIN\_LOW + 0.6 V$$

(4)

Figure 22 shows an example of the VREF\_TRIM and margin timing.

Figure 22. VREF\_TRIM and Margin Example

The nominal 600-mV FB pin references the OV fault, UV fault, and PGOOD limits, as defined by PCT\_VOUT\_FAULT\_PG\_LIMIT command, regardless of VREF\_TRIM or output margining. These limits remain fixed percentages of the nominal 600 mV reference, regardless of output margining.

#### 8.3.6 Switching Frequency

A resistor from the RT pin to AGND establishes the switching frequency during the power-up sequence. To ensure proper detection, select a resistor with 1% tolerance from Table 2.

Table 2. Required RT Resistors

| NOMINAL<br>FREQUENCY<br>(kHz) | 1% RESISTOR<br>VALUE (kΩ) |

|-------------------------------|---------------------------|

| 250                           | 10.0                      |

| 300                           | 17.8                      |

| 400                           | 27.4                      |

| 500                           | 38.3                      |

| 650                           | 56.2                      |

| 750                           | 86.6                      |

## Table 2. Required RT Resistors (continued)

| NOMINAL<br>FREQUENCY<br>(kHz) | 1% RESISTOR<br>VALUE (kΩ) |

|-------------------------------|---------------------------|

| 850                           | 133                       |

| 1000                          | 205                       |

The TPS544B20 and TPS544C20 devices detect values that are out-of-range on the RT pin. If the device detects that RT pin has an out-of-range resistance connected to it, the device selects a frequency setting of either 250 kHz (if the resistance is less than 5 k $\Omega$ ) or 1 MHz (if the resistance is greater than 300 k $\Omega$ ). In this case, the device also asserts the IVFREQ bit in STATUS\_MFR\_SPECIFIC. Once VDD is applied, the frequency latches in memory and RT pin deactives until BP6 falls below V<sub>BP6UV</sub>. When the device has completed the Power-on-reset sequence, it latches the frequency in memory and deactivates the RT pin until the BP6 voltage falls below the BP6 undervoltage threshold setting.

#### 8.3.7 Soft-Start

To control the inrush current needed to charge the output capacitors during the start-up sequence, the TPS544C20 and TPS544B20 devices implement a soft-start time. When the device is enabled, the feedback reference voltage, V<sub>REF</sub>, rises from 0 V to its final value (including output margining or VREF\_TRIM value) at a slew rate defined by the TON\_RISE command. The slew rate needed to increase the reference voltage from 0 V to 600 mV at each given rise time defines the specified rise times. During the soft-start period, the error amplifier operates as a unity-gain buffer to force the COMP pin voltage to track the internal reference and minimize the offset between the internal reference and the output voltage. Because D-CAP mode or D-CAP2 mode control regulates the valley voltage, the average output voltage can exceed the final regulation voltage several millivolts at the end of the soft-start period See Figure 23.

Figure 23. Soft-Start

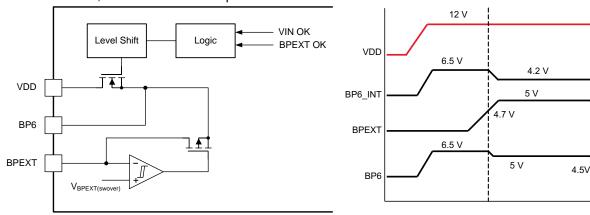

#### 8.3.8 Linear Regulators BP3 and BP6

Two on-board linear regulators provide suitable power for the internal circuitry of the devices. Externally bypass pins BP3 and BP6 for the converter to function properly. BP3 requires a minimum of 100 nF of capacitance connected to AGND. BP6 should be bypassed to GND with a 4.7-µF capacitor.

These devices allow the use of an internal regulator to power other circuits. Ensure that external loads placed on the regulators do not adversely affect operation of the controller. Avoid loads with heavy transient currents that can affect the regulator outputs. Transient voltages on these outputs can result in noisy or erratic operation. Observe the current limits. Shorting the BP3 pin to GND can damage the BP3 regulator. The BP3 regulator input comes from the BP6 regulator output. The BP6 regulator can supply 120 mA of current and the total current drawn from both regulators must be less than 120 mA. This total current includes the device operating current (I<sub>VDD</sub>) plus the gate-drive current required to drive the power MOSFETs.

6.5 V

4.5 V

6.5 V

#### 8.3.9 External Bypass (BPEXT)

The BPEXT pin provides an external bypass of the internal BP6 regulator when the application includes an external bias supply between 4.5 V and 6.5 V. Using an external supply reduces the power dissipation in these devices and can slightly improve system efficiency. If the input voltage is less than the UVLO threshold, or if the voltage on the BPEXT pin is lower than the switch-over voltage,  $V_{BPEXT(swover)}$ , these devices use the internal BP6 regulator. If the voltage on the BPEXT pin exceeds this switch-over voltage, then these devices disable the internal BP6 regulator and BPEXT outputs to BP6, replacing the internal linear regulator, until the voltage on the BPEXT pin falls by the BPEXT switch-over hysteresis amount,  $V_{HYS(swover)}$ . If the application does not require the BPEXT function, connect the BPEXT pin to GND.

Figure 24. BP External

Figure 25. BP Crossover Diagram

#### **NOTE**

It is not recommended to transition BPEXT across the switch-over voltage,  $V_{BPEXT(swover)}$ , during regulation. The transition causes an overshoot or undershoot response on the output voltage. Instead, the BPEXT voltage should be either fully established to its final level, or pulled low to GND prior to entering regulation.

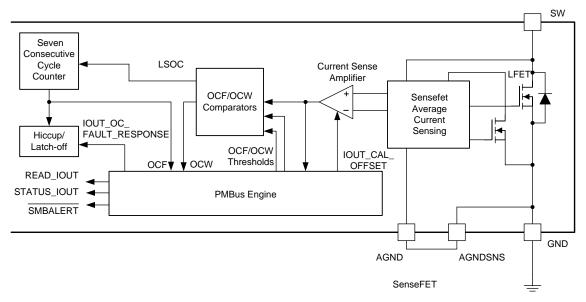

#### 8.3.10 Current Monitoring and Low-Side MOSFET Overcurrent Protection

The TPS544C20 and TPS544B20 devices sense average output current using an internal sensefet. A sensefet conducts a scaled-down version of the power-stage current. Sampling this current in the middle of the low-side drive signal determines the average output current. This architecture achieves excellent current monitoring and better overcurrent threshold accuracy than inductor DCR current sensing with minimal temperature variation and no dependence on power loss in a higher DCR inductor. This enables the use of lower DCR inductors to improve efficiency. Use the IOUT\_CAL\_OFFSET command to improve current sensing and overcurrent accuracy by removing board layout-related systematic errors post assembly. The devices continually digitize the sensed output current, and average it to reduce measurement noise. The devices then store the current value in the read-only READ\_IOUT register, enabling output current telemetry.

Figure 26. Sensefet Average Current Sensing and Low-Side Overcurrent Protection

The TPS544C20 and TPS544B20 devices also implement low-side MOSFET overcurrent protection with programmable fault and warning thresholds. The IOUT\_OC\_FAULT\_LIMIT and IOUT\_OC\_WARN\_LIMIT commands set the low-side overcurrent thresholds.

As shown in Figure 26, if an overcurrent event is detected in a given switching cycle, the device increments an overcurrent counter. When the device detects seven consecutive low-side overcurrent events, the converter responds, flagging the appropriate status registers, triggering SMBALERT if it is not masked, and entering either continuous restart hiccup, or latch-off according to the IOUT\_OC\_FAULT\_RESPONSE command. In continuous restart hiccup mode, the devices implement a time-out function that occurs after seven soft-start cycles; followed by a normal soft-start attempt. When the overcurrent fault clears, normal operation resumes, otherwise, the device detects overcurrent and the process repeats.

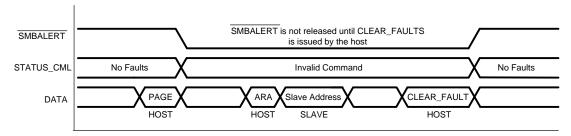

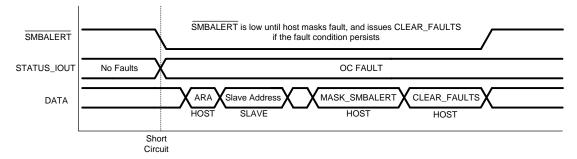

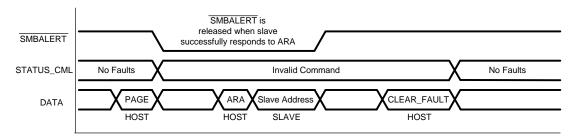

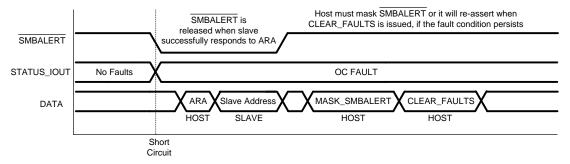

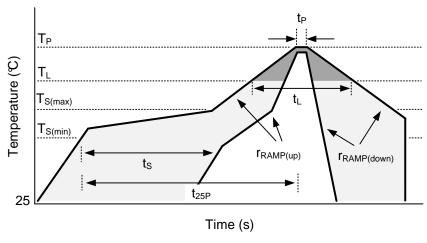

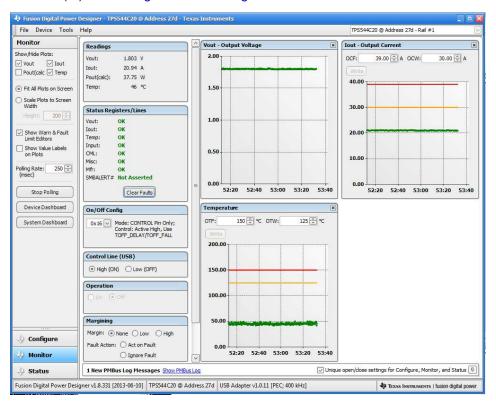

#### 8.3.11 High-Side MOSFET Short-Circuit Protection