# **HCSXXX**

### **HCSXXX** Memory Programming Specification

# This document includes the programming specifications for the following devices:

• HCS200

• HCS360

HCS500

• HCS201

• HCS361

HCS512

• HCS300

• HCS362

HCS515

HCS301

• HCS410

• HCS320

HCS412

### 1.0 PROGRAMMING THE HCSXXX

All of the KEELOQ® devices are programmed using a serial method. This Serial mode allows KEELOQ devices to be programmed while in users' systems, which increases the flexibility of designing cryptographic encoders, decoders and transponders into electronic systems. While some of the devices are capable of being programmed through wireless communications, the subject of this document is focused on wired programmers that make contact with the KEELOQ products while the components are incircuit or in a programmer socket. Additionally, this programming specification only applies to all KEELOQ devices listed above in all packages.

Note:

For the purpose of this document, "KEELOQ devices" and "KEELOQ products" refers to all of the components listed above.

# 1.1 Programming Algorithm Requirements

Depending on the device being programmed, the method for entering Programming mode can be achieved through the use of a combination of logic level signals applied to the programming pins. One or two pins are capable of accepting clock signals, while another pin is dedicated to bidirectional data. These pins are detailed in Table 1-1.

Additionally, the programming voltage range for VDD is  $+5V \pm 10\%$  for all the KEELOQ devices. There is not a requirement to apply high voltages to any of the pins beyond the level of VDD in order to enter the Programming mode. For more details about pin configurations during programming, refer to Table 1-1.

#### 1.2 Program/Verify Mode

The Program/Verify mode for the KEELOQ devices allows programming for all memory locations within the device being programmed. With the exception of the decoders, these pins are also used to verify the memory arrays.

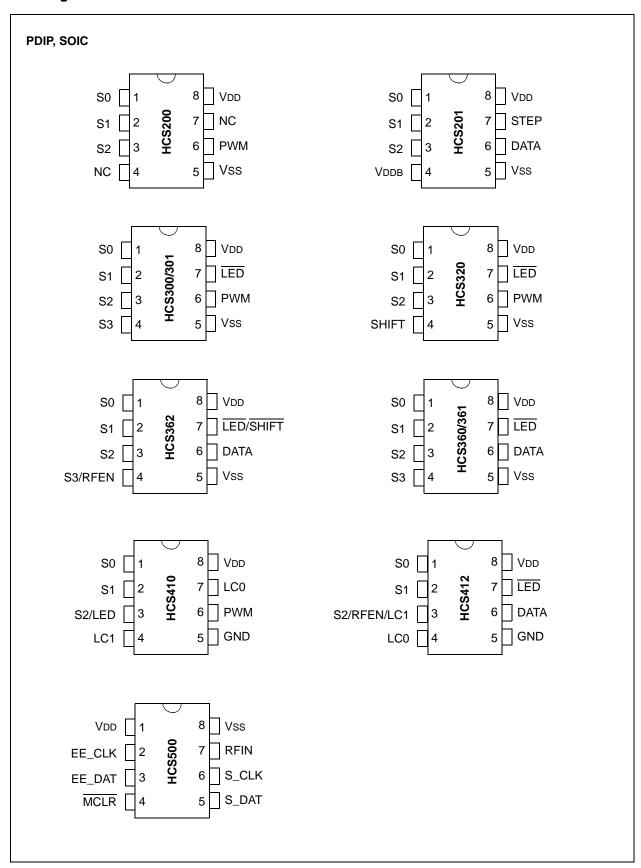

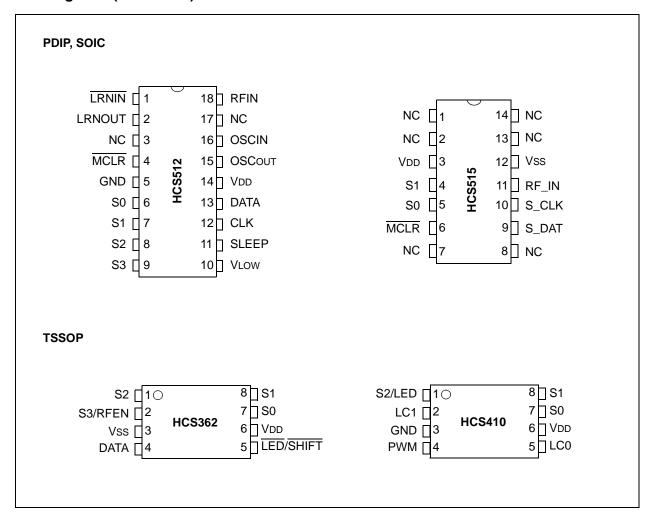

### **Pin Diagrams**

### Pin Diagrams (Continued)

## **HCSXXX**

TABLE 1-1: PIN DESCRIPTIONS (DURING PROGRAMMING)

| Device | Pin Number   |        |       |      |       | 0                     |

|--------|--------------|--------|-------|------|-------|-----------------------|

|        | Power Supply | Ground | Clock | Data | Other | Comments              |

| HCS200 | 8            | 5      | 3     | 6    | _     |                       |

| HCS201 | 8            | 5      | 3     | 6    | _     | (Notes 1)             |

| HCS300 | 8            | 5      | 3, 4  | 6    | _     | (Notes 2)             |

| HCS301 | 8            | 5      | 3, 4  | 6    | _     | (Notes 2)             |

| HCS320 | 8            | 5      | 3     | 6    | _     | (Notes 2)             |

| HCS360 | 8            | 5      | 3, 4  | 6    | 2     | (Notes 2)             |

| HCS361 | 8            | 5      | 3, 4  | 6    | 2     | (Notes 2)             |

| HCS362 | 8            | 5      | 3, 4  | 6    | _     | (Notes 2)             |

| HCS410 | 8            | 5      | 3     | 6    | _     |                       |

| HCS412 | 8            | 5      | 3     | 6    | _     | (Note 1)              |

| HCS500 | 1            | 8      | 6     | 5    | _     | (Notes 2, 3, 4, 7, 8) |

| HCS512 | 14           | 5      | 12    | 13   | 4     | (Notes 5, 6, 8, 9)    |

| HCS515 | 3            | 12     | 10    | 9    | _     | (Notes 7, 8)          |

- Note 1: Sends calibration pulse during ACK periods.

- **2:** VDD pin must be driven low after a Program/Verify cycle.

- 3: In-circuit programming recommended.

- 4: Used in conjunction with a Microchip Technology 24LC02B device.

- **5:** MCLR, pin 4, is used to enter Program mode.

- **6:** Must apply external clock source to OSCIN while programming.

- **7:** Requires command byte preceding data packet.

- 8: Verify function not available.

- 9: Uses checksum in data packet.

### 2.0 MEMORY MAPPING

The program memory maps for KEELOQ products begin at 0x000 and extend as shown in the tables that follow. As a device is being programmed, the address counter automatically increments to the next word location after receiving a data word. The memory maps for all KEELOQ encoders and transponders were designed so that each word is 16 bits wide. Decoder memory maps are 8 bits wide.

### 2.1 Encoder Memory Maps

TABLE 2-1: HCS200 12 X 16-BIT EEPROM MEMORY MAP

| Word Address | Mnemonic | Description                            |

|--------------|----------|----------------------------------------|

| 0x00         | KEY_0    | Word 0 (LSb's) of 64-bit crypt key     |

| 0x01         | KEY_1    | Word 1 of 64-bit crypt key             |

| 0x02         | KEY_2    | Word 2 of 64-bit crypt key             |

| 0x03         | KEY_3    | Word 3 (MSb's) of 64-bit crypt key     |

| 0x04         | SYNC     | 16-bit synchronization value           |

| 0x05         | Reserved | Set to 0x0000                          |

| 0x06         | SER_0    | Word 0 (LSb's) of 32-bit serial number |

| 0x07         | SER_1    | Word 1 (MSb's) of 32-bit serial number |

| 0x08         | SEED_0   | Word 0 (LSb's) of 32-bit seed value    |

| 0x09         | SEED_1   | Word 1 (MSb's) of 32-bit seed value    |

| 0x0A         | Reserved | Set to 0x0000                          |

| 0x0B         | CONFIG   | Configuration Word                     |

TABLE 2-2: HCS201 12 X 16-BIT EEPROM MEMORY MAP

| Word Address | Mnemonic | Description                            |

|--------------|----------|----------------------------------------|

| 0x00         | KEY_0    | Word 0 (LSb's) of 64-bit crypt key     |

| 0x01         | KEY_1    | Word 1 of 64-bit crypt key             |

| 0x02         | KEY_2    | Word 2 of 64-bit crypt key             |

| 0x03         | KEY_3    | Word 3 (MSb's) of 64-bit crypt key     |

| 0x04         | SYNC     | 16-bit synchronization value           |

| 0x05         | Reserved | Set to 0x0000                          |

| 0x06         | SER_0    | Word 0 (LSb's) of 32-bit serial number |

| 0x07         | SER_1    | Word 1 (MSb's) of 32-bit serial number |

| 0x08         | SEED_0   | Word 0 (LSb's) of 32-bit seed value    |

| 0x09         | SEED_1   | Word 1 (MSb's) of 32-bit seed value    |

| 0x0A         | DISC     | Discrimination Word                    |

| 0x0B         | CONFIG   | Configuration Word                     |

TABLE 2-3: HCS300 12 X 16-BIT EEPROM MEMORY MAP

| Word Address | Mnemonic             | Description                            |

|--------------|----------------------|----------------------------------------|

| 0x00         | KEY_0                | Word 0 (LSb's) of 64-bit crypt key     |

| 0x01         | KEY_1                | Word 1 of 64-bit crypt key             |

| 0x02         | KEY_2                | Word 2 of 64-bit crypt key             |

| 0x03         | KEY_3                | Word 3 (MSb's) of 64-bit crypt key     |

| 0x04         | SYNC                 | 16-bit synchronization value           |

| 0x05         | Reserved             | Set to 0x0000                          |

| 0x06         | SER_0                | Word 0 (LSb's) of 32-bit serial number |

| 0x07         | SER_1 <sup>(1)</sup> | Word 1 (MSb's) of 32-bit serial number |

| 0x08         | SEED_0               | Word 0 (LSb's) of 32-bit seed value    |

| 0x09         | SEED_1               | Word 1 (MSb's) of 32-bit seed value    |

| 0x0A         | Reserved             | Set to 0x0000                          |

| 0x0B         | CONFIG               | Configuration Word                     |

**Note 1:** MSb of this word is used for auto-shutoff timer.

TABLE 2-4: HCS301 12 X 16-BIT EEPROM MEMORY MAP

| Word Address | Mnemonic             | Description                            |

|--------------|----------------------|----------------------------------------|

| 0x00         | KEY_0                | Word 0 (LSb's) of 64-bit crypt key     |

| 0x01         | KEY_1                | Word 1 of 64-bit crypt key             |

| 0x02         | KEY_2                | Word 2 of 64-bit crypt key             |

| 0x03         | KEY_3                | Word 3 (MSb's) of 64-bit crypt key     |

| 0x04         | SYNC                 | 16-bit synchronization value           |

| 0x05         | Reserved             | Set to 0x0000                          |

| 0x06         | SER_0                | Word 0 (LSb's) of 32-bit serial number |

| 0x07         | SER_1 <sup>(1)</sup> | Word 1 (MSb's) of 32-bit serial number |

| 0x08         | SEED_0               | Word 0 (LSb's) of 32-bit seed value    |

| 0x09         | SEED_1               | Word 1 (MSb's) of 32-bit seed value    |

| 0x0A         | Reserved             | Set to 0x0000                          |

| 0x0B         | CONFIG               | Configuration Word                     |

Note 1: MSb of this word is used for auto-shutoff timer.

TABLE 2-5: HCS320 12 X 16-BIT EEPROM MEMORY MAP

| Word Address | Mnemonic             | Description                            |

|--------------|----------------------|----------------------------------------|

| 0x00         | KEY_0                | Word 0 (LSb's) of 64-bit crypt key     |

| 0x01         | KEY_1                | Word 1 of 64-bit crypt key             |

| 0x02         | KEY_2                | Word 2 of 64-bit crypt key             |

| 0x03         | KEY_3                | Word 3 (MSb's) of 64-bit crypt key     |

| 0x04         | SYNC                 | 16-bit synchronization value           |

| 0x05         | Reserved             | Set to 0x0000                          |

| 0x06         | SER_0                | Word 0 (LSb's) of 32-bit serial number |

| 0x07         | SER_1 <sup>(1)</sup> | Word 1 (MSb's) of 32-bit serial number |

| 0x08         | _                    | Not used                               |

| 0x09         | _                    | Not used                               |

| 0x0A         | Reserved             | Set to 0x0000                          |

| 0x0B         | CONFIG               | Configuration Word                     |

Note 1: MSb of this word is used for auto-shutoff timer.

TABLE 2-6: HCS360 12 X 16-BIT EEPROM MEMORY MAP

| Word Address | Mnemonic | Description                                           |

|--------------|----------|-------------------------------------------------------|

| 0x00         | KEY_0    | Word 0 (LSb's) of 64-bit crypt key                    |

| 0x01         | KEY_1    | Word 1 of 64-bit crypt key                            |

| 0x02         | KEY_2    | Word 2 of 64-bit crypt key                            |

| 0x03         | KEY_3    | Word 3 (MSb's) of 64-bit crypt key                    |

| 0x04         | SYNC_A   | 16-bit synchronization value A                        |

| 0x05         | SYNC_B   | 16-bit synchronization value B or Seed Value (Word 2) |

| 0x06         | Reserved | Set to 0x0000                                         |

| 0x07         | SEED_0   | Word 0 (LSb's) of 32-bit seed value                   |

| 0x08         | SEED_1   | Word 1 (MSb's) of 32-bit seed value                   |

| 0x09         | SER_0    | Word 0 (LSb's) of 32-bit serial number                |

| 0x0A         | SER_1    | Word 1 (MSb's) of 32-bit serial number                |

| 0x0B         | CONFIG   | Configuration Word                                    |

TABLE 2-7: HCS361 12 X 16-BIT EEPROM MEMORY MAP

| Word Address | Mnemonic      | Description                                           |

|--------------|---------------|-------------------------------------------------------|

| 0x00         | KEY_0         | Word 0 (LSb's) of 64-bit crypt key                    |

| 0x01         | KEY_1         | Word 1 of 64-bit crypt key                            |

| 0x02         | KEY_2         | Word 2 of 64-bit crypt key                            |

| 0x03         | KEY_3         | Word 3 (MSb's) of 64-bit crypt key                    |

| 0x04         | SYNC_A        | 16-bit synchronization value A                        |

| 0x05         | SYNC_B/SEED_2 | 16-bit synchronization value B or Seed Value (Word 2) |

| 0x06         | Reserved      | Set to 0x0000                                         |

| 0x07         | SEED_0        | Word 0 (LSb's) of 32-bit seed value                   |

| 0x08         | SEED_1        | Word 1 (MSb's) of 32-bit seed value                   |

| 0x09         | SER_0         | Word 0 (LSb's) of 32-bit serial number                |

| 0x0A         | SER_1         | Word 1 (MSb's) of 32-bit serial number                |

| 0x0B         | CONFIG        | Configuration Word                                    |

TABLE 2-8: HCS362 18 X 16-BIT EEPROM MEMORY MAP

| Word Address | Mnemonic | Description                            |

|--------------|----------|----------------------------------------|

| 0x00         | KEY1_0   | Word 0 (LSb's) of 64-bit crypt key 1   |

| 0x01         | KEY1_1   | Word 1 of 64-bit crypt key 1           |

| 0x02         | KEY1_2   | Word 2 of 64-bit crypt key 1           |

| 0x03         | KEY1_3   | Word 3 (MSb's) of 64-bit crypt key 1   |

| 0x04         | KEY2_0   | Word 0 (LSb's) of 64-bit crypt key 2   |

| 0x05         | KEY2_1   | Word 1 of 64-bit crypt key 2           |

| 0x06         | KEY2_2   | Word 2 of 64-bit crypt key 2           |

| 0x07         | KEY2_3   | Word 3 (MSb's) of 64-bit crypt key 2   |

| 0x08         | SEED_0   | Word 0 (LSb's) of 64-bit seed value    |

| 0x09         | SEED_1   | Word 1 of 64-bit seed value            |

| 0x0A         | SEED_2   | Word 2 of 64-bit seed value            |

| 0x0B         | SEED_3   | Word 3 (MSb's) of 64-bit seed value    |

| 0x0C         | CONFIG_0 | Configuration Word (LSb's)             |

| 0x0D         | CONFIG_1 | Configuration Word (MSb's)             |

| 0x0E         | SERIAL_0 | Word 0 (LSb's) of 32-bit serial number |

| 0x0F         | SERIAL_0 | Word 1 (MSb's) of 32-bit serial number |

| 0x10         | SYNC     | 16-bit synchronization value           |

| 0x11         | Reserved | Set to 0x00000                         |

TABLE 2-9: HCS500 9 X 8-BIT EEPROM MEMORY MAP

| Word Address | Mnemonic | Description                               |

|--------------|----------|-------------------------------------------|

| 0x00         | CONFIG   | Configuration Word                        |

| 0x01         | KEY0     | Byte 0 (LSb's) of 64-bit manufacturer key |

| 0x02         | KEY1     | Byte 1 of 64-bit manufacturer key         |

| 0x03         | KEY2     | Byte 2 of 64-bit manufacturer key         |

| 0x04         | KEY3     | Byte 3 of 64-bit manufacturer key         |

| 0x05         | KEY4     | Byte 4 of 64-bit manufacturer key         |

| 0x06         | KEY5     | Byte 5 of 64-bit manufacturer key         |

| 0x07         | KEY6     | Byte 6 of 64-bit manufacturer key         |

| 0x08         | KEY7     | Byte 7 (MSb's) of 64-bit manufacturer key |

TABLE 2-10: HCS512 10 X 8-BIT EEPROM MEMORY MAP

| Word Address | Mnemonic | Description                               |

|--------------|----------|-------------------------------------------|

| 0x00         | KEY0     | Byte 0 (LSb's) of 64-bit manufacturer key |

| 0x01         | KEY1     | Byte 1 of 64-bit manufacturer key         |

| 0x02         | KEY2     | Byte 2 of 64-bit manufacturer key         |

| 0x03         | KEY3     | Byte 3 of 64-bit manufacturer key         |

| 0x04         | KEY4     | Byte 4 of 64-bit manufacturer key         |

| 0x05         | KEY5     | Byte 5 of 64-bit manufacturer key         |

| 0x06         | KEY6     | Byte 6 of 64-bit manufacturer key         |

| 0x07         | KEY7     | Byte 7 (MSb's) of 64-bit manufacturer key |

| 0x08         | CONFIG   | Configuration byte                        |

| 0x09         | Checksum | Checksum byte                             |

TABLE 2-11: HCS515 9 X 8-BIT EEPROM MEMORY MAP

| Word Address | Mnemonic | Description                               |

|--------------|----------|-------------------------------------------|

| 0x00         | CONFIG   | Configuration byte                        |

| 0x01         | KEY0     | Byte 0 (LSb's) of 64-bit manufacturer key |

| 0x02         | KEY1     | Byte 1 of 64-bit manufacturer key         |

| 0x03         | KEY2     | Byte 2 of 64-bit manufacturer key         |

| 0x04         | KEY3     | Byte 3 of 64-bit manufacturer key         |

| 0x05         | KEY4     | Byte 4 of 64-bit manufacturer key         |

| 0x06         | KEY5     | Byte 5 of 64-bit manufacturer key         |

| 0x07         | KEY6     | Byte 6 of 64-bit manufacturer key         |

| 0x08         | KEY7     | Byte 7 (MSb's) of 64-bit manufacturer key |

### 2.2 Transponder Memory Maps

TABLE 2-12: HCS410 16 X 16-BIT EEPROM MEMORY MAP

| Word Address | Mnemonic | Description                             |  |  |  |

|--------------|----------|-----------------------------------------|--|--|--|

| 0x00         | KEY_0    | Word 0 (LSb's) of 64-bit crypt key      |  |  |  |

| 0x01         | KEY_1    | Word 1 of 64-bit crypt key              |  |  |  |

| 0x02         | KEY_2    | Word 2 of 64-bit crypt key              |  |  |  |

| 0x03         | KEY_3    | Word 3 (MSb's) of 64-bit crypt key      |  |  |  |

| 0x04         | DISC     | Ext. Config. Word/10-bit Discriminator  |  |  |  |

| 0x05         | CONFIG   | 16-bit Configuration Word               |  |  |  |

| 0x06         | SER_0    | Word 0 (LSb's) of 32-bit serial number  |  |  |  |

| 0x07         | SER_1    | Word 1 (MSb's) of 32-bit serial number  |  |  |  |

| 0x08         | SEED_0   | Word 0 (LSb's) of 64-bit seed value     |  |  |  |

| 0x09         | SEED_1   | Word 1 of 64-bit seed value             |  |  |  |

| 0x0A         | SEED_2   | Word 2 of 64-bit seed value             |  |  |  |

| 0x0B         | SEED_3   | Word 3 (MSb's) of 64-bit seed value     |  |  |  |

| 0x0C         | USR_0    | Word 0 (LSb's) of 64-bit user area      |  |  |  |

| 0x0D         | USR_1    | Word 1 of 64-bit user area              |  |  |  |

| 0x0E         | USR_2    | Word 2 of 64-bit user area              |  |  |  |

| 0x0F         | USR_3    | Word 3 (MSb's) of 64-bit user area SYNC |  |  |  |

TABLE 2-13: HCS412 18 X 16-BIT EEPROM MEMORY MAP

| Word Address | Mnemonic  | Description                                             |  |  |  |  |

|--------------|-----------|---------------------------------------------------------|--|--|--|--|

| 0x00         | KEY0      | Word 0 (LSb's) of 64-bit crypt key 1                    |  |  |  |  |

| 0x01         | KEY1      | Word 1 of 64-bit crypt key 1                            |  |  |  |  |

| 0x02         | KEY2      | Word 2 of 64-bit crypt key 1                            |  |  |  |  |

| 0x03         | KEY3      | Word 3 (MSb's) of 64-bit crypt key 1                    |  |  |  |  |

| 0x04         | SEED0     | Word 0 (LSb's) of 60-bit seed value                     |  |  |  |  |

| 0x05         | SEED1     | Word 1 of 60-bit seed value                             |  |  |  |  |

| 0x06         | SEED2     | Word 2 of 60-bit seed value                             |  |  |  |  |

| 0x07         | CFG/SEED3 | Word 3 of 60-bit seed value/Configuration in top nibble |  |  |  |  |

| 0x08         | CONFIG1   | Configuration Word 1 (security options)                 |  |  |  |  |

| 0x09         | CONFIG2   | Configuration Word 2                                    |  |  |  |  |

| 0x0A         | SER0      | Word 0 (LSb's) of 32-bit serial number                  |  |  |  |  |

| 0x0B         | SER1      | Word 1 (MSb's) of 32-bit serial number                  |  |  |  |  |

| 0x0C         | USR0      | Word 0 (LSb's) of 64-bit user area                      |  |  |  |  |

| 0x0D         | USR1      | Word 1 of 64-bit user area                              |  |  |  |  |

| 0x0E         | USR2      | Word 2 of 64-bit user area                              |  |  |  |  |

| 0x0F         | USR3      | Word 3 (MSb's) of 64-bit user area                      |  |  |  |  |

### 2.3 Entering Program Mode

Entering the Program/Verify mode will be dependent upon the type of device in use. Most KEELOQ devices use a serial clock and bidirectional data line to access the chips' memory maps. In order to enter the Programming mode, a Start condition is sent to the target device, where the clock and data lines must be held high and low for specified periods of time. That is, all lines are held low while the clock line is driven high. After a short delay, the data line is driven high. At this point, both lines must remain high for another delay period prior to dropping back to ground. After dropping both lines low and providing another delay, the state machine for the KEELOQ device will enter the Programming mode and begin to wait for data, or depending on the component, a bulk erase is performed on the memory array.

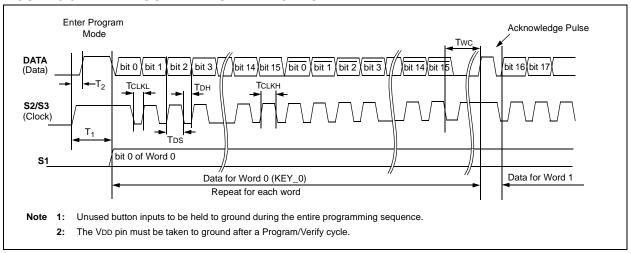

For the HCS360 and HCS361 devices, the Programming mode is entered by providing a clock source on the clock line and a Start pulse on the data line, as described in the previous paragraph. However, the difference is with driving the S1 pin, as shown in Figure 5-5. Bit 0 of the data packet must be driven on the S1 pin and kept at that level throughout the programming cycles and through verification.

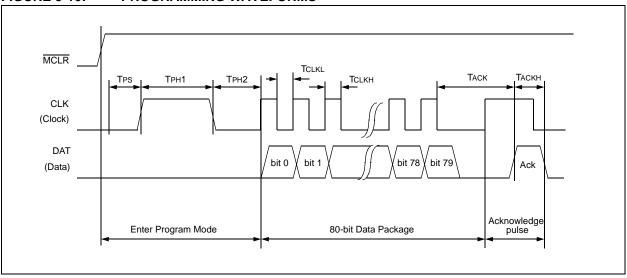

The HCS512 is another device that does not conform to the 2-wire protocol described above. For this device, the MCLR pin is driven high while data is held low. After the minimum setup time has been realized, the clock pin is driven high and then low for a minimum amount of time in order to send the HCS512 a Start condition and complete the Entry mode for the next programming sequence. The associated waveform is detailed in Section 5.0 "Program/Verify Mode Electrical Characteristics". The HCS512 is also the only device that requires a checksum be sent to the target device while it is being programmed. See the Checksum Section in the HCS512 Data Sheet, "KEELog® Code Hopping Decoder" (DS40151), for details on calculating the checksum.

Note: The HCS512 requires an external clock signal for the OSCIN pin. This signal is necessary throughout the Programming mode.

#### 2.4 Bulk Write Device

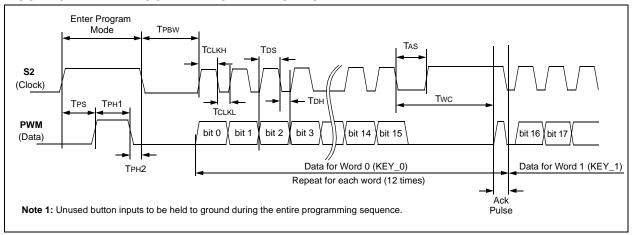

All transponders and encoders are bulk erased and programmed with zeros following the Start condition. The bulk erase/write time frame is specified as TPBW, which is minimally 4.0 ms. After the bulk function is complete, the programming state machine continues into the Program mode where it begins to wait for data and clock signals.

### 2.5 Serial Program/Verify Operation

For all of the encoders and transponders, the memory maps have been designed to be in 16-bit format, which means that each address location contains 16 bits of information including "don't care" bits that are read as zeros. Details relating to the designated pins for clock and data signals are outlined in Table 1-1. The decoders, on the other hand, were designed with memory maps in 8-bit format, so they are discussed separately in the next couple of paragraphs.

For specific information relating to the size of the memory maps for a given family of devices, be sure to review the tables in **Section 2.1 "Encoder Memory Maps"**.

The following paragraphs were written with the assumption that the target device has been placed into the Programming mode and is now waiting for data or a command byte to continue programming the memory array.

#### 2.5.1 ENCODERS/TRANSPONDERS

To input data to the target KEELOQ encoder or transponder, 16 clock cycles are applied to the clock pin of the target device while data is driven into the data pin. Data is clocked into the target device on the falling edge of the clock signal. Also, the minimum high time and low time for the clock signals are 50  $\mu s$ . During verification, data must be sampled on the rising edge of the clock.

### 2.5.2 DECODERS

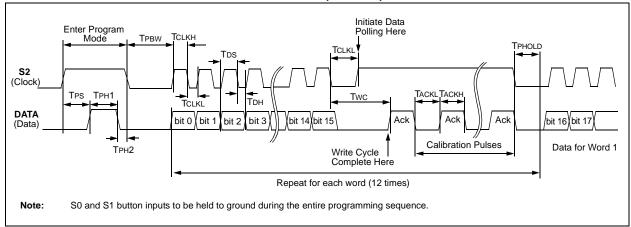

To input data to the target KEELOQ decoder, 8 clock cycles are applied to the clock pin of the target device while data is driven into the data pin. Data is clocked into the target device on the falling edge of the clock signals. Also, the minimum high time and minimum low time for the clock signals are 50  $\mu s$ . For the decoder family, there are no verification functions.

### 2.6 Begin Programming

Write cycles are performed a bit-at-a-time throughout the entire programming sequence for KEELOQ products. The total write cycle, which includes internal processing and programming time, is specified to take a minimum of 50 ms. As a result, programmers can include a delay for the minimum write cycle time or they can poll the target device as discussed in **Section 2.7** "**Polling Write Cycle**".

### 2.7 Polling Write Cycle

#### 2.7.1 HCS201 AND HCS412

Once the 16th clock cycle for the data word has been generated and the next minimum low time for the clock passes, the clock pin can be driven high to poll the completion of the write cycle. Before the write cycle is complete, the data pin for the target KEELOQ device will be low. After the write cycle is complete, the data pin on the HCS201 and the HCS412 will begin to provide pulses to the programmer in order to signal the completion of the write cycle. As a result, the programmer data pin should be set to high-impedance (input) so that it can read the pulses. After reading the pulses on the data pin, the programmer should drive the clock pin low and make the data pin an output so that data can continue to be driven into the target device. These pulses can be used for calibration sequences for the HCS201 and the HCS412. For information relating to oscillator calibration refer to Section 5.0 "Program/Verify Mode Electrical Characteristics", which discusses oscillator tuning. If the programmer polls the target device for the end of a write cycle, these two devices will continue to emit calibration pulses until their clock lines are driven low. In order to measure the calibration pulses, the clock pin must be driven high prior to the end of the write cycle, otherwise the calibration pulses will not appear.

#### 2.7.2 ALL OTHER KEELOQ DEVICES

Once the 16th clock cycle for the data word has been generated for any of the encoders or transponders or the last clock cycle for a decoder data packet is generated, the clock pin can be driven high to poll for the completion of the write cycle. Before the write cycle is complete, the data pin for the target KEELOQ device will be low. As a result, the programmer data pin should be set to high-impedance (input) so that it can sense the rising edge of data. After the write cycle is complete, the data pin will be driven high until the clock line is driven low again.

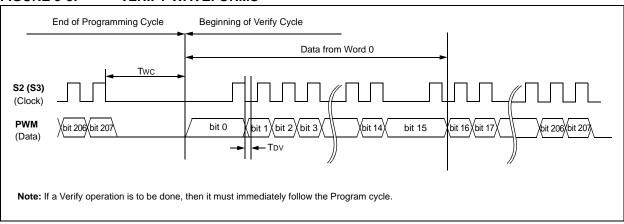

### 2.8 Verify Mode

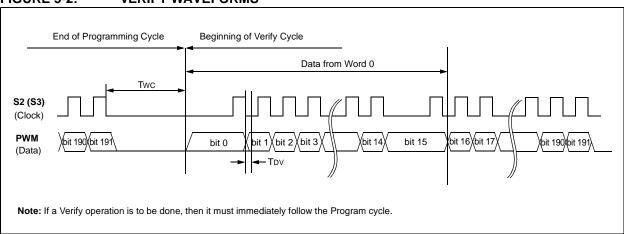

In terms of verify operations, all KEELOQ encoders and transponders incorporate a security feature that only allows one verify operation to be completed, and it must be completed at the end of the programming sequence before exiting the Programming mode.

When implementing polling routines to sense the end of the last write cycle and after driving the clock line low, the programmer can begin to read data by continuing to provide clock cycles to the target device. Note that there is not an Acknowledge bit from KEELOQ devices during the Verify mode.

In the case where the programmer provides a time delay to allow for write cycle completion, the programmer can provide clock cycles after the delay to begin reading data.

**Note:** Decoders do not incorporate a verify function.

### 3.0 CONFIGURATION WORD

For detailed descriptions of bit functions for the configuration words of the KEELOQ devices, be sure to download the latest Data Sheet for the respective device from the Microchip Technology web site (www.microchip.com). Configuration word architectures are also shown earlier in **Section 2.0 "Memory Mapping"**.

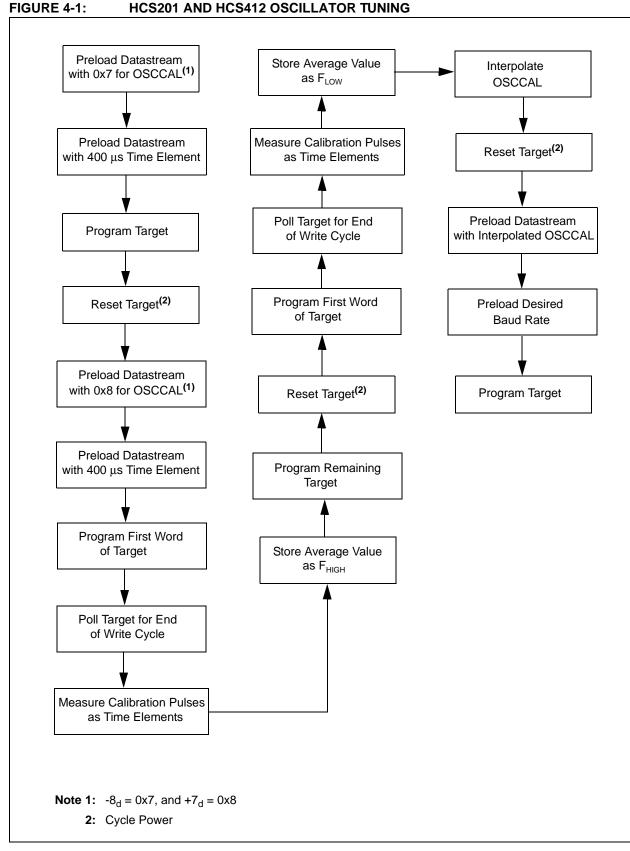

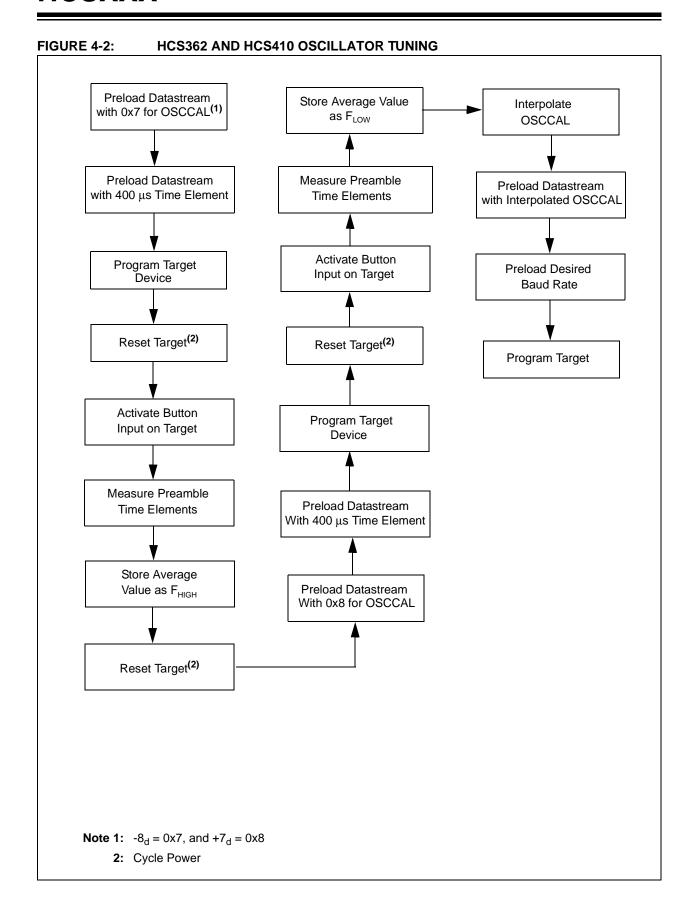

### 4.0 OSCILLATOR TUNING

Calibrating the oscillator of select devices can be completed a number of ways. For the purpose of this document, calibration will be completed using the Two-Point Calibration Algorithm, which is described in Application Note AN824, "KEELoq® Encoders Oscillator Calibration" (DS00824). The algorithm is as follows:

- OSCCAL = -8

- · Program target device

- Measure oscillator frequency FHIGH

- OSCCAL = +7

- · Program target device

- Measure oscillator frequency FLOW

- · Interpolate:

- OSCCAL = 16\*(FIDEAL FLOW)/(FHIGH FLOW)

- · Program target device

For a better understanding of how to implement this algorithm, the following flow charts are being provided:

KEELOQ devices that are capable of oscillator tuning include the HCS201, HCS362, HCS410 and the HCS412. Though, only the HCS201 and HCS412 transmit calibration pulses when polling the chips at the end of write cycles.

The other two devices must be tuned according to the preamble pulses that they transmit at the beginning of a data packet. For the best accuracy, use multiple time elements to achieve an average time element value. Typically, a number that is a power of  $2^n$  is used in order to simplify the resultant quotient (i.e., 4 or 8). In order to obtain the most accurate time element measurement, the widest possible baud rate should be chosen. For simplifying the two flow diagrams below, a common time element was chosen to the devices that share algorithms.

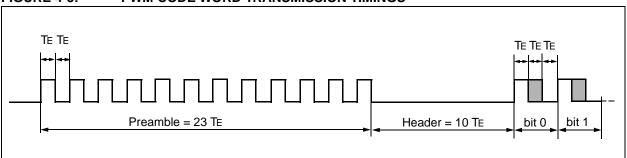

The HCS362 and the HCS410 oscillator tuning register can also be tuned as shown in the algorithm above, but with the caveat that after the device is programmed, the programmer must activate the target device in order to measure the time element in the communication preamble. A typical preamble is shown in Figure 4-3.

FIGURE 4-3: PWM CODE WORD TRANSMISSION TIMINGS

### 4.1 Programming Flow Charts

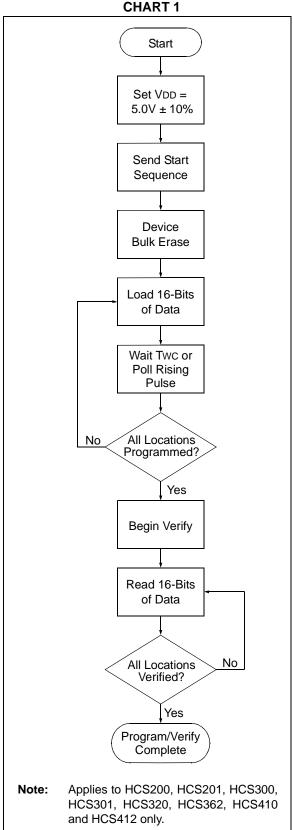

FIGURE 4-4: PROGRAMMING FLOW CHART 1

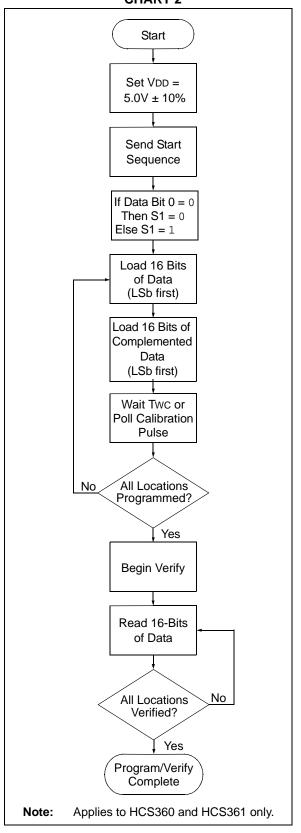

FIGURE 4-5: PROGRAMMING FLOW CHART 2

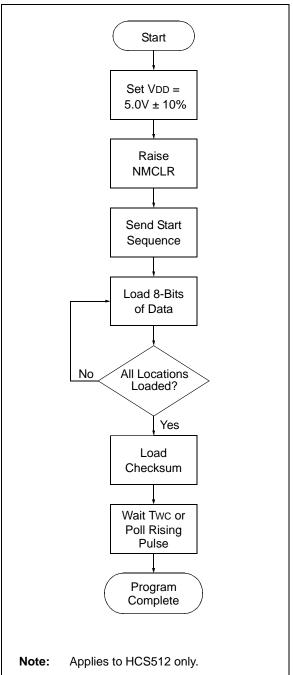

FIGURE 4-6: PROGRAMMING FLOW CHART 3

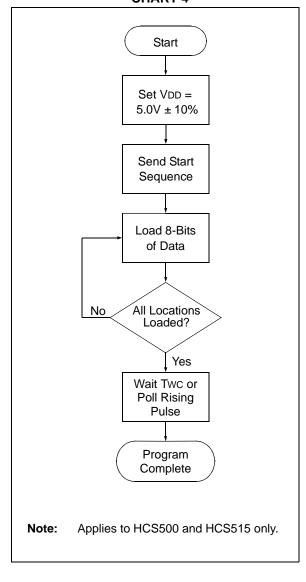

FIGURE 4-7: PROGRAMMING FLOW CHART 4

### 5.0 PROGRAM/VERIFY MODE ELECTRICAL CHARACTERISTICS

### 5.1 Timing Requirements for Program/Verify Mode – Encoders

| AC/DC CHARACTERISTICS |                                  | Standard Operating Conditions (unless otherwise stated)  Operating Temperature $+25^{\circ}\text{C} \pm 5^{\circ}\text{C}$ Operating Voltage $4.5\text{V} \le \text{VDD} \le 5.5\text{V}$ |     |       |                     |  |  |

|-----------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|---------------------|--|--|

| Sym                   | Characteristics                  | Min                                                                                                                                                                                       | Max | Units | Conditions/Comments |  |  |

| HCS200                | , HCS300, HCS301, HCS320 and HCS | 362                                                                                                                                                                                       |     |       |                     |  |  |

| TCLKH                 | Clock high time                  | 50                                                                                                                                                                                        | _   | μs    |                     |  |  |

| TCLKL                 | Clock low time                   | 50                                                                                                                                                                                        | _   | μs    |                     |  |  |

| TDH                   | Data hold time                   | 30                                                                                                                                                                                        | _   | μs    |                     |  |  |

| TDS                   | Data setup time                  | 0                                                                                                                                                                                         | _   | μs    |                     |  |  |

| TDV                   | Data out valid time              | _                                                                                                                                                                                         | 30  | μs    |                     |  |  |

| TPBW                  | Bulk Write time                  | 4.0                                                                                                                                                                                       | _   | ms    |                     |  |  |

| Трн1                  | Hold Time 1                      | 3.5                                                                                                                                                                                       | _   | ms    |                     |  |  |

| Трн2                  | Hold Time 2                      | 50                                                                                                                                                                                        | _   | μs    |                     |  |  |

| TPROG                 | Program delay time               | 4.0                                                                                                                                                                                       | _   | ms    |                     |  |  |

| Tps                   | Program mode setup time          | 3.5                                                                                                                                                                                       | 4.5 | ms    |                     |  |  |

| Twc                   | Program cycle time               | 50                                                                                                                                                                                        | _   | ms    |                     |  |  |

| HCS201                | 1 - 2 - 2                        | ,                                                                                                                                                                                         | ı   | 1     |                     |  |  |

| Таскн                 | Data out valid time              | 800                                                                                                                                                                                       | _   | μs    |                     |  |  |

| TACKL                 | Data hold time                   | 800                                                                                                                                                                                       | _   | μs    |                     |  |  |

| Тськн                 | Clock high time                  | 50                                                                                                                                                                                        | _   | μs    |                     |  |  |

| TCLKL                 | Clock low time                   | 50                                                                                                                                                                                        | _   | μs    |                     |  |  |

| TDH                   | Data hold time                   | 18                                                                                                                                                                                        | _   | μs    |                     |  |  |

| TDS                   | Data setup time                  | 0                                                                                                                                                                                         | _   | μs    |                     |  |  |

| Tov                   | Data out valid time              | _                                                                                                                                                                                         | 30  | μs    |                     |  |  |

| TPBW                  | Bulk Write time                  | 4.0                                                                                                                                                                                       | _   | ms    |                     |  |  |

| Трн1                  | Hold Time 1                      | 4.0                                                                                                                                                                                       | _   | ms    |                     |  |  |

| Трн2                  | Hold Time 2                      | 50                                                                                                                                                                                        | _   | μs    |                     |  |  |

| TPHOLD                | Hold time                        | 100                                                                                                                                                                                       | _   | μs    |                     |  |  |

| TPROG                 | Program delay time               | 4.0                                                                                                                                                                                       | _   | ms    |                     |  |  |

| Tps                   | Program mode setup time          | 2.0                                                                                                                                                                                       | 5.0 | ms    |                     |  |  |

| Twc                   | Program cycle time               | 50                                                                                                                                                                                        | _   | ms    |                     |  |  |

| HCS360                | , HCS361                         | l .                                                                                                                                                                                       | 1   |       |                     |  |  |

| T <sub>1</sub>        | Hold Time 1                      | 9.0                                                                                                                                                                                       | _   | ms    |                     |  |  |

| T <sub>2</sub>        | Program mode setup time          | 0                                                                                                                                                                                         | 4.0 | ms    |                     |  |  |

| TCLKH                 | Clock high time                  | 50                                                                                                                                                                                        | _   | μs    |                     |  |  |

| TCLKL                 | Clock low time                   | 50                                                                                                                                                                                        | _   | μs    |                     |  |  |

| TDH                   | Data hold time                   | 30                                                                                                                                                                                        | _   | μs    |                     |  |  |

| TDS                   | Data setup time                  | 0                                                                                                                                                                                         | _   | μs    |                     |  |  |

| TDV                   | Data out valid time              |                                                                                                                                                                                           | 30  | μs    |                     |  |  |

| Twc                   | Program cycle time               | 50                                                                                                                                                                                        | _   | ms    |                     |  |  |

### 5.2 Timing Requirements for Program/Verify Mode – Transponders

| AC/DC CHARACTERISTICS |                         | Standard Operating Conditions (unless otherwise stated)  Operating Temperature $+25^{\circ}\text{C} \pm 5^{\circ}\text{C}$ Operating Voltage $4.5\text{V} \le \text{V}_{DD} \le 5.5\text{V}$ |     |       |                     |  |  |

|-----------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|---------------------|--|--|

| Sym                   | Characteristics         | Min                                                                                                                                                                                          | Max | Units | Conditions/Comments |  |  |

| HCS410                | ), HCS412               |                                                                                                                                                                                              |     |       |                     |  |  |

| TAS                   | ACK start time          | 100                                                                                                                                                                                          | _   | μs    |                     |  |  |

| TCLKH                 | Clock high time         | 50                                                                                                                                                                                           | _   | μs    |                     |  |  |

| TCLKL                 | Clock low time          | 50                                                                                                                                                                                           | _   | μs    |                     |  |  |

| TDH                   | Data hold time          | 20                                                                                                                                                                                           | _   | μs    |                     |  |  |

| TDS                   | Data stable time        | 20                                                                                                                                                                                           | _   | μs    |                     |  |  |

| TDV                   | Data valid time         | _                                                                                                                                                                                            | 20  | μs    |                     |  |  |

| Трн1                  | Program Hold Time 1     | 4                                                                                                                                                                                            | _   | ms    |                     |  |  |

| Трн2                  | Program Hold Time 2     | 100                                                                                                                                                                                          | _   | μs    |                     |  |  |

| TPROG                 | Bulk write time         | 2.2                                                                                                                                                                                          | _   | ms    |                     |  |  |

| TPS                   | Program mode setup time | 3                                                                                                                                                                                            | 5   | ms    |                     |  |  |

| Twc                   | EEPROM write time       | 36                                                                                                                                                                                           | _   | ms    |                     |  |  |

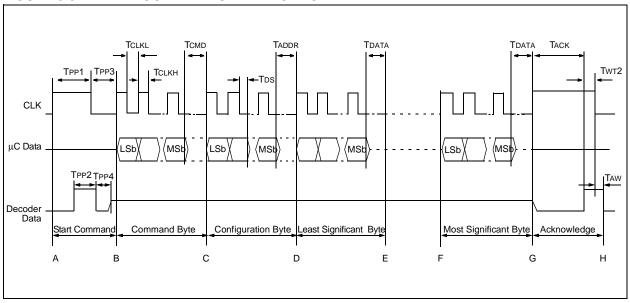

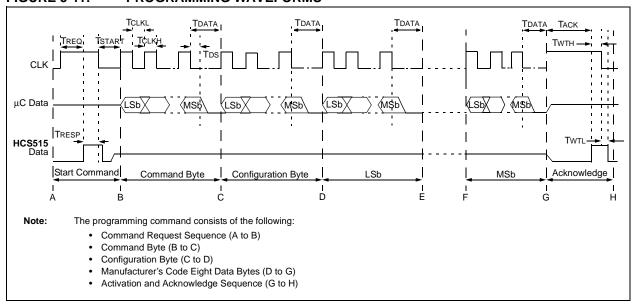

### 5.3 Timing Requirements for Program/Verify Mode – Decoders

| AC/DC CHARACTERISTICS |                                      | Standard Operating Conditions (unless otherwise stated)  Operating Temperature $+25^{\circ}\text{C} \pm 5^{\circ}\text{C}$ Operating Voltage $4.5\text{V} \le \text{VDD} \le 5.5\text{V}$ |       |       |       |                     |  |

|-----------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|---------------------|--|

| Sym                   | Characteristics                      | Sugg.<br>Value                                                                                                                                                                            | Min   | Max   | Units | Conditions/Comments |  |

| HCS500                |                                      |                                                                                                                                                                                           |       |       |       |                     |  |

| FCLK                  | Clock frequency                      | _                                                                                                                                                                                         | 500   | 25000 | Hz    |                     |  |

| TACK                  | Decoder acknowledge time             | _                                                                                                                                                                                         |       | 30    | μs    |                     |  |

| TADDR                 | Address validate time                | _                                                                                                                                                                                         | _     | 10    | μs    |                     |  |

| TCLKH                 | Clock high time                      | _                                                                                                                                                                                         | 20    | 1000  | μs    |                     |  |

| TCLKL                 | Clock low time                       | _                                                                                                                                                                                         | 20    | 1000  | μs    |                     |  |

| Тсмр                  | Command validate time                | _                                                                                                                                                                                         | -     | 10    | μs    |                     |  |

| TDATA                 | Command last bit to data first bit   | _                                                                                                                                                                                         | _     | 10    | μs    |                     |  |

| TDS                   | Data hold time                       | _                                                                                                                                                                                         | 14    | _     | μs    |                     |  |

| TREQ                  | Command request time                 | _                                                                                                                                                                                         | 0.015 | 500   | ms    |                     |  |

| TRESP                 | Acknowledge time                     | _                                                                                                                                                                                         | _     | 1     | ms    |                     |  |

| TSTART                | Command request to first command bit | _                                                                                                                                                                                         | 20    | 1000  | μs    |                     |  |

| HCS512                |                                      | •                                                                                                                                                                                         |       |       | ı     |                     |  |

| TACK                  | Acknowledge time                     | _                                                                                                                                                                                         |       | 80    | ms    | Fosc = 4 MHz        |  |

| Таскн                 | Acknowledge duration                 | _                                                                                                                                                                                         | 1     | _     | μs    | Fosc = 4 MHz        |  |

| TCLKH                 | Clock high time                      | _                                                                                                                                                                                         | 0.05  | 320   | μs    | Fosc = 4 MHz        |  |

| TCLKL                 | Clock low time                       | _                                                                                                                                                                                         | 0.05  | 320   | μs    | Fosc = 4 MHz        |  |

| Трн1                  | Hold Time 1                          | _                                                                                                                                                                                         | 8     | 128   | ms    | Fosc = 4 MHz        |  |

| Трн2                  | Hold Time 2                          | _                                                                                                                                                                                         | 0.05  | 320   | μs    | Fosc = 4 MHz        |  |

| TPS                   | Program mode setup time              | _                                                                                                                                                                                         | 1     | 64    | ms    | Fosc = 4 MHz        |  |

| HCS515                |                                      |                                                                                                                                                                                           |       |       | •     |                     |  |

| TACK                  | Command acknowledge time             | *                                                                                                                                                                                         | 30    | 240   | ms    |                     |  |

| TCLKH                 | Clock high time                      | 100                                                                                                                                                                                       | 20    | 1000  | μs    |                     |  |

| TCLKL                 | Clock low time                       | 100                                                                                                                                                                                       | 20    | 1000  | μs    |                     |  |

| TDATA                 | Command last bit to data first bit   | 100                                                                                                                                                                                       | 10    | 1000  | μs    |                     |  |

| TDS                   | Data hold time                       | 50                                                                                                                                                                                        | 14    | 1000  | μs    |                     |  |

| TREQ                  | Command request time                 | *                                                                                                                                                                                         | 0.005 | 500   | ms    |                     |  |

| TRESP                 | Acknowledge time                     | 100                                                                                                                                                                                       | 10    | 1000  | μs    |                     |  |

| TSTART                | Command request to first command bit | 100                                                                                                                                                                                       | 20    | 1000  | μs    |                     |  |

| TWTH                  | Acknowledge respond time             | 100                                                                                                                                                                                       | 20    | 1000  | μs    |                     |  |

| TWTL                  | Clock low to next command            | 100                                                                                                                                                                                       | 10    | _     | μs    |                     |  |

<sup>\*</sup> Depends on decoder status.

### 5.4 Programming Waveforms (HCS200, HCS300, HCS301, HCS320, HCS362)

### FIGURE 5-1: PROGRAMMING WAVEFORMS

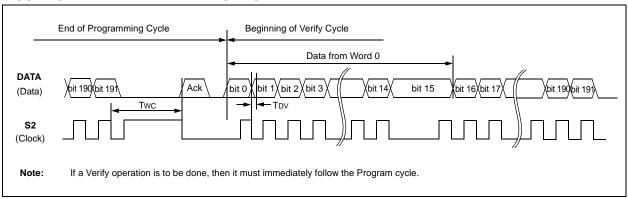

### FIGURE 5-2: VERIFY WAVEFORMS

### 5.5 Programming Waveforms (HCS201)

### FIGURE 5-3: PROGRAMMING WAVEFORMS (HCS201)

### FIGURE 5-4: VERIFY WAVEFORMS

### 5.6 Programming Waveforms (HCS360, HCS361)

### FIGURE 5-5: PROGRAMMING WAVEFORMS

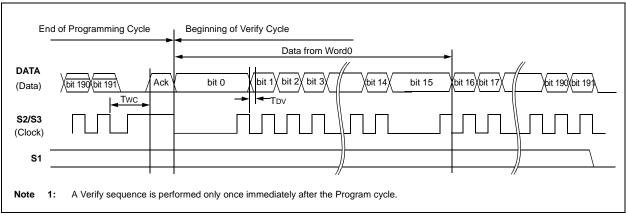

### FIGURE 5-6: VERIFY WAVEFORMS

### 5.7 Programming Waveforms (HCS410, HCS412)

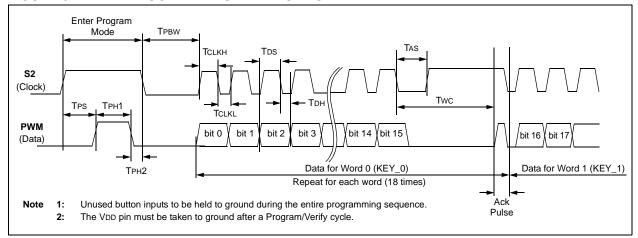

### FIGURE 5-7: PROGRAMMING WAVEFORMS

### FIGURE 5-8: VERIFY WAVEFORMS

### 5.8 Programming Waveforms (HCS500)

FIGURE 5-9: PROGRAMMING WAVEFORMS

### 5.9 Programming Waveforms (HCS512)

FIGURE 5-10: PROGRAMMING WAVEFORMS

### 5.10 Programming Waveforms (HCS515)

### FIGURE 5-11: PROGRAMMING WAVEFORMS

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WAR-RANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC, and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Migratable Memory, MXDEV, MXLAB, PICMASTER, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, MPASM, MPLIB, MPLINK, MPSIM, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2004, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

QUALITY MANAGEMENT SYSTEM

CERTIFIED BY DNV

ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona and Mountain View, California in October 2003. The Company's quality system processes and procedures are for its PICmicro® 8-bit MCUs, KEELoo® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

### WORLDWIDE SALES AND SERVICE

#### **AMERICAS**

**Corporate Office**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200

Fax: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://support.microchip.com

Web Address: www.microchip.com

**Atlanta**

Alpharetta, GA Tel: 770-640-0034 Fax: 770-640-0307

**Boston**

Westford, MA Tel: 978-692-3848 Fax: 978-692-3821

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo

Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

San Jose

Mountain View, CA Tel: 650-215-1444 Fax: 650-961-0286

**Toronto**

Mississauga, Ontario,

Canada

Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

China - Chengdu

Tel: 86-28-8676-6200 Fax: 86-28-8676-6599

China - Fuzhou

Tel: 86-591-8750-3506 Fax: 86-591-8750-3521

China - Hong Kong SAR

Tel: 852-2401-1200 Fax: 852-2401-3431

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang

Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

China - Shunde

Tel: 86-757-2839-5507 Fax: 86-757-2839-5571

China - Qingdao

Tel: 86-532-502-7355 Fax: 86-532-502-7205

#### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-2229-0061 Fax: 91-80-2229-0062

India - New Delhi

Tel: 91-11-5160-8631 Fax: 91-11-5160-8632

Japan - Kanagawa

Tel: 81-45-471-6166 Fax: 81-45-471-6122

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or

82-2-558-5934

**Singapore** Tel: 65-6334-8870

Fax: 65-6334-8850

**Taiwan - Kaohsiung** Tel: 886-7-536-4818 Fax: 886-7-536-4803

Taiwan - Taipei

Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

Taiwan - Hsinchu

Tel: 886-3-572-9526 Fax: 886-3-572-6459

#### **EUROPE**

Austria - Weis

Tel: 43-7242-2244-399 Fax: 43-7242-2244-393 **Denmark - Ballerup**

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Massy

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Ismaning

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399

Fax: 31-416-690340

England - Berkshire

Tel: 44-118-921-5869 Fax: 44-118-921-5820