# **TLD2141-3EP**

### LITIX™ Basic+

## Features

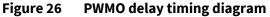

- Triple channel device with integrated and protected output stages (current sources), optimized to drive LEDs as additional low cost current source

- High output current (up to 80 mA) per channel

- Very low current consumption in sleep mode

- Very low output leakage when channel is "off"

- Low current consumption during fault

- Additional output current demand supported by LITIX<sup>™</sup> Companion direct drive without additional components

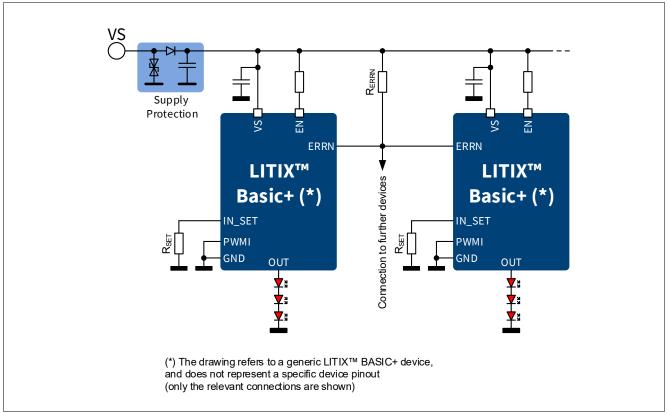

- Intelligent fault management: up to 16 and more devices can share a common error network with only one external resistor

- Reverse polarity protection allows reduction of external components and improves system performance at low battery/input voltages

- Overload protection

- Wide temperature range:  $-40^{\circ}C < T_{J} < 150^{\circ}C$

- Output current control via external low power resistor

- Green product (RoHS compliant)

## **Potential applications**

- Cost effective "stop"/ "tail" function implementation with shared and separated LEDs per function

- Turn indicators

- Position, fog, rear lights and side markers

- Animated light functions like wiping indicators and "welcome/goodbye" functions

- Day Running Light

- Interior lighting functions like ambient lighting (including RGB color control), illumination and dash board lighting

- LED indicators for industrial applications and instrumentation

## **Product validation**

Qualified for Automotive Applications. Product Validation according to AEC-Q100/101.

2019-09-26

## Description

The LITIX<sup>™</sup> Basic+ TLD2141-3EP is a triple channel high-side driver IC with integrated output stages. It is designed to control LEDs with a current up to 80 mA. In typical automotive applications the device is capable of driving 3 red LEDs per chain (total 9 LEDs) with a current up to 60 mA and even above, if not limited by the overall system thermal properties. Practically, the output current is controlled by an external resistor or reference source, independently from load and supply voltage changes.

#### Table 1 Product summary

| Parameter                                                 | Symbol                                        | Values                                                                                                                                                                 |

|-----------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating voltage                                         | V <sub>S(nom)</sub>                           | 5.5 V 40 V                                                                                                                                                             |

| Maximum voltage                                           | V <sub>S(max)</sub><br>V <sub>OUTx(max)</sub> | 40 V                                                                                                                                                                   |

| Nominal output (load) current                             | I <sub>OUTx(nom)</sub>                        | 60 mA (nominal) when using the automotive<br>supply voltage range 8 V - 18 V. Currents up to<br>$I_{OUTx(max)}$ are possible with low thermal resistance<br>$R_{thJA}$ |

| Maximum output (load) current                             | I <sub>OUTx(max)</sub>                        | 80 mA depending on <i>R</i> <sub>thJA</sub>                                                                                                                            |

| Current accuracy at $R_{\text{SET}} = 10 \text{ k}\Omega$ | K <sub>LTx</sub>                              | 300±4.33%                                                                                                                                                              |

| Current consumption in sleep mode                         | I <sub>S(sleep, typ)</sub>                    | 0.1 μΑ                                                                                                                                                                 |

| Maximum current consumption during fault                  | I <sub>S(fault, ERRN)</sub>                   | 850 μA or less when fault is detected from another device (disabled via ERRN)                                                                                          |

| Туре        | Package     | Marking |

|-------------|-------------|---------|

| TLD2141-3EP | PG-TSDSO-14 | TLD2141 |

# **Table of Contents**

| 1              | Block diagram                                                                | . 4 |

|----------------|------------------------------------------------------------------------------|-----|

| 2              | Pin configuration                                                            | . 5 |

| 2.1            | Pin assignment                                                               | . 5 |

| 2.2            | Pin definitions and functions                                                | . 5 |

| 3              | General product characteristics                                              | . 7 |

| 3.1            | Absolute maximum ratings                                                     |     |

| 3.2            | Functional range                                                             | . 8 |

| 3.3            | Thermal resistance                                                           | . 9 |

| 4              | Internal supply                                                              | 10  |

| 4.1            | Description                                                                  | 10  |

| 4.2            | Electrical characteristics internal supply and EN pin                        | 12  |

| 5              | Power stages                                                                 | 14  |

| 5.1            | Protection                                                                   | 14  |

| 5.1.1          | Thermal protection                                                           | 14  |

| 5.1.2          | Reverse battery protection                                                   |     |

| 5.2            | Output configuration via IN_SET, OUT_SET and PWMI pins                       |     |

| 5.2.1          | IN_SET pin                                                                   |     |

| 5.2.2<br>5.2.3 | Output current adjustment via R <sub>SET</sub> Output control via IN_SET     |     |

| 5.2.3<br>5.2.4 | IN_SET pin behavior during device fault management                           |     |

| 5.2.5          | OUT_SET pin                                                                  |     |

| 5.2.6          | Direct control of PWMI                                                       |     |

| 5.2.7          | Timing diagrams                                                              |     |

| 5.3            | Electrical characteristics power stage                                       |     |

| 5.4            | Electrical characteristics IN_SET, OUT_SET and PWMI pins for output settings | 22  |

| 6              | Load diagnosis                                                               | 24  |

| 6.1            | Error management via ERRN and D-pins                                         | 24  |

| 6.1.1          | ERRN pin                                                                     | 24  |

| 6.1.2          | D-pin                                                                        |     |

| 6.2            | Open Load (OL) and short OUTx to GND (SC)                                    |     |

| 6.2.1          | Fault management (D-pin open or connected with a capacitor to GND)           |     |

| 6.2.2          | Fault management (D-pin connected to GND)                                    |     |

| 6.3            | Electrical characteristics: Load diagnosis and Overload management           |     |

| 7              | PWM control (Digital dimming)                                                |     |

| 7.1            | PWM unit                                                                     |     |

| 7.2            | Direct control of PWMI                                                       |     |

| 7.3            | Timing diagrams                                                              |     |

| 7.4            | Electrical characteristics PWM engine                                        |     |

| 8              | Application information                                                      | 39  |

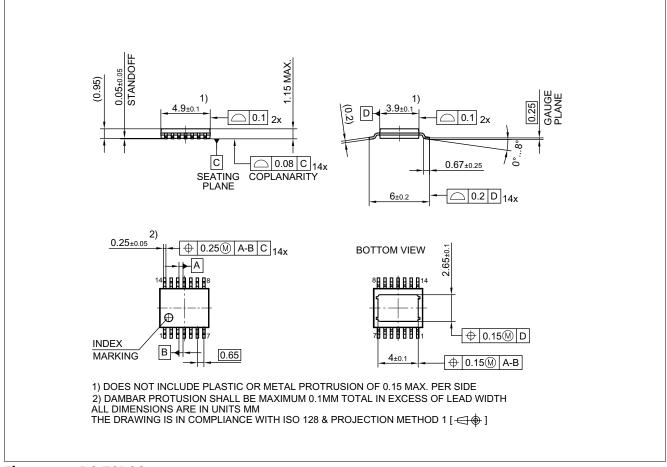

| 9              | Package outline                                                              | 40  |

| 10             | Revision History                                                             | 41  |

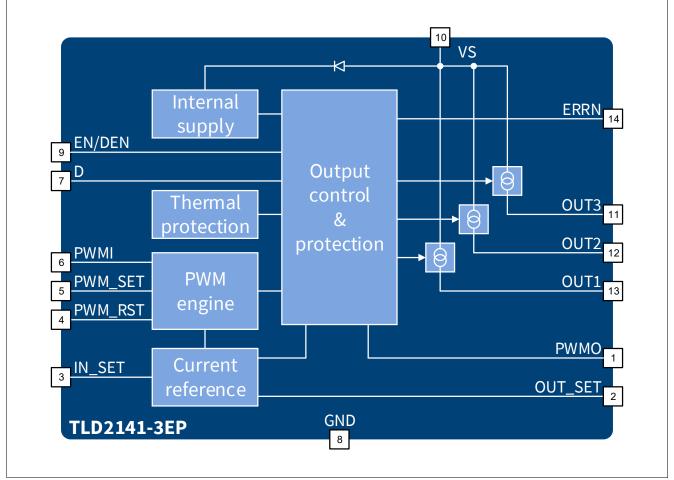

#### **Block diagram**

## 1 Block diagram

Figure 1 Block diagram

**Pin configuration**

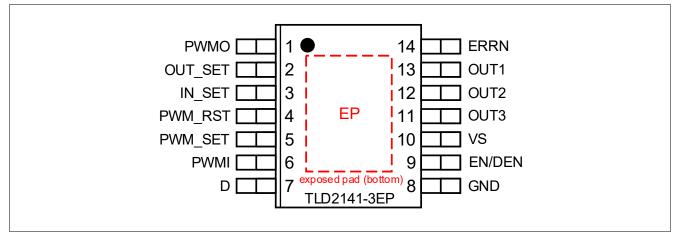

## 2 Pin configuration

### 2.1 Pin assignment

### Figure 2 Pin configuration

### 2.2 Pin definitions and functions

| Pin | Symbol  | Function                                                                                                                                                                                                                               |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10  | VS      | <b>Supply voltage;</b> Connected to battery or supply control switch, with EMC filter                                                                                                                                                  |

| 8   | GND     | Ground; Signal ground                                                                                                                                                                                                                  |

| 3   | IN_SET  | <b>Control input for OUT channels;</b> Connect to a low power resistor to adjust OUT output currents. Alternatively, a different current reference (i.e. the OUT_SET of another LITIX <sup>™</sup> Basic+ LED Driver) may be connected |

| 2   | OUT_SET | <b>Control output for additional current source;</b> If an additional channel or output current with same input control is needed, connect this pin to the IN_SET pin of the additional LED driver. If not used, leave the pin open    |

| 6   | PWMI    | <b>PWM input;</b> Connect to an external PWM controller or a ceramic capacitor (when internal PWM engine is intended to be used). If not used, connect to GND                                                                          |

| 1   | PWMO    | <b>PWM output;</b> Buffered PWMI logic state. Used to drive additional devices with same timing as PWMI. If not used, leave the pin open                                                                                               |

| 4   | PWM_RST | <b>PWM duty cycle reset input;</b> Connect to a low power resistor to adjust PWM frequency and duty cycle. If the internal PWM engine is not used (direct PWMI drive) it should be left open                                           |

| 5   | PWM_SET | <b>PWM duty cycle set input;</b> Connect to a low power resistor to adjust PWM frequency and duty cycle. If the internal PWM engine is not used (direct PWMI drive) it should be left open                                             |

| 7   | D       | <b>Disable/delay error input;</b> Connect to a capacitor, leave open or connect to GND, depending on the required diagnosis management (see <b>Chapter 6</b> for further details)                                                      |

### **Pin configuration**

| Pin            | Symbol | Function                                                                                                                                                                           |

|----------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14             | ERRN   | <b>ERROR flag I/O;</b> Open drain, active low. Connect to a pull-up resistor                                                                                                       |

| 9              | EN/DEN | <b>Outputs enable and diagnosis control input;</b> Connect to a control input (i.e. to VS via a resistor divider or a Zener diode) to enable OUTx control and diagnosis capability |

| 13             | OUT1   | Channel 1 output pin; Connect to the target load                                                                                                                                   |

| 12             | OUT2   | Channel 2 output pin; Connect to the target load                                                                                                                                   |

| 11             | OUT3   | Channel 3 output pin; Connect to the target load                                                                                                                                   |

| Exposed<br>Pad | EP     | <b>Exposed Pad;</b> Connected to GND-pin in application                                                                                                                            |

**General product characteristics**

## 3 General product characteristics

### 3.1 Absolute maximum ratings

### Table 2Absolute maximum ratings1)

$T_{\rm J}$  = -40°C to +150°C;  $R_{\rm IN\_SET}$  = 10 kΩ; all voltages with respect to GND, positive current flowing into input and I/O pins, positive current flowing out from output pins (unless otherwise specified)

| Parameter                                                                         | Symbol                         |      | Values |      |    | Note or        | Number   |

|-----------------------------------------------------------------------------------|--------------------------------|------|--------|------|----|----------------|----------|

|                                                                                   |                                | Min. | Тур.   | Max. |    | Test Condition |          |

| Voltage                                                                           | •                              |      |        | L.   |    |                | •        |

| Supply voltage                                                                    | Vs                             | -18  | -      | 40   | V  | -              | P_4.1.1  |

| EN/DEN voltage                                                                    | V <sub>EN/DEN</sub>            | -18  | -      | 40   | V  | -              | P_4.1.3  |

| EN/DEN voltage related to $V_{\rm S}$ :<br>$V_{\rm EN/DEN} - V_{\rm S}$           | V <sub>EN/DEN(VS</sub>         | -40  | -      | 18   | V  | -              | P_4.1.4  |

| EN/DEN voltage related to $V_{OUTx}$ :<br>$V_{EN/DEN} - V_{OUTx}$                 | V <sub>EN/DEN(V</sub><br>outx) | -18  | -      | 40   | V  | _              | P_4.1.5  |

| Output voltages                                                                   | V <sub>OUTx</sub>              | -1   | -      | 40   | V  | -              | P_4.1.10 |

| Output voltages related to V <sub>S</sub> : V <sub>S</sub><br>- V <sub>OUTx</sub> | V <sub>OUTx(VS)</sub>          | -18  | -      | 40   | V  | -              | P_4.1.11 |

| IN_SET voltages                                                                   | $V_{\rm IN\_SET}$              | -0.3 | -      | 6    | V  | -              | P_4.1.12 |

| PWMI voltage                                                                      | V <sub>PWMI</sub>              | -0.3 | -      | 6    | V  | -              | P_4.1.14 |

| PWMO voltage                                                                      | V <sub>PWMO</sub>              | -0.3 | -      | 6    | V  | -              | P_4.1.15 |

| PWM_RST voltage                                                                   | V <sub>PWM_RST</sub>           | -0.3 | -      | 6    | V  | -              | P_4.1.16 |

| PWM_SET voltage                                                                   | V <sub>PWM_SET</sub>           | -0.3 | -      | 6    | V  | -              | P_4.1.17 |

| ERRN voltage                                                                      | V <sub>ERRN</sub>              | -0.3 | -      | 40   | V  | -              | P_4.1.18 |

| D Voltage                                                                         | V <sub>D</sub>                 | -0.3 | _      | 6    | V  | -              | P_4.1.19 |

| Current                                                                           |                                |      |        | L.   |    |                | ·        |

| Output currents (On each<br>output channel OUTn)                                  | I <sub>OUTx</sub>              | 0    | -      | 90   | mA | -              | P_4.1.21 |

| PWMI current                                                                      | I <sub>PWMI</sub>              | -0.5 | -      | 0.5  | mA | -              | P_4.1.26 |

| PWMO current                                                                      | I <sub>PWMO</sub>              | -2   | _      | 2    | mA | -              | P_4.1.27 |

| PWM_RST current                                                                   | I <sub>PWM_RST</sub>           | 0    | -      | 300  | μA | -              | P_4.1.28 |

| PWM_SET current                                                                   | I <sub>PWM_SET</sub>           | 0    | -      | 300  | μA | -              | P_4.1.29 |

| IN_SET current                                                                    | I <sub>IN_SET</sub>            | 0    | -      | 300  | μA | -              | P_4.1.30 |

| D current                                                                         | I <sub>D</sub>                 | -0.5 | -      | 0.5  | mA | -              | P_4.1.31 |

| OUT_SET current                                                                   | I <sub>OUT_SET</sub>           | 0    | -      | 0.5  | mA | -              | P_4.1.32 |

| Temperature                                                                       |                                |      |        |      |    |                | I        |

| Junction temperature                                                              | T                              | -40  | -      | 150  | °C | -              | P_4.1.33 |

| Storage temperature                                                               | T <sub>stg</sub>               | -55  | _      | 150  | °C | -              | P_4.1.34 |

#### **General product characteristics**

#### Table 2Absolute maximum ratings<sup>1</sup> (cont'd)

$T_{\rm J}$  = -40°C to +150°C;  $R_{\rm IN\_SET}$  = 10 kΩ; all voltages with respect to GND, positive current flowing into input and I/O pins, positive current flowing out from output pins (unless otherwise specified)

| Parameter                                                  | Symbol                       |      | Values | ;    | Unit | Note or               | Number   |

|------------------------------------------------------------|------------------------------|------|--------|------|------|-----------------------|----------|

|                                                            |                              | Min. | Тур.   | Max. |      | <b>Test Condition</b> |          |

| ESD susceptibility                                         |                              |      |        |      |      |                       | i.       |

| ESD susceptibility all pins to GND                         | V <sub>ESD</sub>             | -2   | -      | 2    | kV   | HBM <sup>2)</sup>     | P_4.1.36 |

| ESD susceptibility all pins to GND                         | V <sub>ESD</sub>             | -500 | -      | 500  | V    | CDM <sup>3)</sup>     | P_4.1.37 |

| ESD susceptibility Pin 1, 7, 8, 14<br>(corner pins) to GND | V <sub>ESD1,7,8,1</sub><br>4 | -750 | -      | 750  | V    | CDM <sup>3)</sup>     | P_4.1.38 |

1) Not subject to production test, specified by design

2) ESD susceptibility, HBM according to ANSI/ESDA/JEDEC JS001 (1.5 k $\Omega,$  100 pF)

3) ESD susceptibility, Charged Device Model "CDM" according JEDEC JESD22-C101

#### Notes

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

#### 3.2 Functional range

#### Table 3 Functional range

| Parameter                                    | Symbol              | Values               |      |      | Unit | Note or               | Number  |

|----------------------------------------------|---------------------|----------------------|------|------|------|-----------------------|---------|

|                                              |                     | Min.                 | Тур. | Max. |      | <b>Test Condition</b> |         |

| Voltage range for normal operation           | V <sub>S(nom)</sub> | 5.5                  | -    | 18   | V    | -                     | P_4.2.1 |

| Extended supply voltage for functional range | V <sub>S(ext)</sub> | V <sub>SUV(ON)</sub> | -    | 40   | V    | -                     | P_4.2.2 |

| Junction temperature                         | TJ                  | -40                  | -    | 150  | °C   | -                     | P_4.2.4 |

Note: Within the Normal Operation range, the IC operates as described in the circuit description. Within the Extended Operation range, parameters deviations are possible. The electrical characteristics are specified within the conditions given in the Electrical Characteristics table.

#### **General product characteristics**

#### 3.3 Thermal resistance

*Note:* This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to **www.jedec.org**.

#### Table 4Thermal resistance1)

| Parameter                | Symbol             |      | Value | S    | Unit | Note or                                         | Number  |

|--------------------------|--------------------|------|-------|------|------|-------------------------------------------------|---------|

|                          |                    | Min. | Тур.  | Max. |      | <b>Test Condition</b>                           |         |

| Junction to Case         | R <sub>thJC</sub>  | -    | _     | 10   | K/W  | 1)2)                                            | P_4.3.1 |

| Junction to Ambient 1s0p | R <sub>thJA1</sub> |      |       |      | K/W  | 1)3)                                            | P_4.3.3 |

| board                    |                    | _    | 61    | -    |      | T <sub>A</sub> = 85°C                           |         |

|                          |                    | -    | 56    | -    |      | $T_{\rm A} = 135^{\circ}{\rm C}$                |         |

| Junction to Ambient 2s2p | R <sub>thJA2</sub> |      |       |      | K/W  | 1)4)                                            | P_4.3.4 |

| board                    | (13/12             | _    | 45    | -    |      | $T_{\rm A} = 85^{\circ}{\rm C}$                 |         |

|                          |                    | _    | 43    | -    |      | T <sub>A</sub> = 85°C<br>T <sub>A</sub> = 135°C |         |

1) Not subject to production test, specified by design

2) Specified  $R_{thJC}$  value is simulated at natural convection on a cold plate setup (all pins and exposed pad are fixed to ambient temperature).  $T_A = 85^{\circ}$ C. Total power dissipation = 1.5 W

3) Specified R<sub>thJA</sub> value is according to Jedec JESD51-3 at natural convection on FR4 1s0p board. The product (chip+package) was simulated on a 76.2 × 114.3 × 1.5 mm board with 70 μm Cu, 300 mm<sup>2</sup> cooling area. Total power dissipation 1.5 W distributed statically and homogenously over all power stages

4) Specified R<sub>thJA</sub> value is according to Jedec JESD51-5,-7 at natural convection on FR4 2s2p board; The product (chip+package) was simulated on a 76.2 × 114.3 × 1.5 mm board with 2 inner copper layers (2 × 70 µm Cu, 2 × 35 µm Cu). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer. Total power dissipation 1.5 W distributed statically and homogenously over all power stages

#### **Internal supply**

### 4 Internal supply

This chapter describes the internal supply in its main parameters and functionality.

### 4.1 Description

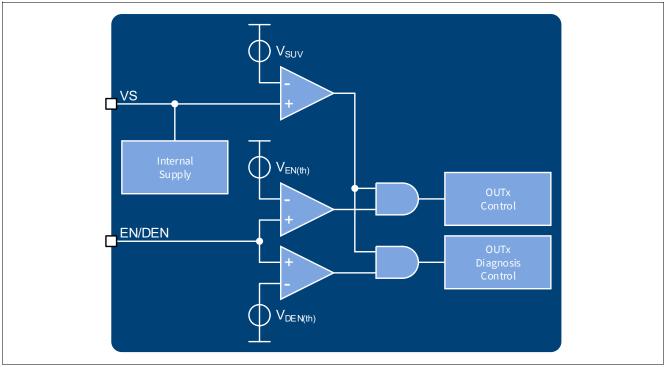

The internal supply principle is highlighted in the concept diagram of **Figure 3**.

If the voltage applied at the EN/DEN pin is below  $V_{\text{EN(th)}}$  the device enters sleep mode. In this state all internal functions are switched off and the current consumption is reduced to  $I_{\text{S(sleep)}}$ .

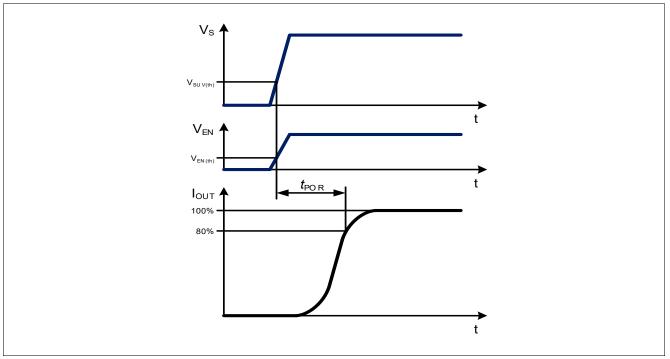

As soon as the voltage applied at the supply pin  $V_{\rm S}$  is above  $V_{\rm SUV(ON)}$  and the voltage applied at the EN/DEN pin is above  $V_{\rm EN(th)}$ , after the power-on reset time  $t_{\rm POR}$ , the device is ready to deliver output current from the output stages. The power on reset time  $t_{\rm POR}$  has to be taken into account also in relevant application conditions, i. e. with PWM control from VS or EN/DEN lines.

Also if PWM control is done via the PWM engine, the conditions  $V_{\rm S} > V_{\rm SUV(ON)}$  and  $V_{\rm EN} > V_{\rm EN(th)}$  must be fulfilled for PWM engine (and, therefore, output) activation.

Figure 3 Internal supply

Furthermore, as soon as the voltage applied at the supply pin VS is above  $V_{SUV(ON)}$  and the voltage applied to the EN/DEN pin  $V_{EN}$  is above  $V_{DEN(th)}$ , the device is ready to detect and report fault conditions via ERRN (error network pin) as described in **Chapter 6**.

To program outputs enable and diagnosis enable via EN/DEN pin there are several possibilities, like a resistor divider from VS to GND, a Zener diode from EN/DEN to VS and also a logic control pin (e.g. from a microcontroller output).

### Internal supply

## 4.2 Electrical characteristics internal supply and EN pin

#### Table 5 Electrical characteristics: Internal supply and EN pin

$T_{\rm J}$  = -40°C to +150°C;  $V_{\rm S}$  =5.5 V to 18 V;  $R_{\rm IN\_SET}$  = 10 kΩ; all voltages with respect to GND, positive current flowing into input and I/O pins, positive current flowing out from output pins (unless otherwise specified)

| Parameter                                                                                                                        | Symbol Value                |      | Value | S    | Unit | Note or                                                                                                                                                            | Number   |

|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------|-------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                                                                                                  |                             | Min. | Тур.  | Max. |      | <b>Test Condition</b>                                                                                                                                              |          |

| Current consumption, sleep mode                                                                                                  | I <sub>S(sleep)</sub>       | -    | 0.1   | 2    | μΑ   | $^{1)}V_{EN} = 0 V$<br>$T_{J} < 85^{\circ}C$<br>$V_{S} = 18 V$<br>$V_{OUTx} = 3.6 V$                                                                               | P_5.2.1  |

| Current consumption, active<br>mode (no fault)                                                                                   | / <sub>S(active)</sub>      | -    | 1.5   | 3    | mA   | $V_{EN} = 5.5 V$ $I_{IN_{SETx}} = 0 \mu A$ $T_{J} < 105^{\circ}C$ $V_{S} = 18 V$ $V_{OUTx} = 3.6 V$ $I_{PWM_{SET}} = I_{PWM_{RST}} =$ $100 \mu A$ $V_{PWMI} = 0 V$ | P_5.2.3  |

| Current consumption during<br>fault condition triggered<br>from another device sharing<br>ERRN bus (all channels<br>deactivated) | I <sub>S(fault, ERRN)</sub> | -    | -     | 850  | μΑ   | $V_{EN} = 5.5 V$<br>$T_{J} < 105^{\circ}C$<br>$V_{S} = 18 V$<br>$V_{ERRN} = 0 V$<br>$V_{OUTx} = 3.6 V$<br>D open<br>$V_{PWMI} = 0 V$                               | P_5.2.4  |

| Current consumption during<br>fault condition (all channels<br>deactivated)                                                      | I <sub>S(fault, OUT)</sub>  | -    | -     | 1.25 | mA   | $V_{EN} = 5.5 V$<br>$T_{J} < 105^{\circ}C$<br>$V_{S} = 18 V$<br>$V_{OUT1} = 0 V$<br>$V_{OUT2} = V_{OUT3} = 3.6 V$<br>D open<br>$V_{PWMI} = 0 V$                    | P_5.2.16 |

| Supply thresholds                                                                                                                |                             |      |       |      |      |                                                                                                                                                                    |          |

| Required supply voltage for output activation                                                                                    | V <sub>SUV(ON)</sub>        | -    | -     | 5.5  | V    | $V_{EN} = V_{S}$ $V_{OUTx} = 3 V$ $R_{IN\_SET} = 6.8 k\Omega$ $I_{OUTx} > 50\%$ $I_{OUTx(nom)}$                                                                    | P_5.2.5  |

| Required supply voltage for output deactivation                                                                                  | V <sub>SUV(OFF)</sub>       | 4.5  | -     | -    | V    | $V_{EN} = V_{S}$ $V_{OUTx} = 3 V$ $R_{IN\_SET} = 6.8 k\Omega$ $I_{OUTx} < 50\%$ $I_{OUTx(nom)}$                                                                    | P_5.2.6  |

| · · · · · · · ·                                                                                                                  |                             | 1    |       |      |      | 1)                                                                                                                                                                 |          |

Supply voltage activation

hysteresis: V<sub>SUV(ON)</sub> - V<sub>SUV(OFF)</sub>

P\_5.2.8

$\overline{}^{(1)}V_{\rm EN} > V_{\rm EN(th)}$

200

\_

\_

m٧

V<sub>SUV(hvs)</sub>

#### Internal supply

#### Table 5Electrical characteristics: Internal supply and EN pin (cont'd)

$T_{\rm J}$  = -40°C to +150°C;  $V_{\rm S}$  =5.5 V to 18 V;  $R_{\rm IN\_SET}$  = 10 kΩ; all voltages with respect to GND, positive current flowing into input and I/O pins, positive current flowing out from output pins (unless otherwise specified)

| Parameter                          | Symbol                  | Values |      |      | Unit | Note or                                                                                                          | Number   |

|------------------------------------|-------------------------|--------|------|------|------|------------------------------------------------------------------------------------------------------------------|----------|

|                                    |                         | Min.   | Тур. | Max. |      | <b>Test Condition</b>                                                                                            |          |

| EN pin                             |                         |        |      |      |      |                                                                                                                  |          |

| EN outputs enable threshold        | V <sub>EN(th)</sub>     | 1.4    | 1.65 | 1.8  | V    | $V_{\rm S} = 5.5 V$ $V_{\rm PS} = 2 V$ $R_{\rm IN\_SET} = 6.8 k\Omega$ $I_{\rm OUTx} = 50\%$ $I_{\rm OUTx(nom)}$ | P_5.2.9  |

| DEN diagnosis enable<br>threshold  | V <sub>DEN(th)</sub>    | 2.4    | 2.5  | 2.8  | V    | V <sub>S</sub> = 5.5 V                                                                                           | P_5.2.11 |

| DEN diagnosis enable<br>hysteresis | V <sub>DEN(hys)</sub>   | -      | 120  | -    | mV   | $^{1)}R_{\rm IN\_SET} = 6.8 \rm k\Omega$                                                                         | P_5.2.12 |

| EN/DEN pull-down current           | I <sub>EN/DEN(PD)</sub> | -      | -    | 60   | μA   | $^{1)}V_{\rm S} > 8 \rm V$<br>$V_{\rm EN/DEN} = 2.8 \rm V$                                                       | P_5.2.17 |

| EN/DEN pull-down current           | I <sub>EN/DEN(PD)</sub> | -      | -    | 110  | μA   | $^{1)}V_{\rm S} > 8 \rm V$<br>$V_{\rm EN/DEN} = 5.5 \rm V$                                                       | P_5.2.14 |

| EN/DEN pull-down current           | I <sub>EN/DEN(PD)</sub> | -      | -    | 350  | μA   | ${}^{1)}V_{\rm S} > 8 \rm V$ $V_{\rm EN/DEN} = V_{\rm S}$                                                        | P_5.2.15 |

| Timing                             |                         |        |      |      |      |                                                                                                                  |          |

| Power on reset delay time          | t <sub>POR</sub>        | -      | -    | 25   | μs   | <sup>1)</sup> $V_{\rm S}$ rising from 0 V<br>to 13.5 V<br>$V_{\rm OUTx}$ = 3.6 V<br>$R_{\rm IN\_SET}$ = 6.8 kΩ   | P_5.2.13 |

$I_{OUTx} = 80\%$  $I_{OUTx(nom)}$

1) Not subjected to production test: specified by design

### 5 Power stages

The three output stages are realized as high-side current sources with an output current up to 80mA. During off state the leakage current at the output stages is minimized in order to prevent a slightly glowing LED. The maximum output current is limited by the power dissipation and used PCB cooling areas. For an operating output current control loop, the supply and output voltages have to be considered according to the following parameters:

- Required supply voltage for current control  $V_{S(CC)}$

- Voltage drop over through the output stage during current control V<sub>PSx(CC)</sub>

- Required output voltage for current control V<sub>OUTx(CC)</sub>

### 5.1 Protection

The device provides embedded protective functions, which are designed to prevent IC damage under fault conditions described in this datasheet. Fault conditions are considered as "outside" normal operating range. Protective functions are not designed for continuous nor for repetitive operations.

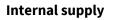

### 5.1.1 Thermal protection

A thermal protection circuitry is integrated in the device. It is realized by a temperature monitoring of the output stages.

As soon as the junction temperature exceeds the current reduction temperature threshold  $T_{J(CRT)}$  the output current can be reduced by the device by reducing the IN\_SETx reference voltage  $V_{IN\_SETx(ref)}$ . This feature greatly helps to avoid LEDs flickering during static output overload conditions. Furthermore, it helps to protect the LEDs, which are mounted thermally close to the device, against overtemperature. If the device temperature still increases, the three output currents decrease close to 0 A. As soon as the device cools down the output currents rise again.

Figure 5 Output current reduction at high temperature (qualitative diagram)

Note: It is assumed that a configuration resistor  $R_{SET}$  is applied from IN\_SET to GND, and not a current source, to make the protection effective.

### 5.1.2 Reverse battery protection

The device has an integrated reverse battery protection feature. This feature protects the driver IC itself and, potentially, also connected LEDs. The output reverse current is limited to  $I_{OUTx(REV)}$  by the reverse battery protection.

### 5.2 Output configuration via IN\_SET, OUT\_SET and PWMI pins

Outputs current can be defined via IN\_SET and OUT\_SET (to drive additional devices without further external components) pins.

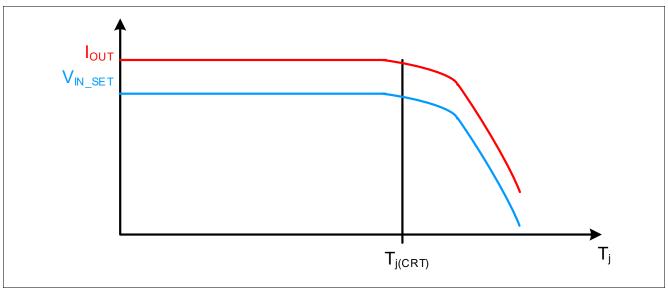

### 5.2.1 IN\_SET pin

The IN\_SET pin is a multiple function pin for the output current definition and input control.

Output currents definition and analog dimming control can be done defining accordingly the IN\_SET current.

Figure 6 IN\_SET pin block diagram

### 5.2.2 Output current adjustment via R<sub>SET</sub>

The output current for the channels can be defined connecting a low power resistor ( $R_{SET}$ ) between the IN\_SET pin and GND. The dimensioning of the resistor can be done using the formula:

$$I_{OUTx} = k_x \cdot I_{IN\_SET} = k_x \cdot V_{IN\_SET(ref)} / R_{SET}$$

(5.1)

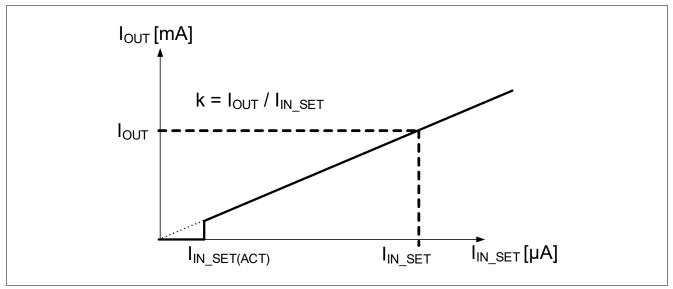

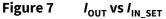

The gain factor  $k_x$  (defined as the ratio  $I_{OUTx}/I_{IN\_SET}$ ) is graphically described in Figure 7.

The current through the  $R_{\text{SETx}}$  is defined by the resistor itself and the reference voltage  $V_{\text{IN}_{\text{SET}(\text{ref})}}$ , which is applied to the IN\_SET pin when the device is supplied and the channel enabled.

### 5.2.3 Output control via IN\_SET

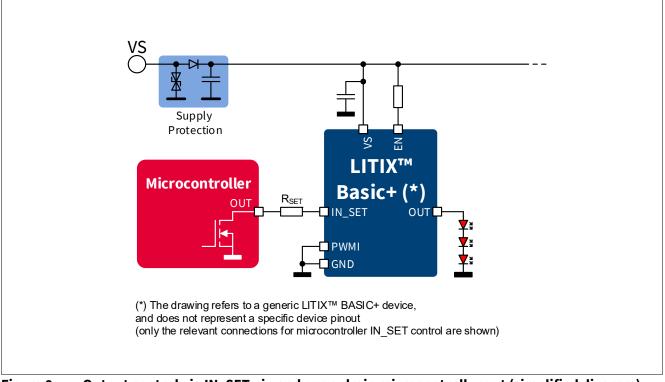

The IN\_SET pin can be connected via  $R_{SET}$  to the open-drain output of a microcontroller or to an external NMOS transistor as described in **Figure 9**. This signal can be used to turn off the relative output stages of the IC.

A minimum IN\_SET current of  $I_{IN\_SET(ACT)}$  is required to turn on the output stages. This feature is implemented to prevent glowing of LEDs caused by leakage currents on the IN\_SET pin, see again **Figure 7** for details.

#### Figure 9 Output control via IN\_SET pin and open-drain microcontroller out (simplified diagram)

### 5.2.4 IN\_SET pin behavior during device fault management

If a fault condition arises on the channel controlled by the IN\_SET pin, once the D-pin reaches the high level threshold  $V_{D(th)}$ , the current of the IN\_SET pin is reduced to  $I_{IN\_SET(fault)}$ , in order to minimise the current consumption of the whole device under fault condition (detailed description is in the load diagnosis section, **Chapter 6**).

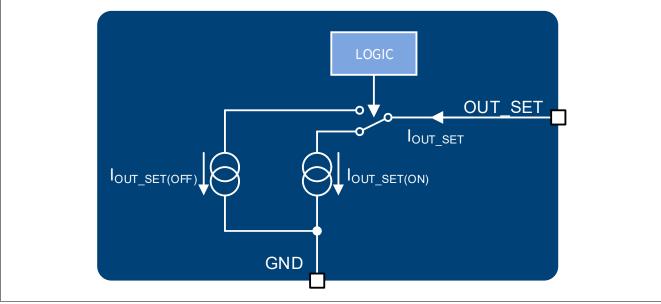

### 5.2.5 OUT\_SET pin

The OUT\_SET pin, mirroring the IN\_SET current defined by the external resistor  $R_{SET}$ , can be used to define the IN\_SET current of an additional companion device.

If minimum IN\_SET activation current  $I_{\text{IN}_{\text{SET}(act)}}$  is not reached or if the D-pin reaches the high level threshold  $V_{\text{D}(th)}$  the OUT\_SET current is reduced to  $I_{\text{OUT}_{\text{SET}(\text{OFF})}}$ . This allows to drive other devices via OUT\_SET, even when digital dimming is required, without external components (see application drawing example in **Chapter 8**).

#### **Power stages**

Figure 10 OUT\_SET pin block diagram

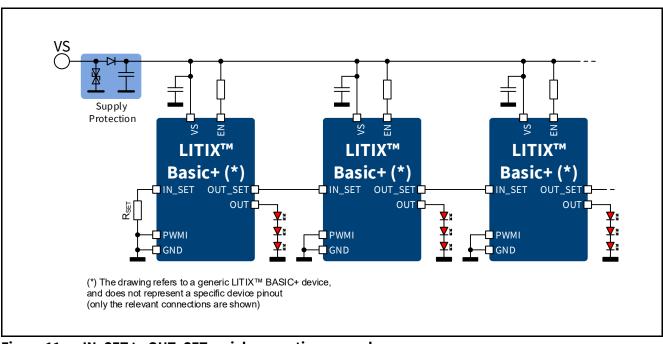

Figure 11 IN\_SET to OUT\_SET serial connection example

### 5.2.6 Direct control of PWMI

PWMI input can be controlled by the PWMO output of another device of LITIX<sup>™</sup> Basic+ family or, alternatively, a push-pull output stage of a microcontroller: the host device decides the digital dimming characteristics by applying the proper control cycle in order to set the "on"/"off" timing, according to the chosen dimming function.

### 5.2.7 Timing diagrams

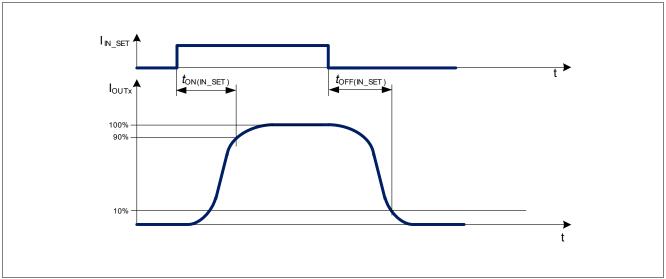

In the following diagrams (**Figure 12**, **Figure 14**) the influences of different driving inputs on output activation delays are shown.

#### **Power stages**

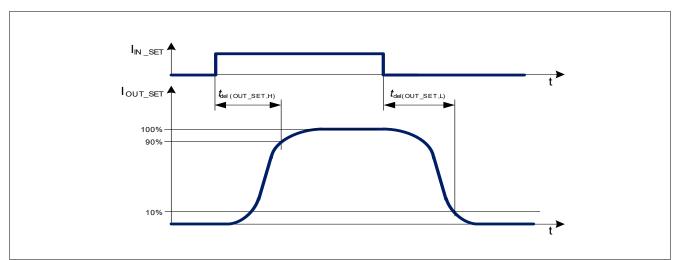

Figure 12 IN\_SET turn on and turn off delay timing diagram

Figure 13 IN\_SET to OUT\_SET activation and deactivation delay timing diagram

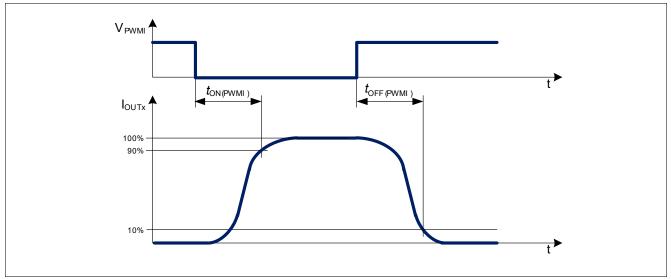

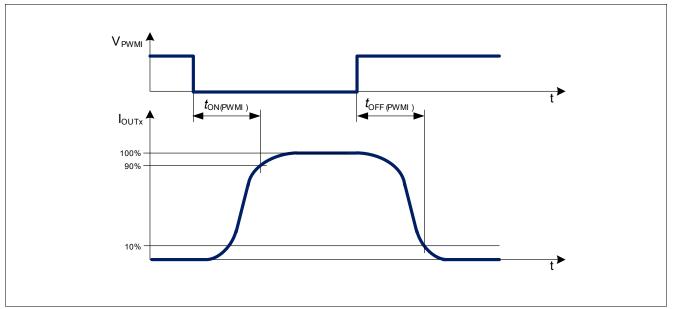

Figure 14 PWMI turn on and turn off timing diagram

#### **Power stages**

### 5.3 Electrical characteristics power stage

#### Table 6 Electrical characteristics: Power stage

$T_{\rm J}$  = -40°C to +150°C;  $V_{\rm S}$  =5.5 V to 18 V;  $R_{\rm IN\_SET}$  = 10 kΩ; all voltages with respect to GND, positive current flowing into input and I/O pins, positive current flowing out from output pins (unless otherwise specified)

| Parameter               | Symbol                  | Values |      |      | Unit | Note or                                                                                                                                                       | Number   |

|-------------------------|-------------------------|--------|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                         |                         | Min.   | Тур. | Max. |      | <b>Test Condition</b>                                                                                                                                         |          |

| Output leakage currents | I <sub>OUTx(leak)</sub> | -      | -    | 3    | μΑ   | <sup>1)</sup> $V_{ENx} = 5.5 V$<br>$I_{IN_{SETx}} = 0 \mu A$<br>$V_{OUTx} = 2.5 V$<br>$T_{J} = 85^{\circ}C$                                                   | P_6.5.1  |

| Output leakage currents | I <sub>OUTx(leak)</sub> | _      | _    | 7    | μΑ   | <sup>1)</sup> $V_{ENx} = 5.5 V$<br>$I_{IN_SETx} = 0 \mu A$<br>$V_{OUTx} = 2.5 V$<br>$T_J = 150°C$                                                             | P_6.5.59 |

| Reverse output currents | I <sub>OUTx(rev)</sub>  | -      | _    | 3    | μΑ   | $^{1)}V_{EN} = V_{s}$<br>$V_{Sx} = -18 V$<br>Output load: LED<br>with break down<br>voltage < - 0.6 V                                                         | P_6.5.2  |

| Output current accuracy | 1                       |        | I    |      |      |                                                                                                                                                               |          |

| Output current accuracy | K <sub>LTx</sub>        | 284    | 300  | 316  | -    | <sup>1)</sup> $T_{J} = 25 115^{\circ}C$<br>$V_{S} = 8 18 V$<br>$V_{PSx} = 2 V$<br>$I_{IN_{SETx}} = 33 \mu A$                                                  | P_6.5.30 |

| Output current accuracy | K <sub>ALLx</sub>       | 281    | 300  | 319  | -    | <sup>1)</sup> $T_{J}$ = -40 115°C<br>$V_{S}$ = 8 18 V<br>$V_{PSx}$ = 2 V<br>$I_{IN_{SETx}}$ = 33 µA                                                           | P_6.5.31 |

| Output current accuracy | K <sub>LTx</sub>        | 287    | 300  | 313  | -    | <sup>1)</sup> $T_{\rm J} = 25 115^{\circ}{\rm C}$<br>$V_{\rm S} = 8 18 {\rm V}$<br>$V_{\rm PSx} = 2 {\rm V}$<br>$I_{\rm IN_{\rm SETx}} = 66 {\rm \mu}{\rm A}$ | P_6.5.32 |

| Output current accuracy | K <sub>ALLx</sub>       | 284    | 300  | 316  | -    | <sup>1)</sup> $T_{J}$ = -40 115°C<br>$V_{S}$ = 8 18 V<br>$V_{PSx}$ = 2 V<br>$I_{IN_{SETx}}$ = 66 µA                                                           | P_6.5.33 |

| Output current accuracy | K <sub>LTx</sub>        | 290    | 300  | 310  | _    | <sup>1)</sup> $T_{J} = 25 115^{\circ}C$<br>$V_{S} = 8 18 V$<br>$V_{PSx} = 2 V$<br>$I_{IN_{SETx}} = 200 \mu\text{A}$                                           | P_6.5.34 |

| Output current accuracy | K <sub>ALLx</sub>       | 287    | 300  | 313  | -    | <sup>1)</sup> $T_{J}$ = -40 115°C<br>$V_{S}$ = 8 18 V<br>$V_{PSx}$ = 2 V<br>$I_{IN\_SETx}$ = 200 µA                                                           | P_6.5.35 |

#### **Power stages**

#### Table 6Electrical characteristics: Power stage (cont'd)

$T_{\rm J}$  = -40°C to +150°C;  $V_{\rm S}$  =5.5 V to 18 V;  $R_{\rm IN\_SET}$  = 10 kΩ; all voltages with respect to GND, positive current flowing into input and I/O pins, positive current flowing out from output pins (unless otherwise specified)

| Parameter                                                                                                    | Symbol                |                                 | Values |      |    | Note or                                                                                                                                                                                        | Number   |

|--------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------------|--------|------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                                                                              |                       | Min.                            | Тур.   | Max. |    | <b>Test Condition</b>                                                                                                                                                                          |          |

| Required voltage drop<br>during current control<br>$V_{PS(CC)} = V_S - V_{OUTx}$                             | V <sub>PSx(CC)</sub>  | 1.0                             | -      | -    | V  | $^{2)}V_{\rm S} = 818 \text{ V}$<br>$I_{\rm OUTx} > 90\% \text{ of}$<br>$K_{\rm x(typ)}^{*}I_{\rm IN\_SET}$                                                                                    | P_6.5.36 |

| Required voltage drop<br>during current control<br>V <sub>PSx(CC)</sub> = V <sub>S</sub> - V <sub>OUTx</sub> | V <sub>PSx(CC)</sub>  | 0.65                            | -      | -    | V  | <sup>2)</sup> $V_{\rm S} = 8 18 \text{ V}$<br>$I_{\rm IN_SET} = 133 \mu\text{A}$<br>$I_{\rm OUTx} > 90\% \text{ of}$<br>$K_{\rm x(typ)} * I_{\rm IN_SET}$<br>$T_{\rm J} = -40^{\circ}\text{C}$ | P_6.5.37 |

| Required voltage drop<br>during current control<br>V <sub>PSx(CC)</sub> = V <sub>S</sub> - V <sub>OUTx</sub> | V <sub>PSx(CC)</sub>  | 0.75                            | -      | -    | V  | $^{2)}V_{\rm S} = 818 V$<br>$I_{\rm IN_SET} = 133 \mu A$<br>$I_{\rm OUTx} > 90\% \text{ of}$<br>$K_{\rm x(typ)} * I_{\rm IN_SET}$<br>$T_{\rm J} = 25^{\circ} \text{C}$                         | P_6.5.38 |

| Required voltage drop<br>during current control<br>V <sub>PSx(CC)</sub> = V <sub>S</sub> - V <sub>OUTx</sub> | V <sub>PSx(CC)</sub>  | 0.85                            | -      | -    | V  | $^{2)}V_{S} = 818V$<br>$I_{IN_{SET}} = 133 \mu A$<br>$I_{OUTx} > 90\% \text{ of}$<br>$K_{x(typ)}*I_{IN_{SET}}$<br>$T_{J} = 150^{\circ}\text{C}$                                                | P_6.5.39 |

| Required supply voltage for current control                                                                  | V <sub>S(CC)</sub>    | 5.5                             | -      | -    | V  | $V_{\rm EN} = 5.5 V$ $V_{\rm OUT} = 3 V$ $R_{\rm IN_{SET}} = 6.8 k\Omega$ $I_{\rm OUT} > 90\% \text{ of}$ $K_{\rm x}*I_{\rm IN_{SET}}$                                                         | P_6.5.40 |

| Required output voltage for current control                                                                  | V <sub>OUT(CC)</sub>  | 1.4                             | -      | -    | V  | $V_{\rm S} = 818 V$<br>$I_{\rm OUT} > 90\% \text{ of}$<br>$K_{\rm x}*I_{\rm IN\_SET}$                                                                                                          | P_6.5.41 |

| Current reduction<br>temperature threshold                                                                   | T <sub>J(CRT)</sub>   | -                               | 140    | -    | °C | 1)                                                                                                                                                                                             | P_6.5.44 |

| Output current during<br>current reduction at high<br>temperature                                            | I <sub>OUT(CRT)</sub> | 85% of<br>I <sub>OUT(typ)</sub> | -      | -    | mA | <sup>1)</sup> <i>T</i> <sub>J</sub> = 150°C                                                                                                                                                    | P_6.5.45 |

1) Not subjected to production test: specified by design

2) In these test conditions, the parameter  $K_{(typ)}$  represents the typical value of output current accuracy.

#### **Power stages**

### 5.4 Electrical characteristics IN\_SET, OUT\_SET and PWMI pins for output settings

#### Table 7 Electrical characteristics: IN\_SET, OUT\_SET and PWMI pins

$T_{\rm J}$  = -40°C to +150°C;  $V_{\rm S}$  =5.5 V to 18 V;  $R_{\rm IN\_SET}$  = 10 kΩ; all voltages with respect to GND, positive current flowing into input and I/O pins, positive current flowing out from output pins (unless otherwise specified)

| Parameter                        | Symbol                                           |       | Value | s T   | Unit | Note or<br>Test Condition                                                                                                                               | Number   |

|----------------------------------|--------------------------------------------------|-------|-------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                  |                                                  | Min.  | Тур.  | Max.  |      |                                                                                                                                                         |          |

| IN_SET reference voltage         | V <sub>IN_SET(ref)</sub>                         | 1.195 | 1.22  | 1.245 | V    | $^{1)}V_{EN} = 5.5 V$<br>$T_{J} = 25^{\circ}C$                                                                                                          | P_6.6.1  |

| IN_SET reference voltage         | V <sub>IN_SET(ref)</sub>                         | 1.184 | 1.22  | 1.256 | V    | $^{1)}V_{EN} = 5.5 V$<br>$T_{J} = -40 115^{\circ}C$                                                                                                     | P_6.6.17 |

| IN_SET output activation current | I <sub>IN_SET(ACT)</sub>                         | -     | -     | 15    | μΑ   | $V_{EN} = 5.5 V$ $V_{PSx} = 3 V$ $I_{OUTx} > 50\% \text{ of}$ $K_{x(typ)} * I_{IN\_SET}$                                                                | P_6.6.2  |

| OUT_SET output current matching  | $\Delta I_{\rm OUT\_SET(ON)}/I_{\rm I}$<br>n_set | -4    | -     | 4     | %    | $V_{\rm S} = 8 \text{ V to } 18 \text{ V}$<br>$V_{\rm OUT\_SET} = 1.2 \text{ V}$<br>$I_{\rm IN\_SET} = 267 \mu\text{A}$                                 | P_6.6.3  |

| Timing                           | 1                                                | T     |       |       |      |                                                                                                                                                         | 1        |

| IN_SET turn on time              | t <sub>on(in_set)</sub>                          | -     | -     | 20    | μs   | ${}^{1)2)}V_{S} = 13.5 V$ $V_{PSx} = 4 V$ $I_{IN_{SET}} rising from 0$ to 180 µA $I_{OUTx} = 90\% \text{ of}$ $K_{x}^{*}I_{IN_{SET}}$                   | P_6.6.8  |

| IN_SET turn off time             | t <sub>off(in_set)</sub>                         | -     | -     | 10    | μs   | ${}^{1)2)}V_{S} = 13.5 V$ $V_{PSx} = 4 V$ $I_{IN\_SET} \text{ falling from}$ $180 \text{ to } 0 \mu A$ $I_{OUTx} = 10\% \text{ of}$ $K_{x}*I_{IN\_SET}$ | P_6.6.9  |

| OUT_SET activation time          | t <sub>del(OUT_SET,H)</sub>                      | -     | -     | 5     | μs   | $^{1)3)}V_{\rm S} = 13.5 \text{ V}$<br>$I_{\rm IN\_SET}$ rising from 0<br>to 180 $\mu$ A<br>$I_{\rm OUT\_SET} = 90\%$ of<br>$I_{\rm IN\_SET}$           | P_6.6.10 |

| OUT_SET deactivation time        | t <sub>del(OUT_SET,L)</sub>                      | -     | -     | 5     | μs   | $^{1)3)}V_{\rm S} = 13.5 \text{ V}$<br>$I_{\rm IN\_SET}$ falling from<br>180 to 0 $\mu$ A<br>$I_{\rm OUT\_SET} = 10\%$ of<br>$I_{\rm IN\_SET}$          | P_6.6.11 |

#### **Power stages**

#### Table 7Electrical characteristics: IN\_SET, OUT\_SET and PWMI pins (cont'd)

$T_{\rm J}$  = -40°C to +150°C;  $V_{\rm S}$  =5.5 V to 18 V;  $R_{\rm IN\_SET}$  = 10 kΩ; all voltages with respect to GND, positive current flowing into input and I/O pins, positive current flowing out from output pins (unless otherwise specified)

| Parameter          | Symbol                 |      | Value | 5    | Unit | Note or<br>Test Condition                                                                                                                                                                                                                        | Number   |

|--------------------|------------------------|------|-------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                    |                        | Min. | Тур.  | Max. |      |                                                                                                                                                                                                                                                  |          |

| PWMI turn on time  | t <sub>on(pwmi)</sub>  | _    | -     | 15   | μs   | $^{1)4)}V_{\rm S} = 8 \text{ V to } 18 \text{ V}$<br>$V_{\rm EN} = 5.5 \text{ V}$<br>$V_{\rm PWMI}$ falling from<br>5  V to  0  V<br>$I_{\rm OUTx} = 90\% \text{ of}$<br>$K_{\rm x}^{*}I_{\rm IN\_SET}$<br>$T_{\rm J} = -40 115^{\circ}\text{C}$ | P_6.6.12 |

| PWMI turn off time | t <sub>off(pwmi)</sub> | -    | -     | 10   | μs   | <sup>1)4)</sup> $V_{\rm S} = 8$ V to 18 V<br>$V_{\rm EN} = 5.5$ V<br>$V_{\rm PWMI} = 0$ rising<br>from 0 V to 5 V<br>$I_{\rm OUTx} = 10\%$ of<br>$K_{\rm x}*I_{\rm IN\_SET}$<br>$T_{\rm J} = -40$ 115°C                                          | P_6.6.13 |

1) Not subjected to production test: specified by design

2) Refer to Figure 12

3) Refer to Figure 13

4) Refer to Figure 14

Load diagnosis

### 6 Load diagnosis

#### 6.1 Error management via ERRN and D-pins

Several diagnosis features are integrated in the TLD2141-3EP:

- Open load detection (OL) for any of the output channels OUTx.

- Short circuit OUTx-GND (SC) for any of the output channels OUTx.

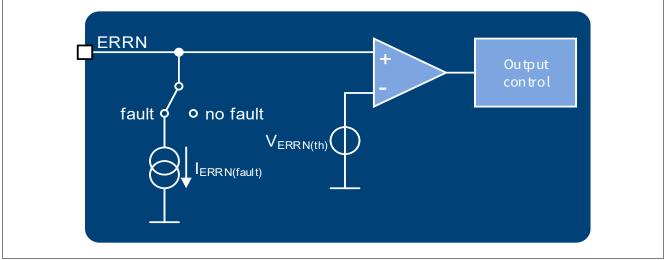

### 6.1.1 ERRN pin

#### Figure 15 ERRN pin (block diagram)

The device is able to report a detected failure in one of its driven loads and react to a fault detected by another LED driver in the system if a shared error network is implemented (i. e. driving LED chains of the same light function). This is possible with the usage of an external pull-up resistor, allowing multiple devices to share the open drain diagnosis output pin ERRN. All devices sharing the common error network are capable to detect the fault from any of the channels driven by the LITIX<sup>™</sup> Basic+ LED drivers and, if desired, to switch multiple loads off.

#### Load diagnosis

#### Figure 16 Shared error network principle between LITIX<sup>™</sup> Basic+ family devices

When one of the channels is detected to be under fault conditions (for, at least, a filter time  $t_{fault}$ ), the opendrain ERRN pin sinks a pull-down current  $I_{ERRN(fault)}$  toward GND. Therefore an active low state can be detected at ERRN pin when  $V_{ERRN} < V_{ERRN(fault)}$  and if this condition is reached, provided the proper setup of the delay pin D, all the channels are switched off. Similarly, when the fault is removed, ERRN pin is put back in high impedance state, and the channels reactivation procedure can be completed once D-pin voltage is below the value  $V_{D(th)}$ , as illustrated in the timing diagrams in this chapter.

#### Load diagnosis

### 6.1.2 D-pin

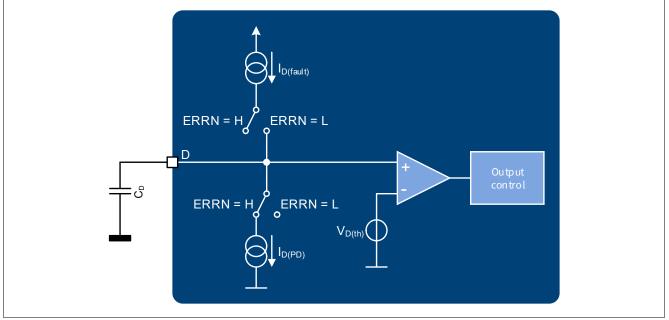

Figure 17 D-pin (block diagram).

The D-pin is designed for 2 main purposes:

- To react to error conditions in LED arrays according to the implemented fault management policy, in systems where multiple LED chains are used for a given light function.

- To extend the channels deactivation delay time of a value  $t_D$ , adding a small signal capacitor from the Dpin to GND. In this way, an unstable or noisy fault condition may be prevented from switching off all the channels of a given light function (i.e. driven by several driver ICs sharing the same error network).

The functionality of the D-pin is shown in the **Figure 17** simplified block diagram:

If one LED within one chain fails in open load condition or one of the device outputs are shorted to GND, the respective LED chain is off. Different automotive applications require a complete deactivation of a light function, if the desired brightness of the function (LED array) can not be achieved due to an internal error condition.

In normal operative status (no fault) a pull-down current  $I_{D(PD)}$  is sunk from the D-pin to GND. If there is a fault condition (for, at least, a filter time  $t_{fault}$ ) in one of the LED channels driven by the IC or in any of the devices sharing the same ERRN error network line, a pull-up current  $I_{D(fault)}$  is instead sourced from the D-pin. As a consequence, if a capacitive or open load is applied at this pin, its voltage starts rising.

When  $V_{D(th)}$  is reached at D-pin, all the channels driven by the device are switched off and if other devices share the same ERRN and D-pins nodes, all the devices turn their outputs off.

Alternatively, if the D-pin is tied to GND, only the channel that has been detected with a fault is safely deactivated.

#### Load diagnosis

The capacitor value used at the D-pin,  $C_D$ , sets the delay times  $t_{D(set/reset)}$  according to the following equations:

$$t_{D(set)} = \frac{C_D \cdot V_{D(th)}}{I_{D(fault)}}$$

(6.1)

$$t_{D(reset)} = \frac{C_D \cdot \left(V_{D(CL)} - V_{D(th)}\right)}{I_{D(PD)}}$$

(6.2)

### 6.2 Open Load (OL) and short OUTx to GND (SC)

The behavior of the device during overload conditions that lead to an excess of internal heating up to overtemperature condition, is already described in **Chapter 5**.

Open load (OL) and OUTx shorted to GND (SC) diagnosis features are also integrated in the TLD2141-3EP.

An open load condition is detected if the voltage drop over one of the output stages  $V_{PSx}$  is below the threshold  $V_{PSx(OL)}$  at least for a filter time  $t_{fault}$ .

A short to GND condition is detected if the voltage of one output stages  $V_{OUTx}$  is below the threshold  $V_{OUTx(SC)}$  at least for a filter time  $t_{fault}$ .

### 6.2.1 Fault management (D-pin open or connected with a capacitor to GND)

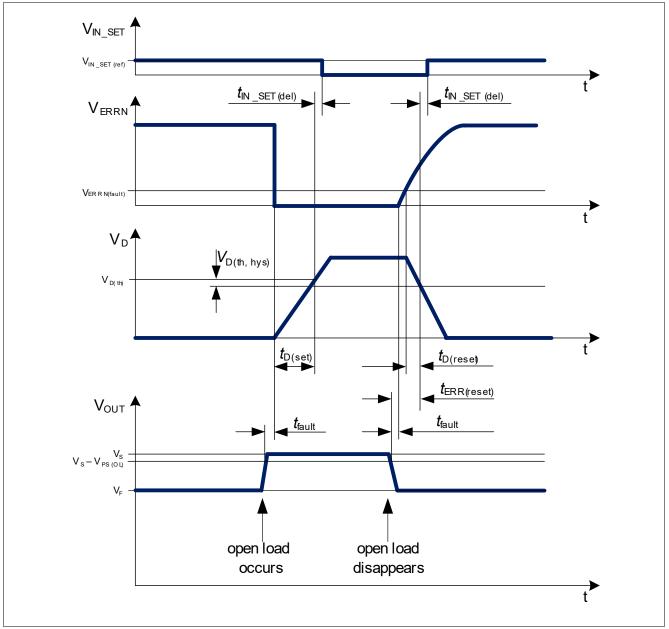

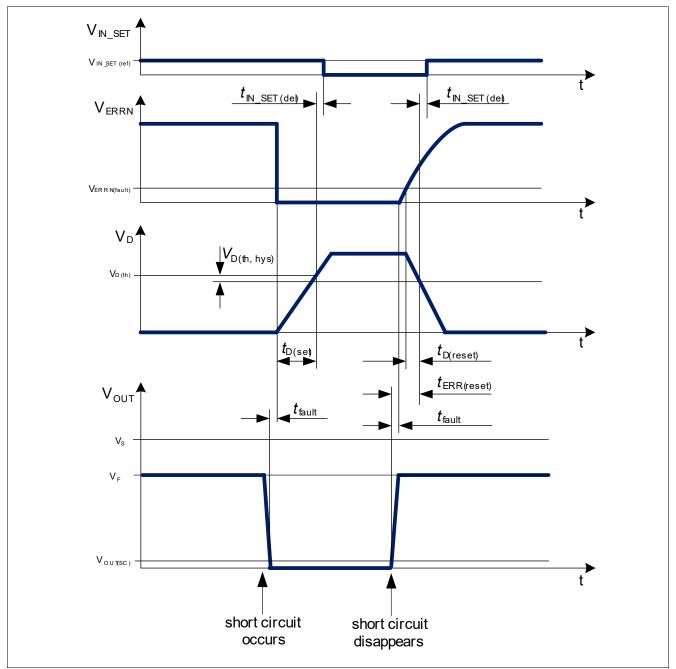

With D-pin open or connected with a capacitor to GND configuration, it is possible to switch off all the channels which share a common error network, without the need of an auxiliary microcontroller. For more details refer also to the timing diagram of **Figure 18**, **Figure 19**.

If there is an OL or SC condition on one of the outputs, a pull-up current  $I_{OUT(fault)}$  then flows out from the affected channel, replacing the configured output current (but limited by the actual load impedance, e.g. reduced to zero with an ideal open load). Under these conditions, the ERRN pin starts sinking a current  $I_{ERRN(fault)}$  toward GND and (with proper dimensioning of the external pull-up resistor) reaches a voltage level below  $V_{ERRN(fault)}$ .

After  $t_{D(set)}$ , the voltage  $V_{D(th)}$  is reached at D-pin, the PWMO pin is pulled down and the IN\_SET goes in a weak pull-down state with a current consumption  $I_{IN\_SET(fault)}$  after an additional latency time  $t_{IN\_SET(del)}$ . The ERRN low voltage can also be used as input signal for a microcontroller to perform the desired diagnosis policy.

The OL and SC error conditions are not latched: as soon as the fault condition is no longer present (at least for a filter time  $t_{fault}$ ) ERRN goes back to high impedance. When its voltage is above  $V_{ERRN(fault)}$ , the D-pin voltage starts decreasing and after  $t_{D(reset)}$  goes below ( $V_{D(th)} - V_{D(th,hys)}$ ). Then the IN\_SET voltage up to  $V_{IN\_SET(ref)}$ , again after a time  $t_{IN\_SET(del)}$ : at this point, the output stages are activated again. The total time between the fault removal and the IN\_SET reactivation  $t_{ERR(reset)}$  is extended by an additional latency which depends on the external ERRN pin pull-up and filter circuitry.

#### Load diagnosis

Figure 18 Open load condition timing diagram example (D-pin unconnected or connected to external capacitor to GND, V<sub>F</sub> represents the typical forward voltage of the output load)

#### Load diagnosis

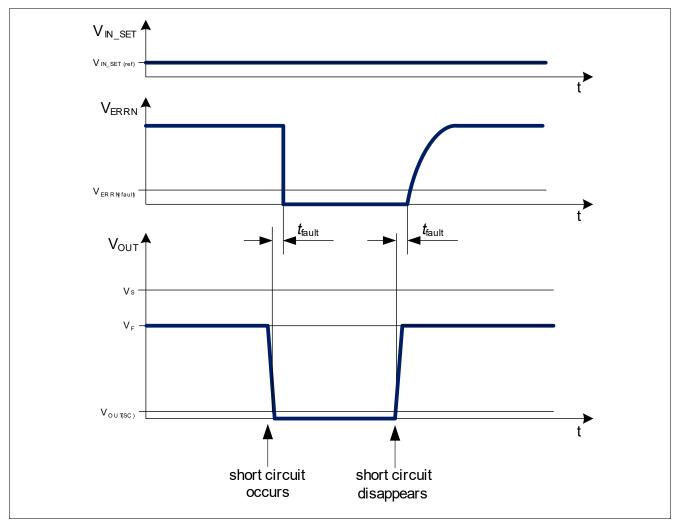

Figure 19 Short circuit to GND condition timing diagram example (D-pin not connected or connected to external capacitor to GND, V<sub>Exvz</sub> represents the forward voltage of the output loads)

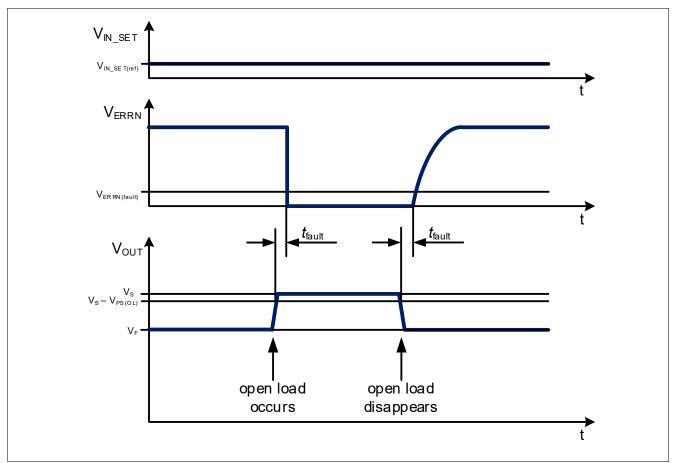

### 6.2.2 Fault management (D-pin connected to GND)

With D-pin connected to GND configuration, it is possible to deactivate only the channel under fault conditions, still sharing ERRN pin in a common error network with other devices of LITIX<sup>™</sup> Basic+ family.

If there is fault condition on one of the outputs, a pull-up current  $I_{OUT(fault)}$  flows out from the affected channel, replacing the configured output current (but limited by the actual load impedance, e.g. reduced to zero with an ideal open load). Under fault conditions the ERRN pin starts sinking a current  $I_{ERRN(fault)}$  to ground and the voltage level on this pin will drop below  $V_{ERRN(fault)}$  if the external pull-up resistor is properly dimensioned. The ERRN low voltage can also be used as input signal for a  $\mu$ C to perform the desired diagnosis policy.

#### Load diagnosis

The fault status is not latched: as soon as the fault condition is no longer present (at least for a filter time  $t_{\text{fault}}$ ), ERRN goes back to high impedance and, once its voltage is above  $V_{\text{ERRN(fault)}}$ , finally the output stages are activated again.

Examples of open load or short to GND diagnosis with D-pin open or connected to GND are shown in the timing diagrams of **Figure 20** and **Figure 21**.

Figure 20 Open load condition timing diagram example (D-pin connected to GND, V<sub>F</sub> represents the forward voltage of the output load)

#### Load diagnosis

Figure 21 Short circuit condition timing diagram example (D-pin connected to GND, V<sub>F</sub> represents the forward voltage of the output load)

### 6.3 Electrical characteristics: Load diagnosis and Overload management

#### Table 8 Electrical Characteristics: Fault management

$T_{\rm J}$  = -40°C to +150°C;  $V_{\rm S}$  =5.5 V to 18 V;  $R_{\rm IN\_SET}$  = 10 kΩ; all voltages with respect to GND, positive current flowing into input and I/O pins, positive current flowing out from output pins (unless otherwise specified)

| Parameter            | Symbol                     |      | Values |      |    | Note or                                                                                                                                                     | Number  |

|----------------------|----------------------------|------|--------|------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|                      |                            | Min. | Тур.   | Max. |    | <b>Test Condition</b>                                                                                                                                       |         |

| IN_SET fault current | I <sub>IN_SET(fault)</sub> | -    | -      | 10   | μΑ | <sup>1)</sup> $V_{\rm S} > 8 V$<br>$V_{\rm OUT} = 3.6 V$<br>$V_{\rm ERRN} = 0 V$<br>$V_{\rm IN\_SET} = 1 V$<br>D open<br>$V_{\rm EN} > V_{\rm DEN(th,max)}$ | P_7.5.1 |

| ERRN fault current   | I <sub>ERRN(fault)</sub>   | 2    | -      | -    | mA | ${}^{1)}V_{\rm S} > 8 V$ $V_{\rm ERRN} = 0.8 V$ Fault condition $V_{\rm EN} > V_{\rm DEN(th,max)}$                                                          | P_7.5.2 |

#### Load diagnosis

#### Table 8 Electrical Characteristics: Fault management (cont'd)

$T_{\rm J}$  = -40°C to +150°C;  $V_{\rm S}$  =5.5 V to 18 V;  $R_{\rm IN\_SET}$  = 10 kΩ; all voltages with respect to GND, positive current flowing into input and I/O pins, positive current flowing out from output pins (unless otherwise specified)

| Parameter                                                                 | Symbol                   |      | Value | s    | Unit | Note or                                                                                                                | Number   |

|---------------------------------------------------------------------------|--------------------------|------|-------|------|------|------------------------------------------------------------------------------------------------------------------------|----------|

|                                                                           |                          | Min. | Тур.  | Max. |      | <b>Test Condition</b>                                                                                                  |          |

| ERRN input threshold                                                      | V <sub>ERRN(th)</sub>    | 0.8  | -     | 2.0  | V    | $^{1)}V_{\rm S} > 8 \rm V$                                                                                             | P_7.5.3  |

| OL detection threshold                                                    | V <sub>PS(OL)</sub>      | 0.2  | -     | 0.4  | V    | $V_{\rm S} > 8 V$<br>$V_{\rm EN} > V_{\rm DEN(th, max)}$                                                               | P_7.5.5  |

| SC detection threshold                                                    | V <sub>OUT(SC)</sub>     | 0.8  | -     | 1.35 | V    | $V_{\rm S} > 8 V$<br>$V_{\rm EN} > V_{\rm DEN(th, max)}$                                                               | P_7.5.6  |

| Fault detection current                                                   | I <sub>OUT(fault)</sub>  | 50   | -     | 180  | μΑ   | $V_{\rm S} > 8 V$<br>$V_{\rm OUT} = 0 V$<br>$V_{\rm EN} > V_{\rm DEN(th, max)}$                                        | P_7.5.7  |

| D-pin                                                                     |                          |      |       |      |      |                                                                                                                        |          |

| Threshold voltage for<br>function de-activation                           | $V_{\rm D(th)}$          | 1.4  | 1.7   | 2    | V    | V <sub>S</sub> > 8 V<br>V <sub>EN</sub> = 5.5 V                                                                        | P_7.5.8  |

| Threshold hysteresis                                                      | V <sub>D(hys)</sub>      | -    | 100   | -    | mV   | ${}^{1)}V_{\rm S} > 8 V$ $V_{\rm EN} = 5.5 V$ $V_{\rm OUT} = V_{\rm OUT(OL)}$                                          | P_7.5.9  |

| Fault pull-up current                                                     | I <sub>D(fault)</sub>    | 20   | 35    | 50   | μA   | $V_{\rm S} > 8 V$<br>$V_{\rm OUT} = V_{\rm OUT(OL)}$<br>$V_{\rm D} = 2 V$                                              | P_7.5.10 |

| Pull-down current                                                         | I <sub>D(PD)</sub>       | 40   | 60    | 95   | μΑ   | $V_{\rm S} > 8 V$ $V_{\rm EN} = 5.5 V$ $V_{\rm D} = 1.4 V$ $V_{\rm ERRN} = 2 V$ $V_{\rm PS} = 3 V$ No fault conditions | P_7.5.11 |

| Internal clamp voltage                                                    | V <sub>D(CL)</sub>       | 4    | -     | 6    | V    | $V_{\rm S} > 8 V$<br>$V_{\rm OUT} = V_{\rm OUT(OL)}$<br>D-pin open                                                     | P_7.5.12 |

| Timing                                                                    | IL                       |      |       | 1    | 4    |                                                                                                                        | L        |

| Fault to ERRN activation delay                                            | t <sub>fault</sub>       | 40   | -     | 150  | μs   | $ V_{S} > 8 V$ $V_{OUT} rising from 5 V$ to $V_{S}$ $V_{EN} > V_{DEN(th, max)}$                                        | P_7.5.19 |

| Fault appearance/removal<br>to IN_SET<br>deactivation/activation<br>delay | t <sub>IN_SET(del)</sub> | -    | -     | 10   | μs   | <sup>1)</sup> $V_{\rm S} > 8 V$<br>OUT open<br>D rising from 0 V to<br>5 V<br>$V_{\rm EN} > V_{\rm DEN(th, max)}$      | P_7.5.20 |

1) Not subjected to production test: specified by design.

#### PWM control (Digital dimming)

## 7 PWM control (Digital dimming)

Digital dimming via PWM control is commonly practiced to adjust luminous intensity, preventing color shift of the LED light source.

### 7.1 **PWM unit**

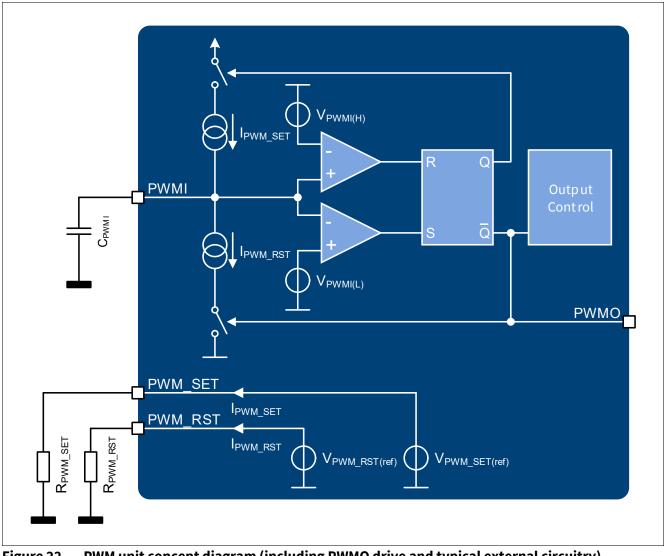

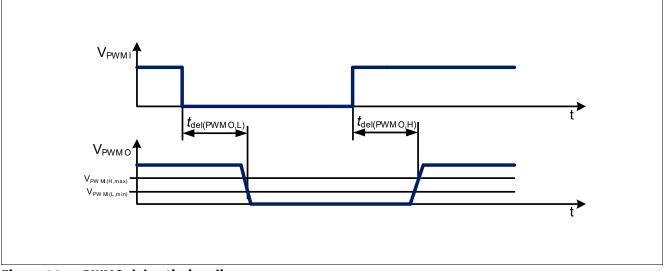

Figure 22 PWM unit concept diagram (including PWMO drive and typical external circuitry)

The PWM unit can be configured connecting a resistor on each of PWM\_SET and PWM\_RST configuration pins and a capacitor to the PWMI pin. This setup (provided that  $V_{EN} > V_{EN(th)}$  and  $V_S > V_{SUV(ON)}$ ) enables the internal Pulse Width Modulation (PWM) generator to drive the PWMO pin with a digital signal, which represents the desired PWM frequency and Duty Cycle (DC).

With reference to the block diagram of **Figure 22** the current flowing through PWM\_SET and PWR\_RST reference pins ( $I_{PWM_SET}$  and  $I_{PWM_RST}$ ) are replicated to charge or discharge the capacitor  $C_{PWMI}$

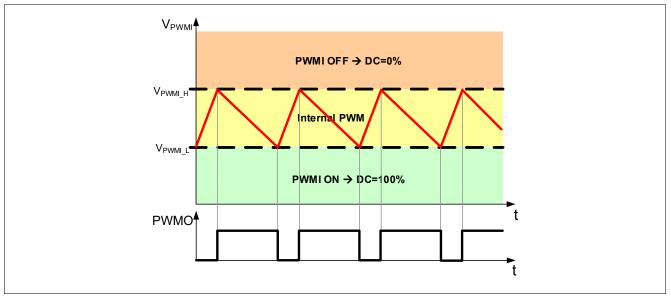

The following figure shows the charging and discharging phases defined by the chosen external components, according to **Figure 23** and the internal PWM unit.

### TLD2141-3EP LITIX™ Basic+

### PWM control (Digital dimming)

Figure 23 PWMI operating voltages and timing diagram example

The PWM typical characteristics can be adjusted using the formulas below.

$$t_{PWM(ON)} = \frac{C_{PWMI}}{I_{PWM\_SET}} \left( V_{PWMI(H)} - V_{PWMI(L)} \right) = \frac{R_{PWM\_SET}C_{PWMI}}{V_{REF\_SET}} \left( V_{PWMI(H)} - V_{PWMI(L)} \right)$$

(7.1)

$$t_{PWM(OFF)} = \frac{C_{PWMI}}{I_{PWM\_RST}} \left( V_{PWMI(H)} - V_{PWMI(L)} \right) = \frac{R_{PWM\_RST}C_{PWMI}}{V_{REF\_RST}} \left( V_{PWMI(H)} - V_{PWMI(L)} \right)$$

(7.2)

$$f_{PWMI} = \frac{1}{t_{PWMI(ON)} + t_{PWMI(OFF)}} = \frac{V_{REF\_SET/RST}}{V_{PWMI(H)} - V_{PWMI(L)}} \cdot \frac{1}{\left(R_{PWM\_SET} + R_{PWM\_RST}\right)C_{PWMI}}$$

(7.3)

$V_{\text{REF SET/RST}}$  is equal to 1.22 V. See P\_8.4.12 and P\_8.4.13.

$$DC_{PWMI} = \frac{t_{PWMI(ON)}}{t_{PWMI(ON)} + t_{PWMI(OFF)}} = \frac{R_{PWM\_SET}}{R_{PWM\_SET} + R_{PWM\_RST}}$$

(7.4)

From these equations, the proper value  $C_{\text{PWMI}}$ ,  $R_{\text{PWM}\_\text{SET}}$  and  $R_{\text{PWM}\_\text{RST}}$  can be calculated, according to the electrical characteristics defined in **Table 9**.

#### 7.2 Direct control of PWMI

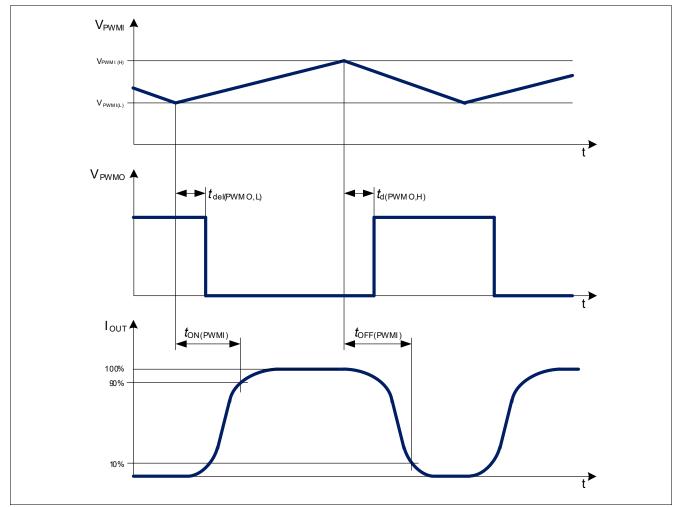

The PWM engine also drives the internal channels and, via the PWMO output pin, the PWM control can be used to synchronize other devices of the LITIX<sup>™</sup> Basic+ family.

PWMI input can be also controlled by the PWMO output of another device of LITIX<sup>™</sup> Basic+ family or, alternatively, a push-pull output stage of a microcontroller: the host device decides the digital dimming characteristics by applying the proper control cycle in order to set the "on"/"off" timing, according to the chosen dimming function.

#### PWM control (Digital dimming)

Figure 24 PWM engine timing overview

Figure 25Output activation delay timing diagram

### TLD2141-3EP LITIX™ Basic+

#### PWM control (Digital dimming)

### 7.4 Electrical characteristics PWM engine

#### Table 9 Electrical characteristics: PWM engine

$T_{\rm J}$  = -40°C to +150°C;  $V_{\rm S}$  =5.5 V to 18 V;  $R_{\rm IN\_SET}$  = 10 kΩ; all voltages with respect to GND, positive current flowing into input and I/O pins, positive current flowing out from output pins (unless otherwise specified)

| Parameter                                                                          | Symbol               | Values |      |      | Unit | Note or                                                                                                                                                               | Number   |

|------------------------------------------------------------------------------------|----------------------|--------|------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                                                    |                      | Min.   | Тур. | Max. |      | <b>Test Condition</b>                                                                                                                                                 |          |

| PWMI low threshold                                                                 | V <sub>PWMI(L)</sub> | 1.5    | 1.7  | 2    | V    | $V_{\rm S} = 8  {\rm V}  {\rm to}  18  {\rm V}$<br>$V_{\rm EN} = 5.5  {\rm V}$                                                                                        | P_8.4.1  |

| PWMI high threshold                                                                | V <sub>PWMI(H)</sub> | 2.5    | 2.7  | 3    | V    | $V_{\rm S} = 8  {\rm V}  {\rm to}  18  {\rm V}$<br>$V_{\rm EN} = 5.5  {\rm V}$                                                                                        | P_8.4.2  |

| PWMI switching threshold<br>difference V <sub>PWMI(H)</sub> - V <sub>PWMI(L)</sub> | ΔV <sub>PWMI</sub>   | 0.85   | 1.0  | 1.15 | V    | $^{1)}V_{\rm S} = 8 \text{ V to } 18 \text{ V}$<br>$V_{\rm EN} = 5.5 \text{ V}$<br>$V_{\rm PS} = 3 \text{ V}$                                                         | P_8.4.3  |

| PWMO Duty Cycle                                                                    | DC <sub>PWMO</sub>   | 9.5    | 10   | 10.5 | %    | $^{1)2)}V_{S} = 8 V \text{ to } 18 V$<br>$I_{PWM_SET} = 270 \mu\text{A}$<br>$I_{PWM_RST} = 30 \mu\text{A}$<br>$C_{PWMI} = 110 \text{nF}$<br>$C_{PWMO} = 50 \text{pF}$ | P_8.4.9  |

| PWMO Duty Cycle                                                                    | DC <sub>PWMO</sub>   | 47     | 50   | 53   | %    | $^{1)2)}V_{S} = 8 V \text{ to } 18 V$<br>$I_{PWM_SET} = 55 \mu A$<br>$I_{PWM_RST} = 55 \mu A$<br>$C_{PWMI} = 110 \text{ nF}$<br>$C_{PWMO} = 50 \text{ pF}$            | P_8.4.8  |

| PWMO Duty Cycle                                                                    | DC <sub>PWMO</sub>   | 78     | 80   | 82   | %    | $^{1)2)}V_{S} = 8 V \text{ to } 18 V$<br>$I_{PWM_{SET}} = 35 \mu A$<br>$I_{PWM_{RST}} = 140 \mu A$<br>$C_{PWMI} = 110 \text{ nF}$<br>$C_{PWMO} = 50 \text{ pF}$       | P_8.4.11 |

### PWM control (Digital dimming)

#### Table 9 Electrical characteristics: PWM engine (cont'd)

$T_{\rm J}$  = -40°C to +150°C;  $V_{\rm S}$  =5.5 V to 18 V;  $R_{\rm IN\_SET}$  = 10 kΩ; all voltages with respect to GND, positive current flowing into input and I/O pins, positive current flowing out from output pins (unless otherwise specified)

| Parameter                                                                                  | Symbol                     | Values |      |       | Unit | Note or                                                                                                                                                                                                                                     | Number   |

|--------------------------------------------------------------------------------------------|----------------------------|--------|------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                                                            |                            | Min.   | Тур. | Max.  |      | Test Condition                                                                                                                                                                                                                              |          |