## CY8CMBR2110

CapSense<sup>®</sup> Express<sup>™</sup> 10-Button Controller

## Features

- Register-configurable CapSense<sup>®</sup> controller

- Does not require firmware or device programming

- □ Ten-button solution configurable through I<sup>2</sup>C protocol

- Ten general purpose outputs (GPOs)

- GPOs are linked to CapSense buttons

- GPOs support direct LED drive

- SmartSense™ Auto-Tuning

- Maintains optimal button performance even in noisy environment

- CapSense parameters dynamically set in runtime

- Saves time and effort in device tuning

- □ Wide parasitic capacitance (C<sub>P</sub>) range (5 pF–40 pF)

- Advanced features

- Robust sensing even with closely-spaced buttons Flanking Sensor Suppression (FSS)

- User-configurable LED effects

- On-system power-on

- · On-button touch

- · LED ON Time after button release

- Standby Mode LED Brightness

- Buzzer Signal Output

- □ Supports analog voltage output (requires external resistors)

- Attention line interrupt to host to indicate any CapSense button status change

- □ CapSense performance data through I<sup>2</sup>C interface

- Simplifies production-line testing and system debug

- Noise Immunity

- Specifically designed for superior noise immunity to external radiated and conducted noise

- Low radiated noise emission

- System diagnostics of CapSense buttons reports faults at device power-up

- Button shorts

- □ Improper value of modulating capacitor (C<sub>MOD</sub>)

- □ Parasitic capacitance (C<sub>P</sub>) value out of range

- EZ-Click<sup>™</sup> Customizer tool

- Simple graphical configuration options

- Dynamically configures all features

- Configurations can be saved and reused later

- I<sup>2</sup>C interface

- No clock stretching

- Supports speed of up to 100 kHz

- Wide operating voltage range

- 1.71 V to 5.5 V ideal for both regulated and unregulated battery applications

- Low power consumption

- $\square$  Supply current in run mode as low as 23  $\mu A^{[1]}$  for each button  $\square$  Deep sleep current: 100 nA

- Industrial temperature range: -40 °C to +85 °C

- 32-pin Quad Flat No-leads (QFN) package (5 mm × 5 mm × 0.6 mm)

#### **Overview**

The CY8CMBR2110 CapSense Express<sup>™</sup> capacitive touch sensing controller saves time and money, quickly enabling a capacitive touch sensing user interface in your design. It is a register-configurable device and does not require any firmware coding or device programming. In addition, this device is enabled with Cypress's SmartSense Auto-Tuning algorithm which eliminates the need to manually tune the user interface during development and production ramp. This speeds the time to volume and saves valuable engineering time, test time, and production yield loss.

The EZ-Click Customizer tool is a simple graphical interface for configuring the device features, through the  $I^2C$  interface. One configuration can be used to configure multiple samples in different boards.

The CY8CMBR2110 CapSense controller supports up to ten capacitive sensing buttons and ten GPOs. The GPO is an active low output controlled directly by the CapSense input making it ideal for a wide variety of consumer, industrial, and medical applications. The wide operating range of 1.71 V to 5.5 V enables unregulated battery operation, further saving component cost. The same device can also be used in different applications with varying power supplies.

This device supports ultra low-power consumption in both run mode and deep sleep modes to stretch battery life. In addition, this device also supports many advanced features, which enhance the robustness and user experience of the end solution. The key advanced features are Noise Immunity and Flanking Sensor Suppression (FSS). Noise Immunity improves the immunity of the device against radiated and conducted noise, such as audio and radio frequency (RF) noise. FSS provides robust sensing even with closely-spaced buttons. FSS is a critical requirement in small form-factor applications.

Power-on LED effects provide visual feedback to the design at system power-on. Button-controlled LED effects provide visual feedback on a button touch. These effects improve the aesthetic value of the end product. Buzzer Signal Output provides audio feedback on a button touch. System diagnostics test for design faults at power-on and report any failures. This simplifies production-line testing and reduces manufacturing costs. CapSense data output through  $I^2C$  gives critical information about the design, such as button C<sub>P</sub> and signal-to-noise ratio (SNR). This further helps in system debug and production-line testing.

#### Note

**Cypress Semiconductor Corporation** Document Number: 001-74494 Rev. \*B

<sup>23</sup> μA per button (4 buttons used, 180 button touch per hour, average button touch time of 1000 ms, buzzer disabled, Button Touch LED Effects disabled, 10 pF < C<sub>P</sub> of all buttons < 20 pF, Button Scan Rate = 541 ms, with power consumption optimized, Noise Immunity level Normal, CSx sensitivity Medium).</li>

## CY8CMBR2110

## Contents

| Pinout                                        | -   |

|-----------------------------------------------|-----|

| Typical Circuits                              |     |

| Schematic 1: Ten Buttons with Ten GPOs        | 4   |

| Schematic 2: Eight Buttons                    |     |

| with Analog Voltage Output                    | 5   |

| Configuring the CY8CMBR2110                   | 6   |

| EZ-Click Customizer Tool                      |     |

| Configuring the Device using a Host Processor | 6   |

| Third-party Programmer                        | 6   |

| Device Features                               |     |

| CapSense Buttons                              |     |

| SmartSense Auto-Tuning                        |     |

| General Purpose Outputs (GPOs)                | 7   |

| Toggle ON/OFF                                 |     |

| Flanking Sensor Suppression (FSS)             | 8   |

| Noise Immunity                                | 8   |

| Automatic Threshold                           | 8   |

| LED ON Time                                   |     |

| Button Auto Reset                             |     |

| Power-on LED Effects                          |     |

| Button Touch LED Effects                      |     |

| Last Button LED Effect                        |     |

| Standby Mode LED Brightness                   |     |

| Latch Status Read                             |     |

| Attention/Sleep Line to Host                  |     |

| Analog Voltage Support                        |     |

| Sensitivity Control                           |     |

| Debounce Control                              |     |

| Buzzer Signal Output                          |     |

| Host Controlled GPOs                          |     |

| System Diagnostics                            |     |

| I2C Communication                             |     |

| Power Consumption and Operating Modes         |     |

| Low-Power Sleep Mode                          |     |

| Deep Sleep Mode                               |     |

| Response Time                                 |     |

| Device Modes                                  |     |

| Operating Mode                                | .23 |

|                                               |     |

| LED Configuration Mode                  | 23 |

|-----------------------------------------|----|

| Device Configuration Mode               | 23 |

| Production Line Test Mode               | 23 |

| Debug Data Mode                         |    |

| Steps to Configure CY8CMBR2110          | 24 |

| CY8CMBR2110 Reset                       |    |

| Layout Guidelines and Best Practices    |    |

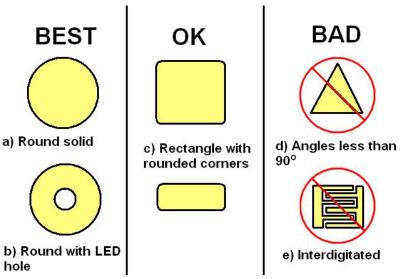

| CapSense Button Shapes                  |    |

| Button Layout Design                    |    |

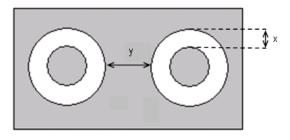

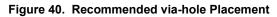

| Recommended via-hole Placement          |    |

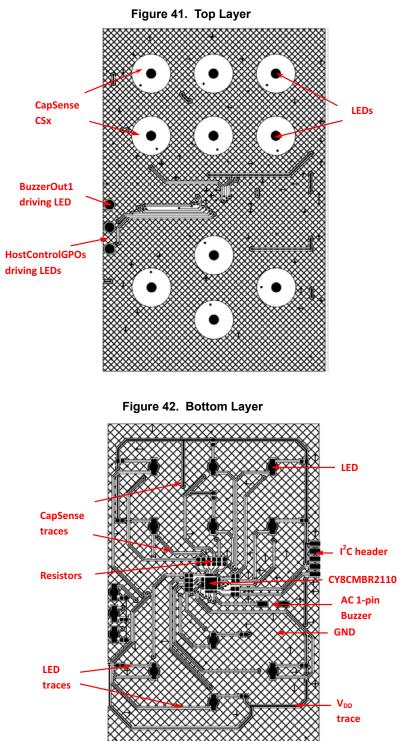

| Example PCB Layout Design               |    |

| with Ten CapSense Buttons and Ten LEDs  | 27 |

| Electrical Specifications               | 28 |

| Absolute Maximum Ratings                | 28 |

| Operating Temperature                   | 28 |

| DC Electrical Characteristics           | 29 |

| AC Electrical Specifications            |    |

| Flash Write Time Specifications         | 33 |

| CapSense Specifications                 | 34 |

| I2C Specifications                      | 34 |

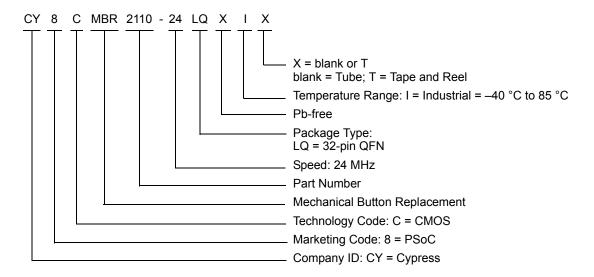

| Ordering Information                    | 35 |

| Ordering Code Definitions               | 35 |

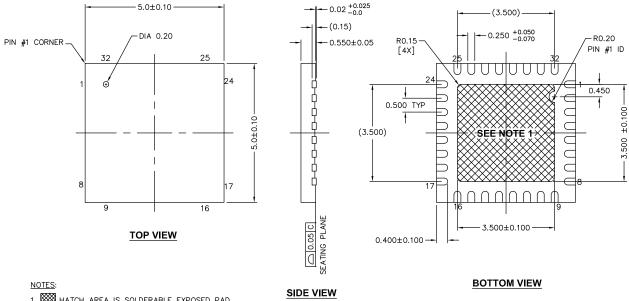

| Package Information                     | 35 |

| Thermal Impedance                       | 35 |

| Solder Reflow Specifications            | 35 |

| Package Diagram                         |    |

| Appendix - Register Map                 | 37 |

| Acronyms                                |    |

| Document Conventions                    | 69 |

| Units of Measure                        | 69 |

| Numeric Naming                          | 69 |

| Document History Page                   | 70 |

| Sales, Solutions, and Legal Information | 71 |

| Worldwide Sales and Design Support      | 71 |

| Products                                | 71 |

| PSoC Solutions                          | 71 |

|                                         |    |

## Pinout

#### Table 1. Pin Diagram and Definitions – CY8CMBR2110

| Pin | Label            | Type <sup>[2]</sup> | Description                                                                                         | If Unused       |                                                                                                                             |

|-----|------------------|---------------------|-----------------------------------------------------------------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------|

| 1   | CS1              | AI                  | CapSense button input, controls GPO1                                                                | Ground          |                                                                                                                             |

| 2   | CS0              | AI                  | CapSense button input, controls GPO0                                                                | Ground          |                                                                                                                             |

| 3   | GPO0             | DO                  | GPO activated by CS0                                                                                | Leave open      | ۲<br>د د مم<br>د د مم<br>د د د د<br>د د د<br>د د د<br>د د د<br>د<br>د<br>د                                                  |

| 4   | GPO1             | DO                  | GPO activated by CS1                                                                                | Leave open      |                                                                                                                             |

| 5   | GPO2             | DO                  | GPO activated by CS2                                                                                | Leave open      | CS1=1 CS7                                                                                                                   |

| 6   | GPO3             | DO                  | GPO activated by CS3                                                                                | Leave open      | CS 0 = 2 23= CS 8<br>GPO 0 = 3 CY8CMBR2110 22= CS 9                                                                         |

| 7   | GPO4             | DO                  | GPO activated by CS4                                                                                | Leave open      | GPO1 4 OEN 21 GPO 9                                                                                                         |

| 8   | I2C SCL          | DIO                 | I <sup>2</sup> C Clock line                                                                         | N/A             | GPO 2 = 5 (Top View) 20= GPO 8<br>GPO 3 = 6 19= GPO 7                                                                       |

| 9   | I2C SDA          | DIO                 | I <sup>2</sup> C Data line                                                                          | N/A             | GPO 4 = 7 18= GPO 6<br>12C SCL= 8 0 0 − N 0 + 0 0 17= XRES                                                                  |

| 10  | BuzzerOut0       | DO                  | Buzzer output pin 0/GPO controlled by register settings                                             | Leave open      |                                                                                                                             |

| 11  | HostControlGPO0  | DO                  | GPO controlled by Register settings                                                                 | Leave open      | Sleep<br>PO 5                                                                                                               |

| 12  | V <sub>SS</sub>  | Р                   | Ground                                                                                              | N/A             | I2C SDA<br>BuzerOut0<br>HostControIGP 00<br>Vss<br>HostControIGP 01<br>BuzzerOut1<br>BuzzerOut1<br>Attention/Sleep<br>GPO 5 |

| 13  | HostControlGPO1  | DO                  | GPO controlled by Register settings                                                                 | Leave open      | e E E E Attter                                                                                                              |

| 14  | BuzzerOut1       | DO                  | Buzzer output pin 1/GPO controlled by register settings                                             | Leave open      | ŤŤ                                                                                                                          |

| 15  | Attention/Sleep  | DIO                 | Used to control I <sup>2</sup> C communication, device power consumption, and device operating mode | V <sub>DD</sub> |                                                                                                                             |

| 16  | GPO5             | DO                  | GPO activated by CS5                                                                                | Leave open      |                                                                                                                             |

| 17  | XRES             | DI                  | Device reset, active high, with internal pull down                                                  | Leave open      |                                                                                                                             |

| 18  | GPO6             | DO                  | GPO activated by CS6                                                                                | Leave open      |                                                                                                                             |

| 19  | GPO7             | DO                  | GPO activated by CS7                                                                                | Leave open      |                                                                                                                             |

| 20  | GPO8             | DO                  | GPO activated by CS8                                                                                | Leave open      |                                                                                                                             |

| 21  | GPO9             | DO                  | GPO activated by CS9                                                                                | Leave open      |                                                                                                                             |

| 22  | CS9              | AI                  | CapSense button input, controls GPO9                                                                | Ground          |                                                                                                                             |

| 23  | CS8              | AI                  | CapSense button input, controls GPO8                                                                | Ground          |                                                                                                                             |

| 24  | CS7              | AI                  | CapSense button input, controls GPO7                                                                | Ground          |                                                                                                                             |

| 25  | CS6              | Al                  | CapSense button input, controls GPO6                                                                | Ground          |                                                                                                                             |

| 26  | CS5              | Al                  | CapSense button input, controls GPO5                                                                | Ground          |                                                                                                                             |

| 27  | CS4              | Al                  | CapSense button input, controls GPO4                                                                | Ground          |                                                                                                                             |

| 28  | V <sub>DD</sub>  | Р                   | Power                                                                                               | N/A             |                                                                                                                             |

| 29  | CS3              | AI                  | CapSense button input, controls GPO3                                                                | Ground          |                                                                                                                             |

| 30  | CS2              | AI                  | CapSense button input, controls GPO2                                                                | Ground          |                                                                                                                             |

| 31  | C <sub>MOD</sub> | AI                  | External modulating capacitor, recommended value 2.2 nF (±10%)                                      | N/A             |                                                                                                                             |

| 32  | V <sub>SS</sub>  | Р                   | Ground                                                                                              | N/A             | ]                                                                                                                           |

## **Typical Circuits**

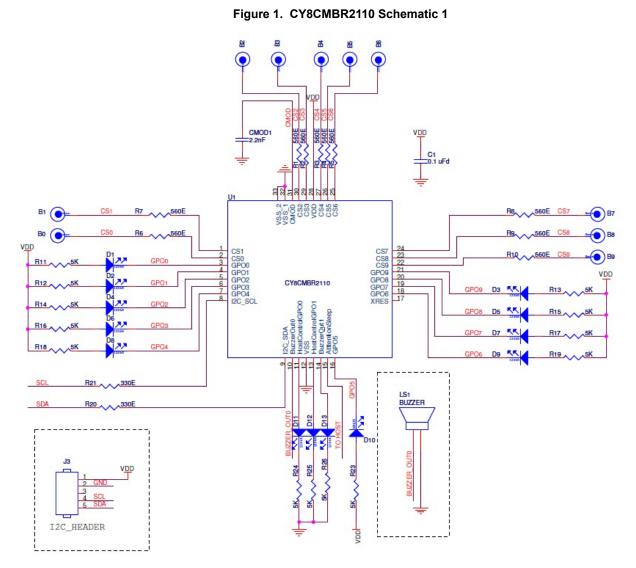

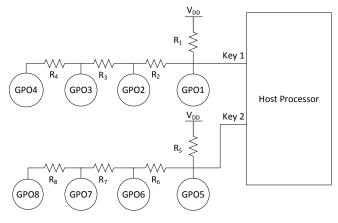

Schematic 1: Ten Buttons with Ten GPOs

In Figure 1, the device is configured in the following manner:

- CS0–CS9 pins: 560 Ω to CapSense buttons □ Ten CapSense buttons (CS0–CS9)

- GPO0–GPO9 pins: LED and 5 kΩ to V<sub>DD</sub>

CapSense buttons driving 10 LEDs (GPO0-GPO9)

- C<sub>MOD</sub> pin: 2.2 nF to ground □ Modulating capacitor

- XRES pin: Floating

For external reset

- BuzzerOut0 pin: To buzzer

AC buzzer (1-pin)

Buzzer second pin to Ground

- BuzzerOut1 pin: LED and 5 kΩ to Ground □ Used as Host Controlled GPO

- HostControlGPO0, HostControlGPO1: LED and 5 kΩ to Ground

- Two Host Controlled GPOs

- HostControlGPO0, HostControlGPO1: Floating

Host Controlled GPOs disabled

- I2C\_SDA, I2C\_SCL pins: 330  $\Omega$  to I<sup>2</sup>C header □ For I<sup>2</sup>C communication

- Attention/Sleep pin: To host

- For controlling I<sup>2</sup>C communication, power consumption, and device operating mode

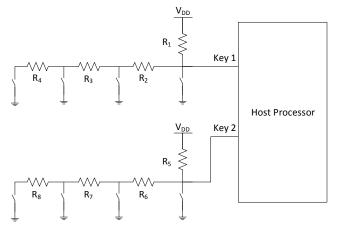

#### Schematic 2: Eight Buttons with Analog Voltage Output

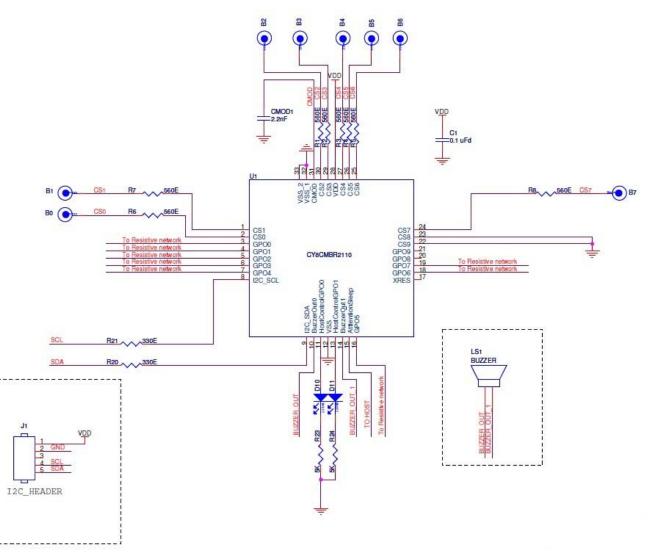

Figure 2. CY8CMBR2110 Schematic 2

- In Figure 2, the device is configured in the following manner:

- $\blacksquare$  CS0–CS7 pins: 560  $\Omega$  to CapSense buttons; CS8, CS9 pins: Ground

- □ Eight CapSense buttons (CS0–CS9) □ CS8 and CS9 buttons not used in design

- GP00–GP07: To external resistive network

Eight GPOs (GP00–GP07) used for Analog Voltage Output

GP08 and GP09 not used in design

- C<sub>MOD</sub> pin: 2.2 nF to ground □ Modulating capacitor

- XRES pin: Floating For external reset

- BuzzerOut0 and BuzzerOut1 pins: To AC buzzer

AC Buzzer (2-pin)

- HostControlGPO0, HostControlGPO1 pins: LED and 5 kΩ to ground

- Two Host-controlled GPOs

- I2C\_SDA, I2C\_SCL pins: 330-Ω to I<sup>2</sup>C header □ For I<sup>2</sup>C communication

- Attention/Sleep pin: To Host

- For controlling I<sup>2</sup>C communication, power consumption, and device operating mode

## Configuring the CY8CMBR2110

#### **EZ-Click Customizer Tool**

The EZ-Click Customizer tool is a simple and intuitive graphical user interface for efficiently configuring the device. It takes all the required parameters and configures the device accordingly, using I<sup>2</sup>C communication. The configuration can be saved locally on the computer and later re-used by the tool for another design. The tool can also be used to generate a configuration file, which can be used through Bridge Control Panel (refer to

AN2397 - CapSense Data Viewing Tools) or by the host (in the host firmware) to configure the device. For more details, refer to the EZ-Click Customizer Tool User Guide.

#### Configuring the Device using a Host Processor

CY8CMBR2110 can be configured by a Host processor. The advantages of using a host processor to configure are listed below.

In-system configuration - no need to take the device (chip) out of the board. Run time configuration - modifying the features dynamically by a host processor.

To configure the device using a Host processor, there is a comprehensive list of APIs and these APIs are to be called from the Host processor in a specific order. These APIs use I2C communication to configure the device features. You can download the source code from http://www.cypress.com/?rID=74590.

For more details refer to CY8CMBR2110  $\mbox{CapSense}^{\mbox{$\mathbb{8}$}}$  Design Guide.

#### Third-party Programmer

To configure large number of devices, Cypress recommends a third-party vendor to perform automated programming on the devices. For this, you must give the hex file of your configuration, generated by EZ-Click Customizer Tool to Hilo systems (a third-party programmer).

Contact http://www.hilosystems.com.tw/en/index.aspx for further information.

### **Device Features**

#### CapSense Buttons

- Supports up to 10 CapSense buttons

- Ground the CSx pin to disable CapSense button input

- Connect a 2.2-nF (±10%) capacitor on the C<sub>MOD</sub> pin for proper CapSense operation

- For proper CapSense operation, ensure C<sub>P</sub> of each button is less than 40 pF

#### SmartSense Auto-Tuning

- Supports auto-tuning of CapSense parameters

- Does not require manual tuning; all parameters are automatically tuned by the device

- Reduces the design cycle time

No manual tuning

- Ensures portability of the user interface design

- Compensates printed circuit board (PCB) variations, device process variations, and PCB vendor changes

#### **General Purpose Outputs (GPOs)**

- GPOx pin outputs are strong drive<sup>[3]</sup>

- The GPOx is controlled by the corresponding CSx

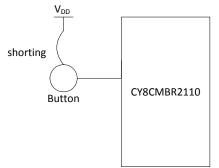

- Active low output supports sinking configuration for LEDs (see Figure 3)

- If CSx is disabled (grounded), then the corresponding GPOx must be left floating

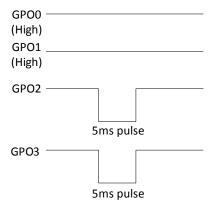

- After power-up on the GPOx, a 5-ms pulse is sent after 350 ms (if Noise Immunity level is "Normal") and 1000 ms (if Noise Immunity level is "High"), if the CSx fails the System Diagnostics

#### Figure 3. Example of GPO0 Driven by CS0

#### Table 2. CY8CMBR2110 Advanced Features

| Feature                                           | Benefits                                                                                                                   |

|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Toggle ON/OFF                                     | Button retains state after touch (ON/OFF)                                                                                  |

| Flanking Sensor Suppression (FSS)                 | Avoids multiple button trigger in a design with closely-spaced buttons                                                     |

| Noise Immunity                                    | Improves device immunity to external noise (such as RF noise)                                                              |

| Automatic Threshold                               | Configurable finger threshold for different noise settings                                                                 |

| LED ON Time                                       | Gives an LED effect on button release                                                                                      |

| Button Auto Reset                                 | Disables false output trigger when the conducting object is placed close to the button                                     |

| Power-on LED Effects and Button Touch LED Effects | Provides visual effects to design at power-on and button touch                                                             |

| Standby Mode LED Brightness                       | Used for LED backlighting                                                                                                  |

| Latch Status Read                                 | No button touch missed by host processor                                                                                   |

| Attention/Sleep Line to Host                      | Provides device interrupt to host. Host can use this to read data from the device.<br>Also controls device operating mode. |

| Analog Voltage Support                            | External resistors can be used with GPOs to generate analog voltage output                                                 |

| Sensitivity Control                               | Maintains optimal button performance for different overlay and noise conditions                                            |

| Debounce Control                                  | Prevents false trigger of buttons                                                                                          |

| Buzzer Signal Output                              | Provides audio feedback on button touch                                                                                    |

| Host Controlled GPOs                              | GPO pins, which can be controlled by the host processor through I <sup>2</sup> C                                           |

| System Diagnostics                                | Supports production testing and debugging                                                                                  |

| Low-Power Sleep Mode and Deep Sleep Mode          | Low power consumption                                                                                                      |

Note

3. When a pin is in strong drive mode, it is pulled up to V<sub>DD</sub> when the output is HIGH and pulled down to Ground when the output is LOW.

#### Toggle ON/OFF

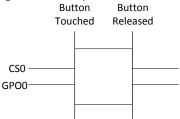

- Toggles the GPO state at each button touch (see Figure 4).

- Use for mechanical button replacement (for example, wall switch).

- Toggle feature can be enabled on each CapSense button individually.

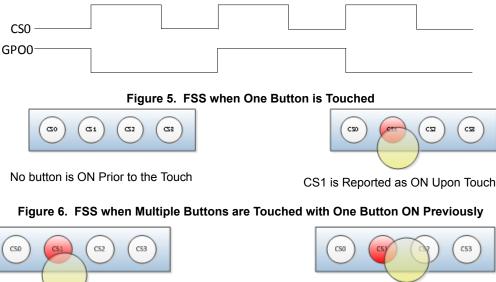

#### Flanking Sensor Suppression (FSS)

- Allows only one button to be in the TOUCH state at a time. You can distinguish TOUCH states for closely spaced buttons.

- If a finger contacts multiple buttons, only the first one to sense a TOUCH state turns ON.

- Also used in situations when a button can produce opposite effects. For example, an interface with two buttons for brightness control (UP or DOWN).

- FSS can be enabled for each button individually. This helps to enable FSS only for those buttons which are closely spaced. For example, if a design has ten buttons with six buttons closely-spaced, FSS can be enabled just for those six buttons.

- FSS action can be explained for the following scenarios:

- 1. When only one button is touched, it is reported as ON (see Figure 5).

- 2. When more than one button is detected as ON, and previously one of those buttons was touched, then the button touched previously is reported as ON (see Figure 6).

#### Noise Immunity

- Improves the immunity of the device against external radiated and conducted noise.

- Reduces the radiated noise emission.

- Possible Noise Immunity levels are "Normal" and "High".

- Select "High" only in a high-noise environment because it increases device power consumption and response time.

#### **Automatic Threshold**

- Button Signal is compared to Finger Threshold for GPO output

- Finger Threshold is configurable; valid range is 50-245 counts

- Used to determine button ON/OFF state for different noise conditions

- You can configure Finger Threshold to be set automatically

- To learn more about Finger Threshold, refer to Section 2.3 in Getting Started with CapSense

#### Figure 4. Example of Toggle ON/OFF Feature on GPO0

CS2 also touched along with CS1; CS1 is reported ON

CS1 is touched; reported ON

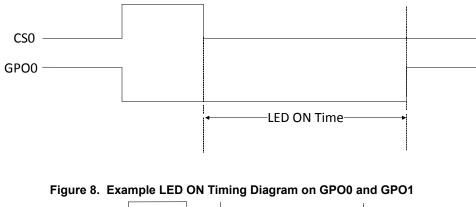

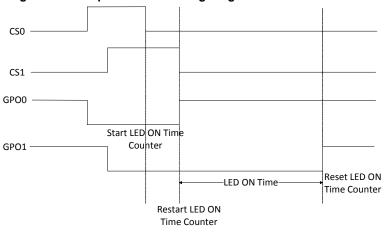

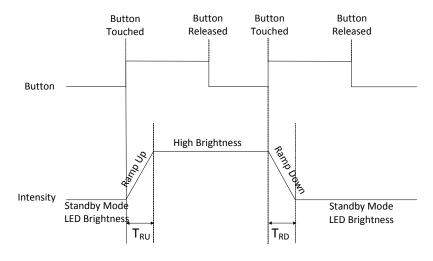

#### **LED ON Time**

- Provides a variable amount of LED ON time (upto 5100 ms) after a button is released.

- The GPOx is driven low for a specified interval after the corresponding CSx button is released (see Figure 7).

- When a button is reset (refer to Button Auto Reset on page 10), LED ON Time is not applied on the corresponding GPO.

- Applicable to the GPO of the last button released

- In Figure 8, GPO0 goes high prematurely (prior to LED ON Time expiration) because CS1 button is released. Therefore, the LED ON Time counter is reset. Now, the GPO1 remains low for LED ON Time after releasing CS1.

- LED ON Time can range from 0-5100 ms.

- LED ON Time resolution is 20 ms.

- LED ON Time is disabled if Toggle ON/OFF is enabled.

#### Figure 7. Example LED ON Timing Diagram on GPO0

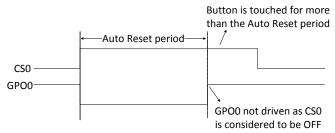

#### **Button Auto Reset**

- Prevents a stuck button due to a metal object placed close to that button.

- Useful when the button is kept ON only for a specific period of time.

- If enabled, button is considered OFF after the Button Auto Reset period, even though the button continues to be touched. See Figure 9.

- Auto Reset period can be set to 5 or 20 seconds.

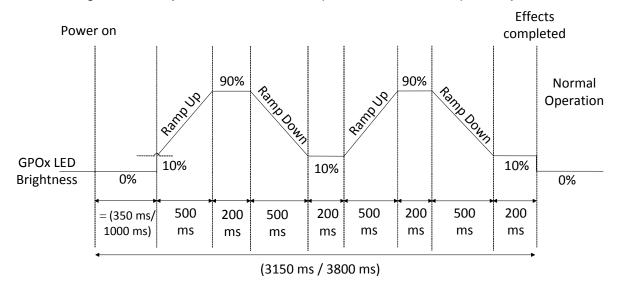

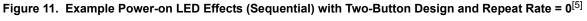

#### **Power-on LED Effects**

- Provides a visual effect at device power-up.

- After power-on, all the LEDs show dimming and fading effects for an initial time.

- Seen on GPOx when CSx is enabled.

- The GPOs are configured in groups to have the same parameters.

- The groups are:

□ GPO1, GPO2, GPO3

- GPO4, GPO5, GPO6

- GP07, GP08, GP09

- GPO0 can be configured separately. Useful in designs with a special use for CS0 button, such as a power button.

- All CapSense buttons are disabled during this time.

- If any CapSense button (CSx) fails the Power-on Self Test, then these effects are not seen on the corresponding GPOx.

- To know more about Power-on Self Test, refer System Diagnostics on page 17.

- The following parameters are set for LED effects:

- Low brightness Minimum LED intensity

- □ Low-brightness time The time period for which the LED remains in a low-brightness state

- Ramp-up time The time period during which the LED transitions from low brightness to high brightness

- High brightness Maximum LED intensity

- High-brightness time The time during which the LED stays in a high-brightness state

- Ramp-down time The time it takes the LED to go from high brightness to low brightness

- Repeat rate The number of times the effects are repeated

- Brightness levels can range from 0 to 100 percent.

- The time range can be 0 to 1600 ms.

- High-brightness level must be more than low-brightness level.

- The effects are seen after the device initialization time from power-on. This time is less than 350 ms (if the Noise Immunity level is "Normal") and less than 1000 ms (if the Noise Immunity level is "High").

- The pattern can be set to occur sequentially or concurrently on all the GPOs (see Figure 10 and Figure 11 on page 11).

- During Power-on LED Effects, the device ACKs I<sup>2</sup>C communication but all write commands are ignored. The Host can only read Operating mode data.

#### Figure 9. Example of Button Auto Reset on GPO0

Figure 10. Example Power-on LED Effects (Concurrent on all GPOs) with Repeat Rate = 1<sup>[4]</sup>

Notes

- Ramp up time = 500 ms; High brightness = 90%; High brightness time = 200 ms; Ramp down time = 500 ms; Low brightness = 10%; Low brightness time = 200 ms; Repeat rate = 1 4

- Ramp up time = 300 ms; High brightness = 100%; High brightness time = 100 ms; Ramp down time = 300 ms; Low brightness = 10%; Low brightness time = 100 ms; 5. Repeat rate = 0

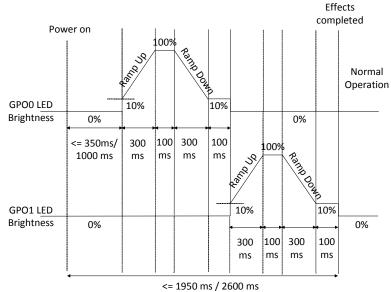

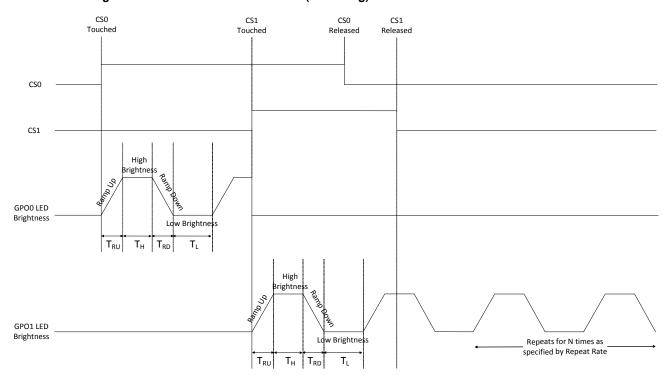

#### **Button Touch LED Effects**

- Provides a visual feedback on a button touch. Improves the aesthetic value of the design.

- Seen on GPOx when CSx is touched.

- The GPOs are configured in groups to have the same parameters. The groups are:

□ GPO1, GPO2, GPO3

🗆 GPO4, GPO5, GPO6

- □ GPO7, GPO8, GPO9

- GPO0 can be configured separately. Useful in designs with a special use for the CS0 button, such as the power button.

- The following parameters can be set for the effects:

- Low brightness Minimum LED intensity

- □ Low-brightness time The time period during which LED remains in a low-brightness state

- Ramp-up time The time period during which the LED transitions from low brightness to high brightness

- □ High brightness Maximum LED intensity

- High-brightness time The time during which the LED stays in a high-brightness state

- Ramp-down time The time it takes the LED to go from high brightness to low brightness

Repeat rate – The number of times the effects are repeated

- Brightness levels can range from 0 to 100 percent.

- The time range can be 0 to 1600 ms.

- High-brightness level should be more than the low-brightness level for proper visual effects.

- Button Touch LED effects can be of two types (see Figure 12 on page 12):

- Breathing effects: When the breathing effect is enabled, LED intensity changes from Standby Mode LED Brightness to Low Brightness immediately after a button touch. It then ramps up to high-brightness and stays for high brightness time. It then ramps down to low brightness and stays for low brightness time. This effect repeats for the duration during which the button is touched. When the button is released, the LED effects cycle that is in progress, continues. After this cycle completes, the LED effects cycle may repeat depending on the Repeat Rate.

- Non-breathing effects: When the breathing effect is disabled, the LED intensity changes from Standby Mode LED Brightness to Low Brightness immediately after a button touch. It then ramps up to high brightness and stays there for the duration during which the button is touched. When the button is released, the LED maintains its state for high brightness time. It then ramps down to low brightness and stays for low brightness time. This effect may then repeat depending on the repeat rate.

- If the Button Touch LED Effects are active on one GPOx and the corresponding CSx is touched again, then the pattern restarts on GPOx.

- If the Toggle ON/OFF effect is also enabled, the LEDs toggle between Standby Mode LED Brightness and High Brightness on successive button touches (see Figure 13 on page 13).

- If Button Touch LED Effects are enabled, the LED ON time is automatically disabled.

- When the device goes to Deep Sleep, ongoing Button Touch LED Effects are immediately disabled.

#### Figure 12. Button Touch LED Effect Pattern<sup>[6]</sup>

#### Figure 13. Button Touch LED Effects with Toggle Enabled

#### Last Button LED Effect

- Button Touch LED Effects can be configured to be interrupted on one GPO if any other button is touched.

- The effects reset on the first GPO and start on the GPO associated with the last button touched (see Figure 14).

- This feature is disabled by default.

- If Toggle ON/OFF is also enabled for some buttons, Last Button LED Effect is disabled for those buttons.

- If the Flanking Sensor Suppression (FSS) feature is also enabled, and two buttons are touched simultaneously, the Last Button LED Effect does not apply because the second button touched does not turn ON.

Figure 14. Button Touch LED Effects (Breathing) with Last Button LED Effect Enabled

#### Note

6.  $T_{RU}$  – Ramp Up Time;  $T_{RD}$  – Ramp Down Time;  $T_{H}$  – High Brightness Time ;  $T_{L}$  – Low Brightness Time

#### Standby Mode LED Brightness

- Provides a better visual feedback for buttons when in OFF state. Improves the aesthetic value.

- The LED associated with GPOx is in Standby Mode LED Brightness after the conclusion of Button Touch LED Effects, when CSx is OFF.

- Standby Mode LED Brightness can be configured to be 0%, 20%, 30%, or 50%.

- Standby Mode LED Brightness increases device power consumption because the device does not go to Low Power Sleep.

- Standby Mode LED Brightness is disabled when the device goes to Deep Sleep.

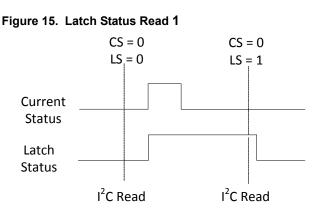

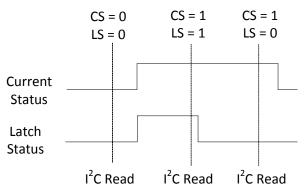

#### Latch Status Read

- Host processor can check the CapSense button status by reading the Register Map through I<sup>2</sup>C communication.

- When a button is touched, the device generates an interrupt to host through the Attention/Sleep line. Host can then read CSx status.

- If the interrupt is not serviced immediately, and the button is released before the interrupt is serviced, the host can miss that button touch.

- To avoid missing any button touch, the host should read both current status (CS) and latch status (LS).

- CS is stored in the Button\_Current\_Stat0 and Button\_Current\_Stat1 registers in Operating Mode.

- LS is stored in the Button\_Latch\_Stat0 and Button\_Latch\_Stat1 registers in Operating Mode.

- To know more about these registers, refer to Operating Mode.

- Table 3 on page 14 lists the various possibilities of button touch acknowledge/miss. These are shown in Figure 15 and Figure 16.

#### Table 3. Latch Status Read

| Current<br>Status<br>(CS) | Latch<br>Status<br>(LS) | Comments                                                                                                                                                  |

|---------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                         | 0                       | CSx is not touched during the current I <sup>2</sup> C read; Host has already acknowl-<br>edged any previous CSx touch in the last I <sup>2</sup> C read. |

| 0                         | 1                       | CSx was touched before the current I <sup>2</sup> C read; this CSx touch was missed by the host.                                                          |

| 1                         | 0                       | CSx was touched and acknowledged<br>by the host during the previous $I^2C$<br>read; the same CSx is still touched<br>during the current $I^2C$ read.      |

| 1                         | 1                       | CSx is touched during the current $I^2C$ read.                                                                                                            |

Figure 16. Latch Status Read 2

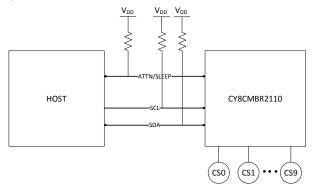

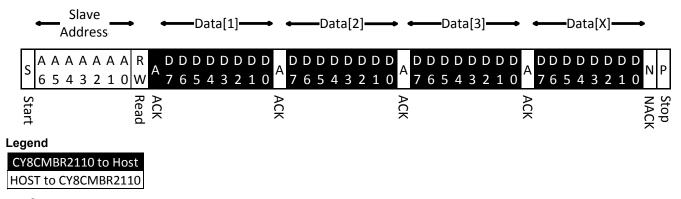

#### **Attention/Sleep Line to Host**

- Bidirectional active low line; can be controlled by both the device and the host.

- The Attention/Sleep line is in the Open Drain Low Drive mode

- The device is in the low-power Sleep mode by default (if the attention/sleep line is high). For more information, refer to the section Low-Power Sleep Mode on page 21.

- The device cannot go to the low-power Sleep mode if the attention/sleep line is low.

- Attention/Sleep line should be pulled low only if required, to reduce device power consumption.

Attention/Sleep line can be used for the following functions:

Device Interrupt to Host

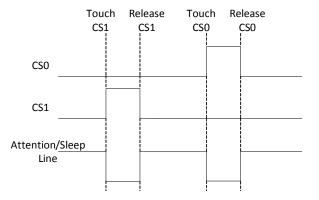

- On any button touch, the device pulls the Attention/Sleep line low to indicate an interrupt to the host (see Figure 17 on page 15).

- If more than one button is touched simultaneously, the attention line is pulled low for the entire duration of any button touch (see Figure 18 on page 15).

- The Attention/Sleep line goes high when the button is released.

## Figure 17. Attention/Sleep Line with CSx Buttons Touched Separately

## Figure 18. Attention/Sleep Line with CSx Buttons Touched Simultaneously

#### I<sup>2</sup>C Communication

- Attention/Sleep line should be pulled low before any I<sup>2</sup>C communication is initiated.

- If the Attention/Sleep line is high, the device may NACK I<sup>2</sup>C communication.

- When the Attention/Sleep line is low, the device may NACK I<sup>2</sup>C communication, but very infrequently.

#### Deep Sleep mode

- To enable the Deep Sleep mode, the host needs to set the "Deep Sleep" bit in Host\_Mode register (in the Operating Mode). The host needs to wait for 50 ms and then pull Attention/Sleep line high.

- Host should pull the Attention/Sleep line low for the device to wake up from deep sleep.

- For more information, refer to the section Deep Sleep Mode on page 21.

#### Analog Voltage Support

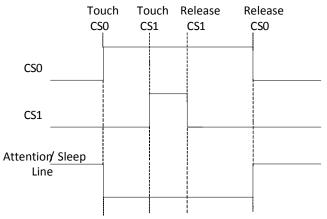

- A general external resistive network with a host processor is shown in Figure 19.

- Host can be configured to perform different functions based on the voltage level at input pins. This is controlled by switches.

- These switches can be controlled by CapSense buttons.

- If enabled, GPOs replace these switches in the network.

- GPOs are in the Open Drain Low Drive mode.

- GPOs cannot be used for the resistive network and LED drive simultaneously.

- If only one button needs to be ON for analog voltage support, FSS should be enabled.

- For CY8CMBR2110, a simple external resistive network is shown in Figure 20.

#### Figure 19. General External Resistive Network

#### Figure 20. Analog Voltage Support for CY8CMBR2110

#### Sensitivity Control

- Sensitivity of each button can be set individually.

- Use higher sensitivity setting when the overlay thickness is higher or if the button diameter is small.

- Use a lower sensitivity setting when power consumption needs to be low.

- Possible sensitivity settings are "High", "Medium", and "Low".

#### **Debounce Control**

- Avoids false triggering of buttons due to noise spike or any other glitches in the system.

- Specifies the minimum time for which a button has to be sensed as touch, for an output trigger. Debounce value can range from 1 to 255.

- Debounce value can be set separately for CS0 and combined for CS1 to CS9. This is useful for additional functions, such as, linking system reset to touch time corresponding to CS0 Debounce.

- The device Response Time depends on the button debounce. Refer to Response Time on page 22.

Table 4 lists some examples of device Response Time for different debounce values.<sup>[7]</sup>

| Table 4. | Exam | ple Res | ponse | Times | for | Debounce | Values |

|----------|------|---------|-------|-------|-----|----------|--------|

|----------|------|---------|-------|-------|-----|----------|--------|

| Debounce Value | Response Time for Consecutive<br>Button Touch (ms) |

|----------------|----------------------------------------------------|

| 1              | 70                                                 |

| 4              | 105                                                |

| 7              | 140                                                |

| 10             | 175                                                |

| 100            | 1225                                               |

| 200            | 2380                                               |

| 255            | 3010                                               |

#### **Buzzer Signal Output**

- Gives audio feedback for a button touch. For more details, refer to Response Time on page 22.

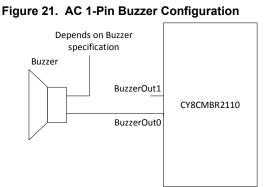

- Buzzer signal output can have two configurations: AC 1-pin and AC 2-pin.

- In the AC 1-pin buzzer configuration, the buzzer must be connected to the BuzzerOut0 pin (see Figure 21). A square wave of the given frequency and duty cycle is driven on this pin. The BuzzerOut1 pin can either be left floating or configured as a Host-controlled GPO.

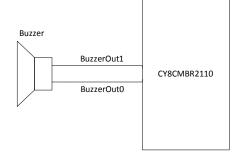

In AC 2-pin buzzer configuration, connect the buzzer between the BuzzerOut0 and BuzzerOut1 pins (see Figure 22). Two out-of-phase square waves of the given frequency and duty cycle are driven on these pins.

#### Figure 22. AC 2-Pin Buzzer Configuration

- If the buzzer is not used, then both the pins can be used as Host-controlled GPOs. Table 5 shows the possible buzzer settings.

- The idle state of the buzzer pin can be configured to be either  $V_{DD}$  or Ground.

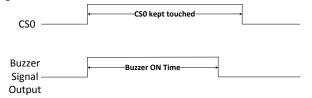

- The buzzer pin is driven to the idle state when no button is touched, or after the Buzzer ON Time elapses, even when the button is kept touched (see Figure 23).

- The buzzer signal frequency is configurable and can assume one of the following values (in kHz) 1.00, 1.14, 1.33, 1.60, 2.00, 2.67, 4.00

- The buzzer output is driven for the configured time and does not depend on the button touch time.

- Buzzer ON Time has a range of (1 to 127) × Button Scan Rate constant. To know more about Button Scan Rate constant, refer to Power Consumption and Operating Modes on page 21.

- Buzzer Signal Output is strong drive.

- The output is driven commonly by all the CSx buttons.

- Buzzer output restarts if any button is touched before the Buzzer ON time expiration (see Figure 24).

Note 7. 8-buttons, Noise Immunity level Normal, Response Time optimized design.

#### Figure 23. Buzzer Time-out

### Figure 24. Buzzer Terminated and Restarted CS0 CS1 Touched Touched CS0 CS1 Buzzer Buzzer ON Time Signal Buzzer output Output restarted

#### Table 5. Buzzer and Host-Controlled GPO Settings

| Buzzer<br>Configuration | BuzzerOut0<br>Pin                    | BuzzerOut1<br>Pin                    | Max Available<br>Host Controlled<br>POs |

|-------------------------|--------------------------------------|--------------------------------------|-----------------------------------------|

| No Buzzer               | Floating/Hos<br>t Controlled<br>GPO3 | Floating/Hos<br>t Controlled<br>GPO2 | 4                                       |

| AC 1-pin<br>buzzer      | Buzzer pin 0                         | Floating/Hos<br>t Controlled<br>GPO2 | 3                                       |

| AC 2-pin<br>buzzer      | Buzzer pin 0                         | Buzzer pin 1                         | 2                                       |

#### Host Controlled GPOs

- Two GPO pins (HostControlGPO0, HostControlGPO1) are available whose logic states can be controlled by the host.

- If the buzzer is not used, then up to two more host-controlled GPOs are available (using BuzzerOut0 and BuzzerOut1 pins).

- The Host can control these GPOs in the Operating mode. Production Line Test mode, and Debug Data mode.

- Host-controlled GPOs are in LOW state at power-on.

- Host-controlled GPO settings cannot be saved to flash and must be configured after reset.

- HostControlGPO1 has a positive going pulse of 16 ms during power-on.

- These outputs are in strong drive mode.

- Table 5 shows the maximum available Host-Controlled GPOs, depending on the buzzer configuration.

#### System Diagnostics

- A built-in Power-on Self Test (POST) mechanism performs some tests at power-on reset (POR), which can be useful in production testing.

- If any button fails these tests, a 5-ms pulse is sent out on the corresponding GPO within 350 ms (if Noise Immunity level is "Normal") or 1000 ms (if Noise Immunity level is "High") after POR.

- To know the System Diagnostics result, the host can read device data in Production Line Test mode through the I<sup>2</sup>C interface.

- Since the host can read data through I<sup>2</sup>C lines, there is no need to interface GPOs to the host.

The following tests are performed on all the buttons.

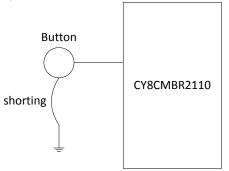

#### Button Shorted to Ground

If any button is shorted to ground, it is disabled. For an accurate detection of Button Shorted to Ground, the resistance between the CSx pin and ground should be less than the limits specified in Table 6.

#### Table 6. Maximum Resistance between CSx and GND for **Proper System Diagnostics Operation**

| Power supply (V <sub>DD</sub> )<br>(V) | Max resistance between CSx and GND ( $\Omega$ ) |

|----------------------------------------|-------------------------------------------------|

| 5.5                                    | 680                                             |

| 5                                      | 760                                             |

| 1.8                                    | 1700                                            |

#### Figure 25. Button Shorted to Ground

Button Shorted to V<sub>DD</sub>

If any button is shorted to V<sub>DD</sub>, it is disabled.

#### Figure 26. Button Shorted to $V_{DD}$

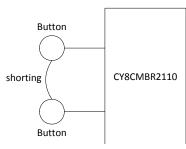

#### Button to Button Short

If two or more buttons are shorted to each other, all of these buttons are disabled.

#### Figure 27. Button to Button Short

### Improper Value of C<sub>MOD</sub>

- Recommended value of C<sub>MOD</sub> is 2 nF to 2.4 nF.

- If the value of C<sub>MOD</sub> is less than 1 nF or greater than 4 nF, all the buttons are disabled.

#### Button $C_P > 40 \ pF$

If the parasitic capacitance (C\_P) of any button is more than 40 pF, that button is disabled.

## Figure 28. Example Showing CS0 and CS1 Passing the POST and CS2 and CS3 Failing

In Figure 28, CS0 and CS1 are enabled; CS2 and CS3 are disabled because they failed the POST. Therefore, a 5-ms pulse is observed on GPO2 and GPO3.

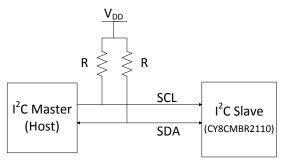

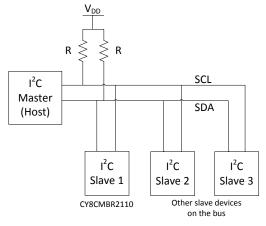

### I<sup>2</sup>C Communication

$\rm I^2C$  is the interface used to communicate between the CY8CMBR2110 (I^2C slave) and the host (I^2C master). It uses a simple two-wire synchronous communication protocol. These two wires are:

- 1. Serial Clock (SCL) This line is used to synchronize the slave with the master.

- 2. Serial Data (SDA) This line is used to send data between the master and the slave.

The CY8CMBR2110 can be a part of a one-slave or a multi-slave environment. See Figure 29 and Figure 30.

# Figure 29. $\rm I^2C$ Communication between One Master and One Slave

# Figure 30. I<sup>2</sup>C Communication between One Master and Multiple Slaves

The CY8CMBR2110 I<sup>2</sup>C interface has the following features:

- 1. Bit rate up to 100 kbps

- 2. Configurable I $^2$ C slave address (0–127), with default slave address as '37h'.

- 3. Hardware address compare

- 4. No bus-stalling No clock stretching

- 5. I<sup>2</sup>C buffer mode (32-byte hardware buffer)

- Register-based access to I<sup>2</sup>C master for read and write operations.

#### I<sup>2</sup>C Slave address

To uniquely identify each device in a multi-device state, an  $I^2C$  slave address is used. This address is a 7-bit value, which allows up to 127 slaves on the bus simultaneously. When the bus master wants to communicate with a slave on the bus, it sends a start condition followed by the  $I^2C$  address of the relevant slave. The start condition alerts all slaves on the bus when a new transaction starts. The slave with the specified  $I^2C$  address acknowledges the master. All the other slaves ignore all further traffic on the bus until the next start condition is detected.

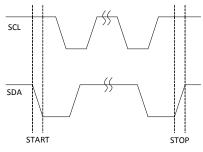

#### Start and Stop Conditions

The master initiates the communication by issuing a START condition on the bus and terminates the communication by issuing a STOP condition. The bus is considered busy between these two conditions. See Figure 31.

A START condition is shown by changing the level of SDA line (from high to low), when the SCL line is high.

A STOP condition is shown by changing the level of SDA line (from low to high), when the SCL line is high.

#### Figure 31. I<sup>2</sup>C START and STOP Conditions

#### Figure 32. I<sup>2</sup>C Interface between Host and Device

#### PC Communication Guidelines for CY8CMBR2110

- 1. The Attention/Sleep line should be pulled low by either the host or the device, before initiating any I<sup>2</sup>C communication.

- The host needs to wait for 350 ms (if Noise Immunity level is "Normal") or 1000 ms (if Noise Immunity level is "High") after device power-on, before initiating any I<sup>2</sup>C communication. Else, the device NACKs any such communication.

- The host needs to wait for a minimum of 60 ms after any I<sup>2</sup>C transaction before initiating a new transaction.

- 4. Host needs to wait for 350 ms (if Noise Immunity level is "Normal") or 1000 ms (if Noise Immunity level is "High") after "Save to flash" and "Software reset" commands are issued before initiating any further transaction.

- 5. In run time the device should be in Operating mode.

- The host should not initiate a new START condition for the device, without a STOP condition for the previous I<sup>2</sup>C communication (also called REPEAT START condition).

- 7. Host needs to maintain a minimum of 60 ms between any two  $\ensuremath{\mathrm{I}^2\mathrm{C}}$  transactions

- a. If the host does not maintain this time while reading, then it gets the same data as read in previous transaction.

- b. If the host writes to the same register twice within this time, then the old data is lost.

- c. If the host writes to different registers within this time (reg x in first write and reg y in second write) then the data is not lost.

#### Write Operation

For a write operation, the following steps are performed:

- 1. The Host sends the START condition to the device on the SDA line.

- 2. The Host specifies the slave address, followed by R/W bit to specify a write operation. The device ACKs the Host.

- 3. The Host specifies the register address to which it has to write. The device ACKs the Host.

- 4. The Host starts sending the data to the device, which is written to the register address specified by the host. This is followed by an ACK from the device.

- 5. If the write operation includes more bytes, each following byte is written to the successive register address. Each successive byte is followed by an ACK from the device.

- 6. After the write operation is complete, the Host sends the STOP condition to the device. This marks the end of the communication. See Figure 33 on page 20.

#### Notes

- 1. The Host must not write to a Read Only register.

- 2. The Host can write a maximum of 32 bytes in one I<sup>2</sup>C transaction.

#### Figure 33. Host Writing x Bytes to the Device Slave Register Data[n] Data[n+1] Data[n+x] Address Address (n) RRRRRRR D D D D D D D D D 7 6 5 4 3 2 1 0 . A A A A A A DDDDDDD DDDDDDD 543210 76543210 76543210 765432 Write ACK ACK Start Å Å ₫

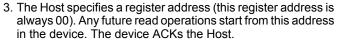

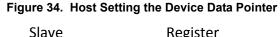

#### Setting the Device Data Pointer

The Host sets the device data pointer to specify the starting point for future read operations. To set the device pointer, perform the following steps:

- 1. The Host sends the START condition to the device on the SDA line.

- 2. The Host specifies the slave address on the SDA line, followed by the Read/Write bit to specify a write operation. The device ACKs the Host.

4. The Host sends the STOP condition to the device. This marks the end of the communication. See Figure 34.

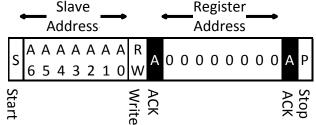

#### Read Operation

For a read operation, perform the following steps:

- 1. The Host sends the START condition to the device on the SDA line.

- 2. The Host specifies the slave address, followed by the Read/Write bit to specify a read operation. The device ACKs the Host.

- 3. The device retrieves the byte from the register address 00 and sends it to the Host. The Host ACKs the device.

- 4. Each successive byte is retrieved from the successive register address and sent to the Host, followed by ACKs from the Host.

- 5. After the host has received the required bytes, it NACKs the device.

- 6. The Host sends the STOP condition to the device. This marks the end of the communication. See Figure 35.

Figure 35. Host Reading x Bytes from the Device

For I<sup>2</sup>C electrical specifications of the device, refer to the I2C Specifications.

## **Power Consumption and Operating Modes**

CY8CMBR2110 can meet low-power requirements of battery-powered applications. To design for the lowest operating current, do the following:

- Ground all unused CapSense inputs (CSx).

- Minimize C<sub>P</sub> using the design guidelines in Getting Started with CapSense, section 3.7.1.

- Reduce supply voltage (valid range: 1.71 V to 5.5 V).

- Reduce the sensitivity of CSx buttons.

- Configure the design to be optimized for power consumption.

- Use 'High' Noise Immunity level only if needed.

- Use a higher Button Scan Rate or Deep Sleep operating mode.

To know more about the steps to reduce power consumption, refer to section 5 in the CY8CMBR2110 Design Guide.

#### Low-Power Sleep Mode

The following flowchart describes the Low-Power Sleep mode operation.

- The Button Scan Rate is equal to the sum of the time the device scans and sleeps.

- The register settings define a Button Scan Rate offset.

- The offset is added to a constant to get the Button Scan Rate.

#### Table 7. Button Scan Rate Constant

- The constant is given in Table 7.

- The range of scan rate is 25 to 561 ms.

#### Figure 36. Low Power Sleep Mode Operation

|              | Button Scan Rate Constant        |                                |                                    |                                |  |  |  |

|--------------|----------------------------------|--------------------------------|------------------------------------|--------------------------------|--|--|--|

| Button Count | Response Time C                  | Optimized Design               | Power Consumption Optimized Design |                                |  |  |  |

|              | Noise Immunity Level<br>"Normal" | Noise Immunity Level<br>"High" | Noise Immunity Level<br>"Normal"   | Noise Immunity Level<br>"High" |  |  |  |

| ≤ 5          | 25 ms                            | 35 ms                          | 35 ms                              | 55 ms                          |  |  |  |

| > 5          | 35 ms                            | 55 ms                          | 35 ms                              | 55 ms                          |  |  |  |

#### **Deep Sleep Mode**

- To enable the Deep Sleep mode, connect the Attention/Sleep line to the host as shown in Figure 37; the host should perform the following steps:

- □ Pull the Attention/Sleep line low

- □ Set the Deep Sleep bit in the Host\_Mode register (in Operating Mode) high

- Wait for 50 ms

- Pull the Attention/Sleep line high

## Figure 37. Attention/Sleep pin Connection to Enable Deep Sleep Mode

- In Deep Sleep mode, all blocks are turned off and the device power consumption is 0.1 µA.

- There is no CapSense scanning in Deep Sleep mode.

- After the device enters Deep Sleep mode, the 'Deep Sleep' bit is automatically cleared.

- The Attention/Sleep line should be pulled low for the device to wake up from Deep Sleep.

- When device comes out of Deep Sleep mode, the CapSense system is re-initialized. The typical time for re-initialization is 20 ms (Normal Noise Immunity level) or 50 ms (High Noise Immunity level). Any button touch within this time is not reported.

- The Deep Sleep bit cannot be set by EZ-Click Customizer Tool and must be set by an external I<sup>2</sup>C communication to the device.

### **Response Time**

Response time is the minimum amount of time the button should be touched for the device to detect as a valid button touch. It is given by the following equations:

1. If Noise Immunity Level is "Normal"

$RT_{CBT} = Button Scan Rate constant + [Button Scan Rate constant \times {Round_{down}((Debounce - 1)/3) + 1}]$

$RT_{FBT} = Button Scan Rate$

+ [Button Scan Rate constant  $\times$  {Round<sub>down</sub>((Debounce - 1)/3) + 1}]

2. If Noise Immunity level is "High".

$RT_{CBT} = Button Scan Rate constant + [Button Scan Rate constant \times Debounce]$

$RT_{FBT} = Button Scan Rate + [Button Scan Rate constant \times Debounce]$

Where

RT<sub>CBT</sub> is Response time for consecutive button touch after first button touch

$\mathsf{RT}_{\mathsf{FBT}}$  is Response time for First button touch

Debounce for CS1-CS9 can be from 1 to 255

Debounce for CS0 can be from 1 to 255

Round<sub>down</sub> is the greatest integer less than or equal to ((Debounce - 1)/3)

Refer to Table 7 on page 21 to obtain Button Scan Rate constant.

For example, consider an eight-button, Response Time-optimized design with the Button Scan Rate offset set to 391 ms. The Noise Immunity level is set to Normal.

Let us assume that CS0 is not used in the design and the Debounce value for each button (CS1–CS8) is set as 3. The Button Scan Rate constant for such a design is 35 ms (see Table 5 on page 17), which results in a Button Scan Rate to be (35 + 391 ms) 426 ms. The response time for such a design is given as:

$RT_{CBT} = 35 + [35 \times \{Round_{down}((3-1)/3) + 1\}] = 70 ms$

$RT_{FBT} = 426 + [35 \times \{Round_{down}((3-1)/3) + 1\}] = 461 \, ms$

## **Device Modes**

The register map is divided into five modes.

- Operating mode

- LED Configuration mode

- Device Configuration mode

- Production Line Test mode

- Debug Data mode

The following sections give an overview of each mode. Each register mode consists of different sets of registers. Refer to the Appendix - Register Map section for description of all the registers in detail.

#### **Operating Mode**

The Host must use this mode after configuring the device in run time. The following can be configured in this mode:

- 1. Host control GPO logic levels

- 2. Deep Sleep mode entry

- 3. Software Reset

- 4. Device mode change

- Host can read the following device information in this mode:

- 1. CapSense current and latched status

- 2. Current configuration (factory default or user configuration)

- 3. Flash checksum

- 4. RAM checksum

- 5. Device ID and firmware revision

#### **LED Configuration Mode**

The Host must use this mode to configure the device and revert back to the Operating mode after configuration.

The Host can configure the following in this mode:

- 1. Analog voltage output settings

- 2. Power-on LED effects

- 3. Button Touch LED effects

- 4. LED ON Time

- 5. Standby Mode LED brightness

- 6. Device Mode change

#### **Device Configuration Mode**

The Host must use this mode to configure the device and then revert back to operating mode after configuration is done. Host can configure the following in this mode:

- 1. I<sup>2</sup>C address

- 2. FSS group buttons

- 3. Toggle ON/OFF option

- 4. Button Sensitivity, Debounce, Finger Threshold

- 5. Buzzer settings

- 6. Automatic threshold settings

- 7. Button Scan rate settings (power settings)

- 8. Noise Immunity settings

- 9. Button Auto Reset time

- 10.Design Optimization settings

- 11.Save settings to flash

- 12.Load factory default configuration

- 13.Device mode change

#### **Production Line Test Mode**

The Host must use this mode only during the design validation and production testing stage of product development.

- The Host can configure the following in this mode:

- 1. Host-controlled GPO logic levels

- 2. Changing device mode

The Host can read the following device information in this mode, which helps in Production Line Test:

- 1. System Diagnostics data

- Button short to ground

- Button short to another button

- $\square$  Button short to  $V_{DD}$

- Button Parasitic capacitance > 40 pF

- $\square$  Improper value of  $C_{\text{MOD}}$  value connected

- 2. All buttons SNR values

- 3. Valid button count

- 4. CapSense current status

#### Debug Data Mode

The Host must use this mode only during the design validation stage of product development.

The Host can configure the following in this mode:

- 1. Host-controlled GPO logic levels

- 2. Parameter type and button number, which the host wants to debug

- 3. Changing device mode

The Host can read the following device information in this mode, which helps in design validation:

- 1. CapSense Raw data (Raw count, baseline and signal)

- 2. CapSense button SNR

- 3. Button parasitic capacitance

- 4. CapSense current status

## Steps to Configure CY8CMBR2110

To configure the CY8CMBR2110, follow these steps:

- 1. Change Device mode to LED Configuration mode.

- 2. Wait for 55 ms.

- 3. Write to all the configuration registers in the LED Configuration mode.

- 4. Wait for 55 ms.

- 5. Change Device mode to Device Configuration mode.

- 6. Wait for 55 ms.

- 7. Write to all the configuration registers in the Device Configuration mode.

- 8. Calculate checksum and enter this value in the registers.

**Checksum** (Checksum\_MSB (0x1E) and Checksum\_LSB (0x1F) in the Device Configuration mode): Checksum is the sum of values of the registers (0x01–0x1F) in the LED Configuration mode and the registers (0x01–0x1D) in the Device Configuration mode. Checksum also takes the values of any reserved register bits. The host should not write to these bits and should add 0 for any such bit, while calculating checksum.

Checksum\_Flash\_xxx registers (in the Operating mode) indicate the checksum stored in the flash. Checksum\_RAM\_xxx registers (in the Operating mode) indicate the checksum calculated by the device and stored in the RAM.

- 9. Wait for 55 ms.

- 10.Read the Checksum matched bit in the Host\_Mode register (in the Device Configuration mode) and verify that it is set to 1. If this bit is not set, start again from the first step and reconfigure the device. The host should keep a backup of the configuration data if this is needed.

**Checksum matched bit**: The CY8CMBR2110 calculates the checksum and compares that with the Checksum register value entered by the host. If both the values match, the Checksum matched bit in the Host\_Mode register (in the Device Configuration mode) is set to 1. If the values do not match (indicating a possible I<sup>2</sup>C write error) this bit is cleared to 0. The host can read the Checksum\_RAM\_xxx register (in the Operating mode) to know the device calculated checksum.

11.If the Checksum matched bit is set to 1, then set the Save to Flash bit in the Host\_mode register.

**Save to Flash bit:** On a Save to Flash, the following sequence is executed:

- The device copies the 64-byte data (LED Configuration mode and Device Configuration mode) to the flash.

- A software reset is done.

- After software reset, the device is in Operating mode.

Any configuration changes are not applicable unless a Save to Flash is done, which is useful when the device has to be configured only once for all future operations. To ensure a flawless Save to Flash, the device power supply must be stable, with V<sub>DD</sub> fluctuations limited to  $\pm 5\%$  of the V<sub>DD</sub>.

12.After a Save to Flash, wait for (T<sub>SAVE\_FLASH</sub> + Device initialization) time. T<sub>SAVE\_FLASH</sub> is mentioned in the Flash Write Time Specifications. The device initialization time is 350 ms (normal Noise Immunity) or 1000 ms (high Noise Immunity). 13.Read the Factory defaults loaded bit in Device\_Stat register (in Operating mode).

**Factory Defaults Loaded bit:** After every reset, the device loads the RAM with the flash content and verifies the RAM checksum with the flash checksum to ensure there is no flash corruption. If the checksum differs, then the device identifies it as a flash corruption and loads the factory default value in the RAM, and sets the Factory Defaults Loaded bit. This resets any register value previously changed by the host. Factory default values of each register are mentioned in the Register Map.

If the factory defaults are loaded, the  $I^2C$  address of the device also changes from the current address (set by the host) to the default address, 37h. The host must then check for the default  $I^2C$  address on the  $I^2C$  bus to communicate with the CY8CMBR2110.

14.Setting the Factory Defaults Loaded bit corrupts the flash and the host needs to reconfigure the device from the first step. If this bit is clear, then the device is successfully configured.

#### CY8CMBR2110 Reset

You can reset the CY8CMBR2110 either through hardware or software using the following options:

- Hardware Reset: For this option, toggle power on the CY8CMBR2110 pins. There are two types of hardware reset:

- Power reset Turn OFF the external power supply on the device V<sub>DD</sub> line and turn ON again (after power down, ensure that the V<sub>DD</sub> is less than 100 mV, before powering backup). On a power reset, there is a high-going pulse of 16 ms on the HostControlGPO1 pin.

- XRES reset Pull the device XRES pin HIGH and then pull LOW. On an XRES reset, there is no pulse on HostControlGPO1 pin. In all other respects, XRES reset is identical to power reset.

On a hardware reset, the LED Configuration mode and Device Configuration mode register values are loaded from the flash to the RAM. All the device blocks are initialized, System Diagnostics is done, and an initial 5-ms pulse is sent on all the GPOx associated with any failing CSx. This is done within 350 ms (normal Noise Immunity) or 1000 ms (high Noise Immunity). Power-on LED Effects (if enabled) are then seen on all the remaining GPOs. After this, the device is in the Operating mode and normal operation begins.

Software Reset: This is done by writing 1 to the Software Reset bit in the Host\_Mode register (in Operating mode). On a software reset, the LED Configuration mode and Device Configuration mode register values are loaded from the flash to the RAM. The device auto-clears the Software Reset bit and all the device blocks are initialized. This is done within 350 ms (normal Noise Immunity) or 1000 ms (high Noise Immunity). After this, the device is in the Operating mode and normal operation begins. System Diagnostics is not done and Power-on LED Effects do not occur. If the user has configured the device for Power-on LED Effects and saved the settings to flash, a hardware reset must be done to see the Power-on LED Effects.

## Layout Guidelines and Best Practices

## Table 8. Layout Guidelines and Best Practices

| SI. No. | Category                                                    | Min                                       | Max     | Recommendations/Remarks                                                                                                                                                                                                                        |  |

|---------|-------------------------------------------------------------|-------------------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1       | Button Shape                                                | -                                         | -       | Solid round pattern, round with LED hole, rectangle with round corners                                                                                                                                                                         |  |

| 2       | Button Size                                                 | 5 mm                                      | 15 mm   | Refer to the Design Toolbox                                                                                                                                                                                                                    |  |

| 3       | Button-Button spacing                                       | Equal to<br>Button<br>Ground<br>Clearance | _       | 8 mm (Y dimension in Figure 39 on page 26)                                                                                                                                                                                                     |  |

| 4       | Button Ground Clearance                                     | 0.5 mm                                    | 2 mm    | Refer to the Design Toolbox (X dimension in Figure 39 on page 26)                                                                                                                                                                              |  |

| 5       | Ground Flood - Top layer                                    | -                                         | -       | Hatched ground 7 mil trace and 45 mil grid (15% filling)                                                                                                                                                                                       |  |

| 6       | Ground Flood - Bottom layer                                 | -                                         | -       | Hatched ground 7 mil trace and 70 mil grid (10% filling)                                                                                                                                                                                       |  |

| 7       | Trace Length from button pad to<br>CapSense controller pins | -                                         | 450 mm  | Refer to the Design Toolbox                                                                                                                                                                                                                    |  |

| 8       | Trace Width                                                 | 0.17 mm                                   | 0.20 mm | 0.17 mm (7 mil)                                                                                                                                                                                                                                |  |

| 9       | Trace Routing                                               | -                                         | -       | Traces should be routed on the non-button side. If any non-CapSense trace crosses CapSense trace, ensure that intersection is orthogonal.                                                                                                      |  |

| 10      | Via Position for the buttons                                | -                                         | -       | Via should be placed near the edge of the button to reduce trace length thereby increasing sensitivity                                                                                                                                         |  |

| 11      | Via Hole Size for button traces                             | -                                         | -       | 10 mil                                                                                                                                                                                                                                         |  |

| 12      | No. of via on button trace                                  | 1                                         | 2       | 1                                                                                                                                                                                                                                              |  |