## **OFN** Quad Flat No-Lead Package

- · Punch or Saw singulated formats

- Body sizes from 2 x 2mm to 12 x 12mm

- Pin counts from 4L to 156L

- · Square or rectangular body sizes

- Leads on four sides of the body (QFN)

- Leads on two opposing sides of the body (DFN)

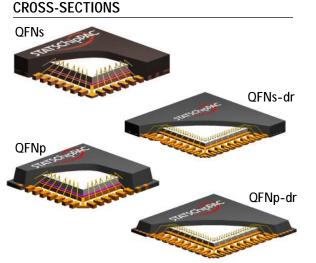

- · Dual row lead design options

- Thin package thickness options

#### FEATURES

- Body sizes: 2 x 2 to 12 x 12mm

- Lead pitch: 0.40, 0.50, 0.65 and 0.80mm

- · Custom lead/pitch configurations available

- Package profile heights: 0.45, 0.50, 0.75, 0.85 and 0.90mm

- Option for non-exposed die pad

- · Green materials set

- Option for PbSn, 100% matte Sn or PPF

- Small chip scale design offers 50% reduction in board space (16L TSSOP vs. 16L QFN)

- 33% weight reduction (in 16L TSSOP vs. 16L QFN)

- Excellent thermal & electrical performance

- Full in-house package and leadframe design capability

- Full in-house assembly and test capability

- Full in-house electrical, thermal and mechanical simulation and measurement capability

- Wide range of open tool leadframe and die pad sizes available

- JEDEC standard compliant (XQFN, UQFN, WQFN, VQFN)

#### DESCRIPTION

STATS ChipPAC's Quad Flat No-Lead (QFN) and Dual Flat No-Lead (DFN) package offering includes the QFNs (saw singulated), QFNp (punch singulated), XQFN, UQFN, WQFN, and QFN-dr. These are leadframe based, plastic encapsulated, chip scale packages in single mold cavity format (punch singulated) or molded array format (saw singulated).

An exposed die pad coupled with extremely low RLC provides excellent electrical and thermal performance enhancements which are ideal for high frequency and high power applications, and are especially suited for wireless and handheld portable applications such as cell phones.

QFN-dr with staggered dual row leads offers higher I/O counts. STATS ChipPAC's QFN packages are currently available in various body sizes and thicknesses, offered in standard and green/lead-free bill of materials and can be processed by conventional SMT equipment, benefiting surface mount operations downstream.

#### **APPLICATIONS**

- RF

- · Power management

- Discretes

- · Analog/Linear

- Logic

- Applications requiring enhanced electrical and thermal performance and reduced package size, thickness and weight

# QFN

### Quad Flat No-Lead Package

#### **SPECIFICATIONS**

| Die Thickness   | 150-350µm                              |

|-----------------|----------------------------------------|

| Gold Wire       | 20-33µm (0.8-1.3mils) diameter         |

| Lead finish     | Matte Tin, preplated Ni/Pd/Au or Sn/Pb |

| Marking         | Laser                                  |

| Packing Options | Tape & reel, tube, JEDEC tray          |

#### RELIABILITY

| Moisture Sensitivity Level | JEDEC MS<br>(depending |

|----------------------------|------------------------|

| Temperature Cycling        | -65°C/15               |

| High Temp Storage          | 150°C, 10              |

| Pressure Cooker Test       | 121°C, 100             |

| Temperature/Humidity Test  | 85°C/85%               |

|                            |                        |

JEDEC MSL 3/2/1 (depending on package) -65°C/150°C, 1000 cycles 150°C, 1000 hrs 121°C, 100% RH, 2 atm, 168 hrs 85°C/85% RH, 1000 hrs

#### THERMAL PERFORMANCE, $\theta$ ja (°C/W)

| Package    | Body Size<br>(mm) | Pad Size<br>(mm) | Die Size<br>(mm) | *Thermal Performance<br>θja(°C/W) | Thermal Vias<br>(on test board) |

|------------|-------------------|------------------|------------------|-----------------------------------|---------------------------------|

| 48L UQFN   | 7 x 7 x 0.50      | 5.1 x 5.1        | 2.26 x 2.26      | 26.3                              | 25                              |

| 64L QFN    | 9 x 9 x 0.85      | 7.3 x 7.3        | 4.52 x 4.52      | 19.2                              | 36                              |

| 76L QFN-dr | 8 x 8 x 0.85      | 5.28 x 5.28      | 4.52 x 4.52      | 26.6                              | 16                              |

Notes: Simulation data for package mounted on 4 layer PCB (per JEDEC JESD51-7) under natural convection as defined in JESD51-2.

#### ELECTRICAL PERFORMANCE

| Package    | Body Size (mm) | Frequency | Length                                          | Inductance (nH)              | Capacitance (pF)                 |

|------------|----------------|-----------|-------------------------------------------------|------------------------------|----------------------------------|

| 48L UQFN   | 7 x 7 x 0.50   | 100 MHz   | Self (short)<br>Mutual<br>Self (long)<br>Mutual | 0.88<br>0.20<br>0.98<br>0.27 | 0.191<br>0.032<br>0.223<br>0.064 |

| 76L QFN-dr | 8 x 8 x 0.85   | 100 MHz   | Self (short)<br>Mutual<br>Self (long)<br>Mutual | 1.33<br>0.45<br>1.68<br>0.53 | 0.180<br>0.080<br>0.270<br>0.110 |

Note: Results are simulated values per JEDEC EIA/JEP123 standards.

#### PACKAGE CONFIGURATIONS

| Pkg Size (mm) | Lead Pitch (mm)     | Lead Count                 |

|---------------|---------------------|----------------------------|

| 2 x 2         | 0.65/0.50           | 4/8                        |

| 2 x 3         | 0.50                | 6/8                        |

| 3 x 3         | 0.80/0.65/0.50/0.40 | 4/8/12/16/20               |

| 4 x 4         | 0.80/0.65/0.50/0.40 | 12/14/16/20/24/28          |

| 5 x 5         | 0.80/0.65/0.50/0.40 | 14/16/20/28/32/40          |

| 6 x 5         | 0.80/0.65/0.50      | 18/20/22/32                |

| 6 x 6         | 0.80/0.65/0.50/0.40 | 20/24/28/32/36/38/40/48    |

| 7 x 7         | 0.80/0.65/0.50/0.40 | 28/32/36/40/44/48/56       |

| 8 x 8         | 0.80/0.65/0.50/0.40 | 28/32/36/40/44/48/52/56/64 |

| 9 x 9         | 0.65/0.50/0.40      | 44/48/56/60/64/72          |

| 10 x 10       | 0.50/0.40           | 64/68/72/88                |

| 10 x 10       | 0.50 dual row       | 124                        |

| 12 x 12       | 0.50 dual row       | 156                        |

|               |                     |                            |

Corporate Office

10 Ang Mo Kio St. 65, #05-17/20 Techpoint, Singapore 569059

Tel: 65-6824-7777

Fax: 65-6720-7823

Global Offices

USA 510-979-8000

JAPAN 81-3-5789-5850

CHINA 86-21-5976-5858

MALAYSIA 603-4257-6222

KOREA 82-31-639-8911

TAIWAN 886-3-593-6565

UK 44-1483-413-700

NETHERLANDS 31-38-333-2023

The STATS ChipPAC logo is a registered trademark of STATS ChipPAC Ltd. All other product names and other company names herein are for identification purposes only and may be the trademarks or registered trademarks of their respective owners. STATS ChipPAC disclaims any and all rights in those marks. STATS ChipPAC be liable for any damages whatsoever arising out of the use of, or inability to use the materials in this document. STATS ChipPAC reserves the right to change the information at any time and without notice.

©Copyright 2006. STATS ChipPAC Ltd. All rights reserved. All rights are started without notice.

Nary Control of the started started without notice.

Control of the started starte