# MQFP-ed

### **Exposed Drop-in Heat Slug Metric Quad Flat Pack**

- 14 x 20mm to 32 x 32mm

- 100 to 240 lead count

- Lead pitch range from 0.80mm to 0.50mm

#### **FEATURES**

Body Sizes: 14 x 20mm to 32 x 32mm

Package Height: 3.4mm

Lead Counts: 100L to 240L

Lead Pitch: 0.80mm to 0.50mm

JEDEC standard compliant

• Lead-free and Green material sets available

#### **APPLICATIONS**

- ASIC

- DSP

- FPGA

- PLD

- Logic, microprocessors / controllers

- High speed logic, high power microprocessors

- 3D graphics, telecom, wireless, audio, CPU / GUI

#### **DESCRIPTION**

STATS ChipPAC's Exposed Drop-In Heat Slug Metric Quad Flat Pack (MQFP-ed) is a thermally enhanced version of the QFP package. Thermal enhancement is achieved by adding a drop-in exposed anodized aluminum heat spreader during the molding process, using a standard leadframe. MQFP-ed typically has 60% higher thermal performance over the standard MQFP and the QFP-d for higher power applications.

## MQFP-ed

## **Exposed Drop-in Heat Slug Metric Quad Flat Pack**

#### **SPECIFICATIONS**

Die Thickness

380-560μm (15-22mils) range preferred

Gold Wire

25/30μm (1.0/1.2mils) diameter, 99.999% Au

**Lead Finish** 85/15 Sn/Pb or Matte Tin

Marking Laser / ink

Packing Options JEDEC tray / tape and reel

#### **RELIABILITY**

Moisture Sensitivity Level JEDEC Level 3

Temperature Cycling -65°C/150°C, 1000 cycles

**High Temperature Storage** 150°C, 500 hrs **Pressure Cooker Test** 121°C 100% RF

121°C 100% RH, 2 atm, 168 hrs

Liquid Thermal Shock (opt) -55°C/125°C, 1000 cycles

#### THERMAL PERFORMANCE, 0ja (°C/W)

| Package | Body Size (mm) | Pad Size (mm) | Die Size (mm) | Thermal Performance, 0ja (°C/W) |

|---------|----------------|---------------|---------------|---------------------------------|

| 208L    | 28 x 28 x 3.4  | 14.0 x 14.0   | 10.2 x 10.2   | 14.9                            |

Note: Simulation data for package mounted on 4 layer PCB (per JEDEC JESD51-7) under natural convection as defined in JESD51-2.

#### **ELECTRICAL PERFORMANCE**

| Package | Body Size (mm) | Pad Size (mm) | Frequency | Self Inductance (nH) | Self Capacitance (pF) |

|---------|----------------|---------------|-----------|----------------------|-----------------------|

| 208L    | 28 x 28 x 3.4  | 10.5 x 10.5   | 100MHz    | 11.6~14.7            | 1.43~1.56             |

Notes: \*Results are simulated. Data is available through 2.5GHz.

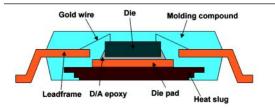

#### **CROSS-SECTION**

#### PACKAGE CONFIGURATIONS

Package Size (mm)

Lead Count

14 x 20

100, 128

28 x 28\*

128, 144, 160, 208

32 x 32

160, 240

Note: \*Cavity down configuation available.

Corporate Office

10 Ang Mo Kio St. 65, #05-17/20 Techpoint, Singapore 569059

Tel: 65-6824-7777

Fax: 65-6720-7823

Global Offices

USA 510-979-8000

JAPAN 81-43-351-3320

CHINA 86-21-5976-5858

MALAYSIA 603-4257-6222

KOREA 82-31-639-8911

TAIWAN 886-3-593-6565

UK 44-1483-413-700

NETHERLANDS 31-38-333-2023

The STATS ChipPAC logo is a registered trademark of STATS ChipPAC Ltd. All other product names and other company names herein are for identification purposes only and may be the trademarks or registered trademarks of their respective owners. STATS ChipPAC disclaims any and all rights in those marks. STATS ChipPAC makes no guarantee or warranty of its accuracy in the information given, or that the use of such information will not infiring on intellectual rights of third parties. Under no circumstances shall STATS ChipPAC be liable for any damages whatsoever arising out of the use of, or inability to use the materials in this document. STATS ChipPAC reserves the right to change the information at any time and without notice.

©Copyright 2005. STATS ChipPAC Ltd. All rights reserved.