# LMH6715 Dual Wideband Video Op Amp

Check for Samples: LMH6715

### **FEATURES**

- $T_A = 25$ °C,  $R_L = 100\Omega$ , Typical Values Unless Specified.

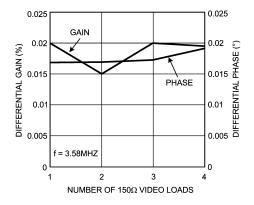

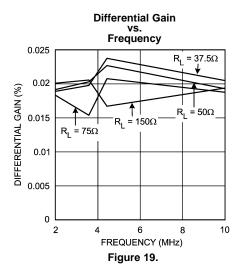

- Very Low Diff. Gain, Phase: 0.02%, 0.02°

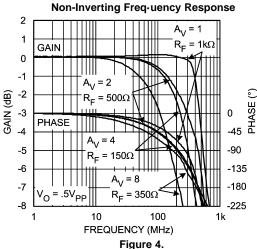

- Wide Bandwidth:  $480MHz (A_V = +1V/V)$ ;  $400MHz (A_V = +2V/V)$

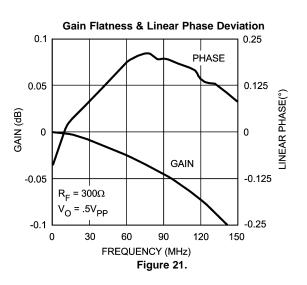

- 0.1dB Gain Flatness to 100MHz

- Low Power: 5.8mA/Channel

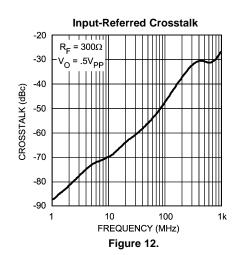

- -70dB Channel-to-Channel Crosstalk (10MHz)

- Fast Slew Rate: 1300V/µs

- **Unity Gain Stable**

- Improved Replacement for CLC412

#### **APPLICATIONS**

- **HDTV, NTSC & PAL Video Systems**

- Video Switching and Distribution

- **IQ Amplifiers**

- Wideband Active Filters

- **Cable Drivers**

- **DC Coupled Single-to-Differential Conversions**

#### DESCRIPTION

The LMH6715 combines TI's VIP10 high speed complementary bipolar process with TI's current feedback topology to produce a very high speed dual op amp. The LMH6715 provides 400MHz small signal bandwidth at a gain of +2V/V and 1300V/µs slew rate while consuming only 5.8mA per amplifier from ±5V supplies.

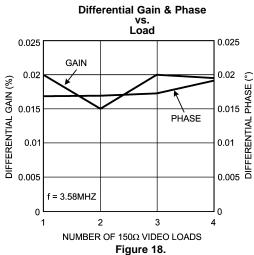

The LMH6715 offers exceptional video performance with its 0.02% and 0.02° differential gain and phase errors for NTSC and PAL video signals while driving up to four back terminated  $75\Omega$  loads. The LMH6715 also offers a flat gain response of 0.1dB to 100MHz and very low channel-to-channel crosstalk of -70dB at 10MHz. Additionally, each amplifier can deliver 70mA of output current. This level of performance makes the LMH6715 an ideal dual op amp for high density, broadcast quality video systems.

The LMH6715's two very well matched amplifiers support a number of applications such as differential line drivers and receivers. In addition, the LMH6715 is well suited for Sallen Key active filters in applications such as anti-aliasing filters for high speed A/D converters. Its small 8-pin SOIC package, low power requirement, low noise and distortion allow the LMH6715 to serve portable RF applications such as IQ channels.

#### **Differential Gain & Phase with Multiple Video Loads**

Figure 1.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

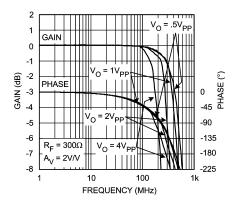

### Frequency Response vs. Vout

Figure 2.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### **Absolute Maximum Ratings**(1)(2)

| Absolute Maximum i           | งนเทยอ           |                    |

|------------------------------|------------------|--------------------|

| ESD Tolerance <sup>(3)</sup> | Human Body Model | 2000V              |

|                              | Machine Model    | 150V               |

| V <sub>CC</sub>              | •                | ±6.75V             |

| I <sub>OUT</sub>             |                  | See <sup>(4)</sup> |

| Common-Mode Input Voltage    |                  | ±V <sub>CC</sub>   |

| Differential Input Voltage   |                  | 2.2V               |

| Maximum Junction Temperatu   | ure              | +150°C             |

| Storage Temperature Range    |                  | -65°C to +150°C    |

| Lead Temperature (Soldering  | 10 sec)          | +300°C             |

|                              |                  |                    |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications, see the Electrical Characteristics tables.

- (2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- (3) Human body model,  $1.5k\Omega$  in series with 100pF. Machine model,  $0\Omega$  In series with 200pF.

- (4) The maximum output current (I<sub>OUT</sub>) is determined by device power dissipation limitations. See the POWER DISSIPATION section for more details.

### **Operating Ratings**

| Thermal Resistance          |                    |                 |  |  |  |  |

|-----------------------------|--------------------|-----------------|--|--|--|--|

| Package                     | $(\theta_{ m JC})$ | $(\theta_{JA})$ |  |  |  |  |

| SOIC                        | 65°C/W             | 145°C/W         |  |  |  |  |

| Operating Temperature Range | -40°C to +85°C     |                 |  |  |  |  |

| Nominal Operating Voltage   |                    | ±5V to ±6V      |  |  |  |  |

## Electrical Characteristics(1)

$A_V$  = +2,  $R_F$  = 500 $\Omega$ ,  $V_{CC}$  = ±5 V,  $R_L$  = 100 $\Omega$ ; unless otherwise specified. **Boldface** limits apply at the temperature extremes.

| Symbol           | Parameter                    | Conditions                               | Min               | Тур  | Max               | Units              |

|------------------|------------------------------|------------------------------------------|-------------------|------|-------------------|--------------------|

| Frequenc         | y Domain Response            |                                          |                   |      |                   | •                  |

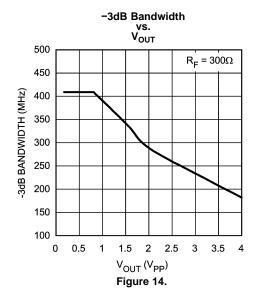

| SSBW             | -3dB Bandwidth               | $V_{OUT} < 0.5V_{PP}, R_F = 300\Omega$   | 280               | 400  |                   | MHz                |

| LSBW             | -3dB Bandwidth               | $V_{OUT} < 4.0 V_{PP}, R_F = 300 \Omega$ |                   | 170  |                   | MHz                |

|                  | Gain Flatness                | V <sub>OUT</sub> < 0.5V <sub>PP</sub>    |                   |      |                   |                    |

| GFP              | Peaking                      | DC to 100MHz, $R_F = 300\Omega$          |                   | 0.1  |                   | dB                 |

| GFR              | Rolloff                      | DC to 100MHz, $R_F = 300\Omega$          |                   | 0.1  |                   | dB                 |

| LPD              | Linear Phase Deviation       | DC to 100MHz, $R_F = 300\Omega$          |                   | 0.25 |                   | deg                |

| DG               | Differential Gain            | $R_L = 150\Omega, 4.43MHz$               |                   | 0.02 |                   | %                  |

| DP               | Differential Phase           | $R_L = 150\Omega, 4.43MHz$               |                   | 0.02 |                   | deg                |

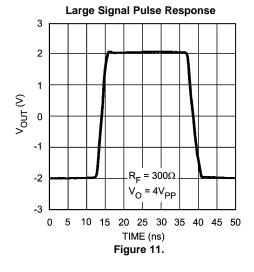

| Time Dom         | nain Response                |                                          | *                 |      |                   | "                  |

| Tr               | Rise and Fall Time           | 0.5V Step                                |                   | 1.4  |                   | ns                 |

|                  |                              | 4V Step                                  |                   | 3    |                   | ns                 |

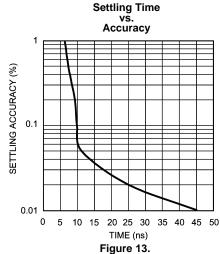

| Ts               | Settling Time to 0.05%       | 2V Step                                  |                   | 12   |                   | ns                 |

| OS               | Overshoot                    | 0.5V Step                                |                   | 1    |                   | %                  |

| SR               | Slew Rate                    | 2V Step                                  |                   | 1300 |                   | V/µs               |

| Distortion       | And Noise Response           |                                          |                   |      |                   | <u>'</u>           |

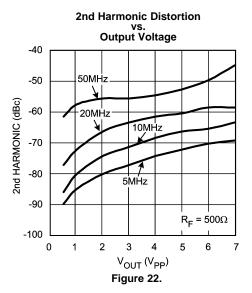

| HD2              | 2nd Harmonic Distortion      | 2V <sub>PP</sub> , 20MHz                 |                   | -60  |                   | dBc                |

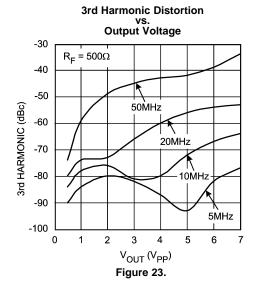

| HD3              | 3rd Harmonic Distortion      | 2V <sub>PP</sub> , 20MHz                 |                   | -75  |                   | dBc                |

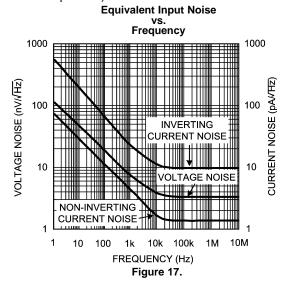

|                  | Equivalent Input Noise       |                                          |                   |      |                   |                    |

| V <sub>N</sub>   | Non-Inverting Voltage        | >1MHz                                    |                   | 3.4  |                   | nV/√ <del>Hz</del> |

| I <sub>N</sub>   | Inverting Current            | >1MHz                                    |                   | 10.0 |                   | pA/√Hz             |

| I <sub>NN</sub>  | Non-Inverting Current        | >1MHz                                    |                   | 1.4  |                   | pA/√ <del>Hz</del> |

| SNF              | Noise Floor                  | >1MHz                                    |                   | -153 |                   | dB <sub>1Hz</sub>  |

| XTLKA            | Crosstalk                    | Input Referred 10MHz                     |                   | -70  |                   | dB                 |

| Static, DC       | Performance                  |                                          |                   |      |                   |                    |

| $V_{IO}$         | Input Offset Voltage         |                                          |                   | ±2   | ±6<br><b>±8</b>   | mV                 |

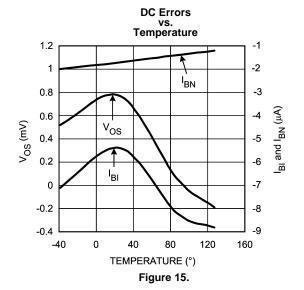

| DV <sub>IO</sub> | Average Drift                |                                          |                   | ±30  |                   | μV/°C              |

| I <sub>BN</sub>  | Input Bias Current           | Non-Inverting                            |                   | ±5   | ±12<br><b>±20</b> | μA                 |

| DI <sub>BN</sub> | Average Drift                |                                          |                   | ±30  |                   | nA/°C              |

| I <sub>BI</sub>  | Input Bias Current           | Inverting                                |                   | ±6   | ±21<br><b>±35</b> | μA                 |

| DI <sub>BI</sub> | Average Drift                |                                          |                   | ±20  |                   | nA/°C              |

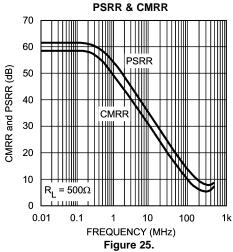

| PSRR             | Power Supply Rejection Ratio | DC                                       | 46<br><b>44</b>   | 60   |                   | dB                 |

| CMRR             | Common Mode Rejection Ratio  | DC                                       | 50<br><b>47</b>   | 56   |                   | dB                 |

| I <sub>CC</sub>  | Supply Current per Amplifier | R <sub>L</sub> = ∞                       | 4.7<br><b>4.1</b> | 5.8  | 7.6<br><b>8.1</b> | mA                 |

| Miscellan        | eous Performance             |                                          |                   |      |                   |                    |

| R <sub>IN</sub>  | Input Resistance             | Non-Inverting                            |                   | 1000 |                   | kΩ                 |

| C <sub>IN</sub>  | Input Capacitance            | Non-Inverting                            |                   | 1.0  |                   | pF                 |

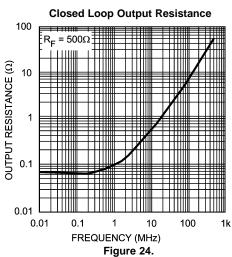

| R <sub>OUT</sub> | Output Resistance            | Closed Loop                              |                   | .06  |                   | Ω                  |

<sup>(1)</sup> Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that T<sub>J</sub> = T<sub>A</sub>. No specification of parametric performance is indicated in the electrical tables under conditions of internal self heating where T<sub>J</sub> > T<sub>A</sub>. See Application Section for information on temperature de-rating of this device." Min/Max ratings are based on product characterization and simulation. Individual parameters are tested as noted.

# Electrical Characteristics<sup>(1)</sup> (continued)

$A_V$  = +2,  $R_F$  = 500 $\Omega$ ,  $V_{CC}$  = ±5 V,  $R_L$  = 100 $\Omega$ ; unless otherwise specified. **Boldface** limits apply at the temperature extremes.

| Symbol          | Parameter            | Conditions         | Min          | Тур  | Max | Units |

|-----------------|----------------------|--------------------|--------------|------|-----|-------|

| Vo              | Output Voltage Range | R <sub>L</sub> = ∞ |              | ±4.0 |     | V     |

| V <sub>OL</sub> |                      | $R_L = 100\Omega$  | ±3.5<br>±3.4 | ±3.9 |     | V     |

| CMIR            | Input Voltage Range  | Common Mode        |              | ±2.2 |     | V     |

| Io              | Output Current       |                    |              | 70   |     | mA    |

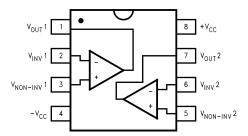

## **Connection Diagram**

Figure 3. 8-Pin SOIC, Top View

Product Folder Links: LMH6715

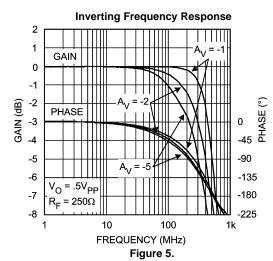

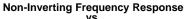

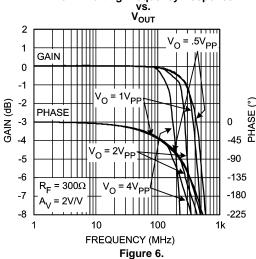

### **Typical Performance Characteristics**

$(T_A = 25^{\circ}C, V_{CC} = \pm 5V, A_V = \pm 2V/V, R_F = 500\Omega, R_L = 100\Omega, unless otherwise specified).$

# Non-Inverting Frequency Response

### **Typical Performance Characteristics (continued)**

$(T_A = 25^{\circ}C, V_{CC} = \pm 5V, A_V = \pm 2V/V, R_F = 500\Omega, R_L = 100\Omega, unless otherwise specified).$

### **Typical Performance Characteristics (continued)**

$(T_A = 25^{\circ}C, V_{CC} = \pm 5V, A_V = \pm 2V/V, R_F = 500\Omega, R_L = 100\Omega, unless otherwise specified).$

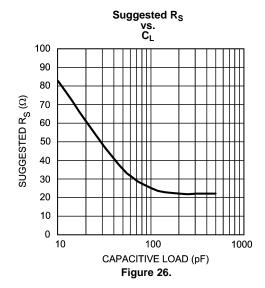

### **Typical Performance Characteristics (continued)**

$(T_A = 25^{\circ}C, V_{CC} = \pm 5V, A_V = \pm 2V/V, R_F = 500\Omega, R_L = 100\Omega, unless otherwise specified).$

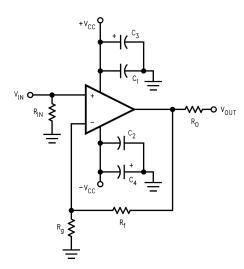

#### **APPLICATION SECTION**

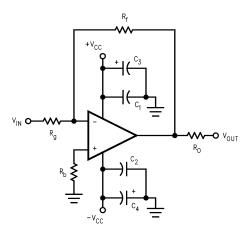

Figure 27. Non-Inverting Configuration with Power Supply Bypassing

Figure 28. Inverting Configuration with Power Supply Bypassing

#### **Application Introduction**

Offered in an 8-pin package for reduced space and cost, the wideband LMH6715 dual current-feedback op amp provides closely matched DC and AC electrical performance characteristics making the part an ideal choice for wideband signal processing. Applications such as broadcast quality video systems, IQ amplifiers, filter blocks, high speed peak detectors, integrators and transimedance amplifiers will all find superior performance in the LMH6715 dual op amp.

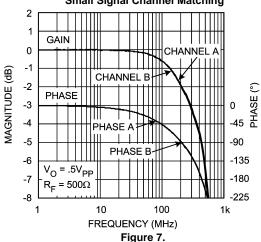

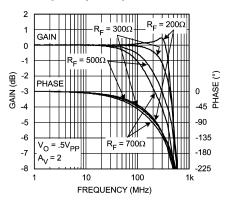

### **FEEDBACK RESISTOR SELECTION**

One of the key benefits of a current feedback operational amplifier is the ability to maintain optimum frequency response independent of gain by using appropriate values for the feedback resistor ( $R_F$ ). The Electrical Characteristics and Typical Performance plots specify an  $R_F$  of  $500\Omega$ , a gain of +2V/V and ±5V power supplies (unless otherwise specified). Generally, lowering  $R_F$  from it's recommended value will peak the frequency response and extend the bandwidth while increasing the value of  $R_F$  will cause the frequency response to roll off faster. Reducing the value of  $R_F$  too far below it's recommended value will cause overshoot, ringing and, eventually, oscillation.

#### Frequency Response vs. R<sub>F</sub>

Figure 29.

Figure 29 shows the LMH6715's frequency response as  $R_F$  is varied ( $R_L$  = 100 $\Omega$ ,  $A_V$  = +2). This plot shows that an  $R_F$  of 200 $\Omega$  results in peaking and marginal stability. An  $R_F$  of 300 $\Omega$  gives near maximal bandwidth and gain flatness with good stability, but with very light loads ( $R_L$  > 300 $\Omega$ ) the device may show some peaking. An  $R_F$  of 500 $\Omega$  gives excellent stability with good bandwidth and is the recommended value for most applications. Since all applications are slightly different it is worth some experimentation to find the optimal  $R_F$  for a given circuit. For more information see Application Note OA-13 (Literature Number SNOA366) which describes the relationship between  $R_F$  and closed-loop frequency response for current feedback operational amplifiers.

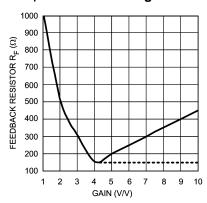

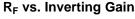

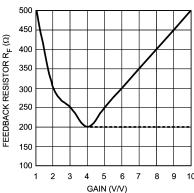

When configuring the LMH6715 for gains other than +2V/V, it is usually necessary to adjust the value of the feedback resistor. The two plots labeled shown in Figure 30 and Figure 31 provide recommended feedback resistor values for a number of gain selections.

#### R<sub>F</sub> vs. Non-Inverting Gain

Figure 30.

Both plots show the value of  $R_F$  approaching a minimum value (dashed line) at high gains. Reducing the feedback resistor below this value will result in instability and possibly oscillation. The recommended value of  $R_F$  is depicted by the solid line, which begins to increase at higher gains. The reason that a higher  $R_F$  is required at higher gains is the need to keep  $R_G$  from decreasing too far below the output impedance of the input buffer. For the LMH6715 the output resistance of the input buffer is approximately  $160\Omega$  and  $50\Omega$  is a practical lower limit for  $R_G$ . Due to the limitations on  $R_G$  the LMH6715 begins to operate in a gain bandwidth limited fashion for gains of  $\pm 5 \text{V/V}$  or greater.

Figure 31.

When using the LMH6715 as a replacement for the CLC412, identical bandwidth can be obtained by using an appropriate value of  $R_F$ . The chart "Frequency Response vs.  $R_F$ " (see Figure 29) shows that an  $R_F$  of approximately  $700\Omega$  will provide bandwidth very close to that of the CLC412. At other gains a similar increase in  $R_F$  can be used to match the new and old parts.

#### **CIRCUIT LAYOUT**

With all high frequency devices, board layouts with stray capacitances have a strong influence over AC performance. The LMH6715 is no exception and its input and output pins are particularly sensitive to the coupling of parasitic capacitances (to AC ground) arising from traces or pads placed too closely (<0.1") to power or ground planes. In some cases, due to the frequency response peaking caused by these parasitics, a small adjustment of the feedback resistor value will serve to compensate the frequency response. Also, it is very important to keep the parasitic capacitance across the feedback resistor to an absolute minimum.

The performance plots in the data sheet can be reproduced using the evaluation boards available from Texas Instruments. The LMH730036 board uses all SMT parts for the evaluation of the LMH6715. The board can serve as an example layout for the final production printed circuit board.

Care must also be taken with the LMH6715's layout in order to achieve the best circuit performance, particularly channel-to-channel isolation. The decoupling capacitors (both tantalum and ceramic) must be chosen with good high frequency characteristics to decouple the power supplies and the physical placement of the LMH6715's external components is critical. Grouping each amplifier's external components with their own ground connection and separating them from the external components of the opposing channel with the maximum possible distance is recommended. The input ( $R_{IN}$ ) and gain setting resistors ( $R_F$ ) are the most critical. It is also recommended that the ceramic decoupling capacitor ( $0.1\mu F$  chip or radial-leaded with low ESR) should be placed as closely to the power pins as possible.

#### **POWER DISSIPATION**

Follow these steps to determine the Maximum power dissipation for the LMH6715:

- 1. Calculate the quiescent (no-load) power:  $P_{AMP} = I_{CC} (V_{CC} V_{EE})$

- 2. Calculate the RMS power at the output stage:  $P_O = (V_{CC} V_{LOAD})(I_{LOAD})$ , where  $V_{LOAD}$  and  $I_{LOAD}$  are the voltage and current across the external load.

- 3. Calculate the total RMS power:  $Pt = P_{AMP} + P_{O}$

The maximum power that the LMH6715, package can dissipate at a given temperature can be derived with the following equation:

Pmax =  $(150^{\circ} - \text{Tamb})/\theta_{JA}$ , where Tamb = Ambient temperature (°C) and  $\theta_{JA}$  = Thermal resistance, from junction to ambient, for a given package (°C/W). For the SOIC package  $\theta_{JA}$  is 145°C/W. (1)

Copyright © 2002–2013, Texas Instruments Incorporated

Product Folder Links: LMH6715

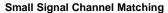

#### **MATCHING PERFORMANCE**

With proper board layout, the AC performance match between the two LMH6715's amplifiers can be tightly controlled as shown in Typical Performance plot labeled "Small-Signal Channel Matching".

The measurements were performed with SMT components using a feedback resistor of 300 $\Omega$  at a gain of +2V/V.

The LMH6715's amplifiers, built on the same die, provide the advantage of having tightly matched DC characteristics.

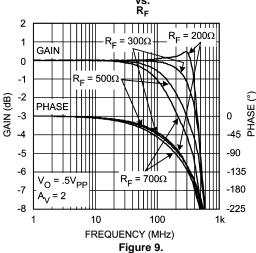

#### SLEW RATE AND SETTLING TIME

One of the advantages of current-feedback topology is an inherently high slew rate which produces a wider full power bandwidth. The LMH6715 has a typical slew rate of  $1300V/\mu s$ . The required slew rate for a design can be calculated by the following equation:  $SR = 2\pi f V_{pk}$ .

Careful attention to parasitic capacitances is critical to achieving the best settling time performance. The LMH6715 has a typical short term settling time to 0.05% of 12ns for a 2V step. Also, the amplifier is virtually free of any long term thermal tail effects at low gains.

When measuring settling time, a solid ground plane should be used in order to reduce ground inductance which can cause common-ground-impedance coupling. Power supply and ground trace parasitic capacitances and the load capacitance will also affect settling time.

Placing a series resistor ( $R_s$ ) at the output pin is recommended for optimal settling time performance when driving a capacitive load. The Typical Performance plot labeled " $R_s$  and Settling Time vs. Capacitive Load" provides a means for selecting a value of  $R_s$  for a given capacitive load.

#### **DC & NOISE PERFORMANCE**

A current-feedback amplifier's input stage does not have equal nor correlated bias currents, therefore they cannot be canceled and each contributes to the total DC offset voltage at the output by the following equation:

$$V_{OFFSET} = \pm \left[I_{BN} \times R_{S} \left[1 + \frac{R_{f}}{R_{g}}\right] + V_{IO} \left[1 + \frac{R_{f}}{R_{g}}\right] + I_{BI} \times R_{f}\right]$$

(2)

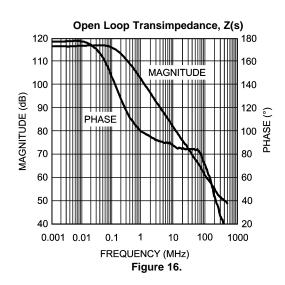

The input resistance is the resistance looking from the non-inverting input back toward the source. For inverting DC-offset calculations, the source resistance seen by the input resistor  $R_g$  must be included in the output offset calculation as a part of the non-inverting gain equation. Application note OA-07 (Literature Number SNOA365) gives several circuits for DC offset correction. The noise currents for the inverting and non-inverting inputs are graphed in the Typical Performance plot labeled "Equivalent Input Noise". A more complete discussion of amplifier input-referred noise and external resistor noise contribution can be found in OA-12 (Literature Number SNOA375).

#### **DIFFERENTIAL GAIN & PHASE**

The LMH6715 can drive multiple video loads with very low differential gain and phase errors. Figure 19 and Figure 20 show performance for loads from 1 to 4. The Electrical Characteristics table also specifies performance for one 150Ω load at 4.43MHz. For NTSC video, the performance specifications also apply. Application note OA-24 (Literature Number SNOA370) "Measuring and Improving Differential Gain & Differential Phase for Video", describes in detail the techniques used to measure differential gain and phase.

#### I/O VOLTAGE & OUTPUT CURRENT

The usable common-mode input voltage range (CMIR) of the LMH6715 specified in the Electrical Characteristics table of the data sheet shows a range of ±2.2 volts. Exceeding this range will cause the input stage to saturate and clip the output signal.

The output voltage range is determined by the load resistor and the choice of power supplies. With  $\pm 5$  volts the class A/B output driver will typically drive  $\pm 3.9$ V into a load resistance of  $100\Omega$ . Increasing the supply voltages will change the common-mode input and output voltage swings while at the same time increase the internal junction temperature.

#### **Applications Circuits**

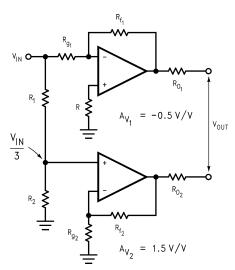

#### SINGLE-TO-DIFFERENTIAL LINE DRIVER

The LMH6715's well matched AC channel-response allows a single-ended input to be transformed to highly matched push-pull driver. From a 1V single-ended input the circuit of Figure 32 produces 1V differential signal between the two outputs. For larger signals the input voltage divider ( $R_1 = 2R_2$ ) is necessary to limit the input voltage on channel 2.

Figure 32. Single-to-Differential Line Driver

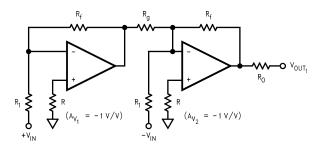

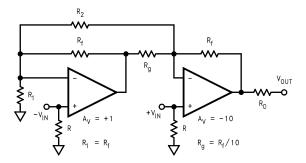

#### **DIFFERENTIAL LINE RECEIVER**

Figure 33 and Figure 34 show two different implementations of an instrumentation amplifier which convert differential signals to single-ended. Figure 34 allows CMRR adjustment through R<sub>2</sub>.

Figure 33. Differential Line Receiver

Figure 34. Differential Line Receiver with CMRR Adjustment

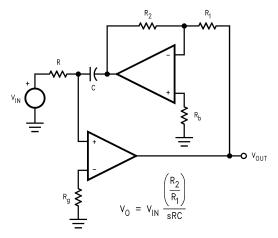

#### NON-INVERTING CURRENT-FEEDBACK INTEGRATOR

The circuit of Figure 35 achieves its high speed integration by placing one of the LMH6715's amplifiers in the feedback loop of the second amplifier configured as shown.

Figure 35. Current Feedback Integrator

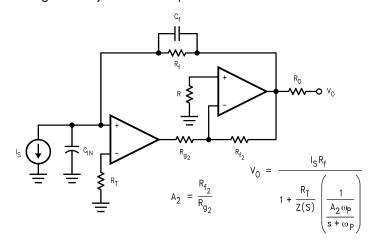

#### LOW NOISE WIDE-BANDWIDTH TRANSIMPEDANCE AMPLIFIER

Figure 36 implements a low noise transimpedance amplifier using both channels of the LMH6715. This circuit takes advantage of the lower input bias current noise of the non-inverting input and achieves negative feedback through the second LMH6715 channel. The output voltage is set by the value of  $R_{\rm F}$  while frequency compensation is achieved through the adjustment of  $R_{\rm T}$ .

Figure 36. Low-Noise, Wide Bandwidth, Transimpedance Amp.

### **REVISION HISTORY**

| Changes from Revision B (April 2013) to Revision C |                                                    |      |  |  |  |

|----------------------------------------------------|----------------------------------------------------|------|--|--|--|

| •                                                  | Changed layout of National Data Sheet to TI format | . 14 |  |  |  |

29-Jun-2017

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                   | Lead/Ball Finish (6) | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|----------------------------|----------------------|--------------------|--------------|-------------------------|---------|

| LMH6715 MDC      | ACTIVE | DIESALE      | Υ                  | 0    | 400            | Green (RoHS<br>& no Sb/Br) | Call TI              | Level-1-NA-UNLIM   | -40 to 85    |                         | Samples |

| LMH6715MA        | NRND   | SOIC         | D                  | 8    | 95             | TBD                        | Call TI              | Call TI            | -40 to 85    | LMH67<br>15MA           |         |

| LMH6715MA/NOPB   | ACTIVE | SOIC         | D                  | 8    | 95             | Green (RoHS<br>& no Sb/Br) | CU SN                | Level-1-260C-UNLIM | -40 to 85    | LMH67<br>15MA           | Samples |

| LMH6715MAX/NOPB  | ACTIVE | SOIC         | D                  | 8    | 2500           | Green (RoHS<br>& no Sb/Br) | CU SN                | Level-1-260C-UNLIM | -40 to 85    | LMH67<br>15MA           | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

### **PACKAGE OPTION ADDENDUM**

29-Jun-2017

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com 23-Sep-2013

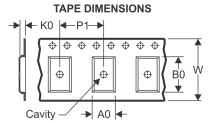

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

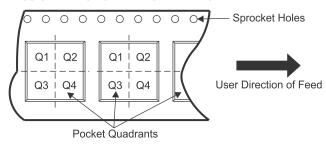

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device          | Package<br>Type | Package<br>Drawing |   |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LMH6715MAX/NOPB | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.5        | 5.4        | 2.0        | 8.0        | 12.0      | Q1               |

www.ti.com 23-Sep-2013

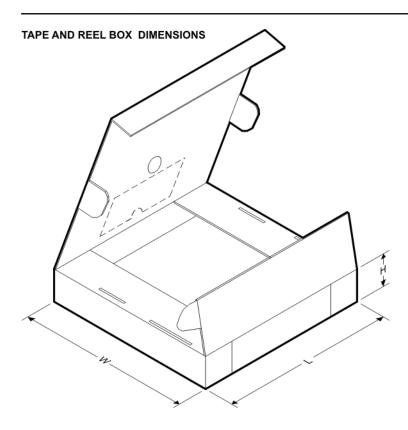

#### \*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| LMH6715MAX/NOPB | SOIC         | D               | 8    | 2500 | 367.0       | 367.0      | 35.0        |  |

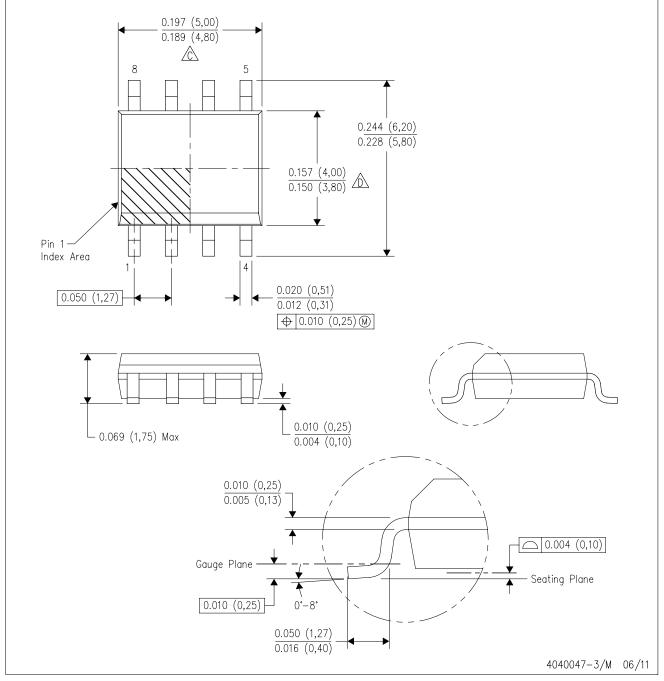

# D (R-PDSO-G8)

### PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.006 (0,15) each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0,43) each side.

- E. Reference JEDEC MS-012 variation AA.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated (TI) reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.

TI's published terms of sale for semiconductor products (http://www.ti.com/sc/docs/stdterms.htm) apply to the sale of packaged integrated circuit products that TI has qualified and released to market. Additional terms may apply to the use or sale of other types of TI products and services.

Reproduction of significant portions of TI information in TI data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such reproduced documentation. Information of third parties may be subject to additional restrictions. Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyers and others who are developing systems that incorporate TI products (collectively, "Designers") understand and agree that Designers remain responsible for using their independent analysis, evaluation and judgment in designing their applications and that Designers have full and exclusive responsibility to assure the safety of Designers' applications and compliance of their applications (and of all TI products used in or for Designers' applications) with all applicable regulations, laws and other applicable requirements. Designer represents that, with respect to their applications, Designer has all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. Designer agrees that prior to using or distributing any applications that include TI products, Designer will thoroughly test such applications and the functionality of such TI products as used in such applications.

TI's provision of technical, application or other design advice, quality characterization, reliability data or other services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using TI Resources in any way, Designer (individually or, if Designer is acting on behalf of a company, Designer's company) agrees to use any particular TI Resource solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

Designer is authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY DESIGNER AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Unless TI has explicitly designated an individual product as meeting the requirements of a particular industry standard (e.g., ISO/TS 16949 and ISO 26262), TI is not responsible for any failure to meet such industry standard requirements.

Where TI specifically promotes products as facilitating functional safety or as compliant with industry functional safety standards, such products are intended to help enable customers to design and create their own applications that meet applicable functional safety standards and requirements. Using products in an application does not by itself establish any safety features in the application. Designers must ensure compliance with safety-related requirements and standards applicable to their applications. Designer may not use any TI products in life-critical medical equipment unless authorized officers of the parties have executed a special contract specifically governing such use. Life-critical medical equipment is medical equipment where failure of such equipment would cause serious bodily injury or death (e.g., life support, pacemakers, defibrillators, heart pumps, neurostimulators, and implantables). Such equipment includes, without limitation, all medical devices identified by the U.S. Food and Drug Administration as Class III devices and equivalent classifications outside the U.S.

TI may expressly designate certain products as completing a particular qualification (e.g., Q100, Military Grade, or Enhanced Product). Designers agree that it has the necessary expertise to select the product with the appropriate qualification designation for their applications and that proper product selection is at Designers' own risk. Designers are solely responsible for compliance with all legal and regulatory requirements in connection with such selection.

Designer will fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of Designer's non-compliance with the terms and provisions of this Notice.