# life.augmented

## STM32F410x8 STM32F410xB

# Arm<sup>®</sup>-Cortex<sup>®</sup>-M4 32b MCU+FPU, 125 DMIPS, 128KB Flash, 32KB RAM, 9 TIMs, 1 ADC, 1 DAC, 1 LPTIM, 9 comm. interfaces

Datasheet - production data

#### **Features**

- Dynamic Efficiency Line with eBAM (enhanced Batch Acquisition Mode)

- 1.7 V to 3.6 V power supply

- -40 °C to 85/105/125 °C temperature range

- Core: Arm<sup>®</sup> 32-bit Cortex<sup>®</sup>-M4 CPU with FPU, Adaptive real-time accelerator (ART Accelerator<sup>™</sup>) allowing 0-wait state execution from Flash memory, frequency up to 100 MHz, memory protection unit, 125 DMIPS/1.25 DMIPS/MHz (Dhrystone 2.1), and DSP instructions

- Memories

- Up to 128 Kbytes of Flash memory

- 512 bytes of OTP memory

- 32 Kbytes of SRAM

- Clock, reset and supply management

- 1.7 V to 3.6 V application supply and I/Os

- POR, PDR, PVD and BOR

- 4-to-26 MHz crystal oscillator

- Internal 16 MHz factory-trimmed RC

- 32 kHz oscillator for RTC with calibration

- Internal 32 kHz RC with calibration

- Power consumption

- Run: 89 µA/MHz (peripheral off)

- Stop (Flash in Stop mode, fast wakeup time): 40 μA Typ @ 25 °C; 49 μA max @25 °C

- Stop (Flash in Deep power down mode, slow wakeup time): down to 6 μA @ 25 °C; 14 μA max @25 °C

- Standby: 2.4  $\mu A$  @25 °C / 1.7 V without RTC; 12  $\mu A$  @85 °C @1.7 V

- V<sub>BAT</sub> supply for RTC: 1 μA @25 °C

- 1×12-bit, 2.4 MSPS ADC: up to 16 channels

- 1×12-bit D/A converter

- General-purpose DMA: 16-stream DMA controllers with FIFOs and burst support

- Up to 9 timers

- One low-power timer (available in Stop mode)

- One 16-bit advanced motor-control timer

- Three 16-bit general purpose timers

- One 32-bit timer up to 100 MHz with up to four IC/OC/PWM or pulse counter and quadrature (incremental) encoder input

- Two watchdog timers (independent window)

- SysTick timer.

- Debug mode

- Serial wire debug (SWD) & JTAG interfaces

- Cortex<sup>®</sup> -M4 Embedded Trace Macrocell™

- Up to 50 I/O ports with interrupt capability

- Up to 45 fast I/Os up to 100 MHz

- Up to 49 5 V-tolerant I/Os

- Up to 9 communication interfaces

- Up to 3x I<sup>2</sup>C interfaces (SMBus/PMBus) including 1x I<sup>2</sup>C Fast-mode at 1 MHz

- Up to 3 USARTs (2 x 12.5 Mbit/s, 1 x 6.25 Mbit/s), ISO 7816 interface, LIN, IrDA, modem control)

- Up to 3 SPI/I2Ss (up to 50 Mbit/s SPI or I2S audio protocol)

- True random number generator

- CRC calculation unit

- 96-bit unique ID

- RTC: subsecond accuracy, hardware calendar

- All packages are ECOPACK<sup>®</sup>2

Table 1. Device summary

|             | •                                        |

|-------------|------------------------------------------|

| Reference   | Part number                              |

| STM32F410x8 | STM32F410T8, STM32F410C8,<br>STM32F410R8 |

| STM32F410xB | STM32F410TB, STM32F410CB,<br>STM32F410RB |

Contents STM32F410x8/B

## **Contents**

| 1 | Intro | duction                                                                             | . 11 |

|---|-------|-------------------------------------------------------------------------------------|------|

| 2 | Desc  | ription                                                                             | . 12 |

|   | 2.1   | Compatibility with STM32F4 series                                                   | . 14 |

| 3 | Func  | ctional overview                                                                    | . 16 |

|   | 3.1   | Arm <sup>®</sup> Cortex <sup>®</sup> -M4 with FPU core with embedded Flash and SRAM | . 16 |

|   | 3.2   | Adaptive real-time memory accelerator (ART Accelerator™)                            | . 16 |

|   | 3.3   | Batch Acquisition mode (BAM)                                                        | . 16 |

|   | 3.4   | Memory protection unit                                                              | . 17 |

|   | 3.5   | Embedded Flash memory                                                               | . 17 |

|   | 3.6   | CRC (cyclic redundancy check) calculation unit                                      | . 17 |

|   | 3.7   | Embedded SRAM                                                                       | . 17 |

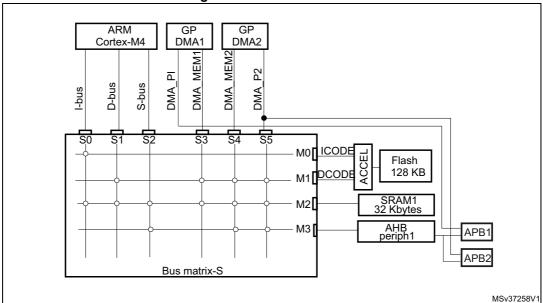

|   | 3.8   | Multi-AHB bus matrix                                                                | . 18 |

|   | 3.9   | DMA controller (DMA)                                                                | . 18 |

|   | 3.10  | Nested vectored interrupt controller (NVIC)                                         | . 19 |

|   | 3.11  | External interrupt/event controller (EXTI)                                          | . 19 |

|   | 3.12  | Clocks and startup                                                                  | . 19 |

|   | 3.13  | Boot modes                                                                          | . 20 |

|   | 3.14  | Power supply schemes                                                                | . 20 |

|   | 3.15  | Power supply supervisor                                                             | . 21 |

|   |       | 3.15.1 Internal reset ON                                                            | 21   |

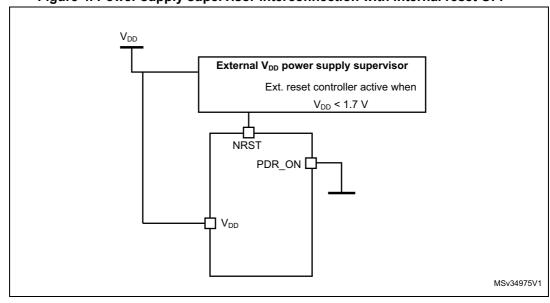

|   |       | 3.15.2 Internal reset OFF                                                           | 21   |

|   | 3.16  | Voltage regulator                                                                   | . 22 |

|   |       | 3.16.1 Internal power supply supervisor availability                                | 22   |

|   | 3.17  | Real-time clock (RTC) and backup registers                                          | . 23 |

|   | 3.18  | Low-power modes                                                                     | . 23 |

|   | 3.19  | V <sub>BAT</sub> operation                                                          | . 24 |

|   | 3.20  | Timers and watchdogs                                                                | . 24 |

|   |       | 3.20.1 Advanced-control timers (TIM1)                                               | 26   |

|   |       | 3.20.2 General-purpose timers (TIM5, TIM9 and TIM11)                                |      |

|   |       | 3.20.3 Basic timer (TIM6)                                                           | 26   |

|                    | 3.20.4                                                                                      | Low-power timer (LPTIM1)                                                                                                                                                                                                                                                                                                         | . 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | 3.20.5                                                                                      | Independent watchdog                                                                                                                                                                                                                                                                                                             | . 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    | 3.20.6                                                                                      | Window watchdog                                                                                                                                                                                                                                                                                                                  | . 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    | 3.20.7                                                                                      | SysTick timer                                                                                                                                                                                                                                                                                                                    | . 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.21               | Inter-int                                                                                   | tegrated circuit interface (I2C)                                                                                                                                                                                                                                                                                                 | . 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.22               | Univers                                                                                     | al synchronous/asynchronous receiver transmitters (USART) .                                                                                                                                                                                                                                                                      | . 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.23               | Serial p                                                                                    | peripheral interface (SPI)                                                                                                                                                                                                                                                                                                       | . 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.24               | Inter-int                                                                                   | tegrated sound (I <sup>2</sup> S)                                                                                                                                                                                                                                                                                                | . 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.25               | Randor                                                                                      | n number generator (RNG)                                                                                                                                                                                                                                                                                                         | . 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.26               | Genera                                                                                      | I-purpose input/outputs (GPIOs)                                                                                                                                                                                                                                                                                                  | . 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.27               | Analog-                                                                                     | -to-digital converter (ADC)                                                                                                                                                                                                                                                                                                      | . 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.28               | Temper                                                                                      | rature sensor                                                                                                                                                                                                                                                                                                                    | . 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

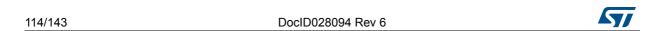

| 3.29               | Digital-t                                                                                   | to-analog converter (DAC)                                                                                                                                                                                                                                                                                                        | . 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.30               | Serial w                                                                                    | vire JTAG debug port (SWJ-DP)                                                                                                                                                                                                                                                                                                    | . 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.31               | Embedo                                                                                      | ded Trace Macrocell™                                                                                                                                                                                                                                                                                                             | . 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

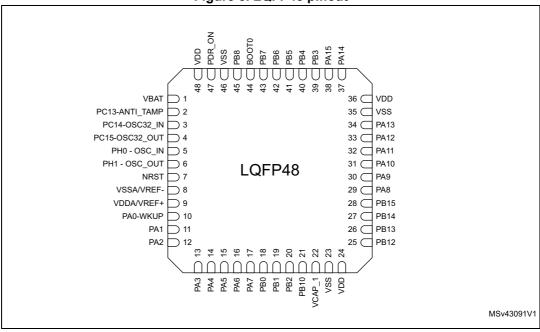

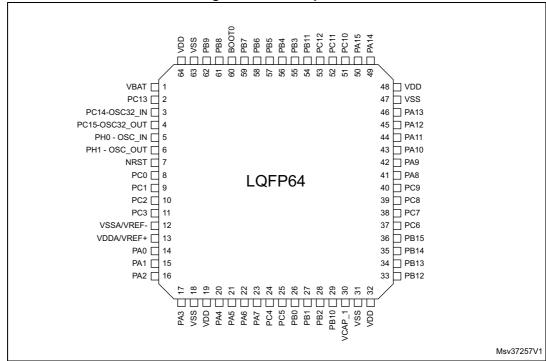

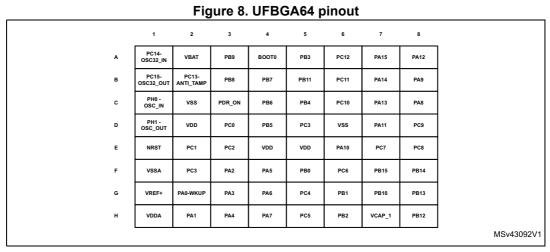

| Pinou              | ıts and                                                                                     | pin description                                                                                                                                                                                                                                                                                                                  | . 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    |                                                                                             |                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Memo               | orv man                                                                                     | pping                                                                                                                                                                                                                                                                                                                            | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                    |                                                                                             | pping                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                    |                                                                                             | aracteristics                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                    | rical ch                                                                                    | aracteristics                                                                                                                                                                                                                                                                                                                    | . <b>48</b><br>. 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Elect              | rical cha<br>Parame<br>6.1.1                                                                | aracteristics eter conditions                                                                                                                                                                                                                                                                                                    | . <b>48</b><br>. 48<br>. 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Elect              | rical cha<br>Parame<br>6.1.1<br>6.1.2                                                       | aracteristics eter conditions                                                                                                                                                                                                                                                                                                    | . <b>48</b><br>. 48<br>. 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Elect              | Parame<br>6.1.1<br>6.1.2<br>6.1.3                                                           | aracteristics eter conditions  Minimum and maximum values  Typical values  Typical curves                                                                                                                                                                                                                                        | . <b>48</b><br>. 48<br>. 48<br>. 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Elect              | Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4                                                  | aracteristics eter conditions  Minimum and maximum values  Typical values  Typical curves  Loading capacitor                                                                                                                                                                                                                     | . <b>48</b><br>. 48<br>. 48<br>. 48<br>. 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Elect              | Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5                                         | aracteristics eter conditions  Minimum and maximum values  Typical values  Typical curves  Loading capacitor  Pin input voltage                                                                                                                                                                                                  | . <b>48</b><br>. 48<br>. 48<br>. 48<br>. 48<br>. 49                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Elect              | Parame 6.1.1 6.1.2 6.1.3 6.1.4 6.1.5 6.1.6                                                  | aracteristics eter conditions  Minimum and maximum values  Typical values  Typical curves  Loading capacitor  Pin input voltage  Power supply scheme                                                                                                                                                                             | . 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 49<br>. 50                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <b>Elect</b> : 6.1 | Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7                       | aracteristics  eter conditions  Minimum and maximum values  Typical values  Typical curves  Loading capacitor  Pin input voltage  Power supply scheme  Current consumption measurement                                                                                                                                           | . 48<br>. 48<br>. 48<br>. 48<br>. 48<br>. 49<br>. 50                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <b>Elect</b> : 6.1 | Parame 6.1.1 6.1.2 6.1.3 6.1.4 6.1.5 6.1.6 6.1.7 Absolut                                    | aracteristics  eter conditions  Minimum and maximum values  Typical values  Typical curves  Loading capacitor  Pin input voltage  Power supply scheme  Current consumption measurement  te maximum ratings                                                                                                                       | . <b>48</b><br>. 48<br>. 48<br>. 48<br>. 49<br>. 50<br>. 51                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <b>Elect</b> : 6.1 | Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>Absolut<br>Operati | aracteristics  eter conditions  Minimum and maximum values  Typical values  Typical curves  Loading capacitor  Pin input voltage  Power supply scheme  Current consumption measurement  te maximum ratings  ng conditions                                                                                                        | . <b>48</b><br>. 48<br>. 48<br>. 48<br>. 49<br>. 50<br>. 51<br>. 51                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <b>Elect</b> : 6.1 | Parame 6.1.1 6.1.2 6.1.3 6.1.4 6.1.5 6.1.6 6.1.7 Absolut Operati 6.3.1                      | aracteristics  eter conditions  Minimum and maximum values  Typical values  Typical curves  Loading capacitor  Pin input voltage  Power supply scheme  Current consumption measurement  ete maximum ratings  ng conditions  General operating conditions                                                                         | . 48<br>. 48<br>. 48<br>. 48<br>. 49<br>. 50<br>. 51<br>. 53<br>. 53                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <b>Elect</b> : 6.1 | Parame 6.1.1 6.1.2 6.1.3 6.1.4 6.1.5 6.1.6 6.1.7 Absolut Operati 6.3.1 6.3.2                | eter conditions  Minimum and maximum values  Typical values  Typical curves  Loading capacitor  Pin input voltage  Power supply scheme  Current consumption measurement  the maximum ratings  Ing conditions  General operating conditions  VCAP_1 external capacitor                                                            | . 48<br>. 48<br>. 48<br>. 48<br>. 49<br>. 50<br>. 51<br>. 53<br>. 53                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <b>Elect</b> : 6.1 | Parame 6.1.1 6.1.2 6.1.3 6.1.4 6.1.5 6.1.6 6.1.7 Absolut Operati 6.3.1 6.3.2 6.3.3          | eter conditions  Minimum and maximum values  Typical values  Typical curves  Loading capacitor  Pin input voltage  Power supply scheme  Current consumption measurement  ete maximum ratings  ng conditions  General operating conditions  VCAP_1 external capacitor  Operating conditions at power-up/power-down (regulator ON) | . 48<br>. 48<br>. 48<br>. 48<br>. 49<br>. 50<br>. 51<br>. 53<br>. 53<br>. 56<br>. 56                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <b>Elect</b> : 6.1 | Parame 6.1.1 6.1.2 6.1.3 6.1.4 6.1.5 6.1.6 6.1.7 Absolut Operati 6.3.1 6.3.2                | eter conditions  Minimum and maximum values  Typical values  Typical curves  Loading capacitor  Pin input voltage  Power supply scheme  Current consumption measurement  the maximum ratings  Ing conditions  General operating conditions  VCAP_1 external capacitor                                                            | . 48<br>. 48<br>. 48<br>. 48<br>. 49<br>. 50<br>. 51<br>. 53<br>. 53<br>. 56<br>. 56                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    | 3.22<br>3.23<br>3.24<br>3.25<br>3.26<br>3.27<br>3.28<br>3.29<br>3.30<br>3.31                | 3.20.5 3.20.6 3.20.7 3.21 Inter-int 3.22 Univers 3.23 Serial p 3.24 Inter-int 3.25 Randor 3.26 Genera 3.27 Analog 3.28 Temper 3.29 Digital-t 3.30 Serial v 3.31 Embedo                                                                                                                                                           | 3.20.5 Independent watchdog 3.20.6 Window watchdog 3.20.7 SysTick timer 3.21 Inter-integrated circuit interface (I2C) 3.22 Universal synchronous/asynchronous receiver transmitters (USART) 3.23 Serial peripheral interface (SPI) 3.24 Inter-integrated sound (I <sup>2</sup> S) 3.25 Random number generator (RNG) 3.26 General-purpose input/outputs (GPIOs) 3.27 Analog-to-digital converter (ADC) 3.28 Temperature sensor 3.29 Digital-to-analog converter (DAC) 3.30 Serial wire JTAG debug port (SWJ-DP) |

| 4/143   |       |                  | DocID028094 Rev 6                                             | <b>47/</b> |

|---------|-------|------------------|---------------------------------------------------------------|------------|

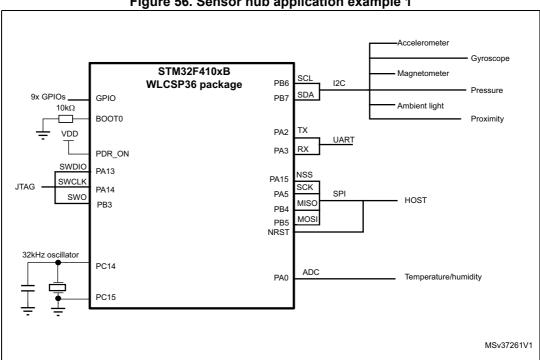

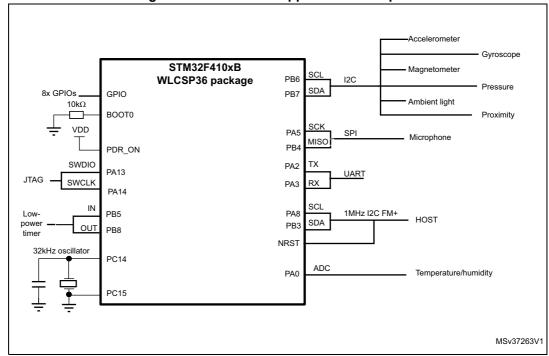

|         | B.1   | Sensor           | Hub application example                                       | 138        |

| Appendi | x B A | Applicati        | ion block diagrams                                            | 138        |

|         | A.1   | Operati          | ing conditions                                                | 137        |

| Appendi | x A F | Recomm           | nendations when using the internal reset OFF                  | 137        |

| 8       | Part  | number           | ing                                                           | 136        |

|         |       | 7.6.1            | Reference document                                            | 135        |

|         | 7.6   |                  | al characteristics                                            |            |

|         | 7.5   |                  | A64 package information                                       |            |

|         | 7.4   |                  | 4 package information                                         |            |

|         | 7.3   |                  | 8 package information                                         |            |

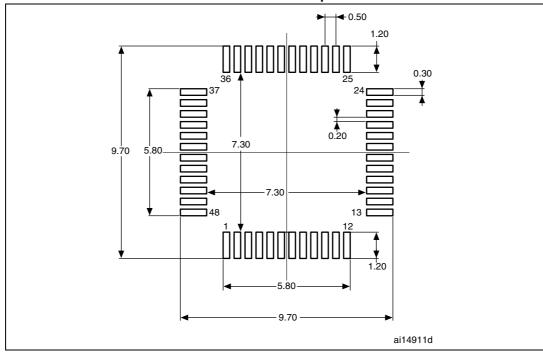

|         | 7.2   |                  | PN48 package information                                      |            |

|         | 7.1   |                  | P36 package information                                       |            |

| 7       |       | _                | ormation                                                      |            |

|         |       |                  |                                                               |            |

|         |       | 6.3.25           | RTC characteristics                                           |            |

|         |       | 6.3.24           | Embedded reference voltage                                    |            |

|         |       | 6.3.22<br>6.3.23 | V <sub>BAT</sub> monitoring characteristics                   |            |

|         |       | 6.3.21           | Temperature sensor characteristics                            |            |

|         |       | 6.3.20           | 12-bit ADC characteristics                                    |            |

|         |       | 6.3.19           | Communications interfaces                                     |            |

|         |       | 6.3.18           | TIM timer characteristics                                     |            |

|         |       | 6.3.17           | NRST pin characteristics                                      |            |

|         |       | 6.3.16           | I/O port characteristics                                      |            |

|         |       | 6.3.15           | I/O current injection characteristics                         | 91         |

|         |       | 6.3.14           | Absolute maximum ratings (electrical sensitivity)             | 91         |

|         |       | 6.3.13           | EMC characteristics                                           | 89         |

|         |       | 6.3.12           | Memory characteristics                                        | 87         |

|         |       | 6.3.11           | PLL spread spectrum clock generation (SSCG) characteristics . | 86         |

|         |       | 6.3.10           | PLL characteristics                                           | 84         |

|         |       | 6.3.9            | Internal clock source characteristics                         | 83         |

|         |       | 6.3.8            | External clock source characteristics                         | 78         |

|         |       | 6.3.7            | Wakeup time from low-power modes                              | 77         |

|         |       | 6.3.6            | Supply current characteristics                                | 58         |

| STM32F410x8/B   | Contents                             |

|-----------------|--------------------------------------|

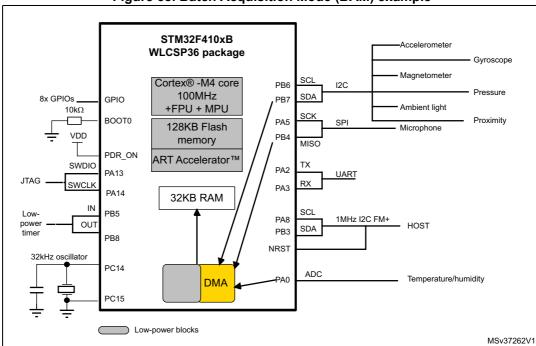

| B.2             | Batch Acquisition Mode (BAM) example |

| Revision histor | y                                    |

List of tables STM32F410x8/B

## List of tables

| Table 1.  | Device summary                                                                                | . 1 |

|-----------|-----------------------------------------------------------------------------------------------|-----|

| Table 2.  | STM32F410x8/B features and peripheral counts                                                  |     |

| Table 3.  | Embedded bootloader interfaces                                                                |     |

| Table 4.  | Regulator ON/OFF and internal power supply supervisor availability                            |     |

| Table 5.  | Timer feature comparison                                                                      |     |

| Table 6.  | Comparison of I2C analog and digital filters                                                  |     |

| Table 7.  | USART feature comparison                                                                      |     |

| Table 8.  | Legend/abbreviations used in the pinout table                                                 |     |

| Table 9.  | STM32F410x8/B pin definitions                                                                 |     |

| Table 10. | Alternate function mapping                                                                    |     |

| Table 11. | STM32F410x8/B register boundary addresses                                                     |     |

| Table 12. | Voltage characteristics                                                                       |     |

| Table 13. | Current characteristics                                                                       |     |

| Table 14. | Thermal characteristics                                                                       |     |

| Table 15. | General operating conditions                                                                  |     |

| Table 16. | Features depending on the operating power supply range                                        |     |

| Table 17. | VCAP_1 operating conditions                                                                   |     |

| Table 18. | Operating conditions at power-up / power-down (regulator ON)                                  |     |

| Table 19. | Operating conditions at power-up / power-down (regulator OFF)                                 |     |

| Table 20. | Embedded reset and power control block characteristics                                        |     |

| Table 21. | Typical and maximum current consumption, code with data processing (ART                       |     |

|           | accelerator disabled) running from SRAM - V <sub>DD</sub> = 1.7 V                             | 59  |

| Table 22. | Typical and maximum current consumption, code with data processing (ART                       |     |

|           | accelerator disabled) running from SRAM - V <sub>DD</sub> = 3.6 V                             | 60  |

| Table 23. | Typical and maximum current consumption in run mode, code with data processing                |     |

|           | (ART accelerator enabled except prefetch) running from Flash memory- V <sub>DD</sub> = 1.7 V  | 61  |

| Table 24. | Typical and maximum current consumption in run mode, code with data processing                |     |

|           | (ART accelerator enabled except prefetch) running from Flash memory - V <sub>DD</sub> = 3.6 V | 62  |

| Table 25. | Typical and maximum current consumption in run mode, code with data processing                |     |

|           | (ART accelerator disabled) running from Flash memory - V <sub>DD</sub> = 3.6 V                | 63  |

| Table 26. | Typical and maximum current consumption in run mode, code with data processing                |     |

|           | (ART accelerator disabled) running from Flash memory - V <sub>DD</sub> = 1.7 V                | 64  |

| Table 27. | Typical and maximum current consumption in run mode, code with data processing                |     |

|           | (ART accelerator enabled with prefetch) running from Flash memory - V <sub>DD</sub> = 3.6 V   | 65  |

| Table 28. | Typical and maximum current consumption in Sleep mode - V <sub>DD</sub> = 3.6 V               |     |

| Table 29. | Typical and maximum current consumption in Sleep mode - $V_{DD}$ = 1.7 V                      |     |

| Table 30. | Typical and maximum current consumptions in Stop mode - $V_{DD}$ = 1.7 V                      | 70  |

| Table 31. | Typical and maximum current consumption in Stop mode - V <sub>DD</sub> =3.6 V                 | 70  |

| Table 32. | Typical and maximum current consumption in Standby mode - V <sub>DD</sub> = 1.7 V             |     |

| Table 33. | Typical and maximum current consumption in Standby mode - V <sub>DD</sub> = 3.6 V             |     |

| Table 34. | Typical and maximum current consumptions in V <sub>BAT</sub> mode                             |     |

|           | (LSE and RTC ON, LSE low- drive mode)                                                         | 71  |

| Table 35. | Switching output I/O current consumption                                                      | 74  |

| Table 36. | Peripheral current consumption                                                                |     |

| Table 37. | Low-power mode wakeup timings                                                                 |     |

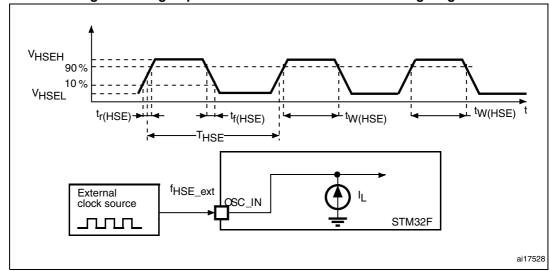

| Table 38. | High-speed external user clock characteristics                                                |     |

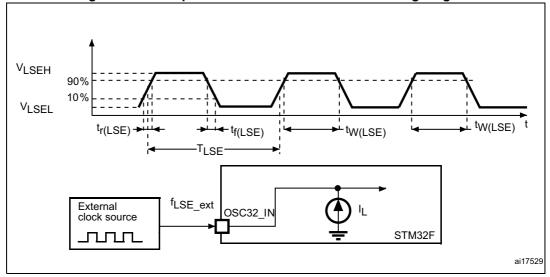

| Table 39. | Low-speed external user clock characteristics                                                 | 79  |

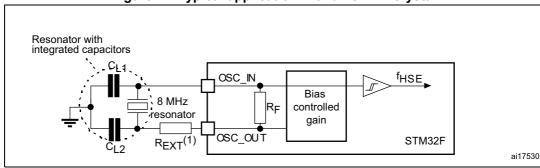

| Table 40. | HSE 4-26 MHz oscillator characteristics                                                       | 81  |

STM32F410x8/B List of tables

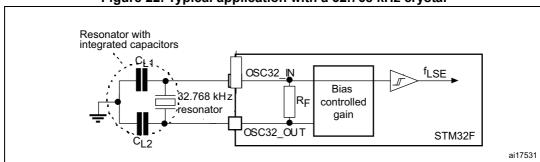

| Table 41.              | LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz)                                    | 82  |

|------------------------|---------------------------------------------------------------------------------------------------|-----|

| Table 42.              | HSI oscillator characteristics                                                                    | 83  |

| Table 43.              | LSI oscillator characteristics                                                                    |     |

| Table 44.              | Main PLL characteristics                                                                          |     |

| Table 45.              | SSCG parameter constraints                                                                        |     |

| Table 46.              | Flash memory characteristics                                                                      |     |

| Table 47.              | Flash memory programming                                                                          |     |

| Table 48.              | Flash memory programming with V <sub>PP</sub> voltage                                             |     |

| Table 49.              | Flash memory endurance and data retention                                                         |     |

| Table 50.              | EMS characteristics                                                                               |     |

| Table 51.              | EMI characteristics for LQFP64                                                                    |     |

| Table 52.              | ESD absolute maximum ratings                                                                      |     |

| Table 53.              | Electrical sensitivities                                                                          |     |

| Table 54.              | I/O current injection susceptibility                                                              |     |

| Table 55.              | I/O static characteristics                                                                        |     |

| Table 56.<br>Table 57. | Output voltage characteristics                                                                    |     |

| Table 57.              | I/O AC characteristics                                                                            |     |

| Table 56.              | TIMx characteristics                                                                              |     |

| Table 60.              | I <sup>2</sup> C characteristics.                                                                 |     |

| Table 61.              | SCL frequency (f <sub>PCLK1</sub> = 50 MHz, V <sub>DD</sub> = V <sub>DD_I2C</sub> = 3.3 V)        |     |

| Table 62.              | SCL frequency (f <sub>PCLK1</sub> = 42 MHz., V <sub>DD</sub> = V <sub>DD I2C</sub> = 3.3 V)       | 101 |

| Table 63.              | FMPI <sup>2</sup> C characteristics                                                               | 102 |

| Table 64.              | SPI dynamic characteristics                                                                       |     |

| Table 65.              | I <sup>2</sup> S dynamic characteristics                                                          |     |

| Table 66.              | ADC characteristics                                                                               |     |

| Table 67.              | ADC accuracy at f <sub>ADC</sub> = 18 MHz                                                         |     |

| Table 68.              | ADC accuracy at f <sub>ADC</sub> = 30 MHz                                                         |     |

| Table 69.              | ADC accuracy at f <sub>ADC</sub> = 36 MHz                                                         |     |

| Table 70.              | ADC dynamic accuracy at f <sub>ADC</sub> = 18 MHz - limited test conditions                       | 111 |

| Table 71.              | ADC dynamic accuracy at f <sub>ADC</sub> = 36 MHz - limited test conditions                       | 111 |

| Table 72.              | Temperature sensor characteristics                                                                | 114 |

| Table 73.              | Temperature sensor calibration values                                                             | 114 |

| Table 74.              | V <sub>BAT</sub> monitoring characteristics                                                       |     |

| Table 75.              | Embedded internal reference voltage                                                               |     |

| Table 76.              | Internal reference voltage calibration values                                                     |     |

| Table 77.              | DAC characteristics                                                                               |     |

| Table 78.              | RTC characteristics                                                                               | 118 |

| Table 79.              | WLCSP36 - 36-pin, 2.553 x 2.579 mm, 0.4 mm pitch wafer level chip scale                           | 400 |

| T-1-1- 00              | package mechanical data                                                                           |     |

| Table 80.              | WLCSP36 recommended PCB design rules (0.4 mm pitch)                                               | 121 |

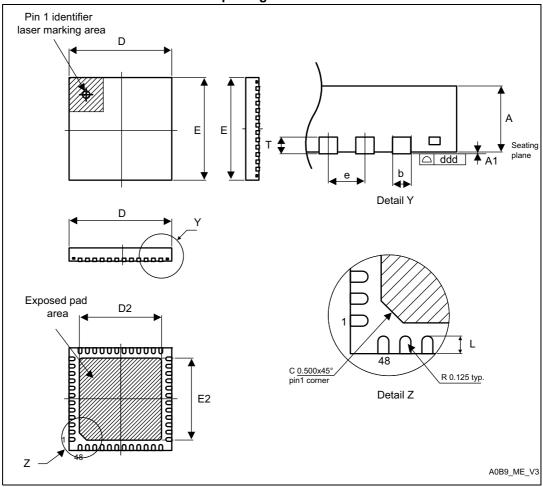

| Table 81.              | UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat package mechanical data | 100 |

| Table 82.              | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package                                           | 123 |

| i abie 62.             | mechanical data                                                                                   | 126 |

| Table 83.              | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package mechanical data                         |     |

| Table 84.              | UFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch ultra profile fine pitch ball grid array                | 150 |

| TADIO UT.              | package mechanical data                                                                           | 132 |

| Table 85.              | UFBGA64 recommended PCB design rules (0.5 mm pitch BGA)                                           |     |

| Table 86.              | Package thermal characteristics                                                                   |     |

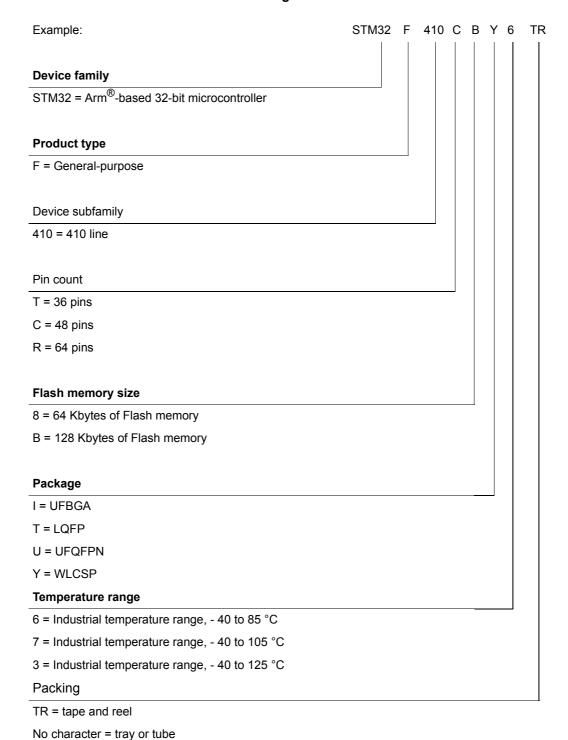

| Table 87.              | Ordering information scheme                                                                       |     |

| Table 88.              | Limitations depending on the operating power supply range                                         |     |

|                        |                                                                                                   |     |

| List of tabl | les                       | STM32F410x8/B |

|--------------|---------------------------|---------------|

|              |                           |               |

| Table 89.    | Document revision history | <br>140       |

STM32F410x8/B List of figures

## List of figures

| Figure 1.  | Compatible board design for LQFP64 package                                  |     |

|------------|-----------------------------------------------------------------------------|-----|

| Figure 2.  | STM32F410x8/B block diagram                                                 |     |

| Figure 3.  | Multi-AHB matrix                                                            |     |

| Figure 4.  | Power supply supervisor interconnection with internal reset OFF             |     |

| Figure 5.  | LQFP48 pinout                                                               |     |

| Figure 6.  | LQFP64 pinout                                                               |     |

| Figure 7.  | UFQFPN48 pinout                                                             |     |

| Figure 8.  | UFBGA64 pinout                                                              |     |

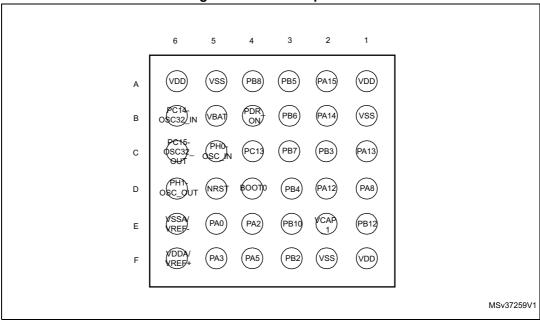

| Figure 9.  | WLCSP36 pinout                                                              |     |

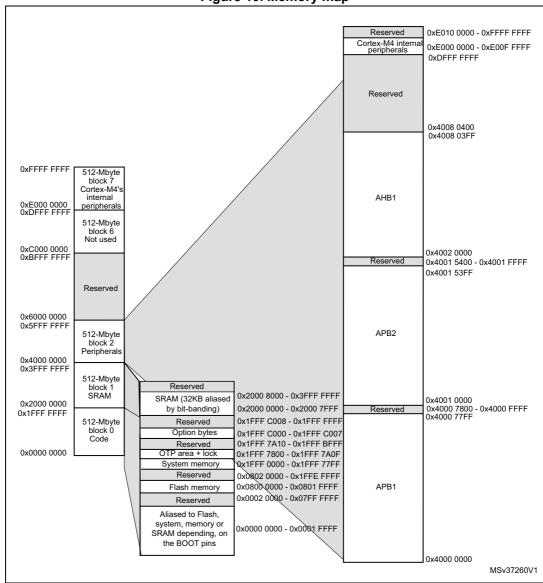

| Figure 10. | Memory map                                                                  |     |

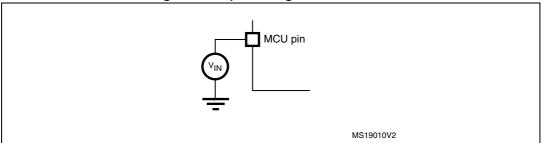

| Figure 11. | Pin loading conditions                                                      |     |

| Figure 12. | Input voltage measurement                                                   |     |

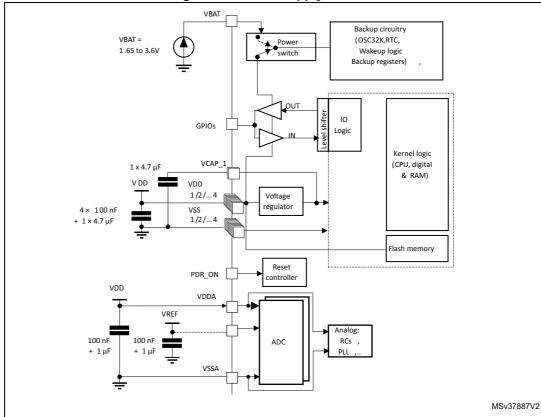

| Figure 13. | Power supply scheme                                                         |     |

| Figure 14. | Current consumption measurement scheme                                      |     |

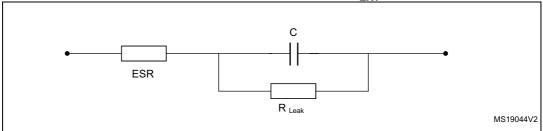

| Figure 15. | External capacitor C <sub>EXT</sub>                                         | 56  |

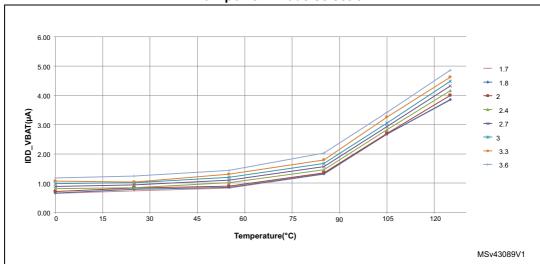

| Figure 16. | Typical V <sub>BAT</sub> current consumption (LSE and RTC ON/LSE oscillator |     |

|            | in "low power" mode selection                                               | 72  |

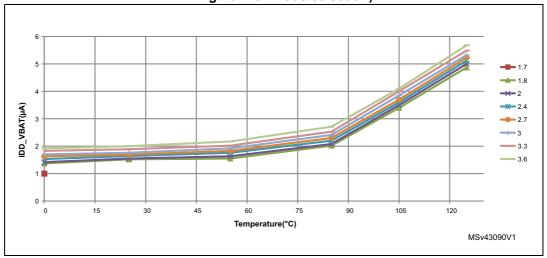

| Figure 17. | Typical V <sub>BAT</sub> current consumption (LSE and RTC ON/LSE oscillator |     |

|            | in "high-drive" mode selection)                                             |     |

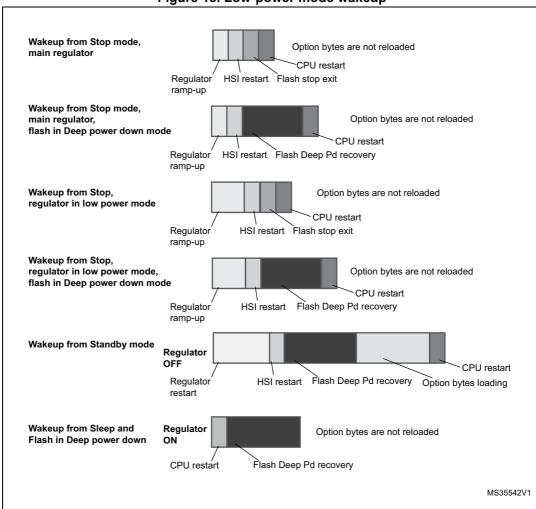

| Figure 18. | Low-power mode wakeup                                                       |     |

| Figure 19. | High-speed external clock source AC timing diagram                          |     |

| Figure 20. | Low-speed external clock source AC timing diagram                           |     |

| Figure 21. | Typical application with an 8 MHz crystal                                   |     |

| Figure 22. | Typical application with a 32.768 kHz crystal                               |     |

| Figure 23. | ACC <sub>HSI</sub> versus temperature                                       |     |

| Figure 24. | ACC <sub>LSI</sub> versus temperature                                       |     |

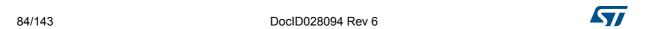

| Figure 25. | PLL output clock waveforms in center spread mode                            |     |

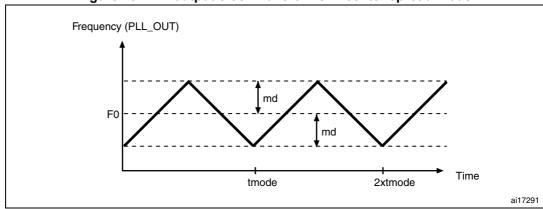

| Figure 26. | PLL output clock waveforms in down spread mode                              |     |

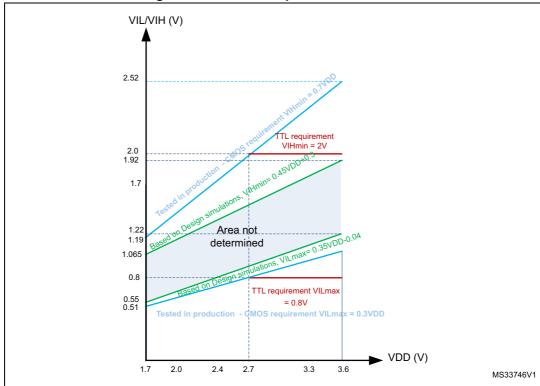

| Figure 27. | FT/TC I/O input characteristics                                             |     |

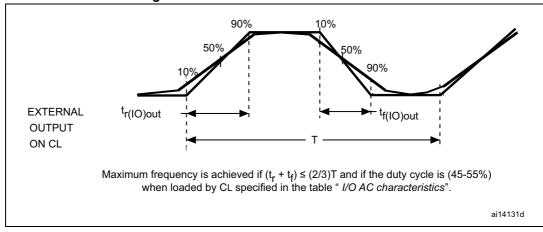

| Figure 28. | I/O AC characteristics definition                                           |     |

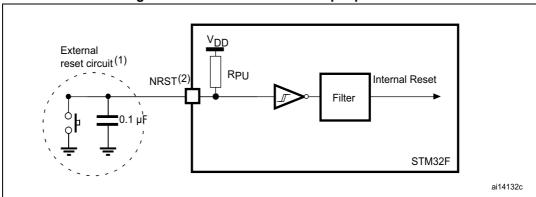

| Figure 29. | Recommended NRST pin protection                                             |     |

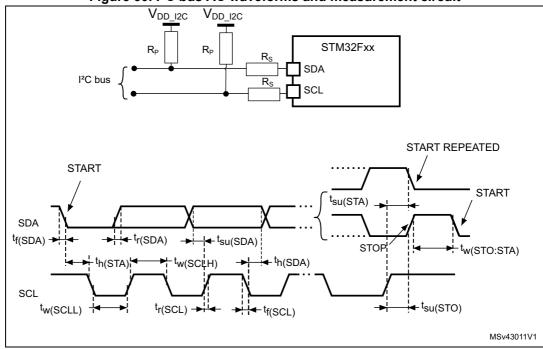

| Figure 30. | I <sup>2</sup> C bus AC waveforms and measurement circuit                   |     |

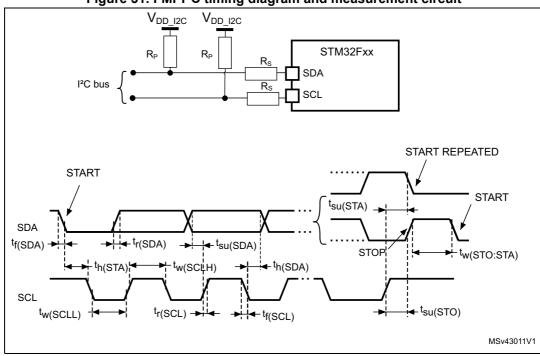

| Figure 31. | FMPI <sup>2</sup> C timing diagram and measurement circuit                  |     |

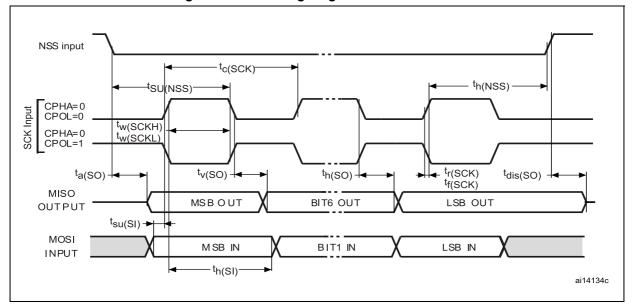

| Figure 32. | SPI timing diagram - slave mode and CPHA = 0                                |     |

| Figure 33. | SPI timing diagram - slave mode and CPHA = 1 <sup>(1)</sup>                 |     |

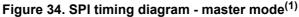

| Figure 34. | SPI timing diagram - master mode <sup>(1)</sup>                             | 106 |

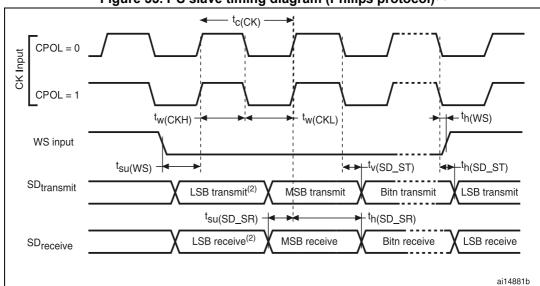

| Figure 35. | I <sup>2</sup> S slave timing diagram (Philips protocol) <sup>(1)</sup>     | 108 |

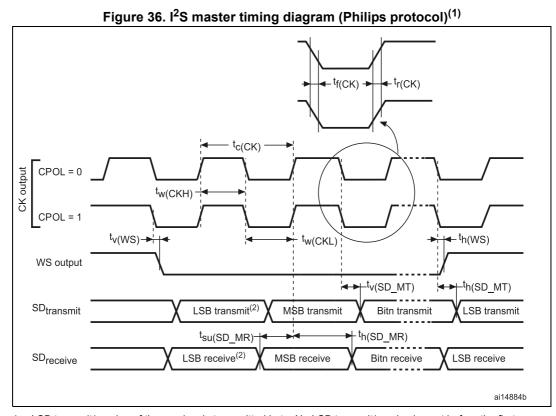

| Figure 36. | I <sup>2</sup> S master timing diagram (Philips protocol) <sup>(1)</sup>    |     |

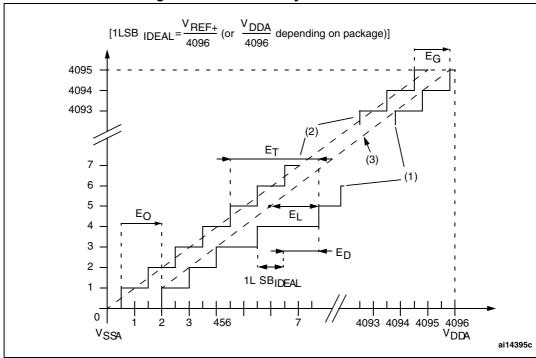

| Figure 37. | ADC accuracy characteristics                                                |     |

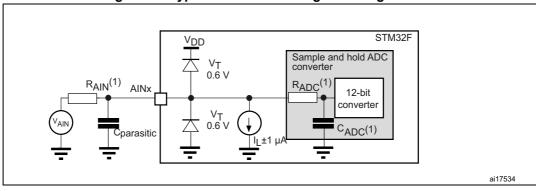

| Figure 38. | Typical connection diagram using the ADC                                    |     |

| Figure 39. | Power supply and reference decoupling                                       |     |

| Figure 40. | 12-bit buffered/non-buffered DAC                                            | 118 |

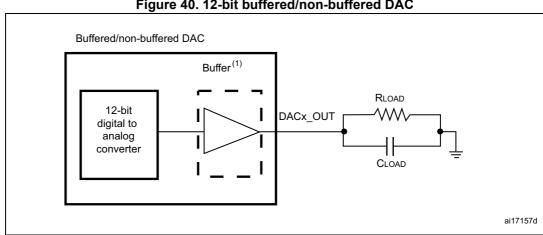

| Figure 41. | WLCSP36 - 36-pin, 2.553 x 2.579 mm, 0.4 mm pitch wafer level chip scale     |     |

|            | package outline                                                             | 119 |

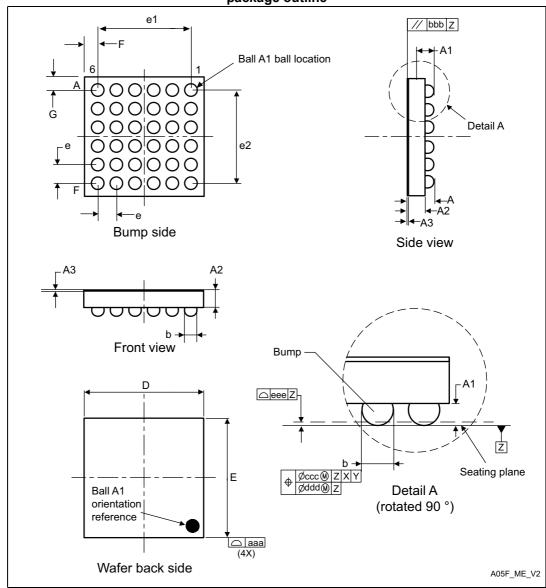

| Figure 42. | WLCSP36 - 36-pin, 2.553 x 2.579 mm, 0.4 mm pitch wafer level chip scale     |     |

|            | package recommended footprint                                               |     |

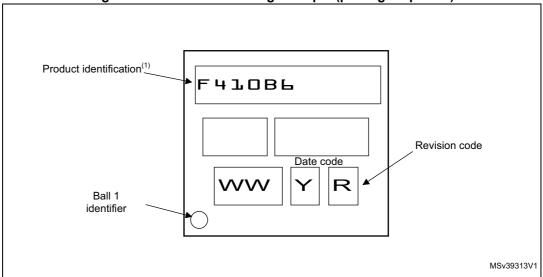

| Figure 43. | WLCSP36 marking example (package top view)                                  | 121 |

| Figure 44. | UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat   |     |

|            |                                                                             |     |

List of figures STM32F410x8/B

|            | package outline                                                                    | 122 |

|------------|------------------------------------------------------------------------------------|-----|

| Figure 45. | UFQFPN48 recommended footprint                                                     |     |

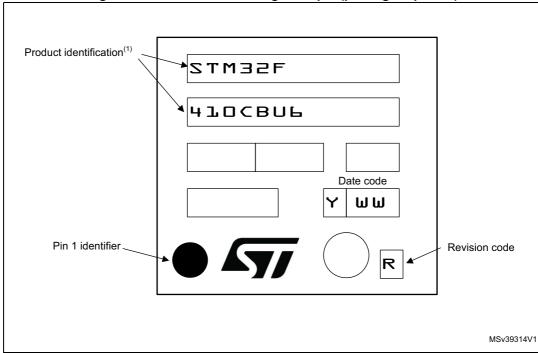

| Figure 46. | UFQFPN48 marking example (package top view)                                        |     |

| Figure 47. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline                    | 125 |

| Figure 48. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package                            |     |

|            | recommended footprint                                                              | 127 |

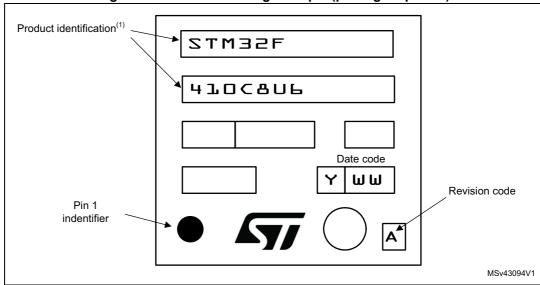

| Figure 49. | LQFP48 marking example (package top view)                                          | 128 |

| Figure 50. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline                  | 129 |

| Figure 51. | LQFP64 recommended footprint                                                       | 130 |

| Figure 52. | LQFP64 marking example (package top view)                                          | 131 |

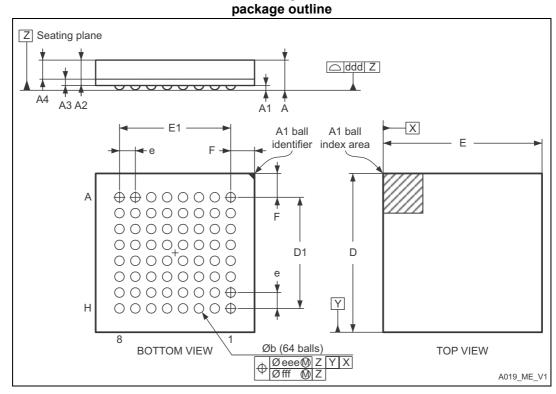

| Figure 53. | UFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch ultra profile fine pitch ball grid array |     |

|            | package outline                                                                    | 132 |

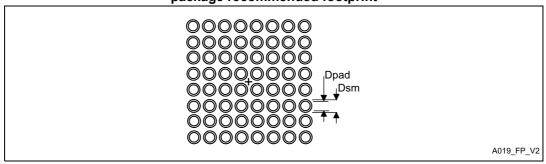

| Figure 54. | UFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch ultra profile fine pitch ball grid array |     |

|            | package recommended footprint                                                      | 133 |

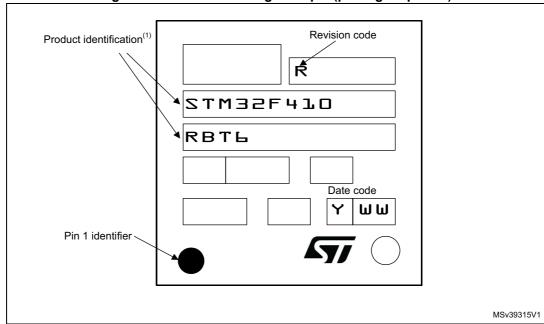

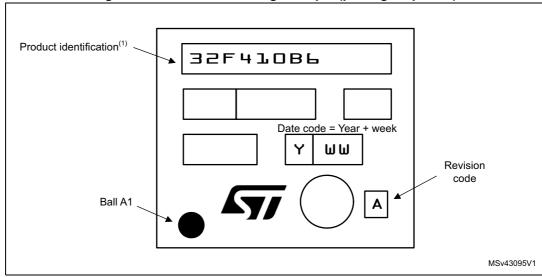

| Figure 55. | UFBGA64 marking example (package top view)                                         |     |

| Figure 56. | Sensor hub application example 1                                                   | 138 |

| Figure 57. | Sensor hub application example 2                                                   | 138 |

| Figure 58. | Batch Acquisition Mode (BAM) example                                               | 139 |

STM32F410x8/B Introduction

## 1 Introduction

This datasheet provides the description of the STM32F410x8/B microcontrollers. For information on the  $Cortex^{@}$ -M4 core, please refer to the  $Cortex^{@}$ -M4 programming manual (PM0214) available from www.st.com.

arm

Description STM32F410x8/B

## 2 Description

The STM32F410x8/B devices are based on the high-performance Arm<sup>®</sup> Cortex<sup>®</sup> -M4 32-bit RISC core operating at a frequency of up to 100 MHz. Their Cortex<sup>®</sup>-M4 core features a Floating point unit (FPU) single precision which supports all Arm single-precision data-processing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit (MPU) which enhances application security.

The STM32F410x8/B belong to the STM32 Dynamic Efficiency<sup>TM</sup> product line (with products combining power efficiency, performance and integration) while adding a new innovative feature called Batch Acquisition Mode (BAM) allowing to save even more power consumption during data batching.

The STM32F410x8/B incorporate high-speed embedded memories (up to 128 Kbytes of Flash memory, 32 Kbytes of SRAM), and an extensive range of enhanced I/Os and peripherals connected to two APB buses, one AHB bus and a 32-bit multi-AHB bus matrix.

All devices offer one 12-bit ADC, one 12-bit DAC, a low-power RTC, three general-purpose 16-bit timers, one PWM timer for motor control, one general-purpose 32-bit timers and one 16-bit low-power timer. They also feature standard and advanced communication interfaces.

- Up to three I<sup>2</sup>Cs

- Three SPIs

- Three I<sup>2</sup>Ss

To achieve audio class accuracy, the I<sup>2</sup>S peripherals can be clocked via the internal PLL or via an external clock to allow synchronization.

Three USARTs.

The STM32F410x8/B are offered in 5 packages ranging from 36 to 64 pins. The set of available peripherals depends on the selected package.

The STM32F410x8/B operate in the -40 to +125 °C temperature range from a 1.7 (PDR OFF) to 3.6 V power supply. A comprehensive set of power-saving mode allows the design of low-power applications.

These features make the STM32F410x8/B microcontrollers suitable for a wide range of applications:

- Motor drive and application control

- Medical equipment

- Industrial applications: PLC, inverters, circuit breakers

- · Printers, and scanners

- Alarm systems, video intercom, and HVAC

- Home audio appliances

- Mobile phone sensor hub

STM32F410x8/B Description

Table 2. STM32F410x8/B features and peripheral counts

| Peripherals                    |                       | STM32<br>F410<br>T8Y                                                       | STM32<br>F410<br>TBY | STM32<br>F410<br>C8U | STM32<br>F410<br>CBU | STM32<br>F410<br>C8T | STM32<br>F410<br>CBT | STM32<br>F410<br>R8T | STM32<br>F410<br>RBT | STM32<br>F410<br>R8I | STM32<br>F410<br>RBI |

|--------------------------------|-----------------------|----------------------------------------------------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| Flash memory in                | Kbytes                | 64                                                                         | 128                  | 64                   | 128                  | 64                   | 128                  | 64                   | 128                  | 64                   | 128                  |

| SRAM in Kbytes                 | System                |                                                                            |                      |                      |                      | 3                    | 2                    |                      |                      |                      |                      |

|                                | General-<br>purpose   |                                                                            |                      |                      |                      | 4                    | 4                    |                      |                      |                      |                      |

| Timers                         | Low-power timer       |                                                                            |                      |                      |                      |                      | 1                    |                      |                      |                      |                      |

|                                | Advanced-<br>control  |                                                                            |                      |                      |                      |                      | 1                    |                      |                      |                      |                      |

| Random number                  | generator             |                                                                            |                      |                      |                      |                      | 1                    |                      |                      |                      |                      |

|                                | SPI/ I <sup>2</sup> S | 1 3                                                                        |                      |                      |                      |                      |                      |                      |                      |                      |                      |

| Communication interfaces       | I <sup>2</sup> C      | 2                                                                          | 2                    | 3                    |                      |                      |                      |                      |                      |                      |                      |

|                                | USART                 | 2 3                                                                        |                      |                      |                      |                      |                      |                      |                      |                      |                      |

| GPIOs                          |                       | 23 36 50                                                                   |                      |                      |                      |                      |                      |                      |                      |                      |                      |

| 12-bit ADC                     |                       |                                                                            |                      | 1                    |                      |                      |                      |                      |                      |                      |                      |

| Number of channe               | els                   | 4 10 16                                                                    |                      |                      |                      |                      |                      |                      |                      |                      |                      |

| 12-bit DAC<br>Number of channe | els                   |                                                                            |                      |                      |                      |                      | 1<br>1               |                      |                      |                      |                      |

| Maximum CPU fre                | equency               | 100 MHz                                                                    |                      |                      |                      |                      |                      |                      |                      |                      |                      |

| Operating voltage              | )                     | 1.7 to                                                                     | 3.6 V                | 1.8 to               | 3.6 V                | 1.7 to               | 3.6 V                | 1.8 to               | 3.6 V                | 1.7 to               | 3.6 V                |

| On another a to see a          | -4                    | Ambient temperatures: - 40 to +85 °C / - 40 to + 105 °C / - 40 to + 125 °C |                      |                      |                      |                      |                      |                      |                      |                      |                      |

| Operating temper               | atures                |                                                                            |                      |                      | Junction             | temperatu            | ire: –40 to          | + 130 °C             |                      |                      |                      |

| Package                        |                       | WLC                                                                        | SP36                 | UFQF                 | PN48                 | LQF                  | P48                  | LQF                  | P64                  | UFB                  | GA64                 |

Description STM32F410x8/B

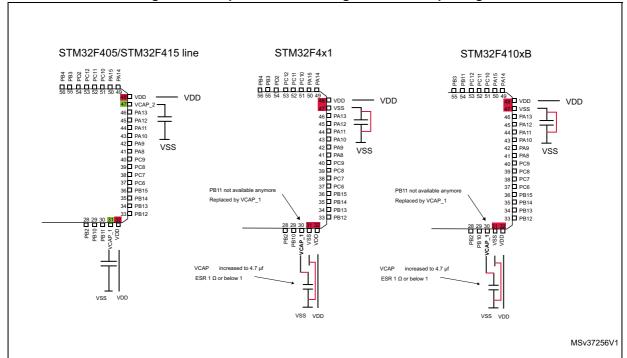

## 2.1 Compatibility with STM32F4 series

The STM32F410x8/B are fully software and feature compatible with the STM32F4 series (STM32F42x, STM32F401, STM32F43x, STM32F41x, STM32F405 and STM32F407)

The STM32F410x8/B can be used as drop-in replacement of the other STM32F4 products but some slight changes have to be done on the PCB board.

Figure 1. Compatible board design for LQFP64 package

1. For STM32F410xB devices, pin 54 is bonded to PB11 instead of PD2.

STM32F410x8/B Description

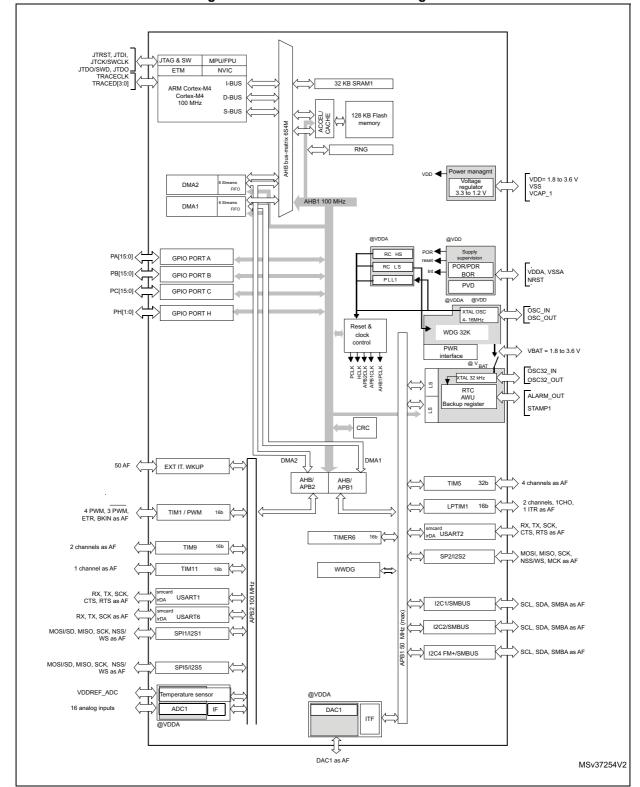

Figure 2. STM32F410x8/B block diagram

The timers connected to APB2 are clocked from TIMxCLK up to 100 MHz, while the timers connected to APB1 are clocked from TIMxCLK up to 100 MHz.

#### **Functional overview** 3

#### Arm® Cortex®-M4 with FPU core with embedded Flash and 3.1 **SRAM**

The Arm® Cortex®-M4 with FPU processor is the latest generation of Arm processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The Arm® Cortex®-M4 with FPU 32-bit RISC processor features exceptional codeefficiency, delivering the high-performance expected from an Arm core in the memory size usually associated with 8- and 16-bit devices. The processor supports a set of DSP instructions which allow efficient signal processing and complex algorithm execution. Its single precision FPU (floating point unit) speeds up software development by using metalanguage development tools, while avoiding saturation.

The STM32F410x8/B devices are compatible with all Arm tools and software.

Figure 2 shows the general block diagram of the STM32F410x8/B.

Cortex<sup>®</sup>-M4 with FPU is binary compatible with Cortex<sup>®</sup>-M3. Note:

#### 3.2 Adaptive real-time memory accelerator (ART Accelerator™)

The ART Accelerator™ is a memory accelerator which is optimized for STM32 industrystandard Arm<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processors. It balances the inherent performance advantage of the Arm<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU over Flash memory technologies, which normally requires the processor to wait for the Flash memory at higher frequencies.

To release the processor full 125 DMIPS performance at this frequency, the accelerator implements an instruction prefetch queue and branch cache, which increases program execution speed from the 128-bit Flash memory. Based on CoreMark benchmark, the performance achieved thanks to the ART Accelerator is equivalent to 0 wait state program execution from Flash memory at a CPU frequency up to 100 MHz.

#### 3.3 **Batch Acquisition mode (BAM)**

The Batch acquisition mode allows enhanced power efficiency during data batching. It enables data acquisition through any communication peripherals directly to memory using the DMA in reduced power consumption as well as data processing while the rest of the system is in low-power mode (including the flash and ART). For example in an audio system, a smart combination of PDM audio sample acquisition and processing from the I2S directly to RAM (flash and ART<sup>TM</sup> stopped) with the DMA using BAM followed by some very short processing from flash allows to drastically reduce the power consumption of the application. A dedicated application note (AN4515) describes how to implement the STM32F410x8/B BAM to allow the best power efficiency.

#### 3.4 Memory protection unit

The memory protection unit (MPU) is used to manage the CPU accesses to memory to prevent one task to accidentally corrupt the memory or resources used by any other active task. This memory area is organized into up to 8 protected areas that can in turn be divided up into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes of addressable memory.